DATA SHEET

HETERO JUNCTION FIELD EFFECT TRANSISTOR

NE32500, NE27200

C to Ka BAND SUPER LOW NOISE AMPLIFIER

N-CHANNEL HJ-FET CHIP

DESCRIPTION

NE32500 and NE27200 are Hetero Junction FET chip that utilizes the hetero junction between Si-doped AlGaAs

and undoped InGaAs to create high mobility electrons. Its excellent low noise and high associated gain make it suitable

for commercial systems, industrial and space applications.

FEATURES

• Super Low Noise Figure & High Associated Gain

NF = 0.45 dB TYP., Ga = 12.5 dB TYP. at f = 12 GHz

• Gate Length : L

• Gate Width : Wg = 200 µm

g = 0.2

µ

m

ORDERING INFORMATION

PART NUMBER QUALITY GRADE

NE32500 Standard (Grade D)

NE27200 Special, specific (Grade C and B)

ABSOLUTE MAXIMUM RATINGS (TA = 25 ˚C)

Drain to Source Voltage VDS 4.0 V

Gate to Source Voltage V

Drain Current ID IDSS mA

Total Power Dissipation Ptot* 200 mW

Channel Temperature T

Storage Temperature Tstg –65 to +175 °C

* Chip mounted on a Alumina heatsink (size: 3 × 3 × 0.6t)

GS –3.0 V

ch 175 °C

ELECTRICAL CHARACTERISTICS (TA = 25 ˚C)

PARAMETER SYMBOL MIN. TYP. MAX. UNIT TEST CONDITIONS

Gate to Source Leak Current IGSO – 0.5 10

Saturated Drain Current IDSS 20 60 90 mA VDS = 2 V, VGS = 0 V

Gate to Source Cutoff Voltage VGS(off) –0.2 –0.7 –2.0 V VDS = 2 V, ID = 100 µA

Transconductance gm 45 60 – mS VDS = 2 V, ID = 10 mA

Thermal Resistance Rth* – – 260 ˚C/W channel to case

Noise Figure NF – 0.45 0.55 dB VDS = 2 V, ID = 10 mA, f = 12 GHz

Associated Gain Ga 11.0 12.5 – dB

µ

AVGS = –3 V

RF performance is determined by packaging and testing 10 chips per wafer.

Wafer rejection criteria for standard devices is 2 rejects per 10 samples.

Document No. P11512EJ2V0DS00 (2nd edition)

Date Published January 1997 N

Printed in Japan

©

1996

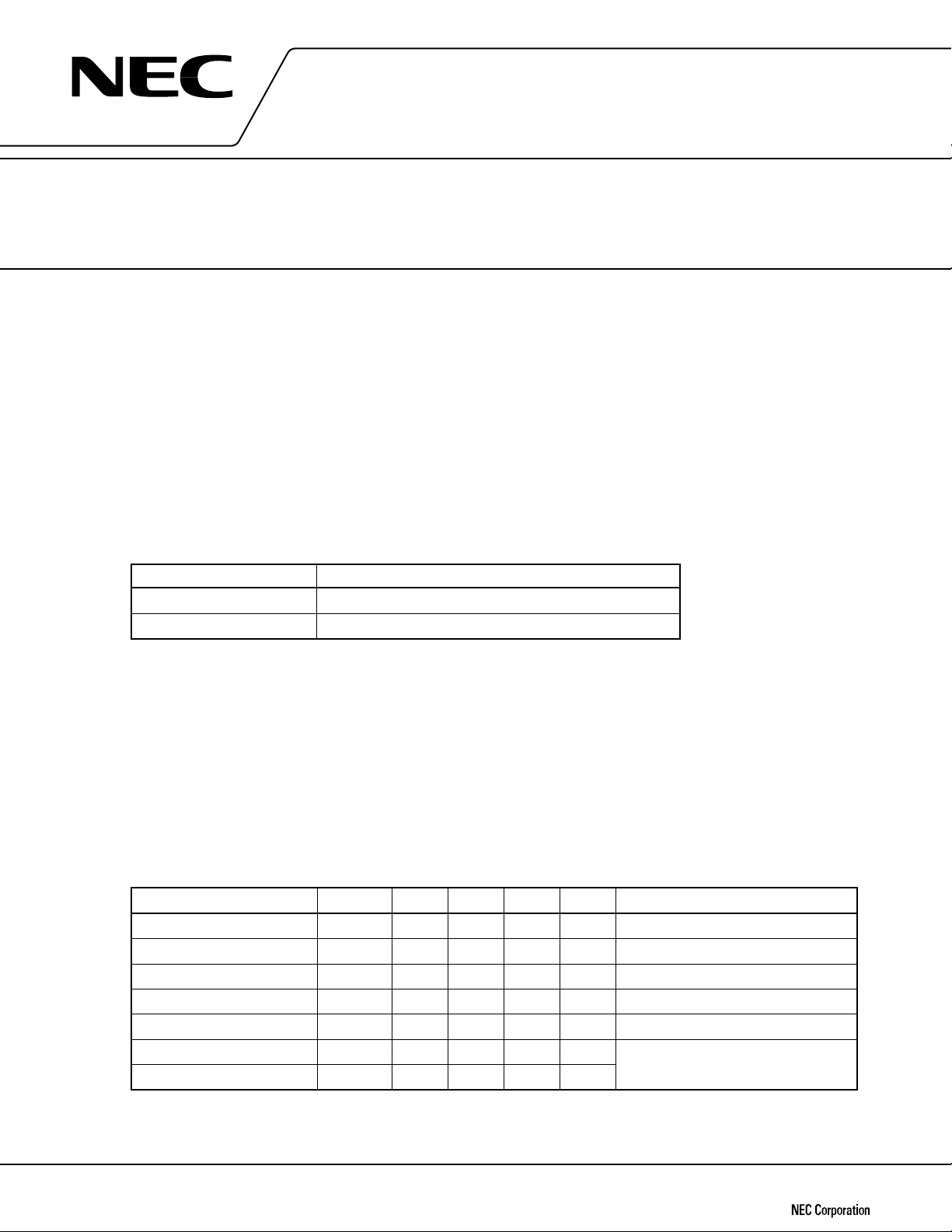

CHIP DIMENSIONS (Unit: µm)

5.5 13

58 36.5 66 25

NE32500, NE27200

2589

13

350

25 21 76.5100.5

Thickness = 140 m

: BONDING AREA

Source Source

25 49.5 4366

13

µ

Drain

Gate

350

38

686046.5

TYPICAL CHARACTERISTICS (TA = 25 ˚C)

TOTAL POWER DISSIPATION vs.

AMBIENT TEMPERATURE

250 100

200

150

100

50

– Total Power Dissipation – mW

tot

P

0050 1.5 3.0100 150 200 250

T

A

– Ambient Temperature – ˚C VDS – Drain to Source Voltage – V

DRAIN CURRENT vs.

DRAIN TO SOURCE VOLTAGE

80

60

40

– Drain Current – mA

D

I

20

VGS = 0 V

–0.2 V

–0.4 V

–0.6 V

–0.8 V

2

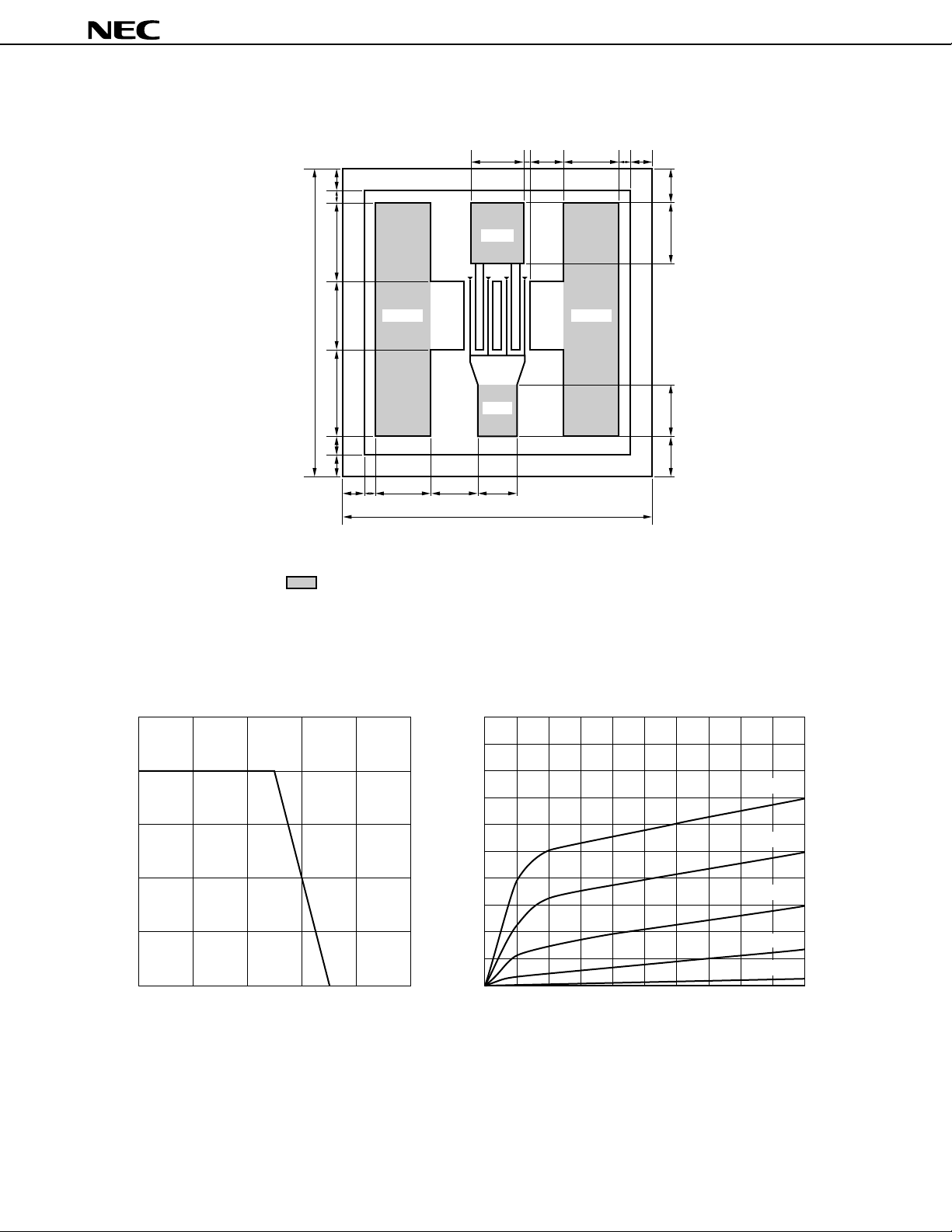

DRAIN CURRENT vs.

GATE TO SOURCE VOLTAGE

60

40

– Drain Current – mA

D

20

I

V

DS

NE32500, NE27200

= 2 V

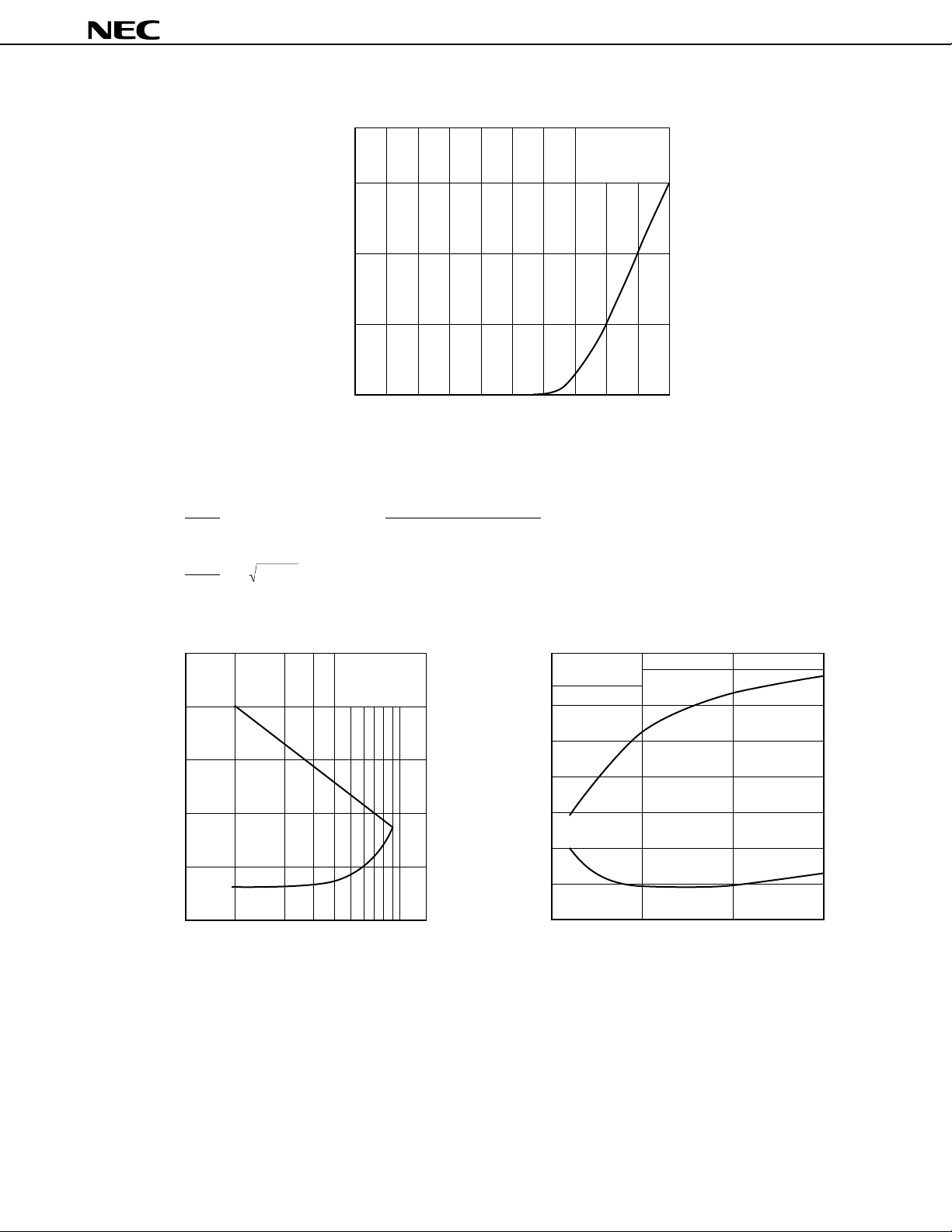

Gain Calculations

||

S

MSG. =

MAG.

21

12

||

S

|S |

21

12

|S |

(K K 1)

=±−

NOISE FIGURE, ASSOCIATED GAIN vs.

FREQUENCY

Ga

1.0

0

–1.0–2.0 0

GS

– Gate to Source Voltage – V

V

2

1 | | |S | |S |

+− −

K

2

∆

∆

=

2|S ||S |

=⋅−⋅SS SS11 22 21 12

2

11

12 21

2

22

NOISE FIGURE, ASSOCIATED GAIN vs.

DRAIN CURRENT

V

DS = 2 V

I

D = 10 mA

24

20

V

DS = 2 V

f = 12 GHz

14

G

a

13

12

16

11

10

12

2.0

1.5

NF – Noise Figure – dB

0.5

a – Associated Gain – dB

G

8

1.0

NF – Noise Figure – dB

0.5

NF

0

1246810142030 10020

4

f – Frequency – GHz I

NF

30

D – Drain Current – mA

a – Associated Gain – dB

G

3

Loading...

Loading...