Page 1

NCR

53C700/53C700-66

SCSI

1/0

Processor

Data

Manual

Page 2

The

product(s) described in this publication

is

a licensed product

of

NCR

Corporation.

TolerANT and SCSI SCRIPTS are registered trademarks

It

is

the policy

firmware become available.

without notice.

NCR

products are

product in such applications without the written consent

For information on updates to this or other

Division electronic bulletin board at (719) 596-1649.

Copyright ©1993

By

NCR

Dayton, Ohio

All

Rights Reserved

Printed in

of

NCR

not

Corporation

U.S.A.

U.S.A.

Corporation to improve products

NCR

Corporation, therefore, reserves the right to change specifications

intended for use in life-suppott appliances, devices, or systems. Use

NCR

products, contact the

of

NCR

Corporation.

as

new technology, components, software, and

of

an

ofthe

appropriate

NCR

NCR

officer

Microelectronic Products

is

prohibited.

NCR

c

Page 3

Preface

SCSI

This manual assumes some prior knowledge

Specifications

of

current

and

proposed

SCSI

standards.

For

background

information, please contact:

ANSI

11

West

42nd

Street

New

York,

NY

10036

(212) 642-4900

Ask for document

Global Engineering

2805

McGaw

number

Documents

X3.131-1986 (SCSI-I)

Irvine, CA 92714

or

(800)-854-7179

.?

Ask for document

ENDL

Publications

14426 Black Walnut

(714) 261-1455

number

X3.131-199X (SCSI-2)

Court

Saratoga, CA 95070

(408) 867-6642

Document

names:

SCSI

Bench Reference,

SCSI

Encyclopedia

Prentice Hall

Englewood Cliffs,

NJ

07632

(201) 767-5937

Ask for document

face

number

ISBN

0-13-796855-8,

SCSI:

Understanding the Small Computer System Inter-

NCR

Microelectronic Products

(719) 596-1649

The

SCSI

Electronic Bulletin

(719) 574-0424

NCR

53C700/53C700-66

Data

Manual

Division

Board

Electronic Bulletin

Board

Page 4

Revision Record

Page

No.

Dale

Remarks

nJa

nJa

nJa

nJa

7-1

nJa

10/89

12/89

2190

1/92

2192

11/92

Revision 2.3, Draft

Revision 2.4, Draft

Revision 2.5, Draft

Revision

Added

Revision

3.0, Preliminary, Added the

Input

Leakage-SCSI

4.0, Final, Reformatted to new standard

NCR

53C700-66 and

RST

electrical specification

NCR

TolerANT

ii

NCR

53C700/53C700-66

Data

Manual

Page 5

Table

Preface .......................................................................................................................................... i

of

Contents

Chapter

One

Introduction

General Description ...................................................................................................................

SlOP

Features Summary ......................................................................................................

Chapter

NCR's

Benefit Summary .................................................................................................................. 1-2

Two

TolerANTTM Active Negation Technology .................................................................

Functional Description

SCSI

Core ...........................................................................................................................

DMA

SCSI

SlOP

How

16-Bit

80286

80386

32-Bit

80486/80386

How

How

Interrupts ............................................................................................................................. 2-8

Core ..........................................................................................................................

SCRIPTS

Data

the

SlOP

Data

Mode

Mode

Data

the

SlOP

to Transfer

Processor .................................................................................................... 2-2

Paths .................................................................................................................. 2-2

Transfers16

Transfers for Bus Master Read

16-Bit

16-Bit

Transfers ........................................................................................................... 2-6

Mode

Data

Data

.............................................................................................................. 2-6

Fetches Instructions ...................................................................................... 2-6

Data

or

32-Bit

Transfers ....................................................................................... 2-4

Transfers ................................................................. , ..................... 2-5

as

a Bus Master .................................................................................. 2-6

Data

............................................................................ 2-3

and

Write Cycles 80286 Mode

or

80386

Mode

1-1

1-1

1-1

2-1

2-1

.... 2-4

Chapter

Three

Signal Descriptions

NCR

53C700/53C700·66

Data

Manual

iii

Page 6

Chapter

Four

Registers

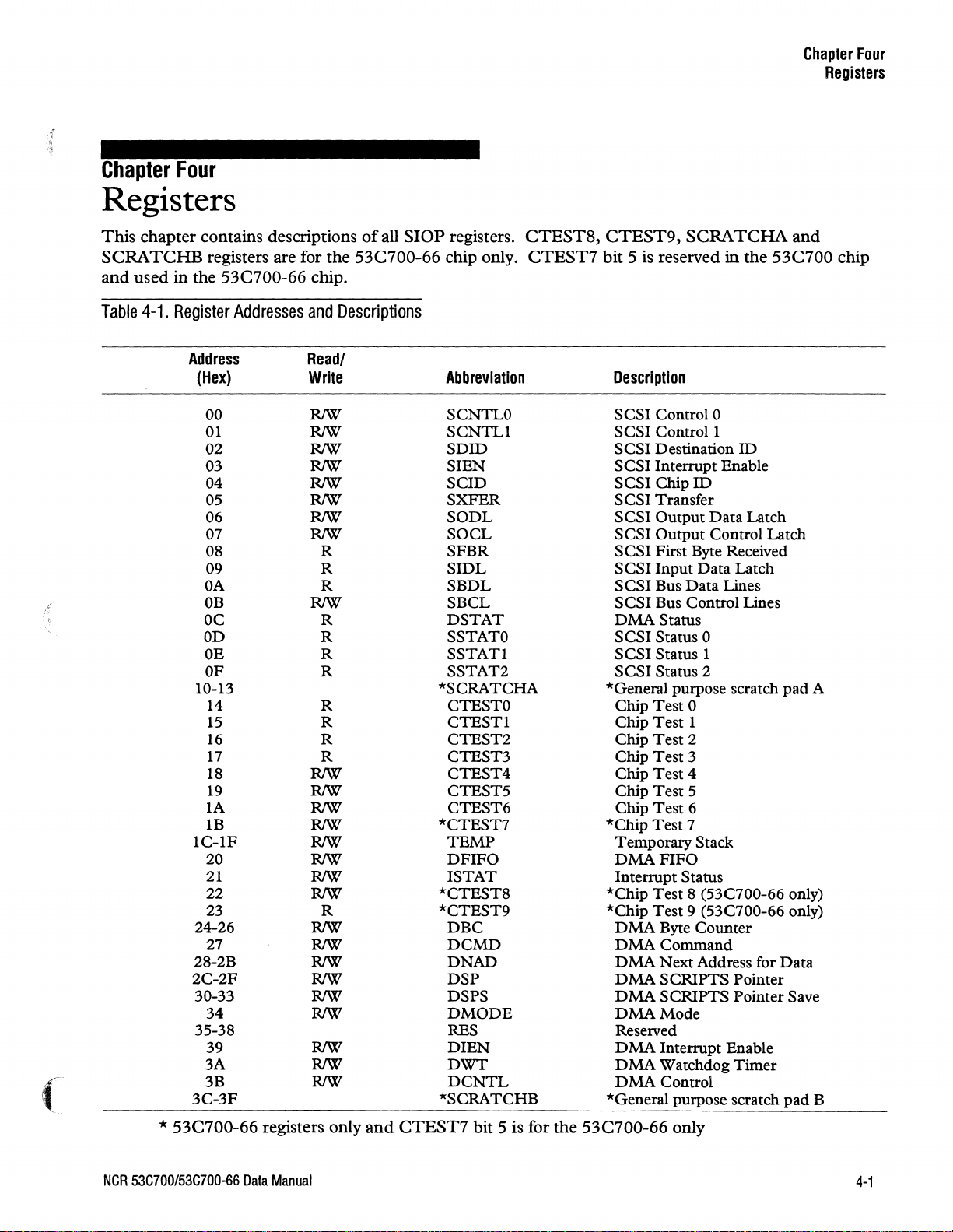

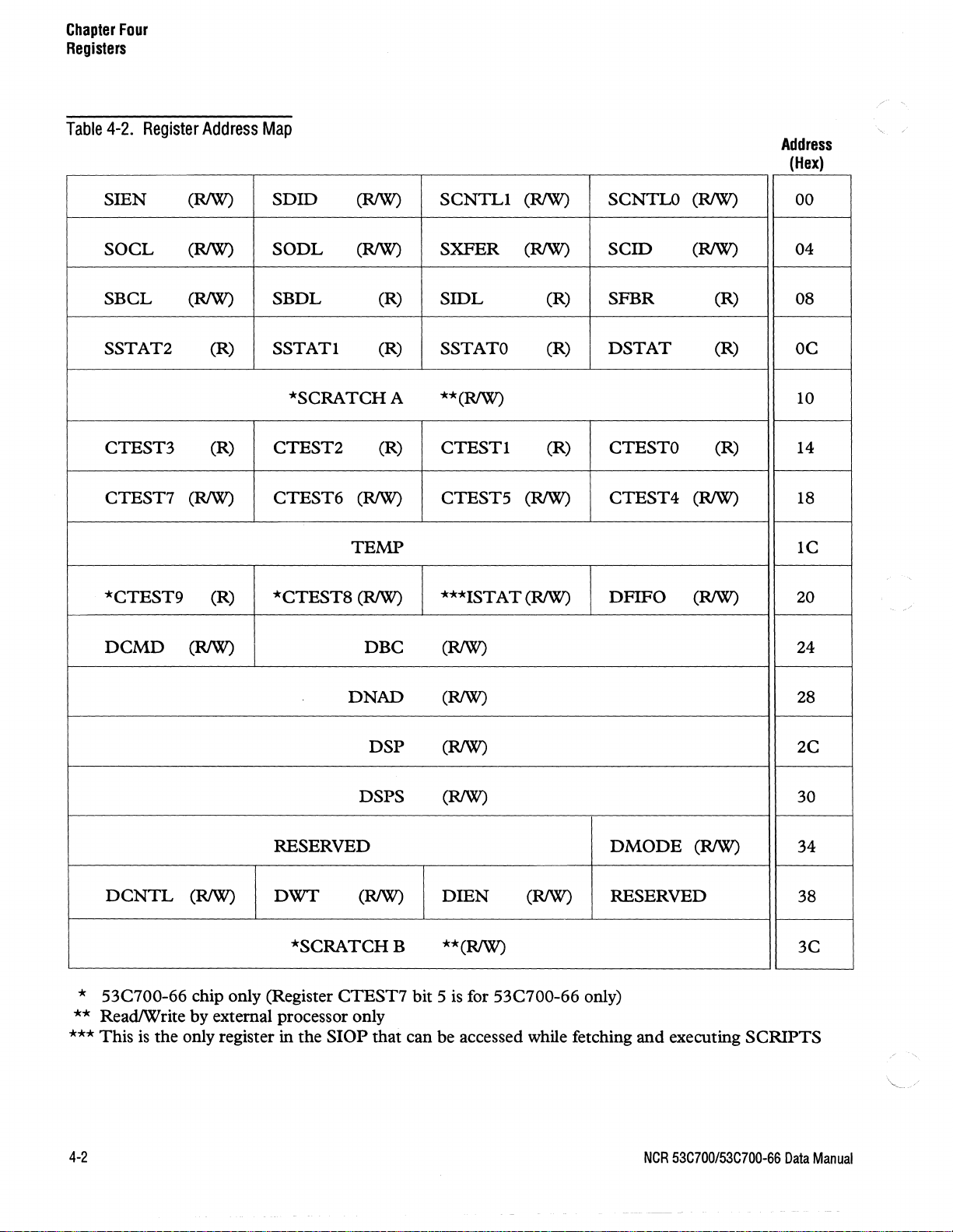

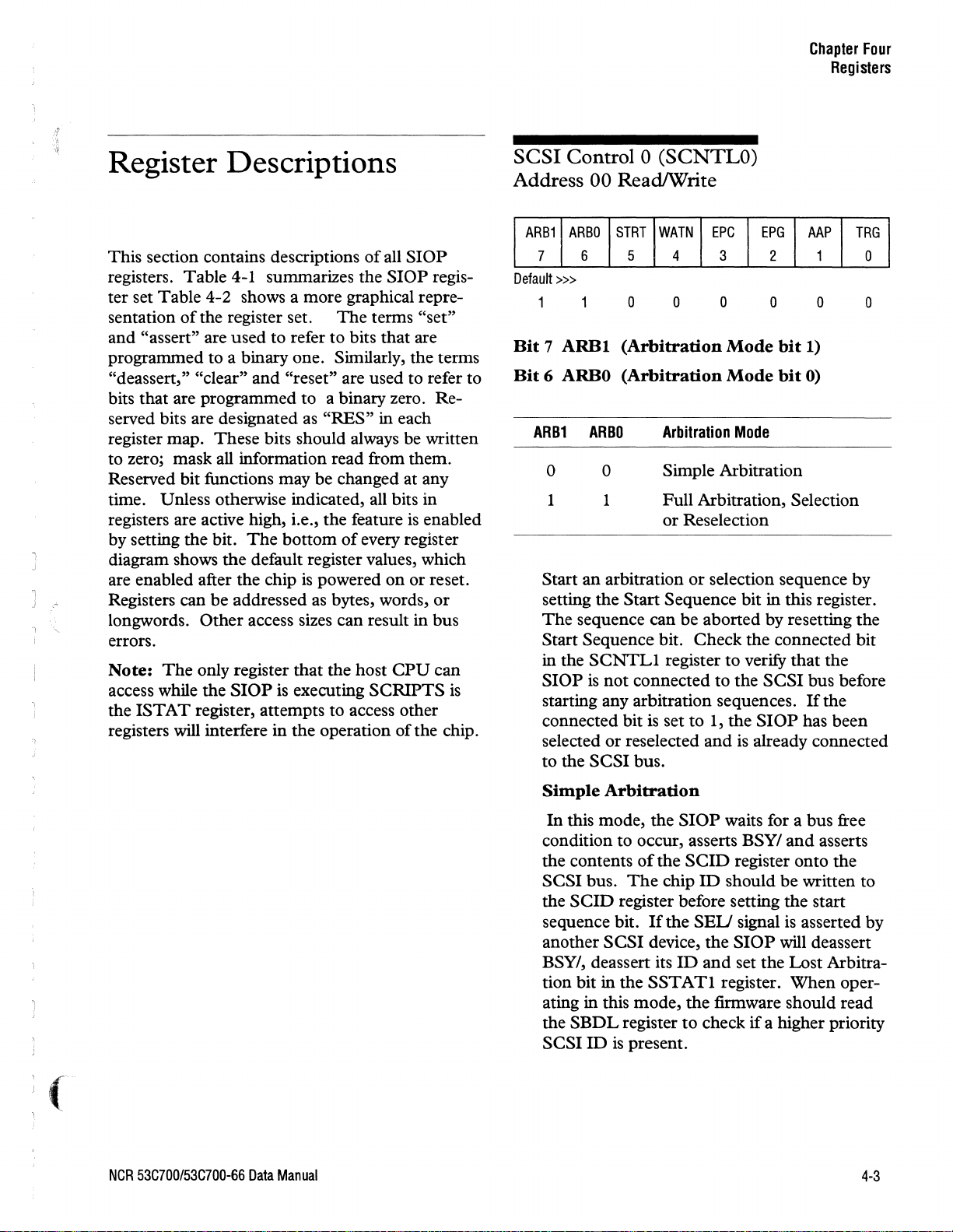

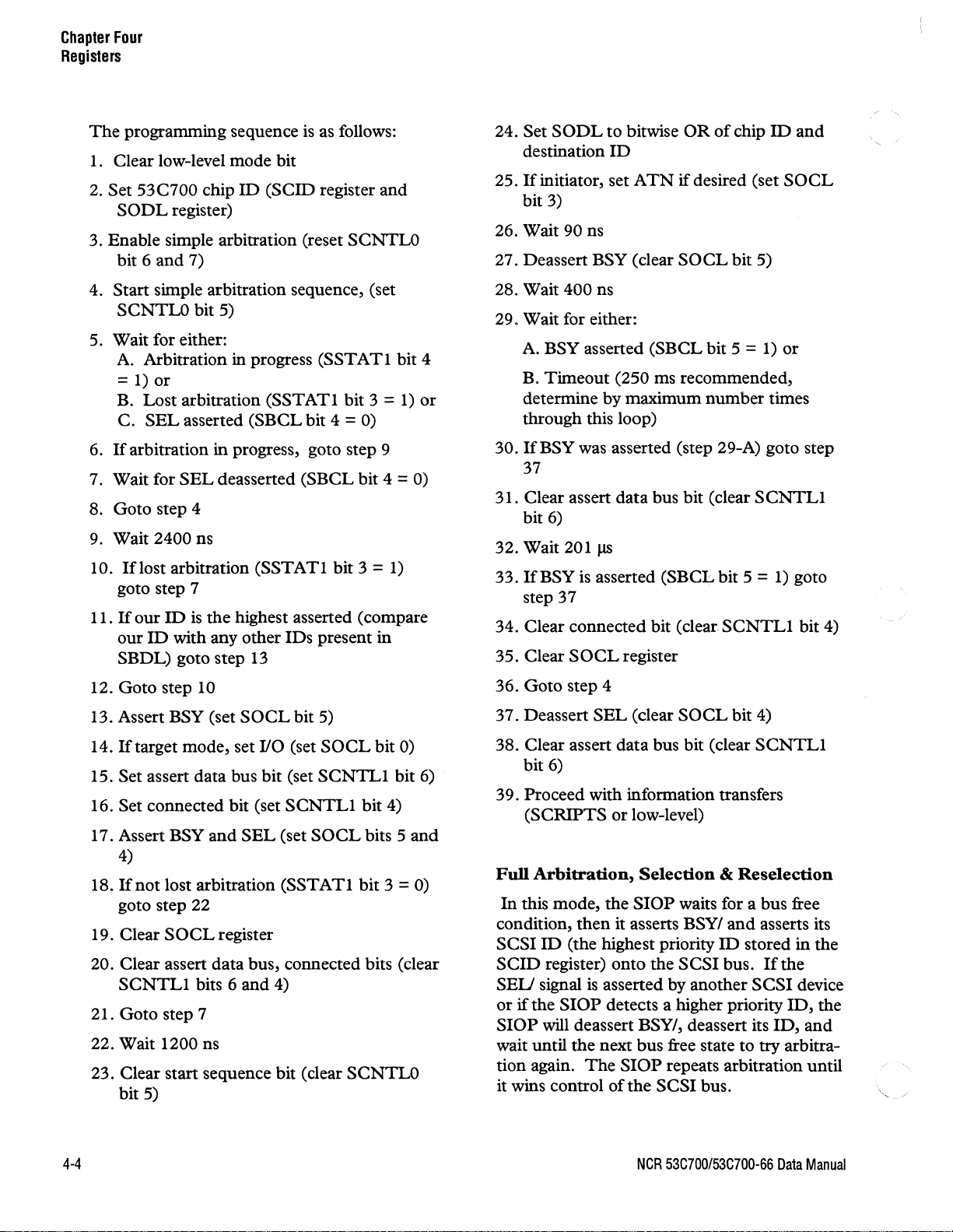

Register Descriptions ................................................................................................................. 4-3

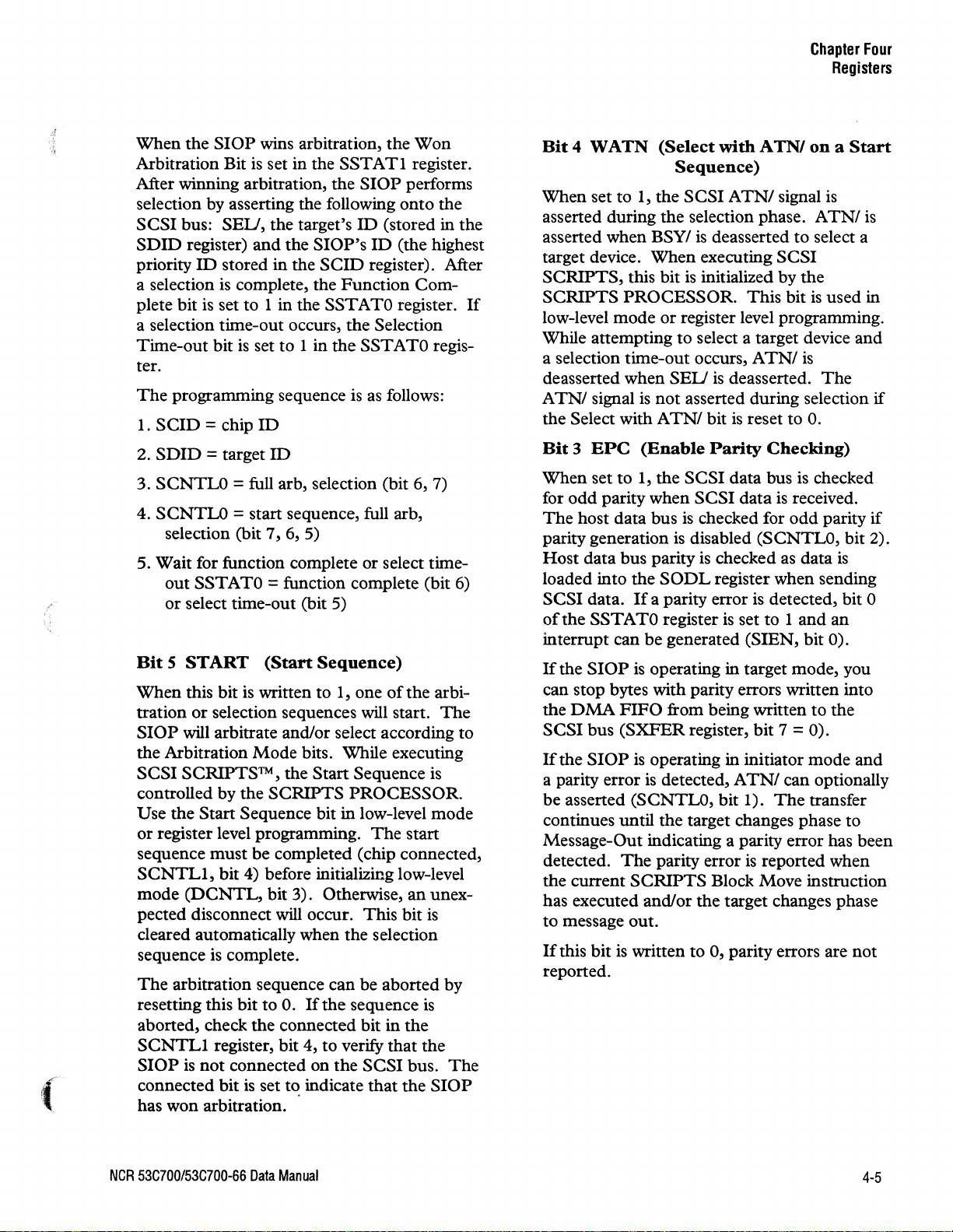

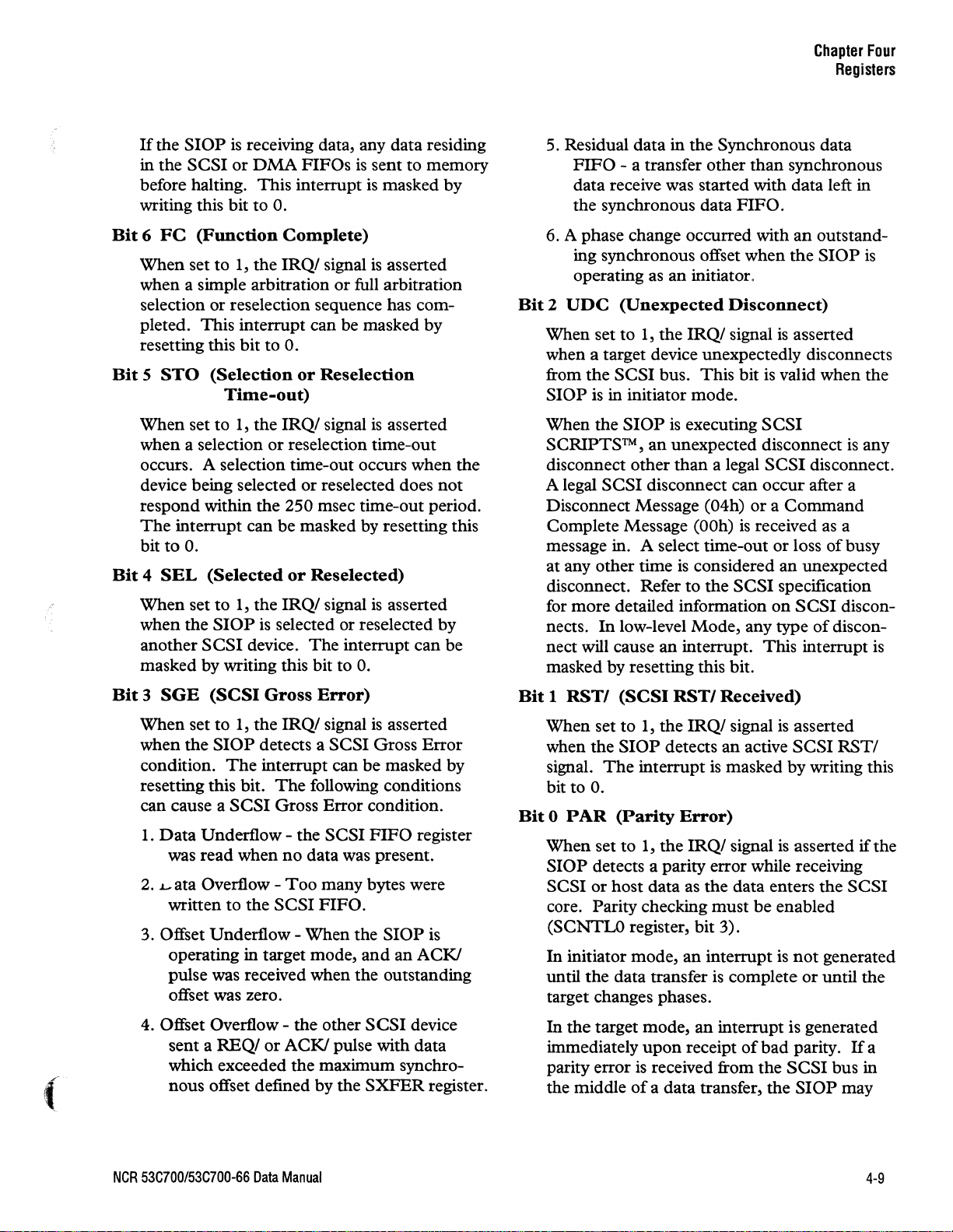

SCSI Control 0 (SCNTLO), Address 00 ReadlWrite ............................................................ .4-3

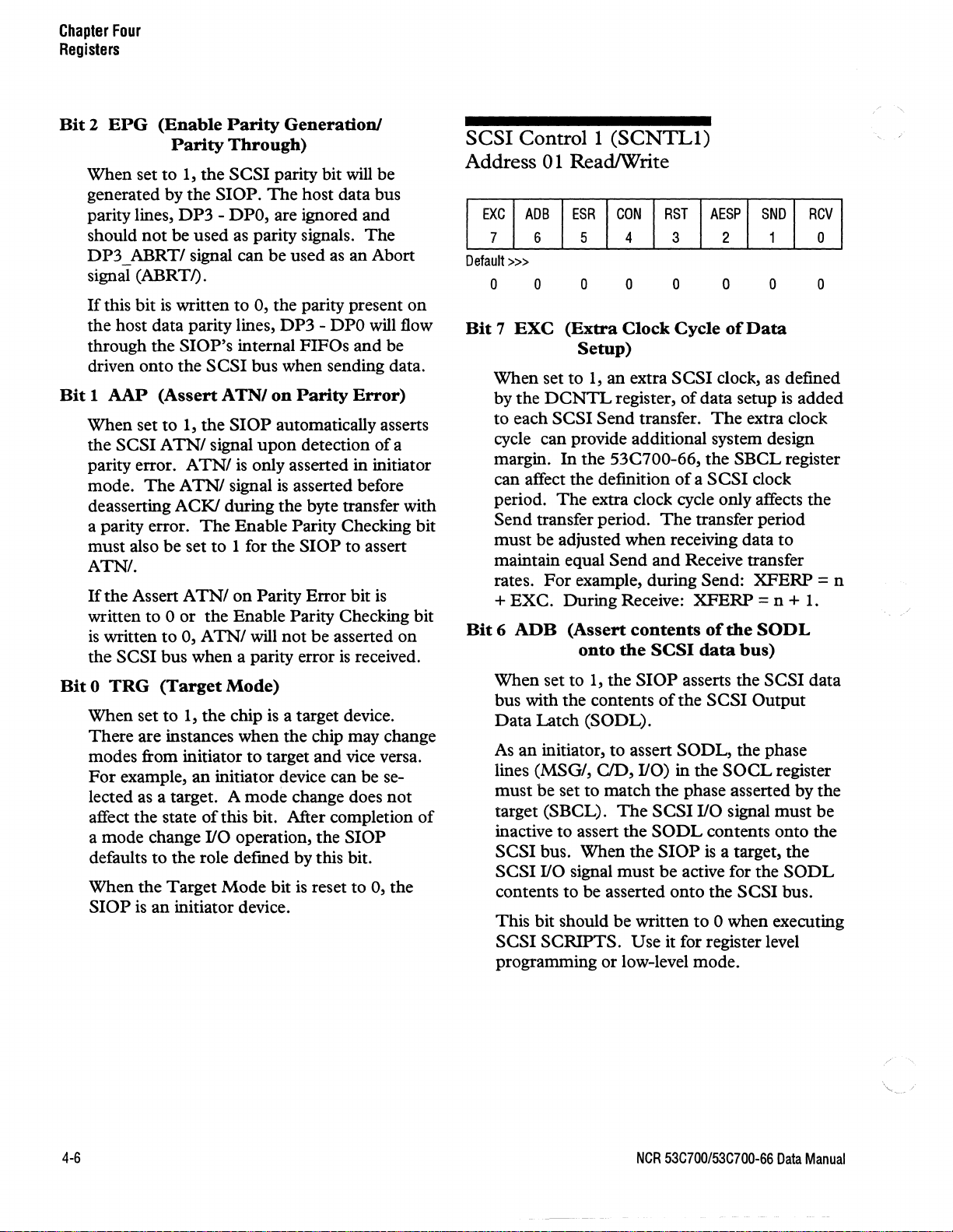

SCSI Control 1

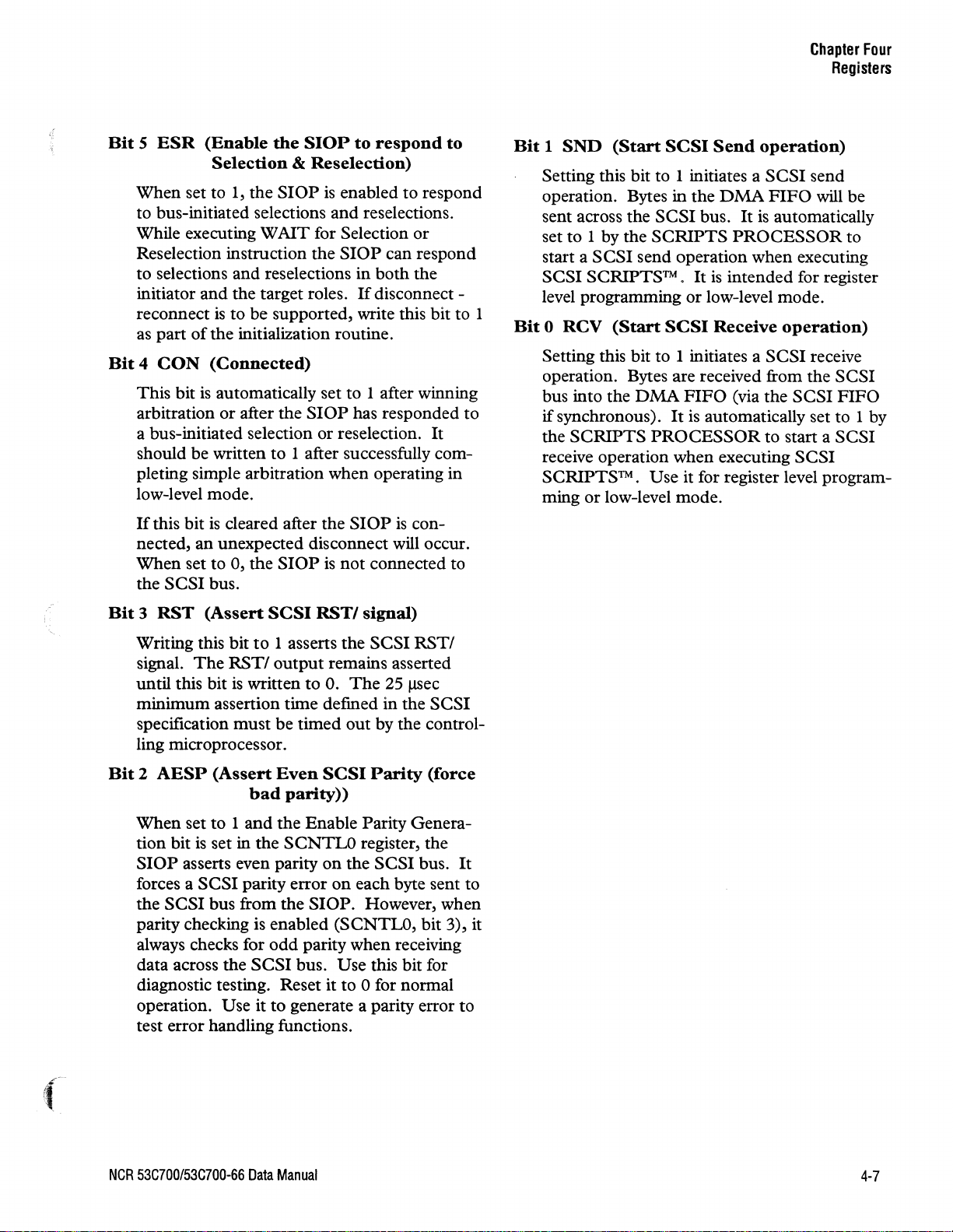

SCSI Destination

(SCNTLl),

ID

(SDID), Address 02 ReadIWrite .......................................................... .4-8

Address

01

ReadlWrite ............................................................ .4-6

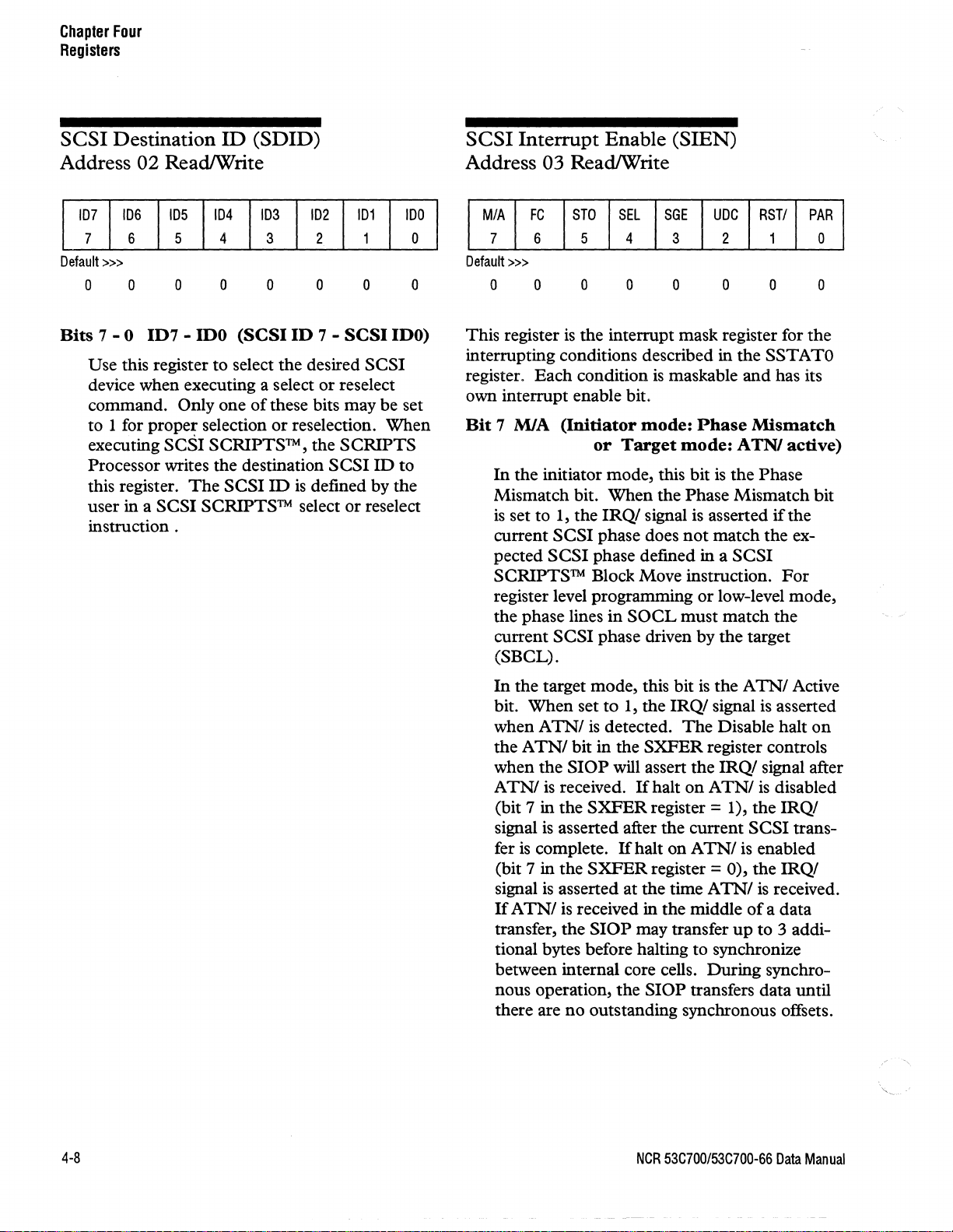

SCSI Interrupt Enable (SIEN), Address 03 ReadIWrite .........................................................

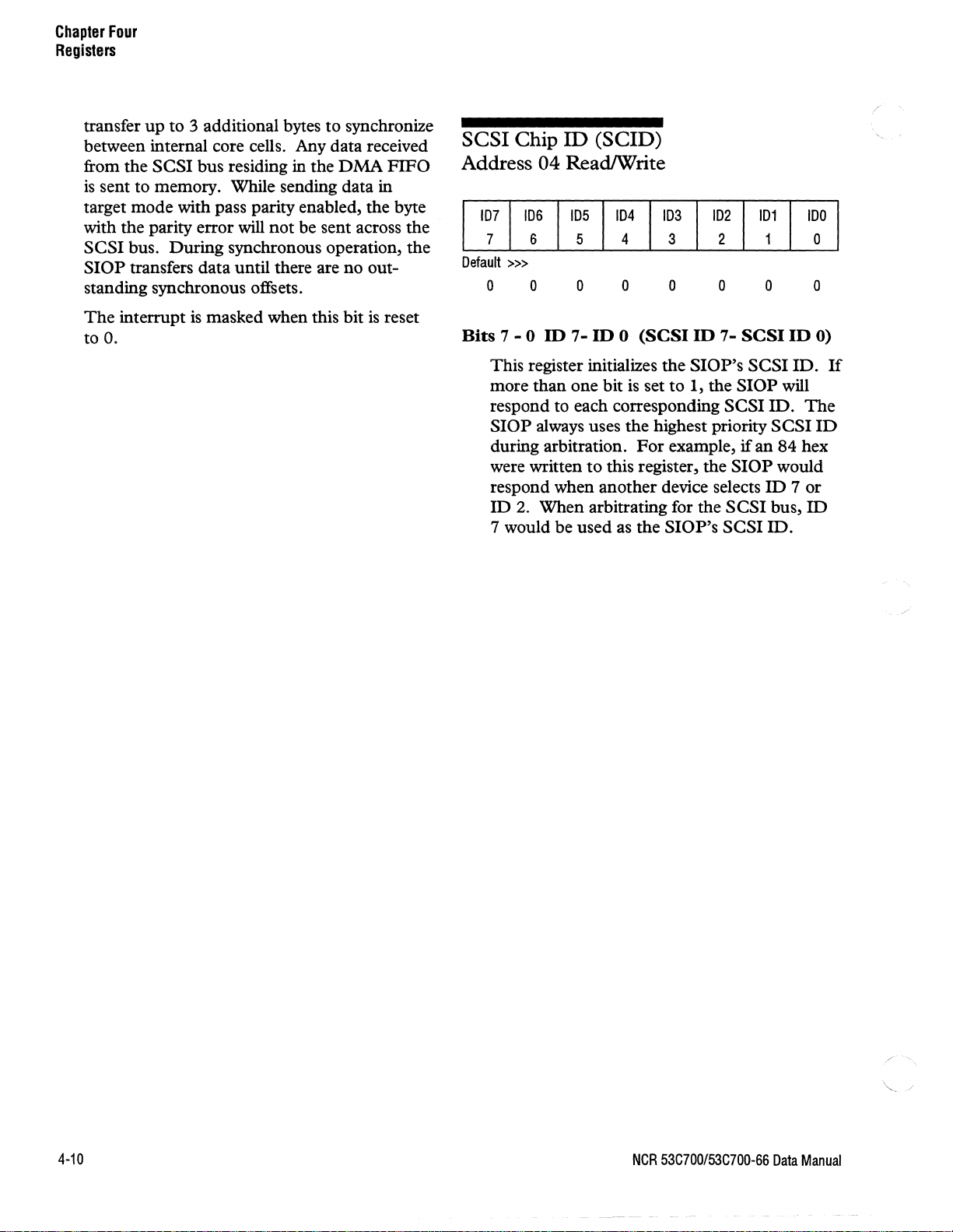

SCSI Chip

SCSI

SCSI

SCSI

ID

(SCID), Address 04 ReadIWrite ................................................................... 4-10

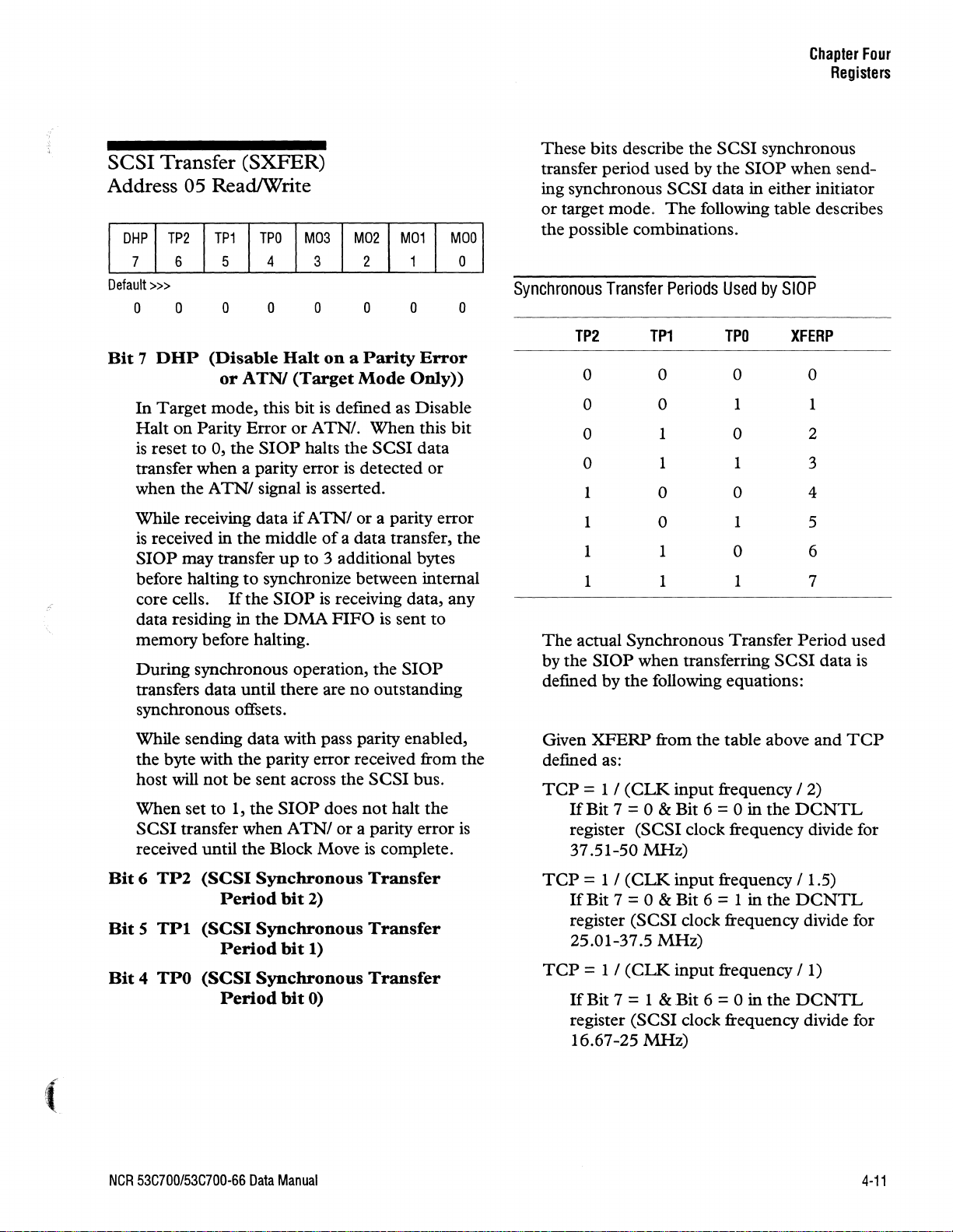

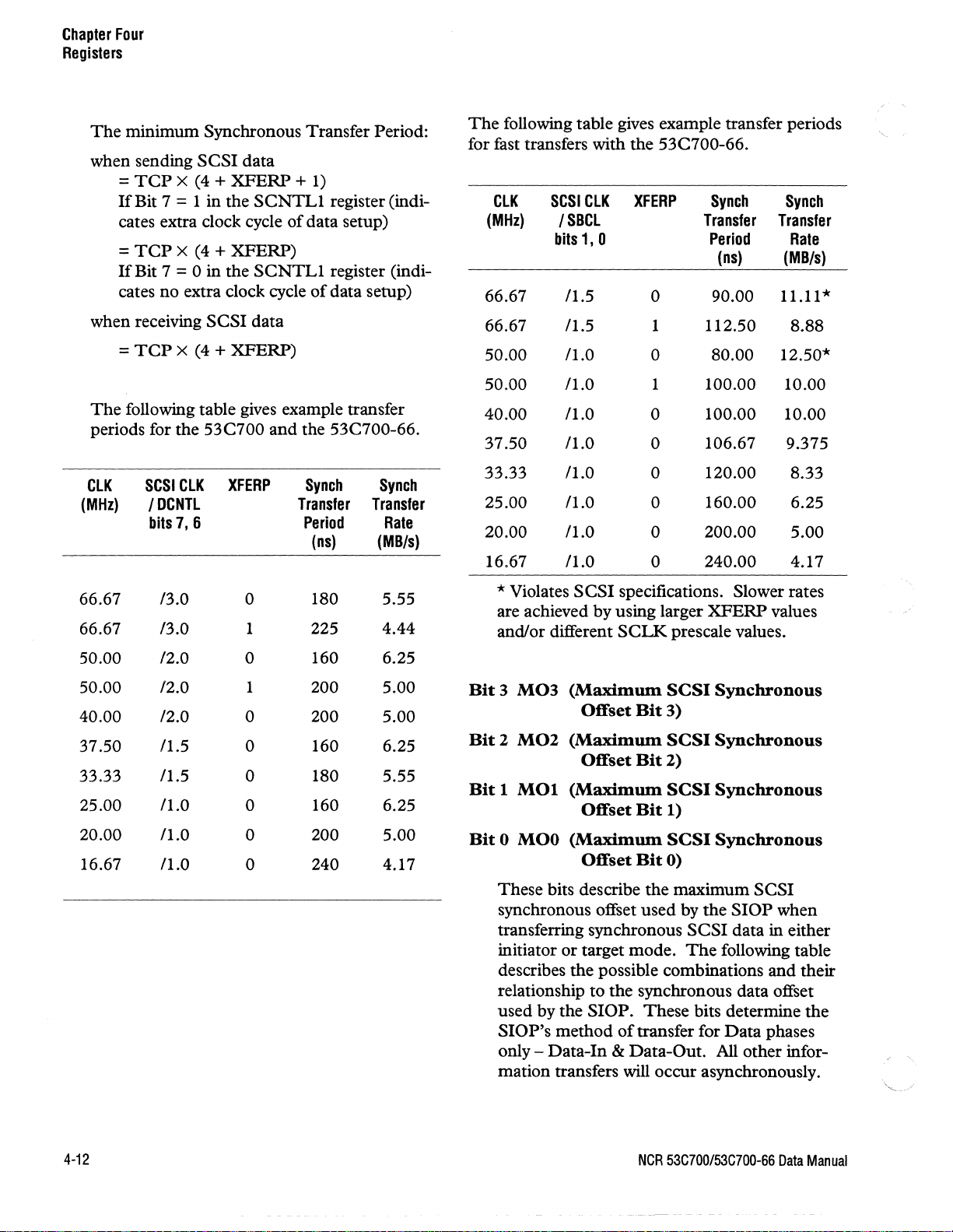

Transfer (SXFER), Address 05 ReadlWrite ............................................................... .4-11

Output

Output

Data

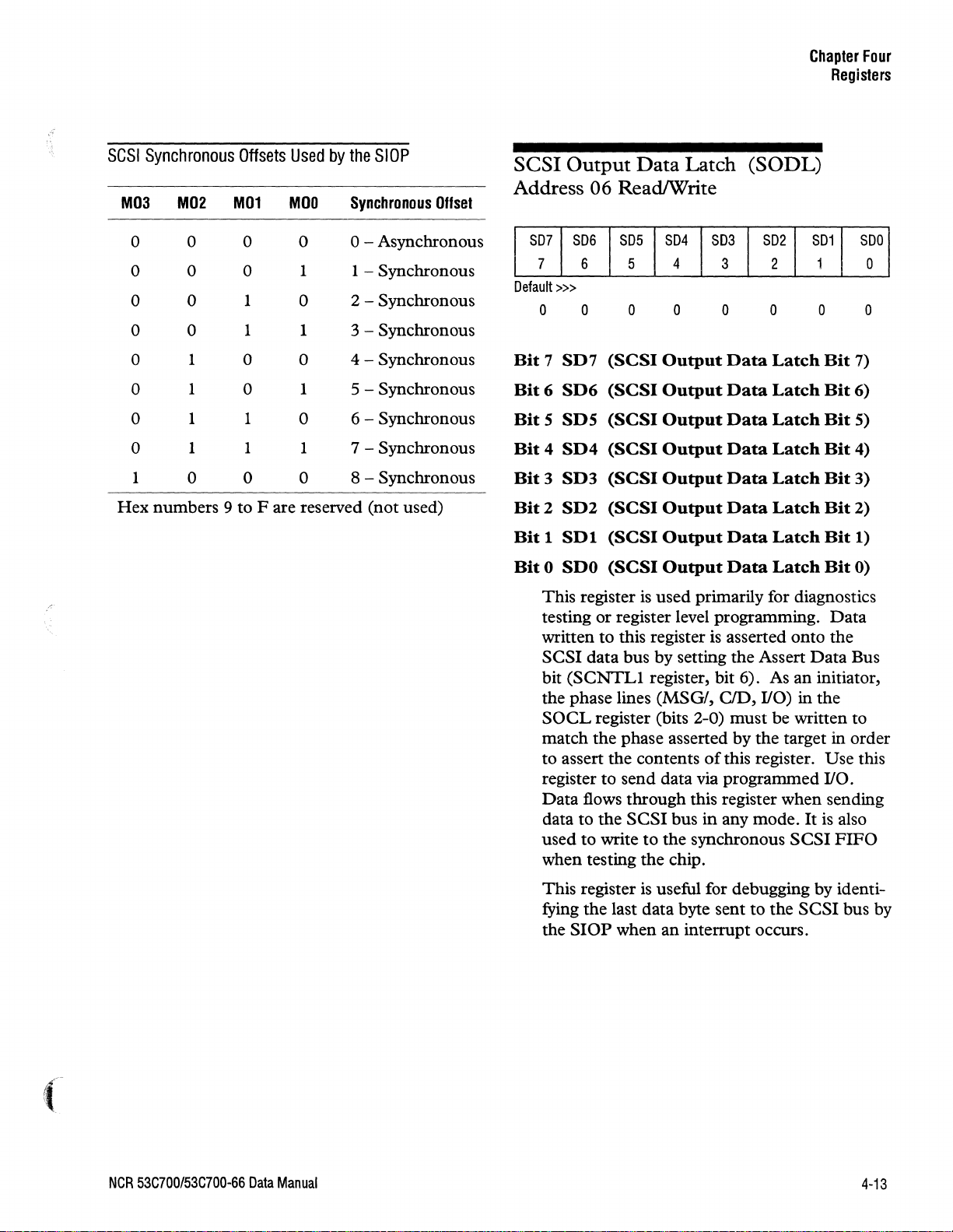

Latch (SODL), Address 06 ReadIWrite ................................................ .4-13

Control Latch (SOCL), Address 07 ReadlWrite .............................................. 4-14

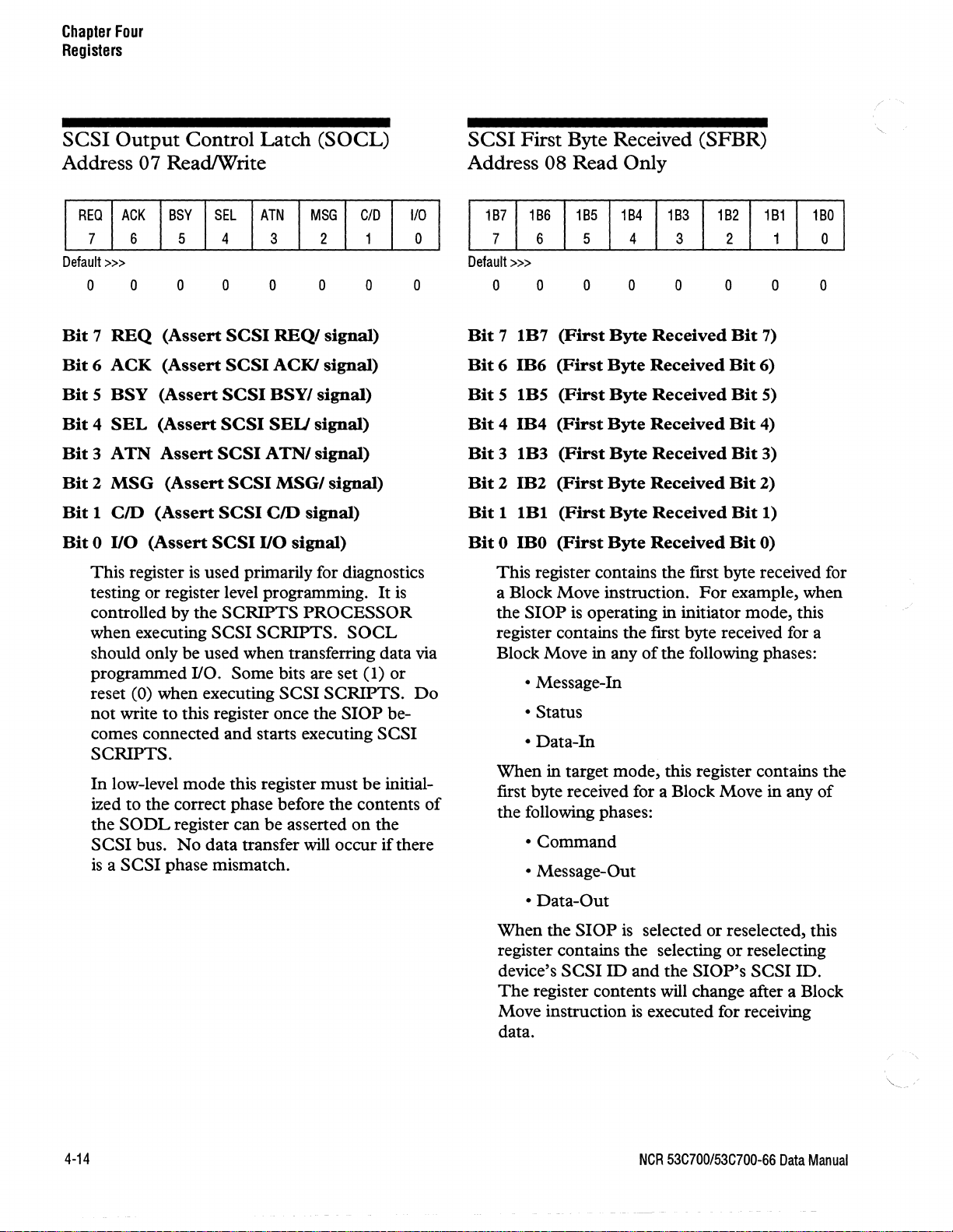

SCSI First Byte Received (SFBR), Address 08 Read Only .................................................. .4-14

SCSI

Input

SCSI Bus

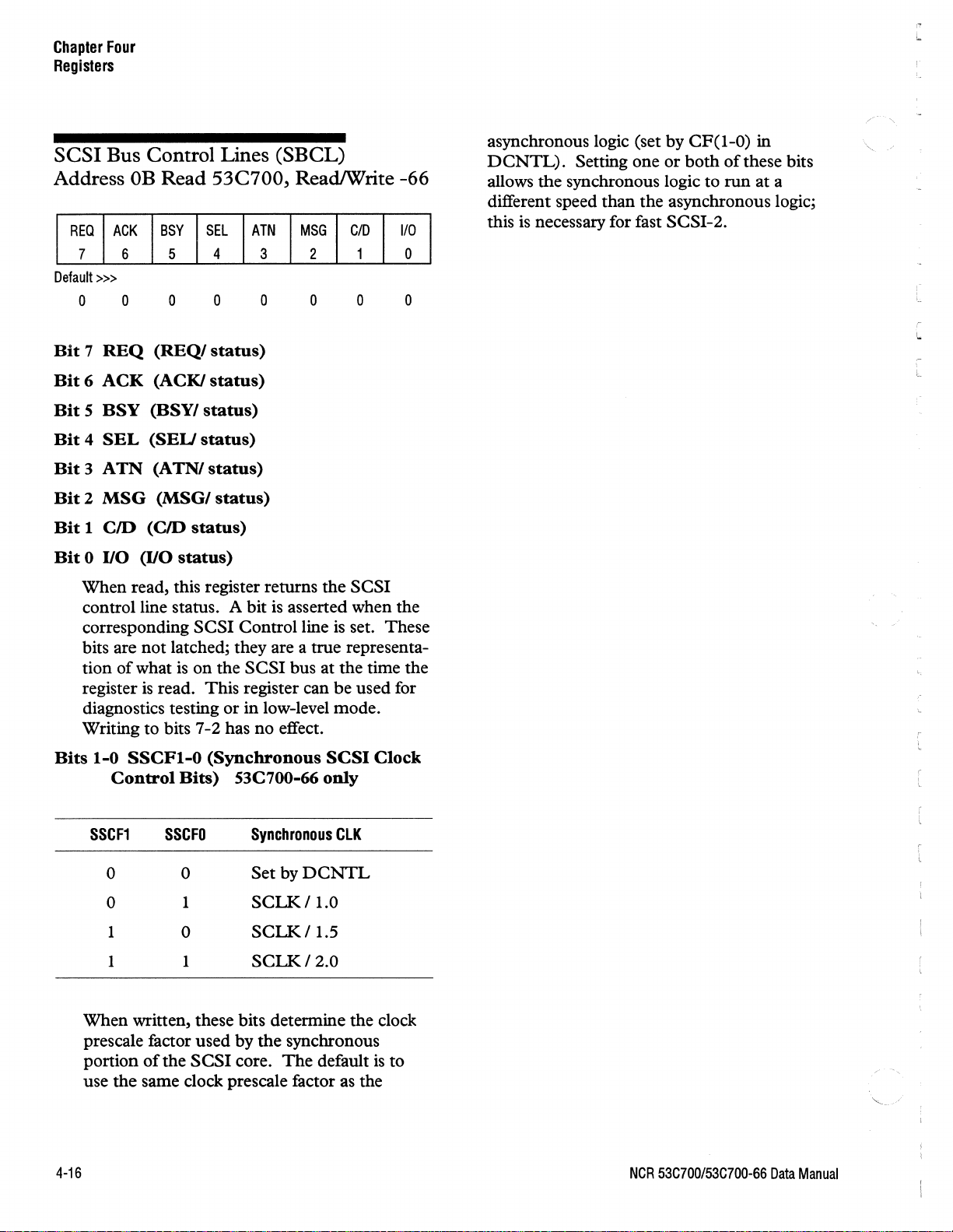

SCSI Bus Control Lines (SBCL), Address

DMA

SCSI

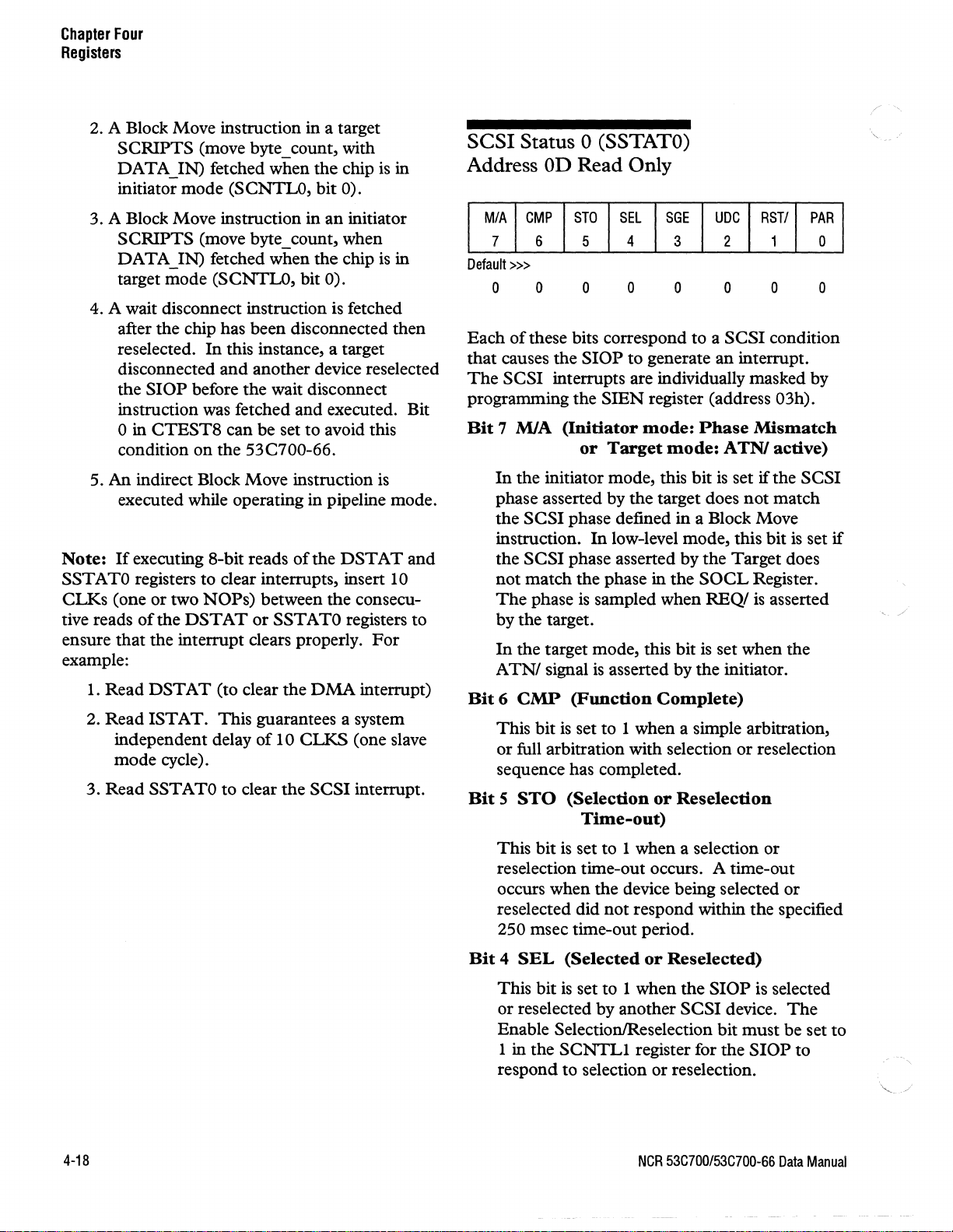

Status 0 (SSTATO), Address

SCSI

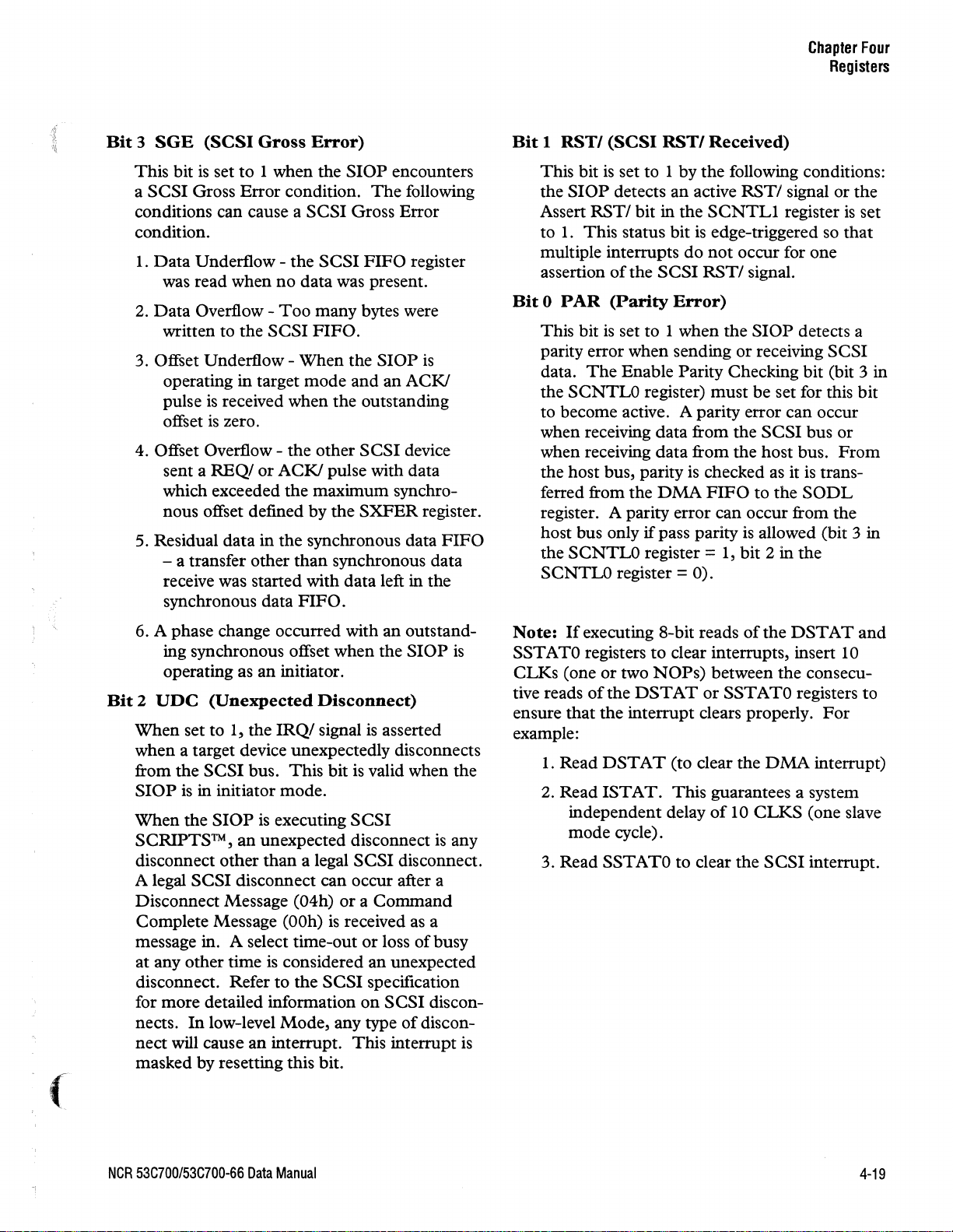

Status 1

SCSI

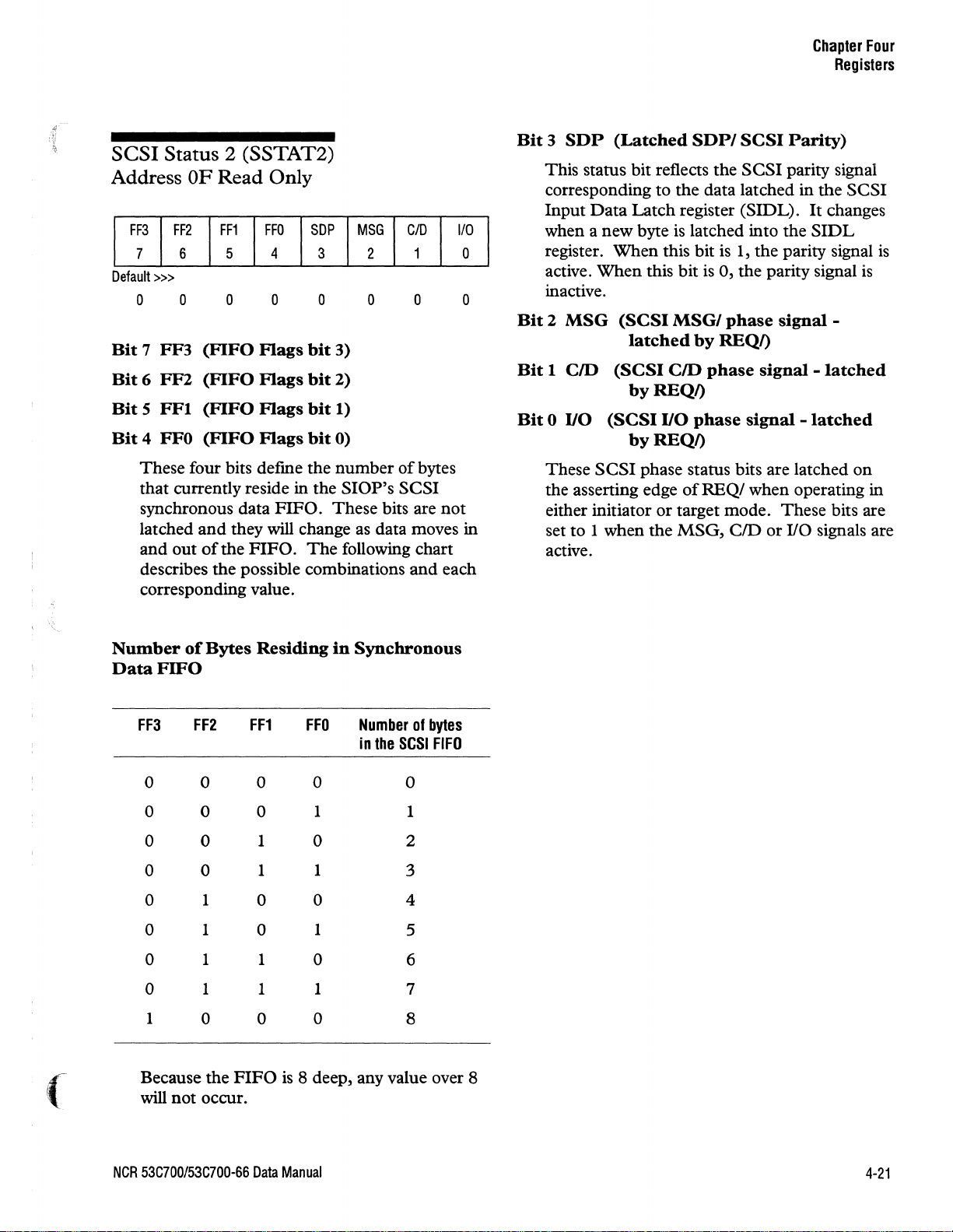

Status 2 (SSTAT2), Address

Data

Latch

Data

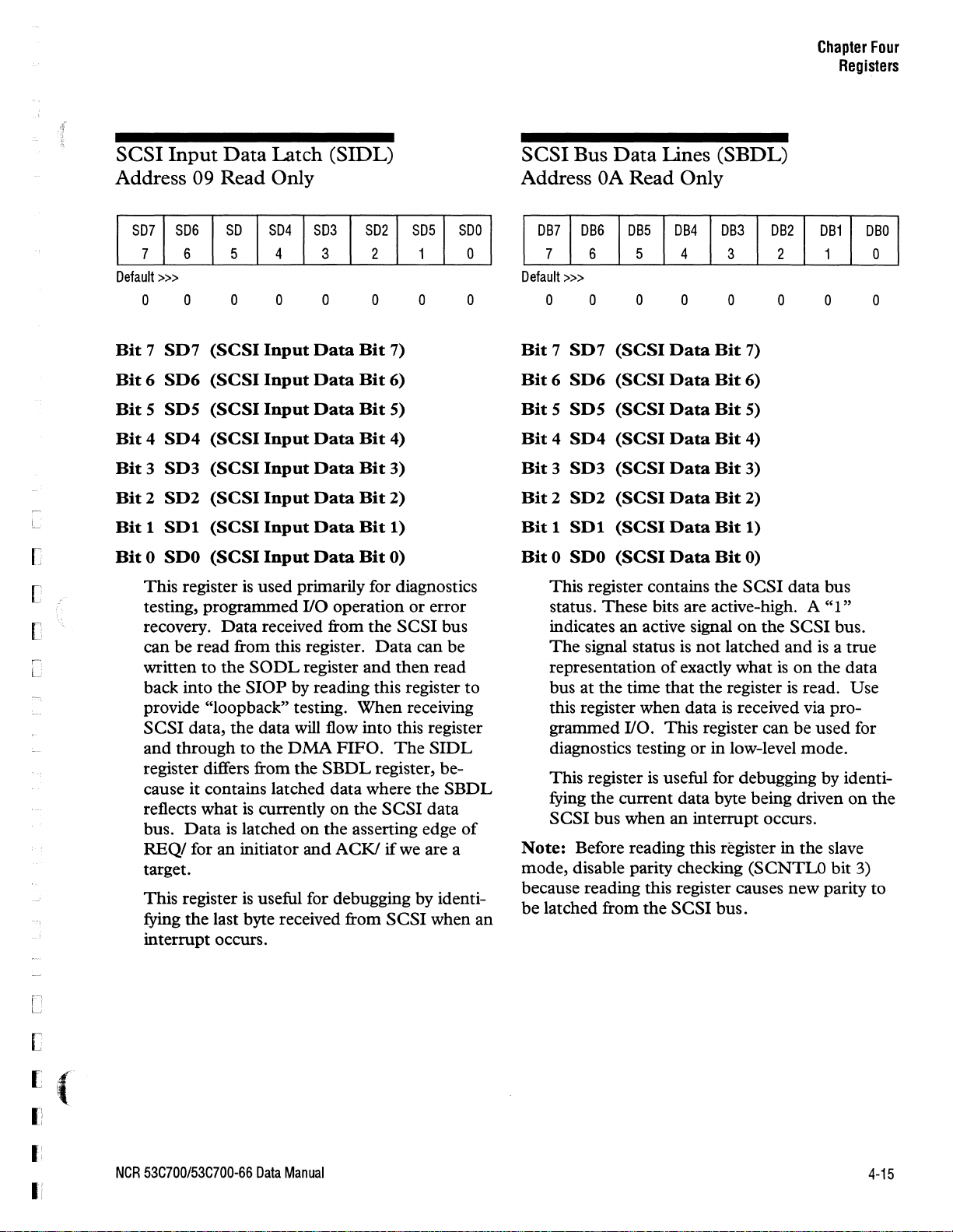

Lines (SBDL), Address

(SIDL), Address 09 Read Only ...................................................... .4-15

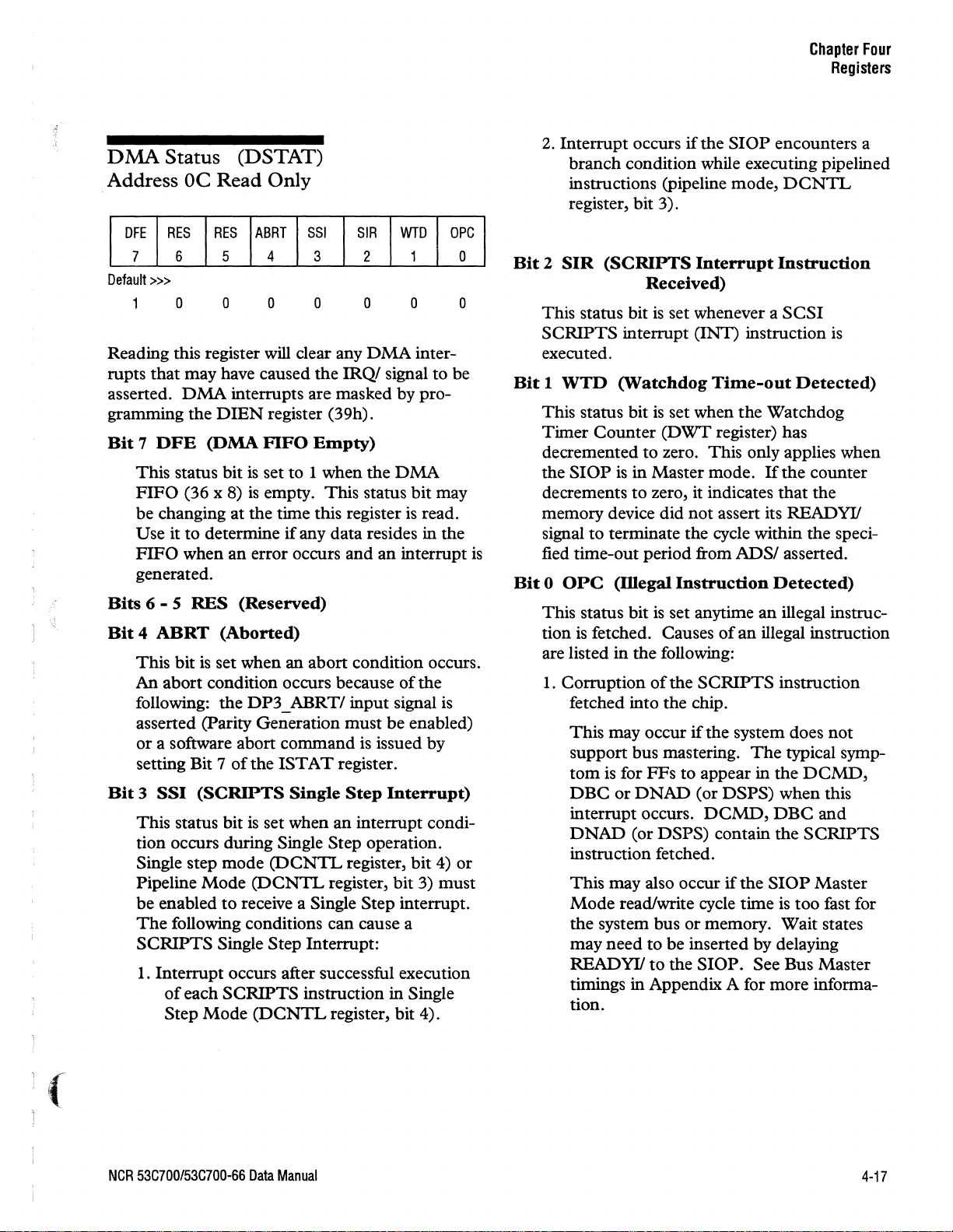

Status (DSTAT), Address

(SSTATl),

Address

OA

Read Only ....................................................... .4-15

OB

Read 53C700, ReadlWrite -66 ......................

OC

Read Only ............................................................... .4-17

OD

Read Only .............................................................. .4-18

OE

Read Only ............................................................... 4-20

OF

Read Only .............................................................. .4-21

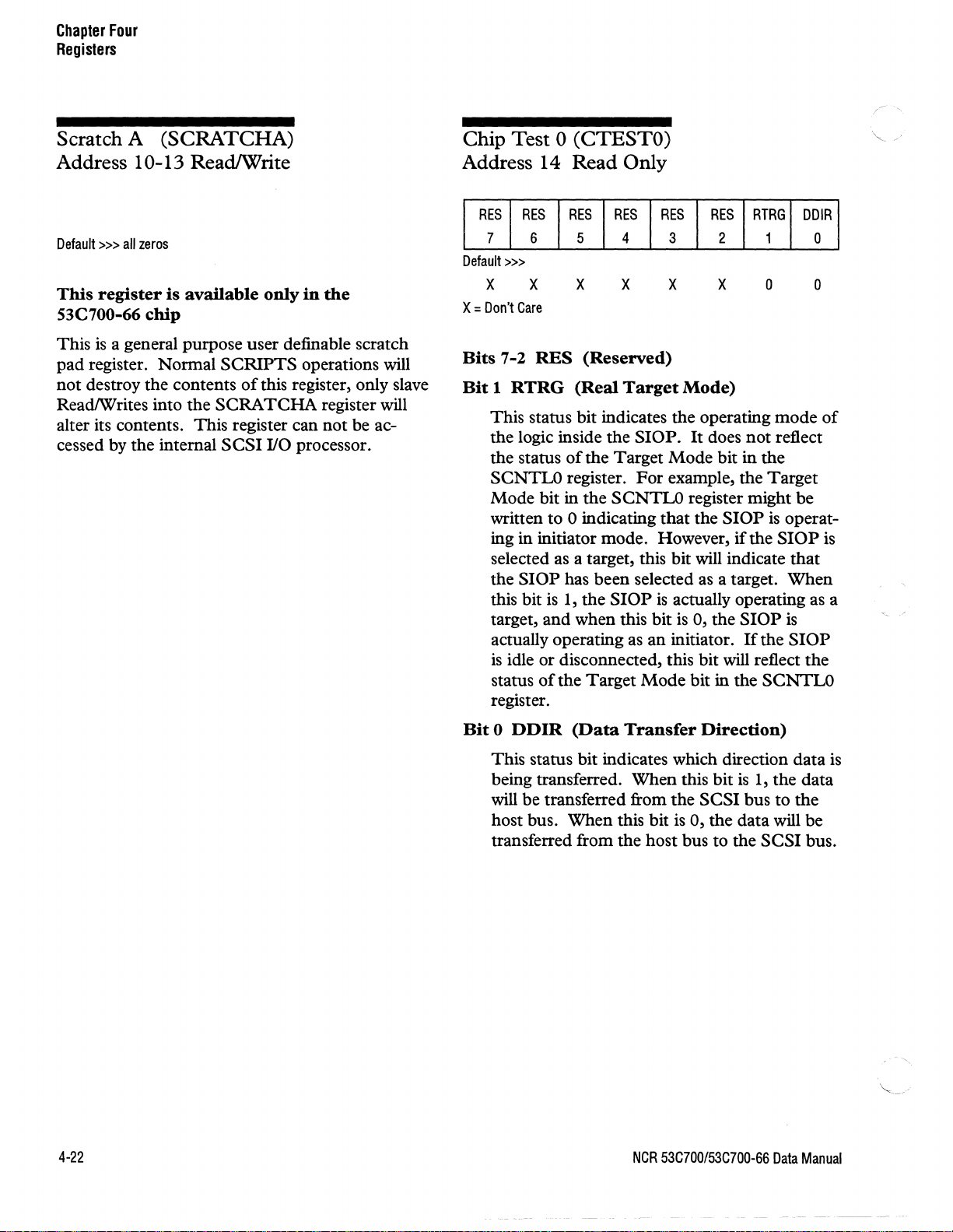

Scratch A (SCRATCHA), Address 10-13 ReadIWrite ....................................................... .4-22

Test

Chip

Chip

Chip

Chip

Chip

Chip

Chip

Chip

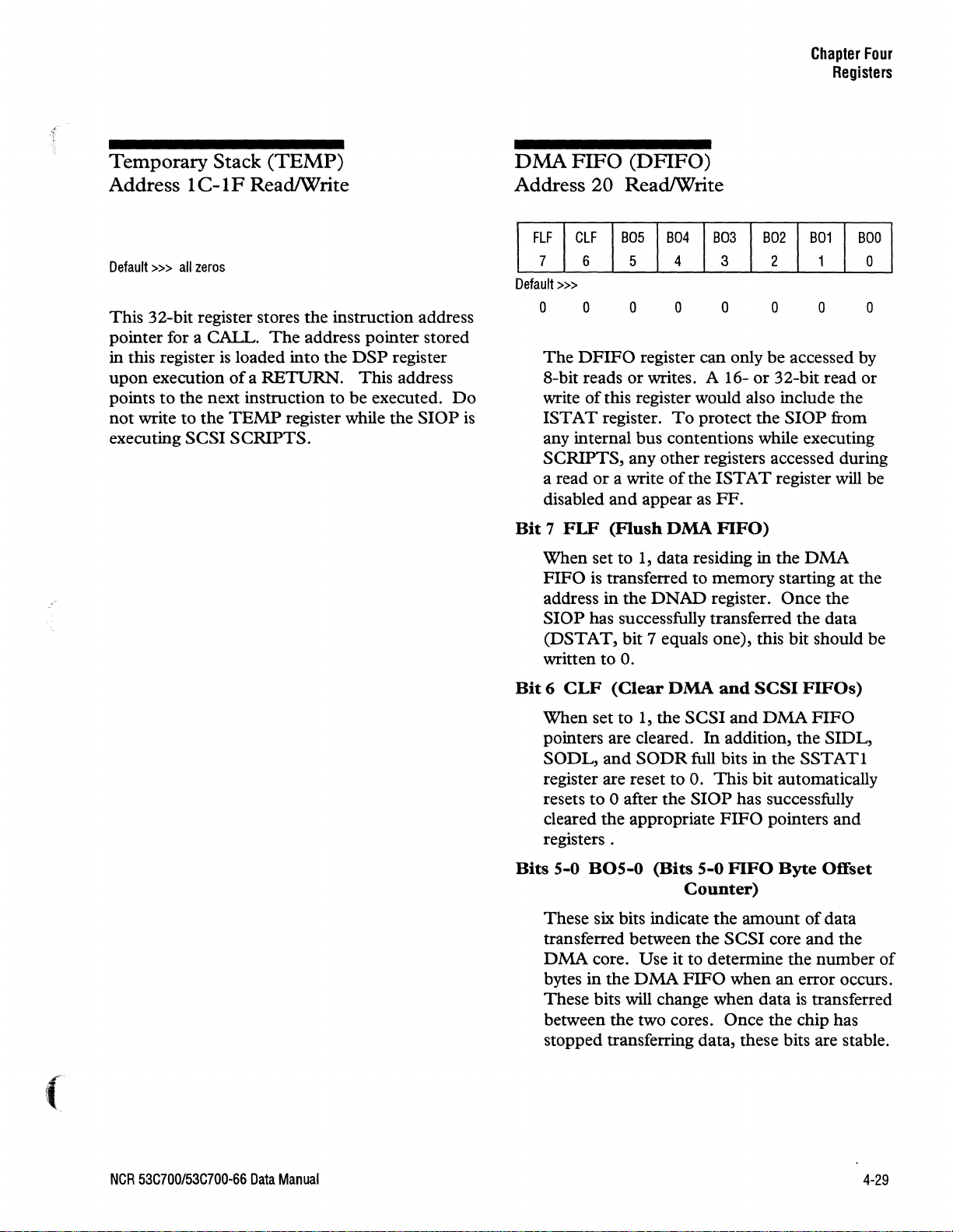

Temporary

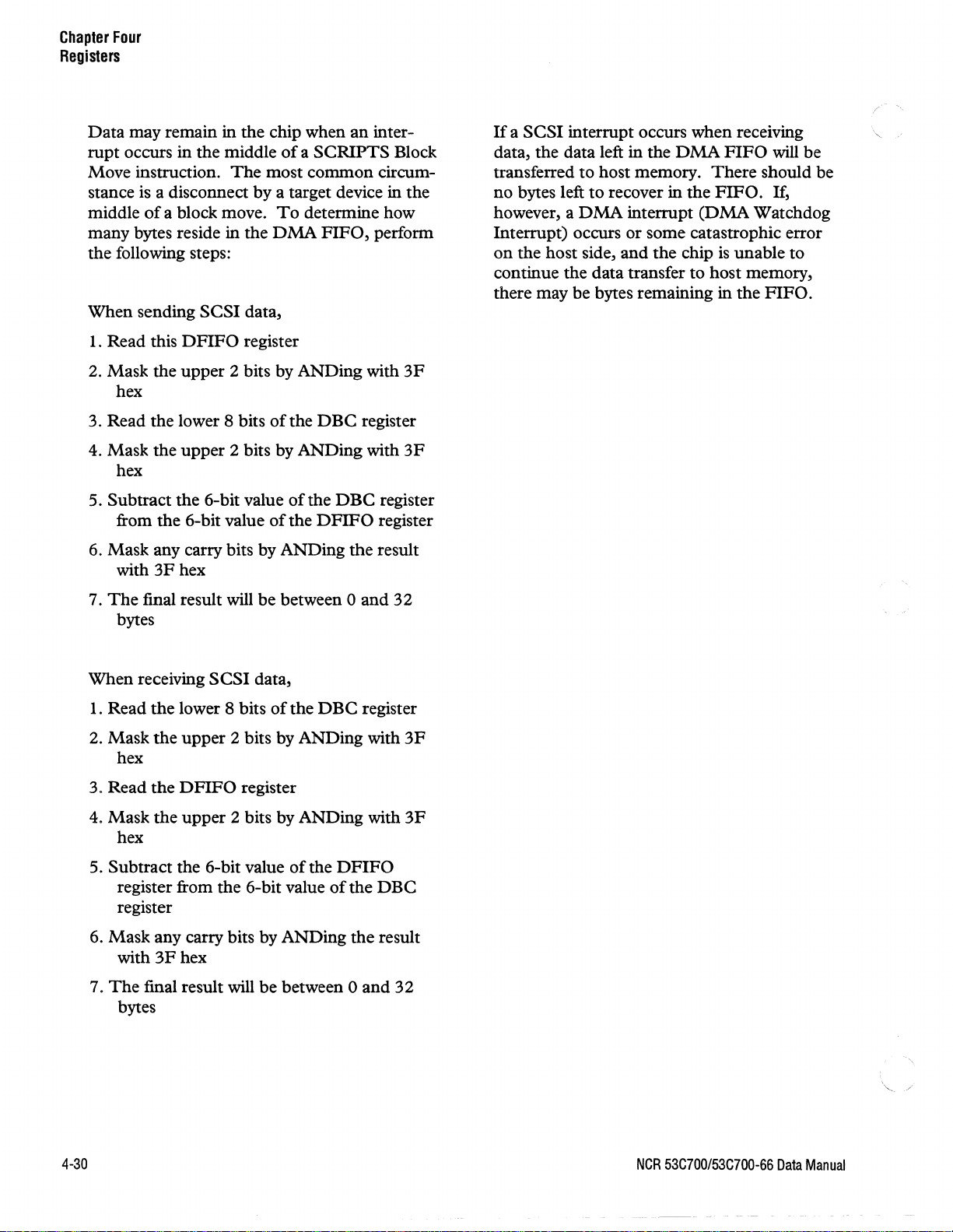

DMA

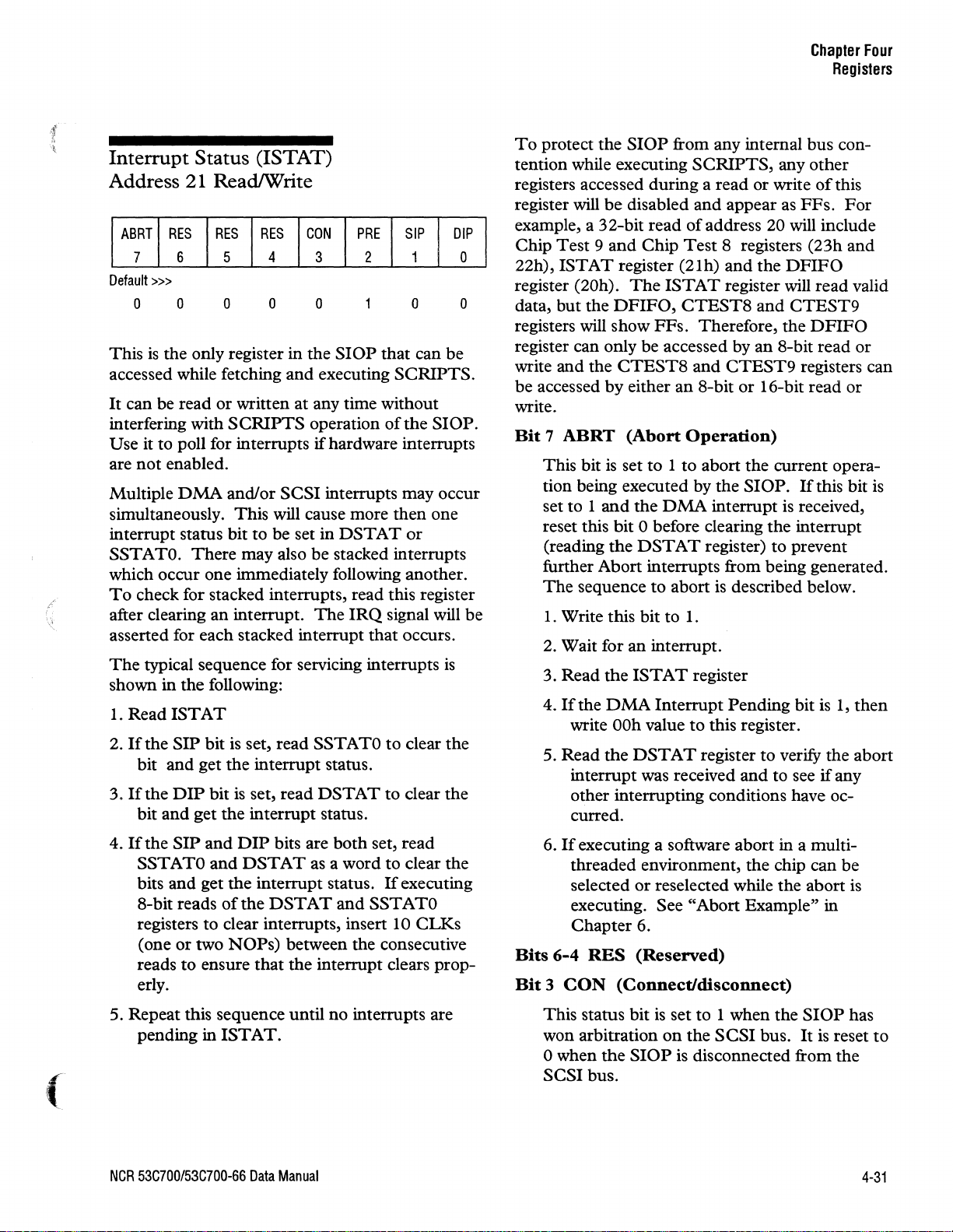

Interrupt

Chip

Chip

DMA

DMA

DMA

DMA

DMA

DMA

DMA

DMA

DMA

Scratch

0 (CTESTO), Address 14 Read Only ................................................................ .4-22

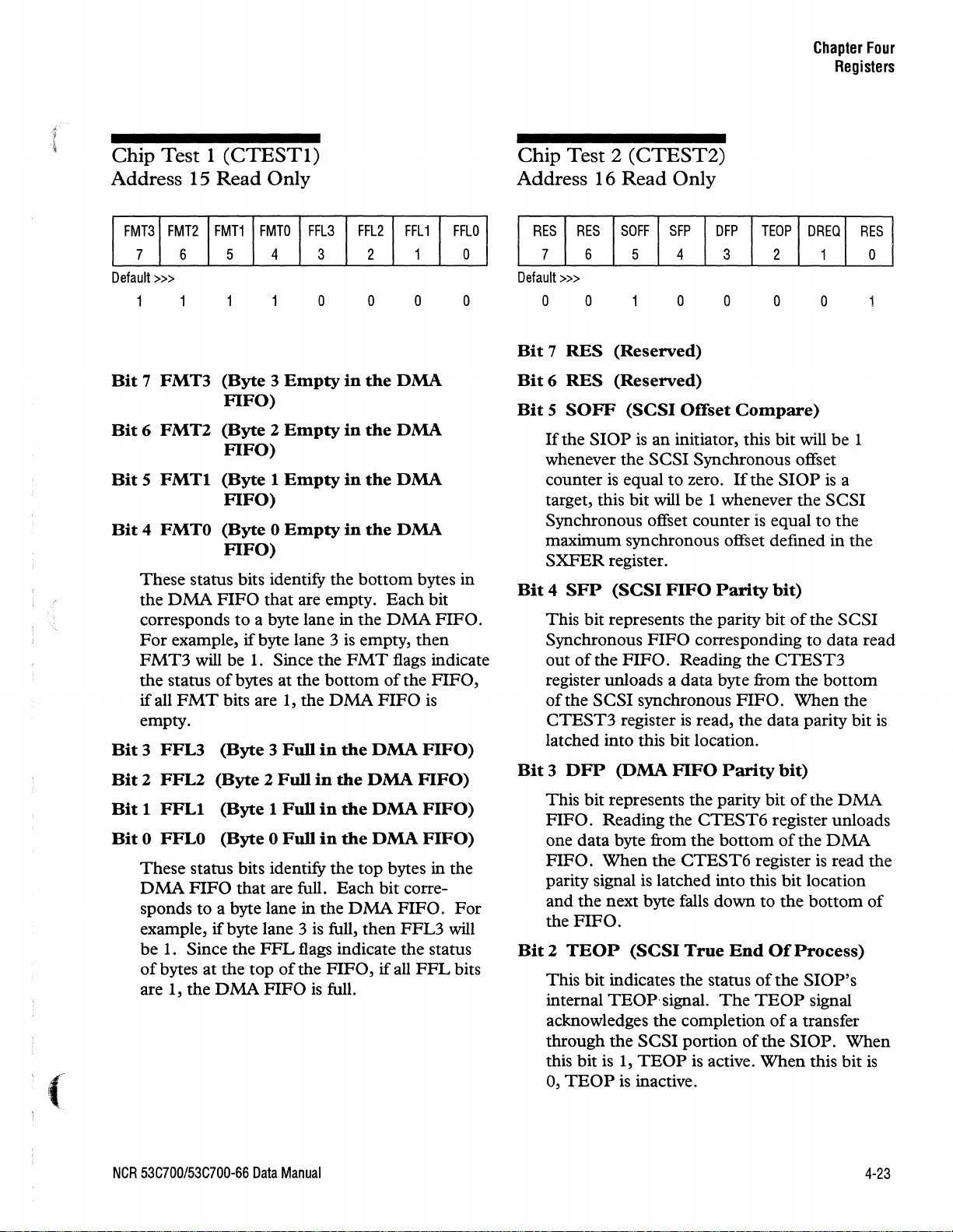

Test 1 (CTESTl),

Test 2 (CTEST2),

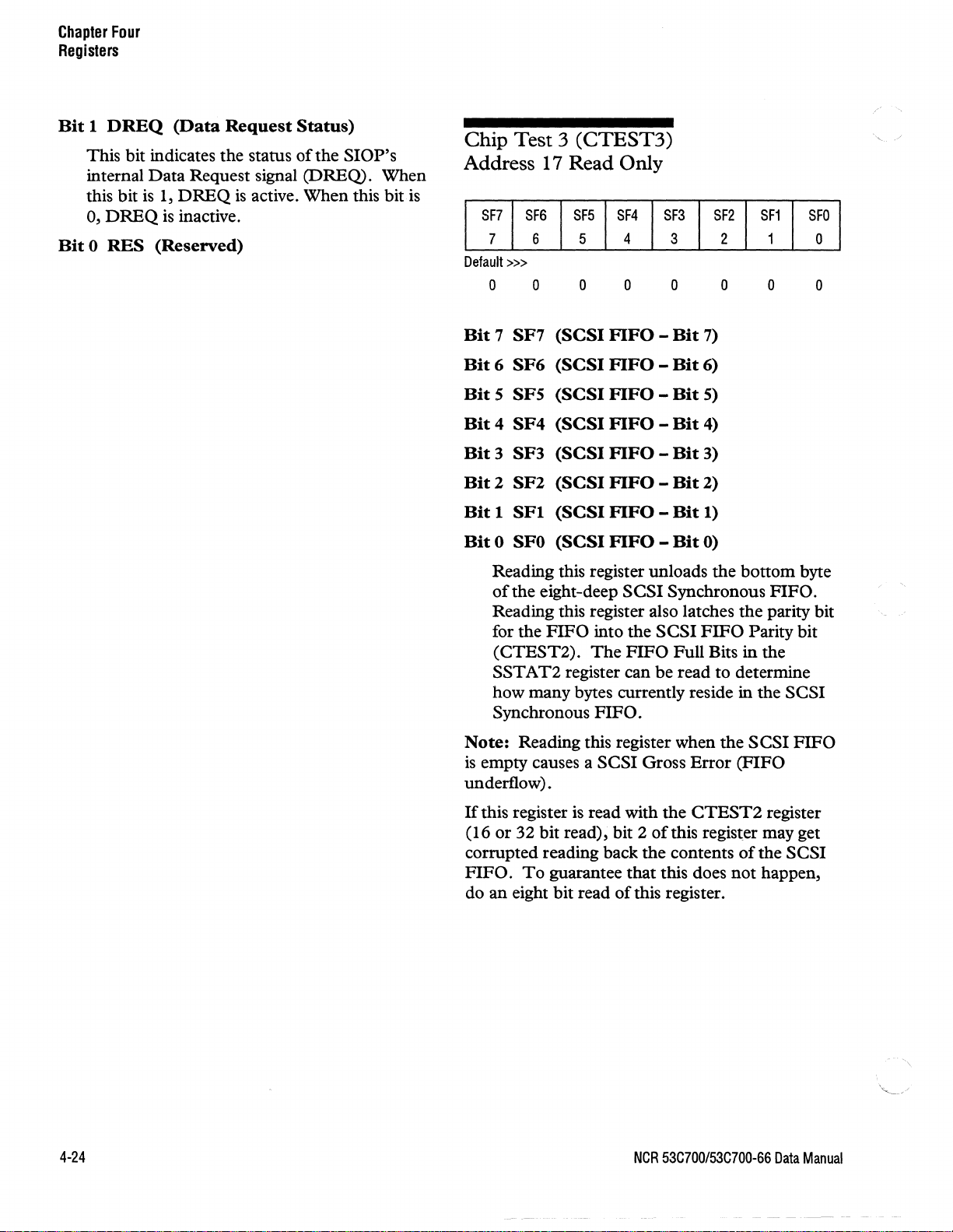

Test 3 (CTEST3),

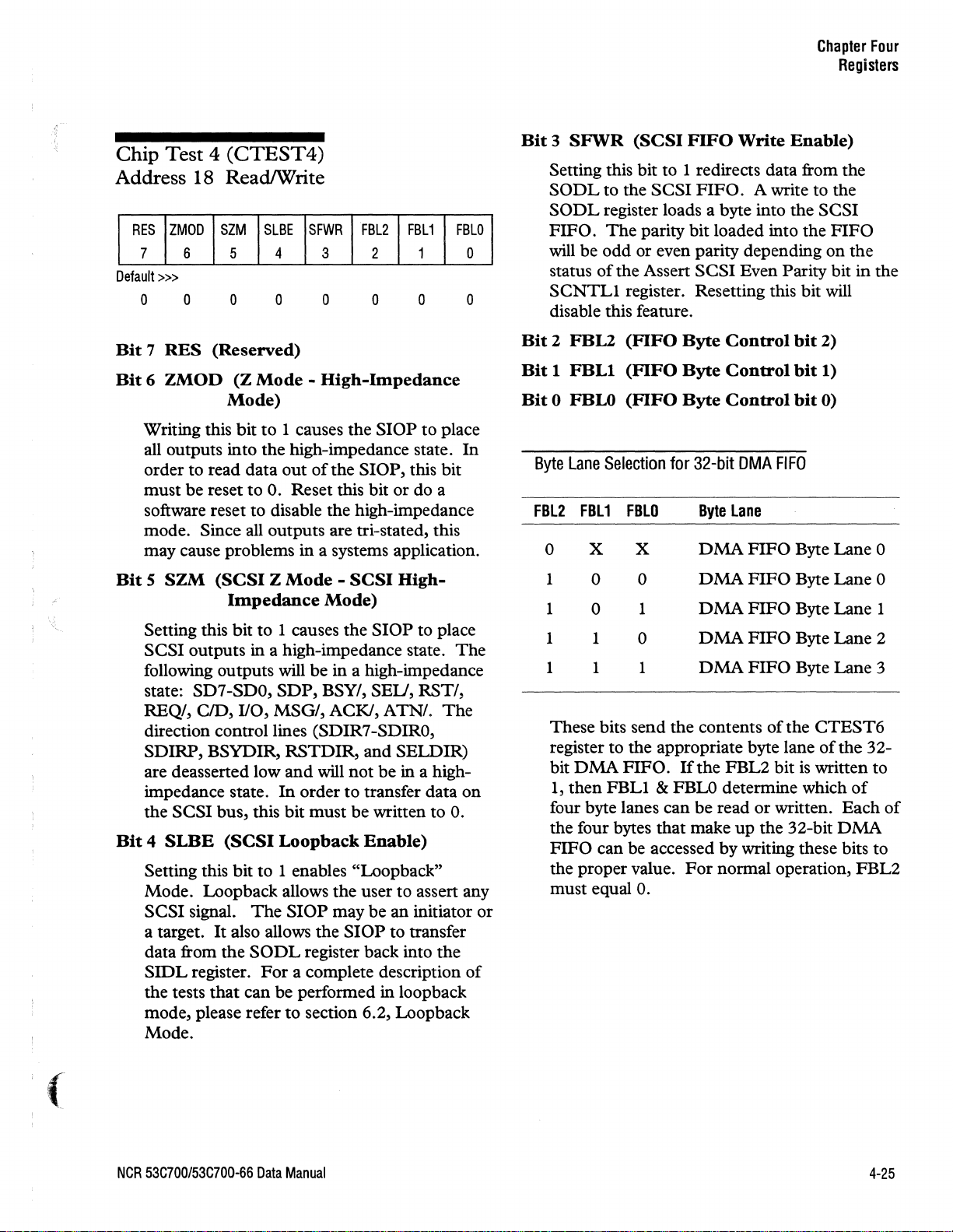

Test 4 (CTEST4),

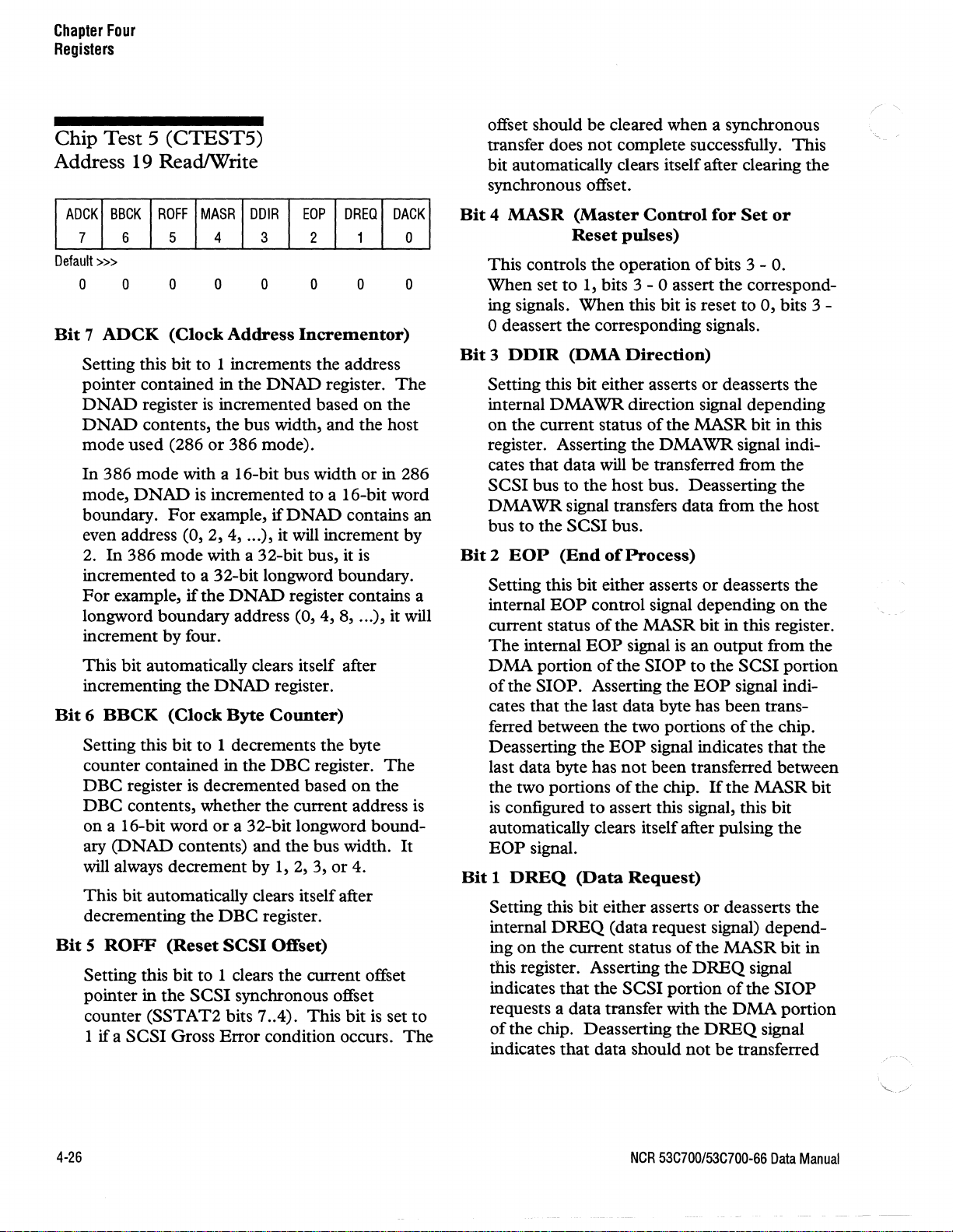

Test 5 (CTEST5),

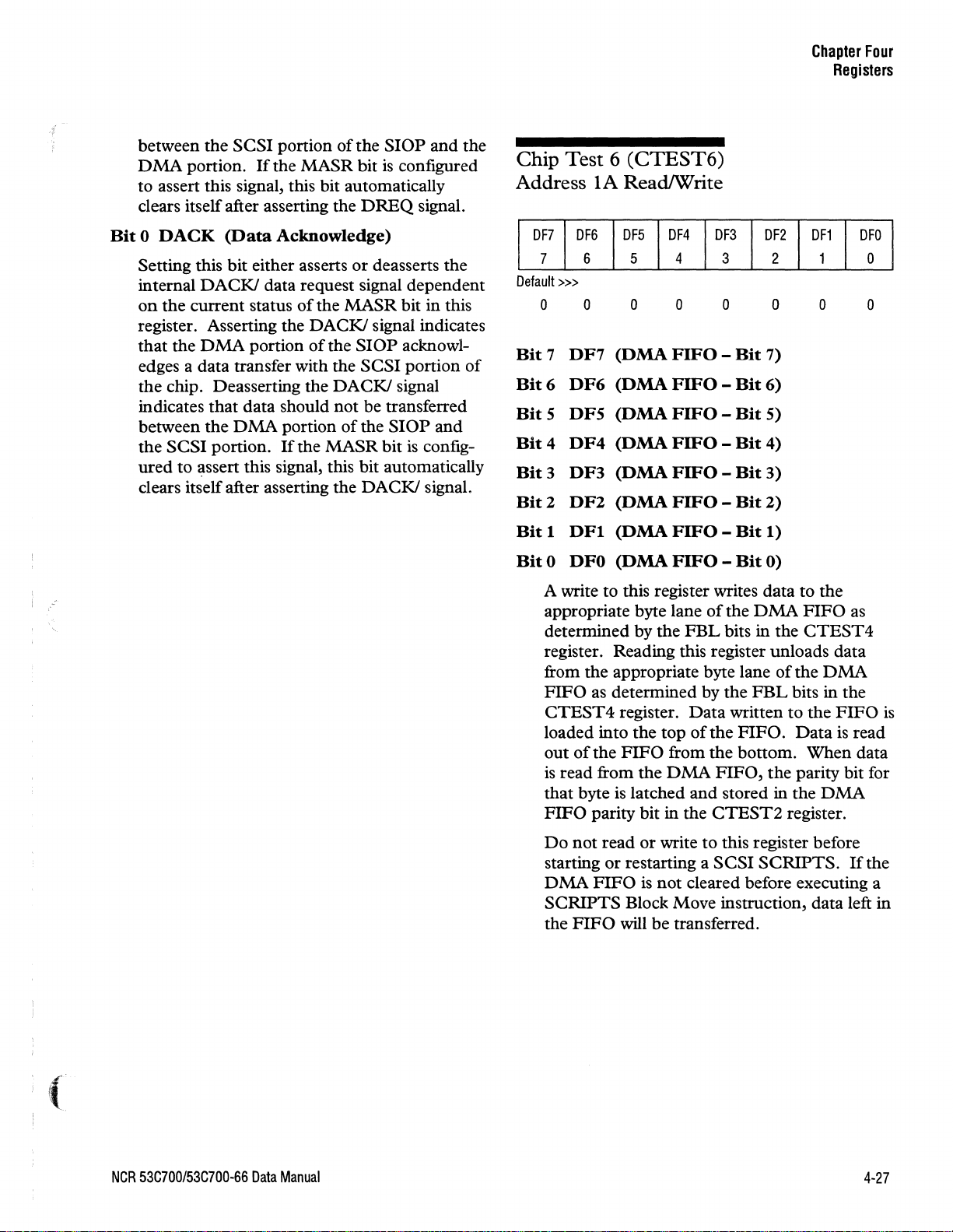

Test 6 (CTEST6),

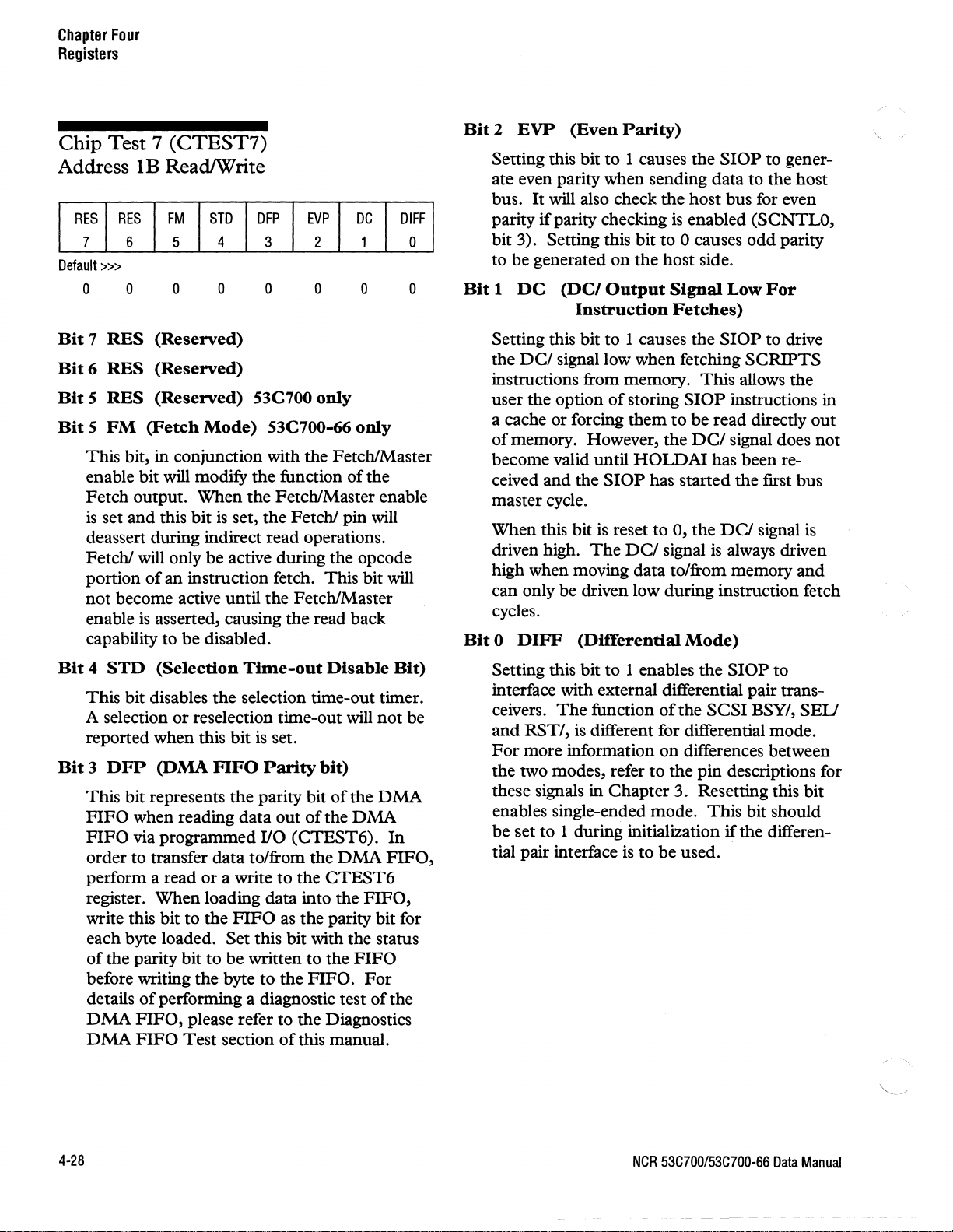

Test 7 (CTEST7),

Stack

(TEMP),

FIFO

(DFIFO),

Status (ISTAT), Address

Test 8 (CTEST8),

Test 9 (CTEST9),

Address 15 Read Only ................................................................. .4-23

Address 16 Read Only ................................................................. .4-23

Address

17

Read Only ................................................................. .4-24

Address 18 ReadlWrite ............................................................... .4-25

Address

Address

Address

19

lA

IB

Address

ReadIWrite ................................................................. 4-26

ReadIWrite ................................................................ .4-27

ReadIWrite ................................................................ .4-28

lC-IF

ReadlWrite ...................................................... .4-29

Address 20 ReadIWrite ................................................................... 4-29

21

ReadlWrite .............................................................. .4-31

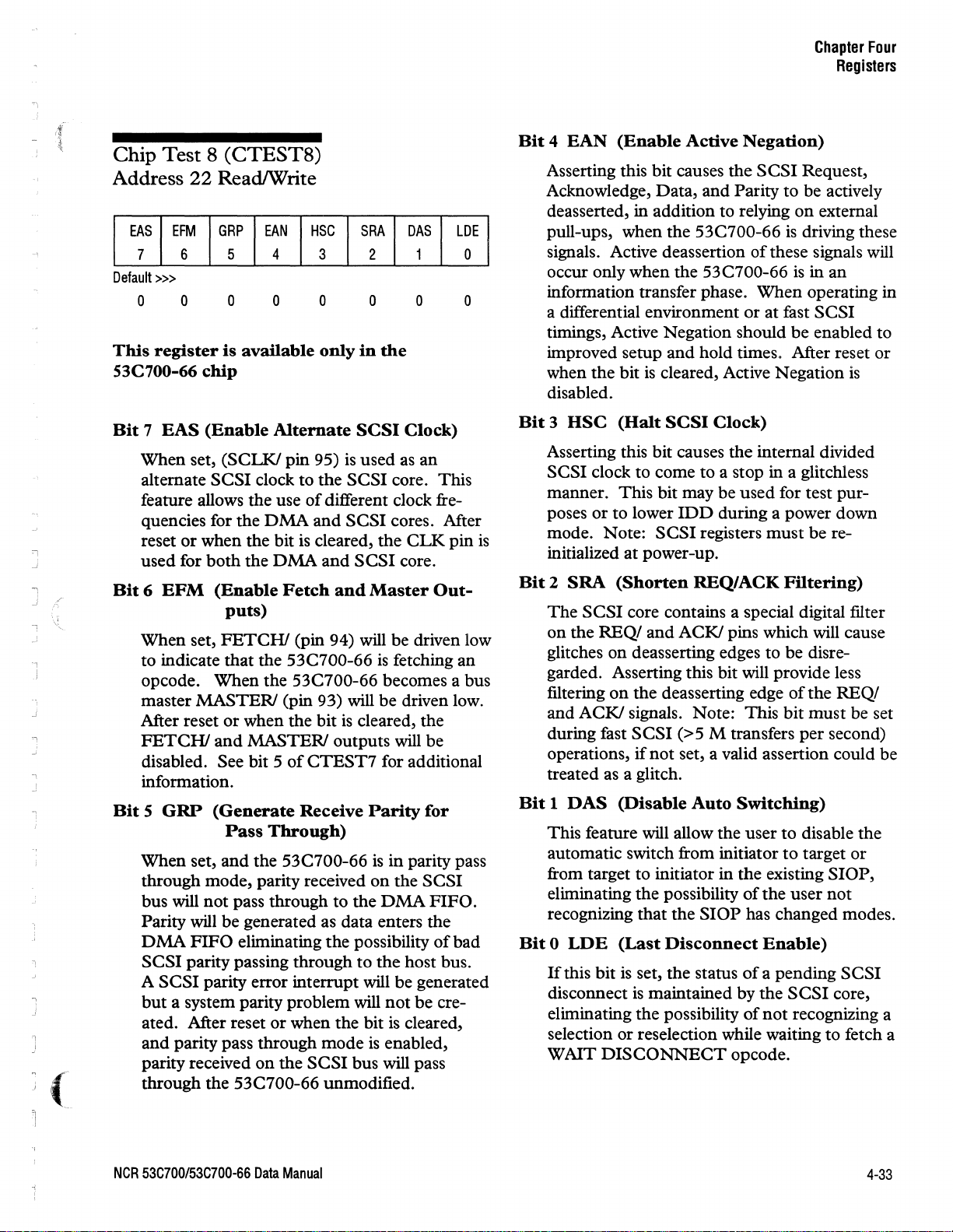

Address 22 ReadlWrite ................................................................. 4-33

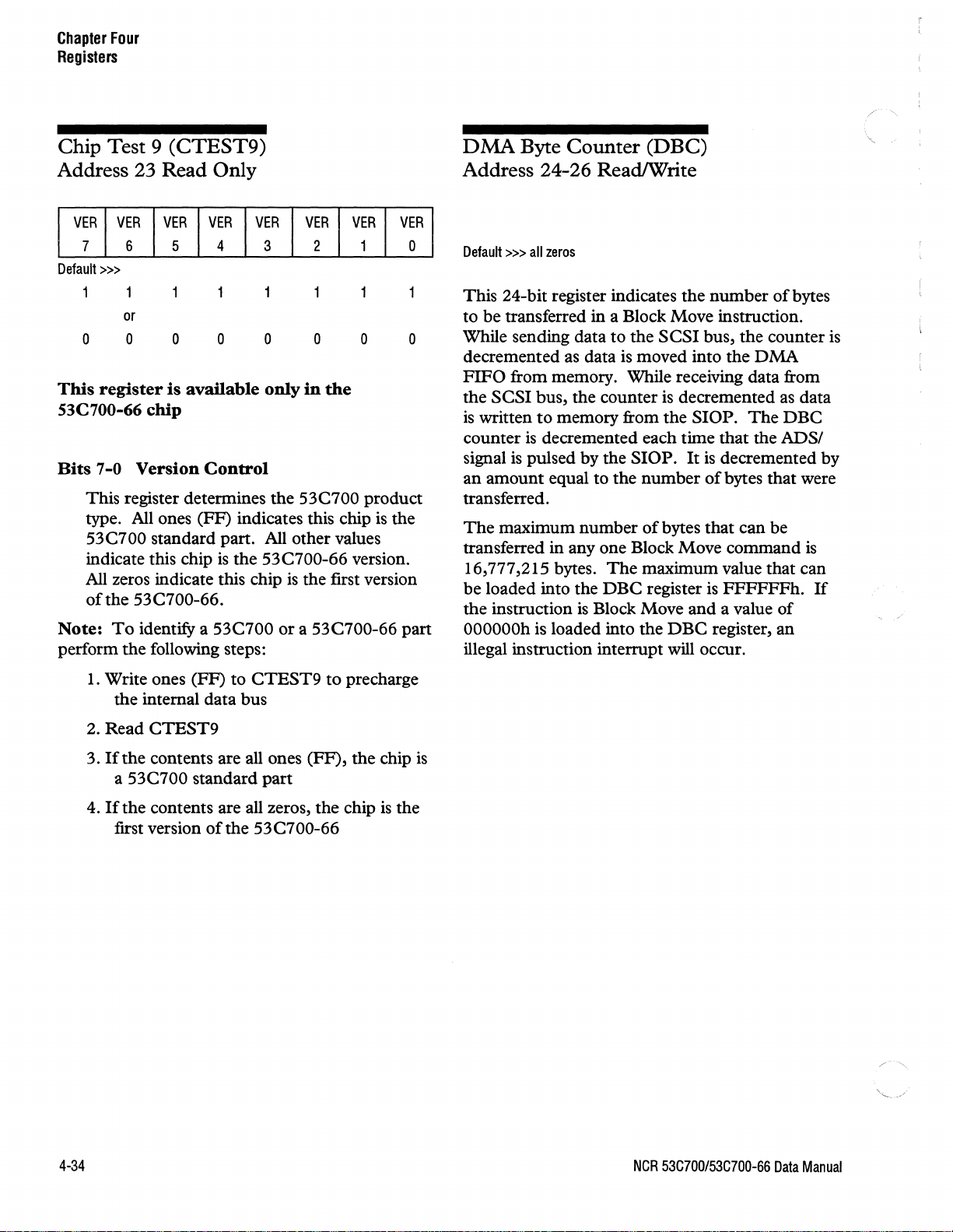

Address 23 Read Only .................................................................. 4-34

Byte Counter (DBC), Address 24-26 ReadIWrite ...................................................... .4-34

Command

Next Address for

SCRIPTS

SCRIPTS

Mode

(DCMD),

Pointer (DSP), Address

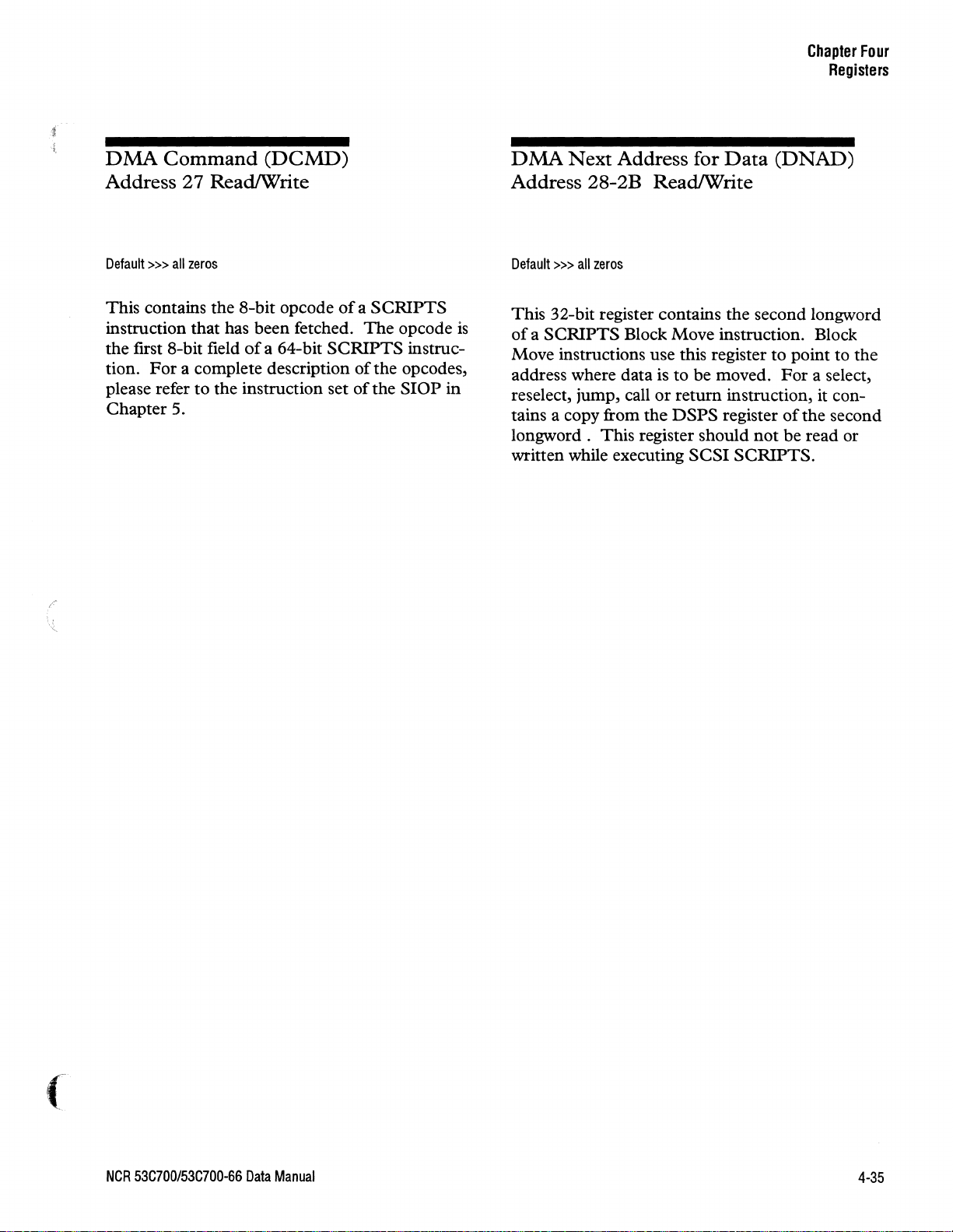

Address 27 ReadlWrite ........................................................... .4-35

Data

(DNAD), Address 28-2B ReadIWrite ................................... .4-35

2C-2F

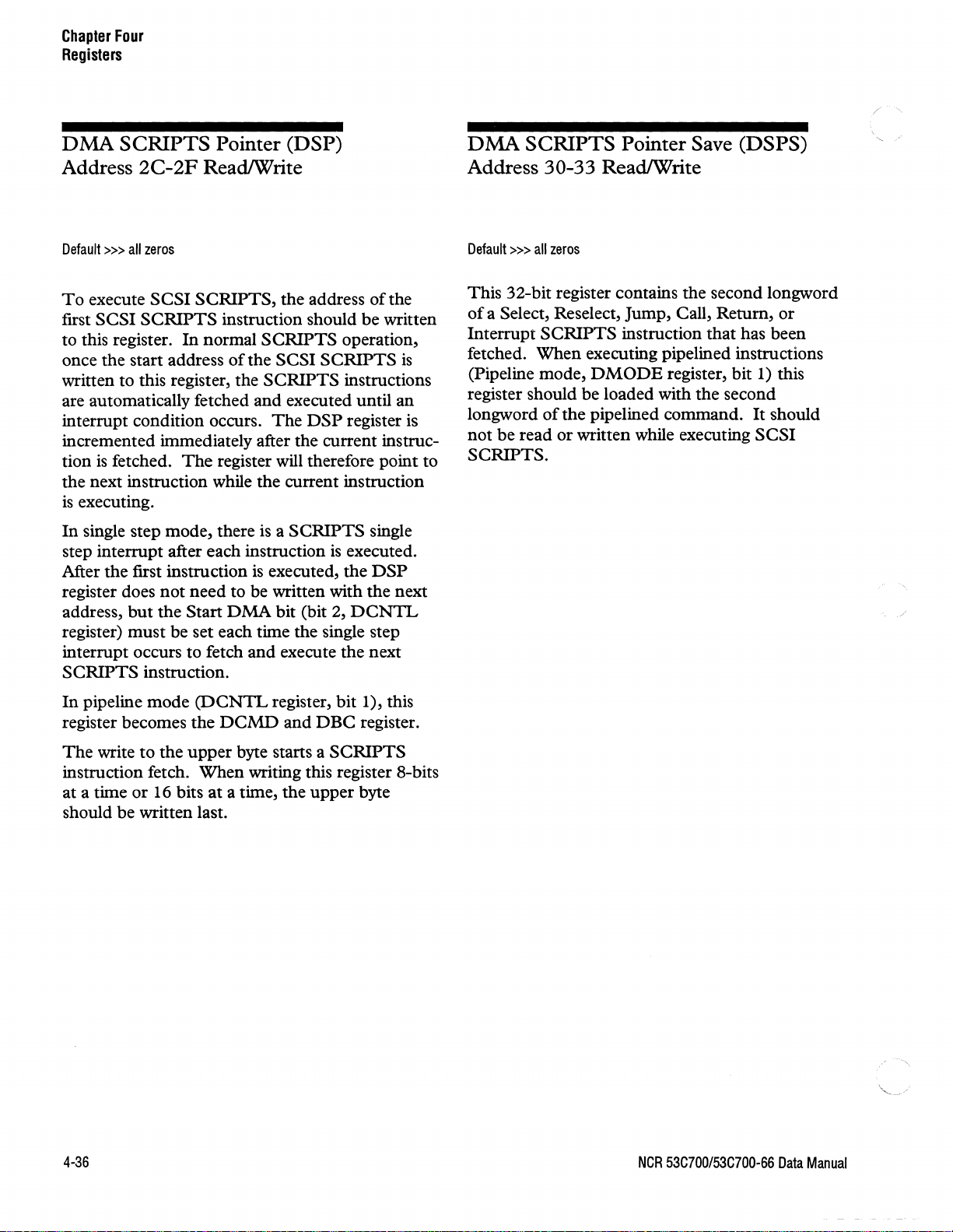

ReadlWrite .............................................. .4-36

Pointer Save (DSPS), Address 30-33 ReadIWrite ...................................... .4-36

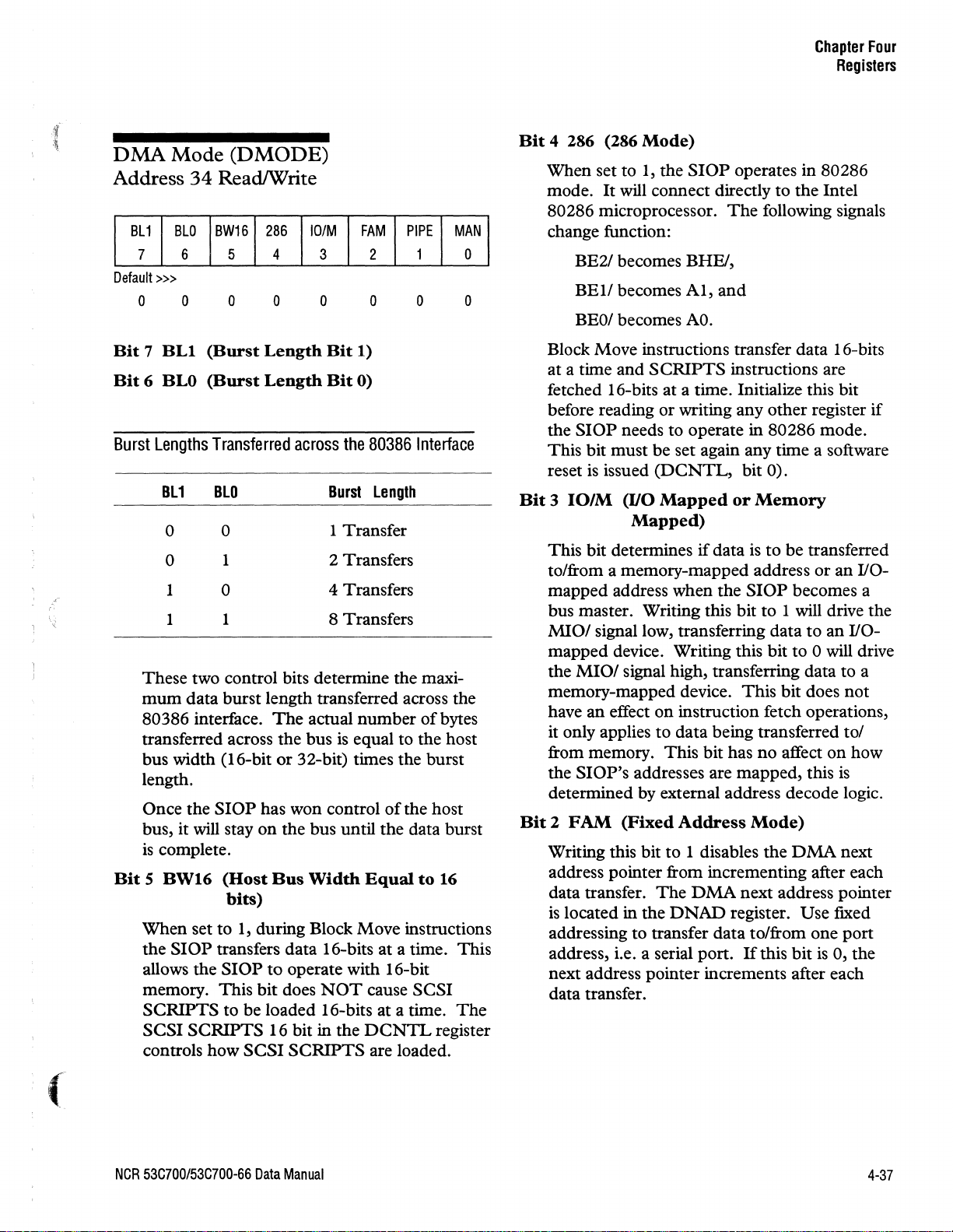

(DMODE),

Address 34 ReadlWrite ............................................................... .4-37

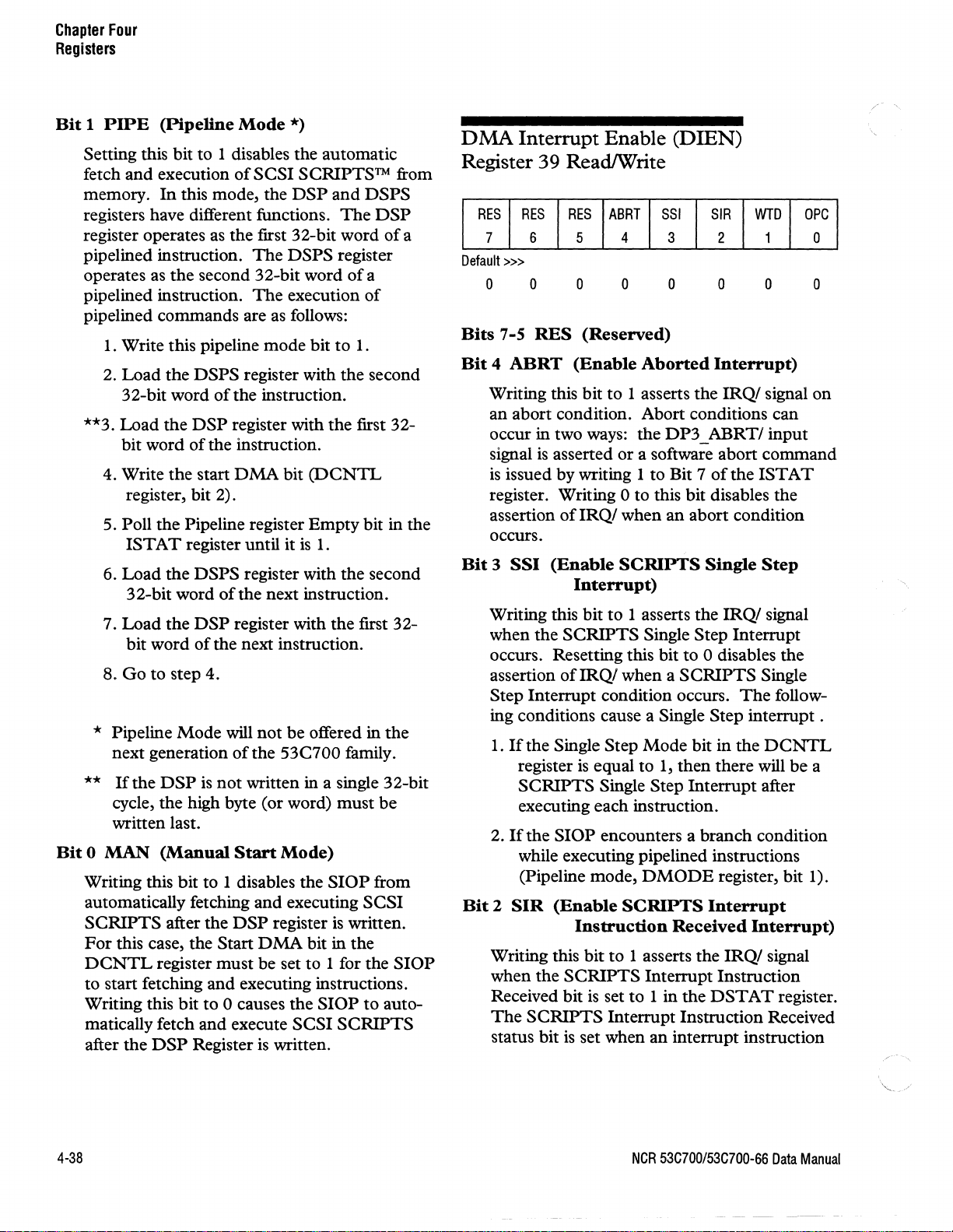

Interrupt Enable (DIEN), Register 39 ReadIWrite ..................................................... 4-38

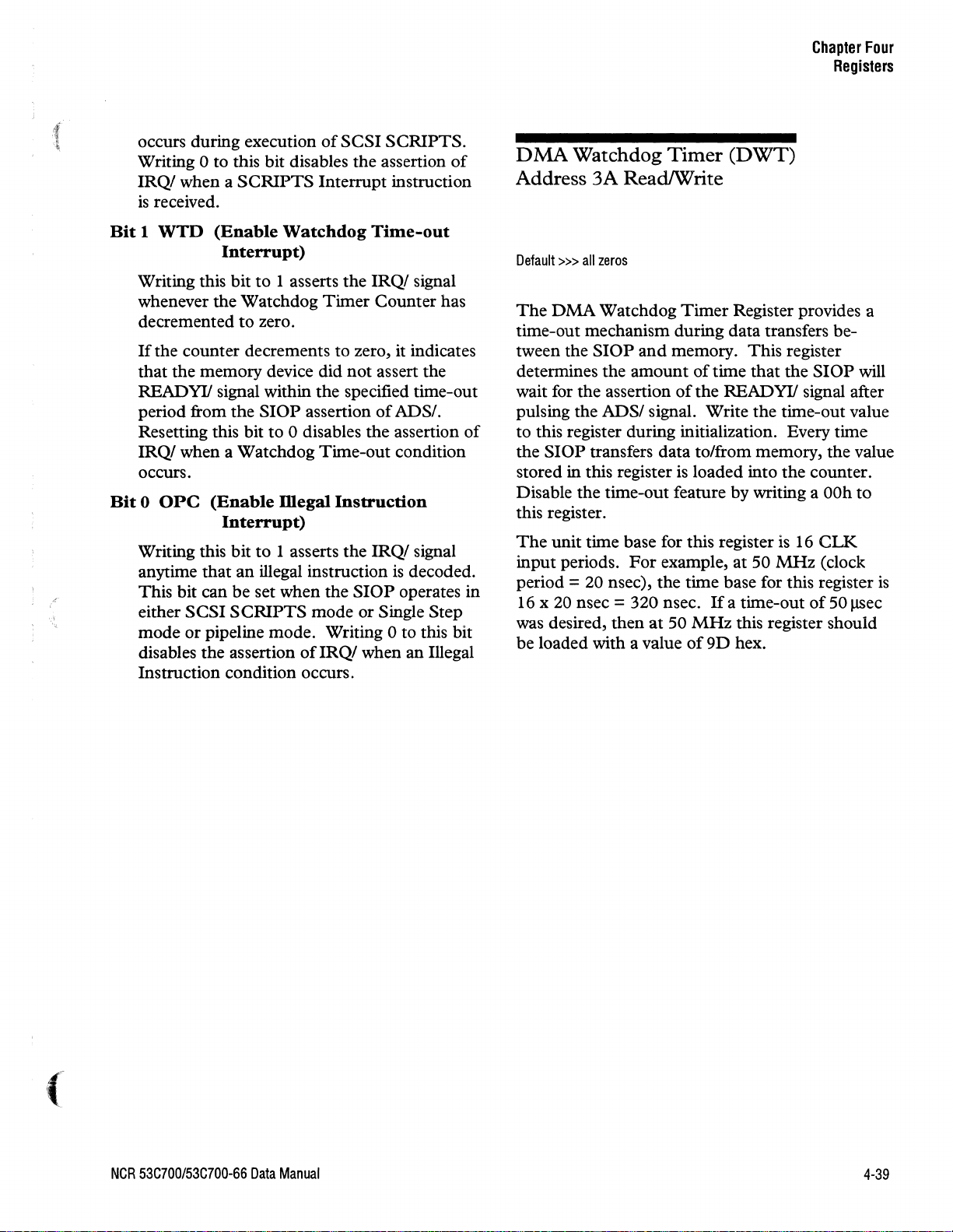

Watchdog

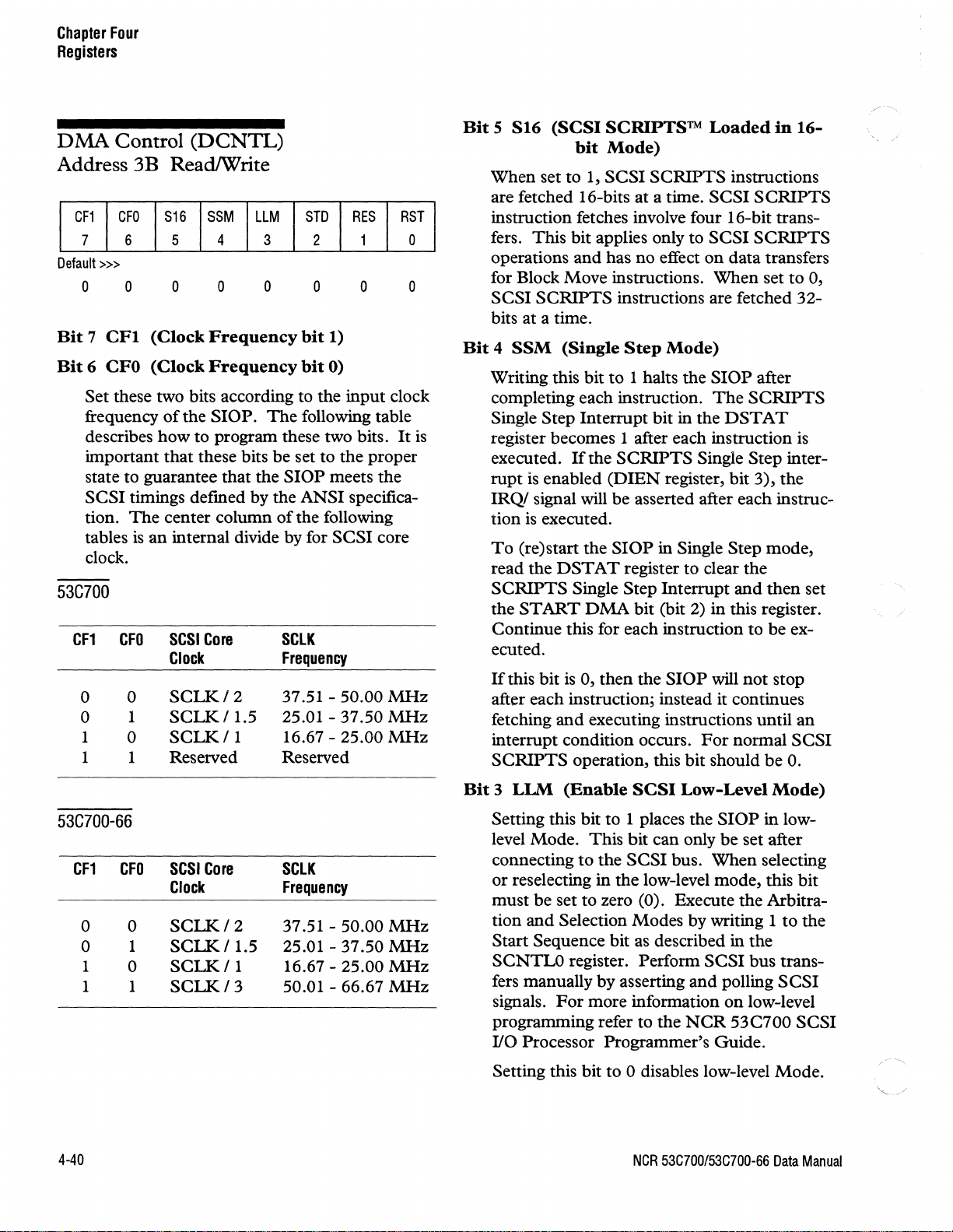

Control

B (SCRATCHB), Address

Timer

(DWT),

(DCNTL),

Address 3A ReadIWrite .................................................... .4-39

Address 3B ReadIWrite ............................................................ .4-40

3C-3F

ReadlWrite ........................................................ .4-41

.4-8

.4-16

iv

NCR

53C700/53C700-66

Data

/ "

1",-

Manual

Page 7

Chapter

Command

Five

Set

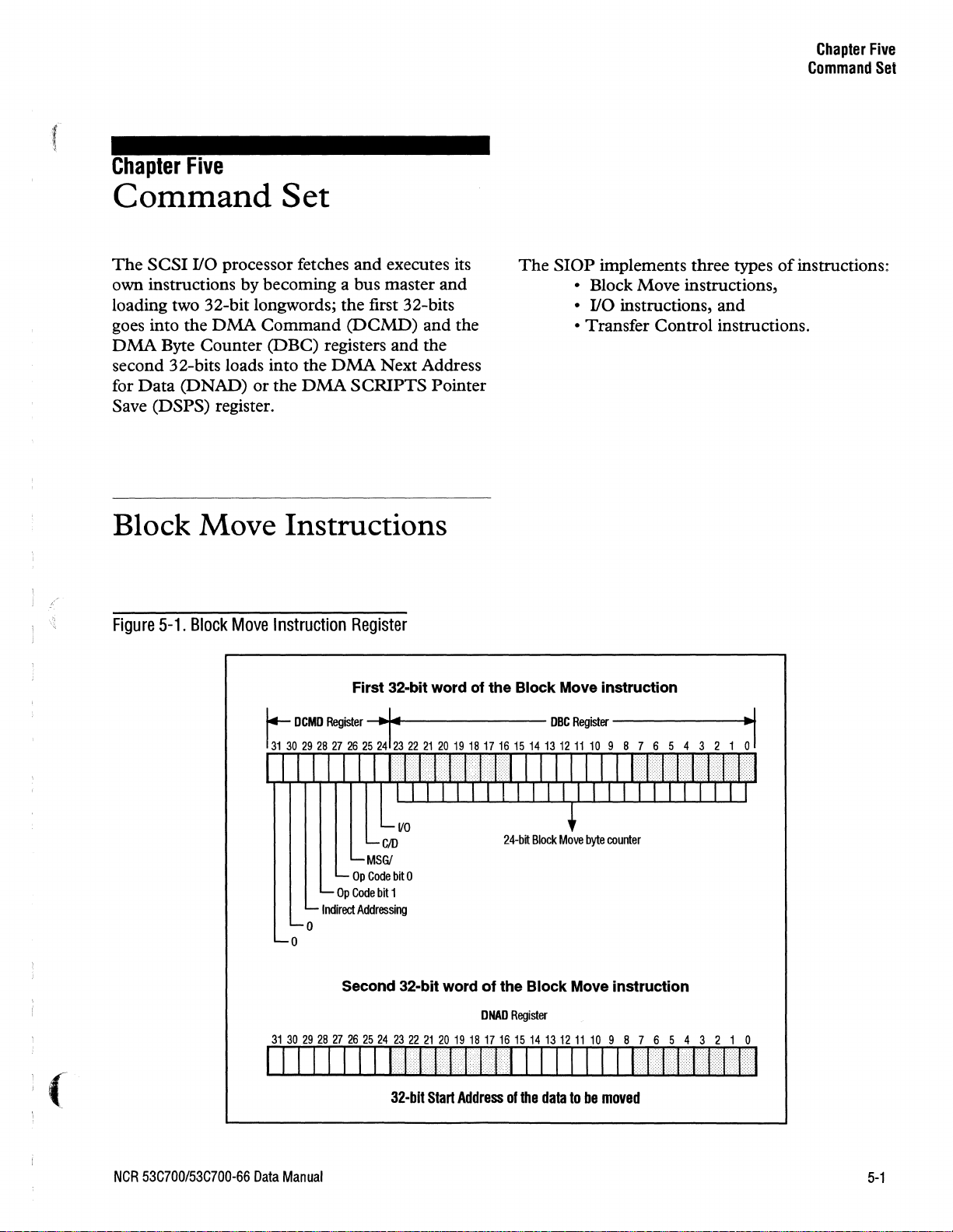

Block Move Instructions ............................................................................................................ 5-1

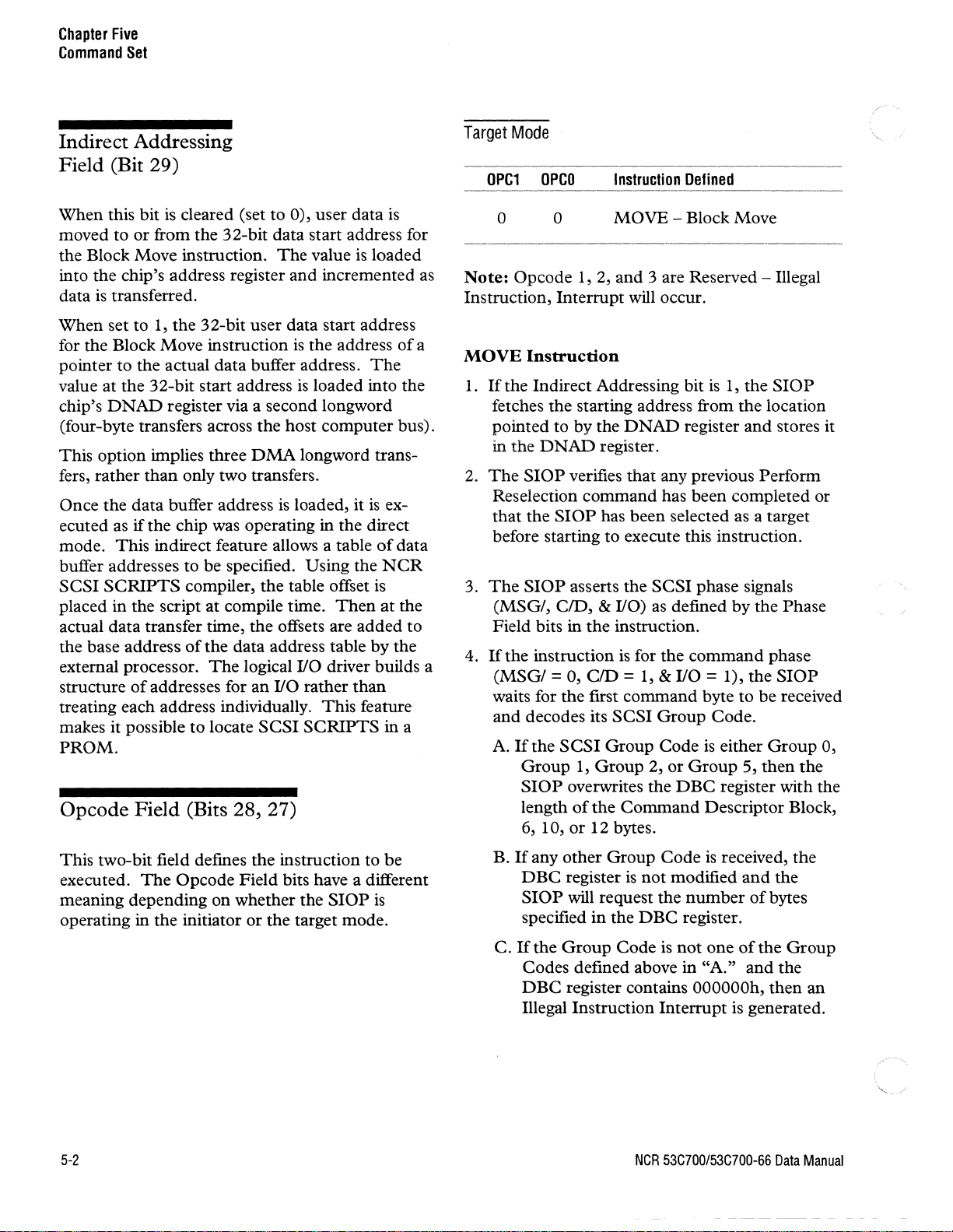

Indirect Addressing Field (Bit 29) ......................................................................................... 5-2

Opcode Field (Bits 28, 27) ................................................................................................... 5-2

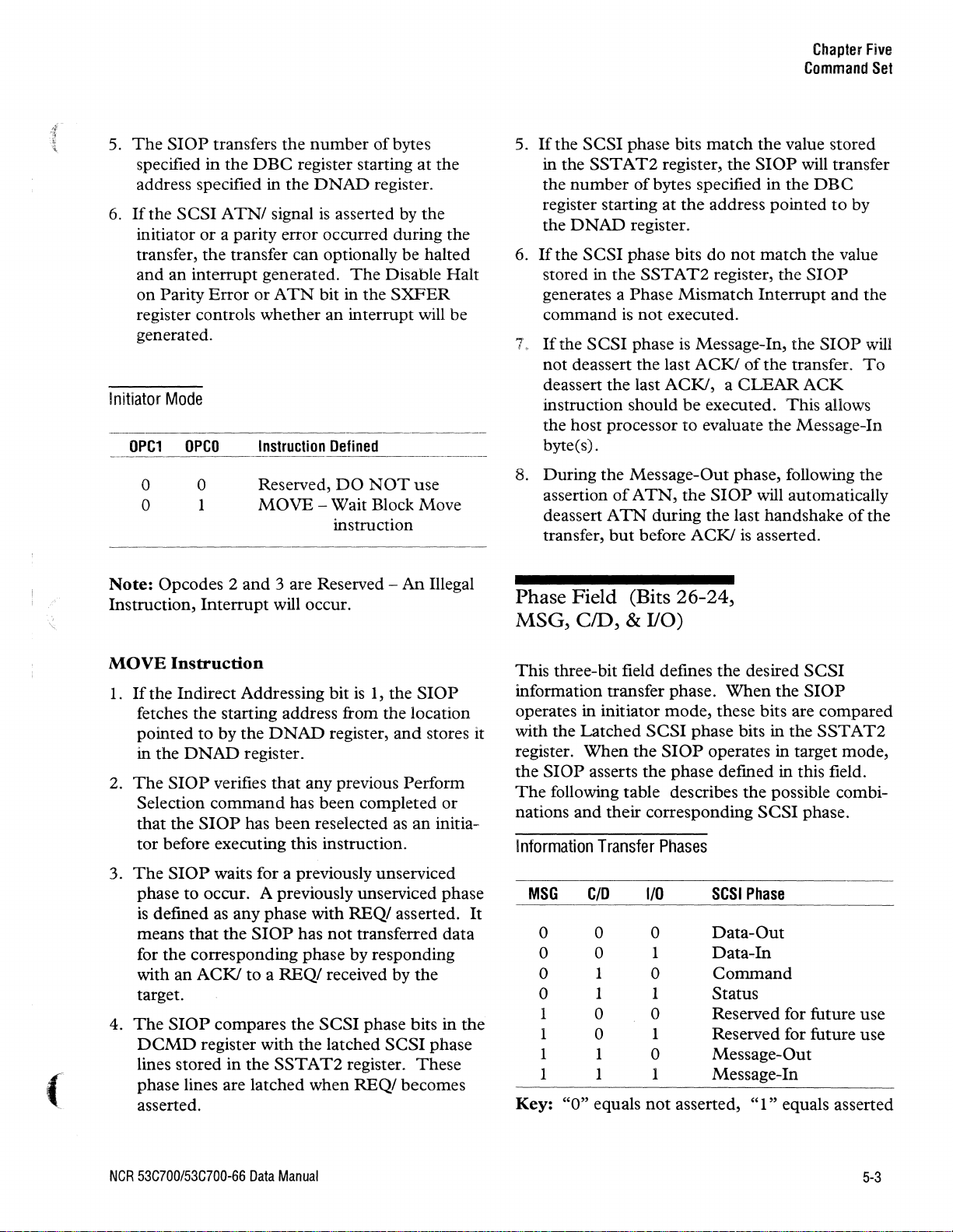

Phase Field (Bits 26-24,

MSG,

Transfer Counter Field (Bits 23-0,

Start Address Field (Bits 31-0,

CID,

& I/O) ......................................................................... 5-3

DBC

register) ................................................................. 5-4

DNAD

register) .................................................................... 5-4

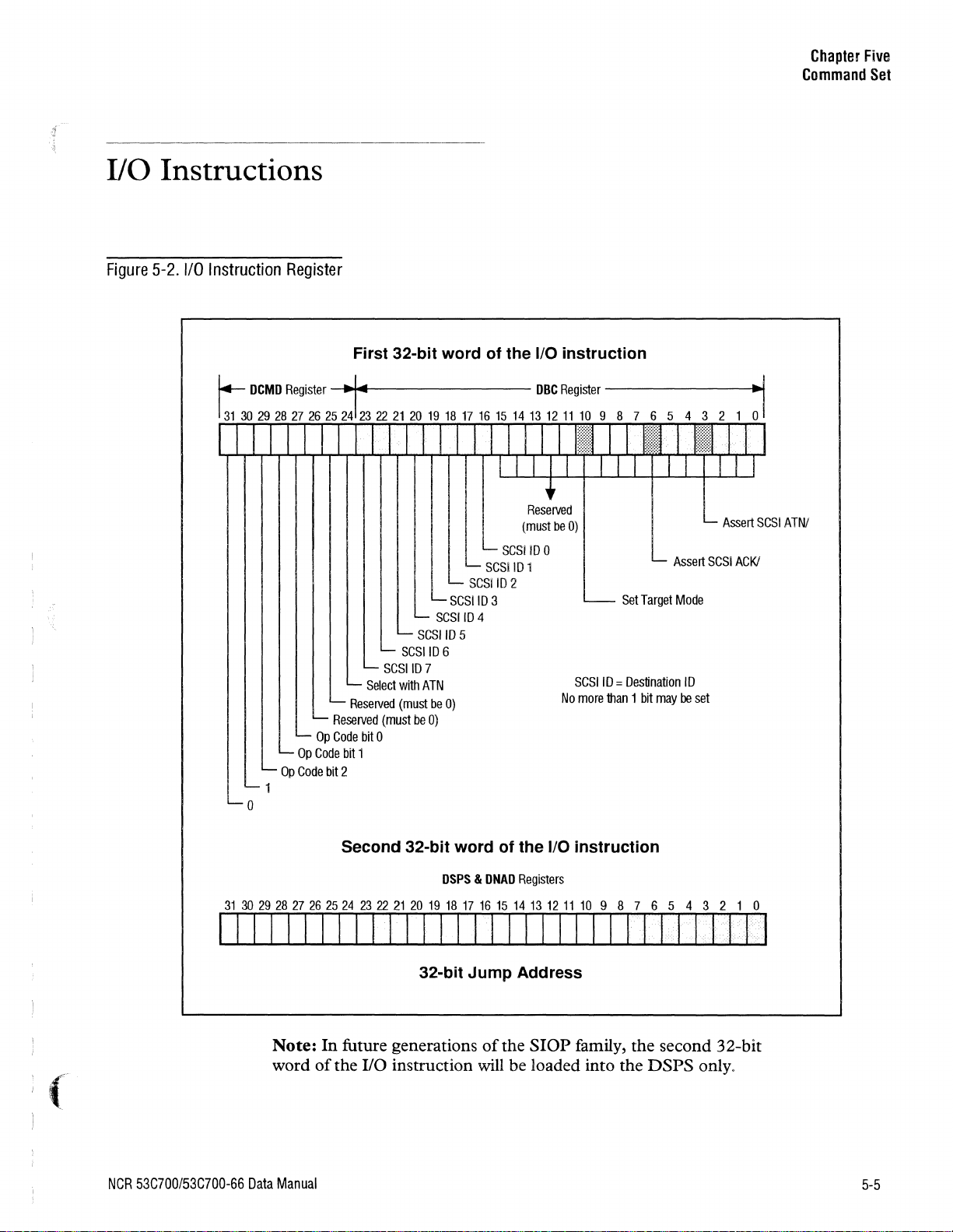

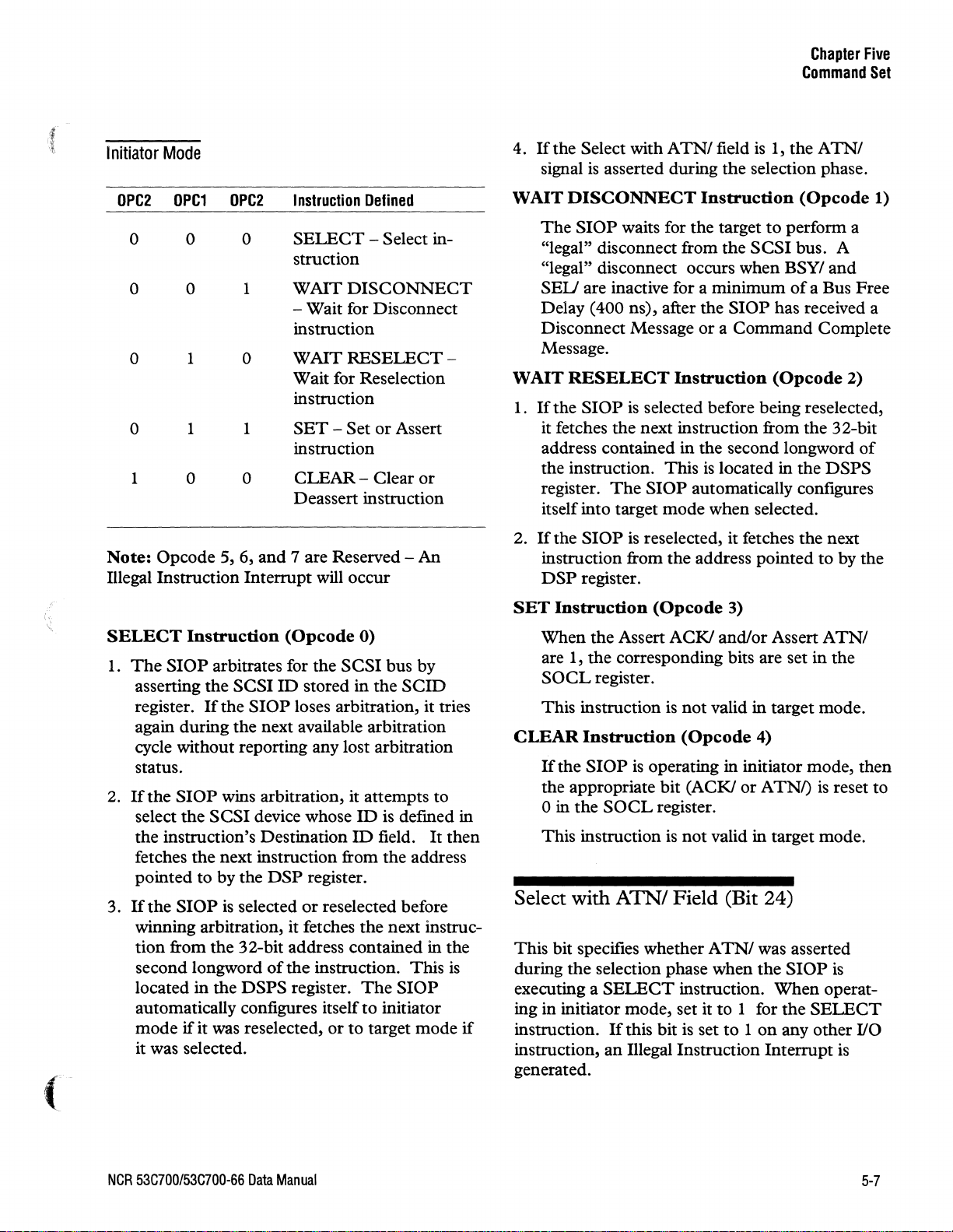

I/O Instructions ......................................................................................................................... 5-5

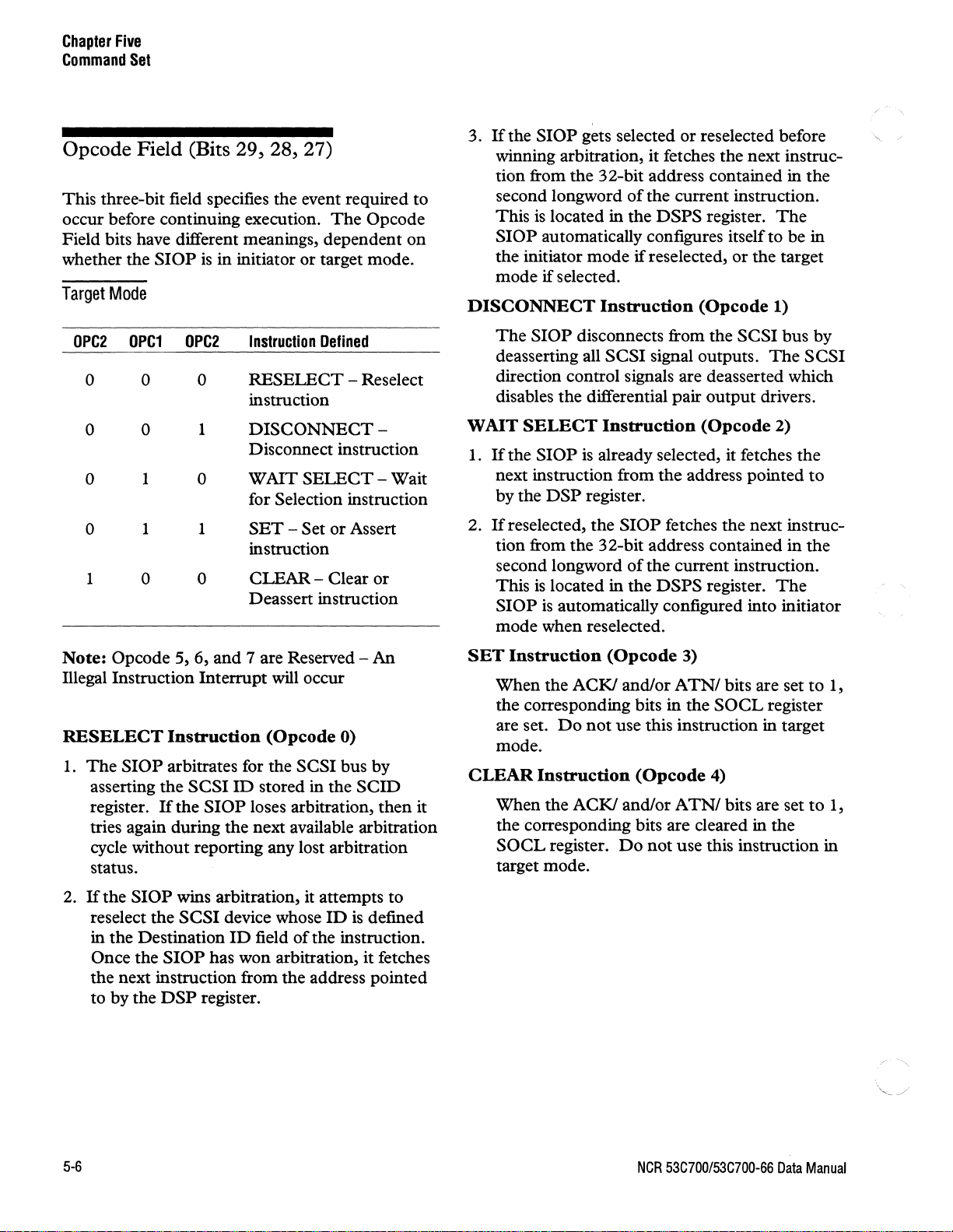

Opcode Field (Bits 29, 28, 27) .............................................................................................. 5-6

Select with A

SCSI

Destination

SET

Target Role (Bit 9) ....................................................................................................... 5-8

Assert

Jump

ACKI

Address Field .............................................................................................................. 5-8

TN/

Field (Bit 24) ............................................................................................ 5-7

ID

Field (Bits 23-16) ................................................................................ 5-8

(Bit 6) & Assert A

TN/

(Bit 3) Fields ................................................................. 5-8

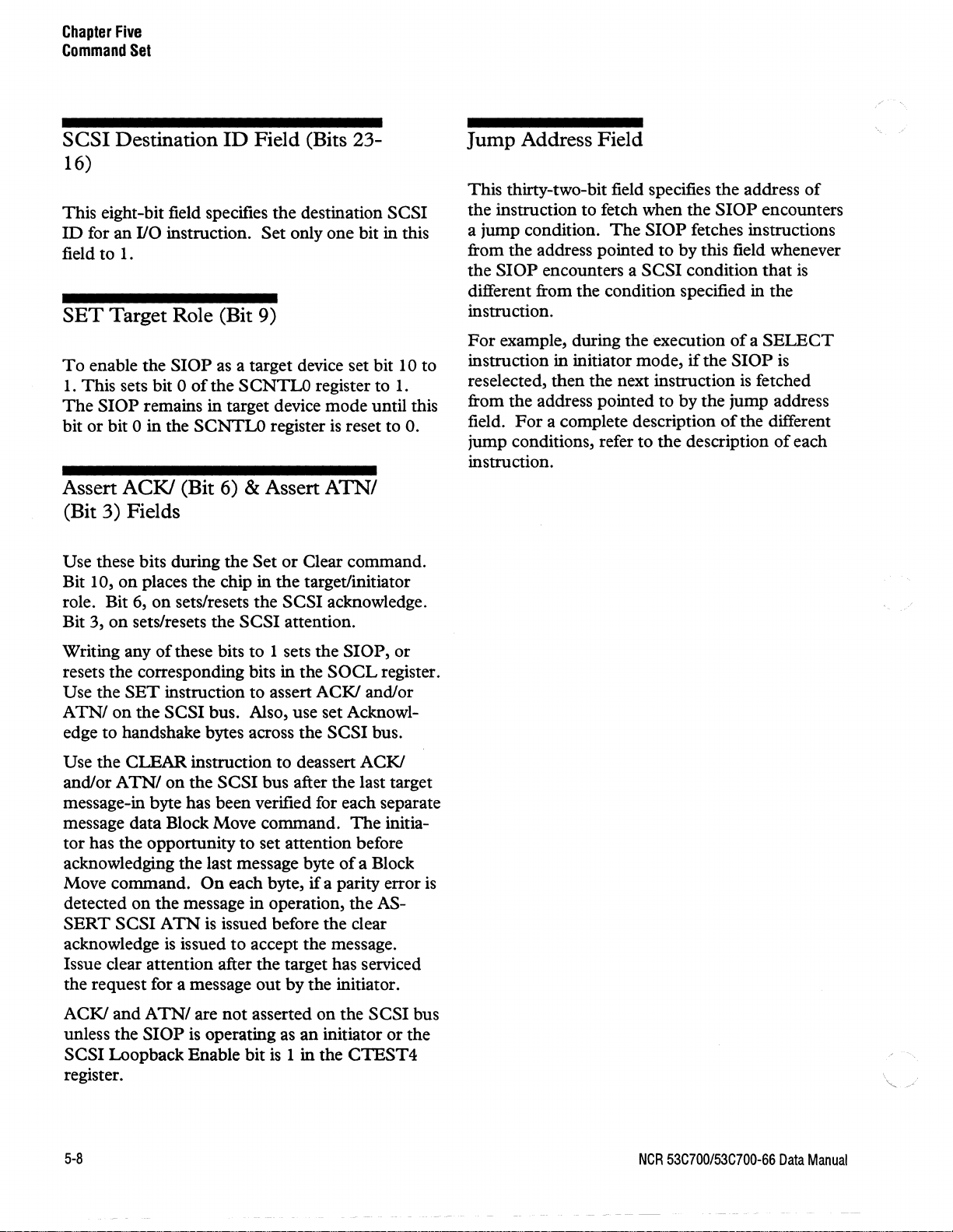

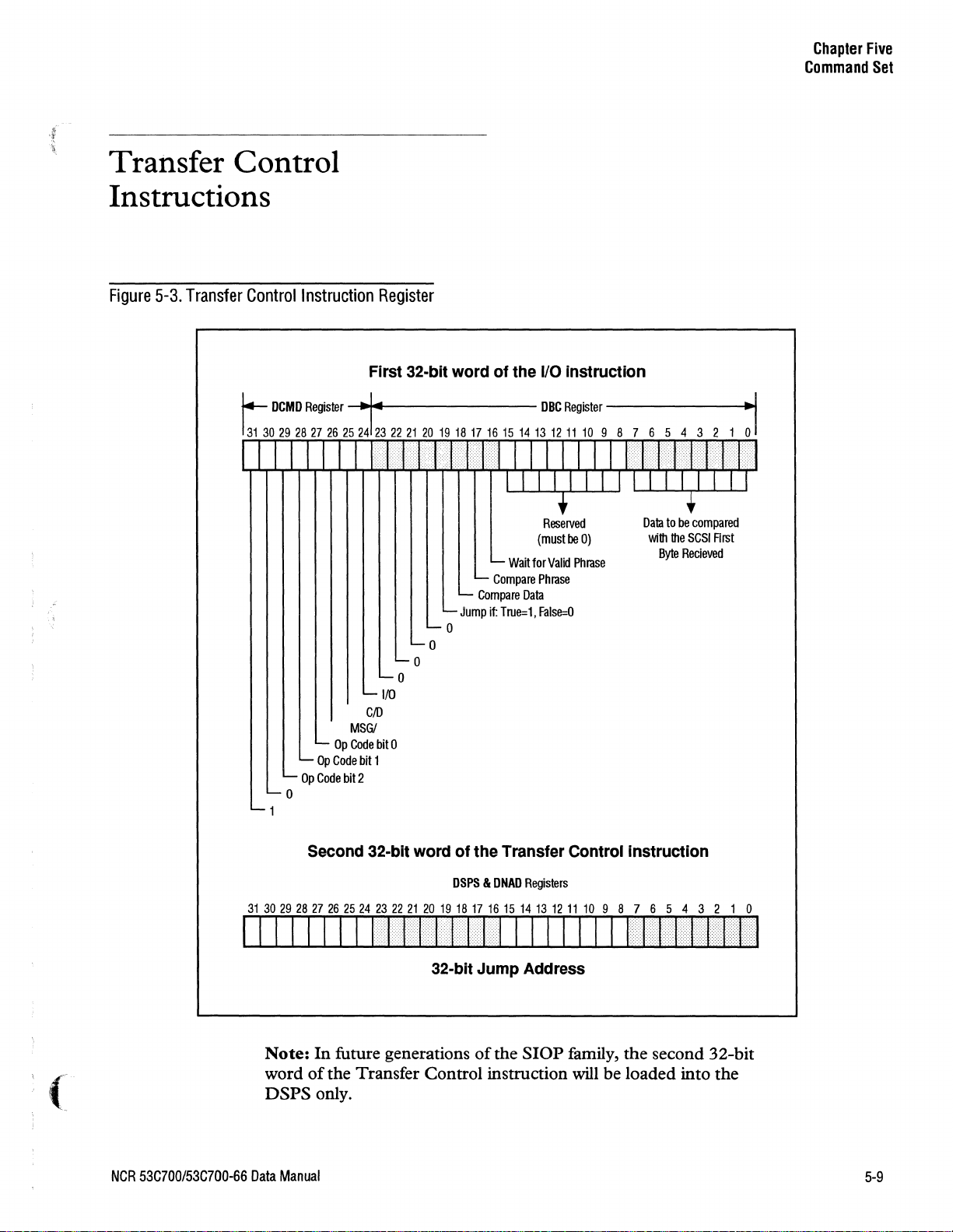

Transfer Control Instructions ..................................................................................................... 5-9

Chapter

How

to

Opcode Field (Bits

29,28,

27) ............................................................................................ 5-10

Phase Field (Bits 26, 25, 24) ............................................................................................... 5-11

Jump

if

TruelFalse Field (Bit 19) ........................................................................................ 5-11

Data

Compare

(Bit 18) ....................................................................................................... 5-12

Compare Phase Field (Bit 17) ............................................................................................. 5-12

Data

Compare

Mask for Compare

Data

to be Compared Field (Bits 7-0) ................................................................................. 5-13

Jump

Address Field (Bits 31-0,

Six

Use

the

How

to Start the

How

to Execute Normal

How

to Execute Single-Step

Steps Necessary to Start

How

to

Test

How

to Implement Parity Options ........................................................................................ 6-4

How

to Control Parity .......................................................................................................... 6-6

What Parity Errors

How

to

Test

Field (Bit 16) .............................................................................................. 5-12

Data

(Bits 15-8) .................................................................................... 5-12

DNAD

register) ................................................................. 5-13

53C700/53C700-66

SlOP

the

the

in the SCSI SCRIPTS

SCRIPTS

SCRIPTS

SCRIPTS

SlOP

in the Loopback Mode ....................................................................... 6-3

and

Interrupts Occur? ............................................................................. 6-7

DMA

FIFO

....................................................................................... 6-1

................................................................................. 6-1

....................................................................................... 6-2

................................................................................................ 6-8

Mode

............................................................. 6-1

NCR

53C700/53C700-66

Data

Manual

v

Page 8

How

to Test the SCSI FIFO ..................................................................................... ............ 6-9

How

to Abort an Operation ................................................................................................ 6-10

How

to Disconnect the

How

to Select a Target ....................................................................................................... 6-14

How

to Reselect

How

to Respond to Multiple SCSI IDs ............................................................................... 6-15

How

to

Use

How

to use Differential SCSI Interface ............................................................................... 6-18

an

Single-Ended SCSI Interface ........................................................................... 6-16

SlOP

.............................................................................................. 6-13

Initiator ................................................................................................ 6-14

How to Terminate the SlOP Device .................................................................................... 6-18

Chapter

Seven

Electrical Specifications

DC

Characteristics ..................................................................................................................... 7-1

NCR

TolerANT Active Negation Technology Electrical Characteristics (53C700-66 Only) ......... 7-5

AC

Electrical Characteristics ...................................................................................................... 7-9

Timings ...................................................................................................................................

Appendix

A

Register Summary

Appendix

B

Mechanical Drawing

Appendix

SCSI Engineering

C

Notes

7-10

Appendix

0

53C700

vi

vs

53C700-66

Differences

NCR

53C700/53C700-66

Data

Manual

Page 9

Chapter

Introduction

One

If

"

Chapter

One

Introduction

General Description

The

NCR

53C700

the industry's fIrst intelligent host adapter

The

chip.

eration solution for high-performance host-toperipheral interfacing.

integrated directly on the motherboard or externally adapted to EISA, Micro

buses.

The

(labeled and called

(labeled

and the 53C700-66 are both packaged

pin

Quad

differences exist between the two chips they will

be called by their names,

functionally equivalent they will be referred to by

SlOP.

SlOP

• Supports 25

memory bus speeds

• Supports 32-bit word data bursts with variable

burst lengths

• Unique interrupt status reporting

• High-speed asynchronous/synchronous

bus transfers

• High performance

• Supports variable block size & scatter/gather

data transfers

53C700 chip

53C700

and

called the 53C700-66).

Flat Pack (QFP). In this manual, when

Features Summary

is

available

and

SCSI

I/O Processor (SlOP)

is

a powerful, next gen-

The

53C700 can

Channel™,

as

either a 50

the

53C700)

but

33

MHz

CMOS

or

when they are

80386 and 80486

technology

a 66

The

on

be

or

MHz

MHz

53C700

as

a 160-

is

a

other

chip

chip

SCSI

• Minimizes

• Performs complex bus sequences without

interrupts

• Memory transfers

53C700 and

53C700-66

•

Single + 5 V supply

Active negation

and

ACK

technology improves rise times

transfer rates in both single-ended and differential modes

NCR

TolerANTTM

SCSI

I/O start latency

up

to 47 MB/s for the

up

to 62 MB/s for the

of

SCSI

signals with

Data, Parity,

NCR's

TolerANT

and

REQ

Fast SCSI

Active Negation Technology

TolerANT

NCR's

to

TolerANT (Active Negation Technology) allows

optional active negation

information transfer phases. More

TolerANT refers to

Technology in

of

ing

is

only in the 53C700-66 chip. Following

summary

in the

• Filters high frequency noise

inputs due to bus reflections

sients

• Wide hysteresis Schmitt triggers with optimal

threshold points

• Fast SCSI-2 performance

ended and differential cables

is

an

NCR

trade marked term referring

SCSI transceiver technology.

of

SCSI

NCR's

SCSI

drivers

input signal in

of

the

53C700-66 chip.

on

VTERM

SCSI

TolerANT

Active Negation

and

receivers. This feature

features

on

NCR's

signals during

specifIcally,

to the condition-

is

a

and

benefits

on

SCSI

signal

or

voltage tran-

both

single-

NCR

53C700/53C700-66

Data

Manual

1-1

Page 10

Chapter

Introduction

•

One

Better high level noise margin

on

SCSI

out-

puts

Reduced data double clocking problems

•

•

Controlled slew rate

• Compatible with

and

ALT-2

controlled V

OJIOH

termination, i.e.

terminator overload

•

Low

power dissipation in terminator

• Glitchless

•

No

current leakage from

powered

SCSI

down

outputs

on

power up/down

SCSI

bus when

• Active Negation

TolerANT

poor cabling environments.

are tolerant

other devices would

provides improved data integrity

NCR

SCSI

devices

of

cabling environments in which

be

subject to

data

corruption.

in

Active negation is some times called active

deassertion.

Active negation

in

(bit 4)

both

the

single-ended

TolerANT

One

and

Alternative

proposed by

is

enabled by setting

CTEST8

is

compatible with both the Alternative

the

American National Standards

register.

and

differential mode.

Two

termination schemes

It

the

can

EAN

be

used

Institute.

Active negation causes

data,

and

parity signals

to

be

actively pulled

REQ,

ACK,

up

the

SCSI

approximately three volts by internal transistors

each pin.

reduced noise when

The

benefits

the

of

this technology include

signal

is

going high

(deasserted), increased performance due to bal-

anced

duty

cycles,

and

improved

Fast

SCSI

transfer rates.

Benefit Summary

no

bit

in

to

on

Supports 32-bit word data bursts with variable

burst lengths

SCSI

Minimizes

110 start latency - Only 500

ns to begin compared to 2- 8 ms

Performs complex

bus

sequences without

interrupts including restore data pointers

Unique

ISR

interrupt status reporting - Reduces

overhead

High-speed asynchronous/synchronous

bus transfers

53C700153C700-66 = 5.0

53C700 = 6.25

53C700-66 = 10

Memory

MBls

MBls

transfers in excess

MBls

asynchronous

synchronous

synchronous

of

50

MB/s

Integration

Full 32-bit

High performance

Integrated

Allows intelligent

on

a mother

Ease

of

Use

Reduces

DMA

bus master

SCSI

SCRIPTS

Host

board

SCSI

development effort

core

processor

adapter performance

Emulates existing intelligent host adapters

Easily adapted

Method

(CAM)

to

the

SCSI

Common

Access

Preserves existing software

Development tools

and

SCSI

SCRIPTS

provided

All interrupts are maskable

and

pollable

SCSI

Performance

Supports 25

and

33

memory bus speeds

Supports variable block size

data transfers

1-2

MHz

80386

or

80486

& scatter/gather

Flexibility

High level programmer's interface (SCSI

SCRIPTS)

Allows tailored

main

from

SCSI

memory

sequences

NCR

53C700/53C700-66

to

be

executed

Data

Manual

Page 11

Chapter

Introduction

One

Flexible sequences

to

adapt

to

unique

to

tune

SCSI

Accommodates changes in

interface defmition

Low

level programmability (register oriented)

80286,

Externally adaptable

80386SX, 80386

to

EISA,

other system buses

Supports changes from initiator

dynamically

Reliability

2 K volts

Typical

ESD

350

protection

mV

SCSI

bus hysteresis

Protection against bus reflections

impedance mismatches

bus

Controlled

improves reliability,

assertion times (reduces

and

tion)

110 performance

devices

the

logical 110

or

80486 support

SCSI

eases

MCA,

FCC

and

to

target roles

signals

due

to

certifica-

or

RFI,

Latch-up

protection greater

Voltage feed-through protection

leakage

20%

Ground

current

of

signals are power

through

plane isolation

of

logic

Testability

All

SCSI

signals accessible

grammedllO

SCSI

loopback diagnostics

Self-selection capability

SCSI

bus signal continuity checking

than

SCSI

and

ground

110 pads

through

100 rnA

(minimum

pads)

and

pro-

chip

NCR

53C700/53C700-66

Data

Manual

1-3

Page 12

~

J,..

SCSI

Core

---------

DMACore

SCSI

FIFO

-----

--

--

SCSI

Data

Test

rl

11

SCSI

and

Reserved

DMA

Async

I

Sync

I

Registers

Registers

Registers

Control

Control

•

SCSI

I

I

I

I

---------

-

Control

SCSI

Sequences

~

ro--------

.on

cO·

c::

@

.....

I

.....

z

C")

::tI

U'I

Ct.)

C")

""-J

o

!i;2

U'I

Ct.)

C")

~

o

I

0)

0)

c::I

g

A

C

~.

PJ

3

-

C")

==-

:::1»

CI"CI

CI.

_

c::

m

n-

:::'c

CI=

=m

z

(")

jj

~

.....

~

n

.....

g

a.

C'>

c

s-

s:

~

s:::

e!...

DMA

FIFO

Host

Data

I/O

Control

-

SCRIPT

Host

Bus

Host

Processor

Control

Control

(

Page 13

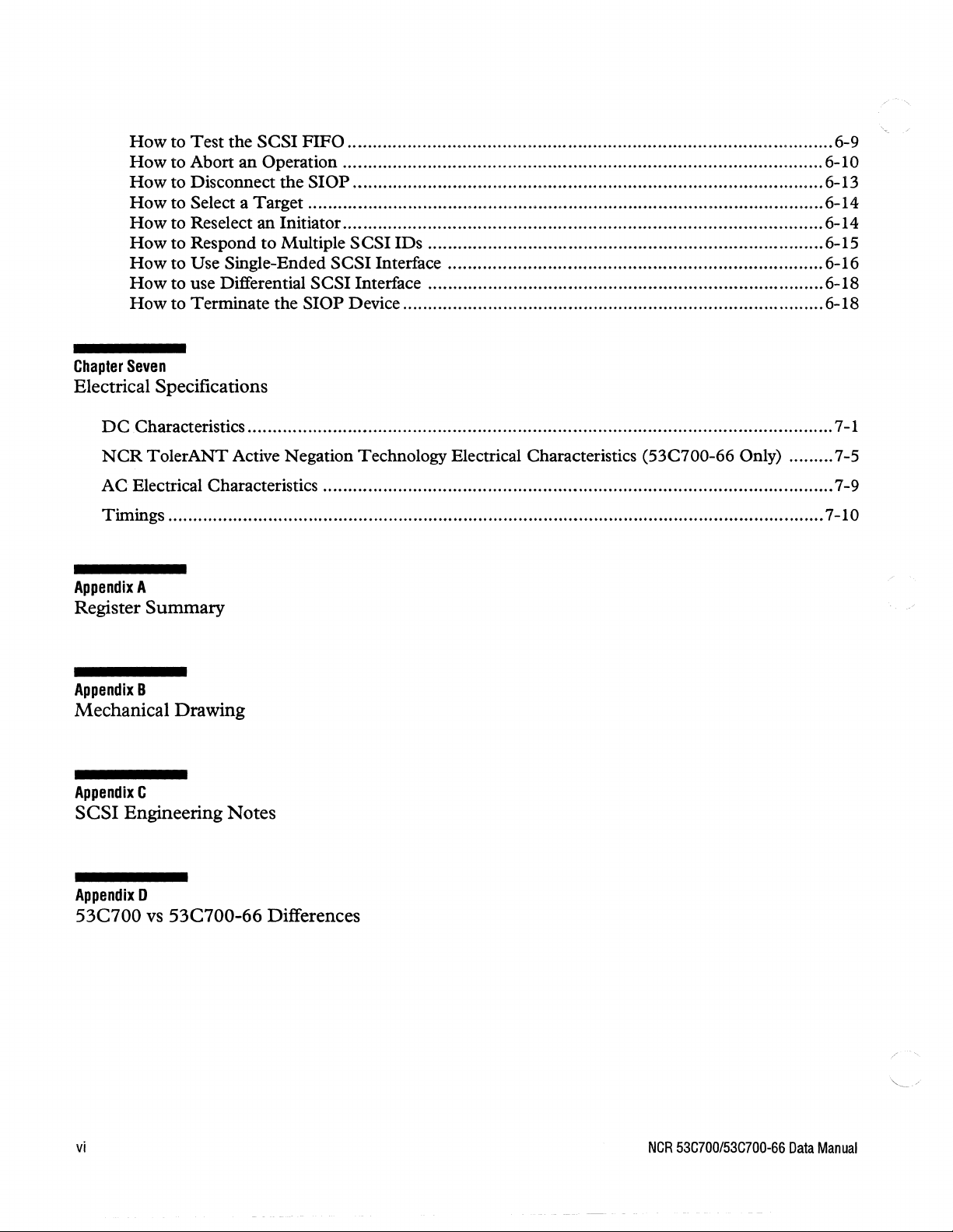

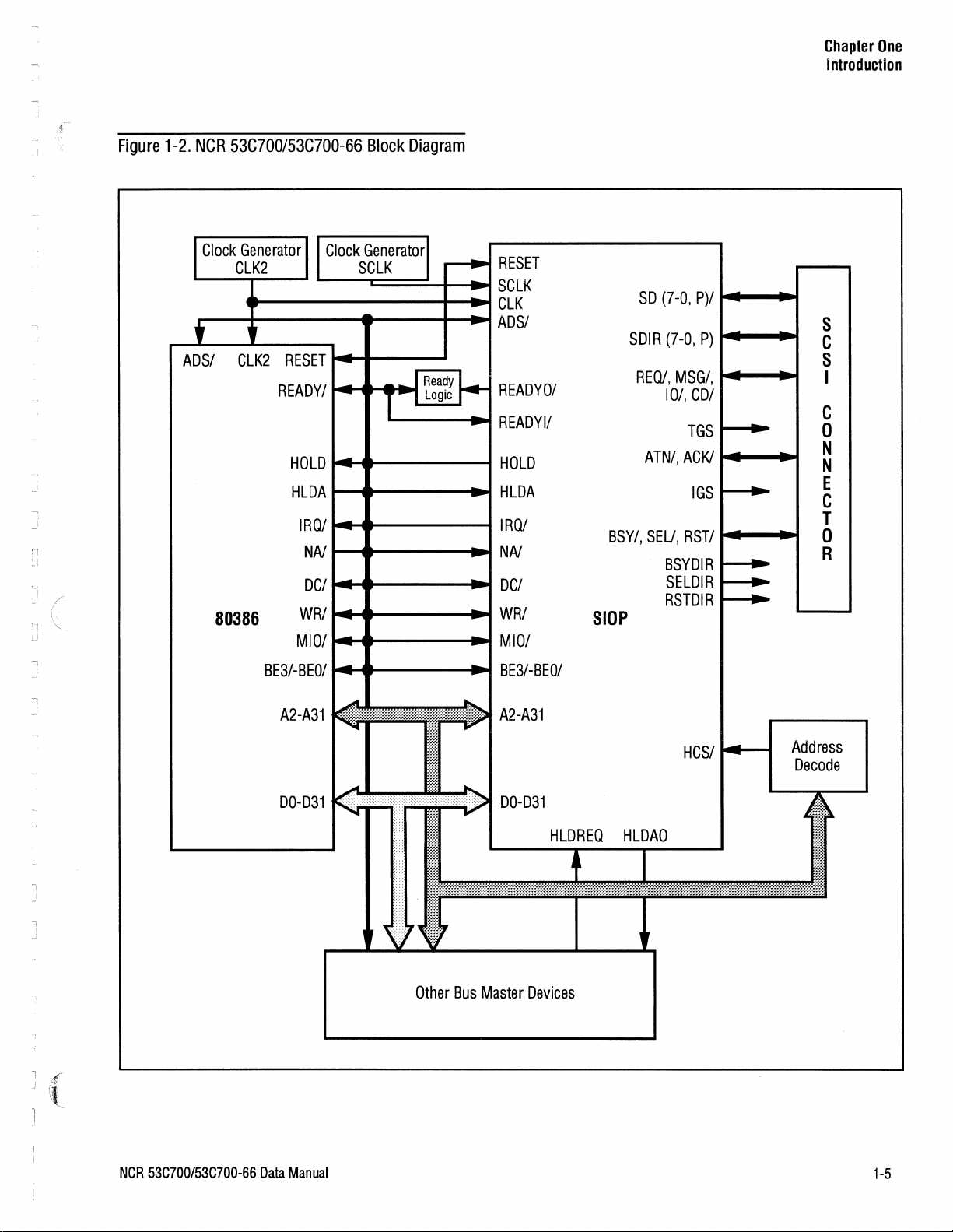

Figure

1-2.

ADSI

NCR

53C700/53C700-66

I

Clock

Generator

CLK2

t

CLK2

80386

RESET

READYI

HOLD

HLDA

BE3/-BEOI

Block

Diagram

II

Clock

Generato

SCLK

_ I

Ready

T

-1

-

IRQ! IRQ!

NN

DCI

-

..

WR/

MIOI MIOI

logic

..

- -

..

-

I---

-

-

-

..

..

..

RESET

SCLK

CLK

ADSI

READYOI

READY

HOLD

HLDA

NN

DCI

WRI

BE3/-BEOI

II

BSY/,

SlOP

SD

SDIR

REQ!,

ATN/,

SEU,

(7-0,

P)I

(7-0,

P)

MSG/,

101,

CDI

TGS

ACKI

IGS

RSTI

BSYDIR

SELDIR

RSTDIR

..

..

Chapter

Introduction

S

C

S

I

C

0

N

N

E

C

T

0

R

One

A2-A31

A2-A31

f4

DO-D31 DO-D31

~

.........

~

>

~

HLDREQ

Jf

Other

Bus

Master

Devices

HLDAO

r

HCSI

Address

Decode

J.

~

NCR

53C700/53C700-66

Data

Manual

1-5

Page 14

[

[

Page 15

pier

Functional Description

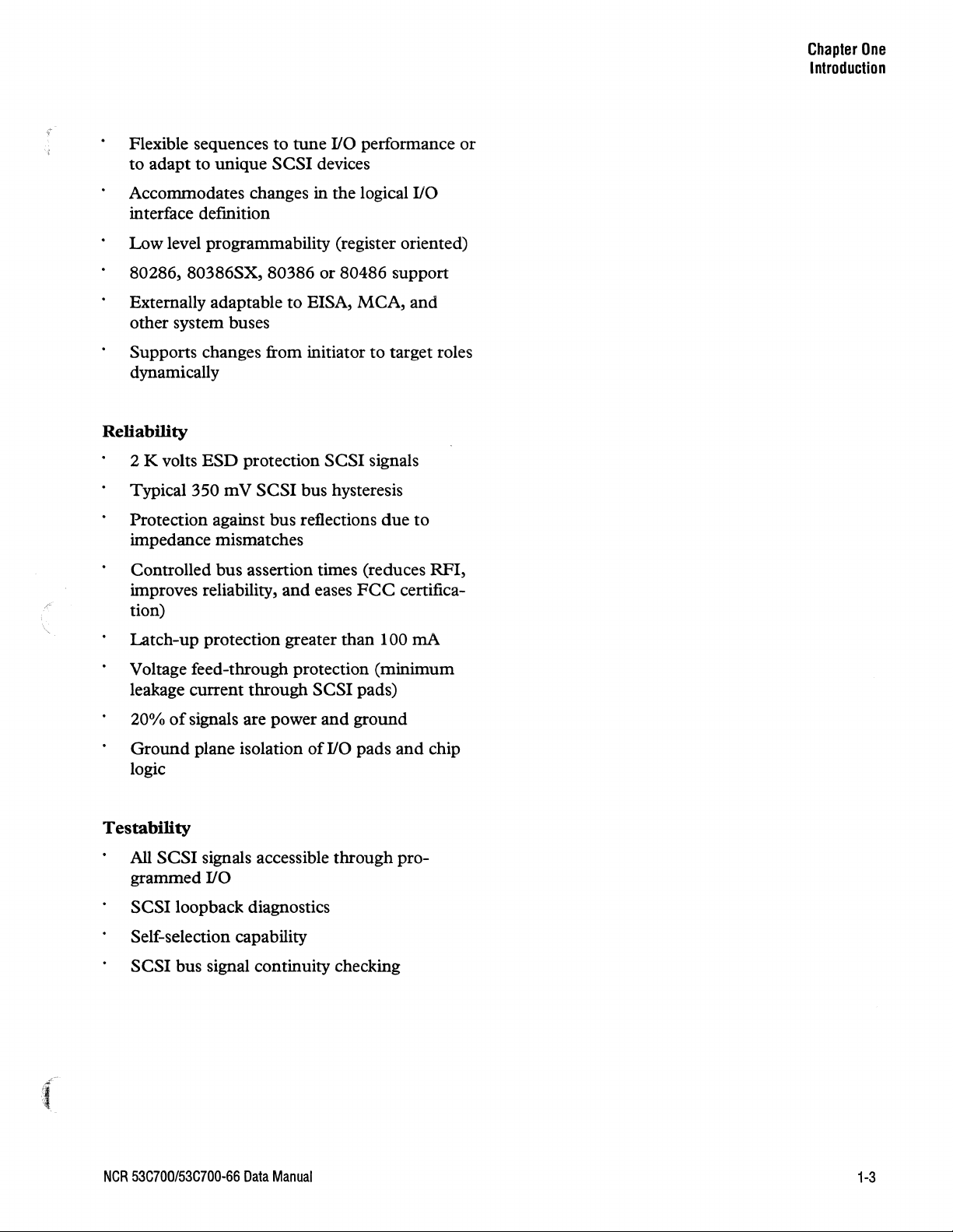

The

NCR

53C700

the first intelligent SCSI Host adapter on a chip.

A high-performance

32-bit bus master

integrated with a

accommodate the flexibility requirements

only

SCSI-I,

This flexibility

protocol performance problems that have plagued

both intelligent and non-intelligent adapter de-

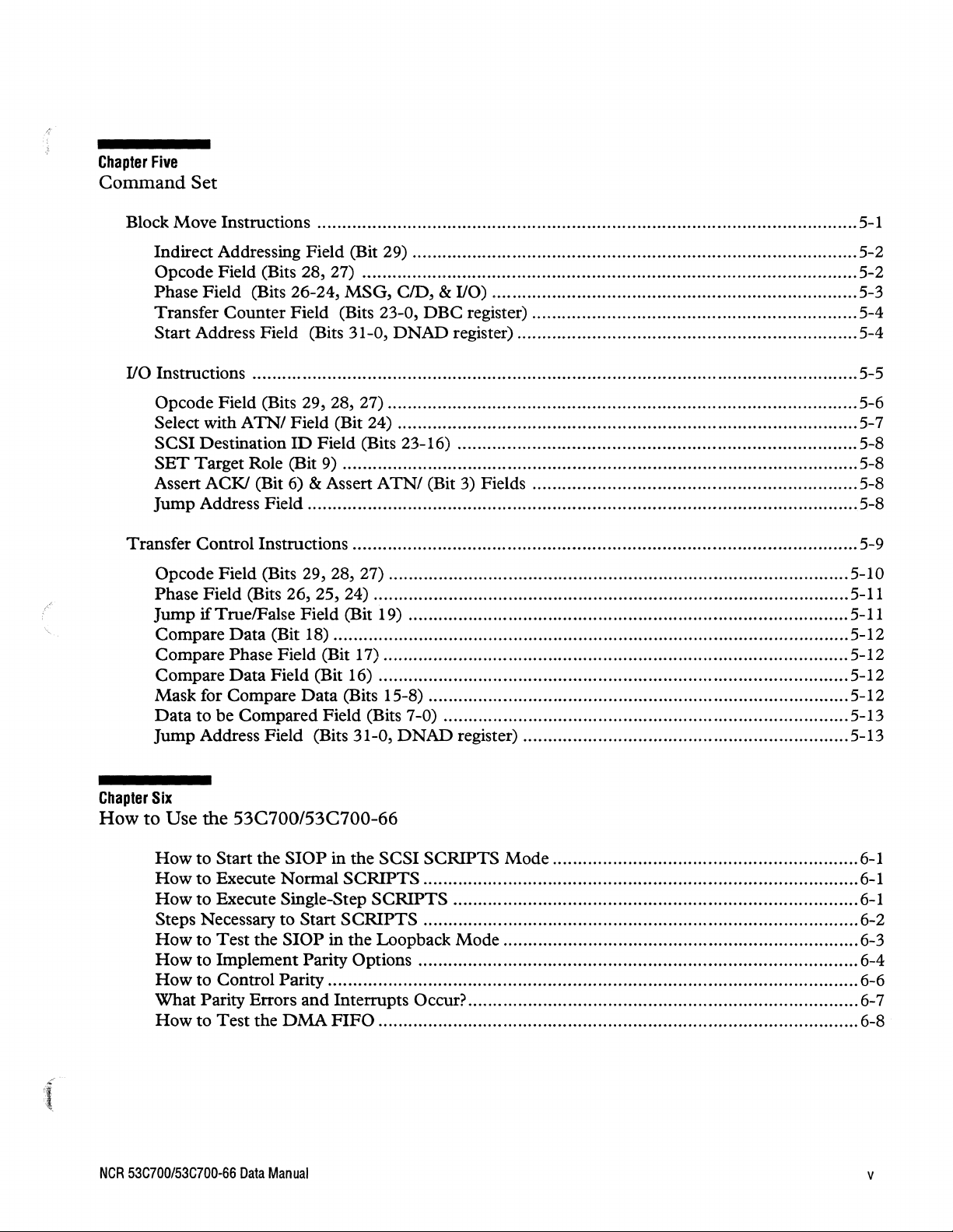

(See the SCSI I/O Processor Block Diagrams

signs

in Figures

the same structure as the

features.

1-1

SCSI

I/O Processor (SlOP)

SCSI

core and an intelligent

DMA

SCSI

but

SCSI-2,

is

supported while solving the

and 1-2).

controller have been

SCRIPTS

and

The

53C700 plus added

Processor™ to

eventually SCSI-3.

53C700-66 contains

of

is

not

Chapter

Functional

ported.

selection and operate as

target.

physical connection to the board or the

Unlike previous generation devices, the

can be controlled by the

through a high level logical interface. Commands

controlling the

main Host memory. These commands instruct

the

for a disconnect, transfer information, change bus

phases and in general, implement all aspects

SCSI protocol.

The

SCSI

core may perform a self-

both

an initiator

The

53C700 can test the

SCRIPTS

SCSI core are fetched out

SCSI core to select, reselect, disconnect, wait

SCSI

pins for

SCSI bus.

SCSI core

Processor

Two

Description

and

a

of

the

of

the

J

,~

SCSI Core

The

SCSI core

tion to

nous transfer rate requirements.

offers synchronous transfers

asynchronous transfers

53C700-66 offers synchronous transfers

MB/s with asynchronous transfers

The

to

requirements or

The

high level control interface. Like first generation

SCSI devices, the

cessed as a register oriented device.

sample and/or assert any signal on the

can be used in error recovery and diagnostic

procedures. Loopback diagnostics are also sup-

SCSI-2 wide bus and enhanced synchro-

programmable SCSI interface makes it easy

"fine

tune"

SCSI core offers low level register access or a

is

designed to allow simple migra-

The

53C700

up

to 6.25 MB/s with

up

to 5 MB/s.

the system for specific mass storage

SCSI-2 requirements.

SlOP

SCSI

core can be ac-

The

up

to 5 MB/s.

The

SCSI bus

up

to 10

ability to

DMACore

The

DMA

attaches easily to the 80286, 80386,

and 80486 processors.

MHz

MHz

externally adapted to other system buses such

EISA, Micro Channel or attached through a "bus

gasket"

The

SlOP

automatically supports misaligned

As

with the 80386/80486, data bus enables are

provided for each byte lane. A 32-byte

allows the

or 32-bit) words to

bus interface providing memory transfer rates

to 47 MB/s for the 53C700

53C700-66.

core

is

a bus master

The

80386/80486 (the 53C700-66 supports 33

80386/80486) bus timings and may be

to a 680XO

supports 16 or 32-bit memory and

SlOP

device.

to support two, four, or eight (16

be

burst across the memory

DMA

53C700 supports 25

and

device that

80386SX,

as

DMA

62 MBlsec for the

transfers.

FIFO

up

(

NCR

53C700/53C700-66

Data

Manual

2-1

Page 16

Chapter

Functional

The

through

uninterrupted

Two

Description

DMA

the

core is tightly coupled

SCRIPTS

processor which supports

to

the

SCSI

scatter/gather memory operations.

core

A flexible arbitration scheme allows either daisychained

"ORed"

memory bus request imple-

or

mentations.

SCSI

SCRIPTSTM

Processor

new

bus device types (i.e. scanners, communication gateways, etc.),

the

SCSI-2/310gical bus defmitions without

sacrificing

SCSI

system

I/O

SCRIPTS

bus

in

use. Therefore, scripts for

implementation

the

scripts for

an

or

to

incorporate changes in

performance.

are independent

of

an

80386

80386SX

Micro

can

ofthe

be

identical

Channel

plementation.

CPU

an

im-

and

EISA

to

The

SCSI

SCRIPTS

processor

structions

that

to

allows

be

Algorithms written

the actions

executed

Complex

pendently

The

SCRIPTS

operation in

ofthe

from

SCSI

of

the

500

16

required for traditional intelligent

The

SCRIPTS

Processor

both

fetched from

in

SCSI

SCSI

and

or

32-bit system memory.

bus

sequences are executed inde-

Host

CPU.

Processor can begin a

ns.

This

is

a 2

DMA

and

Host

memory.

SCRIPTS

DMA

cores

compares

Host

MIPS

SCSI

can

and

SCSI

to

2-8

adapters.

control

Processor offers performance

in-

are

110

ms

and

customized algorithms. Design your own algorithms

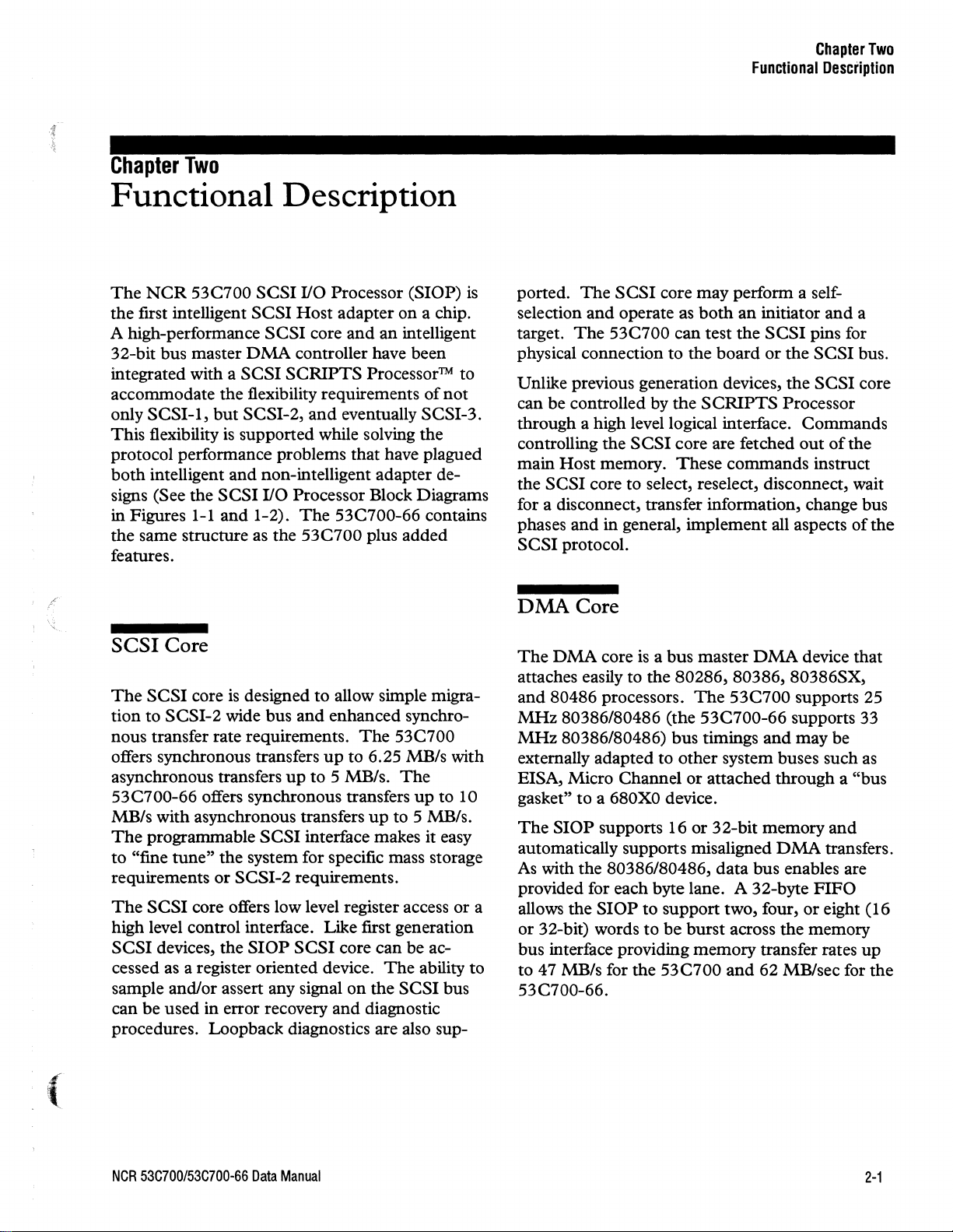

Figure

to

2-1.

tune

SlOP

SCSI

Data

bus

performance,

Paths

to

adjust

SlOP

The

on

two things.

• Is

• Is

Figure 2-1 shows

the

To

determine

when

ing steps.

to

Data

data paths

data

SCSI

Paths

through

being moved

data being sent asynchronously

the

in

synchronously.

how

data

SCSI

bus

in

each

of

the

if

any

bytes remain in

the

chip halts any operation, take

SlOP

is

or

out

moved

are

dependent

of

the

to

four modes.

the

chip

or

from

data

the

or

path

follow-

2-2

Asynchronous

SCSI

Send

Asynchronous

SCSI

Receive

Synchronous

SCSI

Send

Synchronous

SCSI

Receive

NCR

53C700/53C700-66

Data

Manual

Page 17

Functional

Chapter

Description

Two

•

Asynchronous

Target

1.

Use the algorithm described in the

register description to determine

are left in the

2.

Read the

to determine

register.

in the

number

•

Synchronous

SST

SODL

of

Target

1. Use the algorithm described in the

register description to determine

are left in the

2. Read the SSTAT1 register and test bit 5 to

determine

register.

byte in the

to the number

3. Read the

determine

SODR

one byte in the

one to the number

•

Asynchronous

SST

register.

Target

1. Use the algorithm described in the

register description to determine

are left in the

2. Read the SSTAT1 register and test bit 7 to

determine

register.

byte in the

to the number

•

Synchronous

Target

SCSI

Send -Initiator

Operation

DFIFO

if

DMA

AT

if

If

bit 5 equals 1, then there

register and add one to the

bytes left.

FIFO.

1 register and examine bit 5

any bytes are left in the

SCSI

Send -Initiator

Operation

DFIFO

if

DMA

if

any bytes are left in the

Ifbit

SODL

AT

if

any bytes are remaining in the

FIFO.

5 equals

register, therefore, add one

of

bytes left.

1 register and test bit 6 to

Ifbit

SODR

SCSI

1,

then there

6 equals 1, then there

register, therefore, add

of

bytes left.

Receive -

Initiator

Operation

DFIFO

if

DMA

if

any bytes are left in the

If

bit 7 equals 1, then there

SIDL

SCSI

FIFO.

register, therefore,

of

bytes left.

Receive -

Initiator

Operation

and

any bytes

SODL

is

a byte

and

any bytes

SODL

is

one

any bytes

SIDL

is

one

add

one

is

and

and

2. Read the

(the binary representation

valid bytes in the SCSI FIFO) to determine

any bytes are left in the

How the

16

or 32-Bit Data

The

SlOP

transfer.

transferred are summarized below. These two bits

do not determine how

fetched.

register controls whether

loaded 16-bits per transfer or 32-bits per transfer.

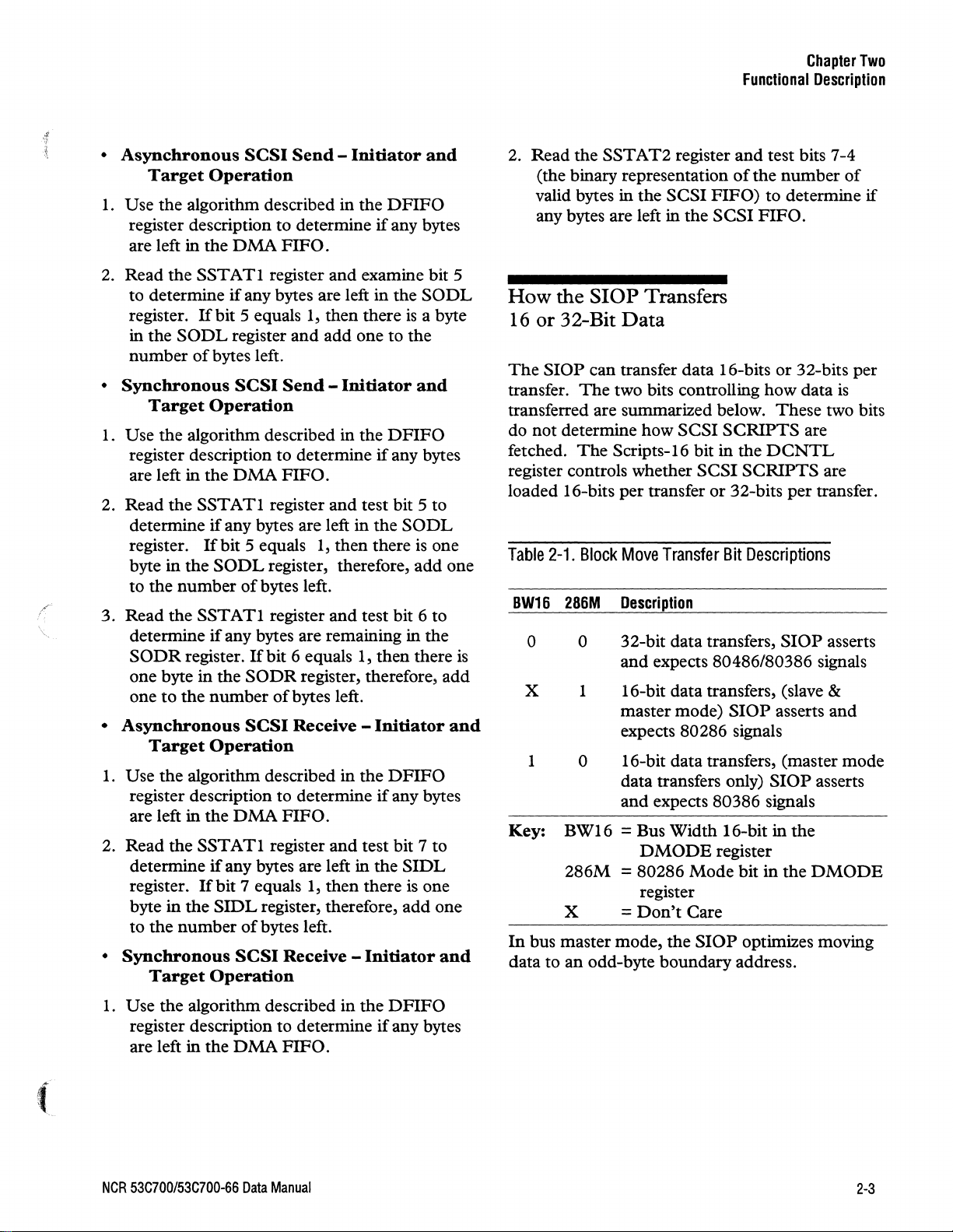

Table

2-1.

BW16

o o

SST A T2

SlOP

can transfer data 16-bits or 32-bits per

The

two bits controlling how data

The

Scripts-16 bit in the

Block

Move

286M

Description

32-bit data transfers,

and expects

register

SCSI

Transfers

SCSI

SCSI

Transfer

80486/80386 signals

and

test bits 7-4

of

the number

FIFO.

SCRIPTS

DCNTL

SCRIPTS

Bit

Descriptions

SlOP

are

of

if

is

are

asserts

x 1 16-bit data transfers, (slave &

master mode)

expects

1

Key: BW16

In

bus master mode, the

data to

0 16-bit data transfers, (master mode

data transfers only)

and expects

= Bus Width 16-bit in the

DMODE

286M

X

an

= 80286 Mode bit in the

=

Don't

odd-byte boundary address.

80286 signals

register

SlOP

80386 signals

register

Care

SlOP

optimizes moving

asserts and

SlOP

asserts

DMODE

1.

Use the algorithm described in the

register description to determine

are left in the

NCR

53C700/53C700-66

DMA

Data

FIFO.

Manual

DFIFO

if

any bytes

2-3

Page 18

Chapter

Functional

Two

Description

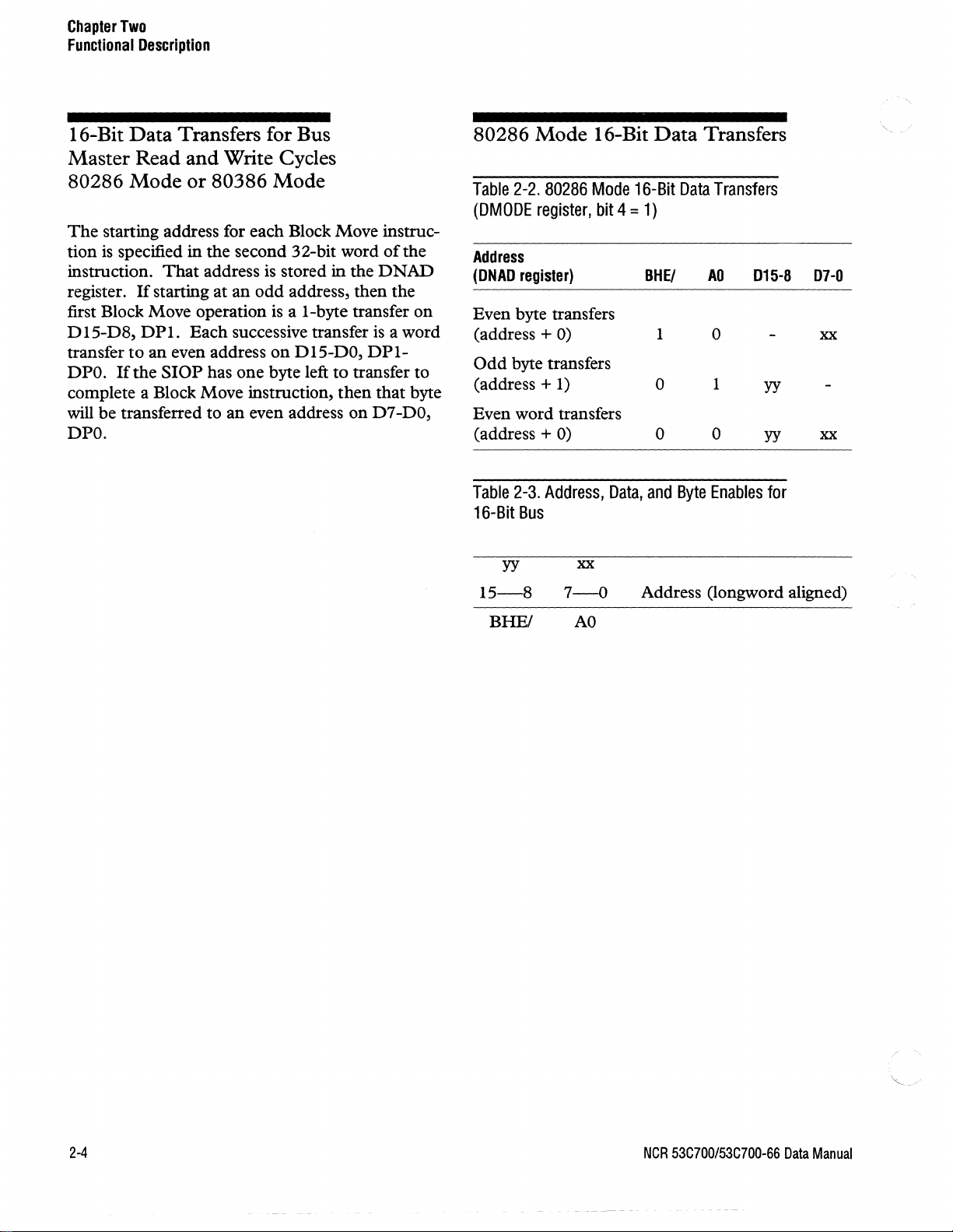

16-Bit

Master Read

80286

The

tion

instruction.

register.

first Block Move operation

DlS-D8,

transfer

DPO.

complete a Block Move instruction,

will

DPO.

Data

Mode

starting address for each Block Move instruc-

is

specified

to

If

be

transferred

Transfers for Bus

and

Write Cycles

or

80386

in

the

second 32-bit word

That

address is stored

If

starting

DPl.

an

the

SlOP

at

an

Each

successive transfer

even address

has

to

an

Mode

odd

address,

is

a I-byte transfer

on

DIS-DO,

one

byte left

even address

in

the

then

to

transfer to

then

on

of

the

DNAD

the

is

a word

DPl-

that

byte

D7-DO,

on

80286

Table

(DMODE

Address

(DNAD

Even byte transfers

(address

Odd

(address

Even word transfers

(address

Table

16-Bit

Mode

2-2.

80286

register,

register)

+ 0)

byte transfers

+ 1) 0

+ 0)

2-3.

Address,

Bus

yy

xx

16-Bit

Mode

bit

Data,

16-Bit

4 =

Data

Data

1)

BHEI

1

0 0

and

Byte

Transfers

Transfers

015-8

AO

0

1

Enables

yy

yy

for

D7-0

xx

xx

15-8

BHEI

7--0

AO

Address (longword aligned)

2-4

NCR

53C700/53C700-66

Data

Manual

Page 19

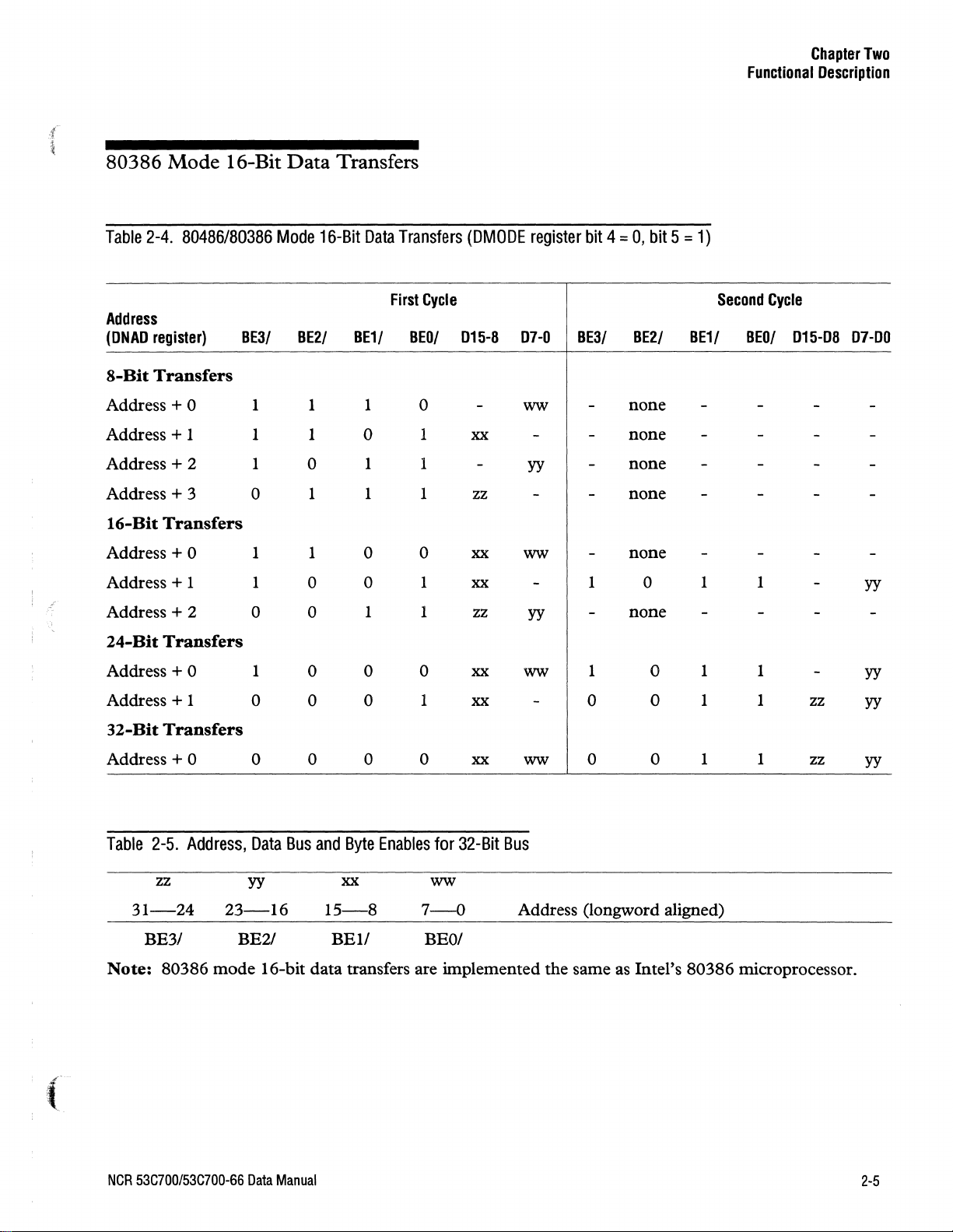

Functional

Chapter

Two

Description

80386

Table

Address

(ONAO

8-Bit

Address + 0

Address + 1

Address + 2

Address + 3 0

16-Bit

Address + 0

Address + 1

/

Address + 2 0 0

Mode

2-4.

80486/80386

register)

Transfers

Transfers

16-Bit

Data

Mode

BE31

1

1 1

1

1 1 0 0

1

Transfers

16-Bit

BE2/

1 1

0

1

0 0

Data

BEll

0

1 1

1 1

1 1

Transfers

First

BEOI

0

1 xx

Cycle

015-8 07-0

(DMODE

ww

yy

register

BE31

zz

xx

1 xx 1 0

zz

ww

yy

bit

4 =

0,

bit

BE2/

none

none

none

none

none

none

5 =

1)

BEll

Second

BEOI

1 1

Cycle

015-08 07-00

yy

24-Bit

Address + 0

Address + 1 0 0 0

32-Bit

Address + 0 0

Table

Note:

Transfers

Transfers

2-5.

zz

31-24

BE31

80386

Address,

23-16

BE2I

mode

1

Data

yy

0

0 0 0

Bus

and

Byte

xx

15-8

BEll

16-bit data transfers are implemented the same as Intel's

0 0

1 xx

Enables

7-0

for

ww

BEOI

xx

xx

32-Bit

ww

ww

1 0

0 0

0 0 1

Bus

Address (longword aligned)

80386

1 1 yy

1 1

1

microprocessor.

zz

zz

yy

yy

('

NCR

53C700/53C700-66

Data

Manual

2-5

Page 20

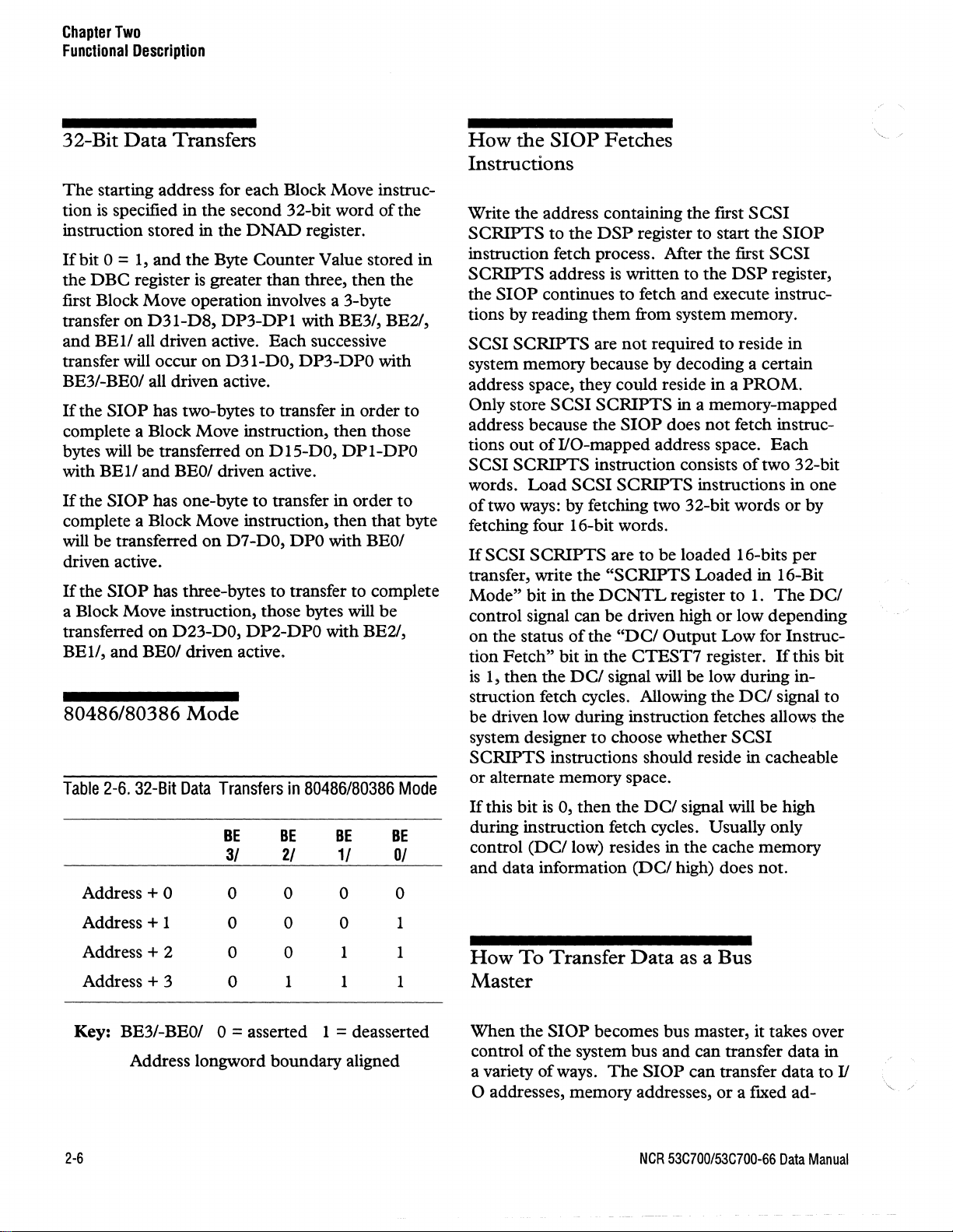

Chapter

Functional

32-Bit

The

tion

instruction stored in

If

the

first Block

transfer

and

transfer will

BE3/-BEOI all driven active.

If

complete a Block Move instruction,

bytes will be transferred

with

If

complete a Block Move instruction,

will

driven active.

If

a Block Move instruction, those bytes

transferred

BEll,

80486/80386

Table

Two

Description

Data

starting address for each Block Move instruc-

is

specified in

bit 0 = 1,

DBC

on

BEll

the

SlOP

BEll

the

SlOP

be

transferred

the

SlOP

and

Transfers

the

second 32-bit word

the

DNAD

and

the

Byte

Counter

register

Move

D3I-D8,

all driven active.

and

BEOI driven active.

is

greater

operation involves a 3-byte

DP3-DPI

occur

on

D31-DO, DP3-DPO with

has two-bytes

BEOI driven active.

has one-byte

on

has three-bytes

on

D23-DO, DP2-DPO with BE2I,

to

on

to

D7-DO, DPO with BEOI

register.

Value stored

than

three,

with BE3/, BE2I,

Each

successive

transfer in order

DIS-DO,

transfer in

to

transfer to complete

then

then

DPI-DPO

order

then

will

Mode

2-6.

32-Bit

Data

Transfers

BE

3/

Address + 0 0 0 0 0

in

80486/80386

BE

2/

BE BE

1/

ofthe

the

to

those

to

that

be

Mode

0/

in

byte

How

the

SlOP

Fetches

Instructions

Write

the

address containing

SCRIPTS

instruction fetch process.

SCRIPTS

the

SlOP

tions by reading

SCSI

system

address space, they could reside

Only store

address because

tions

SCSI

words.

of

two ways: by fetching two 32-bit words

fetching four 16-bit words.

If

SCSI

transfer, write

Mode"

control signal can

on

the

tion

is

I,

struction fetch cycles. Allowing

be

driven low during instruction fetches allows the

system designer

SCRIPTS

or

alternate

If

this

during instruction fetch cycles.

control

and

to

address

continues

SCRIPTS

memory

SCSI

out

of

1I0-mapped

SCRIPTS

Load

SCRIPTS

bit

in

status

Fetch"

then

the

instructions should reside in cacheable

bit

is

0,

(DCI

data

information

the

DSP

register to start

is

written to

to

fetch

them

from system memory.

are

not

because by decoding a certain

SCRIPTS

the

SlOP

instruction consists

SCSI

SCRIPTS

are to

the

"SCRIPTS

the

DCNTL

be

driven high

of

the

"DCI

bit

in

the

CTEST7

DC!

signal will be low

to

choose whether

memory

then

low) resides in

space.

the DC! signal will

(DCI

the

first

SCSI

the

Mter

the

first

SCSI

the

DSP

register,

and

execute instruc-

required

does

address space.

be

register

Output

to

reside

in a PROM.

in a memory-mapped

not

fetch instruc-

Each

of

two 32-bit

instructions

loaded 16-bits

Loaded

register.

Usually only

the

high) does not.

in 16-Bit

to

1.

The

or

low depending

Low

for Instruc-

Ifthis

during

the

DCI

signal

SCSI

be

cache

memory

SlOP

in

or

high

in

by

per

in-

one

DCI

bit

to

\

""'-.

,/

Address + I 0 0

Address

Address

Key:

2-6

+ 2 0

+ 3

BE3/-BEOI

Address longword boundary aligned

0

0=

asserted 1 = deasserted

0

0

I I 1

1 I

1

How

To

Transfer

Master

When

control

a variety

the

of

SlOP

the

of

o addresses,

Data

becomes bus master, it takes over

system bus

ways.

The

memory

as a Bus

and

can

SlOP

can

transfer

addresses,

NCR

53C700/53C700-66

or a fIXed

transfer

data

data

ad-

Data

in

to II

Manual

Page 21

Functional

Chapter

Description

Two

dress.

width and type

once the

The

following three bits determine the

of

data transfer that will occur

SlOP

assumes bus mastership and

is

ready to transfer data.

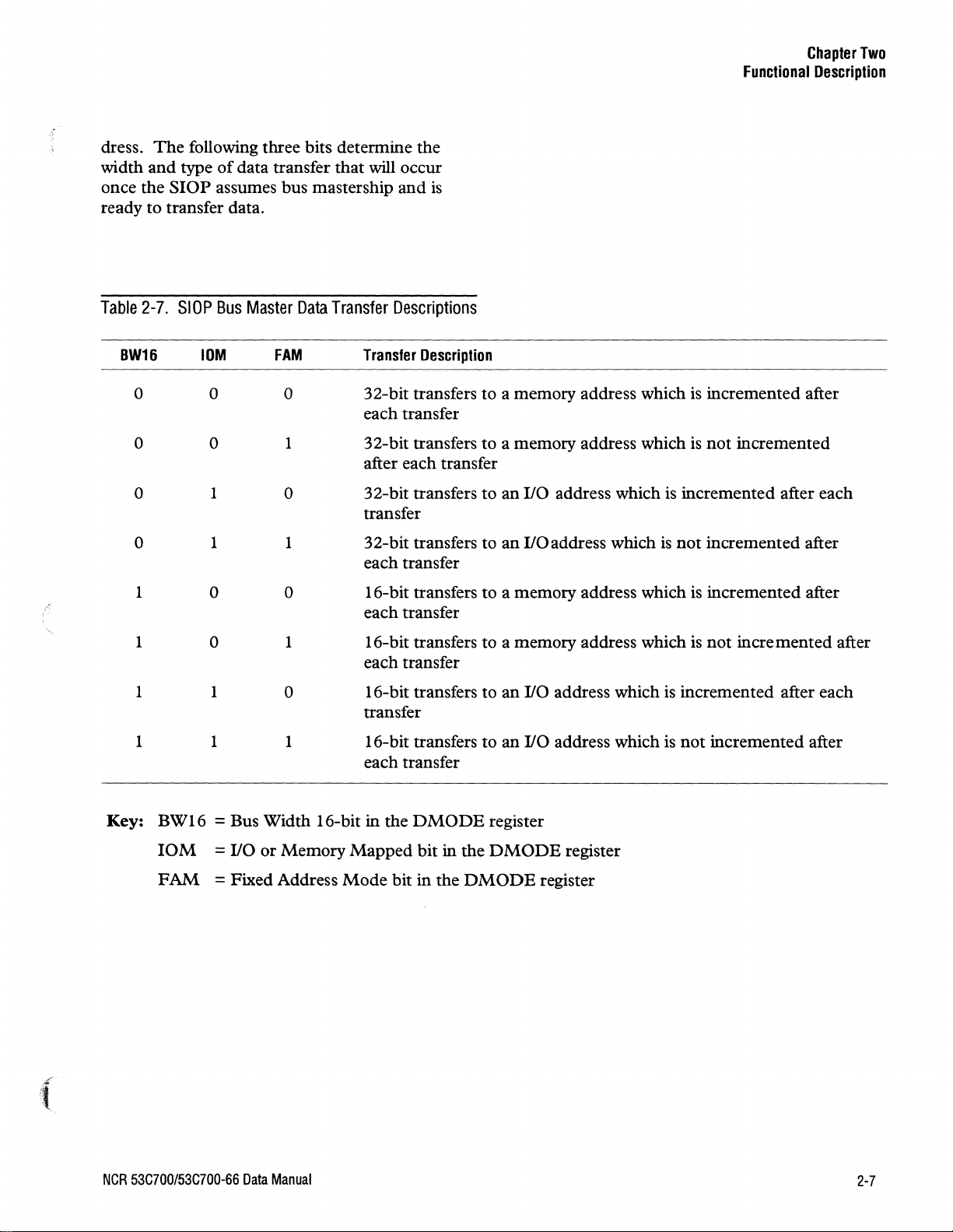

Table

2-7.

SlOP

Bus

BW16

0 0

Master

10M

Data

FAM

0

Transfer

Descriptions

Transfer

Description

32-bit transfers to a memory address which

is

incremented after

each transfer

0 0

1

32-bit transfers to a memory address which

is

not incremented

after each transfer

0

1

0

32-bit transfers to an

110 address which

is

incremented after each

transfer

0 1

1

32-bit transfers to an

110 address which

is

not

incremented after

each transfer

1

0

0

16-bit transfers to a memory address which

is

incremented after

each transfer

"-

I

0 1 16-bit transfers to a memory address which

is

not incremented after

each transfer

(

1 1

1 1

Key: BW16

10M = 110

FAM

0

16-bit transfers to an

transfer

1

16-bit transfers to an

each transfer

= Bus Width 16-bit in the

or Memory Mapped bit in the

= Fixed Address

Mode

bit in the

DMODE

DMODE

110

110

register

DMODE

register

address which

address which

register

is

incremented after each

is

not

incremented after

NCR

53C700/53C700-66

Data

Manual

2-7

Page 22

Chapter

Functional

Two

Description

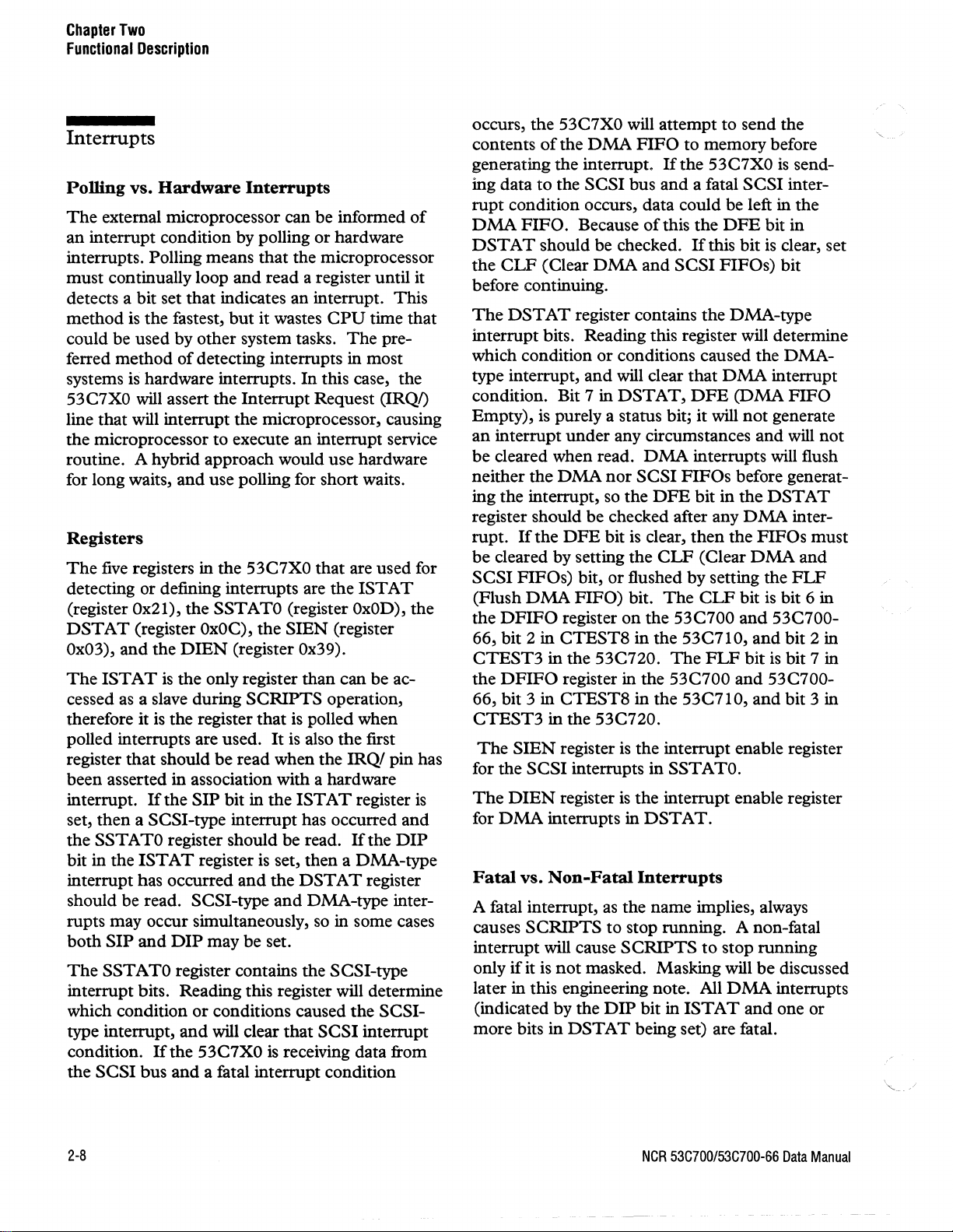

Interrupts

Polling

The

an interrupt condition by polling

interrupts. Polling means that the microprocessor

must continually loop and read a register until it

detects a bit set that indicates an interrupt. This

method

could be used by other system tasks.

ferred method

systems

53C7XO

line that will interrupt the microprocessor, causing

the microprocessor to execute an interrupt service

routine. A hybrid approach would use hardware

for long waits, and use polling for short waits.

Registers

The

detecting or defining interrupts are the

(register

DSTAT

Ox03), and the

The

cessed

therefore it

polled interrupts are used.

register that should be read when the IRQ! pin has

been asserted in association with a hardware

interrupt.

set, then a SCSI-type interrupt has occurred and

the

bit in the 1ST

interrupt has occurred

should be read.

rupts may occur simultaneously,

both

The

interrupt bits. Reading this register will determine

which condition or conditions caused the

type interrupt,

condition.

the

vs.

Hardware

Interrupts

external microprocessor can be informed

or

hardware

is

the fastest,

of

is

hardware interrupts.

will

assert the Interrupt Request (IRQ!)

five

registers in the 53C7XO that are used for

but

it wastes

CPU

The

time that

pre-

detecting interrupts in most

In

this case, the

1ST A T

Ox21), the SSTATO (register

(register

1ST

AT

as

a slave during SCRIPTS operation,

If

OxOC),

DIEN

is

the only register than can be ac-

is

the register

the SIP bit in the

the

SIEN

(register

that

It

Ox39).

is

polled when

is

also the first

ISTAT

SSTATO register should be read.

AT

SIP

and

register

SCSI-type

DIP

may be set.

is

set, then a DMA-type

and

the

DST

and

DMA-type inter-

OxOD),

(register

register

If

the

A T register

so

in some cases

SSTATO register contains the SCSI-type

SCSI-

and

will clear that SCSI interrupt

If

the 53C7XO

is

receiving data from

SCSI bus and a fatal interrupt condition

of

the

is

DIP

occurs, the 53C7XO will attempt to send the

of

the

contents

DMA

generating the interrupt.

ing data to the

rupt

condition occurs, data could be left in the

DMA

DSTA

the

FIFO.

T should be checked.

CLF

SCSI bus and a fatal SCSI inter-

Because

(Clear

DMA

FIFO

to memory before

If

the 53C7XO

of

this the

If

this bit

DFE

is

bit in

is

and SCSI FIFOs) bit

send-

clear, set

before continuing.

The

DSTAT

register contains the DMA-type

interrupt bits. Reading this register will determine

or

which condition

type interrupt,

condition. Bit 7 in

Empty), is purely a status bit; it

an interrupt under any circumstances

be cleared when read.

neither the

DMA

ing the interrupt, so the

register should be checked after any

If

the

rupt.

DFE

be cleared by setting the

SCSI

FIFOs) bit, or flushed

(Flush

the

66, bit 2 in

CTEST3

the

66, bit 3 in

CTEST3

The

for the

The

for

Fatal

DMA

DFIFO

register

CTEST8

in the 53C720.

DFIFO

register in the 53C700 and 53C700-

CTEST8

in the 53C720.

SIEN

register

SCSI interrupts in SSTATO.

DIEN

DMA

register

interrupts in

vs.

Non-Fatal

A fatal interrupt,

causes

interrupt

only

SCRIPTS to stop running. A non-fatal

will

if

it

is

not

later in this engineering note. All

(indicated by the

more bits in

DSTAT

conditions caused the DMA-

and

will

DSTAT,

DMA

nor

SCSI

bit

is

FIFO) bit.

on

the 53C700

clear that

DFE

clear,

CLF

The

DMA

DFE

will

interrupts

FIFOs

bit in the

then

the FIFOs must

(Clear

by

setting the

CLF

interrupt

(DMA

not

and

FIFO

generate

will

not

will

flush

before generat-

DST

AT

DMA

DMA

inter-

and

FLF

bit

is

bit 6 in

and

53C700-

in the 53C710, and bit 2 in

The

FLF

bit

is

bit 7 in

in the 53C71 0, and bit 3 in

is

the interrupt enable register

is

the interrupt enable register

DSTAT.

Interrupts

as

the name implies, always

cause

SCRIPTS

to

stop running

masked. Masking will be discussed

DIP

bit in

DMA

ISTA T and

interrupts

one or

being set) are fatal.

2-8

NCR

53C700/53C700-66

Data

Manual

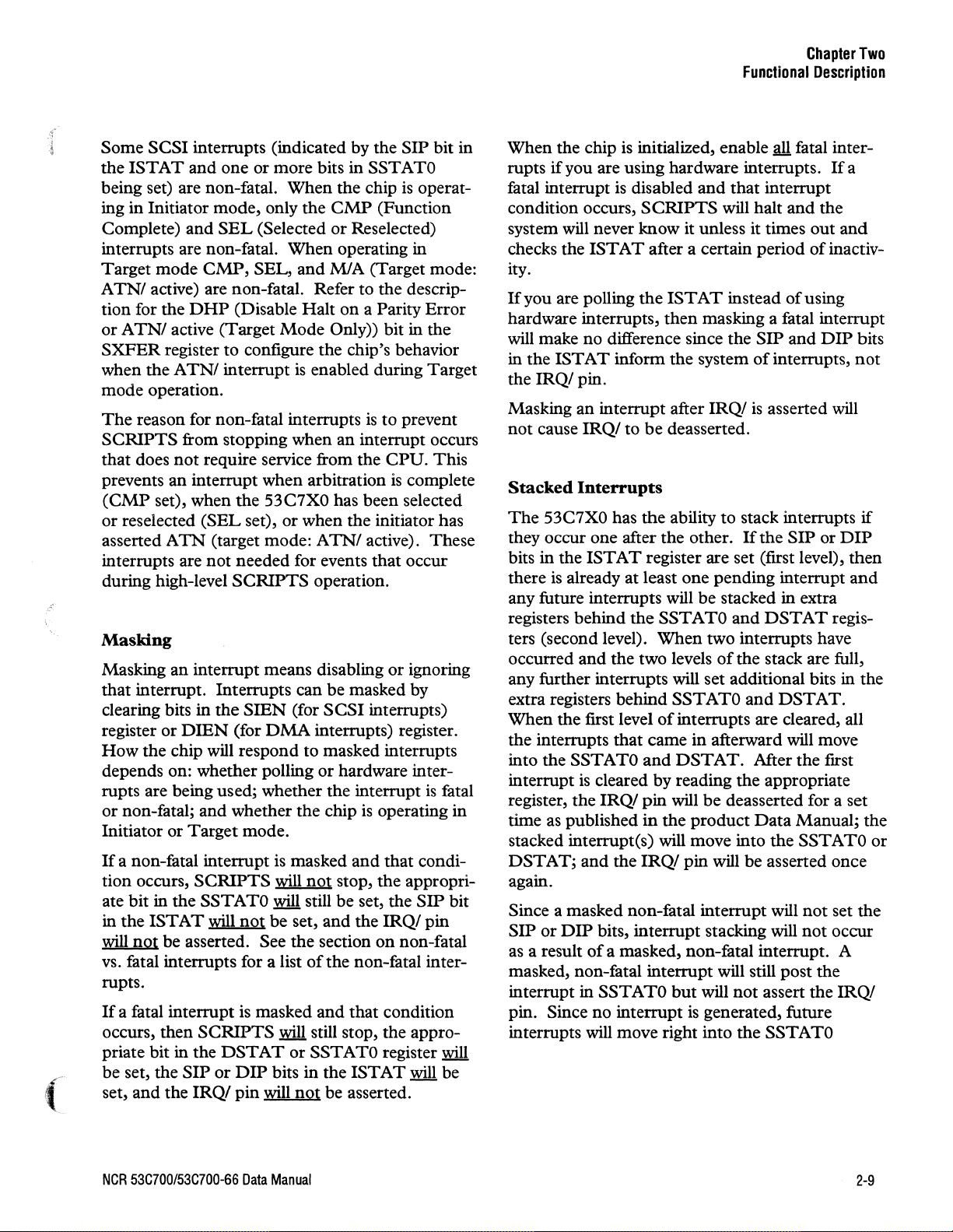

Page 23

.f

I

~

(

Some

the 1ST

being set) are non-fatal. When the chip

ing in Initiator mode, only the

SCSI

interrupts (indicated by the SIP bit in

AT

and one or more bits in SSTATO

Complete) and

SEL

(Selected

CMP

(Function

or

Reselected)

is

operat-

interrupts are non-fatal. When operating in

Target mode

CMP,

SEL, and

MIA

(Target mode:

ATN! active) are non-fatal. Refer to the descrip-

DHP

tion for the

or

ATN! active (Target

SXFER

register to configure the chip's behavior

(Disable Halt

Mode

when the ATN! interrupt

on

a Parity Error

Only)) bit in the

is

enabled during Target

mode operation.

The

reason for non-fatal interrupts

SCRIPTS

that does

prevents

(CMP

or

res elected (SEL set),

asserted A

from stopping when an interrupt occurs

not

require service from the

an

interrupt when arbitration

set), when the 53C7XO has been selected

or

TN

(target mode: A

when the initiator has

is

to prevent

CPU.

is

TN!

active). These

This

complete

interrupts are not needed for events that occur

during high-level

SCRIPTS

operation.

Masking

Masking an interrupt means disabling

or

ignoring

that interrupt. Interrupts can be masked by

the

clearing bits in

or

register

How

DIEN

the chip will respond to masked interrupts

SIEN

(for

depends on: whether polling

rupts are being used; whether the interrupt

or

non-fatal; and whether the chip

(for

DMA

SCSI

interrupts)

interrupts) register.

or

hardware inter-

is

fatal

is

operating in

Initiator or Target mode.

If

a non-fatal interrupt

tion occurs,

ate bit in the

in the 1ST

will

not

SCRIPTS

SST A TO

AT

will

be asserted. See the section

vs. fatal interrupts for a list

is

masked

will

not

stop, the appropri-

will still be set, the

not

be set,

and

of

the non-fatal inter-

and

that condi-

the IRQ!

on

non-fatal

SIP

pin

bit

rupts.

If

a fatal interrupt

occurs, then

priate bit in the

be set, the

and

set,

SIP

the IRQ!

is

masked and that condition

SCRIPTS

DST

AT

or

DIP

pin

will

l£ill.

still stop, the appro-

or

SST A TO

bits in the

not

ISTAT

be asserted.

register

will be

M11.

Chapter

Functional

When the chip

if

rupts

you are using hardware interrupts.

fatal interrupt

condition occurs,

is

initialized, enable all fatal inter-

is

disabled

SCRIPTS

and

that interrupt

will halt and the

system will never know it unless it times out

checks the 1ST A T after a certain period

of

Two

Description

If

a

and

inactiv-

ity.

If

you are polling

the

ISTAT

instead

of

using

hardware interrupts, then masking a fatal interrupt

SIP

and

DIP

will make no difference since the

AT

in the 1ST

inform the system

of

interrupts,

bits

not

the IRQ! pin.

Masking an interrupt after IRQ!

not

cause IRQ! to be deasserted.

Stacked

The

Interrupts

53C7XO has the ability to stack interrupts

they occur one after the other.

bits in the 1ST

is

there

already at least one pending interrupt

any future interrupts will

registers behind

AT

register are set (first level), then

be

the

SSTATO

is

asserted

If

the

SIP

or

stacked in extra

and

DSTAT

will

if

DIP

and

registers (second level). When two interrupts have

occurred

the two levels

of

the stack are full,

and

any further interrupts will set additional bits in the

extra registers behind

When the first level

of

SSTATO

interrupts are cleared, all

and

DSTAT.

the interrupts that came in afterward will move

into the

interrupt

SSTATO

is

cleared by reading the appropriate

register, the IRQ!

as

time

published

stacked interrupt(s) will move into the

DSTAT;

and

and

DSTAT.

pin

will

in

the product

be

After the first

de asserted for a set

Data

Manual; the

SSTATO

the IRQ! pin will be asserted once

or

again.

not

not

set the

occur

Since a masked non-fatal interrupt will

or

DIP

SIP

as

a result

bits, interrupt stacking will

of

a masked, non-fatal interrupt. A

masked, non-fatal interrupt will still post the

interrupt in

pin. Since

SSTATO

no

interrupt

interrupts will move right into the

but

will

not

is

generated, future

assert the IRQ!

SST A TO

NCR

53C700/53C700-66

Data

Manual

2-9

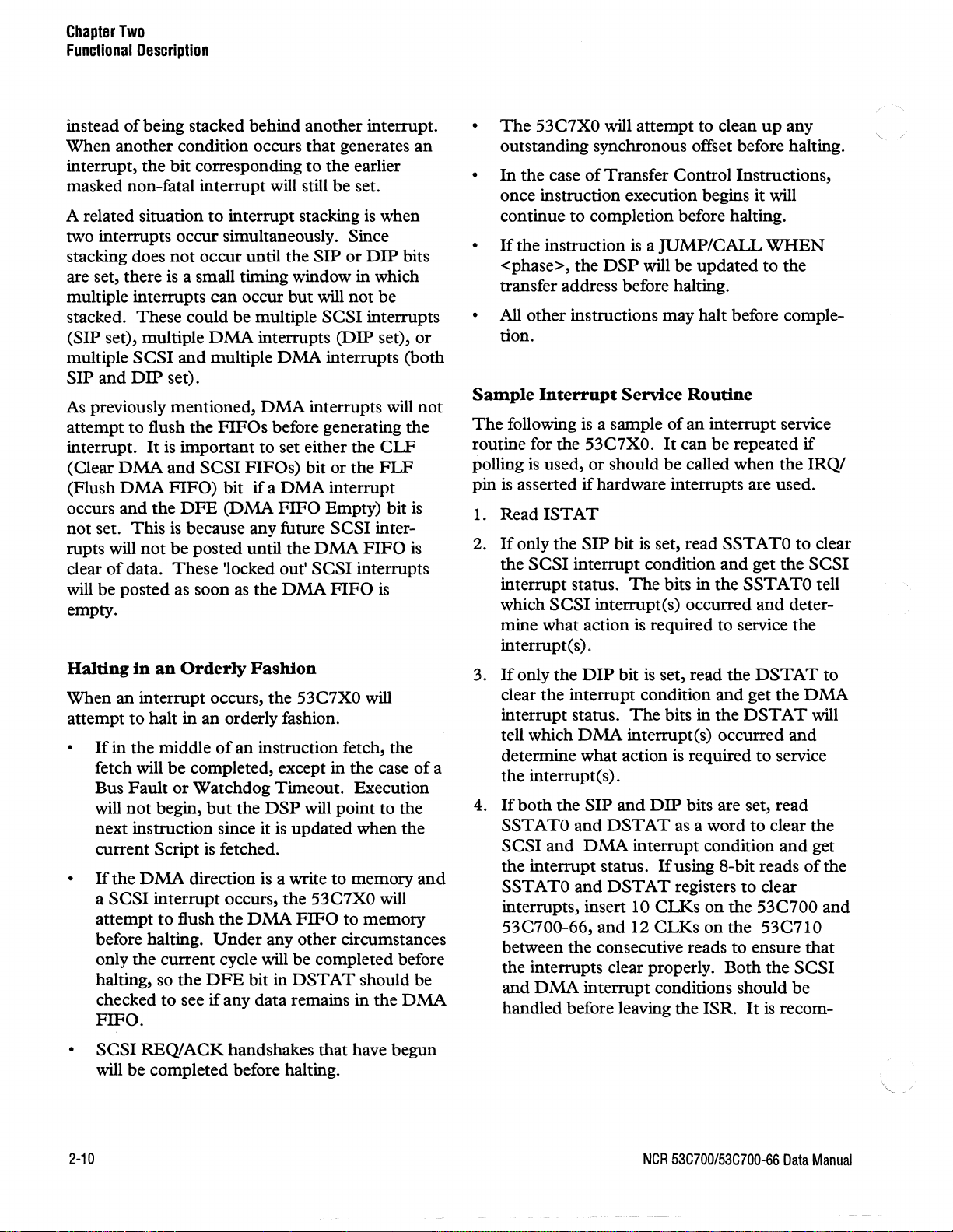

Page 24

Chapter

Functional

Two

Description

instead

of

being stacked behind another interrupt.

When another condition occurs that generates an

interrupt, the bit corresponding

masked non-fatal interrupt

A related situation to interrupt stacking

two interrupts occur simultaneously.

stacking does not occur until the SIP or

to

will

still be set.

the earlier

is

when

Since

DIP

bits

are set, there is a small timing window in which

multiple interrupts can occur

stacked. These could be multiple

(SIP set), multiple

multiple

SIP and

As

attempt

interrupt.

(Clear

(Flush

SCSI

DIP

previously mentioned,

to

flush the

It

DMA

DMA

occurs and the

not set. This

rupts will

clear

will

not

of

data. These 'locked out' SCSI interrupts

be posted as soon

DMA

and multiple

set).

FIFOs

is

important to set either the

and SCSI FIFOs) bit or the

FIFO) bit

DFE

(DMA

is

because any future SCSI inter-

be

posted until the

as

but

will

not

be

SCSI interrupts

interrupts (DIP set),

DMA

DMA

interrupts (both

interrupts will

before generating the

CLF

FLF

if

a

DMA

FIFO

the

DMA

DMA

interrupt

Empty) bit

FIFO

FIFO

is

or

not

is

is

empty.

Halting

When an interrupt occurs, the 53C7XO

attempt

•

•

in

an

to

halt in an orderly fashion.

If

in the middle

Orderly

Fashion

will

of

an instruction fetch, the

fetch will be completed, except in the case

Bus Fault

will

next instruction since it

current

If

the

not

DMA

or

Watchdog Timeout. Execution

begin,

Script

but

the

is

fetched.

direction

DSP

will point to the

is

updated when the

is

a write to memory

of

and

a SCSI interrupt occurs, the 53C7XO will

to

attempt

flush the

before halting.

DMA

Under

FIFO

to memory

any other circumstances

only the current cycle will be completed before

halting, so the

checked to see

DSTAT

if

any data remains in the

should be

DMA

DFE

bit in

FIFO.

•

The

53C7XO will attempt to clean

outstanding synchronous offset before halting.

•

In

the case

of

Transfer Control Instructions,

once instruction execution begins it will

continue to completion before halting.

•

If

the instruction

<phase>, the

is a JUMP/CAlL

DSP

will

be updated to the

transfer address before halting.

• All other instructions may halt before completion.

Sample

The

routine for the

polling

pin

1. Read

2.

Interrupt

following

is

used, or should be called when the

is

asserted

Service

is

a sample

53C7XO.

if

hardware interrupts are used.

Routine

of

an interrupt service

It

can be repeated

ISTAT

If

only the SIP bit

the

SCSI interrupt condition and get the SCSI

interrupt status.

which

SCSI

is

set, read SSTATO to clear

The

bits in the

SSTA

interrupt(s) occurred and determine what action is required to service the

interrupt(s) .

If

3.

only the

DIP

bit

is

set, read the

DSTAT

clear the interrupt condition and get the

interrupt status.

tell which

a

determine what action

the interrupt(s).

If

both

4.

SSTATO

DMA

the SIP

and

SCSI and

The

bits in the

interrupt(s) occurred

is

required to service

and

DIP

bits are set, read

DSTAT

DMA

as a word

interrupt condition

DSTAT

to

the interrupt status. Ifusing 8-bit reads

SSTATO and

interrupts, insert 10

DSTAT

CLKs on the 53C700 and

registers to clear

53C700-66, and 12 CLKs on the 53C710

between the consecutive reads to ensure that

the interrupts clear properly. Both the

and

DMA

handled before leaving the

interrupt conditions should be

ISR.

It

up

any

WHEN

if

mQl

TO

DMA

and

clear the

and

ofthe

SCSI

is

recom-

tell

to

will

get

• SCSI REQI

will

be completed before halting.

2-10

ACK

handshakes that have begun

NCR

53C700/53C700-66

Data

Manual

Page 25

Chapter

Functional

Two

Description

mended that the

before the

DMA

interrupt condition could influence how

the SCSI interrupt

DMA

SCSI

interrupt because a serious

interrupt be serviced

is

acted upon.

5. When using polled interrupts, go back to step

1 before leaving the interrupt service routine,

in case any stacked interrupts moved in when

the

first interrupt was cleared. When using

pin

hardware interrupts, the IRQ!

if

asserted again

there are any stacked inter-

will be

rupts. This should cause the system to reenter the interrupt service routine.

NCR

53C700/53C700-66

Data

Manual

2-11

Page 26

L

I

L

I

L

L

[

'~

Page 27

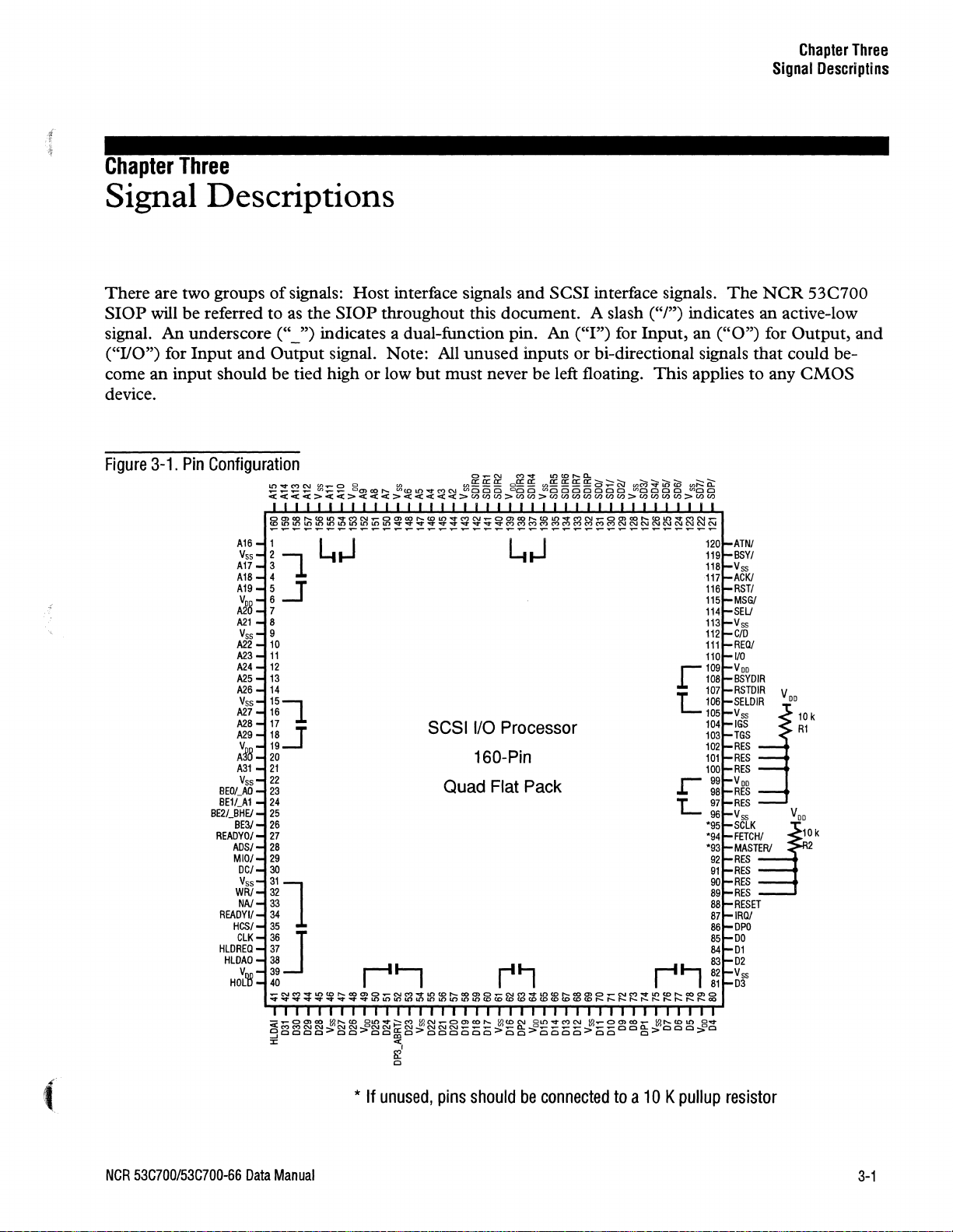

Chapter

Signal

Three

Descriptins

apler

Three

Signal Descriptions

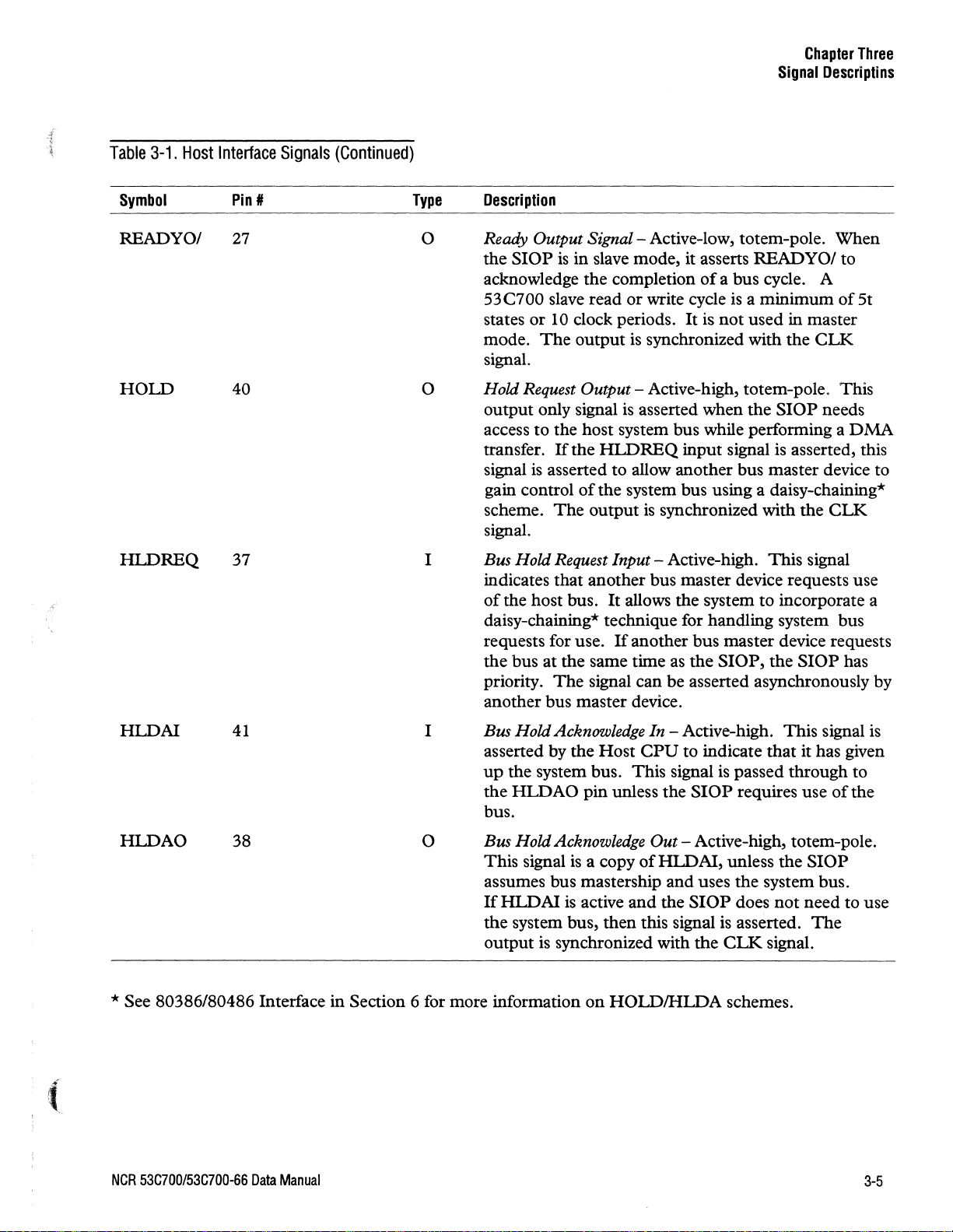

There

SlOP

signal.

("lIO") for

come

device.

Figure

are two groups

will be referred to as the

of

signals:

Host

SlOP

throughout this document. A slash

An underscore ("_") indicates a dual-function pin. An ("I") for Input,

Input

an

input should be tied high

3-1.

Pin

and

Output

Configuration

A16

1

Vss

A17

~J.

A18

A19

iJ

:~8

7

A21

8

9

Vss

A22

10

A23

11

A24

12

A25

13

A26

14

Vss

15!

A27

16

A28

17

J

18

A29

19

:~8

20

A31

21

22

Vss

BEOLAD

BE1LA1

BE2LBHEI

READYOI

READYI/

HLDREQ

23

24

25

26

BE3/

27

28

ADSI

MIOI

29

DCI

30

Vss

WR!

32

NAt

33

34

"1

HCSI

35

CLK

36J

37

HLDAO

38

V

39

HOL'IS

40

;~~~~~~~~g~~~~~~~~m~~~~~~m~mm~~~~~~re~~~~

signal. Note:

or

low

L..J

r"-'

interface signals

All

unused

but

must never be left floating.

SCSI

1/0

Processor

160-Pin

Quad Flat Pack

r'"

and

SCSI

inputs

or

~.J

interface signals.

("I")

The

indicates an active-low

an

("0")

bi-directional signals

This

applies

ATNI

BSYI

Vss

ACK/

RSTI

Msal

SEU

Vss

C/O

REat

I/O

Voo

BSYOIR

RSTDIR

SELDIR

Vss

las

Tas

RES

RES

RES

Voo

RES

RES

Vss

FETCH!

S~K~

MASTER!

RES

RES

RES

RES

RESET

IRat

OPO

DO

D1

,,--,

02

Vss

03

NCR

53C700

for Output,

that

could be-

to

any

CMOS

Voo

10k

R1

Voo

10

and

k

(

NCR

53C700/53C700-66

Data

Manual

* If

unused,

pins

should

be

connected

to

a 10K

pullup

resistor

3-1

Page 28

Chapter

Signal

Descriptions

Three

3·2

NCR

53C700/53C700·66

Data

Manual

Page 29

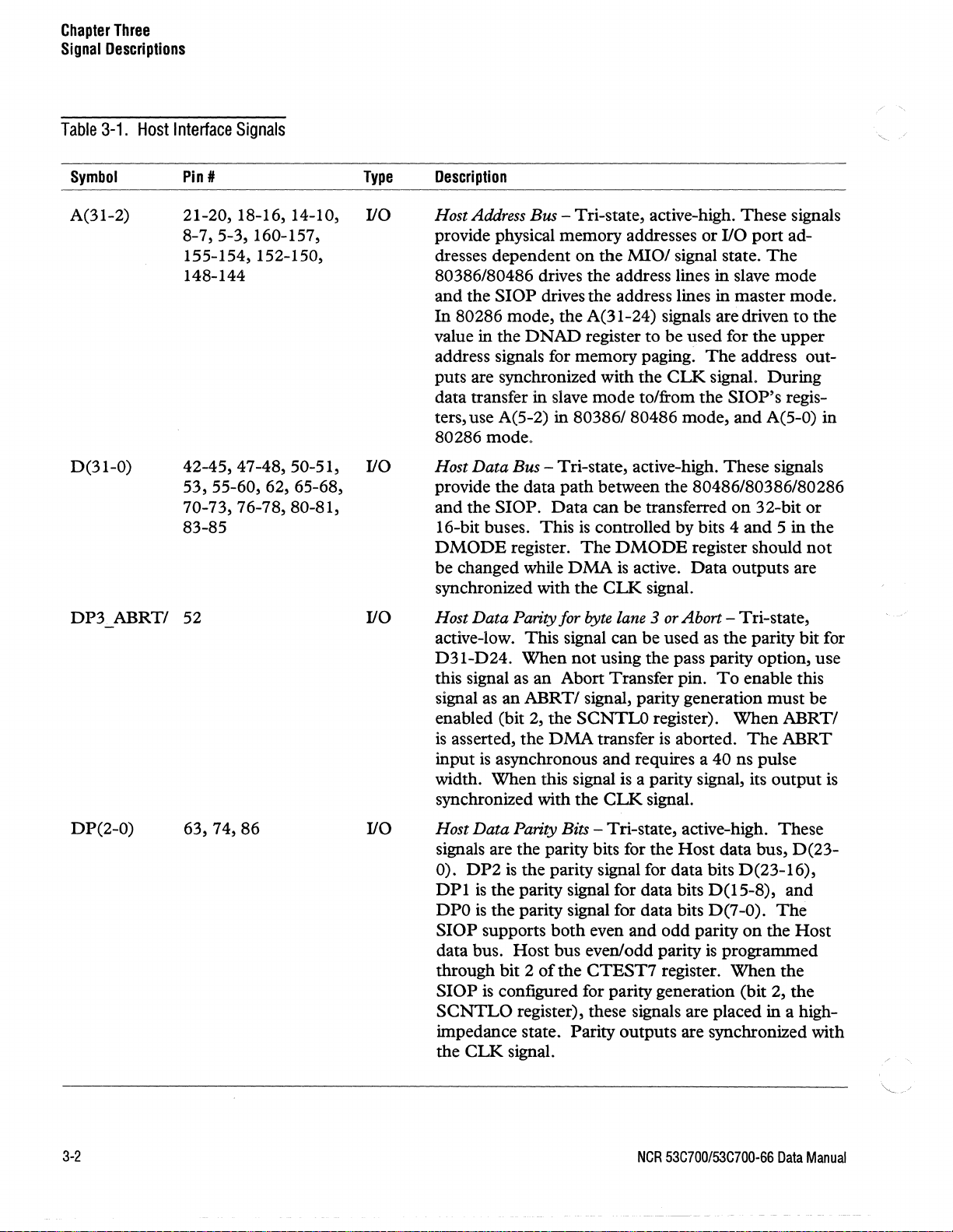

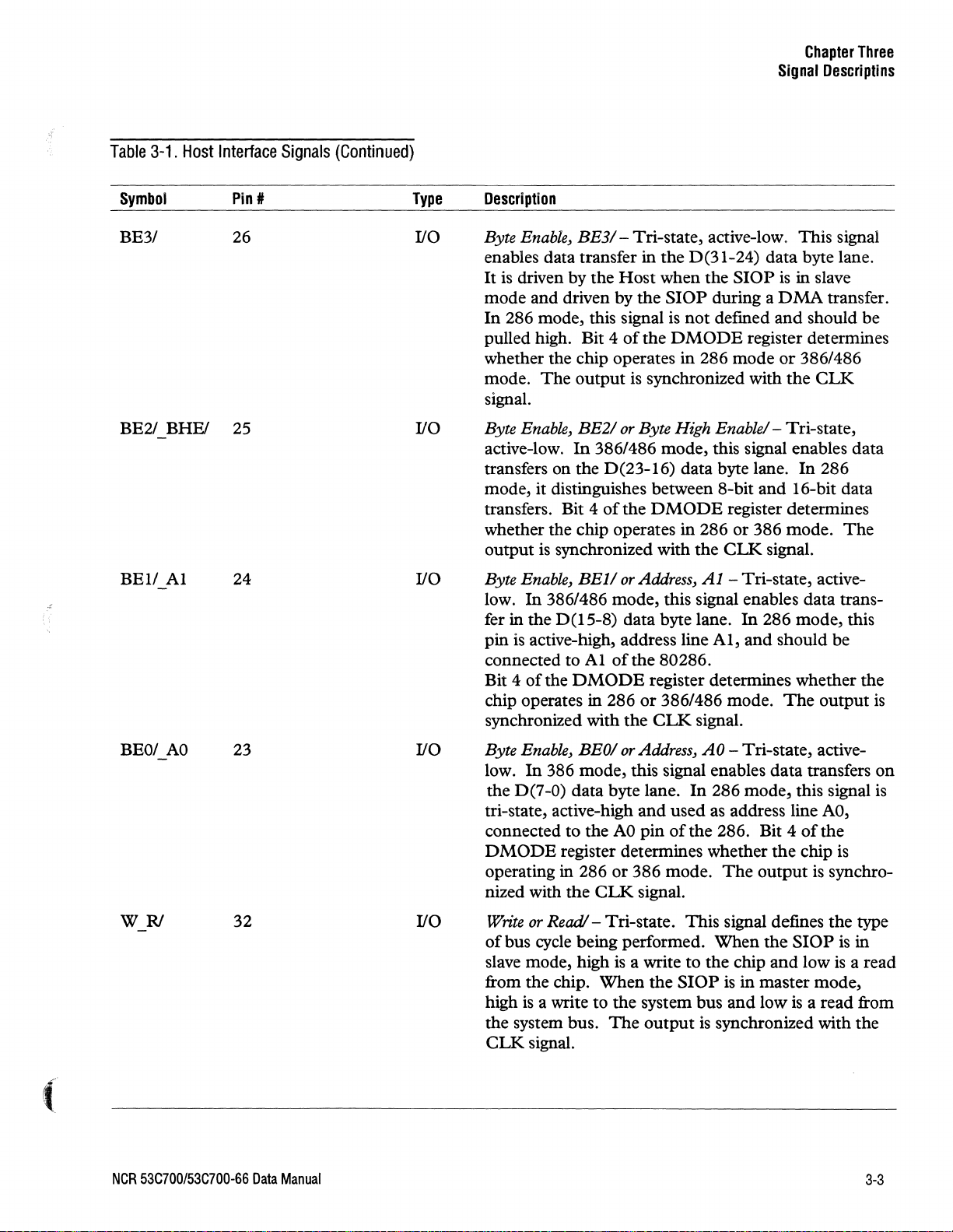

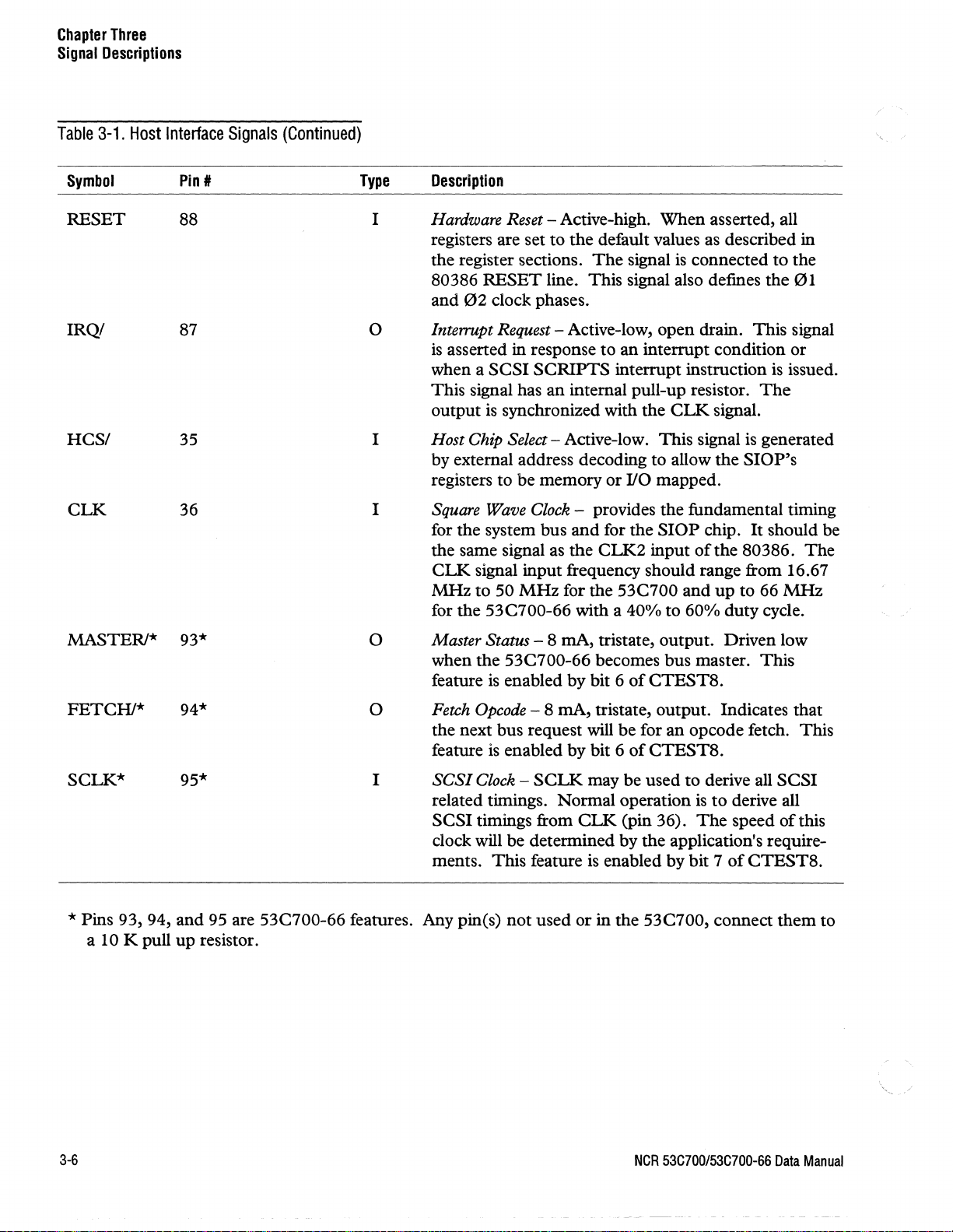

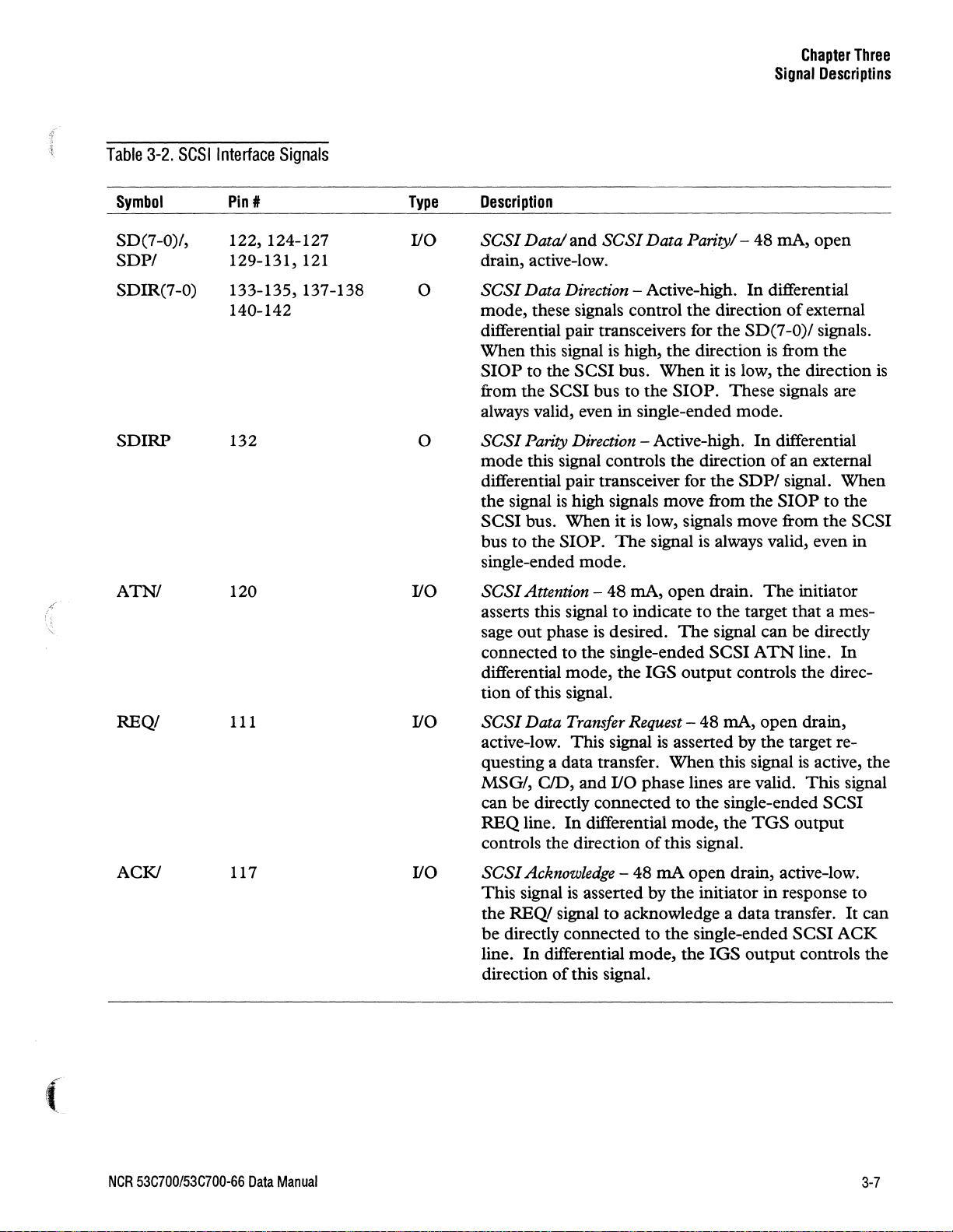

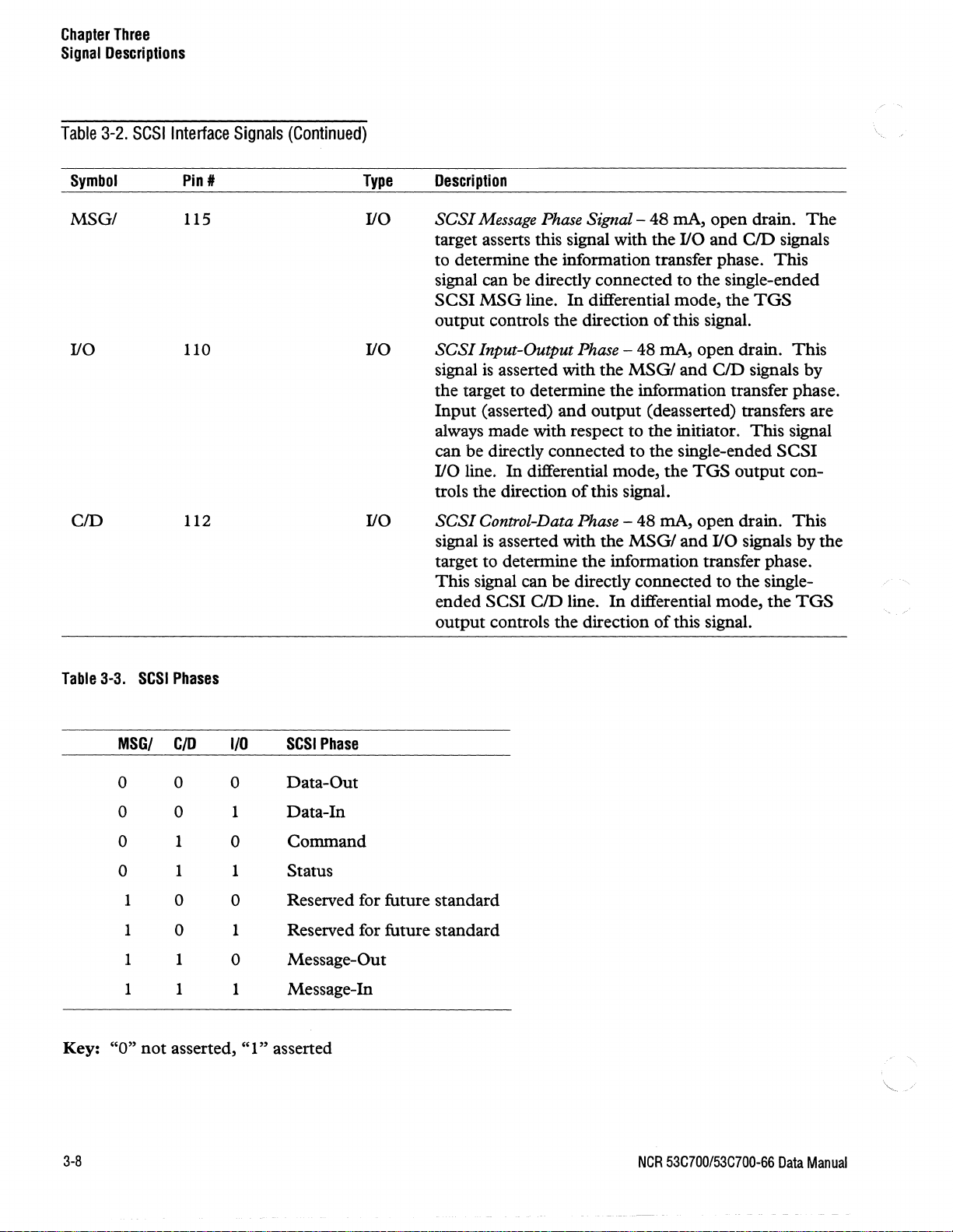

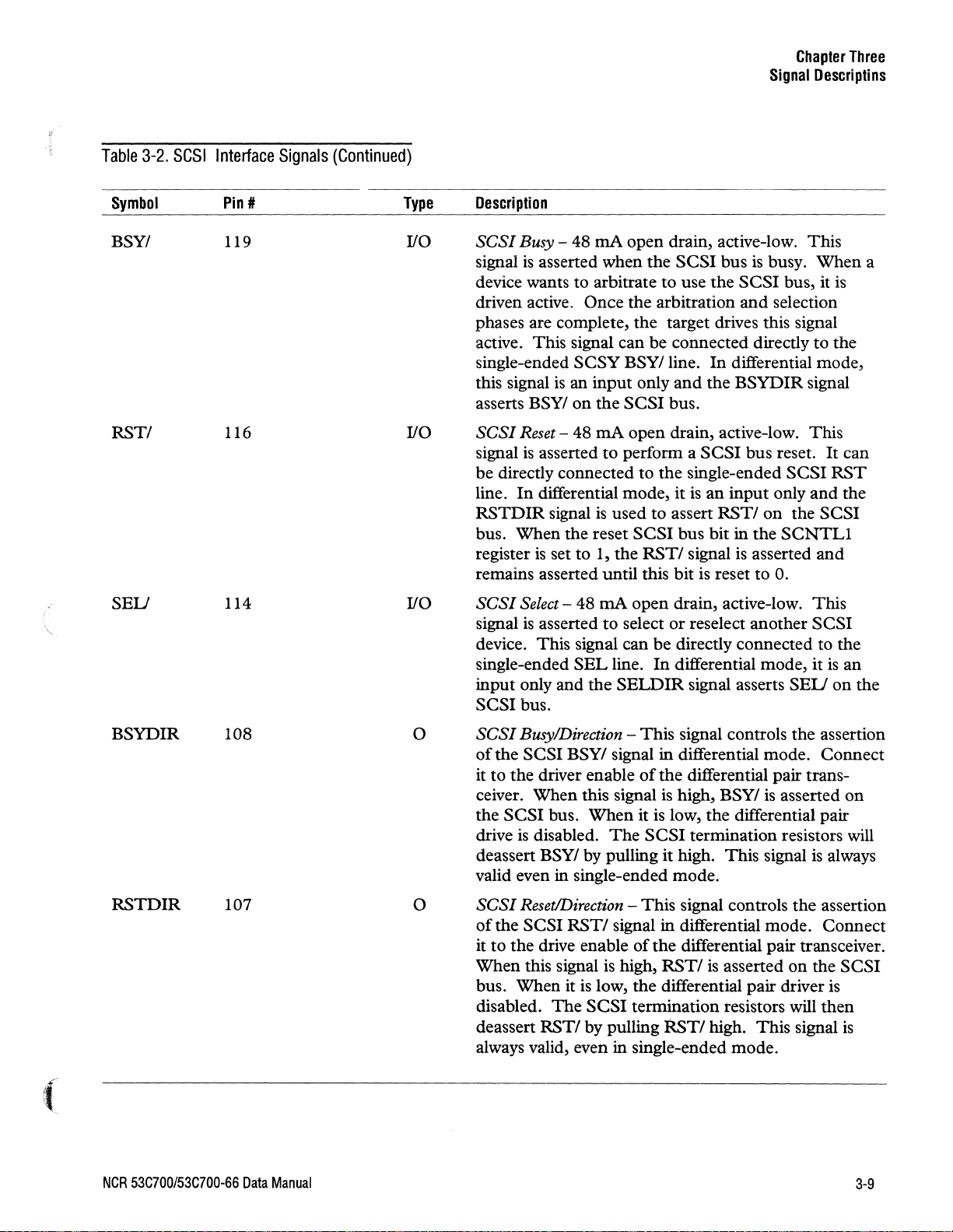

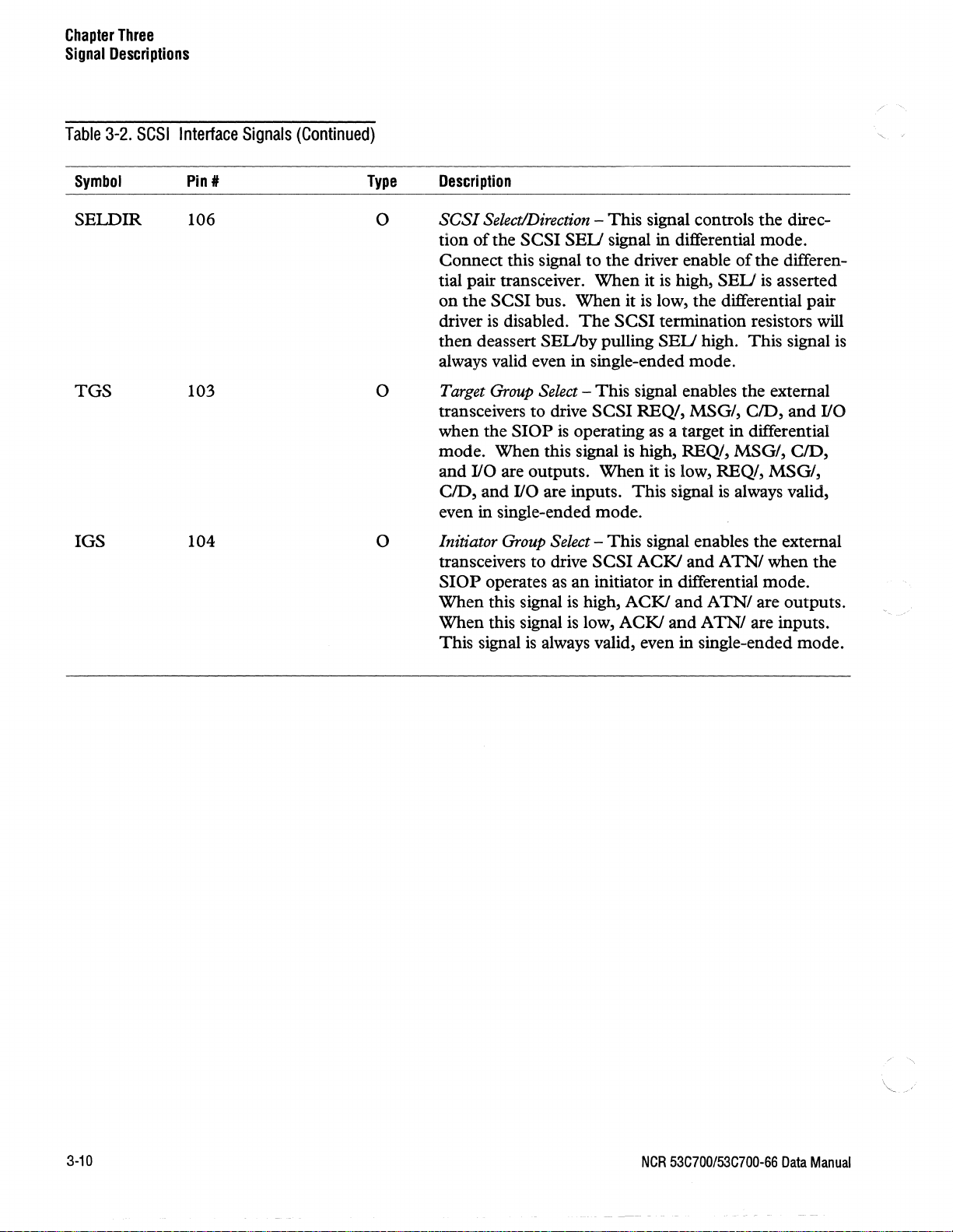

Table

Symbol

3-1.

Host

Interface

Pin

II

Signals

(Continued)

Type

Description

Chapter

Signal

Three

Descriptins

BE31

26

I/O

Byte Enable,

BE3/

- Tri-state, active-low. This signal

enables data transfer in the D(31-24) data byte lane.

It

is

driven by the

mode and driven by the

In

286 mode, this signal

pulled high. Bit 4

whether the chip operates in 286 mode

mode.

The

Host

output

when the

SlOP

is

not

of

the

DMODE

is

synchronized with the eLK

SlOP

is

in slave

during a

defmed

DMA

and

register determines

or

386/486

transfer.

should be

signal.

BE21

BHEI 25 I/O

Byte Enable,

active-low.

BE2/

or Byte High Enable/ - Tri-state,

In

386/486 mode, this signal enables data

transfers on the D(23-16) data byte lane.

In

286

mode, it distinguishes between 8-bit and 16-bit data

of

the

transfers. Bit 4

DMODE

whether the chip operates in 286

output

BEll

Al

.

.f

24 I/O

Byte Enable,

low.

is

synchronized with

BEI/

or Address,

In

386/486 mode, this signal enables data trans-

fer in the D(15-8) data byte lane.

pin

is

active-high, address line

Al

of

connected to

Bit 4

of

the

DMODE

chip operates in 286

the 80286.

register determines whether the

or

386/486 mode.

register determines

or

386 mode.

the

eLK signal.

Al

- Tri-state, active-

In

286 mode, this

AI,

and

should be

The

The

output

is

synchronized with the eLK signal.

(

BEOI

AO

WRI

NCR

53C700/53C700-66

23 I/O

32 I/O

Data

Manual

Byte Enable, BEO/ or Address, AO - Tri-state, active-

In

low.

the

tri-state, active-high

connected to the

DMODE

operating in 286

nized with the

Write

of

slave mode, high

from the chip. When the

high

the system bus.

386 mode, this signal enables data transfers

D(7

-0) data byte lane.

and

AO

pin

register determines whether

or

386 mode.

In

286 mode, this signal

used as address line

of

the 286. Bit 4

the

The

output

eLK signal.

or

Read/-

bus cycle being performed. When the

is

a write to the system bus

Tri-state. This signal defines the type

is

a write to the chip

SlOP

The

output

is

synchronized with the

and

is

in master mode,

and

low

AO,

ofthe

chip

is

is

synchro-

SlOP

is

low

is

a read

is

a read from

eLK signal.

on

is

in

3-3

Page 30

Chapter

Signal

Descriptions

Three

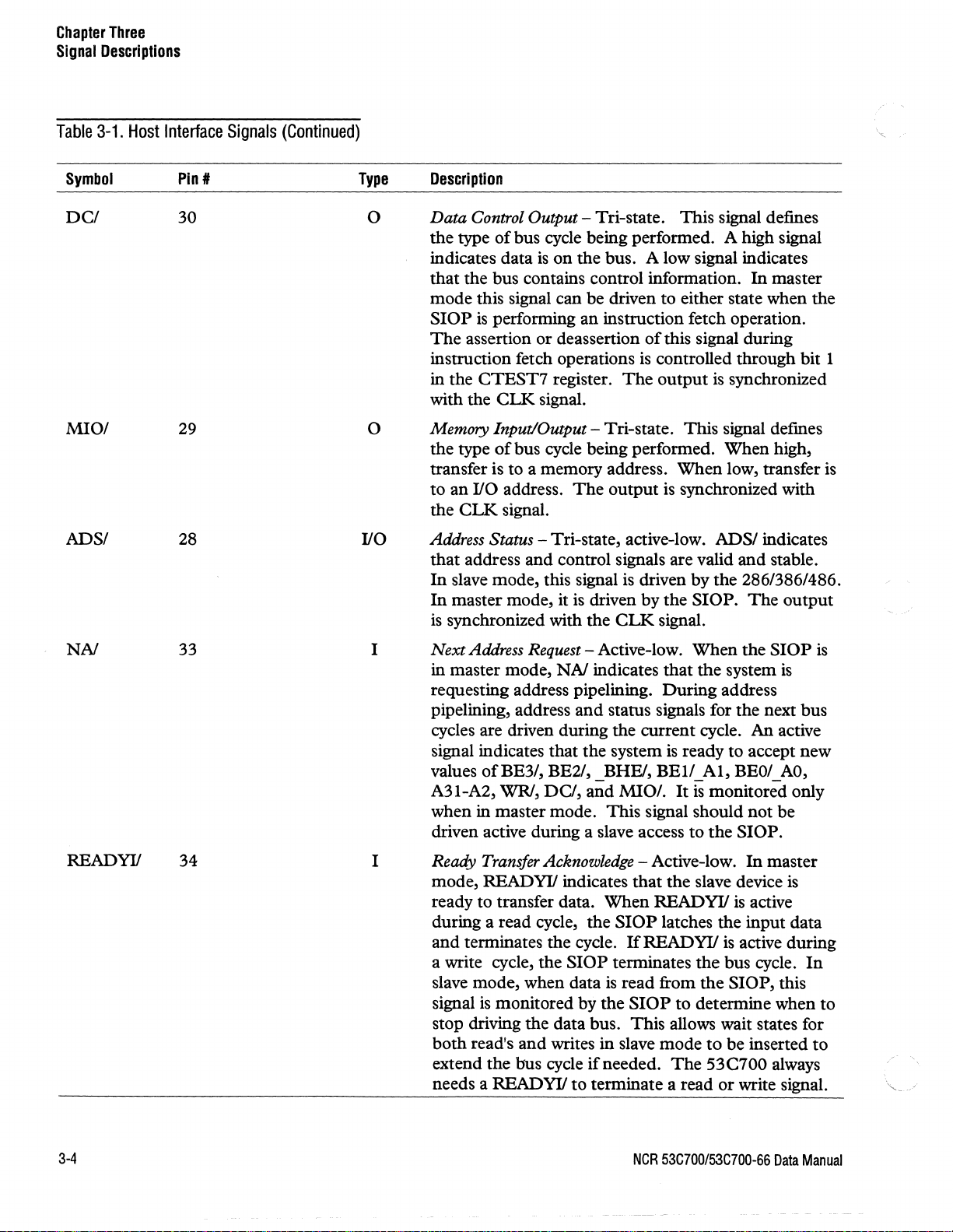

Table

Symbol

DCI

MIOI

ADSI

3-1.

Host

Interface

Pln#

Signals

(Continued)

30

29 a

28

Type

a

I/O

Description

Data

Control Output - Tri-state.

the

type

of

bus

cycle being performed. A high signal

data

is

indicates

that

the

mode

SlOP

The

this signal

is

assertion

bus contains control information.

performing

on

can

or

deassertion

the

bus. A low signal indicates

be

driven

an

instruction fetch operation.

This

signal defines

to

either state when

of

this signal during

In

master