APRIL 2005

CP3BT10 Reprogrammable Connectivity Processor

with Bluetooth® and USB Interfaces

1.0 General Description

The CP3BT10 connectivity processor combines high performance with the massive integration needed for embedded

Bluetooth applications. A powerful RISC core with on-chip

SRAM and Flash memory provides high computing bandwidth, communications peripherals provide high I/O bandwidth, and an external bus provides system expandability.

On-chip communications peripherals include: Bluetooth

Lower Link Controller, USB, ACCESS.bus, Microwire/SPI,

UART, and Advanced Audio Interface (AAI). Additional onchip peripherals include DMA controller, CVSD/PCM conversion module, Timing and Watchdog Unit, Versatile Timer

Unit, Multi-Function Timer, and Multi-Input Wakeup.

Bluetooth hand-held devices can be both smaller and lower

in cost for maximum consumer appeal. The low voltage and

advanced power-saving modes achieve new design points

in the trade-off between battery size and operating time for

handheld and portable applications.

In addition to providing the features needed for the next generation of embedded Bluetooth products, the CP3BT10 is

backed up by the software resources designers need for

rapid time-to-market, including an operating system, Bluetooth protocol stack implementation, reference designs, and

an integrated development environment. Combined with

National’s LMX5252 Bluetooth radio transceiver, the

CP3BT10 provides a complete Bluetooth system solution.

National Semiconductor offers a complete and industryproven application development environment for CP3BT10

applications, including the IAR Embedded Workbench,

iSYSTEM winIDEA and iC3000 Active Emulator, Bluetooth

Development Board, Bluetooth Protocol Stack, and Application Software.

CP3BT10 Reprogrammable Connectivity Processor with Bluetooth and USB Interfaces

FINAL

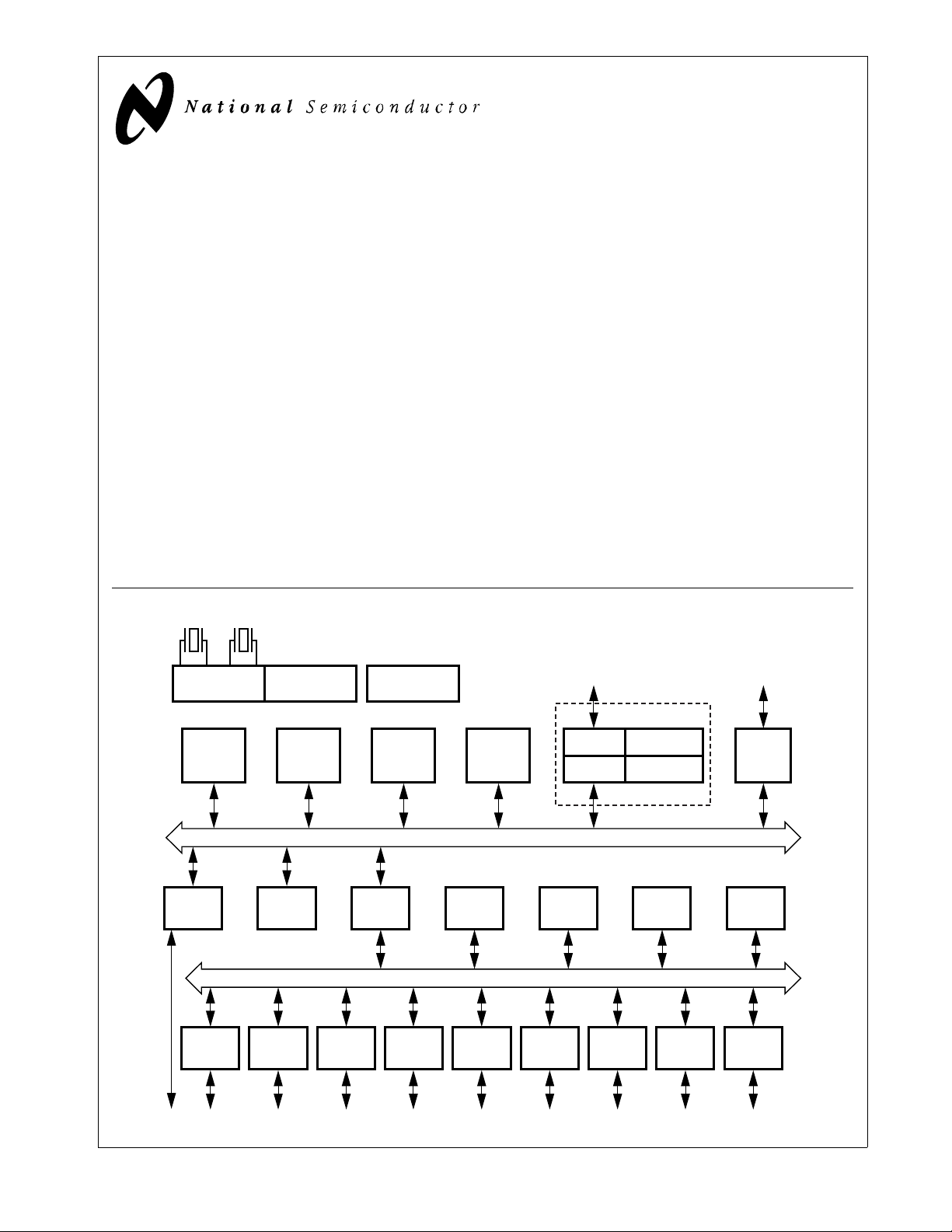

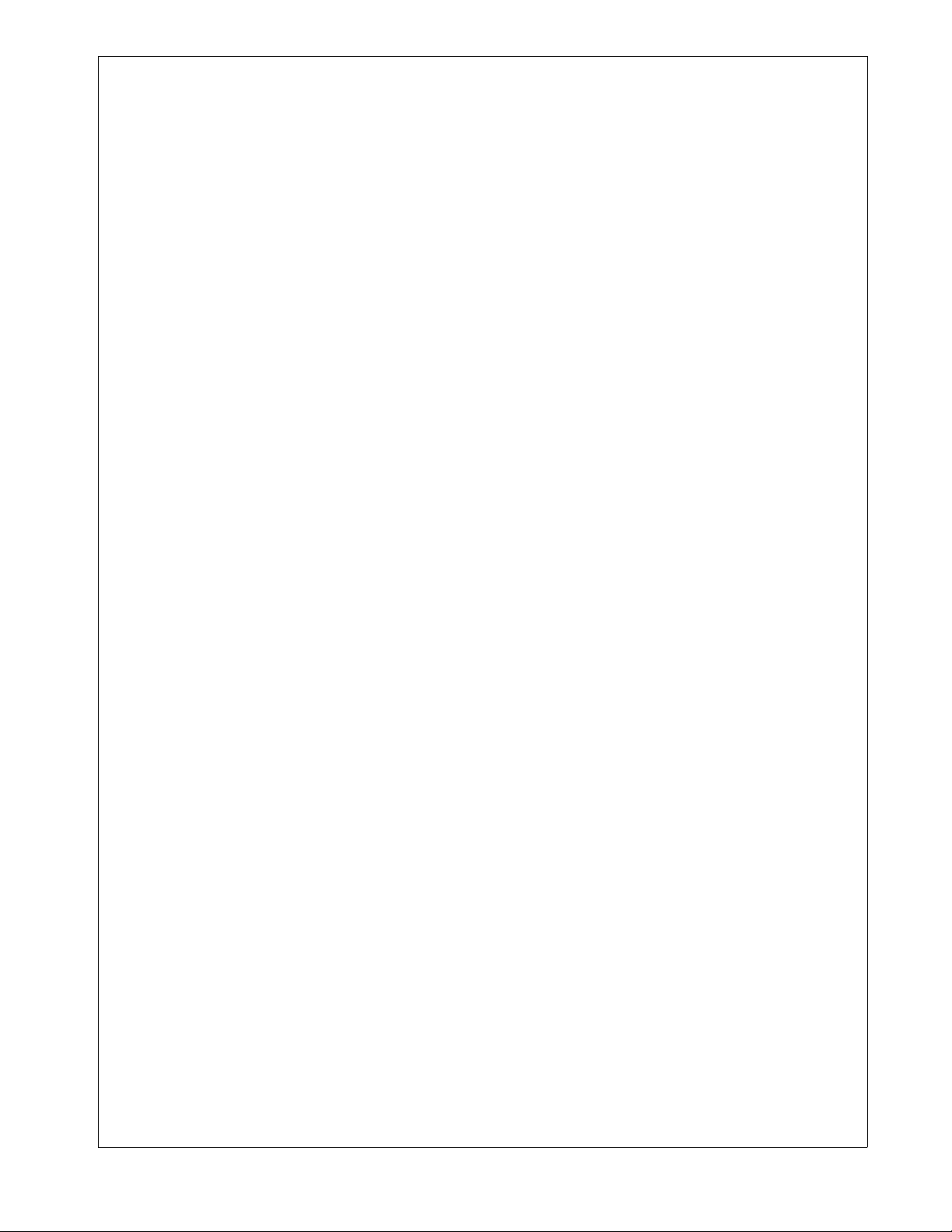

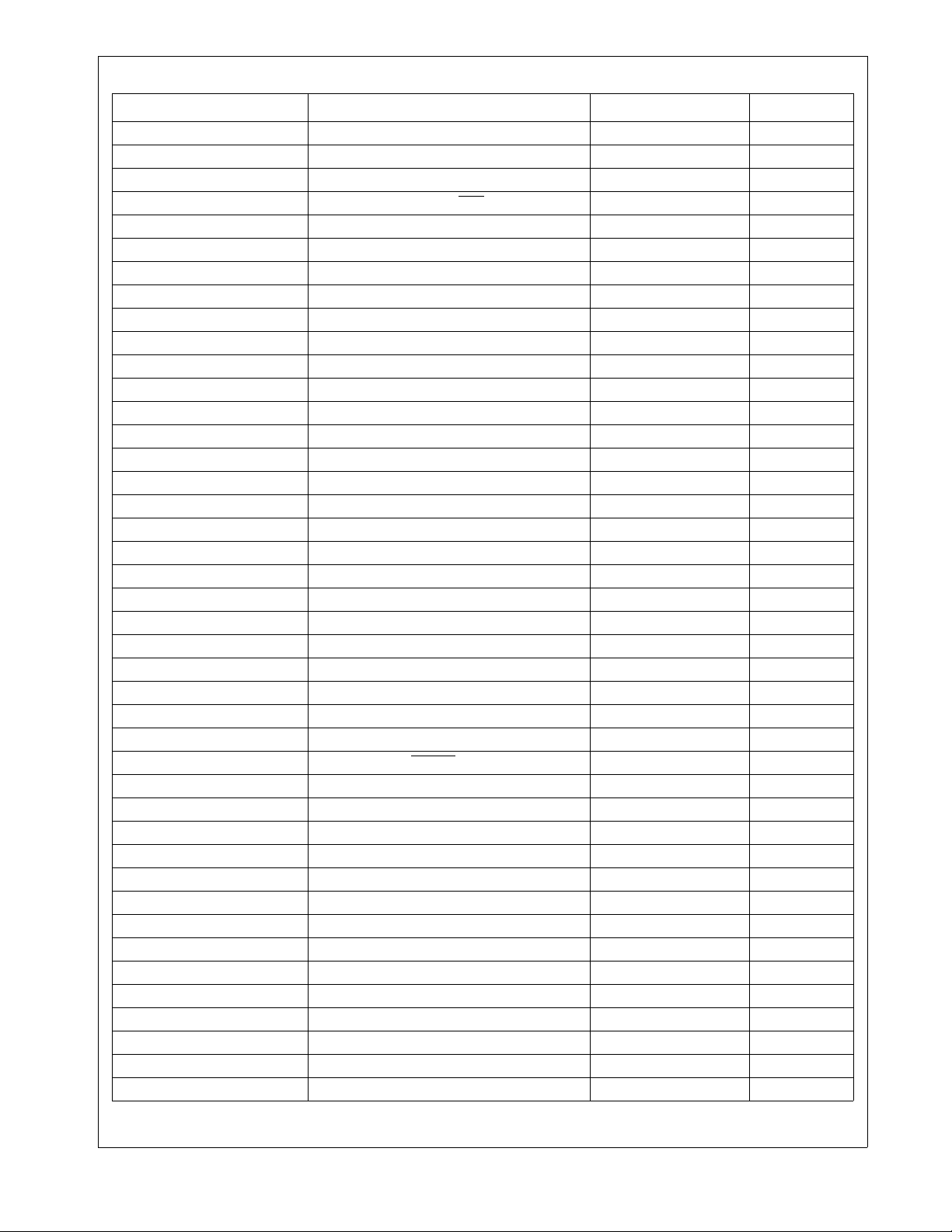

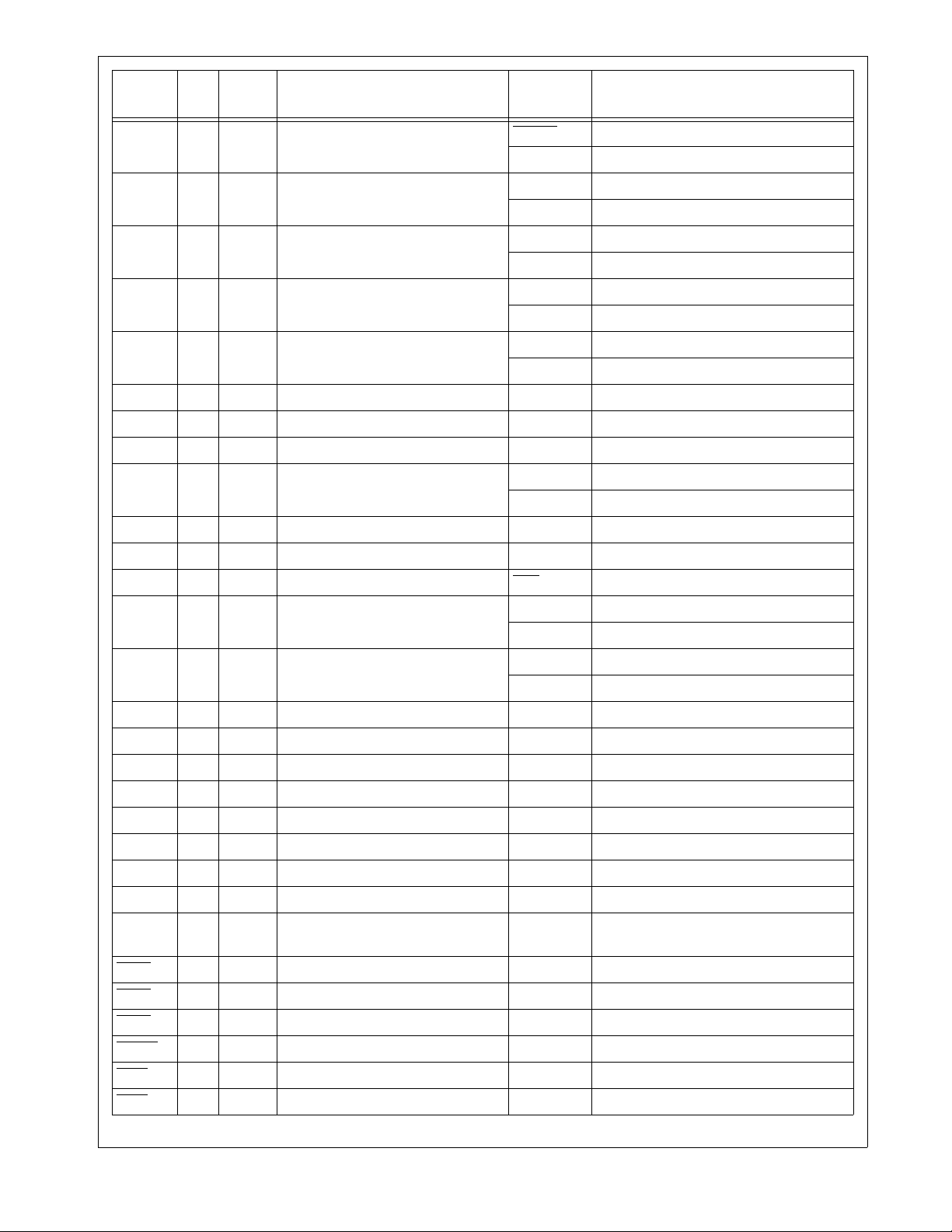

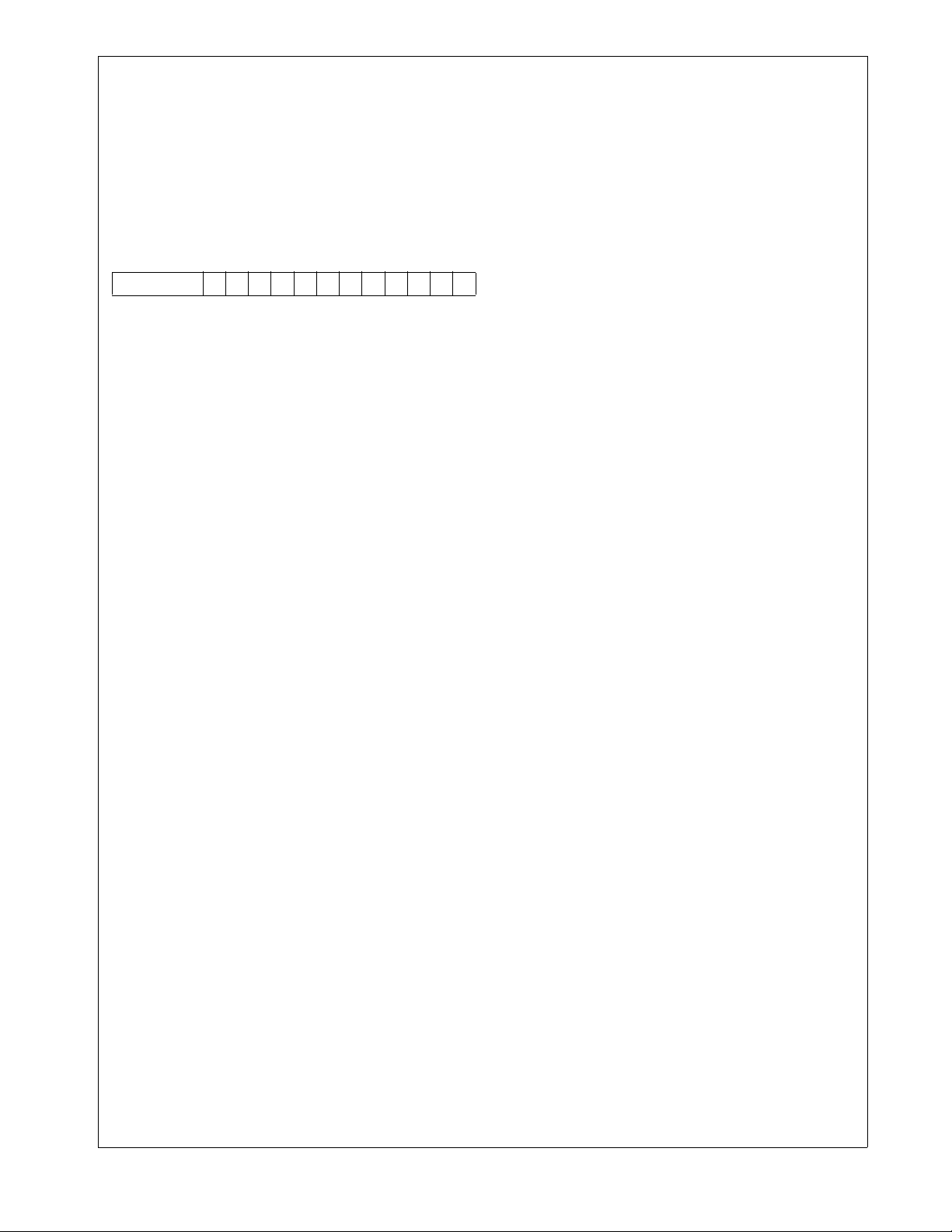

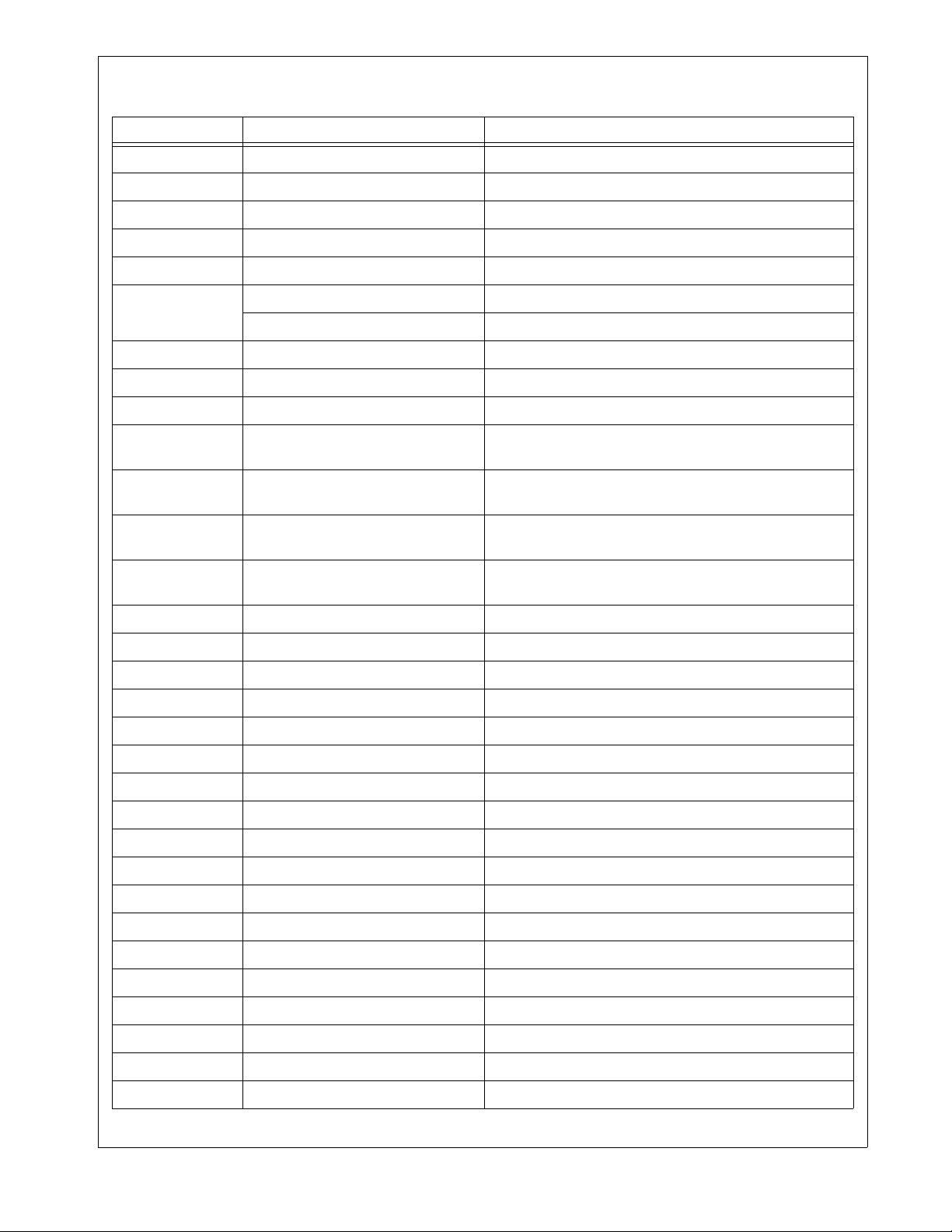

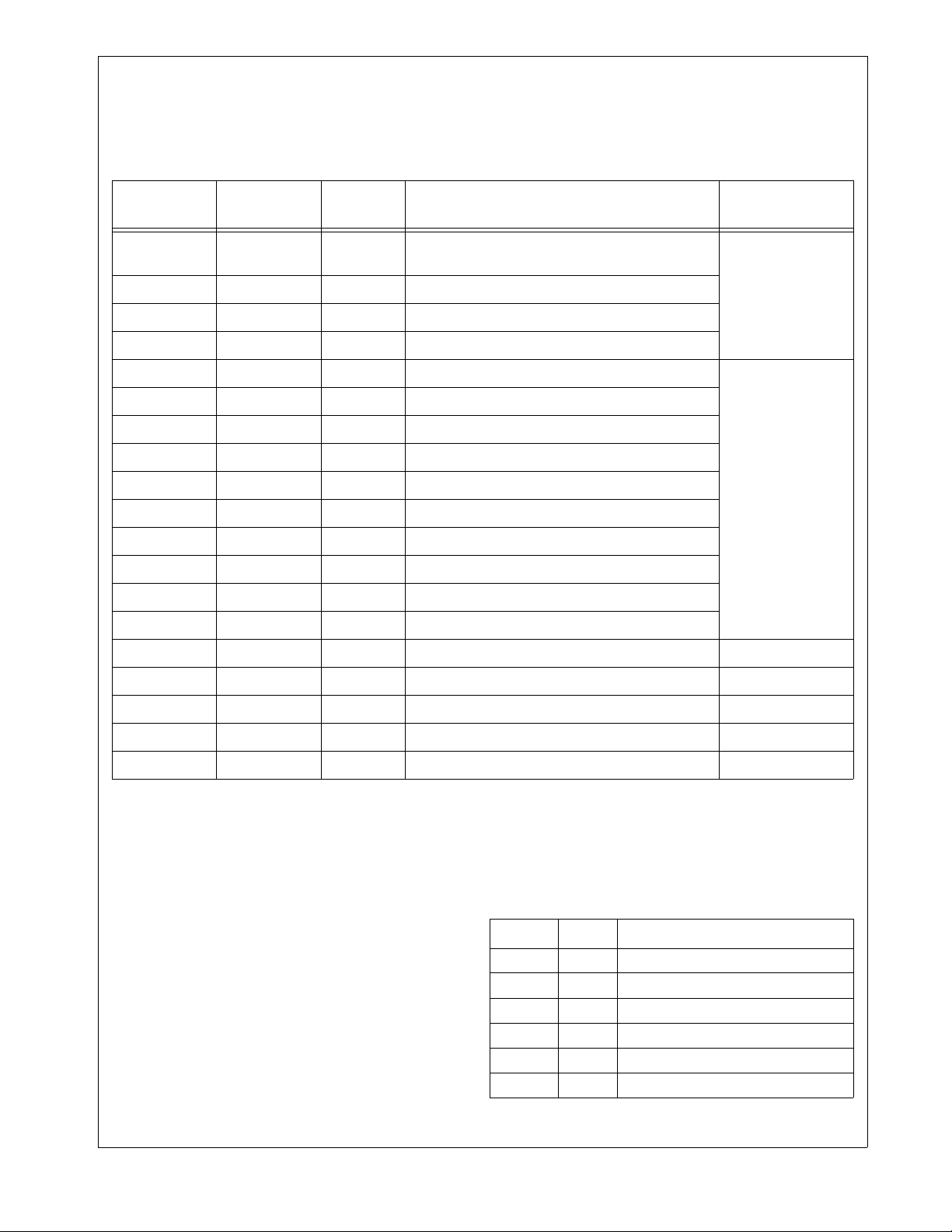

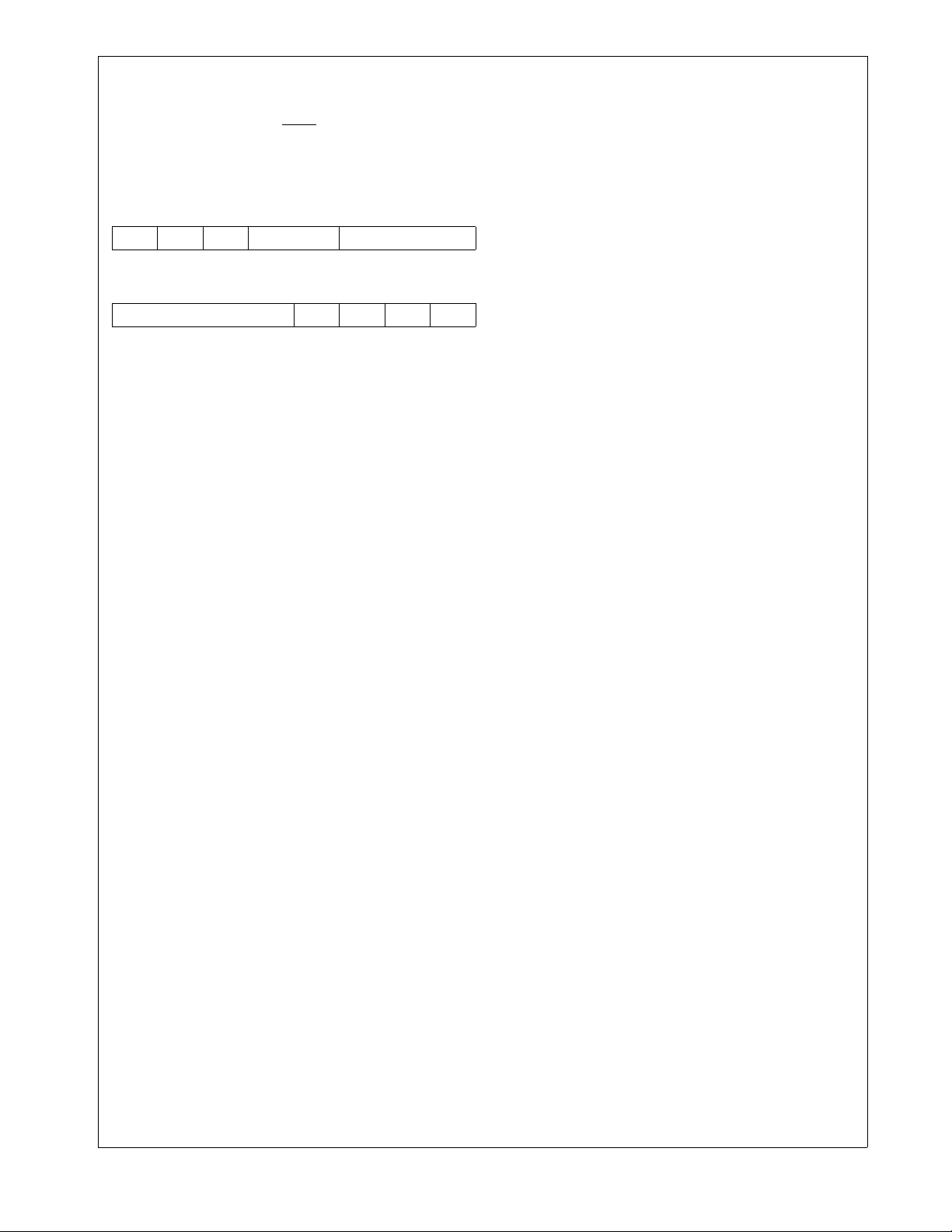

Block Diagram

12 MHz and 32 kHz

Oscillator

CR16C

CPU Core

Bus

Interface

Unit

Clock Generator

PLL and Clock

Generator

256K Bytes

Flash

Program

Memory

DMA

Controller

GPIOUSB

Audio

Interface

Power-on-Reset

8K Bytes

Flash

Peripheral

Bus

Controller

Microwire/

Data

SPI

10K Bytes

Static

RAM

CPU Core Bus

Interrupt

Control

Unit

Peripheral Bus

UART

CVSD/PCM

ACCESS

.bus

RF Interface

Protocol

Core

Versatile

Timer Unit

Bluetooth Lower

Link Controller

1K Byte

Sequencer RAM

4.5K Bytes

Data RAM

Powe r

Manage-

ment

Muti-Func-

tion Timer

Serial

Debug

Interface

Timing and

Watchdog

Unit

Multi-Input

Wake-Up

DS144

Bluetooth is a registered trademark of Bluetooth SIG, Inc. and is used under license by National Semiconductor.

TRI-STATE is a registered trademark of National Semiconductor Corporation.

©2005 National Semiconductor Corporation www.national.com

Table of Contents

1.0 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . 1

CP3BT10

2.0 CPU Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3.0 Device Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.1 CR16C CPU Core. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.2 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.3 Input/Output Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.4 Bus Interface Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.5 Interrupt Control Unit (ICU) . . . . . . . . . . . . . . . . . . . . . . . 4

3.6 Bluetooth LLC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.7 USB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.8 Multi-Input Wake-up . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.9 Triple Clock and Reset . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.10 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.11 Multi-Function Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.12 Versatile Timer Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.13 Timing and Watchdog Module . . . . . . . . . . . . . . . . . . . . 5

3.14 UART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.15 Microwire/SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.16 ACCESS.bus Interface . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.17 DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.18 Advanced Audio interface . . . . . . . . . . . . . . . . . . . . . . . . 6

3.19 CVSD/PCM Conversion Module. . . . . . . . . . . . . . . . . . . 6

3.20 Serial Debug Interface . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3.21 Development Support . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

4.0 Device Pinouts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

4.1 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.0 CPU Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.1 General-Purpose Registers . . . . . . . . . . . . . . . . . . . . . 16

5.2 Dedicated Address Registers . . . . . . . . . . . . . . . . . . . . 16

5.3 Processor Status Register (PSR) . . . . . . . . . . . . . . . . . 17

5.4 Configuration Register (CFG) . . . . . . . . . . . . . . . . . . . . 18

5.5 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

5.6 Stacks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

5.7 Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

6.0 Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

6.1 Operating Environment . . . . . . . . . . . . . . . . . . . . . . . . . 25

6.2 Bus Interface Unit (BIU) . . . . . . . . . . . . . . . . . . . . . . . . 26

6.3 Bus Cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

6.4 BIU Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . 26

6.5 Wait and Hold States . . . . . . . . . . . . . . . . . . . . . . . . . . 29

7.0 System Configuration Registers . . . . . . . . . . . . . . . 30

7.1 Module Configuration Register (MCFG) . . . . . . . . . . . . 30

7.2 Module Status Register (MSTAT) . . . . . . . . . . . . . . . . . 30

8.0 Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

8.1 Flash Memory Protection . . . . . . . . . . . . . . . . . . . . . . . 31

8.2 Flash Memory Organization . . . . . . . . . . . . . . . . . . . . . 31

8.3 Flash Memory Operations. . . . . . . . . . . . . . . . . . . . . . . 32

8.4 Information Block Words . . . . . . . . . . . . . . . . . . . . . . . . 33

8.5 Flash Memory Interface Registers . . . . . . . . . . . . . . . . 35

9.0 DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

9.1 Channel Assignment. . . . . . . . . . . . . . . . . . . . . . . . . . . 41

9.2 Transfer Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

9.3 Operation Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

9.4 Software DMA Request . . . . . . . . . . . . . . . . . . . . . . . . 43

9.5 Debug Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

9.6 DMA Controller Register Set. . . . . . . . . . . . . . . . . . . . . 43

10.0 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

10.1 Non-Maskable Interrupts. . . . . . . . . . . . . . . . . . . . . . . . 47

10.2 Maskable Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

10.3 Interrupt Controller Registers . . . . . . . . . . . . . . . . . . . . 47

10.4 Maskable Interrupt Sources . . . . . . . . . . . . . . . . . . . . . 49

10.5 Nested Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

11.0 Triple Clock and Reset . . . . . . . . . . . . . . . . . . . . . . . 51

11.1 External Crystal Network . . . . . . . . . . . . . . . . . . . . . . . 52

11.2 Main Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

11.3 Slow Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.4 PLL Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.5 System Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.6 Auxiliary Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.7 Power-On Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.8 External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

11.9 Clock and Reset Registers . . . . . . . . . . . . . . . . . . . . . . 55

12.0 Power Management. . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.1 Active Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.2 Power Save Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.3 Idle Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.4 Halt Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

12.5 Hardware Clock Control . . . . . . . . . . . . . . . . . . . . . . . . 57

12.6 Power Management Registers . . . . . . . . . . . . . . . . . . . 58

12.7 Switching Between Power Modes. . . . . . . . . . . . . . . . . 59

13.0 Multi-Input Wake-Up . . . . . . . . . . . . . . . . . . . . . . . . . 61

13.1 Multi-Input Wake-Up Registers . . . . . . . . . . . . . . . . . . . 61

13.2 Programming Procedures . . . . . . . . . . . . . . . . . . . . . . . 63

14.0 Input/Output Ports. . . . . . . . . . . . . . . . . . . . . . . . . . . 64

14.1 Port Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

14.2 Open-Drain Operation. . . . . . . . . . . . . . . . . . . . . . . . . . 67

15.0 Bluetooth Controller . . . . . . . . . . . . . . . . . . . . . . . . . 68

15.1 RF Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

15.2 Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

15.3 LMX5251 Power-Up Sequence . . . . . . . . . . . . . . . . . . . 72

15.4 LMX5252 Power-Up Sequence . . . . . . . . . . . . . . . . . . . 72

15.5 Bluetooth Sleep Mode . . . . . . . . . . . . . . . . . . . . . . . . . . 73

15.6 Bluetooth Global Registers . . . . . . . . . . . . . . . . . . . . . . 73

15.7 Bluetooth Sequencer RAM . . . . . . . . . . . . . . . . . . . . . . 73

15.8 Bluetooth Shared Data RAM . . . . . . . . . . . . . . . . . . . . . 74

16.0 USB Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

16.1 Functional States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

16.2 Endpoint Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

16.3 USB Controller Registers. . . . . . . . . . . . . . . . . . . . . . . . 78

16.4 Transceiver Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

17.0 Advanced Audio Interface. . . . . . . . . . . . . . . . . . . . . 94

17.1 Audio Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . 94

17.2 Audio Interface Modes . . . . . . . . . . . . . . . . . . . . . . . . . . 94

17.3 Bit Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

17.4 Frame Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . 97

17.5 Audio Interface Operation . . . . . . . . . . . . . . . . . . . . . . . 97

17.6 Communication Options. . . . . . . . . . . . . . . . . . . . . . . . . 99

17.7 Audio Interface Registers. . . . . . . . . . . . . . . . . . . . . . . 102

17.8 Usage Hints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

18.0 CVSD/PCM Conversion Module . . . . . . . . . . . . . . . 109

18.1 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

18.2 PCM Conversions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

18.3 CVSD Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

18.4 PCM to CVSD Conversion . . . . . . . . . . . . . . . . . . . . . . 110

18.5 CVSD to PCM Conversion. . . . . . . . . . . . . . . . . . . . . . 110

18.6 Interrupt Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . 110

18.7 DMA Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

18.8 Freeze . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

18.9 CVSD/PCM Converter Registers . . . . . . . . . . . . . . . . . 111

19.0 UART Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

19.1 Functional Overview . . . . . . . . . . . . . . . . . . . . . . . . . . 114

19.2 UART Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

19.3 UART Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

19.4 Baud Rate Calculations . . . . . . . . . . . . . . . . . . . . . . . . 122

20.0 Microwire/SPI Interface . . . . . . . . . . . . . . . . . . . . . . 124

20.1 Microwire Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

20.2 Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

20.3 Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

20.4 Interrupt Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . 127

20.5 Microwire Interface Registers . . . . . . . . . . . . . . . . . . . 127

21.0 ACCESS.bus Interface. . . . . . . . . . . . . . . . . . . . . . . 130

21.1 ACB Protocol Overview . . . . . . . . . . . . . . . . . . . . . . . . 130

21.2 ACB Functional Description. . . . . . . . . . . . . . . . . . . . . 132

21.3 ACCESS.bus Interface Registers . . . . . . . . . . . . . . . . 134

21.4 Usage Hints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

22.0 Timing and Watchdog Module . . . . . . . . . . . . . . . . 139

22.1 TWM Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

22.2 Timer T0 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

22.3 Watchdog Operation . . . . . . . . . . . . . . . . . . . . . . . . . . 140

22.4 TWM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

22.5 Watchdog Programming Procedure. . . . . . . . . . . . . . . 142

23.0 Multi-Function Timer . . . . . . . . . . . . . . . . . . . . . . . . 143

23.1 Timer Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

23.2 Timer Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . 144

23.3 Timer Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

23.4 Timer I/O Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

23.5 Timer Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

24.0 Versatile Timer Unit (VTU). . . . . . . . . . . . . . . . . . . . 152

24.1 VTU Functional Description . . . . . . . . . . . . . . . . . . . . . 152

24.2 VTU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

25.0 Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

26.0 Register Bit Fields . . . . . . . . . . . . . . . . . . . . . . . . . . 171

27.0 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . 182

27.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . 182

27.2 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . 182

27.3 USB Transceiver Electrical Characteristics . . . . . . . . 183

27.4 Flash Memory On-Chip Programming . . . . . . . . . . . . . 184

27.5 Output Signal Levels . . . . . . . . . . . . . . . . . . . . . . . . . . 185

27.6 Clock and Reset Timing . . . . . . . . . . . . . . . . . . . . . . . . 185

27.7 I/O Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 187

27.8 Advanced Audio Interface (AAI) Timing. . . . . . . . . . . . 188

27.9 Microwire/SPI Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 190

27.10 ACCESS.bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 195

27.11 USB Port AC Characteristics . . . . . . . . . . . . . . . . . . . . 198

27.12 Multi-Function Timer (MFT) Timing . . . . . . . . . . . . . . . 198

27.13 Versatile Timing Unit (VTU) Timing . . . . . . . . . . . . . . . 199

27.14 External Bus Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . 200

28.0 Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

29.0 Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . 208

30.0 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . . . 209

www.national.com 2

2.0 CPU Features

CPU Features

Fully static RISC processor core, capable of operating

from 0 to 24 MHz with zero wait/hold states

Minimum 41.7 ns instruction cycle time with a 24-MHz in-

ternal clock frequency, based on a 12-MHz external input

30 independently vectored peripheral interrupts

On-Chip Memory

256K bytes reprogrammable Flash program memory

8K bytes Flash data memory

10K bytes of static RAM data memory

Addresses up to 8 Mbytes of external memory

Broad Range of Hardware Communications Peripherals

Bluetooth Lower Link Controller (LLC) including a shared

4.5K byte Bluetooth RAM and 1K byte Bluetooth Sequencer RAM

Full-speed USB node including seven Endpoint-FIFOs

conforming to USB 1.1 specification

ACCESS.bus serial bus (compatible with Philips I

8/16-bit SPI, Microwire/Plus serial interface

Universal Asynchronous Receiver/Transmitter (UART)

Advanced Audio Interface (AAI) to connect to external 8/

13-bit PCM Codecs as well as to ISDN-Controllers

through the IOM-2 interface (slave only)

CVSD/PCM converter supporting one bidirectional audio

connection

General-Purpose Hardware Peripherals

Dual 16-bit Multi-Function Timer

Versatile Timer Unit with four subsystems (VTU)

Four channel DMA controller

Timing and Watchdog Unit

Flexible I/O

Up to 37 general-purpose I/O pins (shared with on-chip

peripheral I/O pins)

Programmable I/O pin characteristics: TRI-STATE out-

put, push-pull output, weak pull-up input, high-impedance input

Schmitt triggers on general purpose inputs

Multi-Input Wakeup

2

C bus)

CP3BT10

Extensive Power and Clock Management Support

On-chip Phase Locked Loop

Support for multiple clock options

Dual clock and reset

Power-down modes

Power Supply

I/O port operation at 2.5V to 3.3V

Core logic operation at 2.5V

On-chip power-on reset

Temperature Range

-40°C to +85°C (Industrial)

Packages

CSP-48, LQFP-100

Complete Development Environment

Pre-integrated hardware and software support for rapid

prototyping and production

Integrated environment

Project manager

Multi-file C source editor

High-level C source debugger

Comprehensive, integrated, one-stop technical support

Bluetooth Protocol Stack

Applications can interface to the high-level protocols or

directly to the low-level Host Controller Interface (HCI)

Transport layer support allows HCI command-based in-

terface over UART or USB port

Baseband (Link Controller) minimizes the performance

demand on the CPU

Link Manager (LM)

Logical Link Control and Adaptation Protocol (L2CAP)

Service Discovery Protocol (SDP)

RFCOMM Serial Port Emulation Protocol

All packet types, piconet, and scatternet functionality

supported

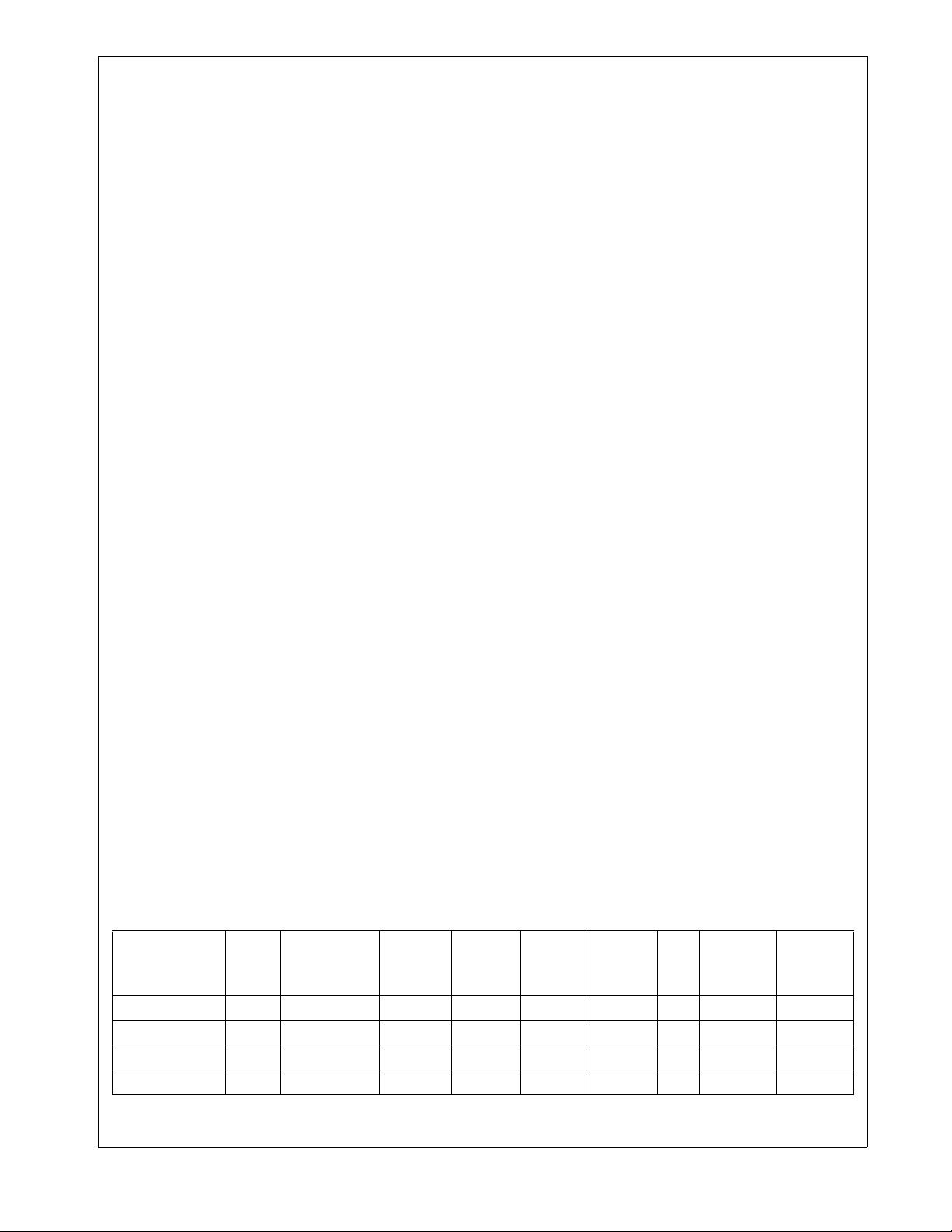

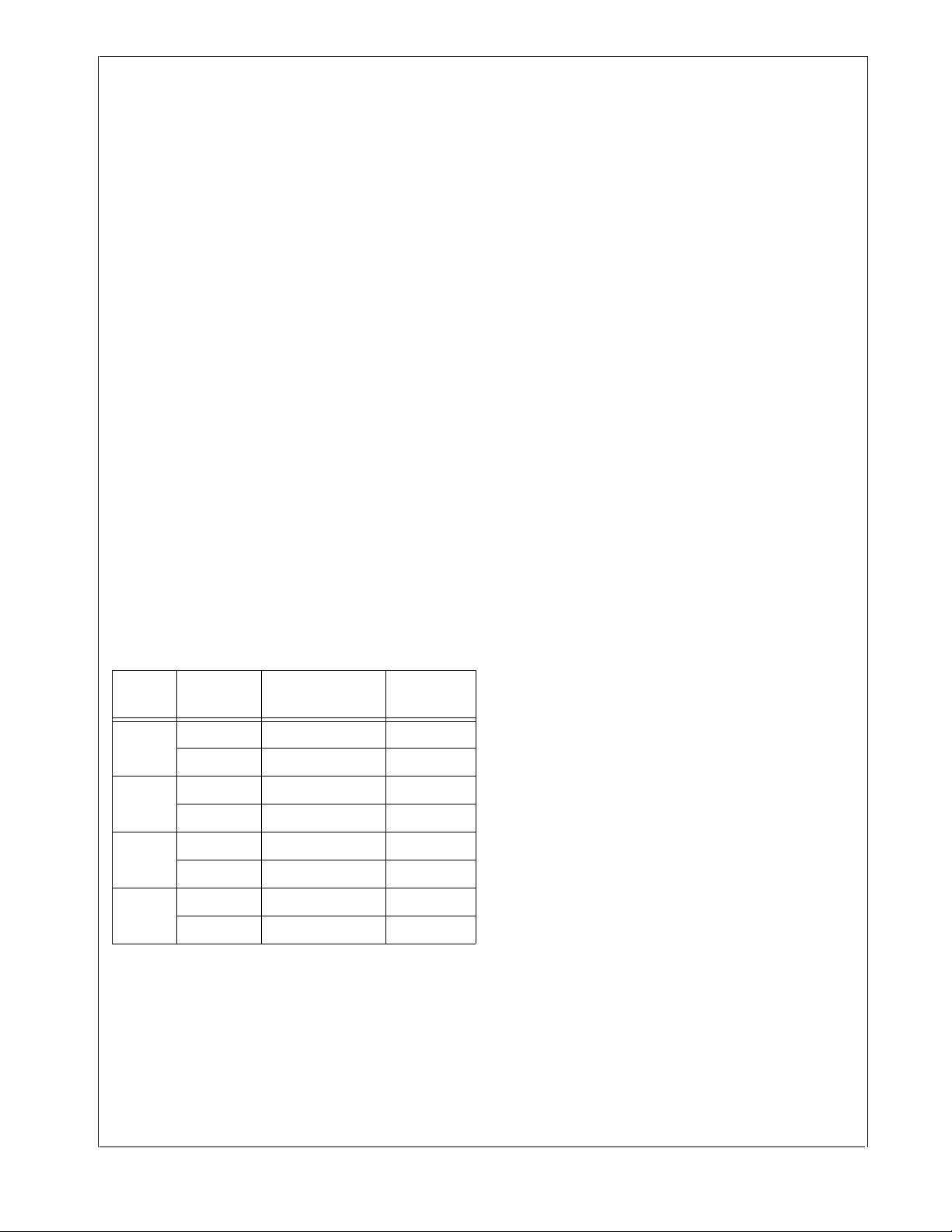

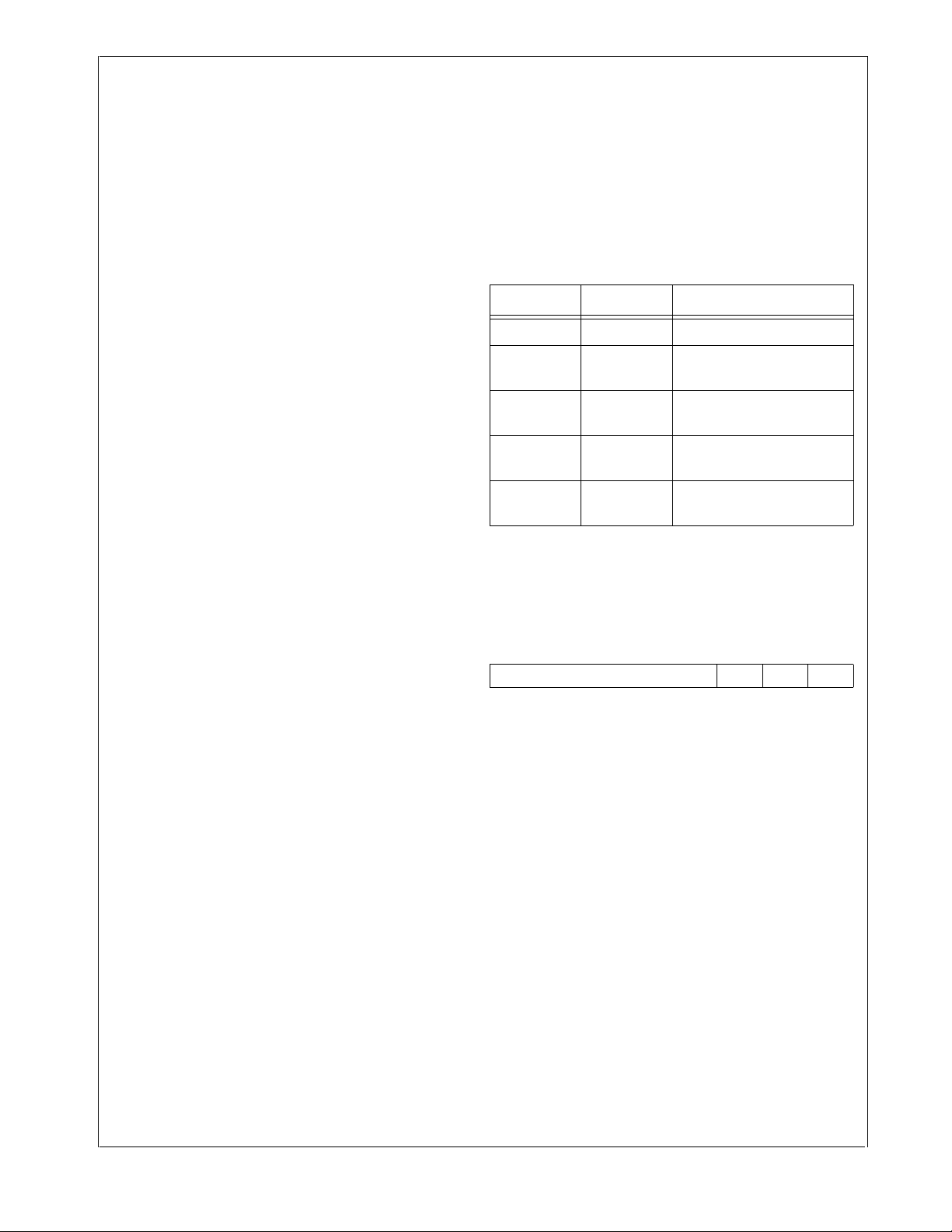

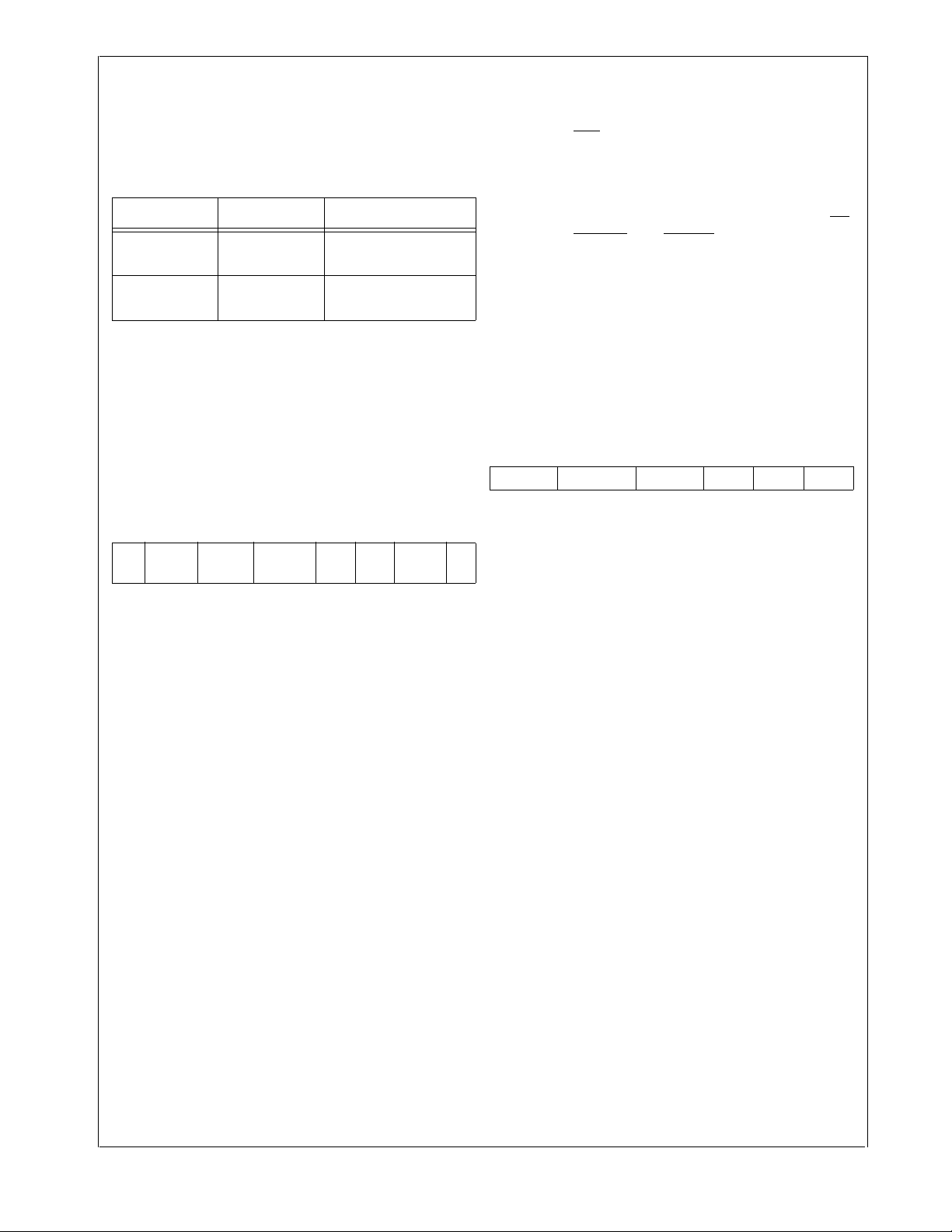

CP3BT10 Connectivity Processor Selection Guide

NSID

CP3BT10G38 24 -40° to +85°C 256 8 10 22 37 LQFP-100 Tray

CP3BT10G38X 24 -40° to +85°C 256 8 10 22 37 LQFP-100 1000-T&R

CP3BT10K38X 24 -40° to +85°C 256 8 10 0 21 CSP-48 2500-T&R

CP3BT10K38Y 24 -40° to +85°C 256 8 10 0 21 CSP-48 250-T&R

T&R = Tape and Reel

Speed

(MHz)

Temp. Range

Program

Flash

(kBytes)

Data

Flash

(kBytes)

SRAM

(kBytes)

External

Address

Lines

I/Os

Package

Typ e

Pack

Method

3 www.national.com

3.0 Device Overview

The CP3BT10 connectivity processor is complete microcomputer with all system timing, interrupt logic, program

CP3BT10

memory, data memory, I/O ports included on-chip, making

them well-suited to a wide range of embedded applications.

The block diagram on page 1 shows the major on-chip components of the CP3BT10.

3.1 CR16C CPU CORE

The CP3BT10 implements the CR16C CPU core module.

The high performance of the CPU core results from the implementation of a pipelined architecture with a two-bytesper-cycle pipelined system bus. As a result, the CPU can

support a peak execution rate of one instruction per clock

cycle.

For more information, please refer to the CR16C Programmer’s Reference Manual (document number 424521772101, which may be downloaded from National’s web site at

http://www.national.com).

The I/O pin characteristics are fully programmable. Each pin

can be configured to operate as a TRI-STATE output, pushpull output, weak pull-up input, or high-impedance input.

3.4 BUS INTERFACE UNIT

The Bus Interface Unit (BIU) controls access to internal/external memory and I/O. It determines the configured parameters for bus access (such as the number of wait states for

memory access) and issues the appropriate bus signals for

each requested access.

The BIU uses a set of control registers to determine how

many wait states and hold states are used when accessing

Flash program memory, and the I/O area (Port B and Port

C). At start-up, the configuration registers are set for slowest

possible memory access. To achieve fastest possible program execution, appropriate values must be programmed.

These settings vary with the clock frequency and the type of

off-chip device being accessed.

3.2 MEMORY

The CP3BT10 supports a uniform linear address space of

up to 16 megabytes. Three types of on-chip memory occupy

specific regions within this address space:

256K bytes of Flash program memory

8K bytes of Flash data memory

10K bytes of static RAM

Up to 8M bytes of external memory (100-pin devices)

The 256K bytes of Flash program memory are used to store

the application program, Bluetooth protocol stack, and realtime operating system. The Flash memory has security features to prevent unintentional programming and to prevent

unauthorized access to the program code. This memory

can be programmed with an external programming unit or

with the device installed in the application system (in-system programming).

The 8K bytes of Flash data memory are used for non-volatile storage of data entered by the end-user, such as configuration settings.

The 10K bytes of static RAM are used for temporary storage

of data and for the program stack and interrupt stack. Read

and write operations can be byte-wide or word-wide, depending on the instruction executed by the CPU.

Up to 8M bytes of external memory can be added on an external bus. The external bus is only available on devices in

100-pin packages.

For Flash program and data memory, the device internally

generates the necessary voltages for programming. No additional power supply is required.

3.3 INPUT/OUTPUT PORTS

The device has up to 37 software-configurable I/O pins, organized into five ports called Port B, Port C, Port G, Port H,

and Port I. Each pin can be configured to operate as a general-purpose input or general-purpose output. In addition,

many I/O pins can be configured to operate as inputs or outputs for on-chip peripheral modules such as the UART, timers, or Microwire/SPI interface.

3.5 INTERRUPT CONTROL UNIT (ICU)

The ICU receives interrupt requests from internal and external sources and generates interrupts to the CPU. An interrupt is an event that temporarily stops the normal flow of

program execution and causes a separate interrupt handler

to be executed. After the interrupt is serviced, CPU execution continues with the next instruction in the program following the point of interruption.

Interrupts from the timers, UART, Microwire/SPI interface,

and Multi-Input Wake-Up, are all maskable interrupts; they

can be enabled or disabled by software. There are 32

maskable interrupts, assigned to 32 linear priority levels.

The highest-priority interrupt is the Non-Maskable Interrupt

), which is generated by a signal received on the NMI

(NMI

input pin.

3.6 BLUETOOTH LLC

The integrated hardware Bluetooth Lower Link Controller

(LLC) complies to the Bluetooth Specification Version 1.1

and integrates the following functions:

4.5K-byte dedicated Bluetooth data RAM

1K-byte dedicated Bluetooth Sequencer RAM

Support of all Bluetooth 1.1 packet types

Support for fast frequency hopping of 1600 hops/s

Access code correlation and slot timing recovery circuit

Power Management Control Logic

BlueRF-compatible interface to connect with National’s

LMX5252 and other RF transceiver chips

3.7 USB

The USB node is a Universal Serial Bus (USB) Node controller compatible with USB Specification, 1.0 and 1.1. It integrates the required USB transceiver, the Serial Interface

Engine (SIE), and USB endpoint FIFOs. A total of seven

endpoint pipes are supported: one bidirectional pipe for the

mandatory control EP0 and an additional six pipes for unidirectional endpoints to support USB interrupt, bulk, and isochronous data transfers.

www.national.com 4

3.8 MULTI-INPUT WAKE-UP

The Multi-Input Wake-Up (MIWU) module can be used for

either of two purposes: to provide inputs for waking up (exiting) from the Halt, Idle, or Power Save mode; or to provide

general-purpose edge-triggered maskable interrupts from

external sources. This 16-channel module generates four

programmable interrupts to the CPU based on the signals

received on its 16 input channels. Channels can be individually enabled or disabled, and programmed to respond to

positive or negative edges.

3.9 TRIPLE CLOCK AND RESET

The Triple Clock and Reset module generates a high-speed

main System Clock from an external crystal network. It also

provides the main system reset signal and a power-on reset

function.

This module generates a slow System Clock (32.768 kHz)

from an optional external crystal network. The Slow Clock is

used for operating the device in power-save mode. The

32.768 kHz external crystal network is optional, because

the low speed System Clock can be derived from the highspeed clock by a prescaler. Also, two independent clocks divided down from the high speed clock are available on output pins.

The Triple Clock and Reset module provides the clock signals required for the operation of the various CP3BT10 onchip modules. From external crystal networks, it generates

the Main Clock, which can be scaled up to 24 MHz from an

external 12 MHz input clock, and a 32.768 kHz secondary

System Clock. The 12 MHz external clock is primarily used

as the reference frequency for the on-chip PLL. Also the

clock for modules which require a fixed clock rate (e.g. the

Bluetooth LLC and the CVSD/PCM transcoder) is generated through prescalers from the 12 MHz clock. The PLL generates the input clock for the USB node and may be used to

drive the high-speed System Clock through a prescaler. Alternatively, the high speed System Clock can be derived directly from the 12 MHz Main Clock.

In addition, this module generates the device reset by using

reset input signals coming from an external reset and various on-chip modules.

3.10 POWER MANAGEMENT

The Power Management Module (PMM) improves the efficiency of the device by changing the operating mode and

power consumption to match the required level of activity.

The device can operate in any of four power modes:

Active—The device operates at full speed using the high-

frequency clock. All device functions are fully operational.

Power Save —The device operates at reduced speed us-

ing the Slow Clock. The CPU and some modules can

continue to operate at this low speed.

Idle—The device is inactive except for the Power Man-

agement Module and Timing and Watchdog Module,

which continue to operate using the Slow Clock.

Halt—The device is inactive but still retains its internal

state (RAM and register contents).

CP3BT10

3.11 MULTI-FUNCTION TIMER

The Multi-Function Timer (MFT) module contains a pair of

16-bit timer/counter registers. Each timer/counter unit can

be configured to operate in any of the following modes:

Processor-Independent Pulse Width Modulation (PWM)

mode—Generates pulses of a specified width and duty

cycle and provides a general-purpose timer/counter.

Dual Input Capture mode—Measures the elapsed time

between occurrences of external event and provides a

general-purpose timer/counter.

Dual Independent Timer mode—Generates system tim-

ing signals or counts occurrences of external events.

Single Input Capture and Single Timer mode—Provides

one external event counter and one system timer.

3.12 VERSATILE TIMER UNIT

The Versatile Timer Unit (VTU) module contains four independent timer subsystems, each operating in either dual 8bit PWM configuration, as a single 16-bit PWM timer, or a

16-bit counter with two input capture channels. Each of the

four timer subsystems offer an 8-bit clock prescaler to accommodate a wide range of frequencies.

3.13 TIMING AND WATCHDOG MODULE

The Timing and Watchdog Module (TWM) contains a RealTime timer and a Watchdog unit. The Real-Time Clock Timing function can be used to generate periodic real-time

based system interrupts. The timer output is one of 16 inputs to the Multi-Input-Wake-Up module which can be used

to exit from a power-saving mode. The Watchdog unit is designed to detect the application program getting stuck in an

infinite loop resulting in loss of program control or “runaway”

programs. When the watchdog triggers, it resets the device.

The TWM is clocked by the low-speed System Clock.

3.14 UART

The UART supports a wide range of programmable baud

rates and data formats, parity generation, and several error

detection schemes. The baud rate is generated on-chip, under software control.

The UART offers a wake-up condition from the power-save

mode using the Multi-Input Wake-Up module.

3.15 MICROWIRE/SPI

The Microwire/SPI (MWSPI) interface module supports synchronous serial communications with other devices that

conform to Microwire or Serial Peripheral Interface (SPI)

specifications. It supports 8-bit and 16-bit data transfers.

The Microwire interface allows several devices to communicate over a single system consisting of four wires: serial in,

serial out, shift clock, and slave enable. At any given time,

the Microwire interface operates as the master or a slave.

The Microwire interface supports the full set of slave select

for multi-slave implementation.

In master mode, the shift clock is generated on chip under

software control. In slave mode, a wake-up out of powersave mode is triggered using the Multi-Input Wake-Up module.

5 www.national.com

3.16 ACCESS.BUS INTERFACE

The ACCESS.bus interface module (ACB) is a two-wire serial interface with the ACCESS.bus physical layer. It is also

compatible with Intel’s System Management Bus (SMBus)

CP3BT10

and Philips’ I

a bus master or slave, and can maintain bidirectional communications with both multiple master and slave devices.

The ACCESS.bus receiver can trigger a wake-up condition

out of the low-power modes using the Multi-Input Wake-Up

module.

2

C bus. The ACB module can be configured as

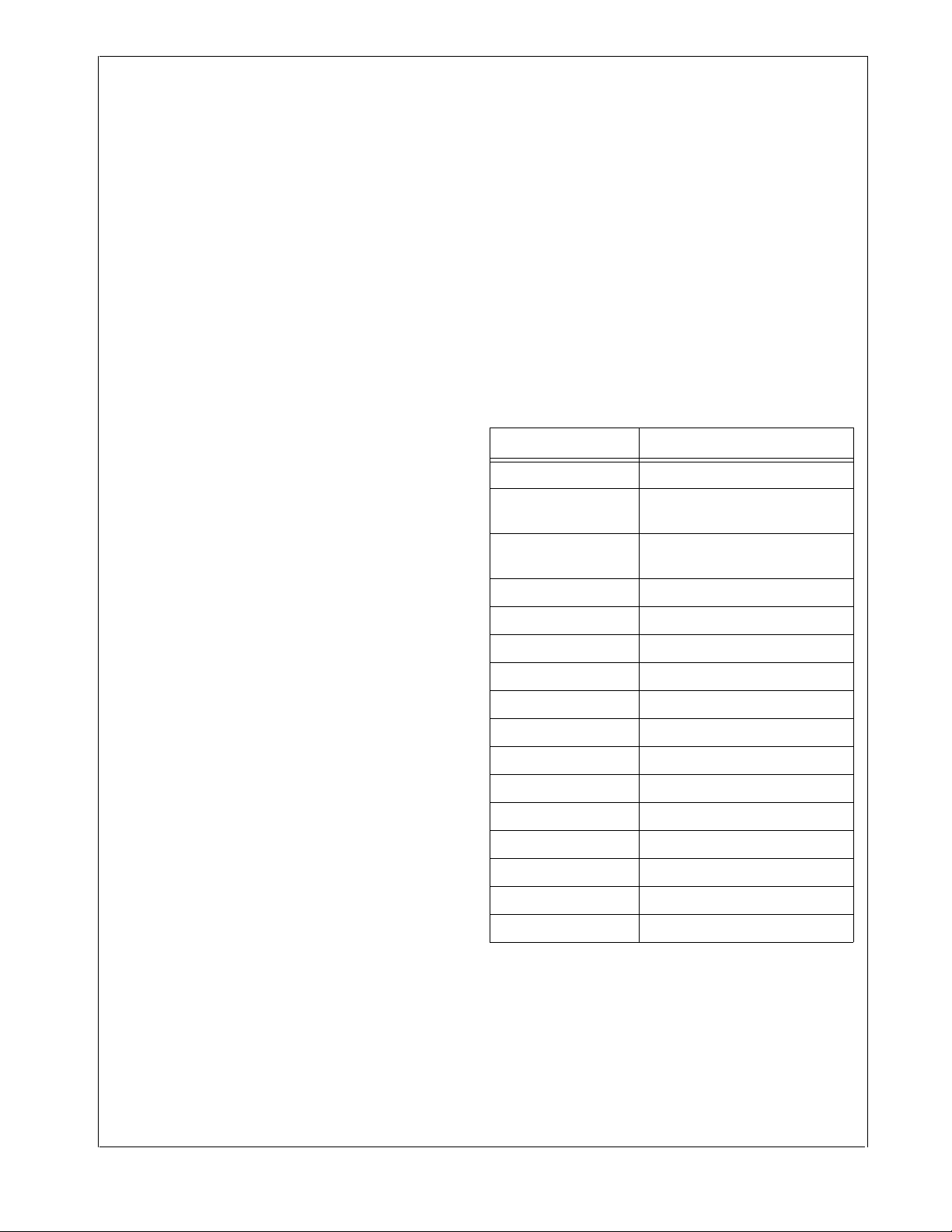

3.17 DMA CONTROLLER

The Direct Memory Access Controller (DMAC) can speed

up data transfer between memory and I/O devices or between two memories, relative to data transfers performed directly by the CPU. A method called cycle-stealing allows the

CPU and the DMAC to use the core bus in parallel. The

DMAC implements four independent DMA channels. DMA

requests from a primary and a secondary source are recognized for each DMA channel, as well as a software DMA request issued directly by the CPU. Table 1 shows the DMA

channel assignment on the CP3BT10 architecture. The following on-chip modules can assert a DMA request to the

DMAC:

CR16C (Software DMA request)

USB

UART

Advanced Audio Interface

CVSD/PCM Converter

Table 1 shows how the four DMA channels are assigned

to the modules listed above.

Table 1 DMA Channel Assignment

Channel

0

1

2

3

Primary/

Secondary

Primary USB Read/Write

Secondary UART Read

Primary UART Write

Secondary Unused N/A

Primary AAI Read

Secondary CVSD/PCM Read

Primary AAI Write

Secondary CVSD/PCM Write

Peripheral Transaction

3.18 ADVANCED AUDIO INTERFACE

The audio interface provides a serial synchronous, full-duplex interface to codecs and similar serial devices. Transmit

and receive paths operate asynchronously with respect to

each other. Each path uses three signals for communication: shift clock, frame synchronization, and data.

In case receive and transmit use separate shift clocks and

frame sync signals, the interface operates in its asynchronous mode. Alternatively, the transmit and receive path can

share the same shift clock and frame sync signals for synchronous mode operation.

The interface can handle data words of either 8- or 16-bit

length and data frames can consist of up to four slots.

In the normal mode of operation, the interface only transfers

one word at a periodic rate. In the network mode, the interface transfers multiple words at a periodic rate. The periodic

rate is also called a data frame and each word within one

frame is called a slot. The beginning of each new data frame

is marked by the frame sync signal.

3.19 CVSD/PCM CONVERSION MODULE

The CVSD/PCM module performs conversion between

CVSD and PCM data, in which the CVSD encoding is as defined in the Bluetooth specification 1.0 and the PCM data

can be 8-bit µ-Law, 8-bit A-Law, or 13-bit to 16-bit Linear.

3.20 SERIAL DEBUG INTERFACE

The Serial Debug Interface module (SDI module) provides

a JTAG-based serial link to an external debugger, for example running on a PC. In addition, the SDI module integrates

an on-chip debug module, which allows the user to set up to

four hardware breakpoints on instruction execution and data

transfer. The SDI module can act as a CPU bus master to

access all memory mapped resources, such as RAM and

peripherals. It also provides fast program download into the

on-chip Flash program memory using the JTAG interface.

Note: The SDI module may assert Freeze mode to gather

information, which may cause periodic fluctuations in response (bus availability, interrupt latency, etc.). Anomalous

behavior often may be traced to SDI activity.

3.21 DEVELOPMENT SUPPORT

In addition to providing the features needed for the next generation of embedded Bluetooth products, the CP3BT10 is

backed up by the software resources designers need for

rapid time-to-market, including an operating system, Bluetooth protocol stack implementation, peripheral drivers, reference designs, and an integrated development

environment. Combined with National’s LMX5252 Bluetooth

radio transceiver, the CP3BT10 provides a total Bluetooth

system solution.

National Semiconductor offers a complete and industryproven application development environment for CP3BT10

applications, including the IAR Embedded Workbench,

iSYSTEM winIDEA and iC3000 Active Emulator, Bluetooth

Development Board, Bluetooth Protocol Stack, and Application Software. See your National Semiconductor sales representative for current information on availability and

features of emulation equipment and evaluation boards.

www.national.com 6

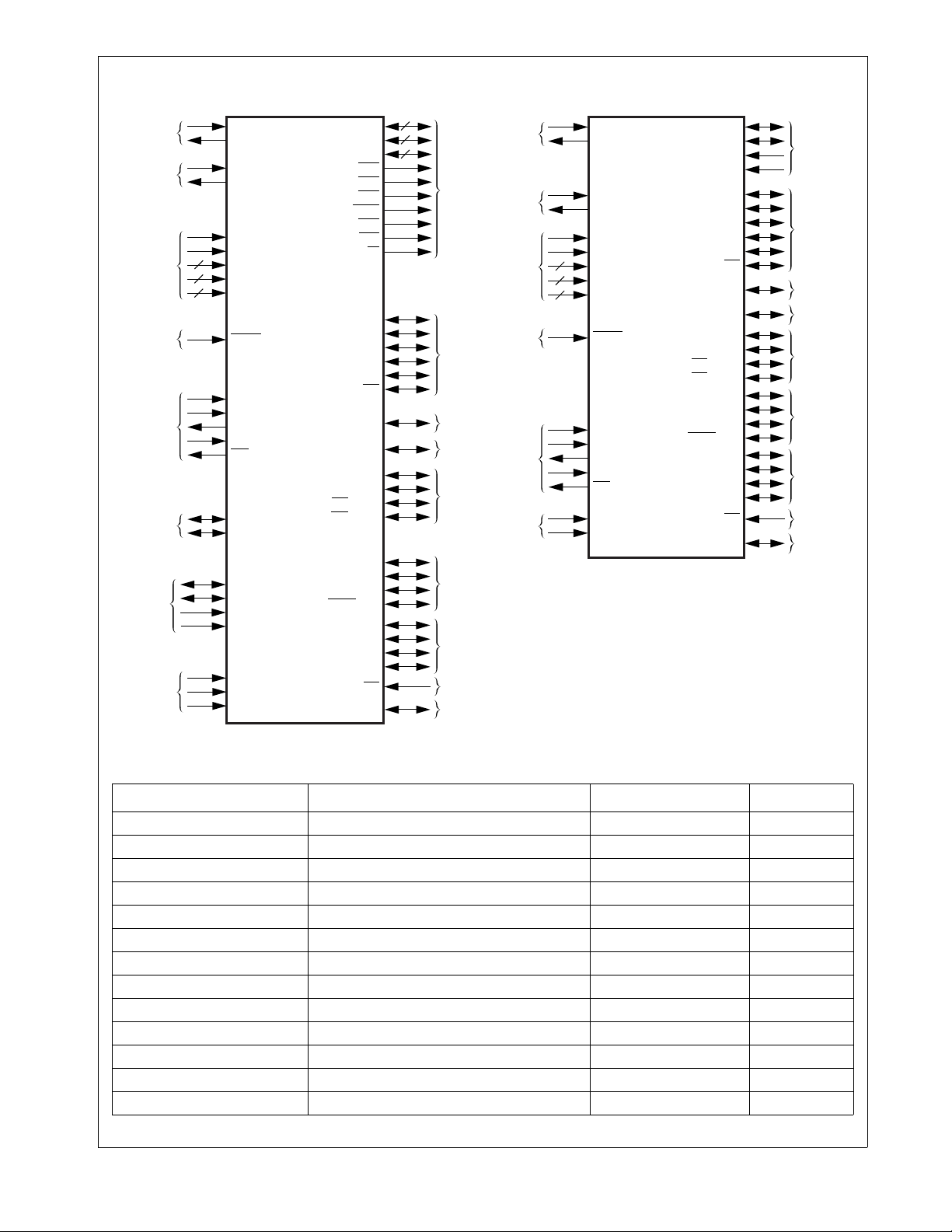

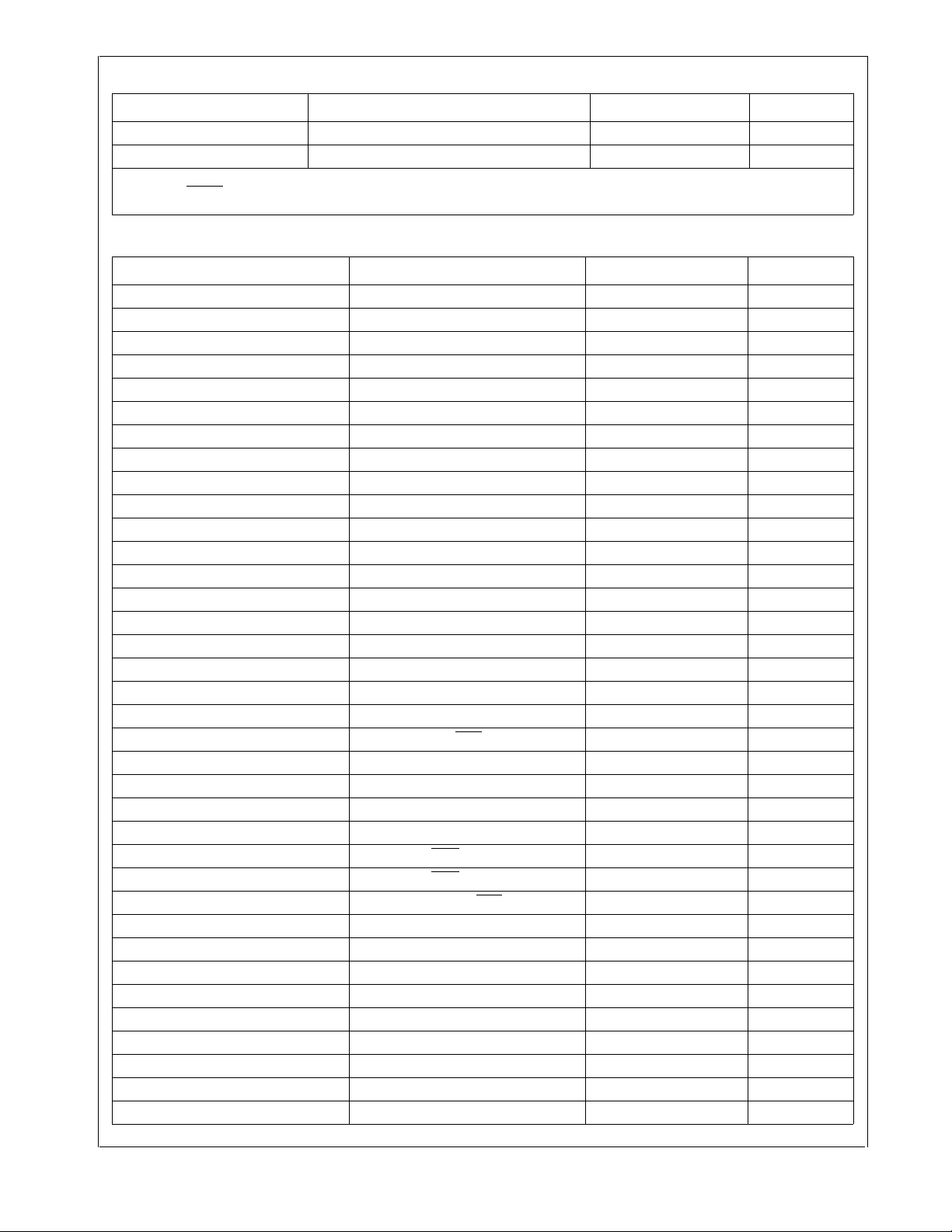

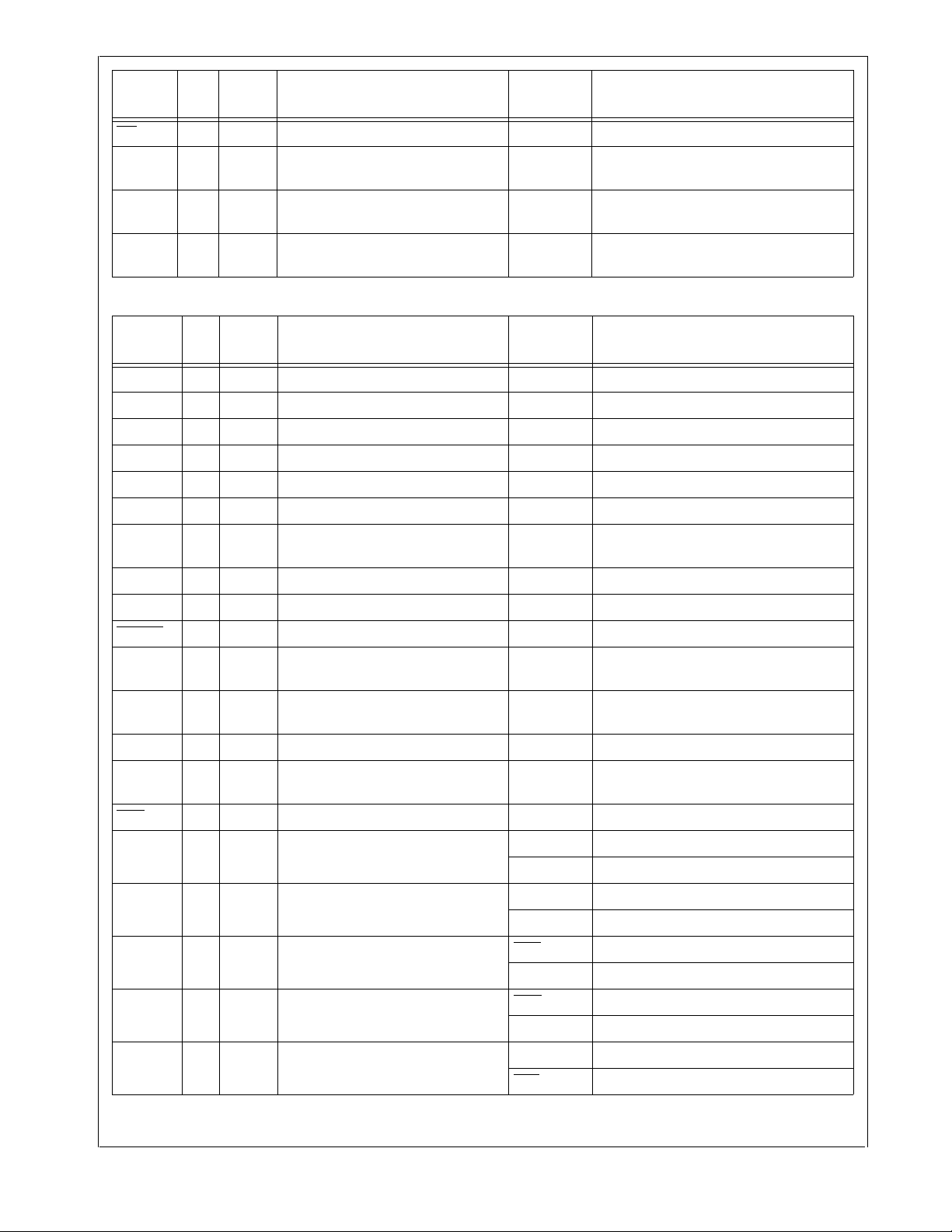

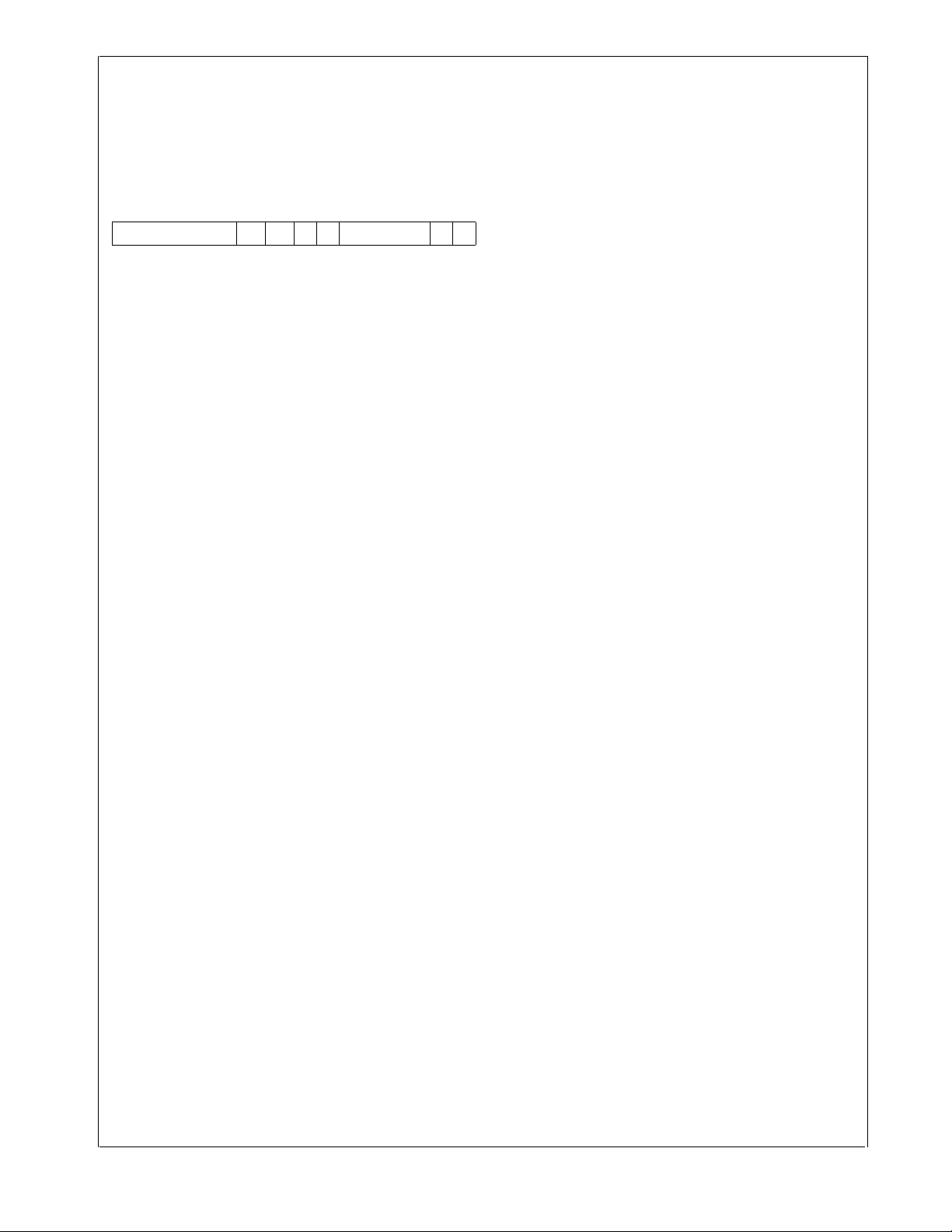

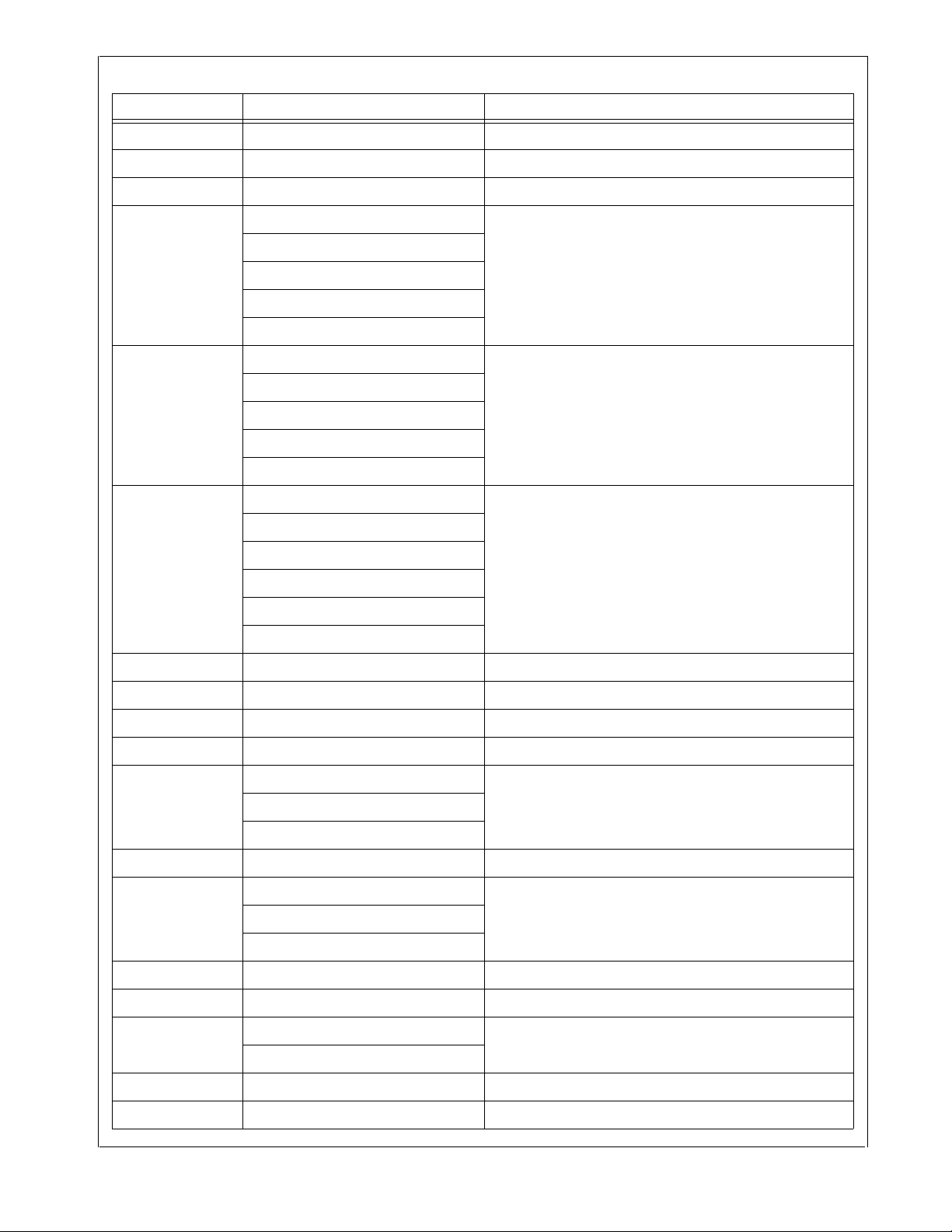

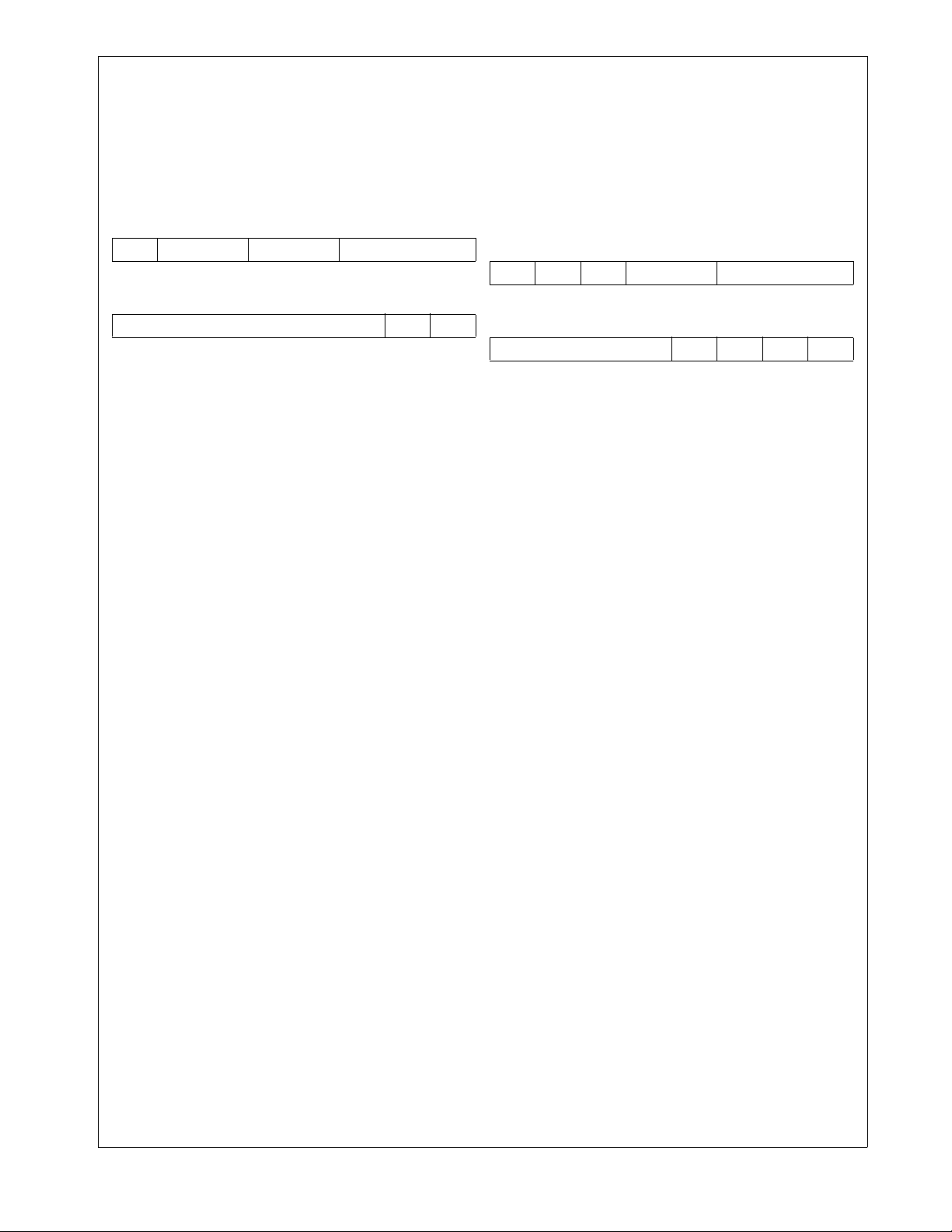

4.0 Device Pinouts

CP3BT10

2 MHz Crystal

or Ext. Clock

32.768 kHz

Crystal

Powe r

Supply

Chip Reset

JTAG I/F to

Debugger/

Programmer

ACCESS.bus

USB

Mode

Selection

2

4

6

X1CKI/BBCLK

X1CKO

X2CKI

X2CKO

AVCC

AGND

CP3BT10

VCC

(LQFP-100)

IOVCC

GND

RESET

TMS

TDI

TDO

TCK

RDY

SDA

SCL

+

D

D-

UVCC

UGND

ENV0

ENV1

ENV2

PB[7:0]

PC[7:0]

A[21:0]

SEL0

SEL1

SEL2

SELIO

WR0

WR1

RD

RFDATA

PIO/RFSYNC

PI1/RFCE

PI3/SCLK

PI4/SDAT

PI5/SLE

PI6/BTSEQ2/WUI9

PI7/BTSEQ3/TA

PG0/RXD/WUI10

PG1/TXD/WUI11

PG2/RTS/WUI12

PG3/CTS/WUI13

PH0/MSK/TIO1

PH1/MDIDO/TIO2

PH2/MDODI/TIO3

PH3/MWCS/TIO4

PH4/SCK/TIO5

PH5/SFS/TIO6

PH6/STD/TIO7

PH7/SRD/TIO8

PG5/SRFS/NMI

PI2/BTSEQ3/SRCLK

8

8

22

12 MHz Crystal

External

Bus

Interface

RF Interface

RF/MIWU

RF/MFT

UART/

MIWU

Microwire/

SPI/

VTU

AAI/

VTU

AAI/NMI

RF/AAI

or Ext. Clock

32.768 kHz

Crystal/

Powe r

Supply

Chip Reset

JTAG I/F to

Debugger/

Programmer

Mode

Selection

2

2

4

X1CKI/BBCLK

X1CKO

X2CKI

X2CKO

AVCC

AGND

CP3BT10

VCC

(CSP-48)

IOVCC

GND

RESET

TMS

TDI

TDO

TCK

RDY

ENV0

ENV1

D

UVCC

UGND

RFDATA

PIO/RFSYNC

PI1/RFCE

PI3/SCLK

PI4/SDAT

PI5/SLE

PI6/BTSEQ2/WUI9

PI7/BTSEQ3/TA

PG0/RXD/WUI10

PG1/TXD/WUI11

PG2/RTS/WUI12

PG3/CTS/WUI13

PH0/MSK/TIO1

PH1/MDIDO/TIO2

PH2/MDODI/TIO3

PH3/MWCS/TIO4

PH4/SCK/TIO5

PH5/SFS/TIO6

PH6/STD/TIO7

PH7/SRD/TIO8

PG5/SRFS/NMI

PI2/BTSEQ1/SRCLK

+

D-

USB

RF Interface

RF/MIWU

RF/MFT

UART/

MIWU

Microwire/

SPI/

VTU

AAI/

VTU

AAI/NMI

RF/AAI

DS148

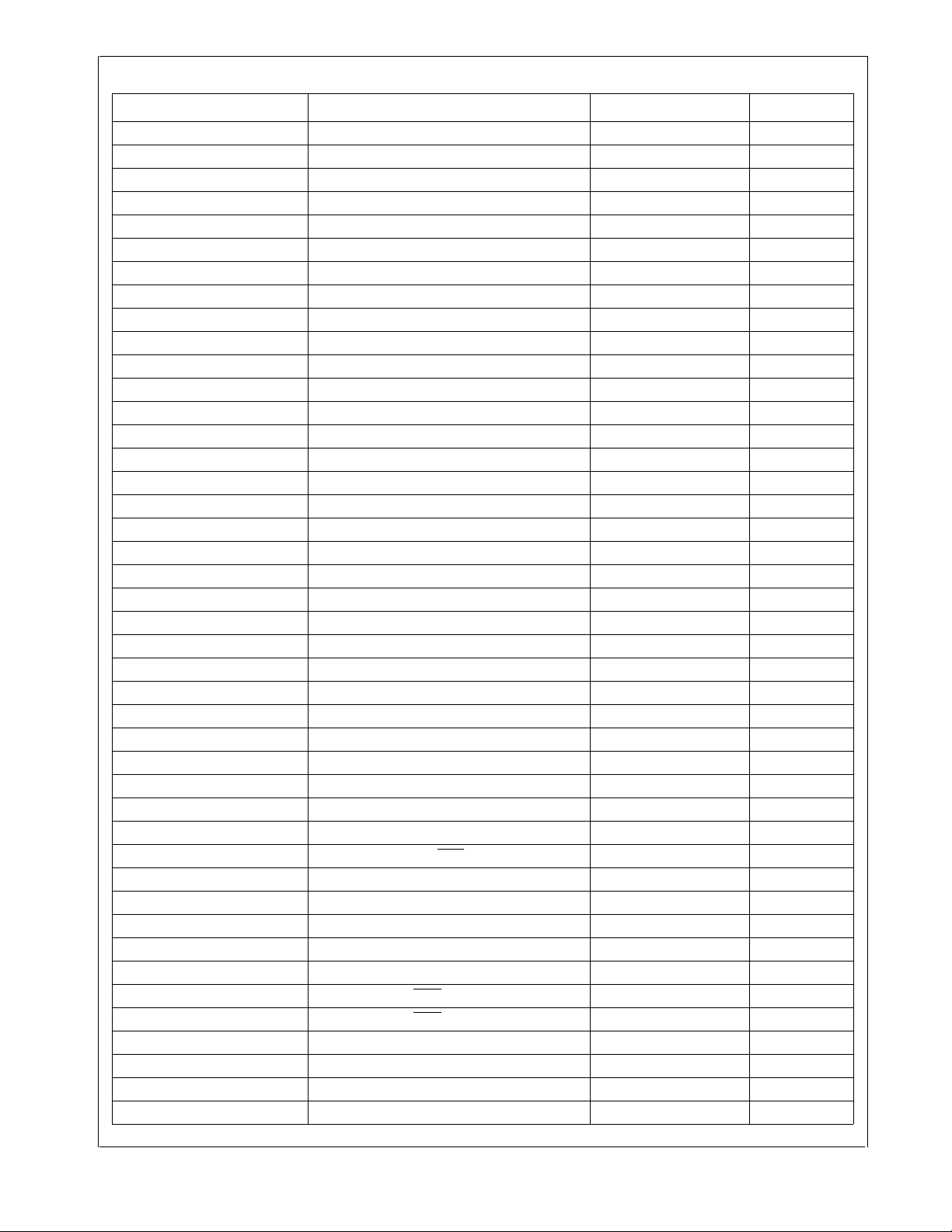

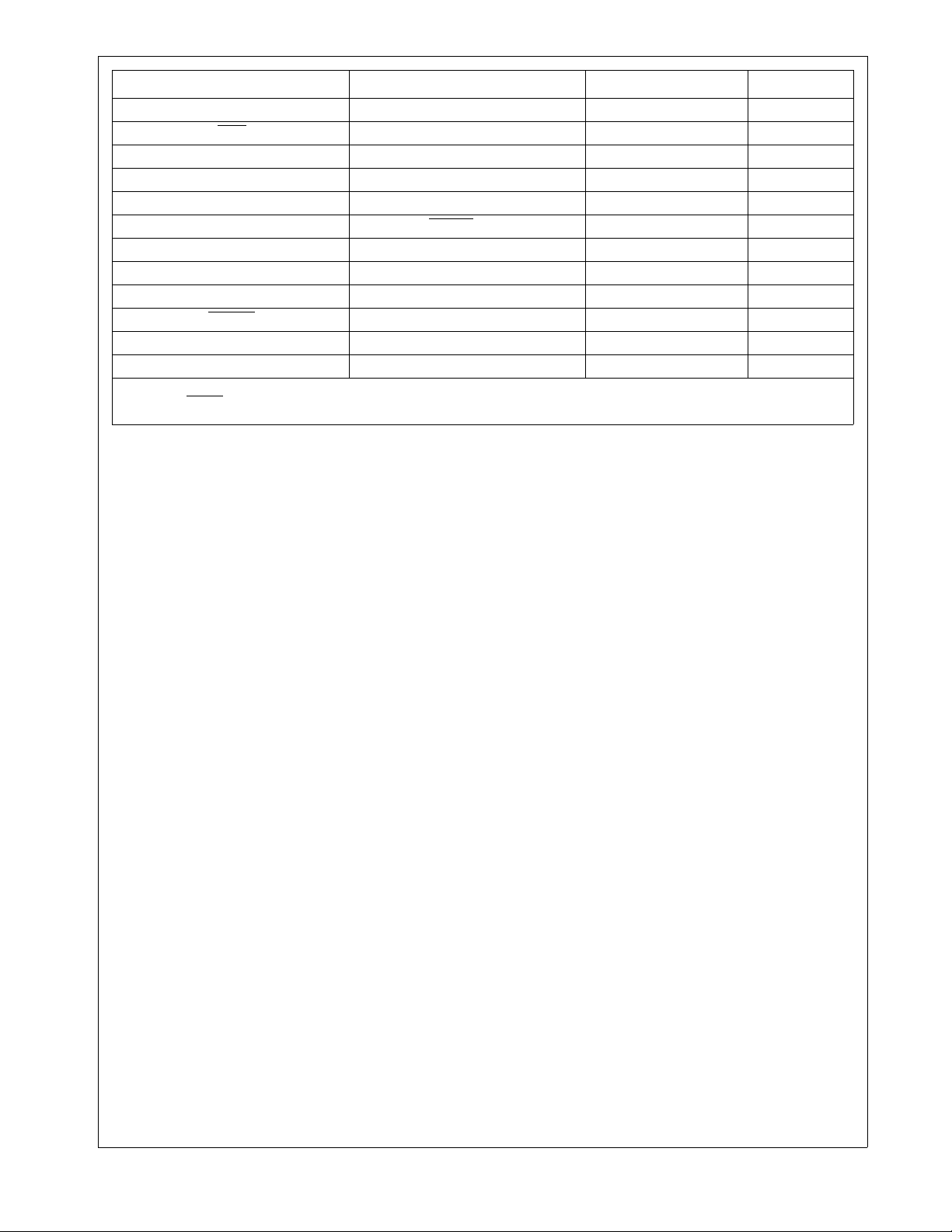

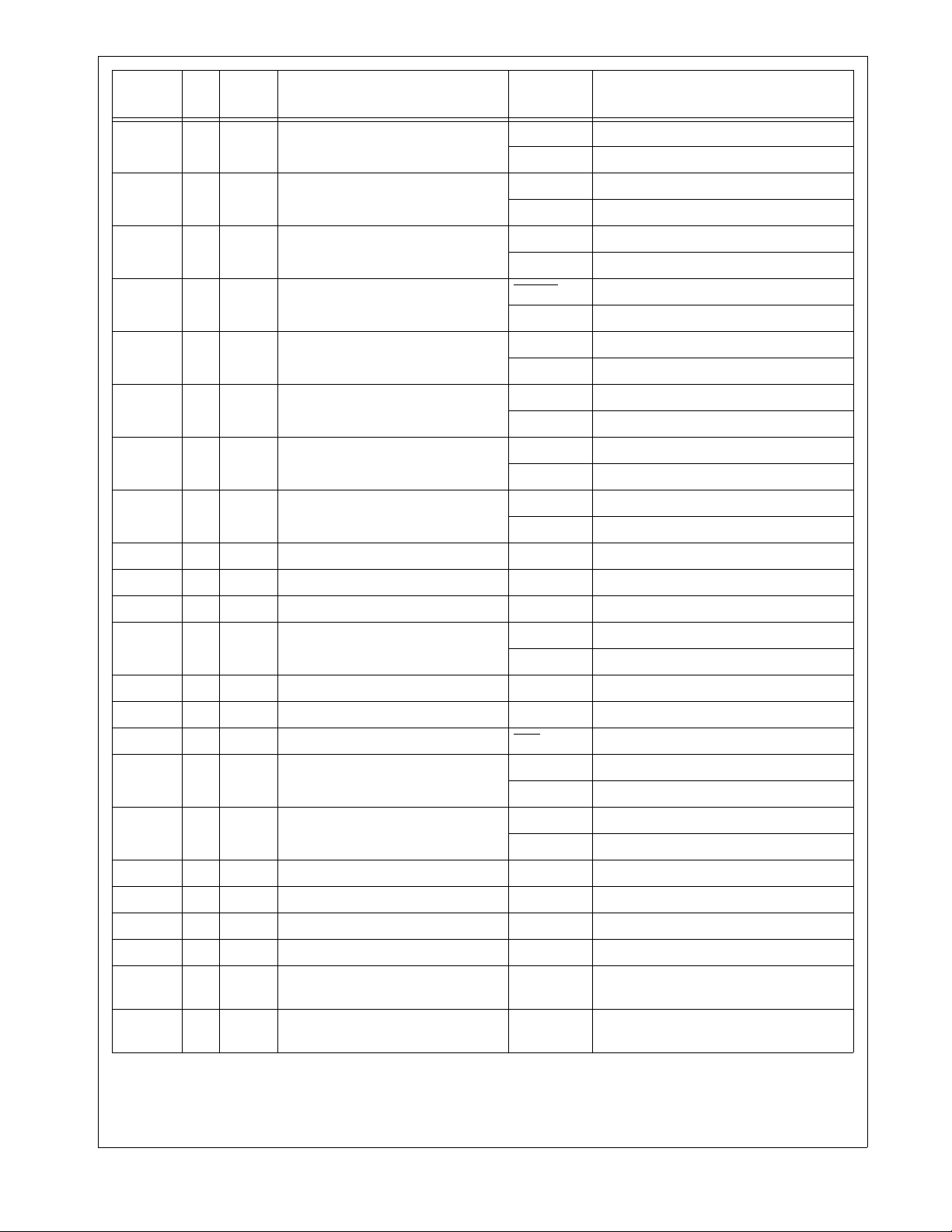

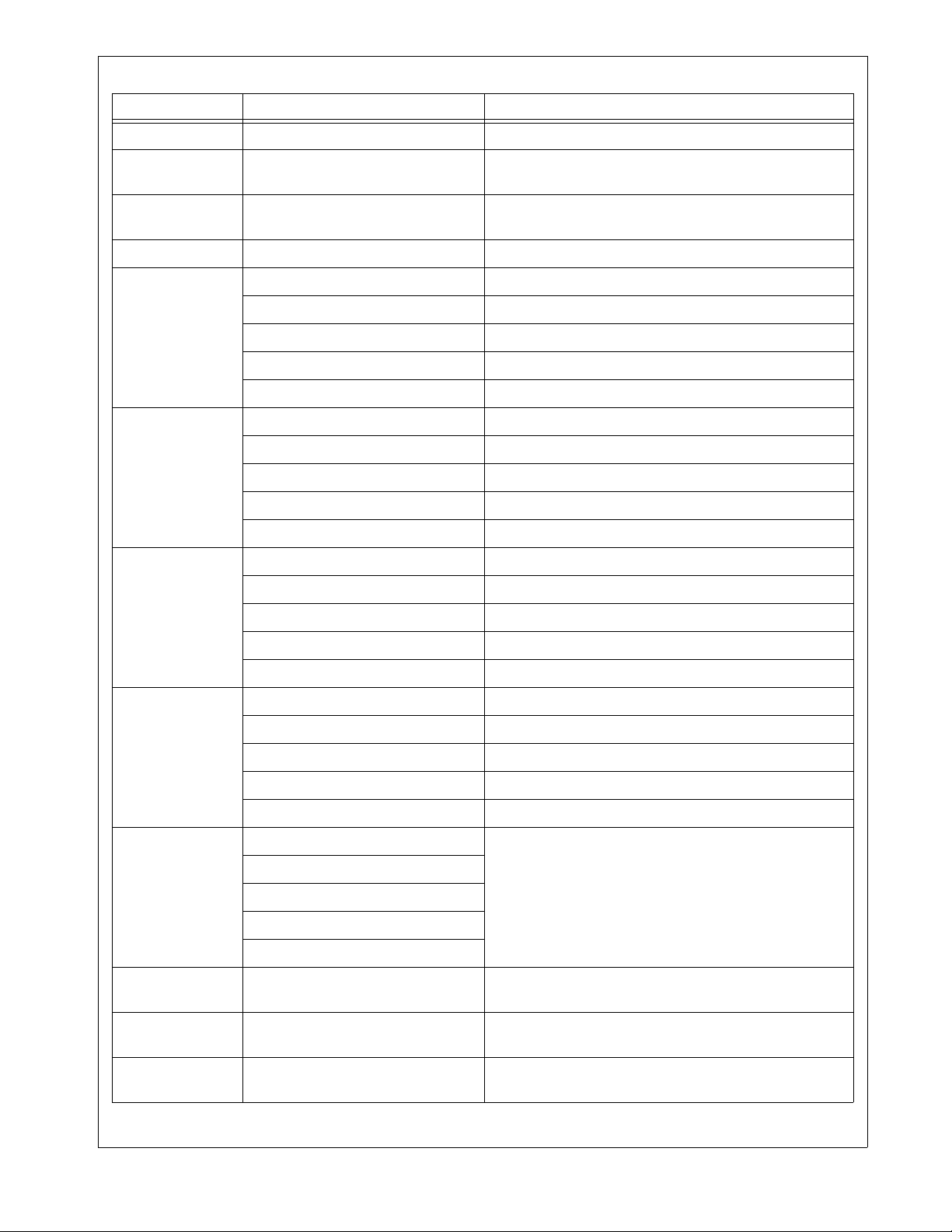

Table 2 Pin Assignments for 100-Pin Package

Pin Name Alternate Function(s) Pin Numbers Type

A14 1 O

A13 2 O

A12 3 O

A11 4 O

A10 5 O

PH6 STD/TIO7 6 GPIO

PH7 SRD/TIO8 7 GPIO

ENV1 8 I/O

A9 9 O

A8 10 O

A7 11 O

A6 12 O

A5 13 O

7 www.national.com

CP3BT10

Table 2 Pin Assignments for 100-Pin Package

Pin Name Alternate Function(s) Pin Numbers Type

A4 14 O

VCC 15 PWR

X2CKI 16 I

X2CKO 17 O

GND 18 PWR

AVC C 19 PWR

AGND 20 PWR

IOVCC 21 PWR

X1CKO 22 O

X1CKI BBCLK 23 I

GND 24 PWR

RFDATA 25 I/O

A3 26 O

A2 27 O

A1 28 O

A0 29 O

PI0 RFSYNC 30 GPIO

PI1 RFCE 31 GPIO

PI2 BTSEQ1/SRCLK 32 GPIO

PB0 D0 33 GPIO

PB1 D1 34 GPIO

PB2 D2 35 GPIO

PB3 D3 36 GPIO

PB4 D4 37 GPIO

PB5 D5 38 GPIO

PB6 D6 39 GPIO

PB7 D7 40 GPIO

GND 41 PWR

IOVCC 42 PWR

PI3 SCLK 43 GPIO

PI4 SDAT 44 GPIO

PI5 SLE

PI6 BTSEQ2/WUI9 46 GPIO

PI7 BTSEQ3/TA 47 GPIO

PG0 RXD/WUI10 48 GPIO

PG1 TXD/WUI11 49 GPIO

PC0 D8 50 GPIO

PG2 RTS

PG3 CTS

PC1 D9 53 GPIO

PC2 D10 54 GPIO

PC3 D11 55 GPIO

PC4 D12 56 GPIO

/WUI12 51 GPIO

/WUI13 52 GPIO

45 GPIO

www.national.com 8

Table 2 Pin Assignments for 100-Pin Package

Pin Name Alternate Function(s) Pin Numbers Type

PC5 D13 57 GPIO

PC6 D14 58 GPIO

PC7 D15 59 GPIO

PG5 SRFS/NMI

TMS 61 I

TCK 62 I

TDI 63 I

GND 64 PWR

IOVCC 65 PWR

ENV2 66 I/O

SEL0 67 O

SCL 68 I/O

SDA 69 I/O

TDO 70 O

D- 71 I/O

D+ 72 I/O

UVCC 73 PWR

UGND 74 PWR

RDY 75 O

SEL1 76 O

SEL2 77 O

SELIO 78 O

A21 79 O

A20 80 O

PH0 MSK/TIO1 81 GPIO

PH1 MDIDO/TIO2 82 GPIO

PH2 MDODI/TIO3 83 GPIO

PH3 MWCS

ENV0 85 I/O

IOVCC 86 PWR

GND 87 PWR

VCC 88 PWR

GND 89 PWR

RESET 90 I

RD 91 O

WR0 92 O

WR1 93 O

A19 94 O

A18 95 O

A17 96 O

A16 97 O

A15 98 O

/TIO4 84 GPIO

60 GPIO

CP3BT10

9 www.national.com

Table 2 Pin Assignments for 100-Pin Package

Pin Name Alternate Function(s) Pin Numbers Type

CP3BT10

PH4 SCK/TIO5 99 GPIO

PH5 SFS/TIO6 100 GPIO

Note 1: The ENV0, ENV1, ENV2, TCK, TDI, and TMS pins each have a weak pull-up to keep the input from floating.

Note 2: The RESET

Note 3: These functions are always enabled, due to the direct low-impedance path to these pins.

input has a weak pulldown.

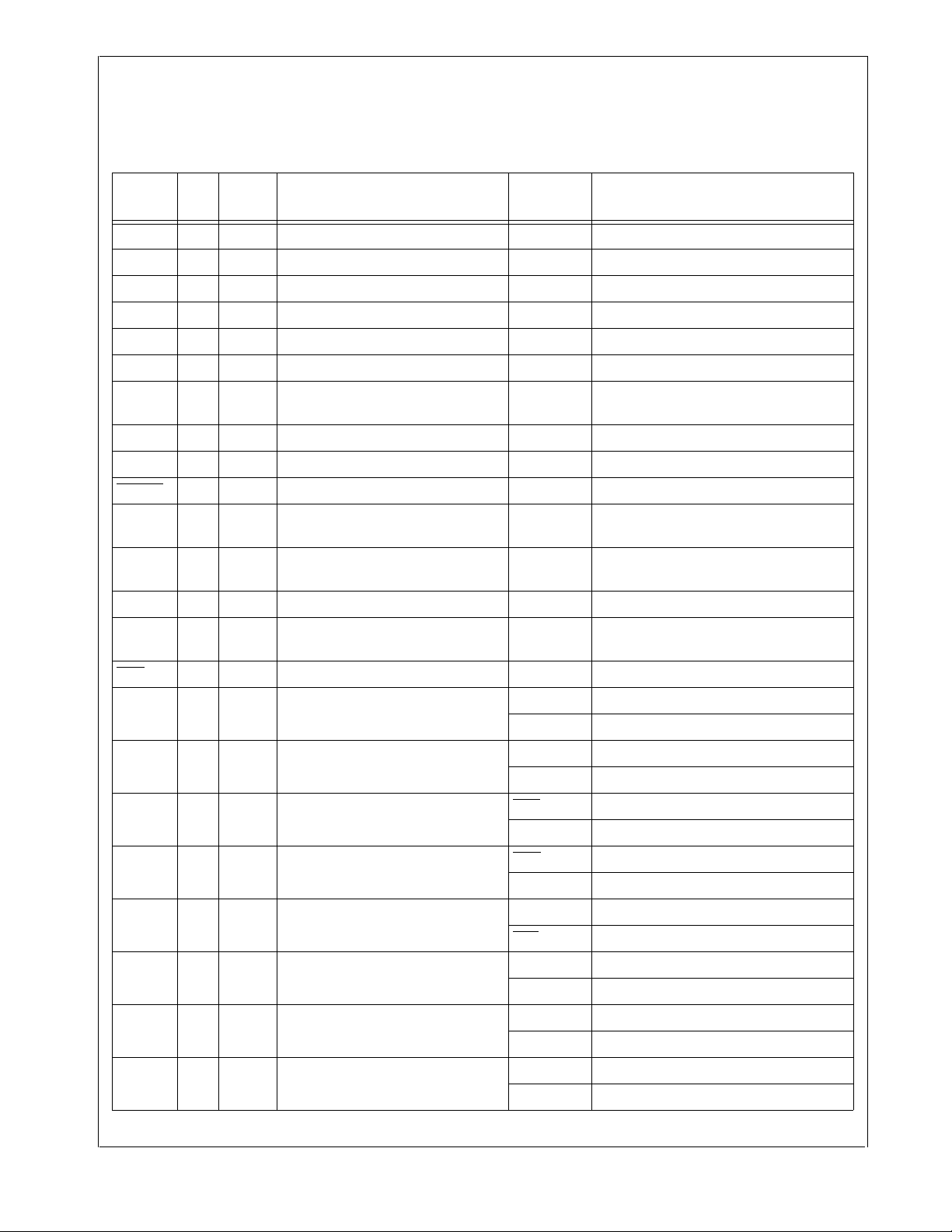

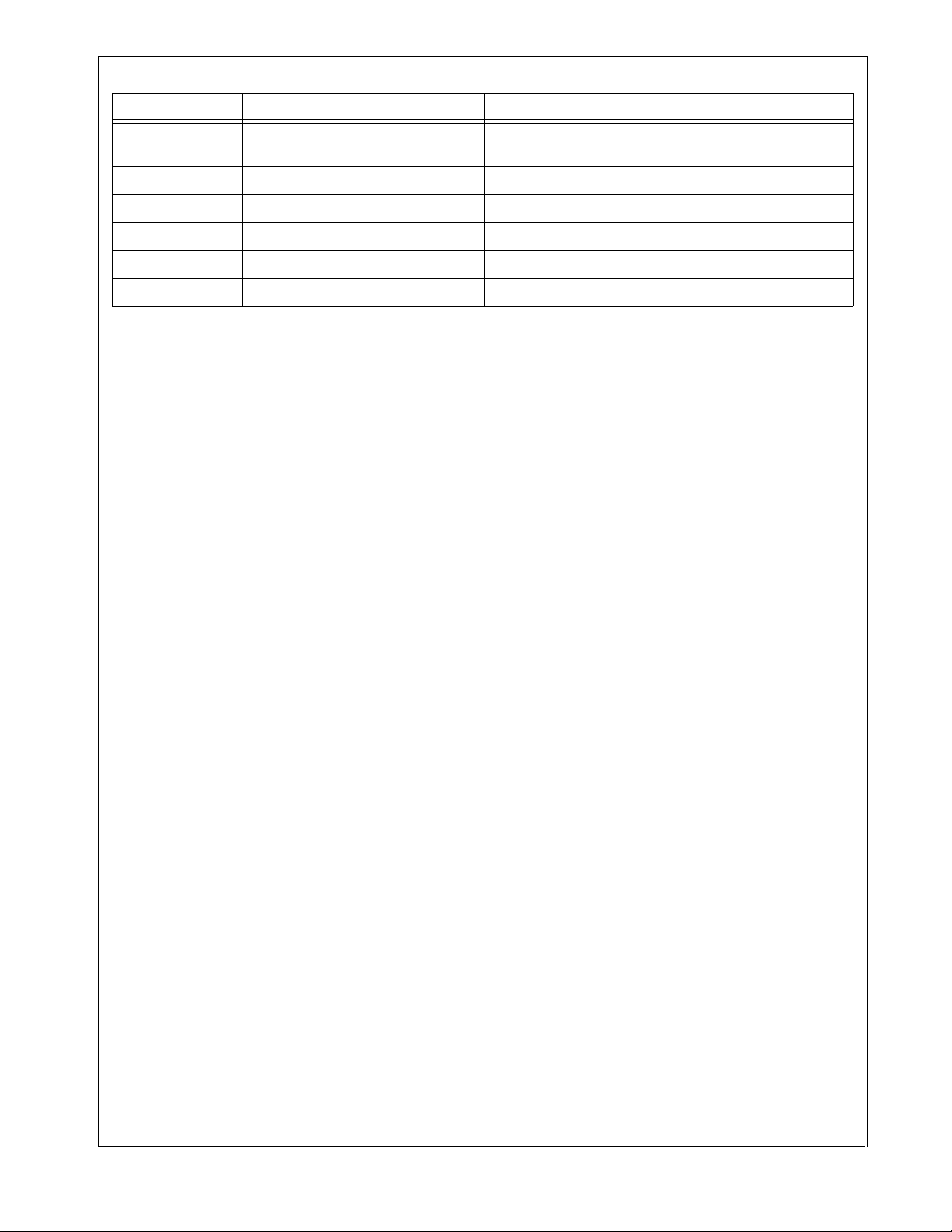

Table 3 Pin Assignments for 48-Pin Package

Pin Name Alternate Function(s) Pin Number Type

PH6 STD/TIO7

PH7 SRD/TIO8

ENV1

VCC

X2CKI

X2CKO

GND

AVC C

AGND

IOVCC

X1CKO

X1CKI BBCLK

GND

RFDATA

PI0 RFSYNC

PI1 RFCE

PI2 BTSEQ1/SRCLK

PI3 SCLK

PI4 SDAT

PI5 SLE

PI6 BTSEQ2/WUI9

PI7 BTSEQ3/TA

PG0 RXD/WUI10

PG1 TXD/WUI11

PG2 RTS

PG3 CTS

/WUI12

/WUI13

PG5 SRFS/NMI

TMS

TCK

TDI

GND

IOVCC

TDO

D-

D+

UVCC

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

1

2

3

4

5

6

7

8

9

GPIO

GPIO

I/O

PWR

I

O

PWR

PWR

PWR

PWR

O

I

PWR

I/O

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

GPIO

I

I

I

PWR

PWR

O, GPIO

O, GPIO

I/O

PWR, I/O

www.national.com 10

Pin Name Alternate Function(s) Pin Number Type

UGND

RDY

PH0 MSK/TIO1

PH1 MDIDO/TIO2

PH2 MDODI/TIO3

PH3 MWCS

/TIO4

ENV0

VCC

GND

RESET

PH4 SCK/TIO5

PH5 SFS/TIO6

Note 1: The ENV0, ENV1 and ENV2, TCK, TDI and TMS pins each have a weak pull-up to keep the input from floating.

Note 2: The RESET

Note 3: These functions are always enabled, due to the direct low-impedance path to these pins.

input has a weak pulldown.

37

38

39

40

41

42

43

44

45

46

47

48

CP3BT10

PWR, O

O

GPIO

GPIO

GPIO

GPIO

I/O

PWR

PWR

I

GPIO

GPIO

11 www.national.com

4.1 PIN DESCRIPTIONS

Some pins may be enabled as general-purpose I/O-port

pins or as alternate functions associated with specific peripherals or interfaces. These pins may be individually con-

CP3BT10

Table 4 CP3BT10 Pin Descriptions for the 100-Pin LQFP Package

figured as port pins, even when the associated peripheral or

interface is enabled. Table 4 lists the device pins.

Name Pins I/O Primary Function

X1CKI 1 Input 12 MHz Oscillator Input BBCLK BB reference clock for the RF Interface

X1CKO 1 Output 12 MHz Oscillator Output None None

X2CKI 1 Input 32 kHz Oscillator Input None None

X2CKO 1 Output 32 kHz Oscillator Output None None

AVCC 1 Input PLL Analog Power Supply None None

IOVCC 4 Input 2.5V - 3.3V I/O Power Supply None None

VCC 2 Input

GND 6 Input Reference Ground None None

AGND 1 Input PLL Analog Ground None None

RESET

TMS 1 Input

TDI 1 Input

TDO 1 Output JTAG Test Data Output None None

TCK 1 Input

RDY

1 Input Chip general reset None None

1 Output NEXUS Ready Output None None

2.5V Core Logic

Power Supply

JTAG Test Mode Select

(with internal weak pull-up)

JTAG Test Data Input

(with internal weak pull-up)

JTAG Test Clock Input

(with internal weak pull-up)

Alternate

Name

None None

None None

None None

None None

Alternate Function

PG0 1 I/O Generic I/O

PG1 1 I/O Generic I/O

PG2 1 I/O Generic I/O

PG3 1 I/O Generic I/O

PG5 1 I/O Generic I/O

PH0 1 I/O Generic I/O

PH1 1 I/O Generic I/O

PH2 1 I/O Generic I/O

RXD UART Receive Data Input

WUI10 Multi-Input Wake-Up Channel 10

TXD UART Transmit Data Output

WUI11 Multi-Input Wake-Up Channel 11

RTS

WUI12 Multi-Input Wake-Up Channel 12

CTS UART Clear-To-Send Input

WUI13 Multi-Input Wake-Up Channel 13

SRFS AAI Receive Frame Sync

NMI

MSK SPI Shift Clock

TIO1 Versatile Timer Channel 1

MDIDO SPI Master In Slave Out

TIO2 Versatile Timer Channel 2

MDODI SPI Master Out Slave In

TIO3 Versatile Timer Channel 3

UART Ready-To-Send Output

Non-Maskable Interrupt Input

www.national.com 12

CP3BT10

Name Pins I/O Primary Function

PH3 1 I/O Generic I/O

PH4 1 I/O Generic I/O

PH5 1 I/O Generic I/O

PH6 1 I/O Generic I/O

PH7 1 I/O Generic I/O

RFDATA 1 I/O Bluetooth RX/TX Data Pin None None

PI0 1 I/O Generic I/O RFSYNC BT AC Correlation/TX Enable Output

PI1 1 I/O Generic I/O RFCE BT RF Chip Enable Output

PI2 1 I/O Generic I/O

PI3 1 I/O Generic I/O SCLK BT Serial I/F Shift Clock Output

Alternate

Name

MWCS

TIO4 Versatile Timer Channel 4

SCK AAI Clock

TIO5 Versatile Timer Channel 5

SFS AAI Frame Synchronization

TIO6 Versatile Timer Channel 6

STD AAI Transmit Data Output

TIO7 Versatile Timer Channel 7

SRD AAI Receive Data Input

TIO8 Versatile Timer Channel 8

BTSEQ1 Bluetooth Sequencer Status

SRCLK AAI Receive Clock

SPI Slave Select Input

Alternate Function

PI4 1 I/O Generic I/O SDAT BT Serial I/F Data

PI5 1 I/O Generic I/O SLE

PI6 1 I/O Generic I/O

PI7 1 I/O Generic I/O

SDA 1 I/O ACCESS.bus Serial Data None None

SCL 1 I/O ACCESS.bus Clock None None

D+ 1 I/O USB D+ Upstream Port None None

D- 1 I/O USB D- Upstream Port None None

UVCC 1 Input 3.3V USB Transceiver Supply None None

UGND 1 Input USB Transceiver Ground None None

PB[7:0] 8 I/O Generic I/O D[7:0] External Data Bus Bit 0 to 7

PC[7:0] 8 I/O Generic I/O D[15:8] External Data Bus Bit 8 to 15

A[21:0] 22 Output

SEL0

SEL1

SEL2

SELIO

1 Output Chip Select for Zone 0 None None

1 Output Chip Select for Zone 1 None None

1 Output Chip Select for Zone 2 None None

1 Output Chip Select for Zone I/O Zone None None

External Address Bus

Bit 0 to 21

WUI9 Multi-Input Wake-Up Channel 9

BTSEQ2 Bluetooth Sequencer Status

TA Multi Function Timer Port A

BTSEQ3 Bluetooth Sequencer Status

None None

BT Serial I/F Load Enable Output

WR0

WR1

1 Output External Memory Write Low Byte None None

1 Output External Memory Write High Byte None None

13 www.national.com

Name Pins I/O Primary Function

Alternate

Name

Alternate Function

RD

CP3BT10

ENV0 1 I/O

ENV1 1 I/O

ENV2 1 I/O

Name Pins I/O Primary Function

X1CKI 1 Input 12 MHz Oscillator Input BBCLK BB reference clock for the RF Interface

X1CKO 1 Output 12 MHz Oscillator Output None None

X2CKI 1 Input 32 kHz Oscillator Input None None

X2CKO 1 Output 32 kHz Oscillator Output None None

AVCC 1 Input PLL Analog Power Supply None None

IOVCC 2 Input 2.5V - 3.3V I/O Power Supply None None

VCC 2 Input

GND 4 Input Reference Ground None None

1 Output External Memory Read None None

Special mode select input with internal pull-up during reset

Special mode select input with internal pull-up during reset

Special mode select input with internal pull-up during reset

Table 5 CP3BT10 Pin Descriptions for the 48-Pin CSP

2.5V Core Logic

Power Supply

PLLCLK PLL Clock Output

CPUCLK CPU Clock Output

SLOWCLK Slow Clock Output

Alternate

Name

None None

Alternate Function

AGND 1 Input PLL Analog Ground None None

RESET

TMS 1 Input

TDI 1 Input

TDO 1 Output JTAG Test Data Output None None

TCK 1 Input

RDY

PG0 1 I/O Generic I/O

PG1 1 I/O Generic I/O

PG2 1 I/O Generic I/O

PG3 1 I/O Generic I/O

PG5 1 I/O Generic I/O

1 Input Chip general reset None None

JTAG Test Mode Select

(with internal weak pull-up)

JTAG Test Data Input

(with internal weak pull-up)

JTAG Test Clock Input

(with internal weak pull-up)

1 Output NEXUS Ready Output None None

None None

None None

None None

RXD UART Receive Data Input

WUI10 Multi-Input Wake-Up Channel 10

TXD UART Transmit Data Output

WUI11 Multi-Input Wake-Up Channel 11

RTS

WUI12 Multi-Input Wake-Up Channel 12

CTS

WUI13 Multi-Input Wake-Up Channel 13

SRFS AAI Receive Frame Sync

NMI

UART Ready-To-Send Output

UART Clear-To-Send Input

Non-Maskable Interrupt Input

www.national.com 14

CP3BT10

Name Pins I/O Primary Function

PH0 1 I/O Generic I/O

PH1 1 I/O Generic I/O

PH2 1 I/O Generic I/O

PH3 1 I/O Generic I/O

PH4 1 I/O Generic I/O

PH5 1 I/O Generic I/O

PH6 1 I/O Generic I/O

PH7 1 I/O Generic I/O

Alternate

Name

MSK SPI Shift Clock

TIO1 Versatile Timer Channel 1

MDIDO SPI Master In Slave Out

TIO2 Versatile Timer Channel 2

MDODI SPI Master Out Slave In

TIO3 Versatile Timer Channel 3

MWCS

TIO4 Versatile Timer Channel 4

SCK AAI Clock

TIO5 Versatile Timer Channel 5

SFS AAI Frame Synchronization

TIO6 Versatile Timer Channel 6

STD AAI Transmit Data Output

TIO7 Versatile Timer Channel 7

SRD AAI Receive Data Input

TIO8 Versatile Timer Channel 8

SPI Slave Select Input

Alternate Function

RFDATA 1 I/O Bluetooth RX/TX Data Pin None None

PI0 1 I/O Generic I/O RFSYNC BT AC Correlation/TX Enable Output

PI1 1 I/O Generic I/O RFCE BT RF Chip Enable Output

PI2 1 I/O Generic I/O

PI3 1 I/O Generic I/O SCLK BT Serial I/F Shift Clock Output

PI4 1 I/O Generic I/O SDAT BT Serial I/F Data

PI5 1 I/O Generic I/O SLE

PI6 1 I/O Generic I/O

PI7 1 I/O Generic I/O

D+ 1 I/O USB D+ Upstream Port None None

D- 1 I/O USB D- Upstream Port None None

UVCC 1 Input 3.3V USB Transceiver Supply None None

UGND 1 Input USB Transceiver Ground None None

ENV0 1 I/O

ENV1 1 I/O

Special mode select input with internal pull-up during reset

Special mode select input with internal pull-up during reset

BTSEQ1 Bluetooth Sequencer Status

SRCLK AAI Receive Clock

BT Serial I/F Load Enable Output

WUI9 Multi-Input Wake-Up Channel 9

BTSEQ2 Bluetooth Sequencer Status

TA Multi Function Timer Port A

BTSEQ3 Bluetooth Sequencer Status

PLLCLK PLL Clock Output

CPUCLK CPU Clock Output

15 www.national.com

5.0 CPU Architecture

The CP3BT10 uses the CR16C third-generation 16-bit

CompactRISC processor core. The CPU implements a Re-

CP3BT10

duced Instruction Set Computer (RISC) architecture that allows an effective execution rate of up to one instruction per

clock cycle. For a detailed description of the CPU16C architecture, see the CompactRISC CR16C Programmer’s Ref-

erence Manual which is available on the National

Semiconductor web site (http://www.nsc.com).

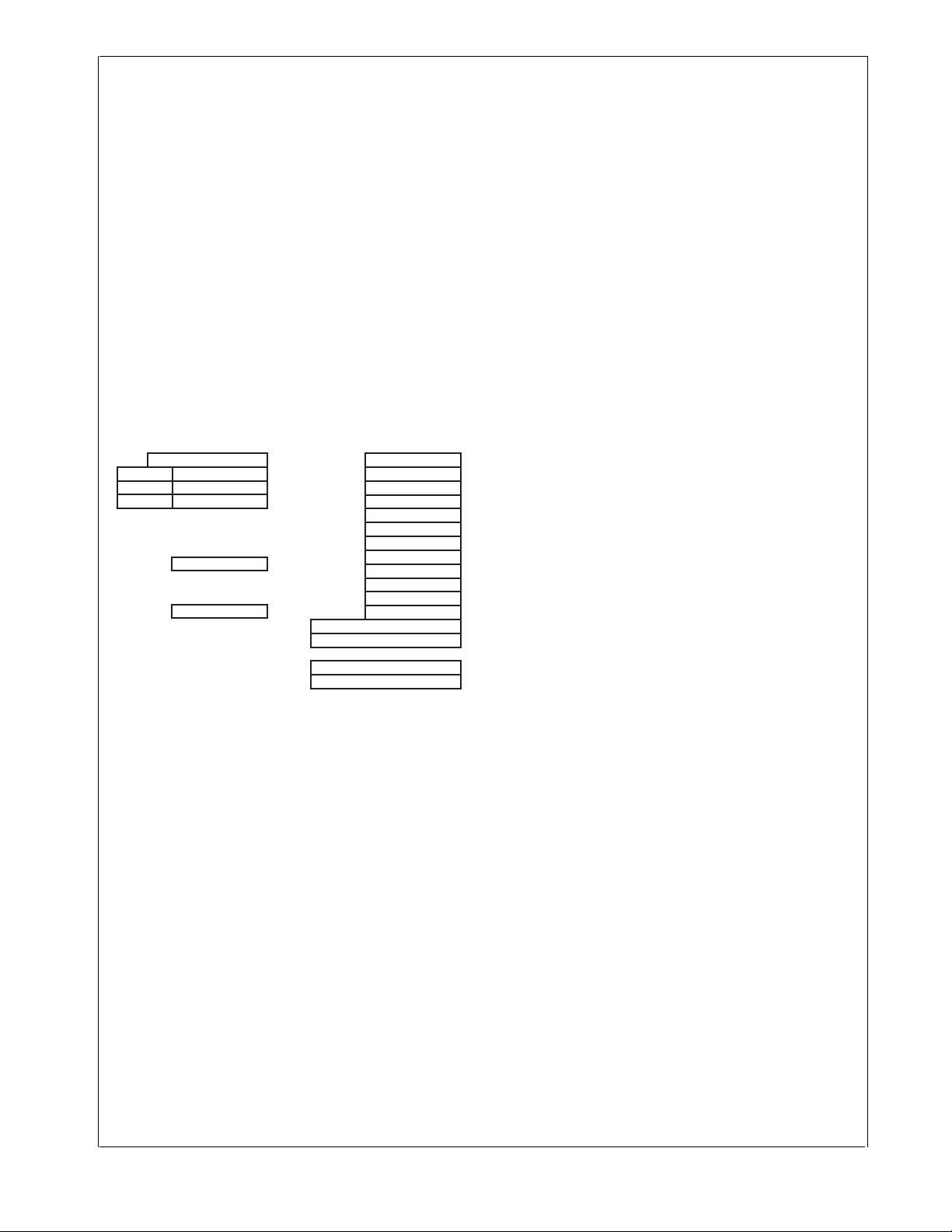

The CR16C CPU core includes these internal registers:

General-purpose registers (R0-R13, RA, and SP)

Dedicated address registers (PC, ISP, USP, and INT-

BASE)

Processor Status Register (PSR)

Configuration Register (CFG)

The R0-R11, PSR, and CFG registers are 16 bits wide. The

R12, R13, RA, SP, ISP and USP registers are 32 bits wide.

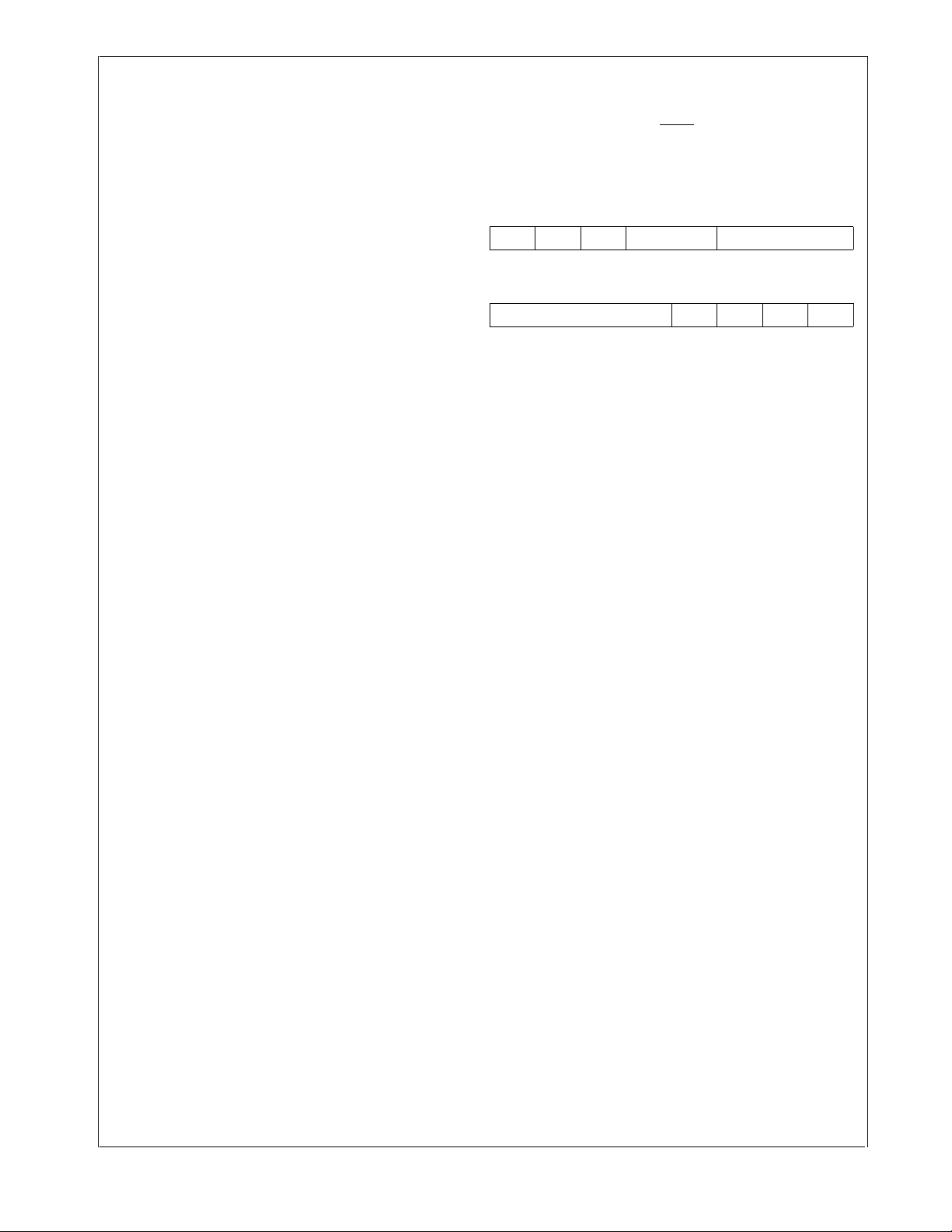

The PC register is 24 bits wide. Figure 1 shows the CPU

registers.

Dedicated Address Registers

31

ISPH

USPH

INTBASEH

15

23

PC

ISPL

USPL

INTBASEL

Processor Status Register

15

PSR

Configuration Register

15

CFG

0

0

0

31

Figure 1. CPU Registers

Some register bits are designated as “reserved.” Software

must write a zero to these bit locations when it writes to the

register. Read operations from reserved bit locations return

undefined values.

5.1 GENERAL-PURPOSE REGISTERS

The CompactRISC CPU features 16 general-purpose registers. These registers are used individually as 16-bit operands or as register pairs for operations on addresses

greater than 16 bits.

General-purpose registers are defined as R0 through

R13, RA, and SP.

Registers are grouped into pairs based on the setting of

the Short Register bit in the Configuration Register

(CFG.SR). When the CFG.SR bit is set, the grouping of

register pairs is upward-compatible with the architecture

of the earlier CR16A/B CPU cores: (R1,R0), (R2,R1) ...

(R11,R10), (R12_L, R11), (R13_L, R12_L), (R14_L,

R13_L) and SP. (R14_L, R13_L) is the same as

(RA,ERA).

General-Purpose Registers

15 0

R0

R1

R2

R3

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

RA

SP

DS004

When the CFG.SR bit is clear, register pairs are grouped

in the manner used by native CR16C software: (R1,R0),

(R2,R1) ... (R11,R10), (R12_L, R11), R12, R13, RA, SP.

R12, R13, RA, and SP are 32-bit registers for holding addresses greater than 16 bits.

With the recommended calling convention for the architecture, some of these registers are assigned special hardware

and software functions. Registers R0 to R13 are for generalpurpose use, such as holding variables, addresses, or index

values. The SP register holds a pointer to the program runtime stack. The RA register holds a subroutine return address. The R12 and R13 registers are available to hold base

addresses used in the index addressing mode.

If a general-purpose register is specified by an operation

that is 8 bits long, only the lower byte of the register is used;

the upper part is not referenced or modified. Similarly, for

word operations on register pairs, only the lower word is

used. The upper word is not referenced or modified.

5.2 DEDICATED ADDRESS REGISTERS

The CR16C has four dedicated address registers to implement specific functions: the PC, ISP, USP, and INTBASE

registers.

5.2.1 Program Counter (PC) Register

The 24-bit value in the PC register points to the first byte of

the instruction currently being executed. CR16C instructions are aligned to even addresses, therefore the least significant bit of the PC is always 0. At reset, the PC is

initialized to 0 or an optional predetermined value. When a

warm reset occurs, value of the PC prior to reset is saved in

the (R1,R0) general-purpose register pair.

5.2.2 Interrupt Stack Pointer (ISP)

The 32-bit ISP register points to the top of the interrupt

stack. This stack is used by hardware to service exceptions

(interrupts and traps). The stack pointer may be accessed

as the ISP register for initialization. The interrupt stack can

be located anywhere in the CPU address space. The ISP

cannot be used for any purpose other than the interrupt

stack, which is used for automatic storage of the CPU registers when an exception occurs and restoration of these

registers when the exception handler returns. The interrupt

stack grows downward in memory. The least significant bit

and the 8 most significant bits of the ISP register are always

0.

5.2.3 User Stack Pointer (USP)

The USP register points to the top of the user-mode program stack. Separate stacks are available for user and supervisor modes, to support protection mechanisms for

multitasking software. The processor mode is controlled by

the U bit in the PSR register (which is called PSR.U in the

shorthand convention). Stack grow downward in memory. If

the USP register points to an illegal address (any address

greater than 0x00FF_FFFF) and the USP is used for stack

access, an IAD trap is taken.

www.national.com 16

5.2.4 Interrupt Base Register (INTBASE)

The INTBASE register holds the address of the dispatch table for exceptions. The dispatch table can be located anywhere in the CPU address space. When loading the

INTBASE register, bits 31 to 24 and bit 0 must written with 0.

5.3 PROCESSOR STATUS REGISTER (PSR)

The PSR provides state information and controls operating

modes for the CPU. The format of the PSR is shown below.

15 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved I P E 0 N Z F 0 U L T C

C The Carry bit indicates whether a carry or bor-

row occurred after addition or subtraction.

0 – No carry or borrow occurred.

1 – Carry or borrow occurred.

T The Trace bit enables execution tracing, in

which a Trace trap (TRC) is taken after every

instruction. Tracing is automatically disabled

during the execution of an exception handler.

– Tracing disabled.

0

1 – Tracing enabled.

L The Low bit indicates the result of the last

comparison operation, with the operands interpreted as unsigned integers.

– Second operand greater than or equal to

0

first operand.

1 – Second operand less than first operand.

U The User Mode bit controls whether the CPU

is in user or supervisor mode. In supervisor

mode, the SP register is used for stack operations. In user mode, the USP register is used

instead. User mode is entered by executing

the Jump USR instruction. When an exception

is taken, the exception handler automatically

begins execution in supervisor mode. The

USP register is accessible using the Load

Processor Register (LPR/LPRD) instruction in

supervisor mode. In user mode, an attempt to

access the USP register generates a UND

trap.

– CPU is executing in supervisor mode.

0

– CPU is executing in user mode.

1

F The Flag bit is a general condition flag for sig-

nalling exception conditions or distinguishing

the results of an instruction, among other

thing uses. For example, integer arithmetic instructions use the F bit to indicate an overflow

condition after an addition or subtraction operation.

Z The Zero bit is used by comparison opera-

tions. In a comparison of integers, the Z bit is

set if the two operands are equal. If the operands are unequal, the Z bit is cleared.

– Source and destination operands un-

0

equal.

1 – Source and destination operands equal.

N The Negative bit indicates the result of the last

comparison operation, with the operands interpreted as signed integers.

– Second operand greater than or equal to

0

first operand.

1 – Second operand less than first operand.

E The Local Maskable Interrupt Enable bit en-

ables or disables maskable interrupts. If this

bit and the Global Maskable Interrupt Enable

(I) bit are both set, all interrupts are enabled.

If either of these bits is clear, only the nonmaskable interrupt is enabled. The E bit is set

by the Enable Interrupts (EI) instruction and

cleared by the Disable Interrupts (DI) instruction.

– Maskable interrupts disabled.

0

1 – Maskable interrupts enabled.

P The Trace Trap Pending bit is used together

with the Trace (T) bit to prevent a Trace (TRC)

trap from occurring more than once for one instruction. At the beginning of the execution of

an instruction, the state of the T bit is copied

into the P bit. If the P bit remains set at the end

of the instruction execution, the TRC trap is

taken.

– No trace trap pending.

0

– Trace trap pending.

1

I The Global Maskable Interrupt Enable bit is

used to enable or disable maskable interrupts.

If this bit and the Local Maskable Interrupt Enable (E) bit are both set, all maskable interrupts are taken. If either bit is clear, only the

non-maskable interrupt is taken. Unlike the E

bit, the I bit is automatically cleared when an

interrupt occurs and automatically set upon

completion of an interrupt handler.

– Maskable interrupts disabled.

0

1 – Maskable interrupts enabled.

Bits Z, C, L, N, and F of the PSR are referenced from assembly language by the condition code in conditional

branch instructions. A conditional branch instruction may

cause a branch in program execution, based on the value of

one or more of these PSR bits. For example, one of the

Bcond instructions, BEQ (Branch EQual), causes a branch

if the PSR.Z bit is set.

On reset, bits 0 through 11 of the PSR are cleared, except

for the PSR.E bit, which is set. On warm reset, the values of

each bit before reset are copied into the R2 general-purpose register. Bits 4 and 8 of the PSR have a constant value

of 0. Bits 12 through 15 are reserved. In general, status bits

are modified only by specific instructions. Otherwise, status

bits maintain their values throughout instructions which do

not implicitly affect them.

CP3BT10

17 www.national.com

5.4 CONFIGURATION REGISTER (CFG)

The CFG register is used to enable or disable various operating modes and to control optional on-chip caches. Because the CP3BT10 does not have cache memory, the

CP3BT10

cache control bits in the CFG register are reserved. All CFG

bits are cleared on reset.

15 10 9 8 7 6 5 2 1 0

Reserved SR ED 0 0 Reserved 0 0

ED The Extended Dispatch bit selects whether

the size of an entry in the interrupt dispatch table (IDT) is 16 or 32 bits. Each entry holds the

address of the appropriate exception handler.

When the IDT has 16-bit entries, and all exception handlers must reside in the first 128K

of the address space. The location of the IDT

is held in the INTBASE register, which is not

affected by the state of the ED bit.

– Interrupt dispatch table has 16-bit entries.

0

1 – Interrupt dispatch table has 32-bit entries.

SR The Short Register bit enables a compatibility

mode for the CR16B large model. In the

CR16C core, registers R12, R13, and RA are

extended to 32 bits. In the CR16B large model, only the lower 16 bits of these registers are

used, and these “short registers” are paired

together for 32-bit operations. In this mode,

the (RA, R13) register pair is used as the extended RA register, and address displacements relative to a single register are

supported with offsets of 0 and 14 bits in place

of the index addressing with these displacements.

– 32-bit registers are used.

0

1 – 16-bit registers are used (CR16B mode).

www.national.com 18

5.5 ADDRESSING MODES

The CR16C CPU core implements a load/store architecture, in which arithmetic and logical instructions operate on

register operands. Memory operands are made accessible

in registers using load and store instructions. For efficient

implementation of I/O-intensive embedded applications, the

architecture also provides a set of bit operations that operate on memory operands.

The load and store instructions support these addressing

modes: register/pair, immediate, relative, absolute, and index addressing. When register pairs are used, the lower bits

are in the lower index register and the upper bits are in the

higher index register. When the CFG.SR bit is clear, the 32bit registers R12, R13, RA, and SP are also treated as register pairs.

References to register pairs in assembly language use parentheses. With a register pair, the lower numbered register

pair must be on the right. For example,

jump (r5, r4)

load $4(r4,r3), (r6,r5)

load $5(r12), (r13)

The instruction set supports the following addressing

modes:

Register/Pair

Mode

Immediate

Mode

Relative Mode In relative mode, the operand is ad-

In register/pair mode, the operand is held

in a general-purpose register, or in a general-purpose register pair. For example,

the following instruction adds the contents of the low byte of register r1 to the

contents of the low byte of r2, and places

the result in the low byte register r2. The

high byte of register r2 is not modified.

ADDB R1, R2

In immediate mode, the operand is a con-

stant value which is encoded in the instruction. For example, the following

instruction multiplies the value of r4 by 4

and places the result in r4.

MULW $4, R4

dressed using a relative value (displacement) encoded in the instruction. This

displacement is relative to the current

Program Counter (PC), a general-purpose register, or a register pair.

In branch instructions, the displacement

is always relative to the current value of

the PC Register. For example, the following instruction causes an unconditional

branch to an address 10 ahead of the

current PC.

BR *+10

CP3BT10

In another example, the operand resides

in memory. Its address is obtained by

adding a displacement encoded in the instruction to the contents of register r5.

The address calculation does not modify

the contents of register r5.

LOADW 12(R5), R6

The following example calculates the ad-

dress of a source operand by adding a

displacement of 4 to the contents of a

register pair (r5, r4) and loads this operand into the register pair (r7, r6). r7 receives the high word of the operand, and

r6 receives the low word.

LOADD 4(r5, r4), (r7, r6)

Index Mode In index mode, the operand address is

calculated with a base address held in either R12 or R13. The CFG.SR bit must

be clear to use this mode.

For relative mode operands, the mem-

ory address is calculated by adding

the value of a register pair and a displacement to the base address. The

displacement can be a 14 or 20-bit unsigned value, which is encoded in the

instruction.

For absolute mode operands, the

memory address is calculated by adding a 20-bit absolute address encoded

in the instruction to the base address.

In the following example, the operand address is the sum of the displacement 4,

the contents of the register pair (r5,r4),

and the base address held in register r12.

The word at this address is loaded into

register r6.

LOADW [r12]4(r5, r4), r6

Absolute Mode In absolute mode, the operand is located

in memory, and its address is encoded in

the instruction (normally 20 or 24 bits).

For example, the following instruction

loads the byte at address 4000 into the

lower 8 bits of register r6.

LOADB 4000, r6

For additional information on the addressing modes, see the

CompactRISC CR16C Programmer's Reference Manual.

19 www.national.com

5.6 STACKS

A stack is a last-in, first-out data structure for dynamic storage of data and addresses. A stack consists of a block of

memory used to hold the data and a pointer to the top of the

CP3BT10

stack. As more data is pushed onto a stack, the stack grows

downward in memory. The CR16C supports two types of

stacks: the interrupt stack and program stacks.

5.6.1 Interrupt Stack

The processor uses the interrupt stack to save and restore

the program state during the exception handling. Hardware

automatically pushes this data onto the interrupt stack before entering an exception handler. When the exception

handler returns, hardware restores the processor state with

data popped from the interrupt stack. The interrupt stack

pointer is held in the ISP register.

5.6.2 Program Stack

The program stack is normally used by software to save and

restore register values on subroutine entry and exit, hold local and temporary variables, and hold parameters passed

between the calling routine and the subroutine. The only

hardware mechanisms which operate on the program stack

are the PUSH, POP, and POPRET instructions.

5.6.3 User and Supervisor Stack Pointers

To support multitasking operating systems, support is provided for two program stack pointers: a user stack pointer

and a supervisor stack pointer. When the PSR.U bit is clear,

the SP register is used for all program stack operations. This

is the default mode when the user/supervisor protection

mechanism is not used, and it is the supervisor mode when

protection is used.

When the PSR.U bit is set, the processor is in user mode,

and the USP register is used as the program stack pointer.

User mode can only be entered using the JUSR instruction,

which performs a jump and sets the PSR.U bit. User mode

is exited when an exception is taken and re-entered when

the exception handler returns. In user mode, the LPRD instruction cannot be used to change the state of processor

registers (such as the PSR).

5.7 INSTRUCTION SET

Table 6 lists the operand specifiers for the instruction set,

and Table 7 is a summary of all instructions. For each instruction, the table shows the mnemonic and a brief description of the operation performed.

In the mnemonic column, the lower-case letter “i” is used to

indicate the type of integer that the instruction operates on,

either “B” for byte or “W” for word. For example, the notation

ADDi for the “add” instruction means that there are two

forms of this instruction, ADDB and ADDW, which operate

on bytes and words, respectively.

Similarly, the lower-case string “cond” is used to indicate the

type of condition tested by the instruction. For example, the

notation Jcond represents a class of conditional jump instructions: JEQ for Jump on Equal, JNE for Jump on Not

Equal, etc. For detailed information on all instructions, see

the CompactRISC CR16C Programmer's Reference Manu-

al.

Table 6 Key to Operand Specifiers

Operand Specifier Description

abs Absolute address

disp

imm

Iposition Bit position in memory

Rbase Base register (relative mode)

Rdest Destination register

Rindex Index register

RPbase, RPbasex Base register pair (relative mode)

RPdest Destination register pair

RPlink Link register pair

Rposition Bit position in register

Displacement (numeric suffix

indicates number of bits)

Immediate operand (numeric suf-

fix indicates number of bits)

www.national.com 20

Rproc 16-bit processor register

Rprocd 32-bit processor register

RPsrc Source register pair

RPtarget Target register pair

Rsrc, Rsrc1, Rsrc2 Source register

Table 7 Instruction Set Summary

Mnemonic Operands Description

MOVi Rsrc/imm, Rdest Move

MOVXB Rsrc, Rdest Move with sign extension

MOVZB Rsrc, Rdest Move with zero extension

MOVXW Rsrc, RPdest Move with sign extension

MOVZW Rsrc, RPdest Move with zero extension

MOVD imm, RPdest Move immediate to register-pair

RPsrc, RPdest Move between register-pairs

ADD[U]i Rsrc/imm, Rdest Add

ADDCi Rsrc/imm, Rdest Add with carry

ADDD RPsrc/imm, RPdest Add with RP or immediate.

MACQWa Rsrc1, Rsrc2, RPdest Multiply signed Q15:

RPdest := RPdest + (Rsrc1 × Rsrc2)

MACSWa Rsrc1, Rsrc2, RPdest Multiply signed and add result:

RPdest := RPdest + (Rsrc1 × Rsrc2)

CP3BT10

MACUWa Rsrc1, Rsrc2, RPdest Multiply unsigned and add result:

RPdest := RPdest + (Rsrc1 × Rsrc2)

MULi Rsrc/imm, Rdest Multiply: Rdest(8) := Rdest(8) × Rsrc(8)/imm

Rdest(16) := Rdest(16) × Rsrc(16)/imm

MULSB Rsrc, Rdest Multiply: Rdest(16) := Rdest(8) × Rsrc(8)

MULSW Rsrc, RPdest Multiply: RPdest := RPdest(16) × Rsrc(16)

MULUW Rsrc, RPdest Multiply: RPdest := RPdest(16) × Rsrc(16);

SUBi Rsrc/imm, Rdest Subtract: (Rdest := Rdest - Rsrc/imm)

SUBD RPsrc/imm, RPdest Subtract: (RPdest := RPdest - RPsrc/imm)

SUBCi Rsrc/imm, Rdest Subtract with carry: (Rdest := Rdest - Rsrc/imm)

CMPi Rsrc/imm, Rdest Compare Rdest - Rsrc/imm

CMPD RPsrc/imm, RPdest Compare RPdest - RPsrc/imm

BEQ0i Rsrc, disp Compare Rsrc to 0 and branch if EQUAL

BNE0i Rsrc, disp Compare Rsrc to 0 and branch if NOT EQUAL

ANDi Rsrc/imm, Rdest Logical AND: Rdest := Rdest & Rsrc/imm

ANDD RPsrc/imm, RPdest Logical AND: RPdest := RPsrc & RPsrc/imm

ORi Rsrc/imm, Rdest Logical OR: Rdest := Rdest | Rsrc/imm

ORD RPsrc/imm, RPdest Logical OR: Rdest := RPdest | RPsrc/imm

Scond Rdest Save condition code as boolean

XORi Rsrc/imm, Rdest Logical exclusive OR: Rdest := Rdest ^ Rsrc/imm

XORD RPsrc/imm, RPdest Logical exclusive OR: Rdest := RPdest ^ RPsrc/imm

ASHUi Rsrc/imm, Rdest Arithmetic left/right shift

21 www.national.com

Table 7 Instruction Set Summary

Mnemonic Operands Description

CP3BT10

ASHUD Rsrc/imm, RPdest Arithmetic left/right shift

LSHi Rsrc/imm, Rdest Logical left/right shift

LSHD Rsrc/imm, RPdest Logical left/right shift

SBITi Iposition, disp(Rbase) Set a bit in memory

Iposition, disp(RPbase)

Iposition, (Rindex)disp(RPbasex)

Iposition, abs

Iposition, (Rindex)abs

CBITi Iposition, disp(Rbase) Clear a bit in memory

Iposition, disp(RPbase)

Iposition, (Rindex)disp(RPbasex)

Iposition, abs

Iposition, (Rindex)abs

(Because this instruction treats the destination as a readmodify-write operand, it not be used to set bits in writeonly registers.)

TBIT

TBITi

LPR Rsrc, Rproc Load processor register

LPRD RPsrc, Rprocd Load double processor register

SPR Rproc, Rdest Store processor register

SPRD Rprocd, RPdest Store 32-bit processor register

Bcond disp9 Conditional branch

BAL RPlink, disp24 Branch and link

BR disp9 Branch

Rposition/imm, Rsrc Test a bit in a register

Iposition, disp(Rbase)

Iposition, disp(RPbase)

Iposition, (Rindex)disp(RPbasex)

Iposition, abs

Iposition, (Rindex)abs

disp17

disp24

disp17

disp24

Test a bit in memory

EXCP vector Trap (vector)

Jcond RPtarget Conditional Jump to a large address

JAL RA, RPtarget, Jump and link to a large address

RPlink, RPtarget

JUMP RPtarget Jump

JUSR RPtarget Jump and set PSR.U

www.national.com 22

Table 7 Instruction Set Summary

Mnemonic Operands Description

RETX Return from exception