Page 1

DAQ

DAQ-STC™ Technical Reference Manual

System Timing Controller for Data Acquisition

DAQ-STC Technical Reference Manual

January 1999 Edition

Part Number 340934B-01

Page 2

Internet Support

E-mail: support@natinst.com

FTP Site: ftp.natinst.com

Web Address: http://www.natinst.com

Bulletin Board Support

BBS United States: 512 794 5422

BBS United Kingdom: 01635 551422

BBS France: 01 48 65 15 59

Fax-on-Demand Support

512 418 1111

Telephone Support (USA)

Tel: 512 795 8248

Fax: 512 794 5678

International Offices

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Brazil 011 288 3336,

Canada (Ontario) 905 785 0085, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 09 725 725 11,

France 01 48 14 24 24, Germany 089 741 31 30, Hong Kong 2645 3186, Israel 03 6120092, Italy 02 413091,

Japan 03 5472 2970, Korea 02 596 7456, Mexico 5 520 2635, Netherlands 0348 433466, Norway 32 84 84 00,

Singapore 2265886, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 200 51 51, Taiwan 02 377 1200,

United Kingdom 01635 523545

National Instruments Corporate Headquarters

6504 Bridge Point Parkway Austin, Texas 78730-5039 USA Tel: 512 794 0100

© Copyright 1995, 1998 National Instruments Corporation. All rights reserved.

Page 3

Important Information

Warranty

The DAQ-STC is warranted against defects in materials and workmanship for a period of one year from the date of

shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace

equipment that proves to be defect ive du ring t he wa rranty period . Th is warranty incl udes parts a nd l abor.

The media on which you receive National Instruments software are warranted not to fail to execute programming

instructions, due to defects in materials and work man ship, for a peri od of 90 d ays from da te o f sh ipm ent, as evi denced

by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not

execute programming instructions if National Instruments receives noti ce of su ch defect s d uring th e warranty perio d.

National Instruments does not warrant that the op eration of t he soft ware shall b e uni nterrup ted or erro r free.

A Return Material Authorization (RMA) number must b e ob tain ed fro m th e facto ry an d clearl y mark ed on t he outsi de

of the package before any equipment wil l be accepted for warranty work. National Instruments will pay the shippi ng costs

of returning to the owner parts which are covered by warran ty.

National Instruments believes that the information in this document is accurate. The document has been carefully

reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves

the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The

reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for

any damages arising out of or related to th is d ocum ent o r th e in form ation con tained in i t.

XCEPT AS SPECIFIED HEREIN

E

ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE

BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE

CUSTOMER

OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF

National Instruments will apply regardless of the form of action, wh ether in con tract or tort , incl udin g n egli gen ce.

Any action against National Instruments must be brought within one year after the cause of action accrues. National

Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty

provided herein does not cover damages, defects, malfuncti ons, or s ervice failur es caused by own er’s fai lure to fol low

the National Instruments installation, operation, or maintenance instructions; owner’s modification of the product;

owner’s abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties,

or other events outside reasonable control.

ATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS

. N

ATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS

, N

Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical,

including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without

the prior written consent of National Instruments Corporation.

USTOMER’S RIGHT TO RECOVER DAMAGES CAUSED

. C

. This limitation of the liability of

,

Trademarks

CVI™, DAQ-STC™, NI-DAQ™, and RTSI™ are trademarks of National Instruments Corporation.

Product and company names mentioned herein are trademarks or trade names of their respective companies.

WARNING REGARDING MEDICAL AND CLINICAL USE OF NATIONAL INSTRUMENTS PRODUCTS

National Instruments products are not designed with com ponent s and tes ting inten ded to ensure a l evel of reliab ilit y

suitable for use in treatment and diagnosis of humans. Applications of National Instruments products invol ving m edical

or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the

user or application designer. Any use or application of National Instruments products for or involving medical or clinical

treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards,

equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always

continue to be used when National Instruments products are being used . National Instrum ents product s are NOT intended

to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health

and safety in medical or clinical treatment.

Page 4

Contents

About This Manual

Organization of This Manual.........................................................................................xxiii

Conventions Used in This Manual.................................................................................xxv

National Instruments Documentation.......................................................................... ..xxvi

Related Documentation........................................... .......................................................xxvi

Customer Communication........................................................................ .....................xxvii

Chapter 1

Introduction

1.1 DAQ-STC Applications......................................... ............................................1-2

1.1.1 Analog Input Application...................................................................1-2

1.1.2 Analog Output Application ................................................................1-3

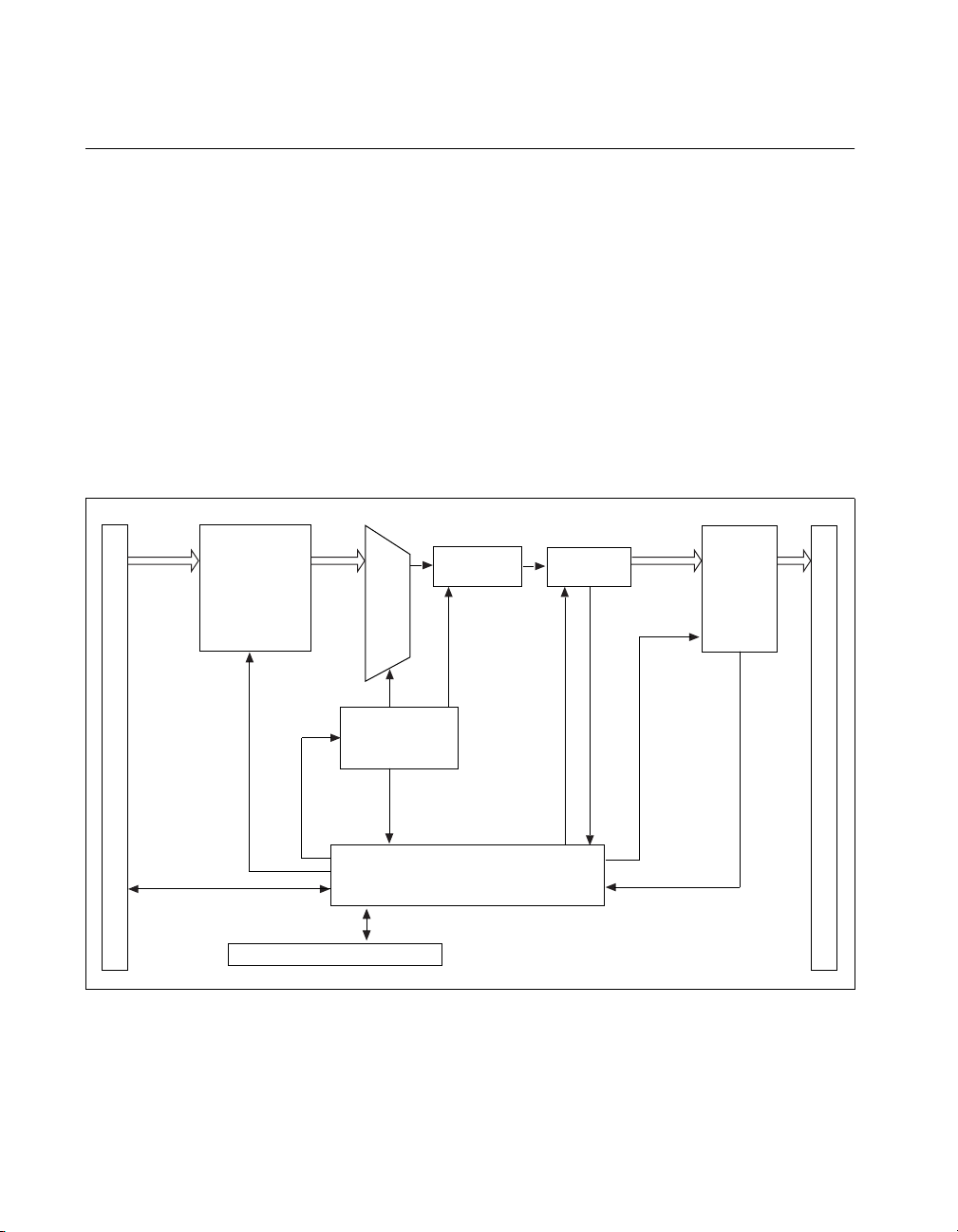

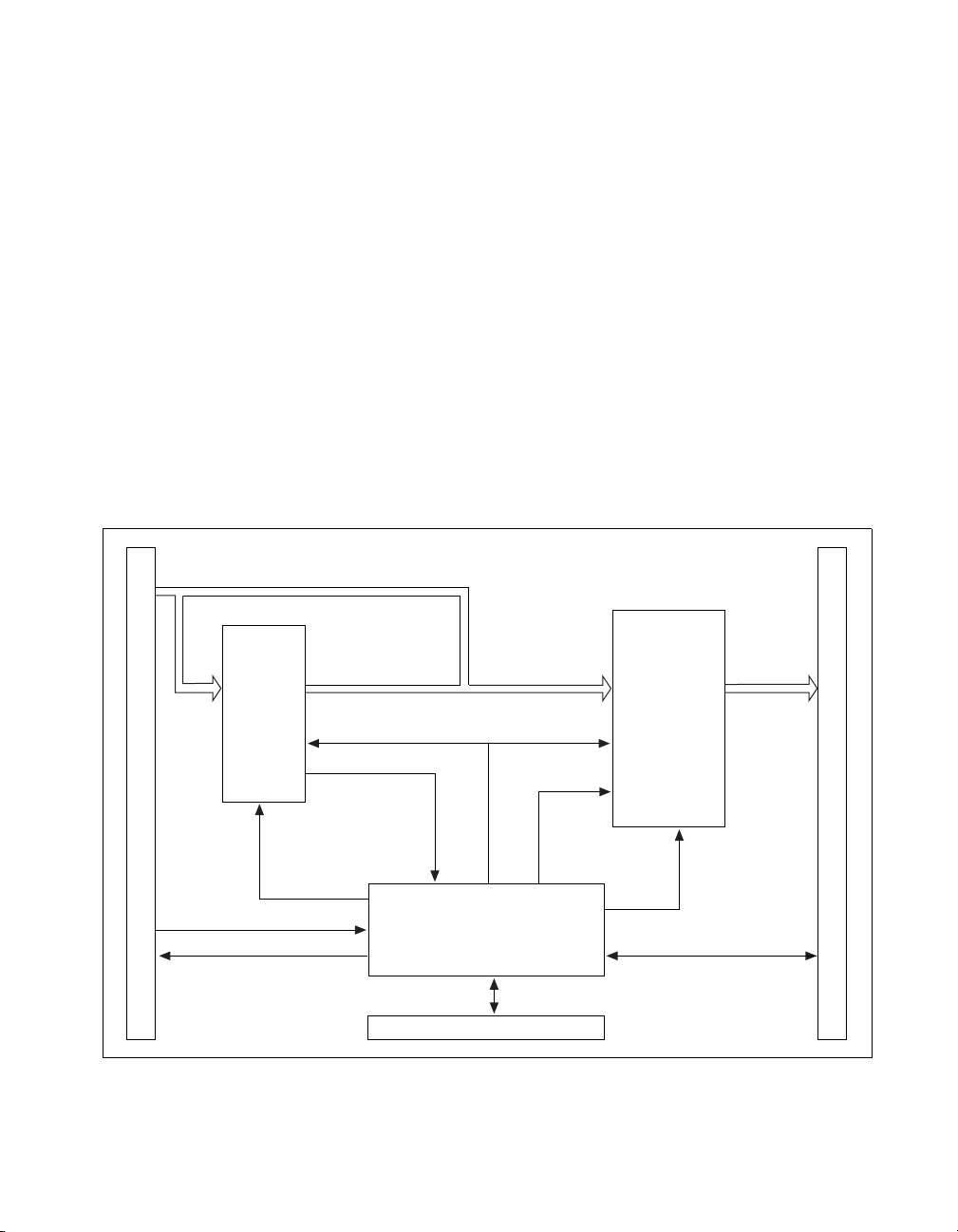

1.2 DAQ-STC Block Diagram.................................................................................1-4

Chapter 2

Analog Input Timing/Control

2.1 Overview............................................................................................................2-1

2.1.1 Programming the AITM.....................................................................2-1

2.2 Features ..............................................................................................................2-2

2.3 Simplified Model................................................................................................2-4

2.4 Analog Input Functions......................................................................................2-6

2.4.1 Low-Level Timing and Control..........................................................2-6

2.4.1.1 ADC Control................................... ..............................2-7

2.4.1.2 Data FIFO Control........................................................2-7

2.4.1.3 Configuration FIFO and External

2.4.1.4 CONVERT Timing.......................................................2-9

2.4.2 Scan-Level Timing and Control.........................................................2-11

2.4.2.1 Internal START Mode..................................................2-11

2.4.2.2 External START Mode.................................................2-12

2.4.3 Acquisition-Level Timing and Control..............................................2-14

2.4.3.1 Posttrigger Acquisition Mode.......................................2-14

2.4.3.2 Pretrigger Acquisition Mode ........................................2-14

2.4.3.3 Continuous Acquisition Mode......................................2-15

2.4.3.4 Staged Acquisition........................................................2-16

2.4.3.5 Master/Slave Trigger ....................................................2-16

2.4.4 Gating.................................................................................................2-16

2.4.4.1 Free-Run Gating Mode.................................................2-17

Multiplexer Control ................................................... 2-7

©

National Instruments Corporation v DAQ-STC Technical Reference Manual

Page 5

Contents

2.4.4.2 Halt-Gating Mode................................................ .........2-17

2.4.5 Single-Wire Mode..............................................................................2-18

2.5 Pin Locator Interface..........................................................................................2-19

2.6 Programming Information .................................................................................2-24

2.6.1 Register and Bitfield Programming Considerations .......................... 2-24

2.6.2 Windowing Registers.........................................................................2-25

2.6.3 Programming for an Analog Input Operation....................................2-25

2.6.3.1 Resetting.......................................................................2-26

2.6.3.2 Board Power-up Initialization ......................................2-27

2.6.3.3 Initialize Configuration Memory Output......................2-28

2.6.3.4 Board Environment Setup ............................................2-29

2.6.3.5 FIFO Request................................................................2-30

2.6.3.6 Hardware Gate Programming.......................................2-30

2.6.3.7 Software Gate Operation..............................................2-31

2.6.3.8 Trigger Signals .............................................................2-32

2.6.3.9 Number of Scans ..........................................................2-33

2.6.3.10 Start of Scan .................................................................2-34

2.6.3.11 End of Scan...................................................................2-37

2.6.3.12 Convert Signal..................................................... .........2-38

2.6.3.13 Enable Interrupts ..........................................................2-40

2.6.3.14 Arming..........................................................................2-41

2.6.3.15 Starting the Acquisition................................................2-41

2.6.3.16 Analog Input Program..................................................2-42

2.6.4 Single Scan.................................................... .....................................2-42

2.6.5 Change Scan Rate during an Acquisition ..........................................2-43

2.6.6 Staged Acquisition.............................................................................2-44

2.6.7 Master/Slave Operation Considerations.............................................2-45

2.6.8 Analog Input-Related Interrupts ........................................................2-46

2.6.9 Bitfield Descriptions ..........................................................................2-48

2.7 Timing Diagrams...............................................................................................2-84

2.7.1 Signal Definitions ...................................... ..................................... ...2-84

2.7.1.1 CONVERT_SRC............................................ ..............2-84

2.7.1.2 OUT_CLK....................................................................2-85

2.7.2 Basic Analog Input Timing................................................................2-86

2.7.3 Data FIFOs.........................................................................................2-88

2.7.4 Configuration Memory ......................................................................2-89

2.7.5 Maximum Rate Analog Input ............................................................2-91

2.7.6 External CONVERT Source..............................................................2-92

2.7.7 External Triggers................................................................................2-93

2.7.8 Trigger Output....................................................................................2-97

2.7.8.1 START1 and START2 Triggers ..................................2-97

2.7.8.2 START Trigger and SCAN_IN_PROG Assertion....... 2-100

DAQ-STC Technical Reference Manual vi

©

National Instruments Corporation

Page 6

Contents

2.7.8.3 SCAN_IN_PROG Deassertion.....................................2-103

2.7.8.4 STOP Trigger................................................................ 2-103

2.7.9 Counter Outputs................................... ..................................... ..........2-105

2.7.9.1 SC_TC ......................................... .................................2-105

2.7.9.2 SI_TC........................................................................ ....2-105

2.7.9.3 DIV_TC ........................................................................2-106

2.7.10 Macro-Level Analog Input Timing ....................................................2-106

2.7.11 External Gating...................................................................................2-109

2.8 Detailed Description...........................................................................................2-112

2.8.1 Internal Signals and Operation...........................................................2-113

2.8.2 Trigger Selection and Conditioning ...................................................2-119

2.8.2.1 Using Edge Detection...................................................2-122

2.8.2.2 Using Synchronization..................................................2-122

2.8.2.3 Trigger Signals..............................................................2-122

2.8.3 Analog Input Counters .......................................................................2-123

2.8.3.1 SC Counter....................................................... .............2-124

2.8.3.2 SC Control ................................................................ ....2-124

2.8.3.3 SI Counter.....................................................................2-126

2.8.3.4 SI Control......................................................................2-126

2.8.3.5 SI2 Counter...................................................................2-127

2.8.3.6 SI2 Control....................................................................2-127

2.8.3.7 DIV Counter .................................................................2-128

2.8.3.8 DIV Control..................................................................2-129

2.8.4 Interrupt Control.................................................................................2-130

2.8.5 Error Detection...................................................................................2-132

2.8.5.1 Overrun Error................................................................2-132

2.8.5.2 Overflow Error..............................................................2-132

2.8.5.3 SC_TC Error.................................................................2-132

2.8.6 Nominal Signal Pulsewidths...............................................................2-133

Chapter 3

Analog Output Timing/Control

3.1 Overview............................................................................................................3-1

3.1.1 Programming the AOTM ...................................................................3-2

3.2 Features ..............................................................................................................3-2

3.3 Simplified Model................................................................................................3-4

3.4 Analog Output Functions...................................................................................3-5

3.4.1 Primary Group Analog Output Modes...............................................3-5

3.4.1.1 DAQ-STC-Driven Analog Output................................3-6

3.4.1.2 CPU-Driven Analog Output .........................................3-6

3.4.1.3 DAQ-STC and CPU Conflict .......................................3-7

3.4.2 DAC Interface ..................................... ...............................................3-8

©

National Instruments Corporation vii DAQ-STC Technical Reference Manual

Page 7

Contents

3.4.3 Data Interfaces ...................................................................................3-8

3.4.3.1 FIFO Data Interface......................................................3-8

3.4.3.2 Serial Link Data Interface ............................................3-10

3.4.3.3 Unbuffered Data Interface......................................... ...3-11

3.4.4 Update Timing for Primary Group Analog Output............................3-11

3.4.4.1 Internal UPDATE.........................................................3-11

3.4.4.2 External UPDATE........................................................3-12

3.4.5 Buffer Timing and Control for Primary Analog Output.................... 3-12

3.4.5.1 Single-Buffer Mode ......................................................3-13

3.4.5.2 Continuous Mode .........................................................3-13

3.4.5.3 Waveform Staging........................................................3-14

3.4.5.4 Mute Buffers.................................................................3-15

3.4.5.5 Master/Slave Trigger....................................................3-15

3.4.6 Secondary Analog Output..................................................................3-16

3.5 Pin Interface.......................................................................................................3-16

3.6 Programming Information .................................................................................3-20

3.6.1 Programming for a Primary Analog Output Operation .....................3-20

3.6.1.1 Overview ......................................................................3-21

3.6.1.2 Resetting.......................................................................3-21

3.6.1.3 Board Power-up Initialization ......................................3-22

3.6.1.4 Trigger Signals .............................................................3-23

3.6.1.5 Number of Buffers........................................................3-24

3.6.1.6 Update Selection...........................................................3-26

3.6.1.7 Channel Select..............................................................3-28

3.6.1.8 LDAC Source and UPDATE Mode.............................3-29

3.6.1.9 Stop On Error ...............................................................3-29

3.6.1.10 FIFO Mode...................................................................3-29

3.6.1.11 Enable Interrupts ..........................................................3-30

3.6.1.12 Arming..........................................................................3-30

3.6.1.13 Starting the Waveform .................................................3-31

3.6.1.14 Primary Analog Output Program..................................3-31

3.6.2 Waveform Staging for Primary Analog Output.................................3-32

3.6.3 Changing Update Rate during an Output Operation for

Primary Analog Output Group ........................................................3-34

3.6.4 Master/Slave Operation Considerations for Primary Analog

Output Group ..................................................................................3-35

3.6.5 Primary Analog Output Group-Related Interrupts.............................3-35

3.6.6 Programming for a Secondary Analog Output Group Operation ...... 3-38

3.6.6.1 Overview ......................................................................3-38

3.6.6.2 Resetting.......................................................................3-38

3.6.6.3 Board Power-up Initialization ......................................3-39

3.6.6.4 Hardware Gate Programming.......................................3-39

3.6.6.5 Software Gate Operation..............................................3-40

DAQ-STC Technical Reference Manual viii

©

National Instruments Corporation

Page 8

Contents

3.6.6.6 Counting for Waveform Staging...................................3-40

3.6.6.7 Update Selection...........................................................3-40

3.6.6.8 Arming..........................................................................3-41

3.6.6.9 Secondary Analog Output Program..............................3-41

3.6.7 Waveform Staging for Secondary Analog Output .............................3-42

3.6.8 Changing Update Rate during an Output Operation for

Secondary Analog Output ...............................................................3-44

3.6.9 Master/Slave Operation Considerations for

Secondary Analog Output ...............................................................3-45

3.6.10 Secondary Analog Output-Related Interrupts....................................3-45

3.6.11 Bitfield Descriptions...........................................................................3-45

3.7 Timing Diagrams................................................................................................3-84

3.7.1 Signal Definitions......................................... ......................................3-84

3.7.1.1 UPDATE_SRC.............................................................3-85

3.7.1.1 UI2_SRC....................................................... ................3-85

3.7.1.1 OUT_CLK ....................................................................3-86

3.7.2 DAQ-STC-Driven Analog Output Timing.........................................3-86

3.7.3 CPU-Driven Analog Output Timing ..................................................3-88

3.7.4 DAQ-STC- and CPU-Driven Analog Output Timing........................3-90

3.7.5 Secondary Analog Output Timing......................................................3-93

3.7.6 Decoded Signal Timing......................................................................3-94

3.7.7 Local Buffer Mode Timing ................................................................3-96

3.7.8 Unbuffered Data Interface Timing.....................................................3-98

3.7.9 Maximum Update Rate Timing..........................................................3-101

3.7.10 External Trigger Timing .....................................................................3-102

3.7.11 Trigger Output....................................................................................3-104

3.7.11.1 START1 Trigger................................ ...........................3-104

3.7.12 Counter Outputs................................... ..................................... ..........3-107

3.7.12.1 BC_TC..........................................................................3-107

3.7.12.2 UC_TC................................. ..................................... ....3-108

3.8 Detailed Description...........................................................................................3-108

3.8.1 Internal Signals and Operation...........................................................3-109

3.8.2 Trigger Selection and Conditioning ...................................................3-114

3.8.2.1 Using Edge Detection...................................................3-116

3.8.2.2 Using Synchronization..................................................3-116

3.8.2.3 Trigger Signals..............................................................3-116

3.8.3 Analog Output Counters.....................................................................3-117

3.8.3.1 UI Counter ........................... .........................................3-117

3.8.3.2 UI Control.............................................................. .......3-118

3.8.3.3 UC Counter...................................................................3-118

3.8.3.4 UC Control....................................................................3-119

3.8.3.5 BC Counter ...................................................................3-120

3.8.3.6 BC Control....................................................................3-120

©

National Instruments Corporation ix DAQ-STC Technical Reference Manual

Page 9

Contents

3.8.3.7 UI2 Counter..................................................................3-121

3.8.3.8 UI2 Control...................................................................3-121

3.8.4 Interrupt Control .......................................................................... ......3-122

3.8.5 Error Detection...................................................................................3-122

3.8.5.1 Overrun Error ...............................................................3-122

3.8.5.2 BC_TC Error................................................................3-123

3.8.5.3 BC_TC Trigger Error...................................................3-123

3.8.5.4 UI2_TC Error ...............................................................3-123

3.8.6 Output Control .......................... ..................................... ....................3-123

3.8.7 Nominal Signal Pulsewidths..............................................................3-124

Chapter 4

General-Purpose Counter/Timer

4.1 Overview............................................................................................................4-1

4.1.1 Programming the GPCT.....................................................................4-1

4.2 Features..............................................................................................................4-1

4.3 Simplified Model...............................................................................................4-2

4.4 Counter/Timer Functions...................................................................................4-3

4.4.1 Event Counting ..................................................................................4-3

4.4.1.1 Simple Event Counting.................................................4-4

4.4.1.2 Simple Gated-Event Counting......................................4-4

4.4.1.3 Buffered Noncumulative Event Counting.................... 4-4

4.4.1.4 Buffered Cumulative Event Counting.......................... 4-5

4.4.1.5 Relative Position Sensing.............................................4-6

4.4.2 Time Measurement ............................................................................4-6

4.4.2.1 Single-Period Measurement .........................................4-6

4.4.2.2 Single-Pulsewidth Measurement..................................4-7

4.4.2.3 Buffered Period Measurement......................................4-7

4.4.2.4 Buffered Semiperiod Measurement..............................4-8

4.4.2.5 Buffered Pulsewidth Measurement .............................. 4-9

4.4.3 Pulse Generation ................................................................................4-9

4.4.3.1 Single Pulse Generation ...............................................4-9

4.4.3.2 Single Triggered Pulse Generation...............................4-10

4.4.3.3 Retriggerable Single Pulse Generation.........................4-11

4.4.3.4 Buffered Retriggerable Single Pulse Generation ......... 4-11

4.4.4 Pulse-Train Generation ......................................................................4-12

4.4.4.1 Continuous Pulse-Train Generation.............................4-12

4.4.4.2 Buffered Static Pulse-Train Generation ....................... 4-13

4.4.4.3 Buffered Pulse-Train Generation .................................4-14

4.4.4.4 Frequency Shift Keying (FSK).....................................4-14

4.4.4.5 Pulse Generation for ETS.............................................4-15

4.5 Pin Interface.......................................................................................................4-16

DAQ-STC Technical Reference Manual x

©

National Instruments Corporation

Page 10

Contents

4.6 Programming Information..................................................................................4-17

4.6.1 Programming for a GPCT Operation .................................................4-17

4.6.1.1 Overview.......................................................................4-17

4.6.1.2 Notation ........................................................................4-18

4.6.1.3 Resetting .......................................................................4-18

4.6.1.4 Arming..........................................................................4-18

4.6.1.5 Simple Event Counting.................................................4-19

4.6.1.6 Buffered Event Counting. .............................................4-20

4.6.1.7 Relative Position Sensing ............................................. 4-23

4.6.1.8 Single-Period and Pulsewidth Measurement ................4-24

4.6.1.9 Buffered Period, Semiperiod, and Pulsewidth

Measurement..............................................................4-26

4.6.1.10 Pulse and Continuous Pulse-Train Generation .............4-28

4.6.1.11 Frequency Shift Keying................................................4-31

4.6.1.12 Pulse-Train Generation for ETS ...................................4-33

4.6.1.13 Reading the Counter Contents......................................4-34

4.6.1.14 Reading the Hardware Save Registers..........................4-34

4.6.1.15 Enabling the General Purpose

Counter/Timer Output Pin .........................................4-35

4.6.2 Bitfield Descriptions...........................................................................4-35

4.7 Timing Diagrams................................................................................................4-53

4.7.1 CTRSRC Minimum Period and Minimum Pulsewidth......................4-55

4.7.2 CTRSRC to CTROUT Delay.............................................................4-55

4.7.3 G_GATE Minimum Pulsewidth.........................................................4-56

4.7.4 CTRGATE to CTROUT Delay..........................................................4-57

4.7.5 CTRGATE to INTERRUPT...............................................................4-57

4.7.6 CTRGATE Setup................................................................................4-58

4.7.7 CTR_U/D Setup .................................................................................4-59

4.8 Detailed Description...........................................................................................4-61

4.8.1 Internal Signals and Operation...........................................................4-62

4.8.2 G_SOURCE Selection and Conditioning...........................................4-63

4.8.3 G_GATE Selection and Conditioning................................................4-64

4.8.4 G_UP_DOWN Control ................................... .. .................................4-64

4.8.5 G_OUT Conditioning and Routing ....................................................4-65

4.8.6 G_CONTROL Conditioning..............................................................4-67

4.8.7 Gate Actions.......................................................................................4-67

4.8.7.1 START/STOP on G_CONTROL.................................4-68

4.8.7.2 Save on G_GATE.........................................................4-68

4.8.7.3 Reload on G_CONTROL .............................................4-68

4.8.7.4 UP/DOWN on G_CONTROL......................................4-69

4.8.7.5 Generate Interrupt on G_GATE....................................4-69

4.8.7.6 Change Output Polarity on G_GATE...........................4-69

4.8.7.7 Select Load Register on G_CONTROL .......................4-69

©

National Instruments Corporation xi DAQ-STC Technical Reference Manual

Page 11

Contents

4.8.7.8 Disarm Counter on G_CONTROL...............................4-70

4.8.7.9 Switch Load Bank Selection on G_CONTROL........... 4-70

4.8.8 Interrupt Control .......................................................................... ......4-70

4.8.9 PFI Selection......................................................................................4-70

4.8.10 Error Detection...................................................................................4-71

4.8.10.1 Gate Acknowledge Latency Error................................4-71

4.8.10.2 Stale Data Error............................................................4-71

4.8.10.3 Permanent Stale Data Error..........................................4-71

4.8.10.4 TC Latency Error..........................................................4-72

4.8.11 Detailed Operation by Application ....................................................4-72

4.8.11.1 Simple Event Counting.................................................4-72

4.8.11.2 Simple Gated-Event Counting......................................4-73

4.8.11.3 Buffered Noncumulative-Event Counting.................... 4-74

4.8.11.4 Buffered Cumulative-Event Counting..........................4-74

4.8.11.5 Relative-Position Sensing.............................................4-75

4.8.11.6 Single-Period Measurement .........................................4-76

4.8.11.7 Single Pulsewidth Measurement ..................................4-77

4.8.11.8 Buffered Period Measurement......................................4-78

4.8.11.9 Buffered Semiperiod Measurement..............................4-79

4.8.11.10 Buffered Pulsewidth Measurement ..............................4-80

4.8.11.11 Single Pulse Generation ...............................................4-81

4.8.11.12 Single-Triggered Pulse Generation ..............................4-82

4.8.11.13 Retriggerable Single Pulse Generation......................... 4-83

4.8.11.14 Continuous Pulse-Train Generation .............................4-84

4.8.11.15 Buffered Pulse-Train Generation .................................4-85

4.8.11.16 Frequency Shift Keying................................................4-86

4.8.11.17 Pulse Generation for ETS.............................................4-87

Chapter 5

Programmable Function Inputs

5.1 Overview............................................................................................................5-1

5.2 Features..............................................................................................................5-1

5.3 Pin Interface.......................................................................................................5-2

5.4 Programming Information .................................................................................5-5

5.4.1 Programming the PFI Pins.................................................................5-5

5.4.2 Bitfield Descriptions ..........................................................................5-6

5.5 Detailed Description ..........................................................................................5-7

Chapter 6

RTSI Trigger

6.1 Overview............................................................................................................6-1

6.2 Features..............................................................................................................6-1

DAQ-STC Technical Reference Manual xii

©

National Instruments Corporation

Page 12

6.3 Pin Interface .......................................................................................................6-1

6.4 Programming Information..................................................................................6-2

6.5 Detailed Description...........................................................................................6-6

Chapter 7

Digital I/O

7.1 Overview............................................................................................................7-1

7.2 Features ..............................................................................................................7-1

7.3 Simplified Model................................................................................................7-1

7.4 Overview of DIO Functions...............................................................................7-2

7.5 Pin Interface .......................................................................................................7-6

7.6 Programming Information..................................................................................7-7

7.7 Timing Diagrams................................................................................................7-15

7.8 Detailed Description...........................................................................................7-17

Contents

6.4.1 Programming the RTSI Interface .......................................................6-2

6.4.2 Bitfield Descriptions...........................................................................6-3

7.4.1 Parallel Mode......................................................................................7-2

7.4.1.1 Parallel Input.............................. ...................................7-3

7.4.1.2 Parallel Output..............................................................7-3

7.4.2 Serial Mode ........................................................................................7-4

7.4.2.1 Serial Input.................................................... ................7-4

7.4.2.2 Serial Output.................................................................7-4

7.4.2.3 Serial I/O..................................................................... ..7-5

7.6.1 Windowed Mode Register Access Example ......................................7-7

7.6.2 Programming the Digital Interface.....................................................7-8

7.6.2.1 Parallel Digital I/O........................................................7-9

7.6.2.2 Hardware-Controlled Serial Digital I/O........................7-10

7.6.2.3 Software-Controlled Serial Digital I/O.........................7-12

7.6.2.4 Programming the Control Lines ...................................7-12

7.6.2.5 Reading the Status Lines...............................................7-13

7.6.3 Bitfield Descriptions...........................................................................7-13

7.7.1 Serial Input Timing.............................................................................7-15

7.7.2 Serial Output Timing..........................................................................7-16

Chapter 8

Interrupt Control

8.1 Overview............................................................................................................8-1

8.2 Features ..............................................................................................................8-1

8.3 Pin Interface .......................................................................................................8-2

8.4 Programming Information..................................................................................8-3

8.4.1 Programming the Interrupt Interface..................................................8-3

8.4.1.1 Interrupt Output Polarity...............................................8-3

©

National Instruments Corporation xiii DAQ-STC Technical Reference Manual

Page 13

Contents

8.4.2 Interrupt Handling..................................................................... .........8-5

8.4.3 Bitfield Descriptions ..........................................................................8-12

8.5 Interrupt Conditions......................................................... ..................................8-15

Chapter 9

Bus Interface

9.1 Overview............................................................................................................9-1

9.2 Features..............................................................................................................9-1

9.2.1 Pin Interface.......................................................................................9-1

9.3 Programming Information .................................................................................9-3

9.3.1 Programming the Write Strobes.........................................................9-4

9.3.2 Bitfield Descriptions ..........................................................................9-4

9.4 Timing Diagrams...............................................................................................9-5

Chapter 10

8.4.1.2 Interrupt Output Select and Enable ..............................8-3

8.4.1.3 Pass-Through Interrupt.................................................8-4

8.4.2.1 Interrupt Program .........................................................8-6

8.4.2.2 Interrupt Group A.........................................................8-6

8.4.2.3 Interrupt Group B.........................................................8-9

Miscellaneous Functions

10.1 Overview............................................................................................................10-1

10.2 Features..............................................................................................................10-1

10.3 Clock Distribution................................................ ..................................... .........10-2

10.4 Frequency Output...............................................................................................10-3

10.5 Analog Trigger...................................................................................................10-3

10.6 Test Mode .......................................................... ................................................10-6

10.7 Pin Interface.......................................................................................................10-9

10.8 Programming Information .................................................................................10-10

10.8.1 Programming Clock Distribution.......................................................10-10

10.8.2 Programming FOUT ..........................................................................10-12

10.8.3 Programming Analog Trigger............................................................10-12

10.8.4 Bitfield Descriptions ..........................................................................10-12

Appendix A

Specifications

Appendix B

Register Information

DAQ-STC Technical Reference Manual xiv

©

National Instruments Corporation

Page 14

Appendix C

Pin List

Appendix D

DAQ-STC Revision History

Appendix E

Customer Communication

Glossary

Index

Figures

Figure 1-1. Analog Input Application......................................................................1-2

Figure 1-2. Analog Output Application ...................................................................1-3

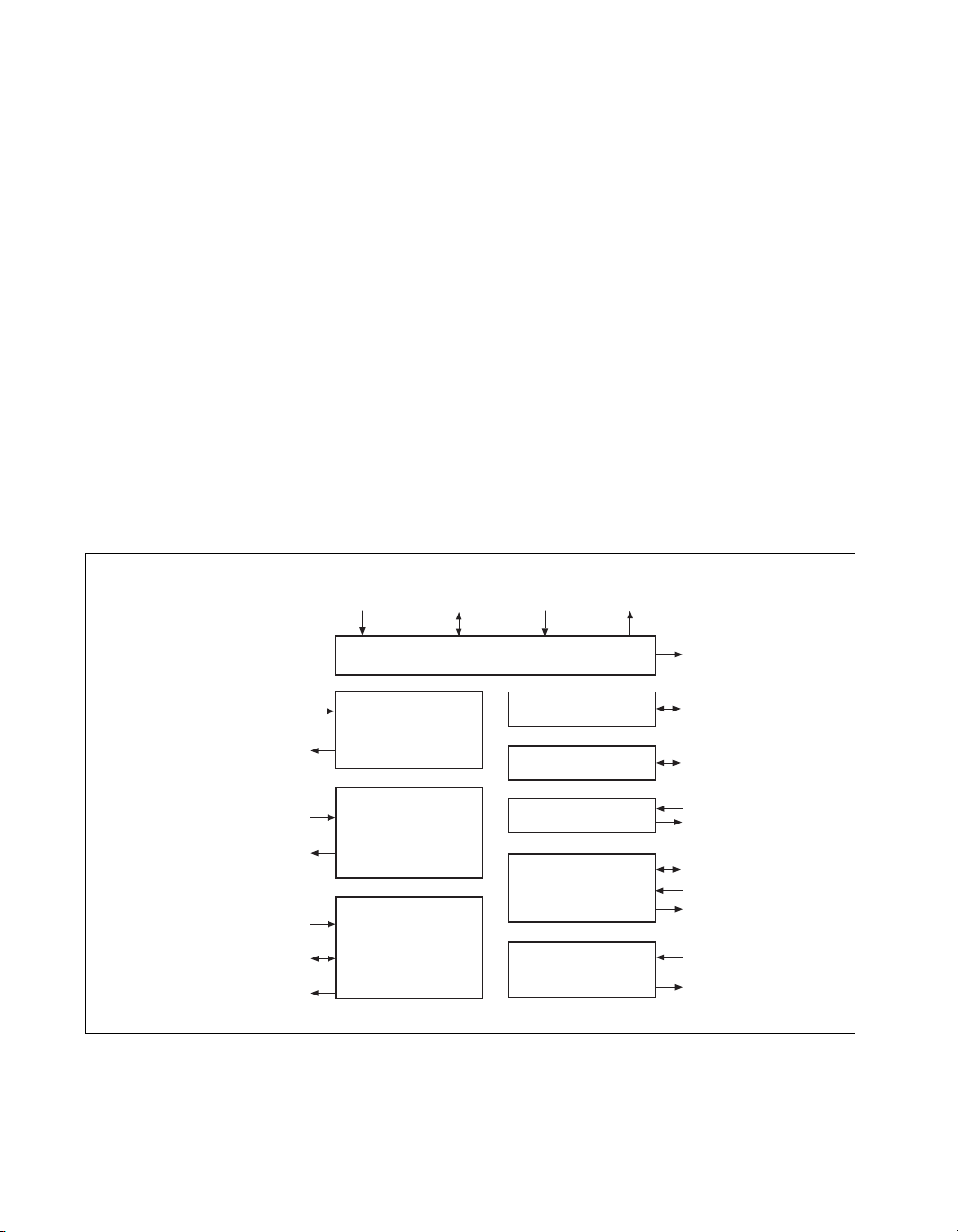

Figure 1-3. DAQ-STC Block Diagram ....................................................................1-4

Contents

Figure 2-1. Typical Analog Input Waveform .......................................................... 2-4

Figure 2-2. AITM Simplified Model .......................................................................2-5

Figure 2-3. ADC Control ............................................. ............................................2-7

Figure 2-4. Configuration FIFO Control..................................................................2-8

Figure 2-5. External Multiplexer Control ................................................................2-9

Figure 2-6. Internal CONVERT Timing..................................................................2-10

Figure 2-7. External CONVERT Timing.................................................................2-11

Figure 2-8. Internal START.....................................................................................2-12

Figure 2-9. External START....................................................................................2-13

Figure 2-10. SI Special Trigger Delay ....................................................................... 2-13

Figure 2-11. Posttrigger Acquisition Mode ...............................................................2-14

Figure 2-12. Pretrigger Acquisition Mode.................................................................2-15

Figure 2-13. Free-Run Gating Mode..........................................................................2-17

Figure 2-14. Halt-Gating Mode..................................................................................2-18

Figure 2-15. Single-Wire Mode .................................................................................2-18

Figure 2-16. Basic Analog Input Timing ...................................................................2-86

Figure 2-17. Data FIFO Timing.................................................................................2-88

Figure 2-18. Configuration Memory Timing.............................................................2-89

Figure 2-19. Maximum Rate Analog Input Timing...................................................2-92

Figure 2-20. External CONVERT_SRC Timing .......................................................2-93

Figure 2-21. External Trigger Timing, Asynchronous Level ....................................2-94

©

National Instruments Corporation xv DAQ-STC Technical Reference Manual

Page 15

Contents

Figure 2-22. External Trigger Timing, Asynchronous Edge.....................................2-94

Figure 2-23. External Trigger Timing , Synchronous Level,

Internal CONVERT Mode.................................................................... 2-95

Figure 2-24. External Trigger Timing , Synchronous Edge,

Internal CONVERT Mode.................................................................... 2-95

Figure 2-25. External Trigger Timing , Synchronous Level,

External CONVERT Mode...................................................................2-96

Figure 2-26. External Trigger Timing , Synchronous Edge,

External CONVERT Mode...................................................................2-96

Figure 2-27. START1 Delays, Synchronous Mode, Internal CONVERT ................ 2-98

Figure 2-28. START2 Delays, Synchronous Mode, Internal CONVERT ............... 2-98

Figure 2-29. START1 Delays, Synchronous Mode, External CONVERT ............... 2-98

Figure 2-30. START2 Delays, Synchronous Mode, External CONVERT ............... 2-99

Figure 2-31. START1 Delays, Asynchronous Mode ................................................ 2-99

Figure 2-32. START2 Delays, Asynchronous Mode ................................................ 2-100

Figure 2-33. START Delays, Internal CONVERT ...................................................2-101

Figure 2-34. START Delays, External CONVERT ..................................................2-102

Figure 2-35. SCAN_IN_PROG Deassertion .................................................... .........2-103

Figure 2-36. STOP Delay, Synchronous Mode.........................................................2-104

Figure 2-37. STOP Delay, Asynchro nous Mod e.......................................................2-104

Figure 2-38. SC_TC Delay.......................................... ..................................... .........2-105

Figure 2-39. SI_TC Delay .........................................................................................2-105

Figure 2-40. DIV_TC Delay......................................................................................2-106

Figure 2-41. Interval Scanning Mode Timing ...........................................................2-106

Figure 2-42. Free-Run Gating Mode Timing, Internal CONVERT ..........................2-109

Figure 2-43. Free-Run Gating Mode Timing, External CONVERT.........................2-110

Figure 2-44. Halt-Gating Mode Timing, Internal CONVERT..................................2-111

Figure 2-45. AITM Block Diagram...........................................................................2-112

Figure 2-46. START and STOP Routing Logic........................................................2-120

Figure 2-47. START1 and START2 Routing Logic .................................................2-120

Figure 2-48. EXT_GATE Routing Logic..................................................................2-121

Figure 2-49. SC Control Circuit State Transitions ....................................................2-125

Figure 2-50. SI Control Circuit State Transitions......................................................2-127

Figure 2-51. SI2 Control Circuit State Transitions....................................................2-128

Figure 2-52. DIV Control Circuit State Transitions ..................................................2-130

Figure 3-1. AOTM Simplified Mode.......................................................................3-4

Figure 3-2. DAQ-STC-Driven Analog Output.................................... ....................3-6

Figure 3-3. CPU-Driven Analog Output .................................................................3-7

Figure 3-4. DAQ-STC and CPU Conflict................................................................3-7

Figure 3-5. FIFO Data Interface ..............................................................................3-9

Figure 3-6. Local Buffer Mode................................................................................3-10

Figure 3-7. Serial Link Data Interface.....................................................................3-10

DAQ-STC Technical Reference Manual xvi

©

National Instruments Corporation

Page 16

Contents

Figure 3-8. Unbuffered Data Interface.....................................................................3-11

Figure 3-9. Internal UPDATE Timing.....................................................................3-12

Figure 3-10. External UPDATE Timing....................................................................3-12

Figure 3-11. Single-Buffer Mode...............................................................................3-13

Figure 3-12. Continuous Mode ..................................................................................3-14

Figure 3-13. Mute Buffers......................................................... .................................3-15

Figure 3-14. DAQ-STC-Driven Analog Output Timing............................................3-87

Figure 3-15. CPU-Driven Analog Output Timing .....................................................3-89

Figure 3-16. Analog Output Contention Timing, Case A..........................................3-91

Figure 3-17. Analog Output Contention Timing, Case B..........................................3-92

Figure 3-18. Secondary Analog Output Timing ........................................................3-93

Figure 3-19. Decoded Signal Timing.........................................................................3-95

Figure 3-20. Local Buffer Mode Timing ...................................................................3-97

Figure 3-21. Unbuffered Data Interface Timing ........................................................3-99

Figure 3-22. Maximum Update Rate Timing.............................................................3-101

Figure 3-23. External Trigger, Asynchronous Level .................................................3-102

Figure 3-24. External Trigger, Asynchronous Edge.................................................3-102

Figure 3-25. External Trigger, Synchronous Level, Internal UPDATE Mode.........3-103

Figure 3-26. External Trigger, Synchronous Edge, Internal UPDATE Mode..........3-103

Figure 3-27. External Trigger, Synchronous Level, Ex ternal UPDATE Mode........3-103

Figure 3-28. External Trigger, Synchronous Edge, Ex ternal UPDATE Mode.........3-103

Figure 3-29. START1 Delays, Synchronous Mode, Internal UPDATE....................3-105

Figure 3-30. START1 Delays, Synchronous Mode, External UPDATE...................3-106

Figure 3-31. START1 Delays, Asynchronous Mode.................................................3-107

Figure 3-32. BC_TC Delay........................................................................................3-107

Figure 3-33. UC_TC Delay........................................................................................3-108

Figure 3-34. AOTM Block Diagram..........................................................................3-109

Figure 3-35. START1 Routing Logic........................................................................3-115

Figure 3-36. EXT_GATE and EXT_GATE2 Routing Logic ....................................3-115

Figure 3-37. UI Control Circuit State Transitions .....................................................3-118

Figure 3-38. UC Control Circuit State Transitions ....................................................3-119

Figure 3-39. BC Control Circuit State Transitions ....................................................3-121

Figure 4-1. General-Purpose Counter/Timer Simplified Model..............................4-2

Figure 4-2. Simple Event Counting .........................................................................4-4

Figure 4-3. Simple Gated-Event Counting...............................................................4-4

Figure 4-4. Buffered Noncumulative Event Counting.............................................4-5

Figure 4-5. Cumulative Event Counting ..................................................................4-5

Figure 4-6. Relative Position Sensing......................................................................4-6

Figure 4-7. Single-Period Measurement ..................................................................4-7

Figure 4-8. Single-Pulsewidth Measurement................................... ........................4-7

Figure 4-9. Buffered Period Measurement...............................................................4-8

Figure 4-10. Buffered Semiperiod Measurement.......................................................4-8

©

National Instruments Corporation xvii DAQ-STC Technical Reference Manual

Page 17

Contents

Figure 4-11. Buffered Pulsewidth Measurement.......................................................4-9

Figure 4-12. Single Pulse Generation........................................................................4-10

Figure 4-13. Single Triggered-Pulse Generation.......................................................4-10

Figure 4-14. Retriggerable Single Pulse Generation .................................................4-11

Figure 4-15. Buffered Retriggerable Single Pulse Generation.................................. 4-12

Figure 4-16. Continuous Pulse-Train Generation......................................................4-13

Figure 4-17. Buffered Static Pulse-Train Generation................................................4-13

Figure 4-18. Buffered Pulse-Train Generation..........................................................4-14

Figure 4-19. Frequency Shift Keying ........................................................................4-15

Figure 4-20. Pulse Generation for ETS .....................................................................4-15

Figure 4-21. CTRSRC Minimum Period and Minimum Pulsewidth ........................4-55

Figure 4-22. CTRSRC to CTROUT Timing .............................................................4-56

Figure 4-23. G_GATE Minimum Pulsewidth ................................. ..........................4-56

Figure 4-24. CTRGATE to CTROUT Timing ..........................................................4-57

Figure 4-25. CTRGATE to INTERRUPT Timing ....................................................4-57

Figure 4-26. CTRGATE Setup Timing, Internal Timing Mode................................4-58

Figure 4-27. CTRGATE Setup Timing, External Timing Mode...............................4-59

Figure 4-28. CTR_U/D Setup Timing, Internal Timing Mode .................................4-60

Figure 4-29. CTR_U/D Setup Timing, External Timing Mode ................................4-60

Figure 4-30. General-Purpose Counter/Timer Model ...............................................4-61

Figure 4-31. G_SOURCE Generation ........................................................... ............4-72

Figure 4-32. Simple Event Counting.........................................................................4-73

Figure 4-33. Simple Gated-Event Counting ..............................................................4-73

Figure 4-34. Buffered Noncumulative-Event Counting............................................ 4-74

Figure 4-35. Buffered Cumulative-Event Counting ..................................................4-75

Figure 4-36. Relative-Position Sensing ......................................................... ... .........4-75

Figure 4-37. Single-Period Measurement..................................................................4-76

Figure 4-38. Single Pulsewidth Measurement.................................................. ... ......4-77

Figure 4-39. Buffered Period Measurement ..............................................................4-78

Figure 4-40. Buffered Semiperiod Measurement ......................................................4-79

Figure 4-41. Buffered Pulsewidth Measurement.......................................................4-80

Figure 4-42. Single Pulse Generation........................................................................4-81

Figure 4-43. Single-Triggered Pulse Generation.......................................................4-82

Figure 4-44. Retriggerable Single Pulse Generation .................................................4-83

Figure 4-45. Continuous Pulse-Train Generation......................................................4-84

Figure 4-46. Buffered Pulse-Train Generation..........................................................4-85

Figure 4-47. Frequency Shift Keying ........................................................................4-86

Figure 4-48. Pulse Generation for ETS .....................................................................4-87

Figure 7-1. DIO Simplified Model ..........................................................................7-2

Figure 7-2. Parallel Input................................... ..................................... .................7-3

Figure 7-3. Parallel Output ...................................... .................................... ............7-3

Figure 7-4. DIO Serial Input....................................................................................7-4

DAQ-STC Technical Reference Manual xviii

©

National Instruments Corporation

Page 18

Tables

Contents

Figure 7-5. Serial Output..........................................................................................7-5

Figure 7-6. Serial I/O ...............................................................................................7-5

Figure 7-7. Serial Input Timing ...............................................................................7-16

Figure 7-8. Serial Output Timing.............................................................................7-16

Figure 9-1. Intel Bus Interface Read Timing ...........................................................9-6

Figure 9-2. Intel Bus Interface Write Timing ..........................................................9-6

Figure 9-3. Motorola Bus Interface Read Timing....................................................9-7

Figure 9-4. Motorola Bus Interface Write Timing...................................................9-8

Figure 10-1. Clock Distribution ......................................................... ........................10-2

Figure 10-2. Low-Window Mode ..............................................................................10-4

Figure 10-3. High-Window Mode..............................................................................10-4

Figure 10-4. Middle-Window Mode..........................................................................10-5

Figure 10-5. High-Hysteresis Mode...........................................................................10-5

Figure 10-6. Low-Hysteresis Mode ...........................................................................10-6

Figure 10-7. Test Mode Internal Gate Tree ...............................................................10-7

Table 2-1. Pin Interface .........................................................................................2-19

Table 2-2. CONVERT_SRC Reference Pin Selection ..........................................2-84

Table 2-3. Basic Analog Input Timing ..................................................................2-86

Table 2-4. Configuration Memory Timing ............................................................2-90

Table 2-5. External Analog Input Timing .............................................................2-96

Table 2-6. START1 and START2 Timing, Synchronous Mode ...........................2-99

Table 2-7. START1 and START2 Timing , Asynchronous Mode .........................2-100

Table 2-8. Interval Scanning Mode Timing ...........................................................2-107

Table 2-9. Internal Signals .....................................................................................2-113

Table 2-10. PFI Selectors..........................................................................................2-121

Table 2-11. Analog Input Interrupts .........................................................................2-131

Table 2-12. Analog Input Nominal Signal Widths ..................................................2-133

Table 3-1. Pin Interface .........................................................................................3-16

Table 3-2. UPDATE_SRC Reference Pin Selection .............................................3-85

Table 3-3. UI2_SRC Reference Pin Selection .......................................................3-85

Table 3-4. DAQ-STC-Driven Analog Output Timing ...........................................3-87

Table 3-5. External Trigger Timing........................................................................3-104

Table 3-6. Internal Signals .....................................................................................3-109

Table 3-7. PFI Selectors .........................................................................................3-115

Table 3-8. Analog Output Interrupts ......................................................................3-122

Table 3-9. Analog Output Nominal Signal Widths ...............................................3-124

©

National Instruments Corporation xix DAQ-STC Technical Reference Manual

Page 19

Contents

Table 4-1. CTRSRC Reference Pin Selection........................................................4-53

Table 4-2. CTRGATE Reference Pin Selection ....................................................4-54

Table 4-3. CTR_U/D Reference Pin Selection ......................................................4-54

Table 4-4. Internal Signal Description ..................................................................4-62

Table 4-5. G_SOURCE Selection..........................................................................4-63

Table 4-6. G_SOURCE Conditioning....................................................................4-63

Table 4-7. G_GATE Selection ...............................................................................4-64

Table 4-8. G_GATE Conditioning.........................................................................4-64

Table 4-9. G_UP_DOWN Modes .........................................................................4-65

Table 4-10. G_OUT Mode .......................................................................................4-65

Table 4-11. G_OUT Polarity....................................................................................4-65

Table 4-12. G_OUT0/RTSI_IO Selection................................................................4-66

Table 4-13. G_OUT1/DIV_TC_OUT Selection......................................................4-66

Table 4-14. G_CONTROL Conditioning.................................................................4-67

Table 4-15. Gate Actions .........................................................................................4-67

Table 4-16. START/STOP Modes for Edge Gating ................................................4-68

Table 4-17. Reload on G_CONTROL Selections ...................................................4-68

Table 4-18. Gate Interrupts ......................................................................................4-69

Table 4-19. PFI Selectors .........................................................................................4-70

Table 5-1. Pin Interface .........................................................................................5-2

Table 5-2. PFI<0..9> Input Selections ..................................................................5-7

Table 5-3. PFI<0..9> Output Selections.................................................................5-8

Table 6-1. Pin Interface..........................................................................................6-2

Table 6-2. RTSI_TRIGGER<0..6> Output Selections...........................................6-6

Table 6-3. RTSI_BRD<0..1> Output Selections....................................................6-7

Table 6-4. RTSI_BRD<2..3> Output Selections....................................................6-7

Table 7-1. Pin Interface .........................................................................................7-6

Table 7-2. Serial Output Source Select ..................................................................7-17

Table 8-1. Pin Interface..........................................................................................8-2

Table 8-2. Interrupt Condition Summary ..............................................................8-15

Table 9-1. Pin Interface .........................................................................................9-2

Table 9-2. Intel Bus Interface Timing ................................................................... 9-6

Table 9-3. Intel Bus Interface Timing .................................................................... 9-8

Table 10-1. Timebases Derived from IN_TIMEBASE ...........................................10-2

Table 10-2. Test Mode Input Pin Pairs ....................................................................10-8

Table 10-3. Pin Interface .........................................................................................10-9

DAQ-STC Technical Reference Manual xx

©

National Instruments Corporation

Page 20

Contents

Table B-1. DAQ-STC Registers .............................................................................B-1

Table B-2. Registers in Order of Address* ............................................................ B-5

Table B-3. Bitfield Description Guide ....................................................................B-9

Table C-1. DAQ-STC Pins in Alphabetical Order .................................................C-1

Table C-2. Summary of Buffer Types.....................................................................C-7

©

National Instruments Corporation xxi DAQ-STC Technical Reference Manual

Page 21

About This Manual

The DAQ-STC is an application-specific integrated circuit (ASIC)

designed by National Instruments. The DAQ-STC Technical Reference

Manual describes the programmable features of the DAQ-STC and is

intended for programmers who need to program the DAQ-STC on an

existing data acquisition (DAQ) board and for hardware engineers who

want to design a DAQ board using the DAQ-STC.

Before using this manual to program the DAQ-STC on an existing board,

you should be familiar with the board that contains your DAQ-STC. You

should begin by reading the user manual for the board containing the

DAQ-STC. Next, read the register-level programmer manual for the same

board. The register-level programmer manual refers to some of the sections

in this manual.

When you are familiar with the material in the register-level programmer

manual, you can refer directly to the DAQ-STC Technical Reference

Manual. Programmers should have to read only the Programming

Information section of each chapter in order to program the DAQ-STC.

Hardware engineers may need to read further for more detailed information

about hardware operation.

Organization of This Manual

The DAQ-STC Technical Reference Manual is organized as follows:

• Chapter 1, Introduction, describes the data acquisition system timing

controller (DAQ-STC), an application-specific integrated circuit

(ASIC) for the system timing requirements of a general-purpose A/D

and D/A system, such as a system containing the National Instruments

multifunction I/O boards.

• Chapter 2, Analog Input Timing/Control, describes the analog input

timing/control module (AITM), which generates timing for the ADC

and controls signals for the associated circuitry.

• Chapter 3, Analog Output Timing/Control, describes the analog output

timing/control module (AOTM), which generates timing for the D ACs

and controls signals for the associated circuitry, such as the data FIFO

buffers.

©

National Instruments Corporation xxiii DAQ-STC Technical Reference Manual

Page 22

About This Manual

• Chapter 4, General-Purpose Counter/Timer, presents information

about the general-purpose counter/timer (GPCT) module of the

DAQ-STC.

• Chapter 5, Programmable Function Inputs, explains the PFI module

on the DAQ-STC.

• Chapter 6, RTSI Trigger, describes the features of the RTSI trigger

module (RTM) and explains how to program the RTSI interface.

• Chapter 7, Digital I/O, describes the digital I/O (DIO) module and

explains how to use it on the DAQ-STC.

• Chapter 8, Interrupt Control, describes the interrupt control module

(ICM), its features, and the conditions that cause interrupts.

• Chapter 9, Bus Interface, describes the features of the bus interface

module, gives programming instructions, and presents the timing

diagrams for the bus interface.

• Chapter 10, Miscellaneous Functions, discusses the miscellaneous

functions not covered in the other chapters. The miscellaneous

functions include clock distribution, the programmable frequency

output, analog triggering, and test mode.

• Appendix A, Specifications, contains specifications for the DA Q-STC.

• Appendix B, Register Information, contains information about the

DAQ-STC registers and bitfields.

• Appendix C, Pin List, contains lists of the DAQ-STC pins.

• Appendix D, DAQ-STC Revision History, lists the differences between

the first two revisions of the DAQ-STC and identifies those boards

containing the first revision of the DAQ-STC.

• Appendix E, Customer Communication, contains forms you can use to

request help from National Instruments or to comment on our products

and manuals.

• The Glossary contains an alphabetical list and description of terms

used in this manual, including abbreviations, acronyms, metric

prefixes, mnemonics, and symbols.

• The Index contains an alphabetical list of key terms and topics in this

manual, including the page where you can find each one.

DAQ-STC Technical Reference Manual xxiv

©

National Instruments Corporation

Page 23

About This Manual

Conventions Used in This Manual

The following conventions are used in this manual:

<> Angle brackets containing numbers separated by an ellipsis represent a

range of values associated with a bit or signal name—for example,

ACH<0..7> stands for ACH0 through ACH7.

This icon to the left of bold italicized text denotes a note, which alerts you

to important information.

!

bold Bold text denotes the names of menu items, or dialog box buttons or

bold italic Bold italic text denotes a note, caution, or warning.

device Device refers to any hardware that contains DAQ-STC.

italic Italic text denotes emphasis, a cross reference, or an introduction to a key

module Module refers to each functional group in the DAQ-STC, as shown in

monospace Text in this font denotes text or characters that you should literally enter

This icon to the left of bold italicized text denotes a caution, which advises

you of precautions to take to avoid injury, data loss, or a system crash.

This icon to the left of bold italicized text denotes a warning, which advises

you of precautions to take to avoid being electrically shocked.

options.

concept.

Figure 1-3, DAQ-STC Block Diagram.

from the keyboard, sections of code, programming examples, and syntax

examples. This font is also used for the proper names of disk drives, paths,

directories, programs, subprograms, subroutines, device names, functions,

operations, variables, filenames and extensions, and for statements and

comments taken from programs.

©

National Instruments Corporation xxv DAQ-STC Technical Reference Manual

Page 24

About This Manual

National Instruments Documentation

The DAQ-STC Technical Reference Manual is one piece of the

documentation set for your data acquisition system. You could hav e any of

several types of manuals depending on the hardware and software in your

system. Use the manuals you have as follows:

• Getting Started with SCXI—If you are using SCXI, this is the first

manual you should read. It gives an overview of the SCXI system and

contains the most commonly needed information for the modules,

chassis, and software.

• Y our SCXI hardw are user manuals—If you are using SCXI, read these

manuals next for detailed information about signal connections and

module configuration. They also explain in greater detail how the

module works and contain application hints.

• Your DAQ hardware user manuals—These manuals have detailed

information about the DAQ hardware that plugs into or is connected

in your computer. Use these manuals for hardware installation and

configuration instructions, specification information about your DAQ

hardware, and application hints.