Page 1

AT-MIO-16X

User Manual

Multifunction I/O Board for the PC AT/EISA

October 1997 Edition

Part Number 320640B-01

© Copyright 1992, 1997 National Instruments Corporation. All rights reserved.

Page 2

Internet Support

support@natinst.com

E-mail: info@natinst.com

FTP Site: ftp.natinst.com

Web Address: http://www.natinst.com

Bulletin Board Support

BBS United States: (512) 794 -5422

BBS United Kingdom: 01635 551422

BBS France: 01 48 65 15 5 9

Fax-on-Demand Support

(512) 418-1111

Telephone Support (U.S.)

Tel: (512) 795-8248

Fax: (512) 794-5678

International Offices

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20,

Canada (Ontario) 905 785 0085, Canada (Québec ) 514 694 8521, Denmark 45 76 26 00,

Finland 09 725 725 11, France 01 48 14 24 24, Germany 089 741 31 30,

Hong Kong 2645 3186, Israel 03 5734815, Ital y 02 413091, Jap an 03 5472 2970,

Korea 02 596 7456, Mexico 5 520 2635, Nethe rlands 034 8 433466, Nor way 32 84 84 00,

Singapore 2265886, Spain 91 640 0085, Swede n 08 730 49 70, Switzerland 056 200 51 51,

Taiwan 02 377 1200, United Kingdom 01635 523545

National Instruments Corporate Headquarters

6504 Bridge Point Parkw ay Austin, TX 78730-503 9 Tel: (512) 794-0100

Page 3

Important Information

Warranty

The AT-MIO-16X is warranted against defects in materials and workmanship for a period of one year from the date of

shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace

equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instru ments software ar e warranted not to fail to execute pro grammi ng

instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced

by receipts or other documentation. National Instruments will, at its option, repair or replace soft ware media that do

not execute programming instructions if National Instruments receives notice of such defects during the warranty

period. National Instrument s does not war rant that the oper ation of the softwar e shall be un interr upted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside

of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping

costs of returning to the owner par ts whi ch are cov ered by w arranty .

National Instruments believes that the information in this manual is accurate. The document has been carefully

reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves

the right to make ch anges to subsequent editions of this document without prior not ice to holders of th is edition. The

reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for

any damages arising out of or related to this docum ent or the in format ion contai ned in it.

E

XCEPT AS SPECIFIED HEREIN

SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE

C

USTOMER’S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL

I

NSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER

WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR

CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF

Instruments will apply regardles s of the fo rm of acti on, whether i n contract or tort, incl uding neg lig ence. Any acti on

against National Instruments must be brought wit hin one year after the cause of action accrues. Nat ion al Instrument s

shall not be liable for any delay in performan ce due to causes beyo nd it s reasonable cont rol. The warranty pr ovided

herein does not cover damages, defects, malf unctio ns, or s ervice fai lures caused by owne r’s fail ure to fol low the

National Instruments in sta llat ion, o perat ion, or ma inte na nce instr uct ions; owner ’s modif icat ion of the p roduct;

owner’s abuse, misuse, or neglige nt acts; and power failur e or surges , fire, floo d, acciden t, actions of third part ies,

or other events outside reasonable cont rol.

, N

ATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND

.

. N

ATIONAL INSTRUMENTS

. This limitation of the liability of National

Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical,

including photocopying, reco rding, storin g in an in format ion retr iev al system , or tra nslati ng, in wh ole or in par t,

without the prior written consent of Nation al Inst rument s Corpo ration .

Trademarks

ComponentWorks™, LabVIEW™, Meas ur e™, NI-DAQ™, RTSI™, and VirtualB ench™ are trademarks of National

Instruments C orporation.

Product and company names listed are trademarks or trade names of their respective companies.

WARNING REGARDING MEDICAL AND CLINICAL USE OF NATIONAL INSTRUMENTS PRODUCTS

National Instruments products are not design ed with comp onents and testing in tend ed to ensure a level o f reliabi lity

suitable for use in treatment and diag nosi s of humans . Appli cations of Nation al Instru men ts product s invol vin g

medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the

part of the user or application designer . Any us e or applicat ion of Nat ional Ins trum ent s products for or involvi ng

medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional

medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury

or death should always continue to be used when National Instruments prod ucts ar e being used. National Instruments

products are NOT intended to be a substitute f or any for m of establ ished pr ocess, proce dure, or equi pmen t used to

monitor or safegua rd huma n he alth and sa fety in med ical or clin ical t reat ment .

Page 4

About This Manual

Organization of This Manual........................................................................................xv

Conventions Used in This Manual................................................................................ xvi

Related Documentation.................................................................................................xvii

Customer Communication....... .....................................................................................xvii

Chapter 1

Introduction

About the AT-MIO-16X...............................................................................................1-1

Analog Input...................................................................................................1-2

Analog Output................................................................................................1-2

Digital and Timing I/O...................................................................................1-3

What You Need to Get Started.....................................................................................1-3

Software Programming Choices...................................................................................1-4

National Instruments Application Software...................................................1-4

NI-DAQ Driver Software...............................................................................1-5

Register-Level Programming.........................................................................1-6

Optional Equipment......................................................................................................1-7

Unpacking.....................................................................................................................1-7

Table

of

Contents

Chapter 2

Configuration and Installation

Board Configuration.....................................................................................................2-2

AT Bus Interface............................................................................................2-2

Base I/O Address Selection............................................................................2-3

Interrupt and DMA Channel Selection...........................................................2-7

Analog Input Configuration..........................................................................................2-7

Input Mode........................... ...... ...... ..............................................................2-7

DIFF Input (Eight Channels)...........................................................2-8

RSE Input (16 Channels).................................................................2-9

NRSE Input (16 Channels) ..............................................................2-9

Input Polarity and Input Range.......................................................................2-10

Considerations for Selecting Input Ranges......................................2-10

Analog Output Configuration.......................................................................................2-11

©

National Instruments Corporation v AT-MIO-16X User Manual

Page 5

Table of Contents

Digital I/O Configuration............................................................................................. 2-12

Board and RTSI Clock Configuration..........................................................................2-12

Hardware Installation ................................................................................................... 2-13

Signal Connections.......................................................................................................2-14

Field Wiring Considerations......................................................................................... 2-42

Cabling Considerations for the AT-MIO-16X with 50-Pin I/O Connector ................. 2-43

Cabling Considerations for the AT-MIO-16X with 68-Pin I/O Connector ................. 2-44

Analog Output Reference Selection...............................................................2-11

Analog Output Polarity Selection.................................................................. 2-12

Signal Connection Descriptions..................................................................... 2-17

Analog Input Signal Connections..................................................................2-19

Types of Signal Sources................................................................................. 2-21

Floating Signal Sources................................................................... 2-21

Ground-Referenced Signal Sources.................................................2-21

Input Configurations...................................................................................... 2-21

Differential Connection Considerations (DIFF Input

Configuration)............................................................................... 2-22

Differential Connections for Ground-Referenced Signal

Sources.......................................................................................... 2-23

Differential Connections for Nonreferenced or Floating

Signal Sources ..............................................................................2-24

Single-Ended Connection Considerations....................................... 2-26

Single-Ended Connections for Floating Signal Sources

(RSE Configuration).....................................................................2-27

Single-Ended Connections for Grounded Signal Sources

(NRSE Configuration).................................................................. 2-28

Common-Mode Signal Rejection Considerations........ ................... 2-29

Analog Output Signal Connections................................................................ 2-29

Digital I/O Signal Connections......................................................................2-31

Power Connections ........................................................................................ 2-32

Timing Connections for Data Acquisition and Analog Output..................... 2-33

SCANCLK Signal ........................................................................... 2-33

EXTSTROBE* Signal............................................ ...... ...... ............. 2-33

EXTCONV* Signal.........................................................................2-34

EXTTRIG* Signal............................................. ..... .........................2-35

EXTGATE* Signal.......................................................................... 2-36

EXTTMRTRIG* Signal.................................................................. 2-36

Counter Signal Connections............................................................2-37

AT-MIO-16X User Manual vi

©

National Instruments Corporation

Page 6

Chapter 3

Theory of Operation

Functional Overview.....................................................................................................3-1

PC I/O Channel Interface Circuitry..............................................................................3-2

Analog Input and Data Acquisition Circuitry...............................................................3-5

Analog Input Circuitry ...................................................................................3-6

Data Acquisition Timing Circuitry................................................ ..... ............3-8

Multiple-Channel Data Acquisition ...............................................................3-12

Analog Output and Timing Circuitry.............................................................3-15

DAC Waveform Circuitry and Timing...........................................................3-18

Digital I/O Circuitry......................................................................................................3-24

Timing I/O Circuitry.....................................................................................................3-25

RTSI Bus Interface Circuitry ........................................................................................ 3-29

Table of Contents

A/D Converter..................................................................................3-6

Analog Input Multiplexers............................................................... 3-6

Analog Input Configuration............................................................. 3-6

PGIA ................................................................................................3-7

ADC FIFO Buffer.............. ..... ...... ...................................................3-7

Analog Input Calibration .................................................................3-7

Single-Read Timing........... ..... .........................................................3-8

Single-Channel Data Acquisition Timing........................................3-9

Continuous Scanning Data Acquisition Timing..............................3-13

Interval Scanning Data Acquisition Timing ....................................3-14

Data Acquisition Rates.....................................................................3-15

Analog Output Circuitry..................................................................3-16

Analog Output Configuration..........................................................3-17

Analog Output Calibration...............................................................3-17

DAC Waveform Circuitry................................................................3-18

DAC Waveform Timing Circuitry....................................... ...... ......3-20

FIFO Continuous Cyclic Waveform Generation.............................3-22

FIFO Programmed Cyclic Waveform Generation...........................3-23

FIFO Pulsed Waveform Generation ................................................3-23

Chapter 4

Register Map and Descriptions

Register Map.................................................................................................................4-1

Register Sizes .................................................................................................4-3

Register Description Format...........................................................................4-3

Configuration and Status Register Group.......................................................4-4

Command Register 1........................................................................4-5

Command Register 2........................................................................4-9

©

National Instruments Corporation vii AT-MIO-16X User Manual

Page 7

Table of Contents

Command Register 3.......................................................................4-13

Command Register 4.......................................................................4-20

Status Register 1.............................................................................. 4-25

Status Register 2.............................................................................. 4-30

Analog Input Register Group......................................................................... 4-31

ADC FIFO Register..................................... ...... ..............................4-32

CONFIGMEM Register .................................................................. 4-35

Analog Output Register Group......................................................................4-41

DAC0 Register ................................................................................4-44

DAC1 Register ................................................................................4-45

ADC Event Strobe Register Group............................................. ...... ............. 4-46

CONFIGMEMCLR Register........................................................... 4-47

CONFIGMEMLD Register............................................................. 4-48

DAQ Clear Register.........................................................................4-49

DAQ Start Register..........................................................................4-50

Single Conversion Register.................... ..... ...... ..............................4-51

ADC Calibration Register ....................................................... ........ 4-52

DAC Event Strobe Register Group............................................. ...... ............. 4-53

TMRREQ Clear Register.................................................................4-54

DAC Update Register................................................... ...... ............. 4-55

DAC Clear Register..................................... ...... ..............................4-56

General Event Strobe Register Group............................................................4-57

DMA Channel Clear Register..........................................................4-58

DMATCA Clear Register................................................... ..... ...... ..4-59

DMATCB Clear Register................................................................4-60

External Strobe Register..................................................................4-61

Calibration DAC 0 Load Register ................................ ...... ..... ........ 4-62

Calibration DAC 1 Load Register ................................ ...... ..... ........ 4-63

Am9513A Counter/Timer Register Group....................................................4-64

Am9513A Data Register ................................................................. 4-65

Am9513A Command Register........................................................4-66

Am9513A Status Register............................................................... 4-67

Digital I/O Register Group............................................................................. 4-68

Digital Input Register ...................................................................... 4-69

Digital Output Register....................................................................4-70

RTSI Switch Register Group......................................................................... 4-71

RTSI Switch Shift Register .............................................................4-72

RTSI Switch Strobe Register........................................................... 4-73

AT-MIO-16X User Manual viii

©

National Instruments Corporation

Page 8

Chapter 5

Programming

Data Acquisition Programming Functions ...................................................................5-14

Programming the Digital I/O Circuitry.........................................................................5-36

Programming the Am9513A Counter/Timer................................................................5-37

RTSI Bus Trigger Line Programming Considerations .................................................5-37

Table of Contents

Register Programming Considerations...........................................................5-1

Resource Allocation Considerations............................ ..... ...... .......................5-1

Initializing the AT-MIO-16X.........................................................................5-2

Initializing the Am9513A ................................................................5-3

Programming the Analog Input Circuitry.......................................................5-5

Single Conversions Using the SCONVERT or

EXTCONV* Signal ......................................................................5-5

Generating a Single Conversion.....................................................................5-6

Reading a Single Conversion Result..............................................................5-7

Programming Single-Channel Data Acquisition Sequence............................5-7

Programming Data Acquisition Sequences with Channel Scanning..............5-10

Continuous Channel Scanning Data Acquisition.............................5-10

Interval-Channel Scanning Data Acquisition.................................................5-12

Clearing the Analog Input Circuitry...............................................................5-14

Programming Single-Analog Input Channel Configurations.........................5-15

Programming Multiple-Analog Input Channel Configurations .....................5-15

Programming the Sample-Interval Counter....................................................5-16

Programming the Sample Counter(s).............................................................5-17

Sample Counts 2 through 65,536.....................................................5-18

Sample Counts Greater than 65,536 ................................................5-18

Programming the Scan-Interval Counter........................................................5-20

Applying a Trigger.........................................................................................5-21

Servicing the Data Acquisition Operation......................................................5-22

Resetting the Hardware after a Data Acquisition Operation..........................5-22

Resetting a Single Am9513A Counter/Timer..................................5-23

Programming the Analog Output Circuitry....................................................5-25

Cyclic Waveform Generation.........................................................................5-26

Programmed Cycle Waveform Generation....................................................5-28

Pulsed Cyclic Waveform Generation.............................................................5-30

Waveform Generation Programming Functions............................................5-32

Clearing the Analog Output Circuitry..............................................5-32

Selecting the Internal Update Counter.............................................5-32

Programming the Update-Interval Counter.................................................... 5-32

Programming the Waveform Cycle Counter..................................................5-34

Programming the Waveform Cycle Interval Counter ....................................5-34

Servicing Update Requests..............................................................5-35

©

National Instruments Corporation ix AT-MIO-16X User Manual

Page 9

Table of Contents

RTSI Switch Signal Connection Considerations.......................................................... 5-38

Programming the RTSI Switch .................................................................................... 5-39

Programming DMA Operations..................................................................... 5-41

Interrupt Programming................................................................................... 5-43

Chapter 6

Calibration Procedures

Calibration Equipment Requirements........................... ...... ......................................... 6-7

Calibration DACs.........................................................................................................6-8

Reference Calibration................................................................................................... 6-8

Analog Input Calibration.............................................................................................. 6-9

Analog Output Calibration........................................................................................... 6-10

Appendix A

Specifications

Appendix B

I/O Connector

Appendix C

AMD Am9513A Data Sheet

Appendix D

Customer Communication

Glossary

Index

Figures

Figure 1-1. The Relationship between the Programming Environment,

NI-DAQ, and Your Hardware.......... ...... ............................................... 1-6

Figure 2-1. AT-MIO-16X with 50-Pin I/O Connector Parts Locator Diagram....... 2-1

Figure 2-2. AT-MIO-16X with 68-Pin I/O Connector Parts Locator Diagram....... 2-2

Figure 2-3. Example Base I/O Address Switch Settings.......................................... 2-3

Figure 2-4. AT-MIO-16X 50-Pin I/O Connector.....................................................2-15

AT-MIO-16X User Manual x

©

National Instruments Corporation

Page 10

Table of Contents

Figure 2-5. AT-MIO-16X 68-Pin I/O Connector.....................................................2-16

Figure 2-6. AT-MIO-16X PGIA ..............................................................................2-20

Figure 2-7. Differential Input Connections for Ground-Referenced Signals...........2-23

Figure 2-8. Differential Input Connections for Nonreferenced Signals...................2-24

Figure 2-9. Single-Ended Input Connections for Nonreferenced or

Floating Signals .....................................................................................2-27

Figure 2-10. Single-Ended Input Connections for Ground-Referenced Signals........2-28

Figure 2-11. Analog Output Connections...................................................................2-30

Figure 2-12. Digital I/O Connections......................................................................... 2-32

Figure 2-13. EXTSTROBE* Signal Timing..............................................................2-33

Figure 2-14. EXTCONV* Signal Timing ..................................................................2-34

Figure 2-15. EXTTRIG* Signal Timing....................................................................2-35

Figure 2-16. EXTTMRTRIG* Signal Timing............................................................2-36

Figure 2-17. Event-Counting Application with External Switch Gating...................2-38

Figure 2-18. Frequency Measurement Application....................................................2-39

Figure 2-19. General-Purpose Timing Signals...........................................................2-41

Figure 3-1. AT-MIO-16X Block Diagram...............................................................3-1

Figure 3-2. PC I/O Channel Interface Circuitry Block Diagram..............................3-3

Figure 3-3. Analog Input and Data Acquisition Circuitry Block Diagram..............3-5

Figure 3-4. ADC Conversion Timing.......................................................................3-8

Figure 3-5. Single-Channel Posttrigger Data Acquisition Timing...........................3-10

Figure 3-6. Single-Channel Pretrigger Data Acquisition Timing.............................3-11

Figure 3-7. Scanning Posttrigger Data Acquisition Timing.....................................3-13

Figure 3-8. Interval Scanning Posttrigger Data Acquisition Timing........................3-14

Figure 3-9. Analog Output Circuitry Block Diagram...............................................3-16

Figure 3-10. Analog Output Waveform Circuitry......................................................3-19

Figure 3-11. Posted DAC Update Timing..................................................................3-20

Figure 3-12. Analog Output Waveform Circuitry......................................................3-21

Figure 3-13. FIFO Cyclic Waveform Generation with Disable.................................3-22

Figure 3-14. FIFO Programmed Cyclic Waveform Timing.......................................3-23

Figure 3-15. FIFO Pulsed Waveform Generation Timing .........................................3-23

Figure 3-16. Digital I/O Circuitry Block Diagram.....................................................3-24

Figure 3-17. Timing I/O Circuitry Block Diagram....................................................3-26

Figure 3-18. Counter Block Diagram.........................................................................3-27

Figure 3-19. RTSI Bus Interface Circuitry Block Diagram.......................................3-29

Figure 5-1. Initializing the Am9513A Counter/Timer.............................................5-4

Figure 5-2. Single Conversion Programming...........................................................5-6

Figure 5-3. Single-Channel Data Acquisition Programming...................................5-9

Figure 5-4. Scanning Data Acquisition Programming.............................................5-11

Figure 5-5. Interval Scanning Data Acquisition Programming................................5-13

Figure 5-6. Resetting an Am9513A Counter/Timer.................................................5-24

©

National Instruments Corporation xi AT-MIO-16X User Manual

Page 11

Table of Contents

Figure 5-7. Cyclic Waveform Programming ........................................................... 5-27

Figure 5-8. Programmed Cycle Waveform Programming....................................... 5-29

Figure 5-9. Pulsed Cyclic Waveform Programming................................................5-31

Figure 5-10. RTSI Switch Control Pattern.................................................................5-40

Figure 6-1. AT-MIO-16X EEPROM Map ............................................................... 6-2

Figure 6-2. Revision and Subrevision Field............................................................. 6-5

Figure 6-3. Configuration Memory Depth Field...................................................... 6-5

Figure 6-4. ADC and DAC FIFO Depth Field......................................................... 6-6

Figure 6-5. Area Information Field..........................................................................6-6

Figure B-1. AT-MIO-16X 50-Pin I/O Connector............................................. ...... ..B-2

Figure B-2. AT-MIO-16X 68-Pin I/O Connector............................................. ...... ..B-3

Tables

Table 2-1. Default Settings of National Instruments Products for the PC.............. 2-4

Table 2-2. Switch Settings with Corresponding Base I/O Address and

Table 2-3. Available Input Configurations for the AT-MIO-16X..........................2-8

Table 2-4. Actual Range and Measurement Precision Versus Input Range

Table 2-5. Recommended Input Configurations for Ground-Referenced and

Base I/O Address Space........................................................................2-5

Selection and Gain.................................................................................2-11

Floating Signal Sources......................................................................... 2-22

Table 4-1. AT-MIO-16X Register Map..................................................................4-1

Table 4-2. DMA Channel Selection ....................................................................... 4-12

Table 4-3. DMA and Interrupt Modes....................................................................4-16

Table 4-4. Interrupt Level Selection.......................................................................4-19

Table 4-5. Board and RTSI Clock Selection..........................................................4-21

Table 4-6. Analog Output Waveform Modes......................................................... 4-22

Table 4-7. Straight Binary Mode A/D Conversion Values..................................... 4-33

Table 4-8. Two’s Complement Mode A/D Conversion Values............................. 4-34

Table 4-9. Input Configuration...............................................................................4-39

Table 4-10. Analog Output Voltage Versus Digital Code (Unipolar Mode)............ 4-42

Table 4-11. Analog Output Voltage Versus Digital Code (Bipolar Mode) .............. 4-42

Table 5-1. Am9513A Counter/Timer Allocations..................................................5-2

Table 5-2. RTSI Switch Signal Connections.......................................................... 5-38

Table 6-1. EEPROM Factory Area Information..................................................... 6-2

Table 6-2. Calibration DACs..................................................................................6-8

AT-MIO-16X User Manual xii

©

National Instruments Corporation

Page 12

Table of Contents

Table A-1. Equivalent Offset Errors in 16-Bit Systems ..........................................A-3

Table A-2. Equivalent Gain Errors in 16-Bit Systems.............................................A-4

Table A-3. Typical Multiple-Channel Scanning Settling Times .............................A-5

Table B-1. Signal Connection Descriptions............................................................. B-4

©

National Instruments Corporation xiii AT-MIO-16X User Manual

Page 13

This manual describes the mechanical and electrical aspects of the

AT-MIO-16X board and contains information concerning its operation

and programming. Th e A T-M IO -16X is a high-pe rf orman ce,

multifunction analog, digital, and timing I/O board for the IBM PC AT

and compatibles and EISA perso nal comp uters (PCs).

Organization of This Manual

The AT-MIO-16X Us er Man ual is orga nized a s fo llows:

• Chapter 1, Introduction, describes the AT-MIO-16X, lists the

contents of your AT -M IO-1 6X kit, the o ptiona l so ftware, and

optional equipment, and explains how to unpack the AT-MIO-16X.

• Chapter 2, Configuration and Installation, ex plains bo ar d

configuration, installation of the AT-MIO-16X into the PC, signal

connections to the AT -MIO -1 6X, an d ca ble c onsid eration s.

• Chapter 3, Theory of Operation, contains a functional overvie w of

the AT-MIO-16X and explains the operation of each functional unit

making up the AT-MIO - 16X.

• Chapter 4, Register Map a nd D escriptions , describes in detail the

address and function of each of the AT-MIO-16X control and status

registers.

• Chapter 5, Programming, contains program ming instruc tions f or

operating the circuitry on the AT-MIO-1 6X.

• Chapter 6, Calibration Procedures, discusses the calibration

resources and proc edur es fo r the A T-MI O-16 X an alog in put a nd

analog output circuitry.

• Appendix A, Specifications, lists the specifications of the

AT-MIO-16X.

• Appendix B, I/O Connector, describes the pinout and signal names

for the AT-MIO-16X 50-pin I/O conn ector and the 68 -pin I/O

connector.

About

This

Manual

©

National Instruments Corporation xv AT-MIO-16X User Manual

Page 14

About This Manual

• Appendix C, AMD Am9513A Data Sheet, contains the

manufacturer data shee t f or the AM D Am95 13A System T iming

Controller integrated circuit (Advanced Micro Devices, Inc.). This

controller i s use d on the A T-M IO -1 6X.

• Appendix D, Customer Communication, contains forms you can

use to request help from National Instruments or to comment on our

products.

•The Glossary contains an alphabetical list and description of terms

used in this manual, including abbreviations, acronym s, metric

prefixes, mnemonics, and symbols.

•The Index cont ains an alphabet ical li st of key terms and topics used

in this manual, including the page where you can find each one.

Conventions Used in This Manual

The following conventions are used in this manual:

<> Angle brackets containing numbers separated by an ellipsis represent a

range of values associated with a bit or signal name (for exam ple,

DBIO<3..0>).

This icon to the left of bold italicized text denotes a note, which alerts

you to important information.

!

bold italic Bold italic text denotes a note, caution, or warning.

italic Italic text denotes emphasis, a cross reference, or an introduction to a

NI-DAQ NI-DAQ is used throughout this manual to refer to the NI-DAQ

PC PC refers to the IBM PC AT and compatibles, and to EISA personal

AT-MIO-16X User Manual xvi

This icon to the left of bold italicized text denotes a caution, which

advises you of precau tions to take to av oid injury , d ata lo ss, or a

system crash.

key concept.

software for DOS/Windows/LabWindo ws unless otherwise no ted.

computers.

The Glossary lists abbreviations, acronyms, metric prefixes,

mnemonics, symbols, and ter ms.

©

National Instruments Corporation

Page 15

Related Documentation

The following document contains information that you may find helpful

as you read this manual:

• IBM Personal Computer AT Technical Reference

You may also want to consult the following Advanced Micro D evices

information if you plan to prog ram the Am9 513 A Coun ter/Ti mer u sed

on the AT-MIO-16X:

• Am9513A/Am9513 System Timing Controller

Customer Communication

National Instruments want to receive your co mments on ou r products

and manuals. We are interested in the applications you develop with our

products, and we want to help if you have problems with them. To make

it easy for you to contact us, this manual contains comment and

configuration forms for you to complete. These for ms are in

Appendix D, Customer Communication, at the end of this manual.

About This Manual

©

National Instruments Corporation xvii AT-MIO-16X User Manual

Page 16

Chapter

Introduction

This chapter describes the AT-MIO-16X, lists the contents of your

AT-MIO-16X kit, the optional sof tware, an d optional equi pment, and

explains how to unpack the AT-MI O-16 X.

About the AT-MIO-16X

Congratulations on your p urcha se of the Na tional I nstrume nts

AT-MIO-16X. The AT -MIO-1 6X is a high-perf ormance ,

software-configurable 16-bit DAQ board for laboratory, test and

measurement, and data ac quisition and contro l a pplication s. The

board performs high-accu racy measurements with self-calibration,

high-speed settling to 16 bits, noise as low as 0.8 LSBrms, and a

maximum DNL of ±0.5 LSB . Because of its large FIFO s and

dual-channel DMA, the AT-MIO-16X can achieve high performance,

even when used in environments that may have long interrupt latencies,

such as Windows.

Because off-the-shelf instrumentation amplifiers require 500 µsec and

more to settle to 16-bit accuracy at high gains when sampling multiple

channels , Na t i o nal Instruments devel o pe d the NI-PGIA. The NI-PGIA,

which is used on the AT-MIO-16X, is an instrumentation amplifier that

settles to 16 bits in 40 µs, even when the board is used at its high est gain

of 100.

1

A common problem with DAQ boards is that you cannot easily

synchronize several mea sur em ent fu nctio ns to a c ommon trig ger o r

timing event. The AT -MI O- 1 6X has the Real-Time System Integ rat io n

(RTSI) bus to solve this pr oble m. T he RT SIbus co nsists of our custom

RTSI bus interface chip and a ribbon cable to route timing and trigger

signals between several functions on one or more DAQ boa rds in

your PC.

The AT-MIO-16X can interface to the Signal Conditioning eXtensions

for Instrumentation (SCXI) system so that you can acquire over 3,000

analog signals from therm oco uples, RT Ds , strain ga ug es, v oltag e

sources, and curr en t sou rc es . You c a n also ac qu ire or ge nera te dig ital

©

National Instruments Corporation 1-1 AT-MIO-16X User Manual

Page 17

Chapter 1 Introduction

Analog Input

signals for communication and control. SCXI is the instrumentation

front end for plug-in DA Q b oards .

The AT-MIO-16X is a high-performance multifunction analog, digital,

and timing I/O boar d for the PC. The AT-M IO- 16X has a 10 µsec,

16-bit, sampling ADC that can monitor a single input channel, or scan

through the 16 single-ended or 8 differential channels (expandable with

National Instruments multiplexing products) at a programmable gain of

1, 2, 5, 10, 20, 50, o r 100 fo r unipo lar or bip olar inp ut r ange s. A

512-word ADC FIFO buffer can perform seamless data acquisition at

the maximum rate without data loss. Internal or external triggering and

sampling are supported. If signal conditioning or additional analog

inputs are required, you can use the SCXI signal conditioning modules,

SCXI multiplexer products, or the AMUX-64T multiplexer board.

You can use the NI-DAQ software included with the AT-MIO-16X to

calibrate the analog input circuitry. This software adjusts the offset

and gain errors to zero by means of board-level calibration DACs. You

can store calibration DAC constants resulting from the calibration

procedure in the onboard EEPROM for later use. See Chapter 6,

Calibration Procedures, for additional information on calibration

procedures for the AT-MIO-16X.

Analog Output

The AT-MIO-16X also has two deglitched, double-buffered,

multiplying, 16-bit DACs that may be configured for a unipolar or

bipolar voltage output range . An o nbo ar d, + 10-V refe renc e is th e

internal reference to the circuitry of the DAC. A 2,048-word DAC FIFO

buffer allows seamless wavefo rm genera tion at the maximum ra te

without data loss. The DAC FIFO can perform cyclic waveform

generation directly from the FIFO, independent of the PC interface.

You can use the analog output circuitry for internal timer an d external

signal update capability for waveform generation.

You calibrate the analog output circuitry through the NI-DAQ software

provided with the boar d. Th is soft ware a djusts th e DAC offset and gain

errors of each channel to zero by means of board-level calibration

DACs. Calibration DAC constants resulting from the calibration

procedure may be stored in the onboard EEPROM for later use. See

Chapter 6, Calibration Procedures, for additio nal info rmati on on

calibration pro ce du res f or t he AT -M IO-1 6X .

AT-MIO-16X User Manual 1-2

©

National Instruments Corporation

Page 18

Digital and Timing I/O

In addition to the analog input and analog output capabilities of the

AT-MIO-16X, the AT-MIO -16X al so ha s ei ght digital I/O lines th at

can sink up to 24 mA of current, and three independe nt 16-bit

counter/timers for frequency counting, event counting, and pulse

output applications. The AT-MIO-16X has timer-generated inte rrupts,

a high-performance RTSI bus interface, and four triggers for

system-level timing.

You can use the AT-MIO-16X, with its multifunction analog, digital,

and timing I/O, in many applications, including machine and process

control automation, level monitoring and control, instrumentation,

electronic testing, and many others. You can use the multichannel

analog input for signal and transient analysis, data logging, and

chromatography. The tw o ana log outp ut cha nnels a re use ful for

machine and process co ntro l, a nalog fu nc tion g en eration, 16- bit

resolution voltage source, and pro grammab le signal attenu ation. You

can use the eight TTL-compatible digital I/O lines for machine and

process control, intermac hine co mmunic ation, and r elay switching

control. The three 16-bit counter/timers are useful for such functions

as pulse and clock gener ation , time d con trol o f labo ratory equipm e nt,

and frequency, event, and pulse-width measurement. With all these

functions on one bo ard, yo u ca n au to matica lly m onitor and co ntro l

laboratory processes.

Chapter 1 Introduction

The AT-MIO-16X is interfaced to the National Instruments RTSI bus.

With this bus, National Instru ments A T Se ries b oa rds ca n se nd timing

signals to each other. T he A T-M IO-16 X can send sign als from th e

onboard counter/timer to another board, or another board can control

single and multiple A/D con version s on the AT -MIO -16X .

Detailed specifications for the AT-MIO-16X are listed in Appendix A,

Specifications.

What You Need to Get Started

To set up and use y our AT -MIO -16X Serie s b oa rd, y ou will nee d the

following:

❑ One of the following boards:

AT-MIO-16X 50-pin

AT-MIO-16X 68-pin

©

National Instruments Corporation 1-3 AT-MIO-16X User Manual

Page 19

Chapter 1 Introduction

AT-MIO-16X User Man ual

❑

❑ One of the following software packages and documentation:

ComponentWorks

LabVIEW for Windows

LabWindows/CVI fo r W indo ws

Measure

NI-DAQ for PC Compatibles

VirtualBen ch

❑ Your comp uter

Software Programming Choices

You have several options to choose from w hen progra mming you r

National Instruments DAQ and SCXI hardware. You can use National

Instruments application software, NI-DAQ, or register-level

programming.

National Instruments Application Software

ComponentWorks con tains tools for data acq uisition and instr ument

control built on NI-DAQ driver softw are. Component Works provide s a

higher-level programming interface for building virtual instruments

through standard OLE controls and DLLs. With ComponentWorks, you

can use all of the configuration tools, resource management utilities,

and interactive control utilities included with NI-DAQ.

LabVIEW features interactive graphics, a state-of-the-art user

interface, and a po werf ul g raphic al progr am ming langua ge. The

LabVIEW Data Acquisition VI L ibra r y, a se ries of V Is fo r using

LabVIEW with National Instruments DAQ hardware, is included with

LabVIEW. The LabVIEW D ata A cquisitio n VI Libr ar y is functiona lly

equivalent to NI-DAQ software.

LabWindows/CVI features interactive graphics, state-of-the-art user

interface, and uses th e ANSI standa rd C pr ogr am ming la nguage . The

LabWindows/CVI Data Ac quisition Lib rary, a se ries of fun ctions f or

using LabWindows/CVI with National Instruments DAQ hardware, is

included with the NI-DAQ software kit. The LabWindow s/CVI Data

Acquisition Library is functionally equivalent to the NI-D AQ sof twar e.

AT-MIO-16X User Manual 1-4

©

National Instruments Corporation

Page 20

VirtualBench features virtual instruments that combine DAQ products,

software, and your co mputer to creat e a stand-alone in strument with the

added benefit of the processing, display, and storage capabilities of

your computer. VirtualBench instruments load and save waveform data

to disk in th e s ame form s th at ca n be u sed i n pop ular sp re ad she et

programs and w ord proc e ssors.

Using ComponentWork s, LabVIE W, LabWindo ws /CVI, or

VirtualBench software will greatly reduce the development time for

your data acquisition and control application.

NI-DAQ Driver Software

The NI-DAQ driver sof tware is included at no ch ar ge with all National

Instruments DAQ hardware. NI-DAQ is not packaged with SCXI or

accessory products, except for the SCXI-1200. NI-DAQ has an

extensive library of functions that you can call from your ap plicatio n

programmin g enviro nment. These func tions in clude r outines for anal og

input (A/D conversion), buffered data acquisition (high-sp eed A/D

conversion), analog outp ut ( D/A con version ), wavef orm g eneration

(timed D/A conversion), digital I/O, counter/timer operations, SCXI,

RTSI, self-calibration, messaging, and acquiring data to extended

memory.

Chapter 1 Introduction

NI-DAQ has both high-level DAQ I/O functions for maximum ease of

use and low-level DAQ I/O functions for maximum flexibility and

performance. Ex am ples of h igh- leve l func tions are stre aming data to

disk or acquiring a certain number of data po ints. An examp le of a

low-level function is writing directly to registers on the DAQ device.

NI-DAQ does not sacrifice the performance of National Instruments

DAQ devices because it lets multiple devices operate at their peak.

NI-DAQ also internal ly addr esses many of the co mplex i ssues bet wee n

the computer and the DAQ hardware such as programming interrupts

and DMA controllers. NI-DAQ maintains a consistent software

interface among its different versions so that you can change platforms

with minimal modifications to your code. Whether you are using

conventional programming lan guages o r Na tional I nstrum ents

application software, your ap plication use s the NI-DAQ driv er

software, as illustrated in Figure 1-1.

©

National Instruments Corporation 1-5 AT-MIO-16X User Manual

Page 21

Chapter 1 Introduction

Programming Environment

SCXI Hardware

Figure 1-1. The Relationship between the Programming Environment,

Register-Level Programming

The final option for programming any National Instruments DAQ

hardware is t o wr it e r eg iste r- lev el softw are . Writ ing re gist er-l ev el

programming software can be very time-c on sum ing and ine ffi cient,

and is not recomm en de d f or mo st u s ers .

Conventional

DAQ or

ComponentWorks,

LabVIEW,

LabWindows/CVI, or

VirtualBench

NI-DAQ

Driver Software

Personal

Computer or

Workstation

NI-DAQ, and Your Hardware

Even if you are an experienced register-level programmer, using

NI-DAQ or applica tion sof tware to pro gram you r Nation al Inst rume nts

DAQ hardware is ea sier than, and as flexib le as, regi ster- lev el

programming, and can sa ve w ee ks of deve lopment time.

AT-MIO-16X User Manual 1-6

©

National Instruments Corporation

Page 22

Optional Equipment

National Instruments offers a var iety of pr odu cts to use w ith yo ur

AT-MIO-16X board, inclu ding cables, c onnector bloc ks, and other

accessories, as follows:

• Cables and cable assemblies, shielded and ribb on

• Connector blocks, shield ed and uns hielde d 50 a nd 68-pin scr ew

terminals

• Real Time System Integration (RTSI) bus cables

• SCXI modules and accessories for isolating, amplifying, exciting,

and multiplexing signals for relays and analog output. With SCXI

you can condition and acquire up to 3,072 channels.

• Low channel count signa l con ditioning module s, bo ards, and

accessories, including co nditionin g for strain ga uges a nd RT Ds,

simultaneous sample and ho ld, and re lays

For more specific information about these products, refer to your

National Instruments catalogue or call the office nearest you.

Chapter 1 Introduction

Unpacking

Your AT-MIO-16X board is shipped in an antistatic package to prevent

electrostatic damage to the board. Electrostatic discharge can damage

several com ponents on the board. To avoid such damage in handling the

board, take the following pre cautions:

• Ground yourself via a ground ing strap or by hold ing a grounded

object.

• Touch the antistatic package to a metal part of your computer

chassis before removing the board from the package.

• Remove the board fro m the package and in spect the board for loose

components or an y o ther sig n o f dama ge. No tif y Nationa l

Instruments if the board appears da maged in any way. Do not

install a damaged board into your computer.

• Never touch the exposed pins of connectors.

©

National Instruments Corporation 1-7 AT-MIO-16X User Manual

Page 23

Configuration and

Chapter

Installation

1

2

This chapter explains board configuration, installation of the

AT-MIO-16X into the PC, signal connections to the AT-MIO-16X,

and cable considerations.

234

1 Product Name, Assembly Number, and Revision Letter 2Fuse 3 U112 4 Spare Fuse

Figure 2-1.

©

National Instruments Corporation 2-1 AT-MIO-16X User Manual

AT-MIO-16X with 50-Pin I/O Connector Parts Locator Diagram

Page 24

Chapter 2 Configuration and Installation

1

234

1 Product Name, Assembly Number, and Revision Letter 2Fuse 3 U112 4 Spare Fuse

Figure 2-2. AT-MIO-16X with 68-Pin I/O Connector Parts Locator Diagram

Board Configuration

The AT-MIO-16X contain s one DIP switch to conf igure the base

address selection for the AT bus interface. The remaining resource

selections, such as DMA and interrupt channel selections, are

determined by programming the individual reg isters in the

AT-MIO-16X register set. The general location of the registers in the

I/O space of the PC is determined by the base address selection, whereas

the specific location of the registers within the register set is determined

by the AT-MIO-16X dec ode c irc uitry.

AT Bus Interface

Operation of the AT-MIO-16X multifunction I/O board is controlled

through accesses to registers within the board register set. Some of th e

registers in the register set retain data written to them to determine

board operation. Other registers in the register set contain impo rtant

status information necessary for proper sequencing of events. Still other

registers perform functions by accessing them either by reading from or

writing to their location. However, these registers do not retain

pertinent data when written to, nor do they provide pertinent status

information when read.

AT-MIO-16X User Manual 2-2

©

National Instruments Corporation

Page 25

The PC defines accesses to plug- in boa rds to be I/O mappe d acc esses

within the I/O space of the computer. Locations are either written to or

read from as bytes or words. Each register in the register set is mapped

to a certain offset from the base address selection of the board as read

or write, and as a word or byte location as defined by the decode

circuitry.

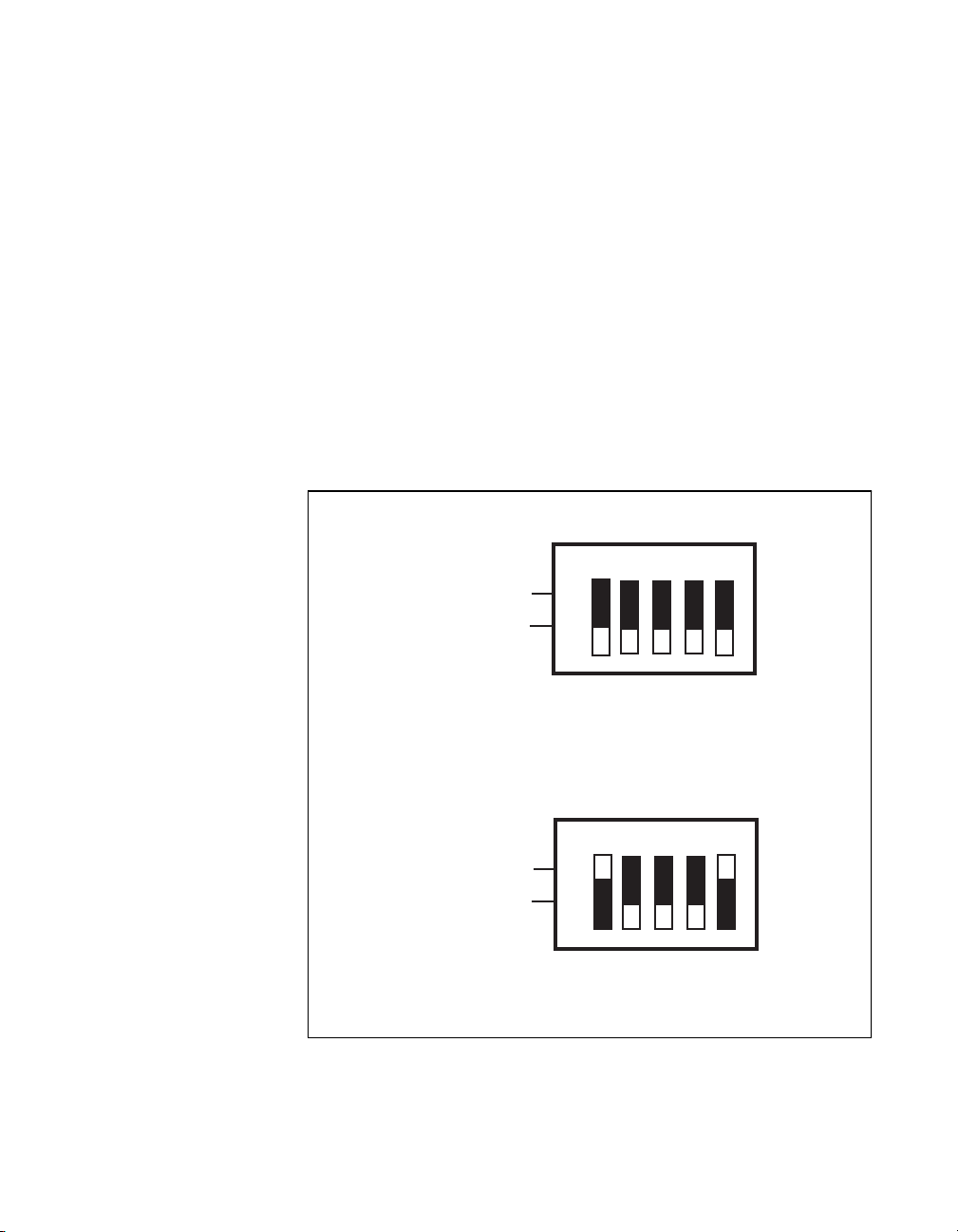

Base I/O Address Selection

The AT-MIO-16X is conf igur ed a t the f actor y to a ba se I /O addre ss

of 220 hex. This base address setting is suitable for most systems.

However, if your sy stem has othe r har dw are at this ba se I/O a ddre ss,

you must change either the AT-MIO-16X base address DIP switch or

the other hardware base address to avoid a conflict. Figure 2-3 shows a

graphical representation of the b ase add ress se lection D IP switc h, a nd

also shows how to reconfigure the selected base address.

Switch up for 1

Switch down for 0

Chapter 2 Configuration and Installation

U112

12345

O

N

O

F

F

A7

A9

A8

A6

A5

A. Switches Set to Base I/O Address of Hex 000

U112

12345

Switch up for 1

Switch down for 0

O

N

O

F

F

A9

A8

A7

A6

A5

B. Switches Set to Base I/O Address of Hex 220 (Factory Setting)

Figure 2-3.

©

National Instruments Corporation 2-3 AT-MIO-16X User Manual

Example Base I/O Address Switch Settings

Page 26

Chapter 2 Configuration and Installation

The base address DIP switch is arranged so that a logical 1 or true state

for the associated address selection bit is selected by pushing the toggle

switch up, or toward the top of the board. A lternate ly, a logical 0 or

false state is selected by pushing the toggle switch down, or toward the

bottom of the board. In Figur e 2-3B, A 9 is up (tr ue), A8 thro ugh A6

are low (false), and A5 is up (true). This repres ents a binary value of

10001XXXXX, or hex 220. The Xs indicate don’t care bits and are the

five least significant bits (LSBs) of the a ddre ss (A 4 throu gh A0 ) use d

by the AT-MIO-16X circuitry to decode the individual register

selections. The don’t care bits indicate the size of the register space. In

this case, the AT-MIO-16X u ses I/O a ddress he x 2 20 th rough h ex 23 F

in the factory-default setting.

Note: If you change the AT-MIO-16X base I/O addres s, yo u must make a

corresponding change to any so ftware pac kage s you use with the

AT-MIO-16X. Table 2-1 lists the default settings of other National

Instruments products for the PC. Table 2-2 lists the possible switch

settings, the corresponding base I/O address, and the base I/O address

space used for that setting. For more information about the I/O address

of your PC, refer to the technical reference manual for your computer.

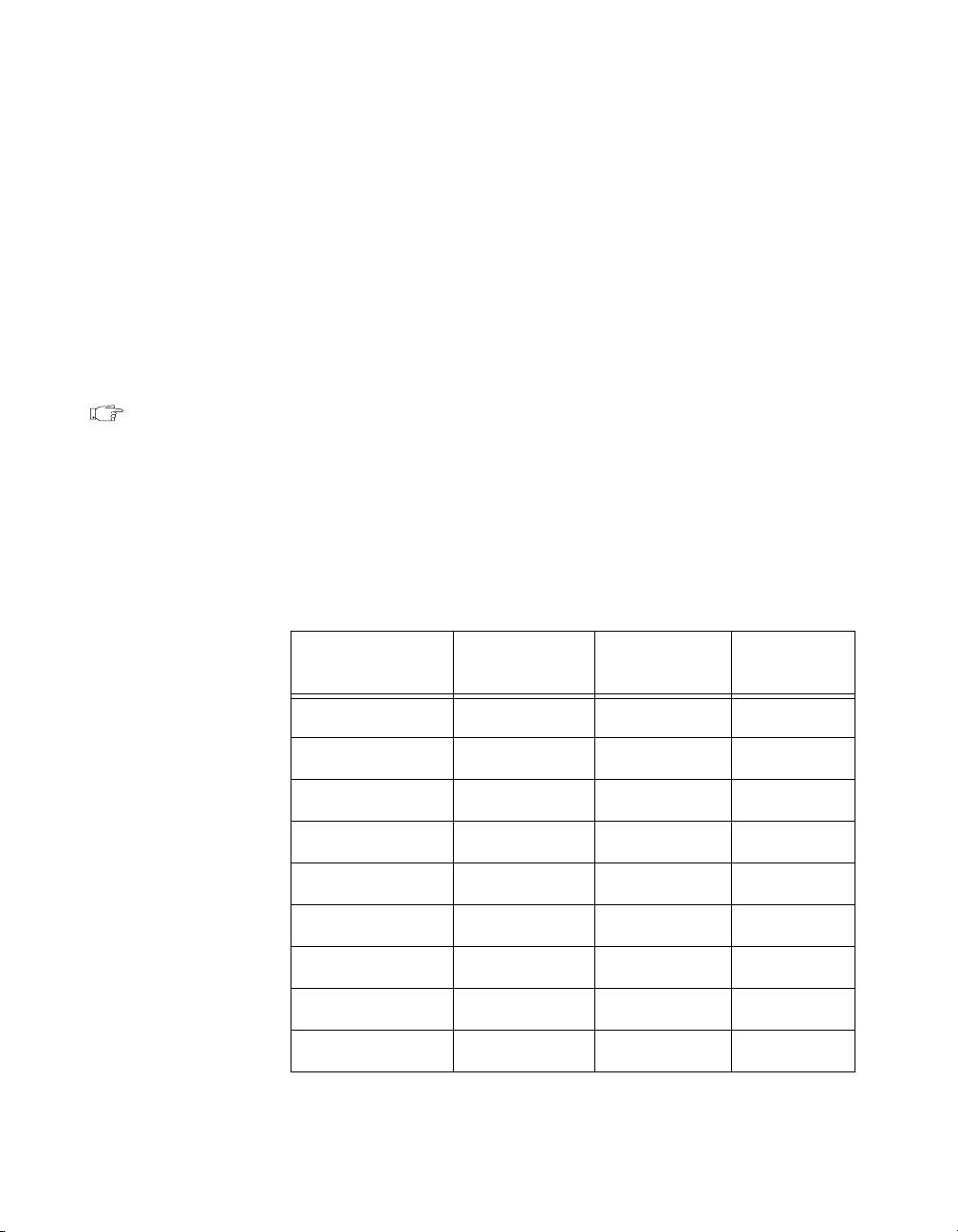

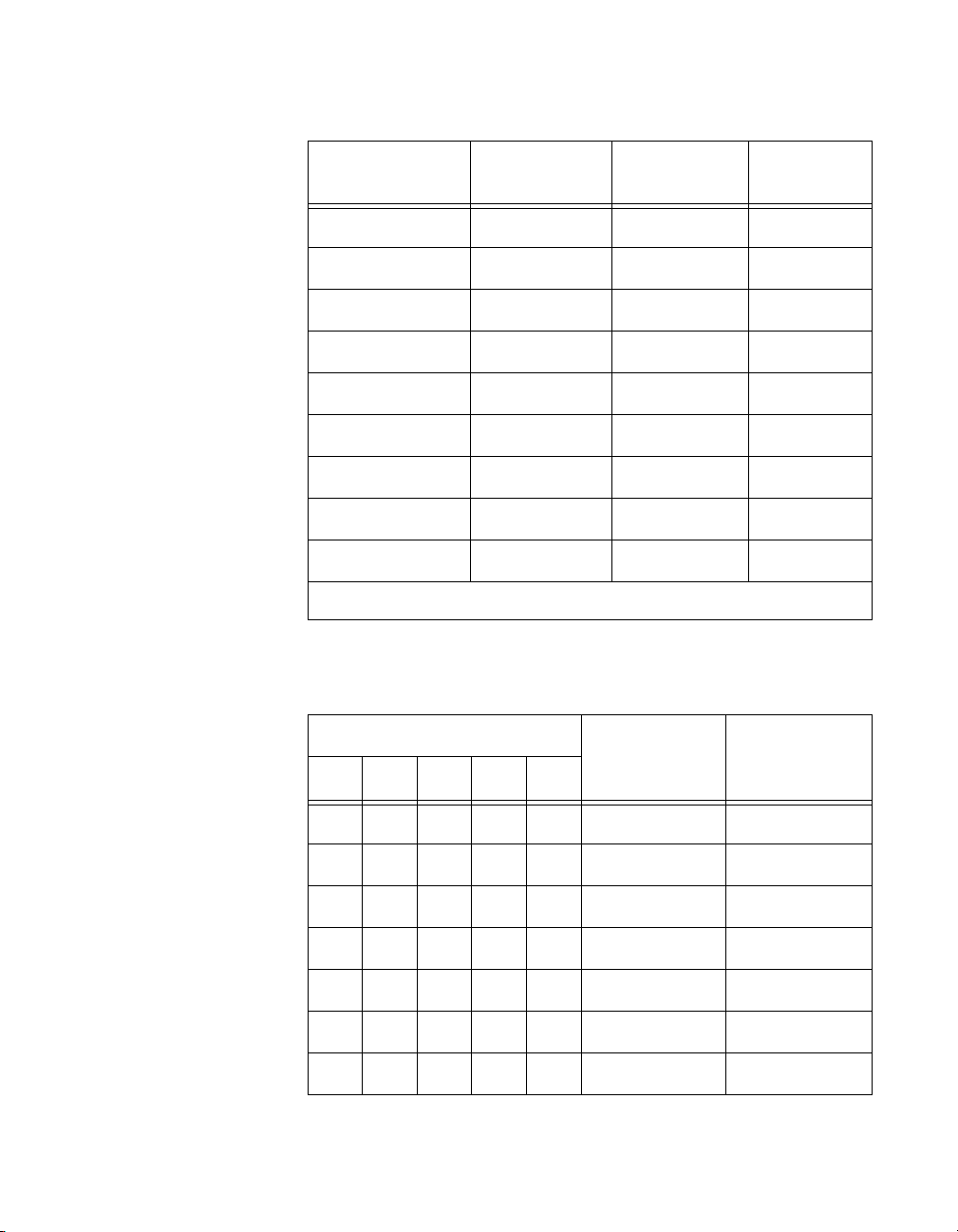

Table 2-1. Default Settings of National Instruments Products for the PC

Board DMA

AT-A2150 None* None* 120 hex

AT-AO-6/10 Channel 5 Lines 11, 12 1C0 hex

AT-DIO-32F Channels 5, 6 Lines 11, 12 240 hex

AT-DSP2200 None* None* 120 hex

AT-GPIB Channel 5 Line 11 2C0 hex

AT-MIO-16 Channels 6, 7 Line 10 220 hex

AT-MIO-16D Channels 6, 7 Lines 5, 10 220 hex

AT-MIO-16F-5 Channels 6, 7 Line 10 220 hex

AT-MIO-16X None* None* 220 hex

AT-MIO-16X User Manual 2-4

Channel

Interrupt

Level

©

National Instruments Corporation

Base I/O

Address

Page 27

Chapter 2 Configuration and Installation

Table 2-1. Default Settings of National Instruments Products for the PC (Continued)

Board DMA

Channel

Interrupt

Level

Base I/O

Address

AT-MIO-64F-5 None* None* 220 hex

GPIB-PCII Channel 1 Line 7 2B8 hex

GPIB-PCIIA Channel 1 Line 7 02E1 hex

GPIB-PCIII Channel 1 Line 7 280 hex

Lab-PC Channel 3 Line 5 260 hex

PC-DIO-24 None Line 5 210 hex

PC-DIO-96 None Line 5 180 hex

PC-LPM-16 None Line 5 260 hex

PC-TIO-10 None Line 5 1A0 hex

* These settings are software configurable and are disabled a t sta rt up ti m e.

Table 2-2. Switch Settings with Corresponding Base I/O Address and

Base I/O Address Space

Switch Setting

A9 A8 A7 A6 A5

Base I/O

Address (hex)

Base I/O

Address Space

Used (hex)

0 0 X X X 000 - E00 Reserved

0 1 0 0 0 100 100 - 11F

0 1 0 0 1 120 120 - 13F

0 1 0 1 0 140 140 - 15F

0 1 0 1 1 160 160 - 17F

0 1 1 0 0 180 180 - 19F

0 1 1 0 1 1A0 1A0 - 1BF

©

National Instruments Corporation 2-5 AT-MIO-16X User Manual

Page 28

Chapter 2 Configuration and Installation

Table 2-2. Switch Settings with Corresponding Base I/O Address and

Base I/O Address Space (Continued)

Switch Setting

A9 A8 A7 A6 A5

Base I/O

Address (hex)

Base I/O

Address Space

Used (hex)

0 1 1 1 0 1C0 1C0 - 1DF

0 1 1 1 1 1E0 1E0 - 1FF

1 0 0 0 0 200 200 - 21F

1 0 0 0 1 220 220 - 23F

1 0 0 1 0 240 240 - 25F

1 0 0 1 1 260 260 - 27F

1 0 1 0 0 280 280 - 29F

1 0 1 0 1 2A0 2A0 - 2BF

1 0 1 1 0 2C0 2C0 - 2DF

1 0 1 1 1 2E0 2E0 - 2FF

1 1 0 0 0 300 300 - 31F

1 1 0 0 1 320 320 - 33F

1 1 0 1 0 340 340 - 35F

1 1 0 1 1 360 360 - 37F

1 1 1 0 0 380 380 - 39F

1 1 1 0 1 3A0 3A0 - 3BF

1 1 1 1 0 3C0 3C0 - 3DF

1 1 1 1 1 3E0 3E0 - 3FF

AT-MIO-16X User Manual 2-6

©

National Instruments Corporation

Page 29

Interrupt and DMA Channel Selection

The base I/O address selection is the only resource on the AT-MIO-16X

board that must be set manually before the board is placed into the PC.

The interrupt level and DMA channels used by the AT-MIO-16X are

selected via registers in the AT-MIO-16X register set. The

AT-MIO-16X powers up with all interrupt and DMA requests disabled.

To use the interrupt capability of the AT-MIO-16X, an interrupt level

must first be selected via register programming, then the specific

interrupt mode must be enabled. The same method holds for DMA

channel selection. To use the DMA capability of the board, one or two

DMA channels must be selected through the appropriate register, then

the specific DMA mode must be enabled. It is possible to have interrupt

and DMA resourc es con cur rently en ab led.

The interrupt lines supported by the AT-MIO-16X hardware are IRQ3,

IRQ4, IRQ5, IRQ7, IRQ10, IRQ11, IRQ12, and IRQ15. The DMA

channels supported are Channe ls 0 through 3, and Channe ls 5

through 7. If you use the AT-MIO-16X in an AT-ty pe compute r, you

should only use DMA Channels 5 through 7 beca use these are the only

16-bit channels available. If you use the board in an EISA computer, all

channels are capable of 16- bit transfers an d you can use them . The

AT-MIO-16X does not use and cannot be configured to use th e 8-b it

DMA Channels 0 throug h 3 o n the PC I /O chan ne l fo r 16-bit tra nsf ers.

Chapter 2 Configuration and Installation

Analog Input Configuration

The analog input section of the AT-MIO-16X is software configurable.

You can select different analog in put config urations by progr amming

the appropriate register in the AT-MIO-16X register set. The following

paragraphs describe in detail each of the analog input categories.

Input Mode

The AT-MIO-16X offer s th ree diff er ent inpu t m odesSE) inp ut,

referenced single-en de d (RSE ) in put, and diff eren tial (DI FF) input.

The single-ended input conf igura tions use u p to 16 cha nnels. T he

DIFF input configuration uses up to eight channels. Input modes are

programmed on a per chann el basis for multimode scanning. For

example, the circuitry can be conf igured to effectively sca n

12 channels, four diffe rentia lly c onfigur ed cha nne ls and ei ght

single-ended channels. The in put configura tions are de scribe d in

Table 2-3.

©

National Instruments Corporation 2-7 AT-MIO-16X User Manual

Page 30

Chapter 2 Configuration and Installation

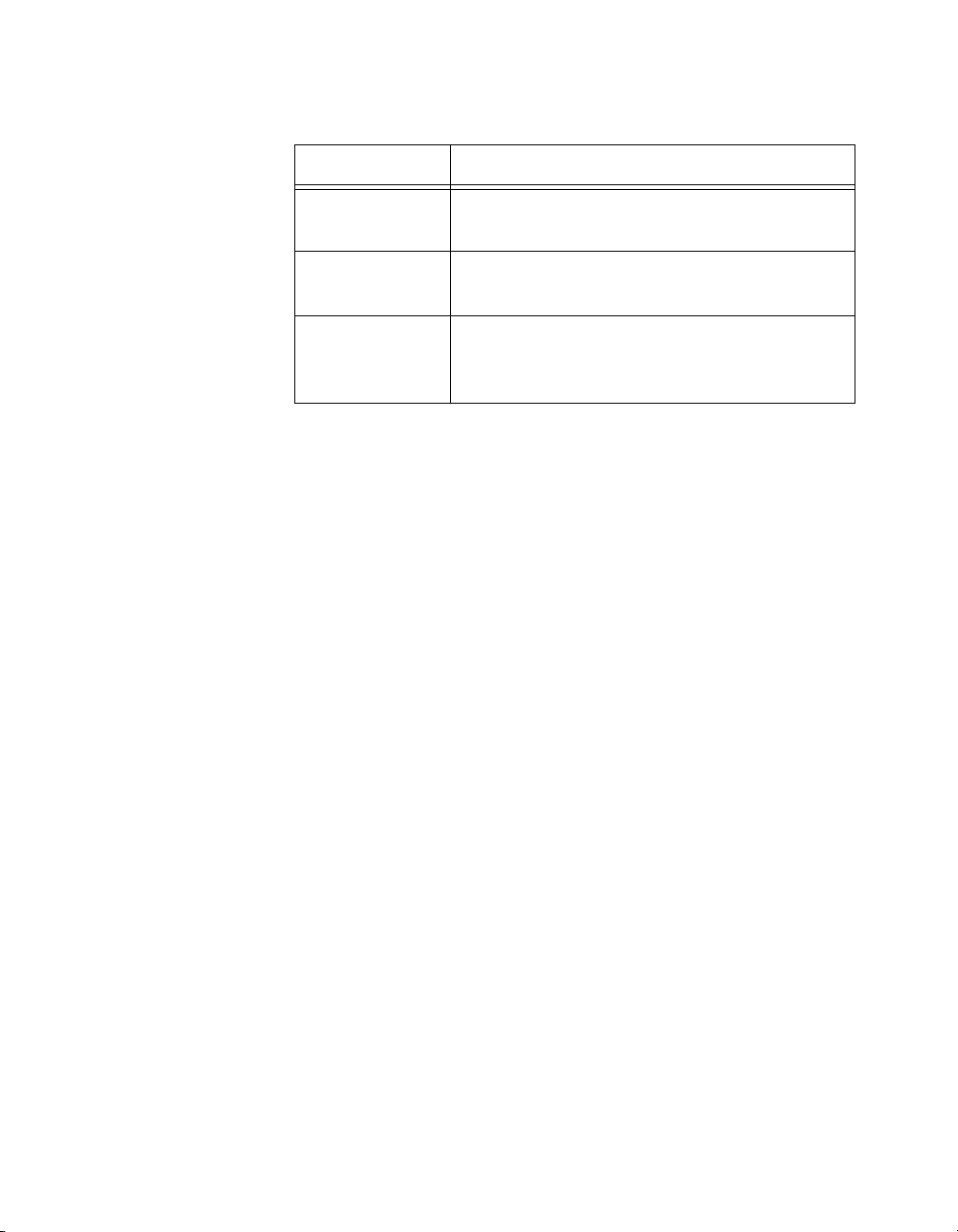

Table 2-3.

Available Input Configurations for the AT-MIO-16X

Configuration Description

DIFF Differential configurationnput of the PGIA tied to

the multiplexer output of Channels 8 thro ugh 15.

RSE Referenced single-end ed configurationve ( –) input

of the PGIA referenced to analog ground.

NRSE Nonreferenced single-ended configurationative (–)

input of the PGIA tied to AI SENSE and not

connected to ground.

While reading the following paragraphs, you may find it helpful to refer

to the Analog Input Signal Connections section later in this chapter,

which contains diagrams showing the signal paths for the three

configurations.

DIFF Input (Eight Channels)

DIFF input means that each input signal has its own reference, an d the

difference bet ween each sign al and its re ference is me asured. The signa l

and its reference are assigned an input channel. This is the

recommended con figura tion. With this inpu t c onfigur ation , th e

AT-MIO-16X can monitor up to eigh t different ana log input signals.

This configuration is se lect ed v ia softwa re. See th e co nfig uration

memory register a nd T abl e 4-9 i n Cha pt er 4, Register Map and

Descriptions. The results of this configuration are as follows:

• One of Channels 0 thro ugh 7 is tied to the p ositive (+) inpu t of

the PGIA.

• One of Channe ls 8 thro ugh 15 is tied to the neg ative (–) inp ut o f

the PGIA.

• Multiplexer control is configured to control up to eight input

channels.

• AI SENSE may be driven by the board analog input ground or left

unconnected.

Considerations for using the DIFF input configuration are discussed in

the Signal Connections section later in this chapter. Figure 2-8 shows a

schematic diagram of this configuration.

AT-MIO-16X User Manual 2-8

©

National Instruments Corporation

Page 31

Chapter 2 Configuration and Installation

RSE Input (16 Channels)

RSE input means that all input signals are referenced to a common

ground point that is also tied to the analo g in put gro und of the

AT-MIO-16X board. Th e negative (–) input of the differ ential input

amplifier is tied to the analog ground. This configuration is useful when

measuring flo ati ng sign al sour ces . Se e t he Type s of Sign al So urces

section later in this chapter for more information. With this input

configuration, the AT-MIO- 16X ca n mo nitor up to 16 differ e nt analog

input signals. This configuration is selected via softw are. See th e

configuration memory re gister a nd Tab le 4-9 in Cha pter 4, Register

Map and Descriptions. The resu lt s of th is con figu ra t io n ar e as fo llow s:

• The negative (–) input of the PGIA is tied to the PGIA signal

ground.

• Multiplexer outputs are tied together into the positive (+) input

of the PGIA.

• Multiplexer control is configur ed to control up to 16 input

channels.

• AI SENSE may be dr iven b y the board a nal og inpu t groun d o r

left unconnected.

Considerations for using the R SE co nfigura tion are disc ussed in the

Signal Connections section later in this chapter. Figure 2-18 shows

a schematic diagram of this configuration.

NRSE Input (16 Channels)

NRSE input means that all input signals are referenced to the same

common-mode voltage, but this com mon-mode voltage can floa t

with respect to the analo g g round of the A T-M IO-1 6X b oard. This

common-mode voltage is subsequently subt racted from the signals

by the input PGIA. This configuration is useful when measuring

ground-referenced signal sources. See the Types of Signal Sources

section later in this chapter for more information. With this input

configuration, the AT-MIO-16X can measure up to 16 different analog

input signals. This configuration is selected via softw are. See th e

configuration memory re gister a nd Tab le 4-9 in Cha pter 4, Register

Map and Descriptions, for additional information. The results of this

configuration ar e as fol lows:

• AI SENSE is tied into the negative (–) input of the PGIA.

• Multiplexer outputs are tied together into the positive (+) input

of the PGIA.

©

National Instruments Corporation 2-9 AT-MIO-16X User Manual

Page 32

Chapter 2 Configuration and Installation

• Multiplexer control is configur ed to control up to 16 input

channels.

Note: The NRSE input mode is the only mode in which the AI SENSE signa l

from the I/O connector is used as an input. In all other modes, AI SENSE

is either programmed to be unused or driven with the board analog input

ground.

Considerations for using the NRSE input configuration are discussed in

the Signal Connections section later in this chapter. Figure 2-8 shows a

schematic diagram of this configuration.

Input Polarity and Input Range

The AT-MIO-16X has two polarities: unipolar in put and bipolar input.

Unipolar input means that the input voltage range is between 0 and V

where V

input voltage range is between –V

a maximum unipolar input range of 10 V, and a maximum bipolar input

range of 20 V (±10 V). Polarity and range settings are programmed on

a per channel basis through the co nfiguration me mory registe r.

is a positive reference voltage. Bipolar input means that the

ref

and +V

ref

. The AT-MIO-16X has

ref

ref

Considerations for Selecting Input Ranges

Input polarity and range selection depend on the expected input range

of the incoming signal. A large input range can accommodate a large

signal variation but lowers the voltage resolution. Choosing a smaller

input range increases the voltage resolution but may re sult in the input

signal going out of range. For best results, the input range should be

matched as closely as possible to the expected range of the input signal.

For example, if the input signal is certain not to be negative (below

0 V), a unipolar input is best. However, if the signal is ever negative,

inaccurate readings will occur if unipolar input polarity is used.

The software-p rog ramm able g ain on the AT -M IO-1 6X i n crea se s its

overall flexibility by matching the input signal ranges to those that the

AT-MIO-16X analog-to- digital converte r (ADC) can a ccommod ate.

The AT-MIO-16X board has gains of 1, 2, 5, 10, 20, 50, and 100 and is

suited for a wide variety of signal levels. With the proper gain setting,

the full resolution of the ADC can be used to measure the input signal.

Table 2-4 shows the overall input range and prec ision acco rding to the

input range configuration and gain used.

AT-MIO-16X User Manual 2-10

©

National Instruments Corporation

Page 33

Chapter 2 Configuration and Installation

Table 2-4.

Range

Configuration

0 to +10 V 1.0

–10 to +10 V 1.0

* The value of 1 LSB of the 16-bit ADC; that is, the voltage increment corresponding to

a change of 1 count in the ADC 16-bit count.

Note:

Actual Range and Measurement Precision Versus Input Range

Selection and Gain

Gain Actual

Input Range

0 to +10.0 V

2.0

5.0

10.0

20.0

50.0

100.0

0 to +5.0 V

0 to +2.0 V

0 to +1.0 V

0 to +0.5 V

0 to +0.2 V

0 to 100.0 mV

–10.0 to +10.0 V

See Appendix A,

2.0

5.0

10.0

20.0

50.0

100.0

Specifications

–5.0 to +5.0 V

–2.0 to +2.0 V

–1.0 to +1.0 V

–0.5 to +0.5 V

–0.2 to +0.2 V

–100.0 to +100.0 mV

, for absolute maximum rati ngs.

Precision*

152.59 µV

76.29 µV

30.52 µV

15.26 µV

7.63 µV

3.05 µV

1.53 µV

305.18 µV

152.59 µV

61.04 µV

30.52 µV

15.26 µV

6.10 µV

3.05 µV

Analog Output Configuration

The AT-MIO-16X supplies two c hannels of anal og output voltag e at

the I/O connector. The analog output circuitry is configurable through

programming of a register in th e board reg ister se t. The refer ence an d

range for the analog o utput ci rcuitry ca n be selecte d thr ough sof tw are.

The reference can be either internal or external, whereas the range can

be either bipolar o r unipolar .

Analog Output Reference Selection

Each DAC can be connected to the AT-MIO-16X internal reference of

10 V or to the external reference signal connected to the EXTREF pin

on the I/O connector. This signal applied to EXTREF must be between

–18 and +18 V. Both channels ne ed not be configu red for the same

mode.

©

National Instruments Corporation 2-11 AT-MIO-16X User Manual

Page 34

Chapter 2 Configuration and Installation

Analog Output Polarity Selection

Each analog output c ha nnel c an be c onf igur ed fo r eithe r unipo lar or

bipolar output. A unipolar configuratio n has a range of 0 to V

analog output. A bi polar con figura tion h as a ra ng e of –V

the analog output. V

analog output circuitry and can be either the 10-V onboard reference or

an externally supplied reference between –18 and +18 V. Both channels

need not be configu red f or the sa m e ra nge.

Selecting a bipolar range for a particular DAC means that any data

written to that DAC will be interpreted as two’s complement format.

In two’s complement mode, data values written to the analog output

channel range from –32,768 to +32,767 decimal (8000 to 7FFF hex). If

unipolar range is selected, data is interpr eted in straight bina ry forma t.

In straight binary mode, data values written to the analog output channel

range from 0 to 65,535 decimal (0 to FFFF hex).

Digital I/O Configuration

The AT-MIO-16X contain s eight lines of digital I/O for

general-purpose use. The eight digital I/O lines supplied are configured

as two 4-bit ports. Each po rt can b e individua lly conf igur ed thr ough

programming of a r egis ter in th e boa rd reg is ter se t a s ei ther inp ut or

output. At system startup and reset, the digital I/O ports are both

configured for input.

at the

ref

to +V

is the voltage reference used by t he DACs i n the

ref

ref

ref

at

Board and RTSI Clock Configuration

When multiple AT Series boards are connected via the RTSI bus,

you may want all of the boa rds to use the same 10-MH z c lock. T his

arrangement is useful for applications that require counter/timer

synchronization between boards. Each AT Series board with a RTSI bus

interface has an onboard 10-MHz oscillator. Thus, one board can drive

the RTSI bus clock signal, and the other b oards c an r eceive this signa l

or disconnect from it.

Many functions pe rfo rmed by the AT -M IO- 16X boa rd requ ir e a

frequency timebase to generate the necessary timing signals for

controlling ADC conversions, DAC updates, or general-purpose signals

at the I/O connector. You select this t imebase through programming one

of the registers in the AT-MIO-16X register set.

AT-MIO-16X User Manual 2-12

©

National Instruments Corporation

Page 35

The AT-MIO-16X can use either its internal 10-MHz timebase, or it can

use a timebase received over the RTSI bus. In addition, if the board is

configured to use the internal timebase, it can also be programmed to

drive its internal timebase over the RTSI bus to another board that is

programmed to re ceive this timeb ase signal. Th is clock sourc e, whether

local or from the RTSI bus, is then divided by 10 and used as the

Am9513A frequency source. The defau lt config uration at startup is to

use the internal timebase without driving the RTSI bus timebase signal.

Hardware Installation

You can install the AT-MIO-16X in any avai lable 16-bit ex pansion

slot in your AT Series computer. However, to achieve best noise

performance, yo u should leave as muc h room a s possible betwee n the

AT-MIO-16X and other boa rds and har dw are . Th e AT -MIO -1 6X does