MXIC MX10EXA Datasheet

FEA TURE

PRELIMINARY

MX10EXA

XA 16-bit Microcontroller Family

64K Flash/2K RAM, Watchdog, 2UARTs

• 4.5V to 5.5V

• 64K bytes of on-chip Flash program memory with InSystem Programming capability

• Five Flash blocks = two 8k byte blocks and three 16k

byte blocks

• Single supply voltage In-System Programming of the

Flash memory, (VPP=VDD or VPP=12V ifdesired)

• Boot ROM contains low level Flash programming

routines for In-Application Programming and a default

serial loader using the UART

• 2048 bytes of on-chip data RAM

• Supports off-chip program and data addressing up to 1

megabyte (20 address lines)

GENERAL DESCRIPTION

The MX10EXA is a member of Philips’ 80C51 XA

(eXtended Architecture) family of high performance 16bit single-chip microcontrollers.

The MX10EXA contains 64k bytes of Flash program

memory, and provides three general purpose timers/

counters, a watchdog timer , dual U AR Ts, and f our general purpose I/O ports with programmable output configurations.

• Three standard counter/timers with enhanced features

All timers have a toggle output capability

• Watchdog timer

• Two enhanced UARTs with independent baud rates

• Seven software interrupts

• Four 8-bit I/O ports, with 4 programmable output

configurations for each pin

• 30 MHz operating frequency at 5V

• Power saving operating modes: Idle and PowerDown.Wake-Up from power-down via an external interrupt is supported.

• 44-pin PLCC (MX10EXAQC) and 44-pin LQFP

(MX10EXAUC) packages

A default serial loader program in the Boot ROM allows

In-System Programming (ISP) of the Flash memory without the need for a loader in the Flash code. User programs may erase and reprogram the Flash memory at

will through the use of standard routines contained in

the Boot ROM (In-Application Programming).

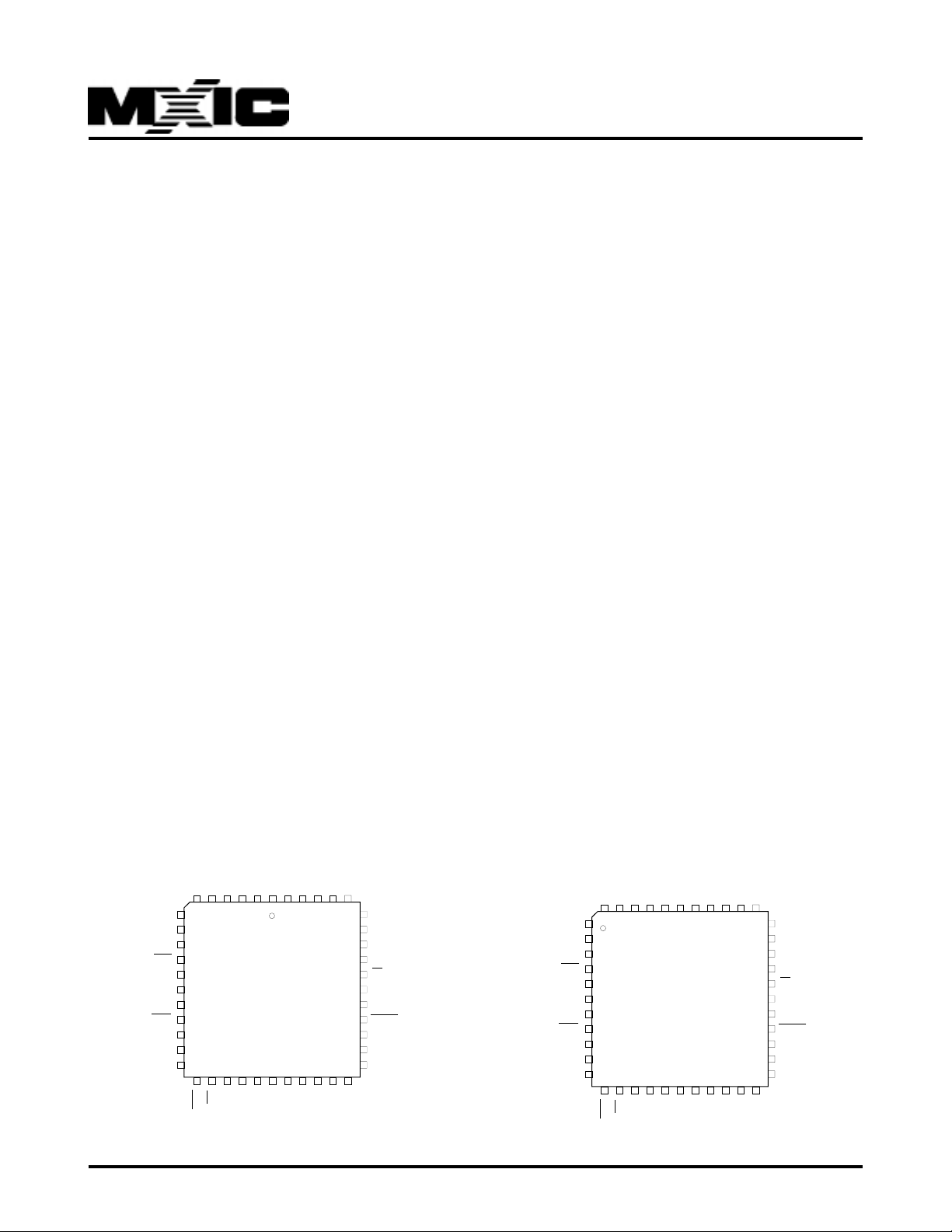

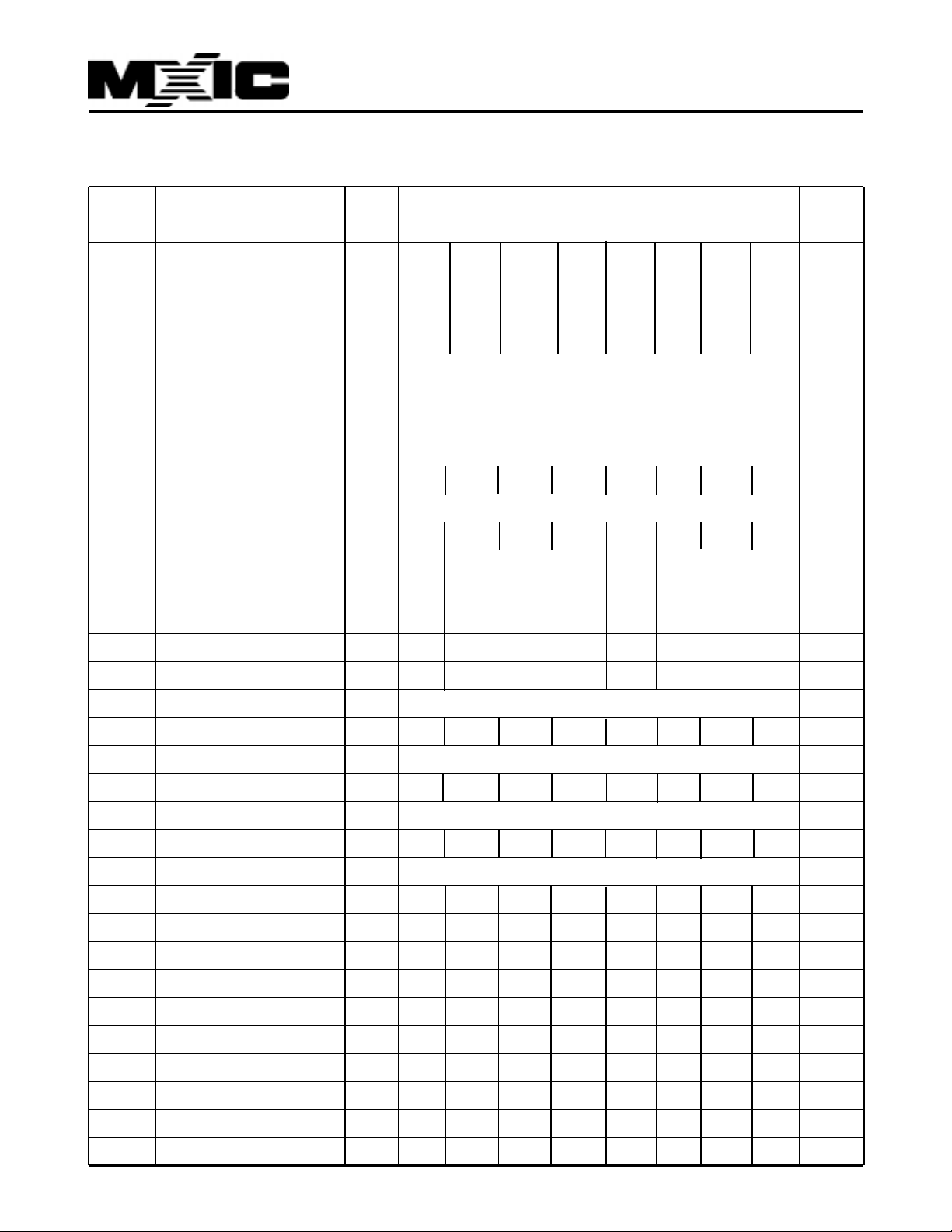

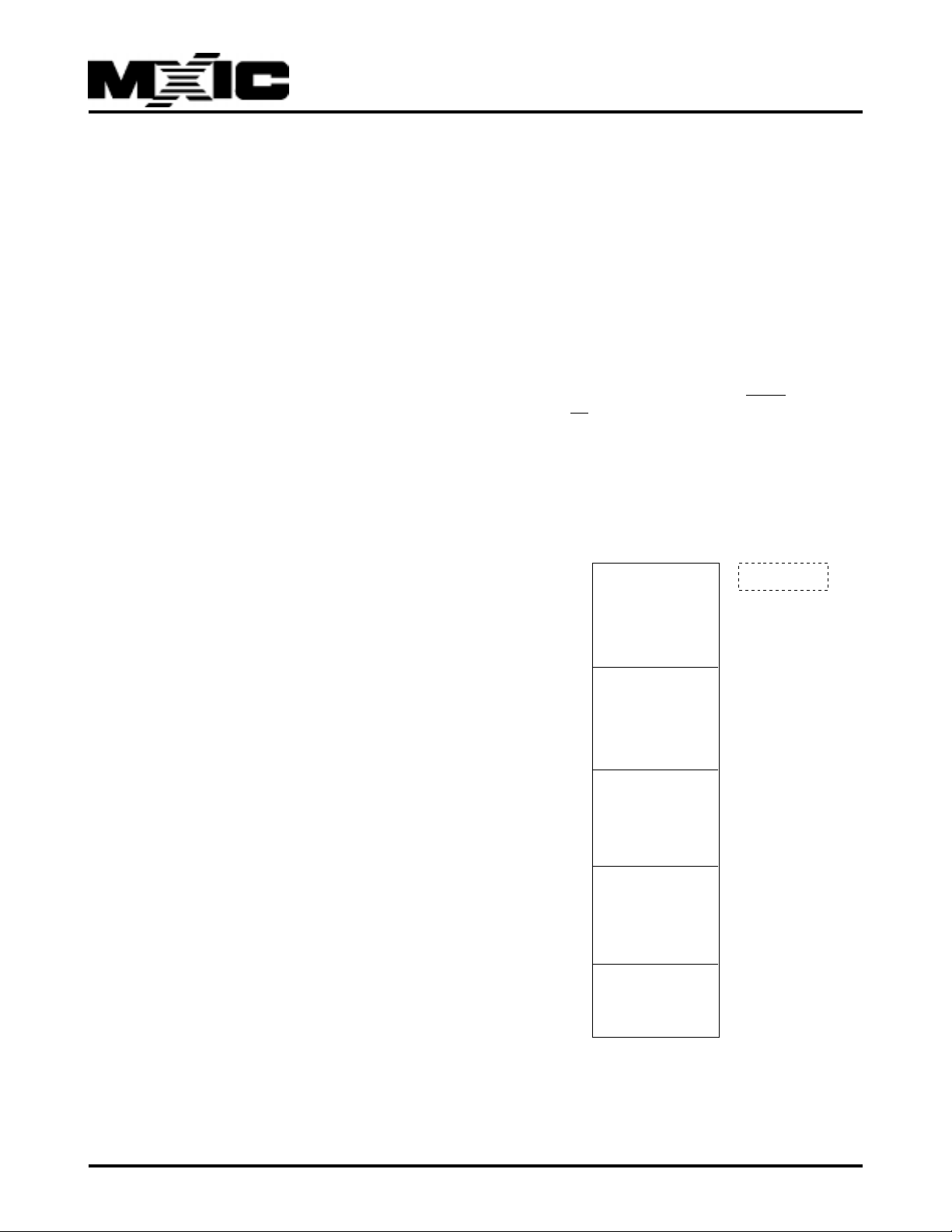

PIN CONFIGURATIONS

44 PLCC

P1.4/RxD1

P1.3/A3

P1.2/A2

P1.1/A1

P1.0/A0/WRH

P1.5/TxD1

P1.7/T2EX

P3.0/RxD0

P3.1/TxD0

P3.2/INT0

P3.3/INT1

P3.5/T1/BUSW

P/N:PM0625

P1.6/T2

RST

NC

P3.4/T0

64440

7

12

17

18 23 28

P3.7/RD

P3.6/WRL

1

MX10EXAQC

SS

V

XTAL2

XTAL1

VSSVDDP0.0/A4D0

P0.1/A5D1

P0.2/A6D2

DD

V

P2.0/A12D8

P2.1/A13D9

P2.2/A14D10

P2.3/A15D11

P0.3/A7D3

P0.4/A8D4

39

P0.5/A9D5

P0.6/A10D6

P0.7/A11D7

EA/VPP/WAIT

NC

34

ALE

PSEN

P2.7/A19D15

P2.6/A18D14

P2.5/A17D13

29

P2.4/A16D12

44 LQFP

1

P1.5/TxD1

P1.6/T2

P1.7/T2EX

RST

P3.0/RxD0

NC

P3.1/TxD0

P3.2/INT0

P3.3/INT1

P3.4/T0

P3.5/T1/BUSW

P1.4/RxD1

P1.3/A3

P1.2/A2

P1.1/A1

P1.0/A0/WRH

VSSVDDP0.0/A4D0

P0.1/A5D1

44 34

1

MX10EXAUC

11

12 22

SS

DD

V

V

XTAL2

XTAL1

P3.7/RD

P3.6/WRL

P2.0/A12D8

P2.1/A13D9

P2.2/A14D10

P0.2/A6D2

P0.3/A7D3

P0.4/A8D4

33

P0.5/A9D5

P0.6/A10D6

P0.7/A11D7

EA/VPP/WAIT

NC

ALE

PSEN

P2.7/A19D15

P2.6/A18D14

P2.5/A17D13

23

P2.3/A15D11

P2.4/A16D12

REV. 1.1, MAY 05, 1999

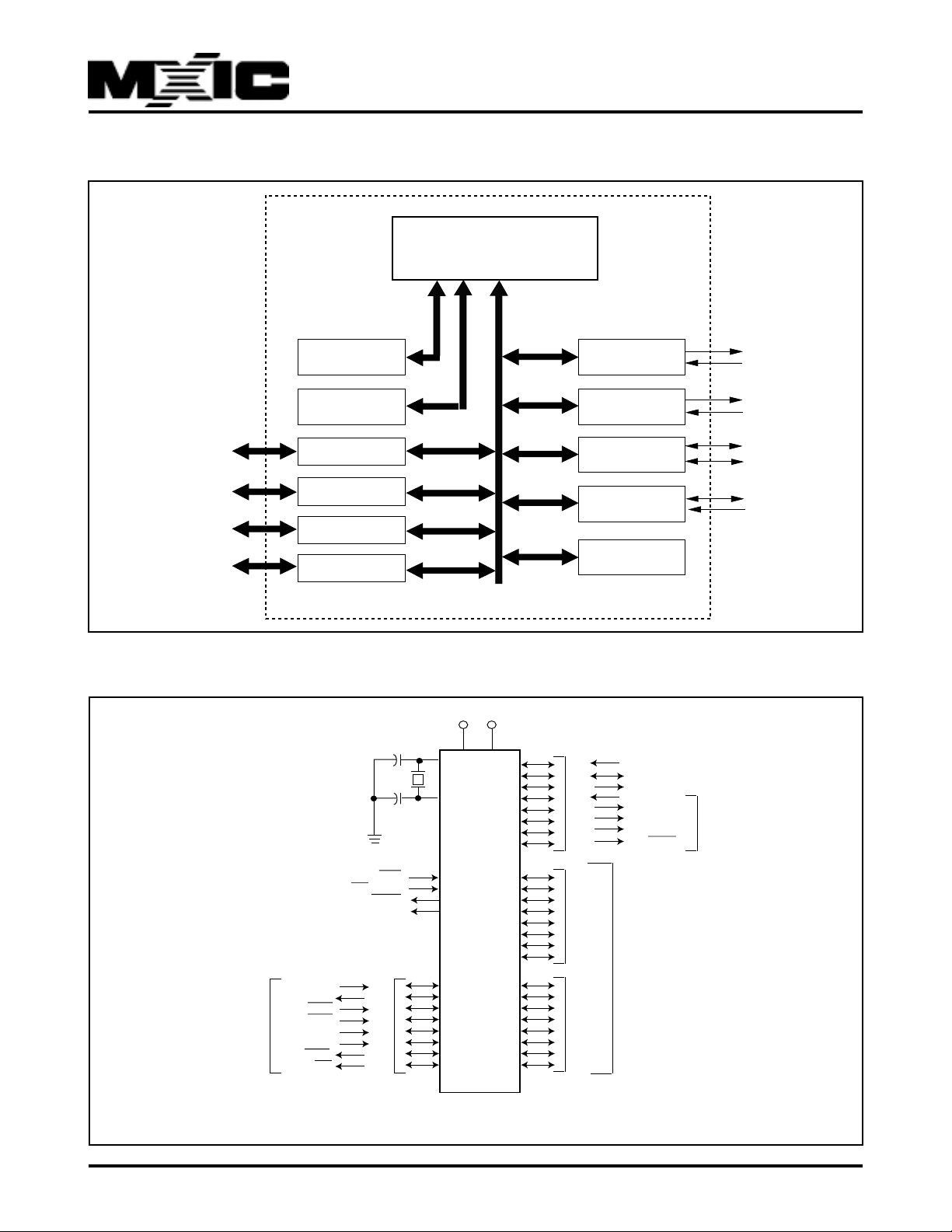

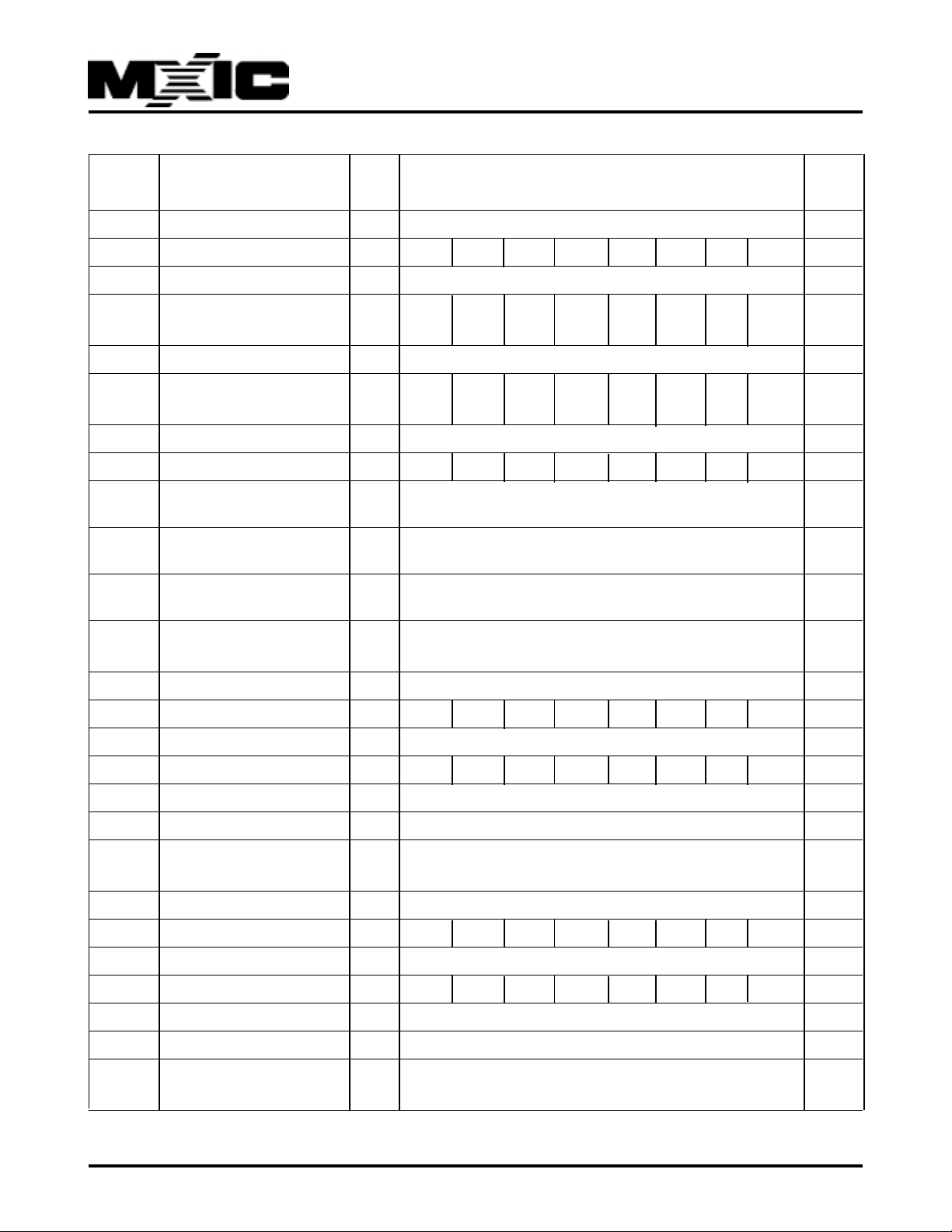

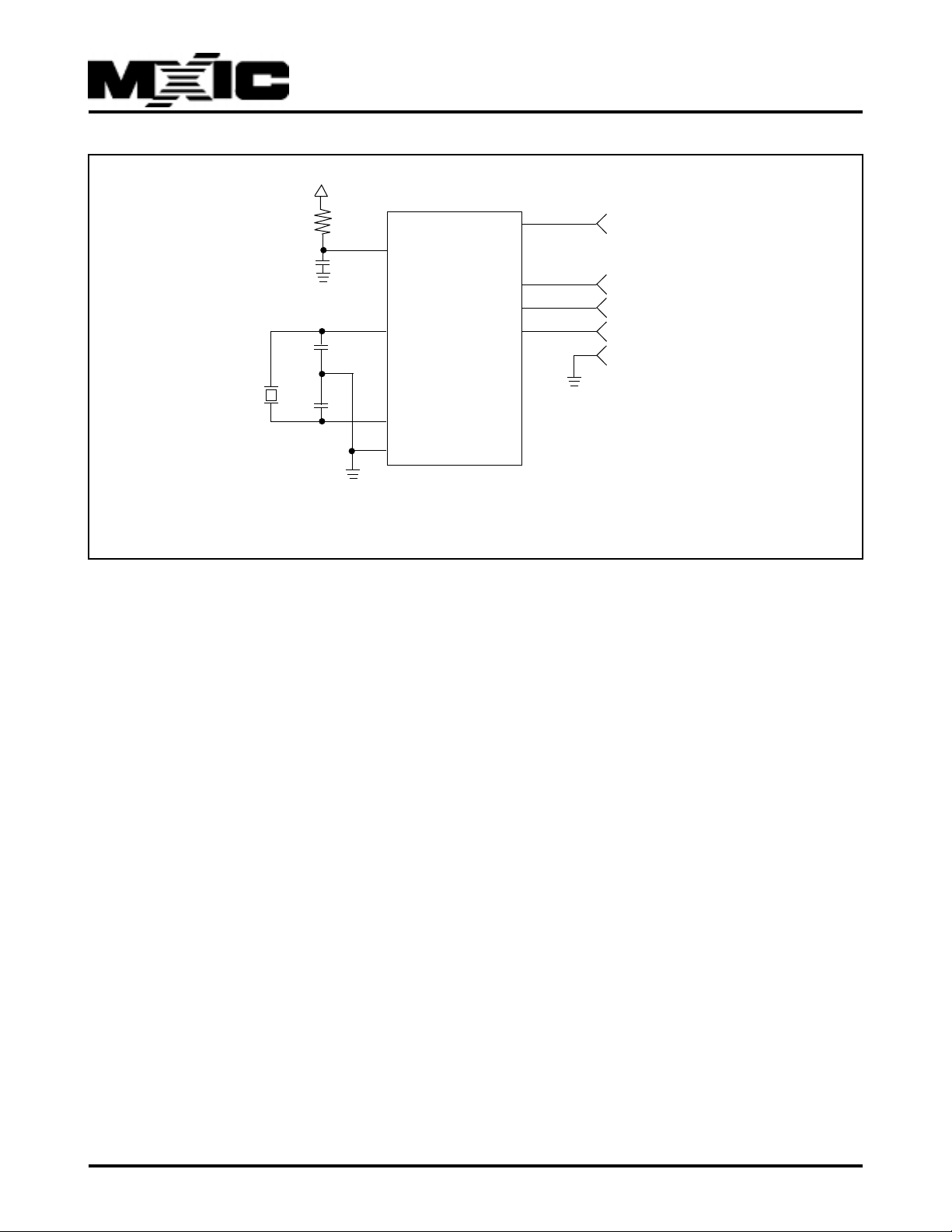

BLOCK DIAGRAM

MX10EXA

XA CPU Core

LOGIC SYMBOL

Memory Bus

64K Bytes

FLASH

2048 Bytes

Static RAM

Port 0

Port 1

Port 2

Port 3

Program

XTAL1

XTAL2

Data

Bus

VDD VSS

SFR

Bus

PORT 1

UART0

UART1

Timer 0,1

Timer 2

Watchdog

Timer

T2EX*

T2*

TxD1

RxD1

A3

A2

A1

A0/WRH

BUS

ADDRESS

P/N:PM0625

RxD0

TxD0

INT0

INT1

T0

T1/BUSW

WRL

RD

ALTERNATE FUNCTIONS

RST

EA/WAIT

PSEN

ALE

PORT 2PORT 0

PORT 3

* NOT AVAILABLE ON 40-PIN DIP PACKAGE

2

ADDRESS AND DATA BUS

REV. 1.1, MAY 05, 1999

MX10EXA

PIN DESCRIPTIONS

MNEMONIC PIN. NO. TYPE NAME AND FUNCTION

PLCC LQFP

V SS 1, 22 16,39 I Ground: 0V reference.

V DD 23, 44 17,38 I Power Supply: This is the power supply voltage for normal, idle, and

power down operation.

P0.0-P0.7 43-36 37-30 I/O Port 0: Port 0 is an 8-bit I/O port with a user-configurable output type.

Port 0 latches have 1s written to them and are configured in the quasibidirectional mode during reset. The operation of port 0 pins as inputs

and outputs depends upon the port configuration selected. Each port

pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details.

When the external program/data bus is used, P ort 0 becomes the multiplexed low data/instruction byte and address lines 4 through 11.

P1.0-P1.7 2- 9 40-44, I/O Port 1: Port 1 is an 8-bit I/O port with a user-configurable output type.

1- 3 Port 1 latches have 1s written to them and are configured in the quasi-

bidirectional mode during reset. The operation of port 1 pins as inputs

and outputs depends upon the port configuration selected. Each port

pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details.

Port 1 also provides special functions as described below .

240OA0/WRH: Address bit 0 of the external address bus when the external

data bus is configured for an 8 bit width. When the external data bus is

configured for a 16 bit width, this pin becomes the high byte write

strobe.

341OA1: Address bit 1 of the external address bus.

442OA2: Address bit 2 of the external address bus.

543OA3: Address bit 3 of the external address bus.

644IRxD1 (P1.4): Receiv er input for serial port 1.

71OTxD1 (P1.5): Transmitter output f or serial port 1.

8 2 I/O T2 (P1.6): Timer/counter 2 external count input/clock out.

93IT2EX (P1.7): Timer/counter 2 reload/capture/direction control

P2.0-P2.7 24-31 18-25 I/O Port 2: Port 2 is an 8-bit I/O port with a user-configurable output type.

Port 2 latches have 1s written to them and are configured in the quasi-

bidirectional mode during reset. The operation of port 2 pins as inputs

and outputs depends upon the port configuration selected. Each port

pin is configured independently. Refer to the section on I/O port con-

figuration and the DC Electrical Characteristics for details.

When the external program/data bus is used in 16-bit mode, Por t 2

becomes the multiplexed high data/instruction byte and address lines

12 through 19. When the external program/data bus is used in 8-bit

mode, the number of address lines that appear on port 2 is user pro-

grammable.

P/N:PM0625

REV. 1.1, MAY 05, 1999

3

MX10EXA

MNEMONIC PIN. NO. TYPE NAME AND FUNCTION

PLCC LQFP

P3.0-P3.7 11,13-19 5,7-13 I/O Port 3: Port 3 is an 8-bit I/O port with a user configurab le output type.

Port 3 latches have 1s written to them and are configured in the quasi-

bidirectional mode during reset. the operation of port 3 pins as inputs

and outputs depends upon the port configuration selected. Each port

pin is configured independently. Refer to the section on I/O port con-

figuration and the DC Electrical Characteristics for details.

Port 3 also provides various special functions as described below .

11 5 I RxD0 (P3.0): Receiv er input for serial port 0.

13 7 O TxD0 (P3.1): Transmitter output for serial port 0.

14 8 I INT0 (P3.2): External interrupt 0 input.

15 9 I INT1 (P3.3): External interrupt 1 input.

16 10 I/O T0 (P3.4): Timer 0 external input, or timer 0 overflow output.

17 11 I/O T1/BUSW (P3.5): Timer 1 external input, or timer 1 overflow output.

The value on this pin is latched as the external reset input is released

and defines the default external data bus width (BUSW). 0 = 8-bit bus

and 1 = 16-bit bus.

18 12 O WRL (P3.6): External data memory low byte write strobe.

19 13 O RD (P3.7): External data memory read strobe.

RST 10 4 I Reset: A low on this pin resets the microcontroller, causing I/O ports

and peripherals to take on their default states, and the processor to

begin execution at the address contained in the reset v ector . Refer to

the section on Reset for details.

ALE 33 27 I/O Address Latch Enable: A high output on the ALE pin signals external

circuitry to latch the address por tion of the multiplexed address/data

bus. A pulse on ALE occurs only when it is needed in order to process

a bus cycle.

PSEN 32 26 O Program Store Enable: The read strobe f or external program memory .

When the microcontroller accesses external program memory , PSEN

is driven low in order to enable memory devices. PSEN is only active

when external code accesses are performed.

EA/WAIT 35 29 I External Access/Wait/Programming Suppl y V oltage: The EA input

/VPP determines whether the internal program memory of the microcontroller

is used for code execution. The value on the EA pin is latched as the

external reset input is released and applies during later execution. When

latched as a 0, external program memory is used exclusively, when

latched as a 1, internal program memory will be used up to its limit, and

external program memory used above that point. After reset is released,

this pin takes on the function of bus Wait input. If Wait is asserted high

during any external bus access, that cycle will be e xtended until Wait

is released. During EPROM programming, this pin is also the program-

ming supply voltage input.

XTAL1 21 15 I Crystal 1: Input to the inv erting amplifier used in the oscillator circuit

and input to the internal clock generator circuits.

XTAL2 20 14 O Crystal 2: Output from the oscillator amplifier.

P/N:PM0625

REV. 1.1, MAY 05, 1999

4

MX10EXA

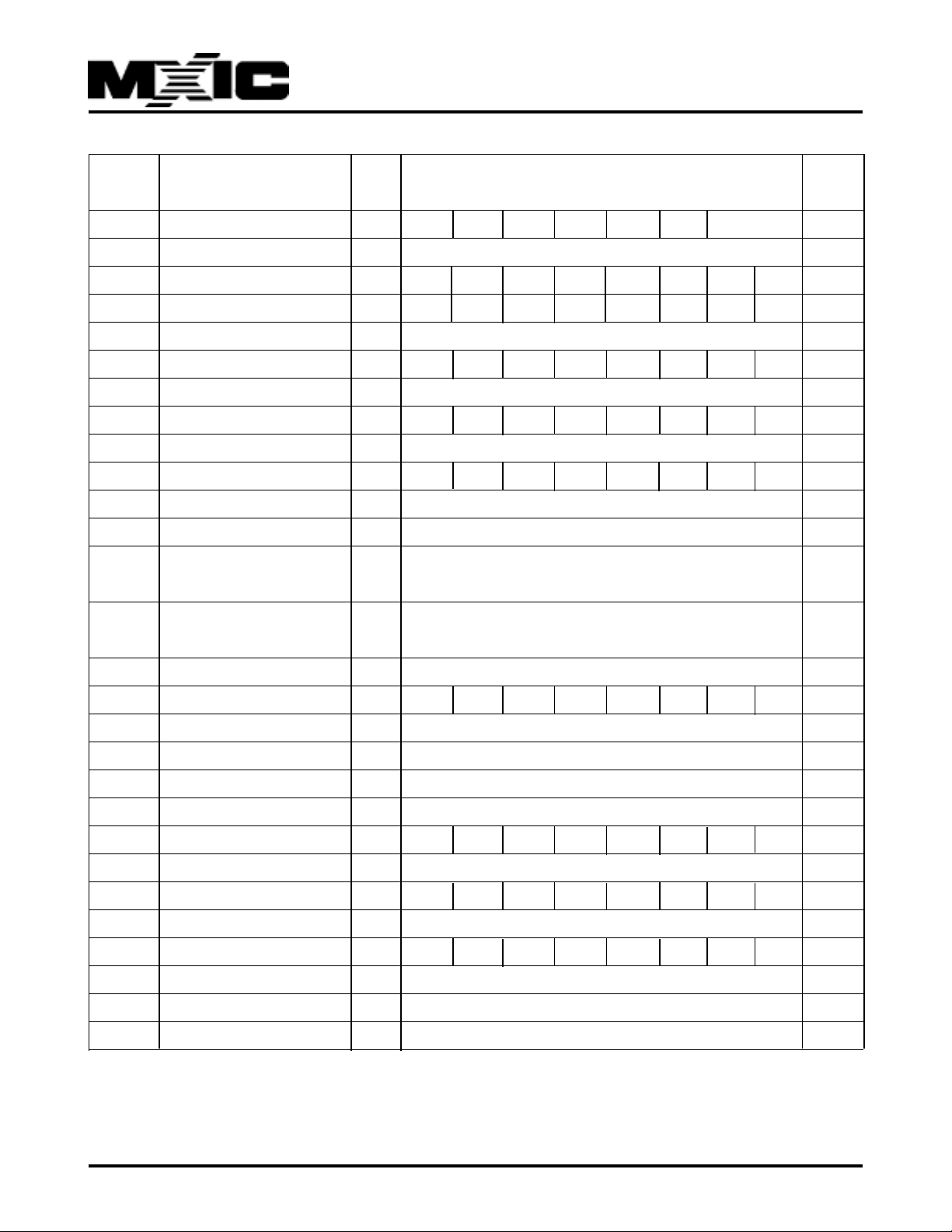

SPECIAL FUNCTION REGISTERS

NAME DESCRIPTION SFR BIT FUNCTIONS AND ADDRESSES Reset

ADDRESS MSB LSB VALUE

AUXR Auxiliary function register 44C ENBOOT FMIDLE PWR_VLD --- --- --- --- ---

BCR Bus configuration register 46A — — — --- --- --- WAITD BUSD BC2 BC1 BC0 Note 1

BTRH Bus timing register high byte 469 DW1 D W0 DWA1 DWA0 DR1 DR0 DRA1 DRA0 FF

BTRL Bus timing register low byte 468 WM1 WM0 ALEW — --- CR1 CR0 CRA1 CRA0 EF

CS Code segment 443 00

DS Data segment 44 1 00

ES Extra segment 44 2 0 0

33F 33E 33D 33C 33B 33A 339 338

IEH* Interrupt enable high byte 427 --- --- --- --- ETI1 ERI1 ETI0 ERI0 00

337 336 335 334 333 332 331 330

IEL* Interrupt enable low byte 4 26 EA --- --- ET2 ET1 EX 1 ET0 EX0 00

IPA0 Interrupt priority 0 4A0 --- PT0 --- PX0 0 0

IPA1 Interrupt priority 1 4A1 --- PT1 --- PX1 00

IPA2 Interrupt priority 2 4A2 --- --- --- PT2 0 0

IPA4 Interrupt priority 4 4A4 --- PTI0 --- PRI0 00

IPA5 Interrupt priority 5 4A5 --- PTI1 --- PRI1 00

387 386 385 384 383 382 381 380

P0* P ort 0 430 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 F F

38F 38E 38D 38C 38B 38A 389 388

P1* Port 1 431 T2EX T2 TxD1 RxD1 A3 A2 A1 WRH FF

397 396 395 394 393 392 391 390

P2* Port 2 432 P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0 FF

39F 39E 39D 39C 39B 39A 399 398

P3* Port 3 433 RD WR T1 T0 INT1 INT0 TxD0 RxD0 F F

P0CFGA Port 0 configuration A 47 0 Note 5

P1CFGA Port 1 configuration A 47 1 Note 5

P2CFGA Port 2 configuration A 47 2 Note 5

P3CFGA Port 3 configuration A 47 3 Note 5

P0CFGB Port 0 configuration B 4F0 Note 5

P1CFGB Port 1 configuration B 4F1 Note 5

P2CFGB Port 2 configuration B 4F2 Note 5

P3CFGB Port 3 configuration B 4F3 Note 5

P/N:PM0625

5

REV. 1.1, MAY 05, 1999

MX10EXA

NAME DESCRIPTION SFR BIT FUNCTIONS AND ADDRESSES Reset

address M SB LSB VALUE

227 226 225 224 223 222 221 220

PCON* Power control register 404 --- --- --- --- --- --- PD IDL 00

20F 20E 20D 20C 20B 20A 209 208

PSWH* Program status word 40 1 SM TM RS 1 RS0 IM3 IM2 IM1 I M 0 Note 2

(high byte)

207 206 205 204 203 202 201 200

PSWL* Program status word 400 C AC --- --- --- V N Z Note 2

(low byte)

217 216 215 214 213 212 211 210

PSW51* 80C51 compatible PSW 40 2 C AC F0 RS1 RS0 V F1 P Note 3

RTH0 Timer 0 extended reload, 45 5 00

high byte

RTH1 Timer 1 extended reload, 457 00

high byte

RTL0 Timer 0 extended reload, 4 5 4 0 0

low byte

RTL1 Timer 1 extended reload, 4 5 6 0 0

low byte

307 306 305 304 303 302 301 300

S0CON* Serial port 0 control register 420 SM0_0 SM1_0 SM2_0 REN_0 TB8_0 RB8_0 TI_0 RI_0 00

30F 30E 30 D 30C 30B 30A 309 308

S0STAT* Serial port 0 extended status 4 21 --- --- --- --- FE0 BR 0 OE0 STINT0 00

S0BUF Serial port 0 buffer register 460 x

S0ADDR Serial port 0 address register 461 0

S0ADEN Serial port 0 address enable 462 00

register

327 326 325 324 323 322 321 320

S1CON* Serial port 1 control register 424 SM0_1 SM1_1 SM2_1 REN_1 TB8_1 RB8_1 TI_1 RI_1 00

32F 32E 32 D 3 2 C 32B 32A 329 328

S1STAT* Serial port 1 extended status 425 --- --- --- --- FE1 B R1 OE1 STINT1 00

S1BUF Serial port 1 buffer register 464 x

S1ADDR Serial port 1 address register 465 0 0

S1ADEN Serial port 1 address enabler 46 6 0 0

register

P/N:PM0625

REV. 1.1, MAY 05, 1999

6

MX10EXA

NAME DESCRIPTION SFR BIT FUNCTIONS AND ADDRESSES Reset

address M SB LSB VALUE

SCR System configuration register 440 --- --- --- --- PT1 PT0 CM PZ 00

21F 21E 21D 21C 21B 21A 219 218

SSEL* Segment selection register 40 3 ESWEN R6SEG R5SEG R4SEG R3SEG R2SEG R1SEG R0SEG 00

SWE Software Interrupt Enable 47A --- SWE7 SWE6 SWE5 SWE4 SWE3 SWE2 SWE1 0 0

357 356 355 354 353 352 351 350

SWR* Software Interrupt Request 42A --- SWR7 SWR6 SWR5 SWR4 SWR3 SWR2 SWR1 0 0

2C7 2C6 2C5 2C4 2C3 2C2 2C1 2C0

T2CON* Timer 2 control register 4 18 TF2 EXF2 RCLK0 TCLK0 EXEN2 T R2 C/T2 CP/RL2 00

2CF 2CE 2CD 2CC 2CB 2CA 2C9 2C8

T2MOD* Timer 2 mode control 41 9 --- --- RCLK1 TCLK1 --- -- - T2OE DCEN 00

TH2 Timer 2 high byte 459 0 0

TL2 Timer 2 low byte 458 00

T2CAPH Timer 2 capture register, 4 5 B 00

high byte

T2CAPL Timer 2 capture register, 4 5 A 00

low byte

287 286 285 284 283 282 281 280

TCON* Timer 0 and 1 control register410 TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 00

TH0 Timer 0 high byte 451 0 0

TH1 Timer 1 high byte 453 00

TL0 Timer 0 low byte 450 00

TL1 Timer 1 low byte 452 00

TMOD Timer 0 and 1 mode control 4 5 C GATE C/T M1 M0 GATE C/T M1 M0 0 0

28F 28E 28D 2 8C 28B 28A 289 288

TSTAT* Timer 0 and 1 extended status 411 --- --- --- --- --- T1OE --- T0OE 00

2FF 2FE 2FD 2FC 2FB 2FA 2F9 2F8

WDCON* Watchdog control register 41F PRE2 PRE1 PRE0 --- --- WDRUN WDTOF --- Note 6

WDL Watchdog timer reload 45F 00

WFEED1 Watchdog feed 1 45D x

WFEED2 Watchdog feed 2 45E x

P/N:PM0625

7

REV. 1.1, MAY 05, 1999

MX10EXA

NOTES:

* SFRs are bit addressable.

1. At reset, the BCR register is loaded with the binary value 0000 0a11, where "a" is the value on the B USW pin. This

defaults the address bus size to 20 bits, Since the MX10EXA has only 20 address lines.

2. SFR is loaded from the reset v ector.

3. All bits except F1, F0, and P are loaded from the reset vector. Those bits are all 0.

4. Unimplemented bits in SFRs are X (unknown) at all times. Ones should not be written to these bits since they may

be used for other purposes in future XA derivatives. The reset value shown f or these bits is 0.

5. Port configurations def ault to quasi-bidirectional when the XA begins e x ecution from internal code memory after

reset, based on the condition found on the EA pin. Thus all PnCFGA registers will contain FF and PnCFGB

registers will contain 00. When the XA begins e xecution using external code memory , the default configuration f or

pins that are associated with the external bus will be push-pull. The PnCFGA and PnCFGB register contents will

reflect this difference.

6. The WDCON reset value is E6 for a W atchdog reset, E4 f or all other reset causes.

7. The MX10EXA implements an 8-bit SFR bus. All SFR accesses must be 8-bit operations .

Attempts to write 16 bits to an SFR will actually write only the lower 8 bits. Sixteen bit SFR reads will return

undefined data in the upper byte.

P/N:PM0625

REV. 1.1, MAY 05, 1999

8

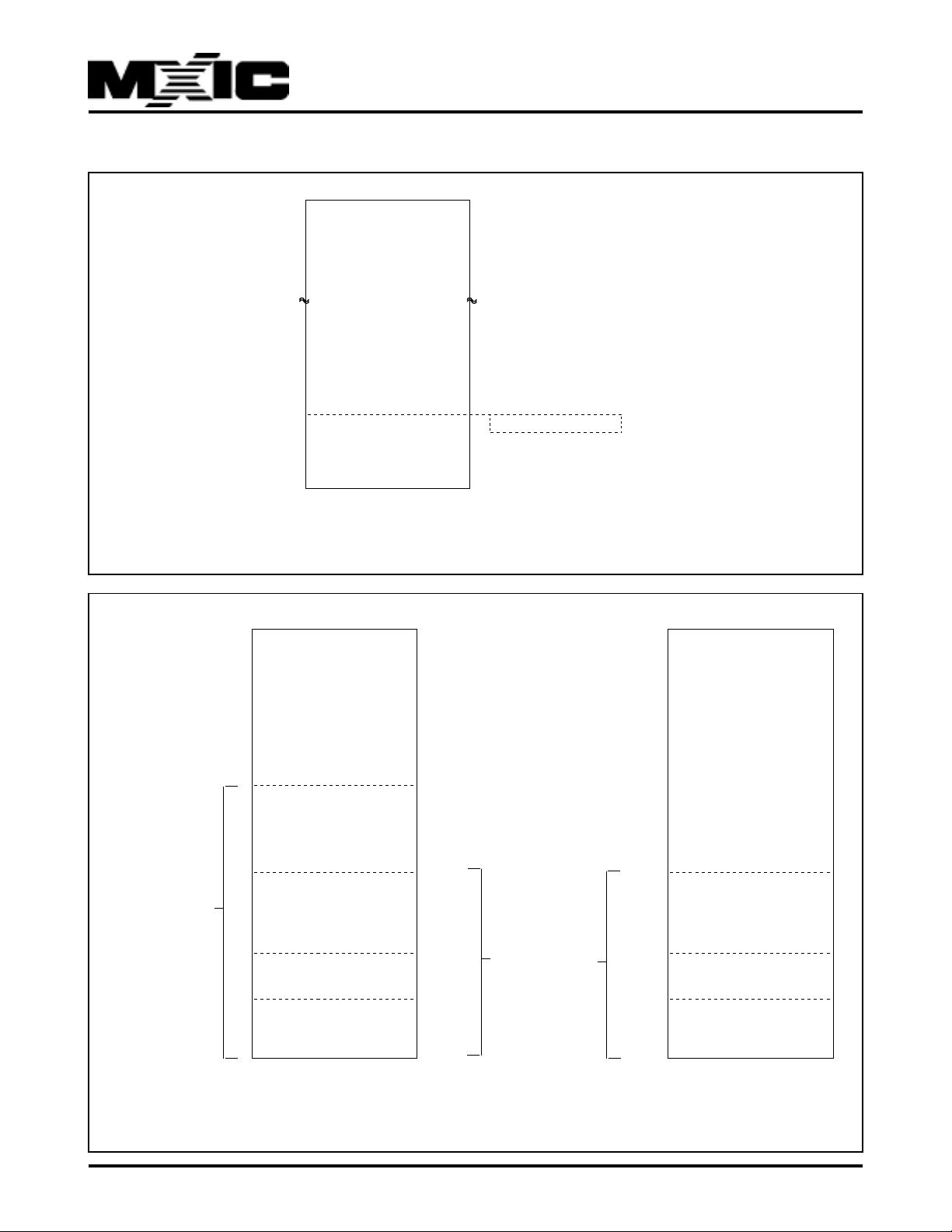

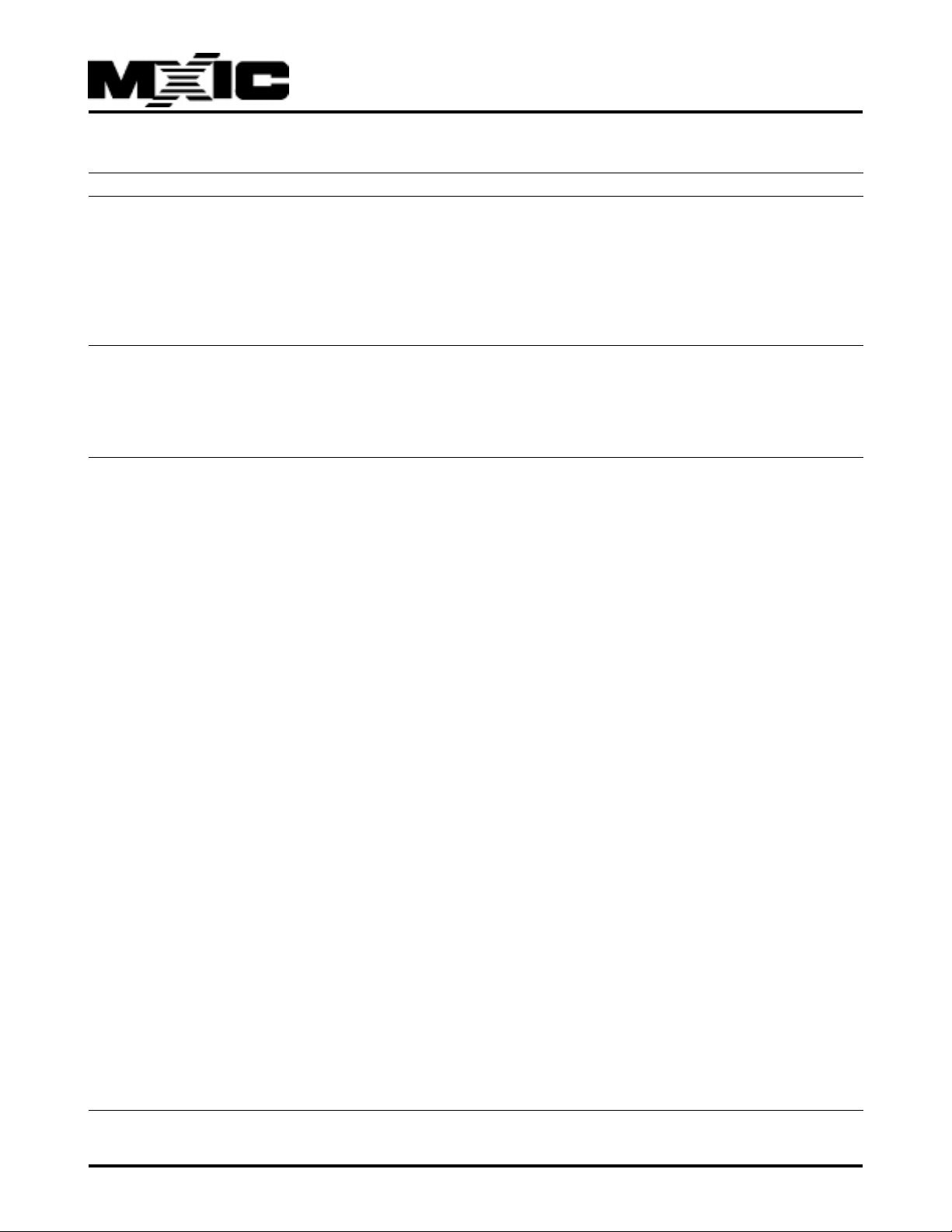

FFFFFh

UP TO 1M BYTES

TOTAL CODE

MEMORY

MX10EXA

2K BYTES

ON-CHIP DATA

MEMORY (RAM)

10000h

FFFFh

64K BYTEs

ON-CHIP

CODE MEMORY

0000h

Note:The Boot ROM replaces the top 2K bytes of Flash memory

when it is enable via the xxx bit in xxx.

Figure 1. XA Program Memory Map

2K BYTE BOOT ROM

Data Segment 0

FFFFFh

DATA MEMORY

(INDIRECTLY ADDRESSED,

OFF-CHIP)

0800h

07FFh

DATA MEMORY

(INDIRECTLY ADDRESSED,

ON CHIP)

0400H

03FFh

DATA MEMORY

(DIRECTLY AND INDIRECTLY

ADDRESSABLE, ON CHIP)

BIT-ADDRESSABLE

DATA AREA

0040h

003Fh

DIRECTLY

ADDRESSED DATA

(1K PER SEGMENT)

0020h

DATA MEMORY

001Fh

(DIRECTLY AND INDIRECTLY

ADDRESSABLE, ON CHIP)

0000h

FFFFh

F800h

FFFFFh

0400H

03FFh

0040h

003Fh

0020h

001Fh

0000h

Other Data Segments

DATA MEMORY

(INDIRECTLY ADDRESSED,

OFF-CHIP)

DATA MEMORY

(DIRECTLY AND INDIRECTLY

ADDRESSABLE, OFF-CHIP)

BIT-ADDRESSABLE

DATA AREA

DATA MEMORY

(DIRECTLY AND INDIRECTLY

ADDRESSABLE, OFF-CHIP)

P/N:PM0625

Figure 1. XA Data Memory Map

REV. 1.1, MAY 05, 1999

9

MX10EXA

FLASH EPROM MEMORY

GENERAL DESCRIPTION

The XA Flash memory augments EPROM functionality

with in-circuit electrical erasure and programming. The

Flash can be read and written as bytes. The Chip Erase

operation will erase the entire program memory . The Block

Erase function can erase any single Flash block. In-circuit programming and standard parallel programming are

both available. On-chip erase and write timing generation contribute to a user friendly programming interface.

The XA Flash reliably stores memory contents even after 10,000 erase and program cycles. The cell is designed

to optimize the erase and programming mechanisms. In

addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and programming operations produces reliable cycling. For InSystem Programming, the XA can use a single +5 V

power supply. Faster In-system Programming may be

obtained, if required, through the use of a+12V VPP supply . Parallel prog ramming (using separate programming

hardware) uses a+12V VPP supply.

FEA TURES

• Flash EPROM internal program memory with Block

Erase.

• Internal 2k byte fixed boot ROM, containing low-level

programming routines and a default loader. The Boot

ROM can be turned off to provide access to the full 64k

byte Flash memory.

• Boot vector allows user provided Flash loader code to

reside anywhere in the Flash memory space. This

configuration provides flexibility to the user.

• Default loader in Boot ROM allows programming via the

serial port without the need for a user provided loader.

• Up to 1Mbyte external program memory if the internal

program memory is disabled(EA=0).

• Programming and erase voltage VPP = VDD or 12V

±5% for ISP, 12V ±5% for parallel programming.

• Read/Programming/Erase:

- Byte-wise read (60 ns access time at 4.5 V).

- Byte Programming (40us).

- Typical erase times :

Block Erase (8k bytes or 16k bytes) in 1.6 seconds.

Full Erase (64k bytes) in 1.6 seconds.

• In-circuit programming via user selected method, typically RS232 or parallel I/O port interface.

• Programmable security for the code in the Flash

• 10,000 minimum erase/program cycles

• 10 year minimum data retention.

P/N:PM0625

REV. 1.1, MAY 05, 1999

10

MX10EXA

CAP ABILITIES OF THE PHILIPS 89C51 FLASHBASED MICROCONTROLLERS

Flash organization

The XA contains 64k bytes of Flash program memory.

This memory is organized as 5 separate blocks. The

first two blocks are 8k bytes in size, filling the program

memory space from address 0 through 3FFF hex. The

final three blocks are 16k bytes in size and occupy addresses from 4000 through FFFF hex.

Figure 3 depicts the Flash memory configuration.

Flash Programming and Erasure

The XA Flash microcontroller supports a number of programming possibilities for the on-chip Flash memory . The

Flash memory may be programmed in a parallel fashion

on standard programming equipment in a manner similar

to an EPROM microcontroller. The XA microcontroller is

able to program its own Flash memory while the application code is running. Also, a default loader built into a

Boot ROM allows programming blank devices serially

through the UAR T .

Using any of these types of programming, any of the

individual blocks may be er ased separately , or the entire

chip may be erased. Programming of the Flash memory

is accomplished one byte at a time.

ENBOOT and PWR_VLD

Setting the ENBOOT bit in the AUXR register enables

the Boot ROM and activates the on-chip VPP generator if

VPP is connected to rather than 12V externally. The

PWR_VLD flag indicates that VPP is available for

programming and erase operations. This flag should be

checked prior to calling the Boot ROM for programming

and erase services. When ENBOOT is set, it typically

takes 5 microseconds for the internal programming

voltage to be ready.

The ENBOOT bit will automatically be set if the status

byte is non-zero during reset, or when PSEN is low , ALE

is high, and EA is high at the falling edge of reset. Otherwise, ENBOOT will be cleared during reset.

When programming functions are not needed, ENBOO T

may be cleared. This enables access to the 2k bytes of

Flash code memory that is overlaid by the Boot ROM,

allowing a full 64k bytes of Flash cede memory.

FFFF

BOOT ROM

BLOCK 4

16K BYTES

C000

BLOCK 3

16K BYTES

FFFF

F800

Boot ROM

When the microcontroller programs its own Flash

memory , all of the low le vel details are handled b y code

that is permanently contained in a 2k byte “Boot ROM”

that is separate from the Flash memory . A user progr am

simply calls the entry point with the appropriate

parameters to accomplish the desired operation. Boot

ROM operations include things like: erase block, program

byte, v erity byte, program security lock bit, etc. The Boot

ROM overlays the program memory space at the top of

the address space from F800 to FFFF hex, when it is

enabled by setting the ENBOOT bit at AUXR1.7.. The

Boot ROM may be turned off so that the upper 2k bytes

of Flash program memory are accessible for execution.

P/N:PM0625

11

PROGRAM

ADDRESS

8000

BLOCK 2

16K BYTES

4000

BLOCK 1

8K BYTES

2000

BLOCK 0

8K BYTES

0000

Figure 3. Flash Memory Configuration

REV. 1.1, MAY 05, 1999

MX10EXA

FMIDLE

The FMIDLE bit in the AUXR register allows sa ving additional power by turning off the Flash memory when the

CPU is in the Idle mode. This m ust be done just prior to

initiating the Idle mode, as shown below .

OR AUXR, #$40 ;Set Flash memory to idle

mode.

O R PCON, #$0l ;Turn on Idle mode.

. . ;Execution resumes here when

Idle mode terminates.

When the Flash memory is put into the Idle mode by

setting FMIDLE, restarting the CPU upon exiting Idle

mode takes slightly longer , about 3 microseconds. Howeve r, the standby current consumed by the Flash memory

is reduced from about 8mA to about 1mA.

Default Loader

A default loader that accepts programming commands

in a predetermined format is contained permanently in

the Boot ROM. A factory fresh device will enter this loader

automatically if it is powered up without first being programmed by the user . Loader commands include functions such as erase block; program Flash memory; read

Flash memory; and blank check.

Boot Vector

The XA contains two special FLASH registers: the BOOT

VECTOR and the STATUS BYTE.

The "Boot Vector" allows forcing the e xecution of a user

supplied Flash loader upon reset, under two specific sets

of conditions. At the falling edge of reset, the XA examines the contents of the Status Byte. If the Status Byte

is set to zero, power-up execution starts at location

0000H, which is the normal start address of the user’s

application code.

NOTE: When erasing the Status Byte or Boot Vector,

these bytes are erased at the same time. It is necessary

to reprogram the Boot Vector after erasing and updating

the Status Byte.

Hardware Activation of the Boot V ector

Program ex ecution at the Boot V ector ma y also be forced

from outside of the microcontroller by setting the correct

state on a few pins . While Reset is asserted, the PSEN

pin must be pulled low , the ALE pin allowed to float high

(need not be pulled up externally), and the EA pin driven

to a logic high (or up to VPP). Then reset may be released.

This is the same effect as having a non-zero status byte.

This allows building an application that will normally execute the end user’s code but can be manually forced

into ISP operation. The Boot ROM is enab led when use

of the Boot Vector is forced as described above, so the

branch may go to the default loader. Conversely, user

code in the top 2k bytes of the Flash memory may not

be ex ecuted when the Boot Vector is used.

If the factory defauolt setting for the BPC (F800h) is

changed, it will no longer point to the ISP masked-ROM

boot loader code. If this happens, the only possible way

to change the contents of the Boot Vector is through the

parallel programming method, provided that the end user

application does not contain a customized loader that

provides for erasing and reprogramming of the Boot V ector and Status Byte.

After programming the FLASH, the status byte should

be erased to zero in order to allow e xecution of the user’ s

application code beginning at address 0000H.

When the Status Byte is set to a value other than zero,

the Boot Vector is used as the reset vector (4 bytes),

including the Boot Program Counter (BPC) and the Boot

PSW (BPSW). The f actory default settings are 8000h for

the BPSW and F800h for the BPC, which corresponds

to the address F900h for the factory masked-ROM ISP

boot loader. The Status Byte is automatically set to a

non-zero value when a programming error occurs. A custom boot loader can be written with the Boot Vector set

to the custom boot loader.

P/N:PM0625

REV. 1.1, MAY 05, 1999

12

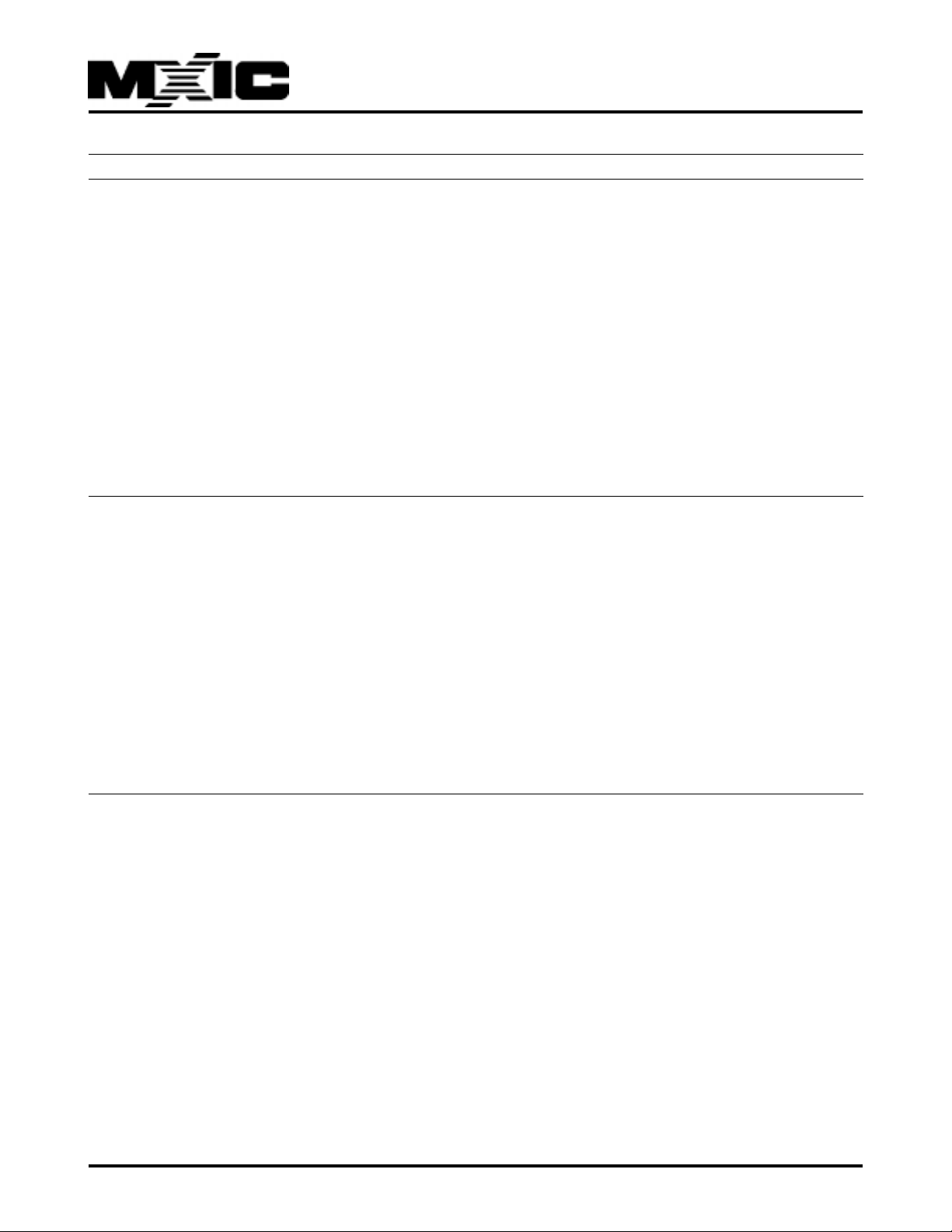

VCC

MX10EXA

RST

XT AL2

XTAL1

VSS

Figure 4. In-System Programming with a Minimum of Pins

In-System Programming (ISP)

In-System Programming (ISP) is performed without removing the microcontroller from the system. The In-System Programming (ISP) facility consists of a series of

internal hardware resources coupled with internal firmware to facilitate remote programming of the XA through

the serial port.

The In-System Programming (ISP) facility has made incircuit programming in an embedded application possible

with a minimum of additional expense in components

and circuit board area.

The ISP function uses five pins: TxD, RxD , VSS, and V

(see Figure 4). Only a small connector needs to be available to interface your application to an external circuit in

order to use this feature. The VPP supply should be adequately decoupled and VPP not allowed to exceed data

sheet limits.

Using In-System Programming (ISP)

When ISP mode is entered, the default loader first disables the watchdog timer to prevent a watchdog reset

from occurring during programming.

The ISP feature allows for a wide range of baud rates to

VPP

VDD

VxD

RxD

+12V±5% or VDD

+4.5V to 5.5V

TxD

RxD

VSS

be used in the application, independent of the oscillator

frequency . It is also adaptable to a wide range of oscillator frequencies. This is accomplished by measuring the

bit-time of a single bit in a received character . This inf ormation is then used to program the baud rate in terms of

timer counts based on the oscillator frequency . The ISP

feature requires that an initial character (a lowercase f)

be sent to the XA to establish the baud rate. The ISP

firmware provides auto-echo of received characters.

Once baud rate initialization has been performed, the

ISP firmware will only accept specific Intel Hex-type

records. Intel Hex records consist of ASCII characters

PP

used to represent hexadecimal values and are summarized below:

:NNAAAARRDD ..DDCC<crlf>

In the Intel Hex record, the “NN” represents the number

of data bytes in the record. The XA will accept up to 16

(10H) data bytes. The "AAAA"” string represents the address of the first byte in the record. If there are zero

bytes in the record, this field is often set to 0000. The

"RR" string indicates the record type. A record type of

"00" is a data record. A record type of "01" indicates the

end-of-file mark. In this application, additional record types

will be added to indicate either commands or data for the

P/N:PM0625

REV. 1.1, MAY 05, 1999

13

MX10EXA

ISP facility. The maximum number of data bytes in a

record is limited to 16 (decimal). ISP commands are summarized in Table 1.

As a record is received by the XA, the information in the

record is stored internally and a checksum calculation is

performed. The operation indicated b y the record type is

not performed until the entire record has been received.

Should an error occur in the checksum, the XA will send

an "X" out the serial port indicating a checksum error. If

the checksum calculation is found to match the

checksum in the record, then the command will be executed. In most cases, successful reception of the record

will be indicated by transmitting a "." character out the

serial port (displaying the contents of the internal program memory is an exception).

In the case of a Data Record (record type 00), an additional check is made. A "." character will NOT be sent

unless the record checksum matched the calculated

checksum and all of the bytes in the record were successfully programmed. For a data record, an "X" indicates that the checksum failed to match, and an "R"

character indicates that one of the bytes did not property program.

by the user into the microcontroller in a parallel fashion

or via the default loader during their manufacturing process. The entire initial Flash contents may be prog rammed

at that time, or the rest of the application may be programmed into the Flash memory at a later time, possibly

using the loader code to do the programming.

This application controlled programming capability allows

for the possibility of changing the application code in the

field. If the application circuit is embedded in a PC, or

has a way to establish a telephone data link to a user’s

or m a n u facturer’ s computer , ne w code could be downloaded from diskette or a manufacturer’s support system. There is even the possibility of conducting very

specialized remote testing of a failing circuit board by

the manufacturer by remotely programming a series of

detailed test programs into the application board and

checking the results.

Any user supplied loader should take the watchdog timer

into account. Typically , the watchdog timer w ould be disabled upon entry to the loader if it might be running, in

order to prevent a watchdog reset from occurring during

programming.

The ISP facility was designed so that specific crystal

frequencies were not required in order to generate baud

rates or time the programming pulses.

User Supplied Loader

A user program can simply decide at any time, for any

reason, to begin Flash programming operations. All it has

to do in advance is to instruct external circuitry to apply

+5V or +12V to the VPP pin, and make certain that the

Boot ROM is enabled. User code may contain a loader

designed to replace the application code contained in

the Flash memory by loading new code through any communication medium available in the application. This is

completely flexible and defined by the designer of the

system. It could be done serially using RS-232, serially

using some other method, or even parallel over a user

defined I/O port. The user has the freedom to choose a

method that does not interfere with the application circuit. As an added feature, the application program may

also use the Flash memory as a long term data storage,

saving configuration information, sensor readings, or any

other desired data.

The actual loader code would typically be programmed

P/N:PM0625

REV. 1.1, MAY 05, 1999

14

T able 1. Intel-He x Records Used by In-System Programming

RECORD TYPE COMMANDIDA T A FUNCTION

00 or 80 Data Record

:nnaaaa00dd....ddcc

Where:

N n = number of bytes (hex) in record

Aaaa = memory address of first byte in record

dd....dd= data bytes

cc = checksum

Example:10008000AF5F67F0602703E0322CFA92007780C3FD

0l or 81 End of File (EOF), no operation

:xxxxxx0lcc

Where:

xxxxxx = required field, but value is a "don't care”

cc = checksum

Example:00000001FF

83 Miscellaneous Write Functions

:nnxxxx83 ffssddcc

Where:

n n = number of bytes (hex) in record

xxxx = required field, but value is a "don't care”

83 = Write Function

ff = subfunction code

ss = selection code

d d = data input (as needed)

cc = checksum

Subfunction Code = 0l (Erase Blocks)

ff = 0l

ss = block number in bits 7:5, Bits 4:0 = zeros

block 0 : = 00h

block 1 : ss = 20h

block 2 : ss = 40h

block 3 : ss = 80h

block 4 : ss = C0h

Example:0200008301203C erase block 1

Subfunction Code =04 (Erase Boot Vector and Status Byte)

ff = 04

as = don't care

dd = don't care

Example:010000830478 erase boot vector and status byte

Subtunction Code = 05 (Program Security Bits)

ff = 05

ss = 00 program security bit 1 (inhibit writing to FLASH)

01 program security bit 2 (inhibit FLASH verify)

02 program security bit 3 (disable external memory)

Example:02000083050175 program security bit 2

Subtunction Code = 06 (Program Status Byte or Boot V ector)

ff = 06

ss = 00 program status byte

0l program boot vector

Example:020000830601FC78 program boot vector to FC00h

MX10EXA

P/N:PM0625

REV. 1.1, MAY 05, 1999

15

MX10EXA

RECORD TYPE COMMANDIDA T A FUNCTION

8 4 Display Device Data or Blank Check - Record type 84 causes the contents of the entire

FLASH array to be sent out the serial port in a formatted display. This displa y consists of an

address and the contents of 16 bytes starting with that address. No displa y of the device

contents will occur it security bit 2 has been programmed. The dumping of the de vice data to

the serial port is terminated by the reception of an y character .

General Format of Function 84 :05xxxx84sssseeeeffcc

Where:

0 5 = number of bytes (hex) in record

xxxx = required field, but value is a "don't care”

8 4 = "Display Device Data or blank Check" function code

ssss = starting address

eeee = ending address

ff = subfunction

00 = display data

01 = blank check

cc = checksum

Example:0500008440004FFF00E9 display 4000-4FFF

85 Miscellaneous Read Functions

General Format of Function 85 :02xxxx85ffsscc

Where:

0 2 = number of bytes (hex) in record

xxxx = required field, but value is a "don't care”

8 5 = "Miscellaneous Read" function code

ffss = subfunction and selection code

0000 = read signature byte - manufacturer id(15H)

0001 = read signature byte - device id # 1(EAH)

0002 = read signature byte - device id # 2(XA= 54H))

0700 = read security bits (returned value bits 3:1 = sb3,sb2,sbl)

0701 = read status byte

0702 = read boot vector

cc = checksum

Example:02000085000178 read signature byte - device id # 1

P/N:PM0625

REV. 1.1, MAY 05, 1999

16

Loading...

Loading...