MXIC MX10C8050PI, MX10C8051FC, MX10C8050QC, MX10C8054PI, MX10C8054FI Datasheet

...

1

P/N:PM0591 REV. 0.3, APR. 09, 1999

MX10C805X

SINGLE-CHIP 8-BIT MICROCONTROLLER

ADVANCED INFORMATION

FEATURE

• High performance CMOS ROM CPU

• Operation Voltage 5V

• Up to 40MHz operation (3.5MHz to 40MHz)

• Three 16-bit timer/counters

• 256 Bytes of on-chip data RAM

• 4/8/16/32/64 Kbytes on-chip Program memory

• 32 Programmable I/O lines

• On-chip Watch-Dog-Timer (WDT)

• 6 interrupt Sources

• ROM Code protection

• Two priority levels

• Power saving Idle and power down modes

• 64 K external program memory space

• 64 K external data memory space

• Available in PLCC, PQFP, and PDIP package

• Four 8-bit I/O ports

• Full-duplex enhanced UART compatible with the standard 80C51 and the 80C52

• Extended Temperature Range (-40°C to +85°C)

GENERAL DESCRIPTION

The single-chip 8-bit microcontroller is manufactured in

MXIC's advanced CMOS process. This de vice uses the

same powerful instruction set, has the same architecture, and is pin-to-pin compatible with the existing 80C51.

The added features make it an even more powerful

microcontroller for applications that require clock output, and up/down counting capabilities such as motor

control. It also has a more v ersatile serial channel that

facilitates multi-processor communications .

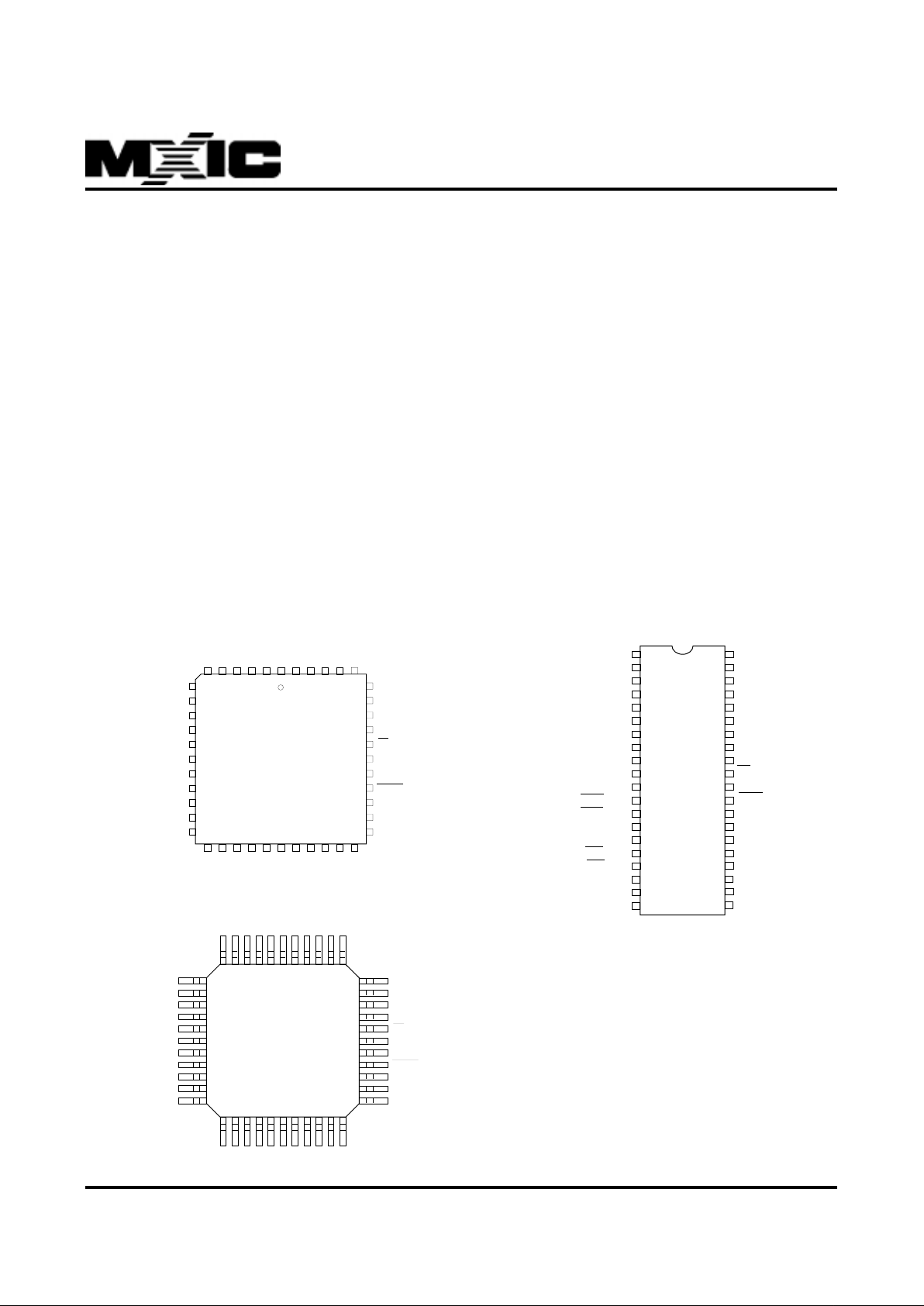

PIN CONFIGURATIONS

40 PDIP

44 PLCC

44 PQFP

MX10C805X

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

(T2) P1.0

(T2EX) P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

RESET

(RXD) P3.0

(TXD)P3.1

(INT0) P3.2

(INT1) P3.3

(T0) P3.4

(T1) P3.5

(WR) P3.6

(RD) P3.7

XTAL2

XTAL1

VSS

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

VCC

P0.0 (AD0)

P0.1 (AD1)

P0.2 (AD2)

P0.3 (AD3)

P0.4 (AD4)

P0.5 (AD5)

P0.6 (AD6)

P0.7 (AD7)

EA

ALE

PSEN

P2.7 (A15)

P2.6 (A14)

P2.5 (A13)

P2.4 (A12)

P2.3 (A11)

P2.2 (A10)

P2.1 (A9)

P2.0 (A8)

MX10C805X

P1.5

P1.6

P1.7

RST

P3.0

N.C.

P3.1

P3.2

P3.3

P3.4

P3.5

P0.4

P0.5

P0.6

P0.7

EA

N.C.

ALE

PSEN

P2.7

P2.6

P2.5

P1.4

P1.3

P1.2

P1.1

P1.0

N.C.

VCC

P0.0

P0.1

P0.2

P0.3

P3.6

P3.7

XTAL2

XTAL1

VSS

N.C.

P2.0

P2.1

P2.2

P2.3

P2.4

64440

39

34

29

7

12

17

18 23 28

1

1

11

12 22

23

33

34

44

P0.4

P0.5

P0.6

P0.7

EA

N.C.

ALE

PSEN

P2.7

P2.6

P2.5

P1.5

P1.6

P1.7

RST

P3.0

N.C.

P3.1

P3.2

P3.3

P3.4

P3.5

P1.4

P1.3

P1.2

P1.1

P1.0

N.C.

VCC

P0.0

P0.1

P0.2

P0.3

P3.6

P3.7

XTAL2

XTAL1

VSS

N.C.

P2.0

P2.1

P2.2

P2.3

P2.4

MX10C805X

2

P/N:PM0591

REV. 0.3, APR. 09, 1999

MX10C805X

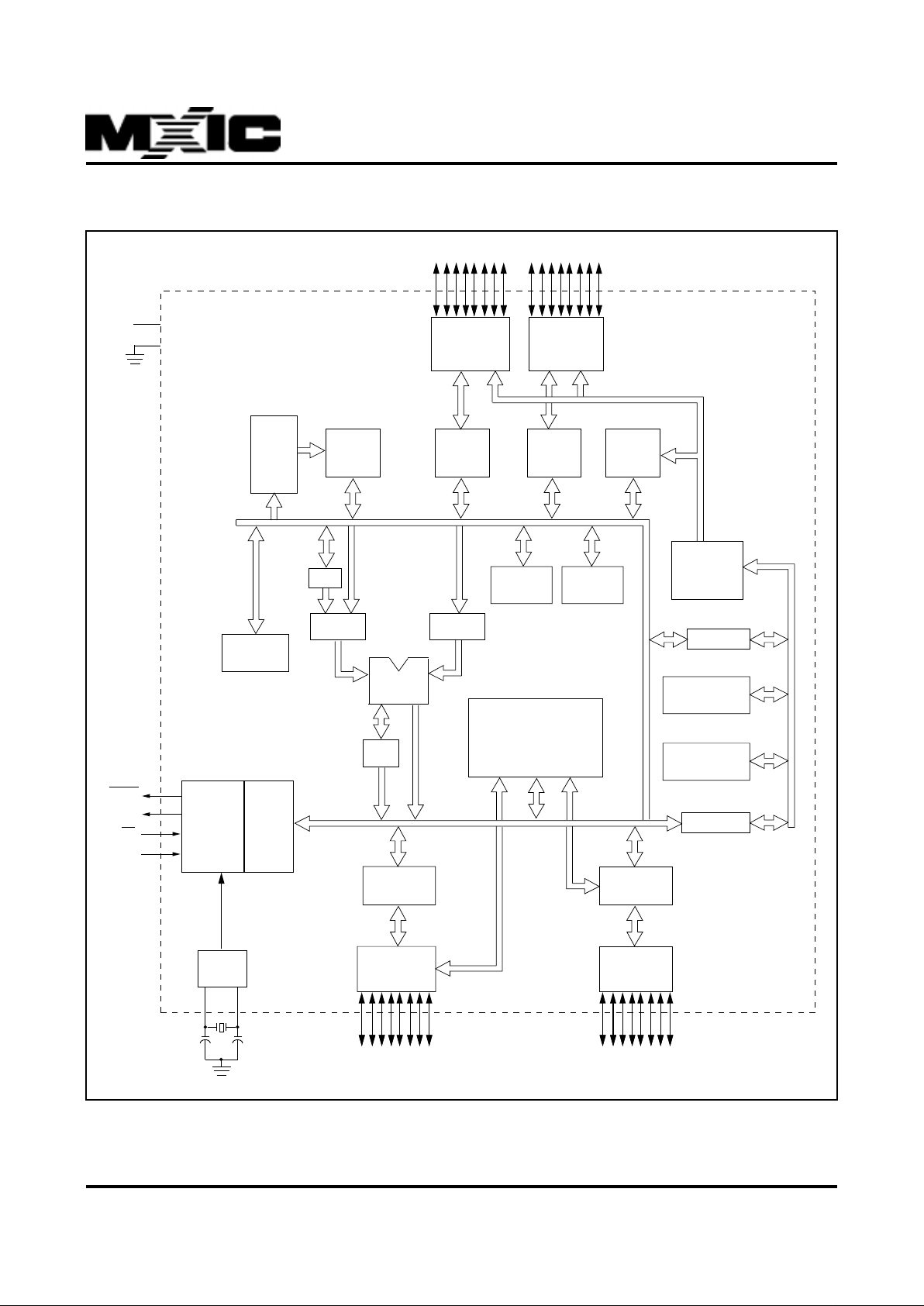

BLOCK DIAGRAM

PORT 0

DRIVERS

PORT 0

LATCH

ACC

PSW

TMP2

PORT 1

LATCH

PORT 1

DRIVERS

P1.0-P1.7

XTAL2

XTAL1

OSC.

TMP1

ALU

B

REGISTER

TIMING

AND

CONTROL

RAM

Vcc

Vss

RAM ADDR.

REGISTER

INSTRUCTION

REGISTER

PORT 2

LATCH

STACK

POINTER

ROM

PORT 2

DRIVERS

BUFFER

DPTR

PROGRAM

ADDR.

REGISTER

T0/T1/T2

SFRs

TIMERS

PORT 3

LATCH

PORT 3

DRIVERS

PC

INCREMENTER

PROGRAM

COUNTER

P0.0-P0.7 P2.0-P2.7

P3.0-P3.7

PSEN

ALE

EA

RST

T3

WATCHDOG

TIMER

3

P/N:PM0591

REV. 0.3, APR. 09, 1999

MX10C805X

PIN DESCRIPTIONS

VCC : Supply v oltage.

VSS : Circuit ground.

Port 0 : Port 0 is an 8-bit, open drain, bidirectional I/O

port. As an output port each pin can sink several LS

TTL inputs. Port 0 pins that have 1's written to them

float, and in that state can be used as high-impedance

inputs.

Port 0 is also the multiplex ed low-order address and data

bus during accesses to external Program and Data

Memory. In this application it uses strong internal pullups

when emitting 1's, and can source and sink serveral LS

TTL inputs.

Port 1 : P ort 1 is an 8-bit bidirectional I/O port with internal pullups. The port 1 output buffers can drive LS TTL

inputs. Port 1 pins that have 1's written to them are

pulled high by the internal pullups, and in that state can

be used as inputs. As inputs, P ort 1 pins that are externally pulled low will source current (IIL, on the data sheet)

because of the internal pullups.

In additional, Port 1 serves the functions of the following

special features of the MX10C805X :

Port Pin Alternate Function

P1.0 T2 (Exter nal Count Input to Timer/

Counter 2), Clock-Out

P1.1 T2EX (Timer/Counter 2 Capture/Reload

Trigger and Direction Control)

Port 2 : P ort 2 is an 8-bit bidirectional I/O port with internal pullups. The port 2 output buffers can drive LS TTL

inputs. Port 2 pins that have 1's written to them are

pulled high by the internal pullups, and in that state can

be used as inputs. As inputs, P ort 2 pins that are externally pulled low will source current (IIL, on the data sheet)

because of the internal pullups.

Port 2 emits the high-order address byte during fetches

from external Program Memory and during accesses to

external Data Memory that use 16-bit addresses (MOVX

@DPTR). In this application it uses strong internal

pullups when emitting 1's. During accesses to external

Data Memory that use 8-bit addresses (MOVX @Ri),

Port 2 emits the contents of the P2 Special Function

Register.

Port 3 : P ort 3 is an 8-bit bidirectional I/O port with internal pullups. The port 3 output buffers can drive LS TTL

inputs. Port 3 pins that have 1's written to them are

pulled high by the internal pullups, and in that state can

be used as inputs. As inputs, P ort 3 pins that are externally pulled low will source current (IIL, on the data sheet)

because of the internal pullups.

Port 3 also serves the function of various special features of the 8051 Family, as listed below :

Port Pin Alternate Function

P3.0 RXD (serial input port)

P3.1 TXD (serial output port)

P3.2 INT0 (external interrupt 0)

P3.3 INT1 (external interrupt 1)

P3.4 T0 (Timer 0 external input)

P3.5 T1 (Timer 1 external input)

P3.6 WR (external data memory write sttobe)

P3.7 RD (external data memory read strobe)

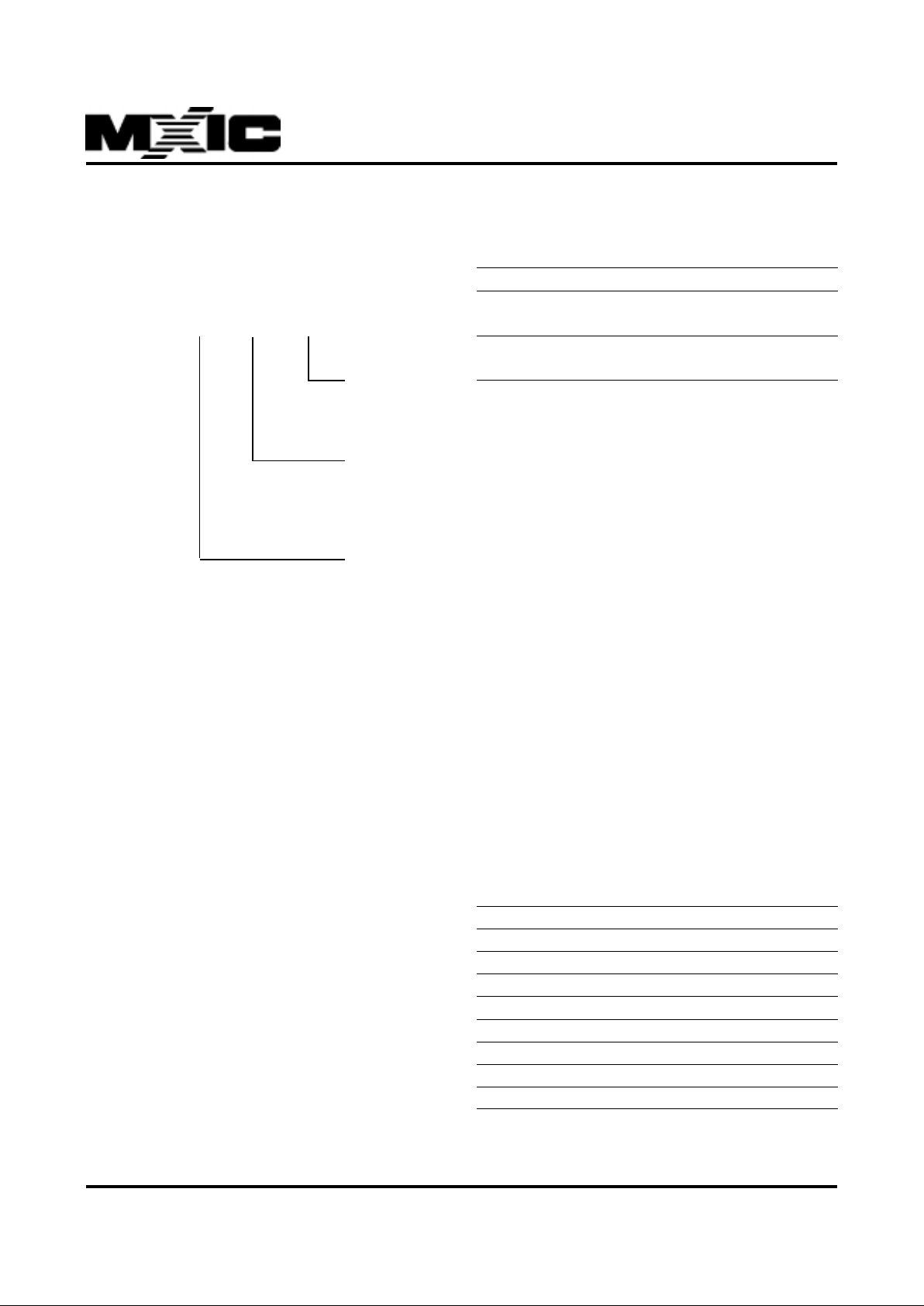

PROCESS INFORMATION

This device is manuf actured on a MXIC CMOS process.

P A CKAGES

MX10C805 1 P C

T emperature

C=0°C to 70°C

I=-40°C to 85°C

Package

P=PDIP

Q=PLCC

F=PQFP

ROM Size

0=64K Bytes

1=4K Bytes

2=8K Bytes

4=16K Bytes

8=32K Bytes

4

P/N:PM0591

REV. 0.3, APR. 09, 1999

MX10C805X

RST : Reset input. A high on this pin for two machine

cycles while the oscillator is running resets the device.

The port pins will be driven to their reset condition when

a minimum VIHI voltage is applied whether the oscillator is running or not. An internal pulldown resistor permits a power-on reset with only a capacitor connected

to VCC.

ALE : Address Latch Enable output pulse for latching

the low byte of the address during accesses to external

memory .

In normal operation ALE is emitted at a constant rate of

1/6 the oscillator frequency, and may be used for e xternal timing or clocking purposes. Note, however, that

one ALE pulse is skipped during each access to external Data Memory .

If desired, ALE operation can be disabled by setting bit

5 of SFR location 87H (PCON). With this bit set, the pin

is weakly pulled high. Howe ver, the ALE disab le feature

will be suspended during a MOVX or MO VC instruction,

idle mode, power do wn mode. The ALE disable f eature

will be terminated by reset. When the ALE disable f eature is suspended or terminated, the ALE pin will no

longer be pulled up weakly. Setting the ALE-disable bit

has no affect if the micrcontroller is in external execution mode.

Throughout the remainder of this data sheet, ALE will

refer to the signal coming out of the ALE pin, and the pin

will be referred to as the ALE pin.

PSEN : Progr am Store Enable is the read strobe to external Program Memory.

When the MX10C805X is executing code from e xternal

Program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are

skipped during each access to external Data memory.

EA/VPP : Extrernal Access enable. EA must be str apped

to VSS in order to enable the twiceto fetch code from

external Program Memory locations 0000H to 0FFFFH.

EA will be internally latched on reset.

EA should be strapped to VCC f or internal program executions.

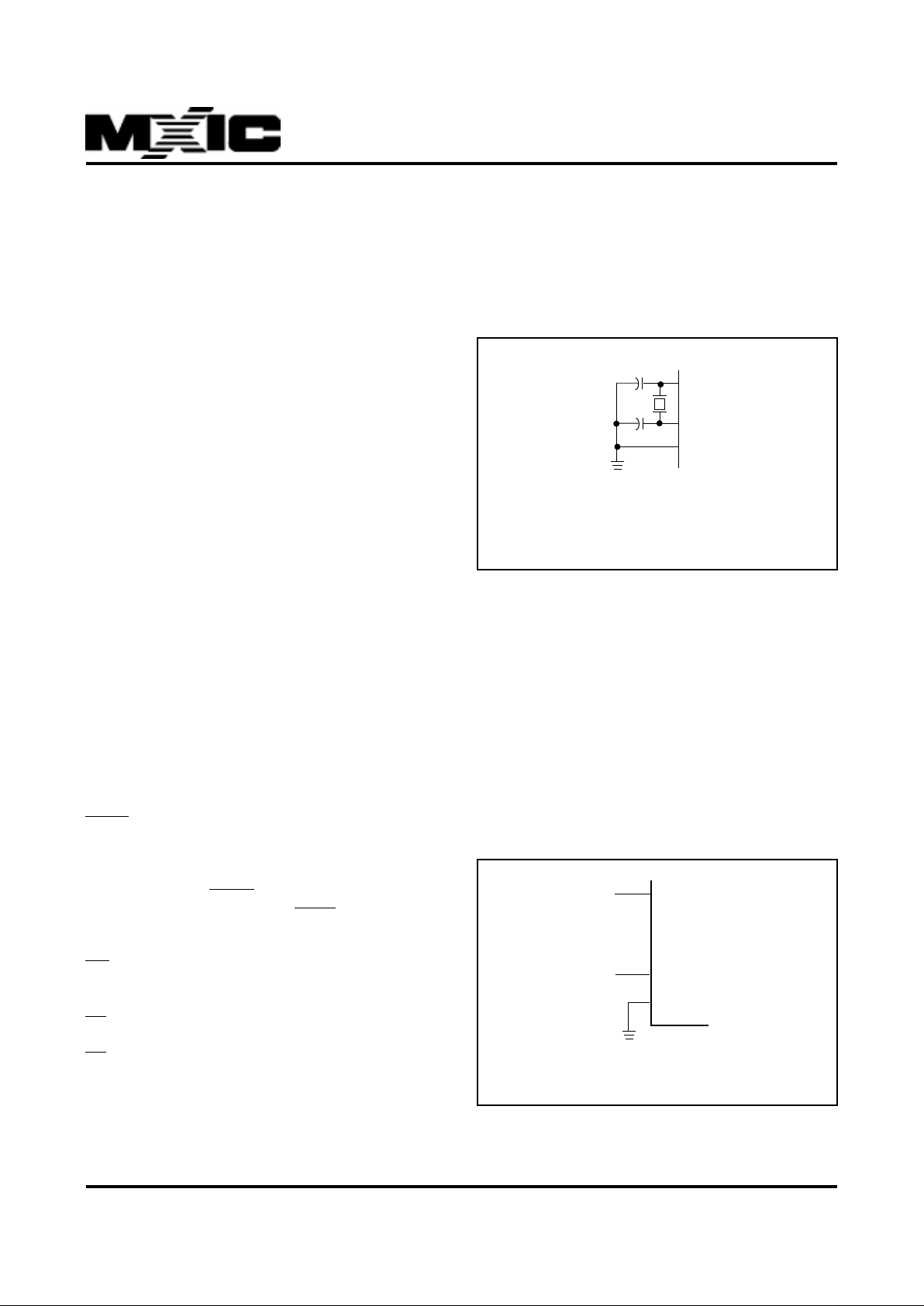

XTAL1 : Input to the inverting oscillator amplifier.

XTAL2 : Output from the inverting oscillator amplifier.

T o drive the de vice from an external clock source, XTAL1

should be driven, while XTAL2 floats, as shown in Figure 4. There are no requirememts on the duty cycle of

the external clock signal, since the input to the internal

clocking circuitry is through a divide-by-two flip-flop, b ut

minimum and maximum high and low times specified

on the data sheet must be observed.

An external oscillator may encounter as much as a 100

pF load at XTAL1 when it starts up. This is due to interaction between the amplifer and its feedback capacitance. Once the e xternal signal meets the VIL and VIH

specifications the capacitance will not exceed 20 pF.

C2

XTAL2

XTAL1

VSS

Figure 3. Oscillator Connections

C1, C2 = 30 pF is equal to or less than 10 pF for Crystal

For Ceramic Resonators,contact resonator manufacture.

C1

N/C

XTAL1

VSS

XTAL2

EXTERNAL

OSCILLATOR

SIGNAL

Figure 4. External Clock Drive Configuration

OSCILLA T OR CHARA CTERISTICS

XT AL1 and XTAL2 are the input and output, respectively ,

of a inverting amplifier which can be configured for use

as an on-chip oscillator, as sho wn in Figure 3. Either a

quartz crystal or ceramic resonator may be used.

5

P/N:PM0591

REV. 0.3, APR. 09, 1999

MX10C805X

T a ble 2. Status of the External Pins during Idle and Power Do wn

Mode Program Memory ALE PSEN PORT0 PORT1 PORT2 PORT3

Idle Internal 1 1 Data Data Data Data

Idle External 1 1 Float Data Address Data

Pow er Down Internal 0 0 Data Data Data Data

Pow er Down External 0 0 Float Data Data Data

POWER DOWN MODE

To save even more power, a Po wer Down mode can be

invok ed by software. If this mode, the oscillator is stopped

and the instruction that invoked Power Down is the last

instruction executed. The on-chip RAM and Special

Function Registers retain their values until the Power

Down mode is terminated.

On the MX10C805X either a hardware reset or an external interrupt can cause an exit from Power Down. Reset redefines all the SFRs but does not change the onchip RAM. An external interrupt allows both the SFRs

and on-chip RAM to retain their values.

ABSOLUTE MAXIMUM RATING*

Ambient Temperature Under Bias -40°C to +85°C

Storage T emperature -65°C to +150°C

Voltage on Any Other Pin to VSS -0.5V to +6.5V

IOL Per I/O Pin 15mA

Pow er Dissipation 1.5W

(Based on PACKAGE heat transfer limitations, not device consumption)

IDLE MODE

The user's software can invoke the Idle Mode. When

the microcontroller is in this mode, power consumption

is reduced. The Special Function Registers and the

onboard RAM retain their values during Idle, but the processor stops executing instructions. Idle Mode will be

exited if the chip is reset or if an enabled interrupt occurs.

OPERATING CONDITIONS

Symbol Description Min Max Units

TA Ambient Temperature Under Bias

Commerical 0 +70 °C

Industrial -40 +85 °C

VCC 4.5 5.5 V

fOSC Oscillator Frequency 3.5 40 MHz

To properly terminate Power Down, the reset or external interrupt should not be executed before VCC is restored to its normal operating level, and must be held

active long enough for the oscillator to restart and stabilize (normally less than 10 ms).

With an external interrupt, INT0 and INT1 must be enabled and configured as lev el-sensitive. Holding the pin

low restarts the oscillator but bringing the pin back high

completes the exit. Once the interrupt is serviced, the

next instruction to be executed after RETI will be the

one following the instruction that put the de vice into Power

Down.

Loading...

Loading...