Page 1

HGFEDCBA

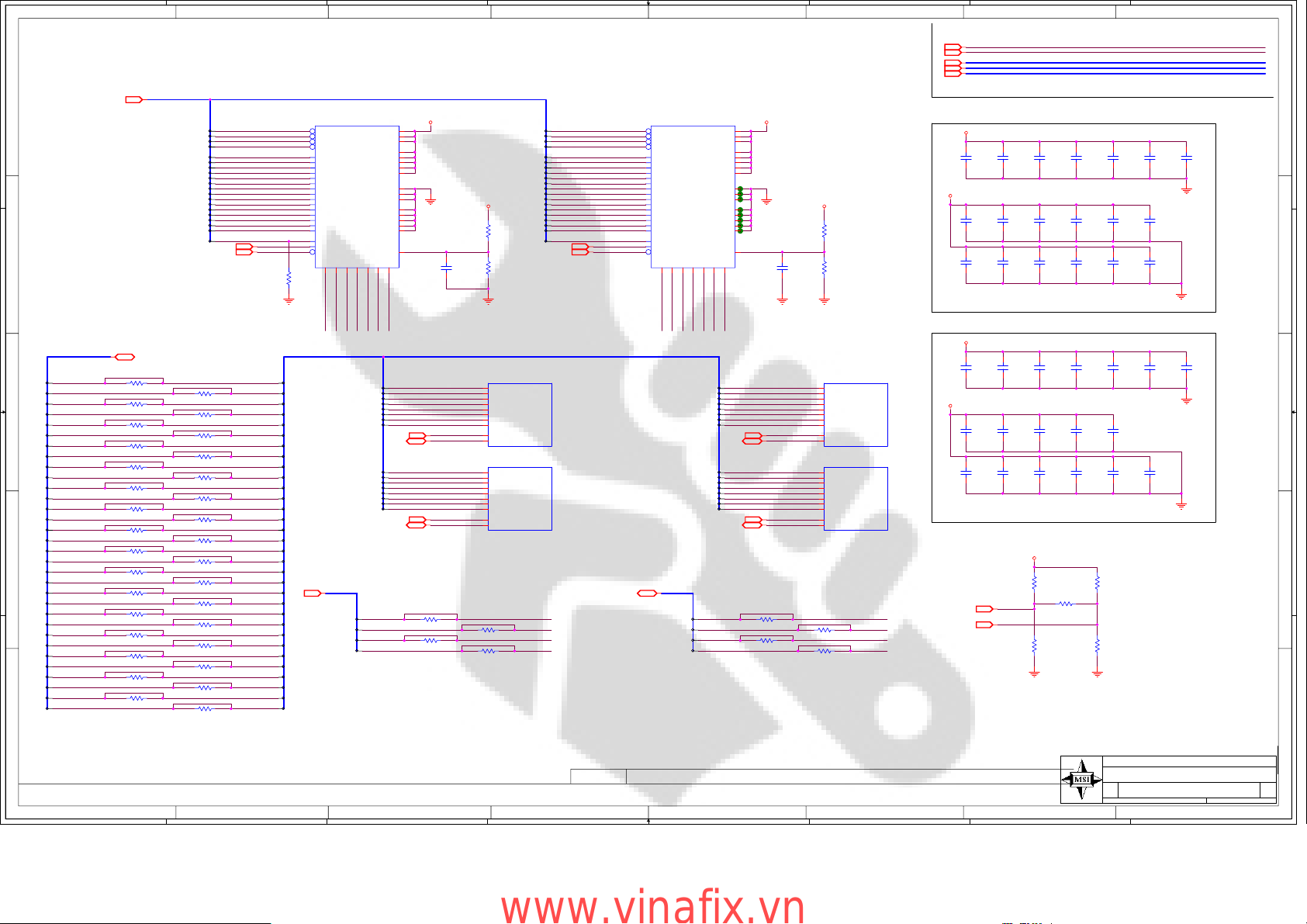

P283: LOW PROFILE NV44/G3-64, TSOP MEMORY x16

1

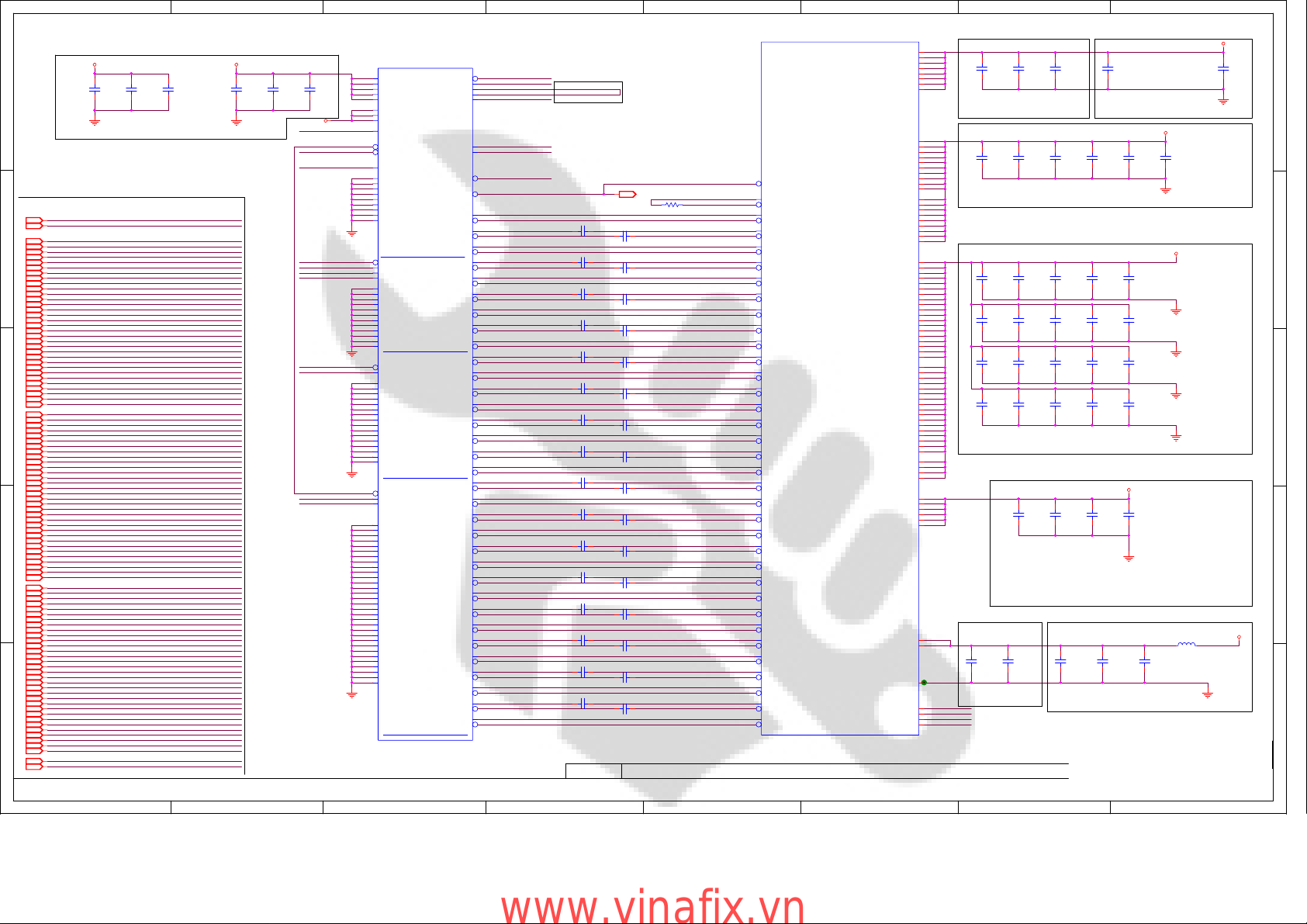

Page1: P262 Overview

Page2: PCI Express Interface

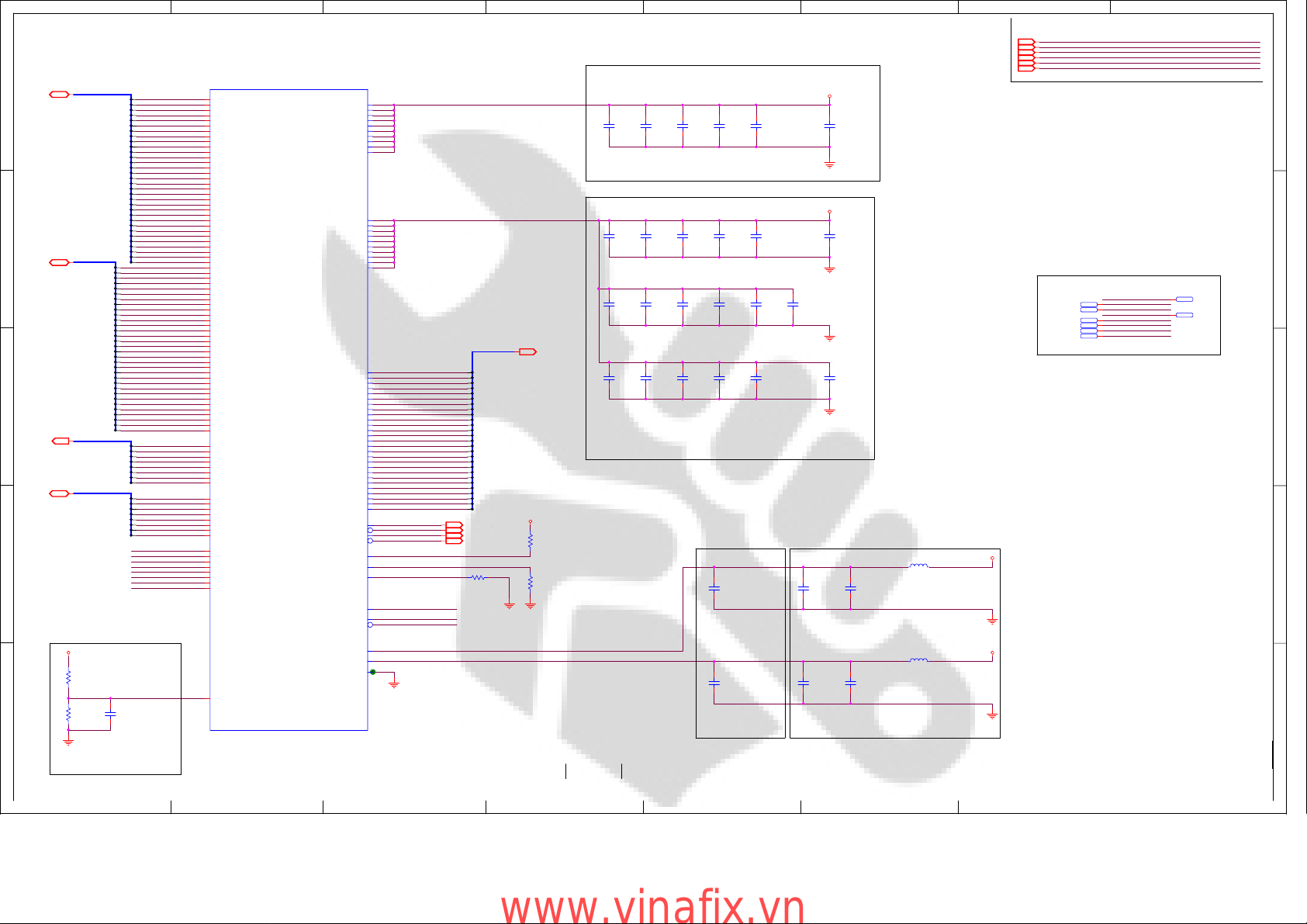

Page3: Frame Buffer Interface

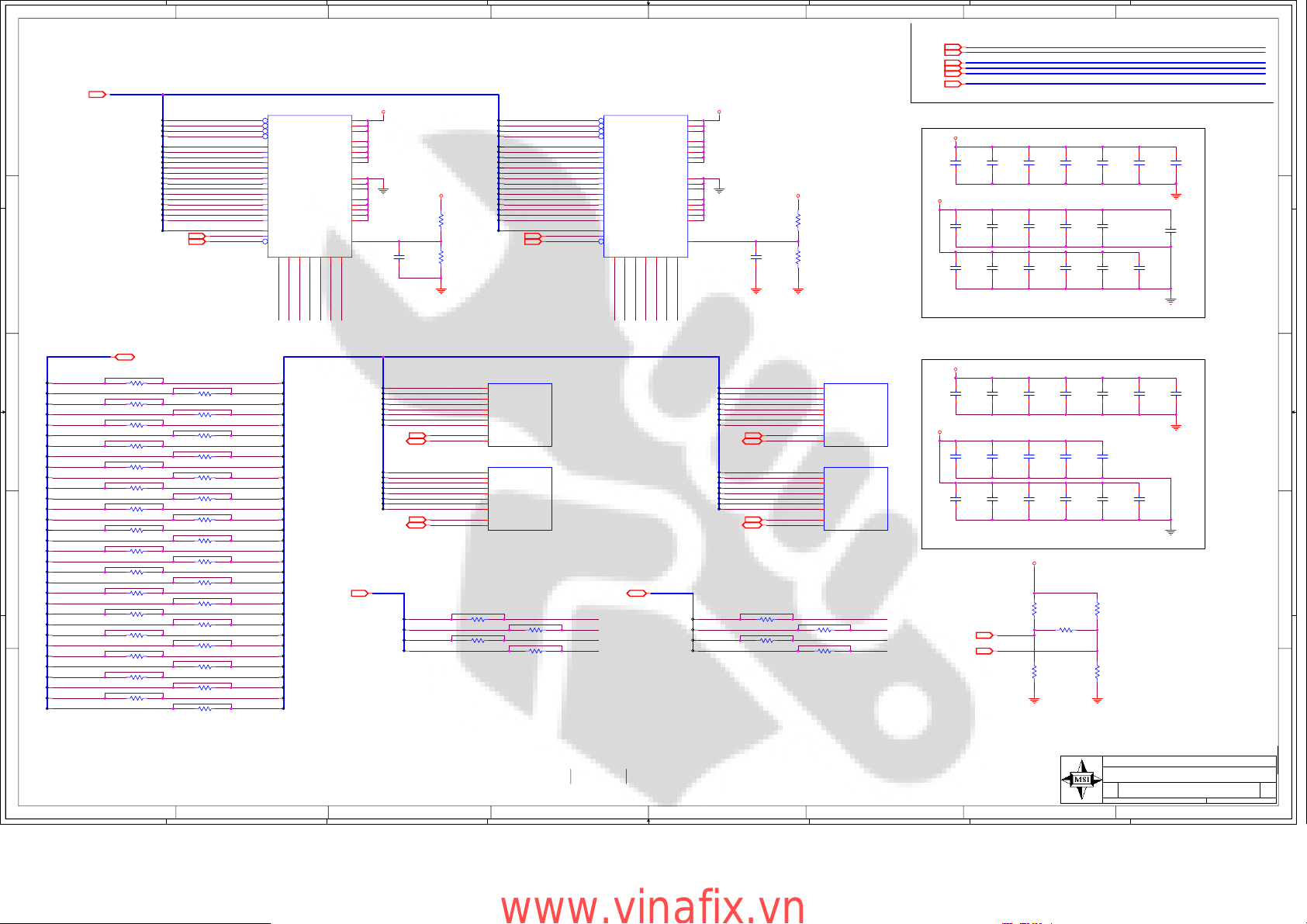

Page4: Memory 1st bank 0..31

Page5: Memory 1st bank 32..63

2

3

Page6: DACA VGA

Page7: DACB RGB

Page8: TMDS LINK A

Page9: TMDS LINK C

Page10:TVO Connector

Page11: GPIO, PLL, BIOS

Page12: MIO

Page13: STRAPS, Mechanical Parts

Page14: NVVDD & FBVDDQ

Page15: TMDS_IOVDD,TMDS_PLLVDD,5V,F3V3

REV HISTORY

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFEREN CE BOARDS, FI LES, DRAWINGS, DIAGNOSTICS , LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLAT IONS OR DEVIATIONS OF INDUSTRY STANDARDS AND S PECIFICATIONS. NVIDIA MAKES NO WARRANT IES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

VARIANT ASSEMBLY

SKU

BASE

B

1

2

0001

<UNDEFINED>

3

<UNDEFINED>

4

<UNDEFINED>

5

<UNDEFINED>

6

<UNDEFINED>

7

<UNDEFINED>

8

<UNDEFINED>

9

<UNDEFINED>

10

<UNDEFINED>

11

<UNDEFINED>

12

<UNDEFINED>

13

<UNDEFINED>

14

<UNDEFINED>

15

A B D F H

NVPN

600-f0ppp-xxxx-vvv

600-50283-0000-100WORKSTATION_SKU00

600-10283-0001-000

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED> <UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

NVS SKU00

SKU01 - NV44 G3-64, VGA+HDTV, 350/275MHz, 64-bit 64MB MEMORY INTERFACE

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

www.vinafix.vn

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

P283 Overview

E GC

4

5

Page 2

PEX-Interface

3V3

PLACE NEAR FINGERS

C22

C19

C24

1UF

1

10V

10%

X7R

0603

COMMON

.1UF

10V

10%

X5R

0402

COMMON

.01UF

16V

10%

X7R

0402

COMMON

GND

Net Name

PEX_TSTCLK

IN

PEX_TSTCLK*

IN

PEX_TX0

IN

PEX_TX0*

IN

2

3

4

5

PEX_TX1

IN

PEX_TX1*

IN

PEX_TX2

IN

PEX_TX2*

IN

PEX_TX3

IN

PEX_TX3*

IN

PEX_TX4

IN

PEX_TX4*

IN

PEX_TX5

IN

PEX_TX5*

IN

PEX_TX6

IN

PEX_TX6*

IN

PEX_TX7

IN

PEX_TX7*

IN

PEX_TX8

IN

PEX_TX8*

IN

PEX_TX9

IN

PEX_TX9*

IN

PEX_TX10

IN

PEX_TX10*

IN

PEX_TX11

IN

PEX_TX11*

IN

PEX_TX12

IN

PEX_TX12*

IN

PEX_TX13

IN

PEX_TX13*

IN

PEX_TX14

IN

PEX_TX14*

IN

PEX_TX15

IN

PEX_TX15*

IN

PEX_TXX0

IN

PEX_TXX0*

IN

PEX_TXX1

IN

PEX_TXX1*

IN

PEX_TXX2

IN

PEX_TXX2*

IN

PEX_TXX3

IN

PEX_TXX3*

IN

PEX_TXX4

IN

PEX_TXX4*

IN

PEX_TXX5

IN

PEX_TXX5*

IN

PEX_TXX6

IN

PEX_TXX6*

IN

PEX_TXX7

IN

PEX_TXX7*

IN

PEX_TXX8

IN

PEX_TXX8*

IN

PEX_TXX9

IN

IN

PEX_TXX10

IN

PEX_TXX10*

IN

PEX_TXX11

IN

PEX_TXX11*

IN

PEX_TXX12

IN

PEX_TXX12*

IN

PEX_TXX13

IN

PEX_TXX13*

IN

PEX_TXX14

IN

PEX_TXX14*

IN

PEX_TXX15

IN

PEX_TXX15*

IN

PEX_RX0

IN

PEX_RX0*

IN

PEX_RX1

IN

PEX_RX1*

IN

PEX_RX2

IN

PEX_RX2*

IN

PEX_RX3

IN

PEX_RX3*

IN

PEX_RX4

IN

PEX_RX4*

IN

PEX_RX5

IN

PEX_RX5*

IN

PEX_RX6

IN

PEX_RX6*

IN

PEX_RX7

IN

PEX_RX7*

IN

PEX_RX8

IN

PEX_RX8*

IN

PEX_RX9

IN

PEX_RX9*

IN

PEX_RX10

IN

PEX_RX10*

IN

PEX_RX11

IN

PEX_RX11*

IN

PEX_RX12

IN

PEX_RX12*

IN

PEX_RX13

IN

PEX_RX13*

IN

PEX_RX14

IN

PEX_RX14*

IN

PEX_RX15

IN

PEX_RX15*

IN

PEX_REFCLK

IN

PEX_REFCLK*

IN

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFEREN CE BOARDS, FI LES, DRAWINGS, DIAGNOSTICS , LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLAT IONS OR DEVIATIONS OF INDUSTRY STANDARDS AND S PECIFICATIONS. NVIDIA MAKES NO WARRANT IES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

DIFF_PAIR

PEX_TX2 25MIL

PEX_TX3 25MIL

PEX_TX3 25MIL

PEX_TX4 25MIL

PEX_TX4 25MIL

PEX_TX5 25MIL

PEX_TX5 25MIL

PEX_TX6 25MIL

PEX_TX6 25MIL

PEX_TX7 25MIL

PEX_TX7 25MIL

PEX_TX8 25MIL

PEX_TX8 25MIL

PEX_TX9 25MIL

PEX_TX9 25MIL

PEX_TX10 25MIL

PEX_TX10 25MIL

PEX_TX11 25MIL

PEX_TX11 25MIL

PEX_TX12 25MIL

PEX_TX12 25MIL

PEX_TX13 25MIL

PEX_TX13 25MIL

PEX_TX14 25MIL

PEX_TX14 25MIL

PEX_TX15 25MIL

PEX_TX15 25MIL

PEX_TXX0 25MIL

PEX_TXX0 25MIL

PEX_TXX1 25MIL

PEX_TXX1 25MIL

PEX_TXX2 25MIL

PEX_TXX2 25MIL

PEX_TXX3 25MIL

PEX_TXX3 25MIL

PEX_TXX4 25MIL

PEX_TXX4 25MIL

PEX_TXX5 25MIL

PEX_TXX5 25MIL

PEX_TXX7 25MIL

PEX_TXX7 25MIL

PEX_TXX8 25MIL

PEX_TXX8 25MIL

PEX_TXX9 25MIL

PEX_TXX9 25MIL

PEX_TXX10 25MIL

PEX_TXX10 25MIL

PEX_TXX11 25MIL

PEX_TXX11 25MIL

PEX_TXX12 25MIL

PEX_TXX12 25MIL

PEX_TXX13 25MIL

PEX_TXX13 25MIL

PEX_TXX14 25MIL

PEX_TXX14 25MIL

PEX_TXX15 25MIL

PEX_TXX15 25MIL

PEX_RX0 25MIL

PEX_RX0 25MIL

PEX_RX1 25MIL

PEX_RX1 25MIL

PEX_RX2 25MIL

PEX_RX2 25MIL

PEX_RX3 25MIL

PEX_RX3 25MIL

PEX_RX4 25MIL

PEX_RX4 25MIL

PEX_RX5 25MIL

PEX_RX5 25MIL

PEX_RX6 25MIL

PEX_RX6 25MIL

PEX_RX7 25MIL

PEX_RX7 25MIL

PEX_RX8 25MIL

PEX_RX8 25MIL

PEX_RX9 25MIL

PEX_RX9 25MIL

PEX_RX10 25MIL

PEX_RX11 25MIL

PEX_RX11 25MIL

PEX_RX12 25MIL

PEX_RX12 25MIL

PEX_RX13 25MIL

PEX_RX13 25MIL

PEX_RX14 25MIL

PEX_RX14 25MIL

PEX_RX15 25MIL

PEX_RX15 25MIL

PEX_REFCLK 25MIL

PEX_REFCLK 25MIL

NET_SPACING_TYPE

25MILPEX_TST

25MILPEX_TST

25MILPEX_TX0

25MILPEX_TX0

25MILPEX_TX1

25MILPEX_TX1

25MILPEX_TX2

25MILPEX_TXX6

25MILPEX_TXX6

25MILPEX_RX10

A B D F H

12V

C700

C703

4.7UF

16V

20%

X7R

1206

COMMON

C696

.01UF

16V

10%

X7R

0402

COMMON

3V3

SNN_3V3AUX

PRSNT

SNN_PE_PRSNT2_A

SNN_PE_RSVD2

SNN_PE_PRSNT2_B

SNN_PE_RSVD3

SNN_PE_RSVD4

SNN_PE_RSVD5

SNN_PE_PRSNT2_C

SNN_PE_RSVD6

SNN_PE_RSVD7

SNN_PE_RSVD8

4.7UF

16V

20%

X7R

1206

COMMON

GND

GND

GND

GND

GND

CN1

EDGE_PEX_164_FINGER

CON_X16

COMMON

B1

B2

A2

A3

B3

B8

A9

A10

B10

A1

B17

B12

B4

A4

B7

A12

B13

A15

B16

B18

A18

B31

A19

B30

A32

A20

B21

B22

A23

A24

B25

B26

A27

A28

B29

A31

B32

B48

A33

A34

B35

B36

A37

A38

B39

B40

A41

A42

B43

B44

A45

A46

B47

B49

A49

B81

A50

B82

A51

B52

B53

A54

A55

B56

B57

A58

A59

B60

B61

A62

A63

B64

B65

A66

A67

B68

B69

A70

A71

B72

B73

A74

A75

B76

B77

A78

A79

B80

A82

+12V

+12V

+12V

+12V

+12V/RSVD

+3V3

+3V3

+3V3

+3V3AUX

PRSNT1

PRSNT2

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

END OF X1

END OF X4

END OF X8

END OF X16

TRST* JTAG1

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

SMCLK

SMDAT

PERST

REFCLK

REFCLK

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

SNN_JTAGE_TRST*

B9

SNN_JTAGE_TCLK

A5

JTAGE_TDI/O

A6

A7

SNN_JTAGE_TMS

A8

SNN_PEX_SMCLK

B5

SNN_PEX_SMDAT

B6

SNN_PEX_WAKE*

B11

WAKE

PEX_PWRGD*

A11

PEX_REFCLK

A13

PEX_REFCLK*

A14

PEX_TXX0

A16

PEX_TXX0*

COMMON 0402X5R 10%

A17

PEX_RX0

B14

PEX_RX0*

B15

PEX_TXX1

A21

PEX_TXX1*

COMMON 0402X5R 10% 10V

A22

PEX_RX1

B19

PEX_RX1*

B20

PEX_TXX2

A25

PEX_TXX2*

COMMON 040210% 10VX5R

A26

PEX_RX2

B23

PEX_RX2*

B24

PEX_TXX3

A29

PEX_TXX3*

A30

PEX_RX3

B27

PEX_RX3*

B28

PEX_TXX4

A35

PEX_TXX4*

A36

PEX_RX4

B33

PEX_RX4*

B34

PEX_TXX5

A39

PEX_TXX5*

A40

PEX_RX5

B37

PEX_RX5*

B38

PEX_TXX6

A43

PEX_TXX6*

A44

PEX_RX6

B41

PEX_RX6*

B42

PEX_TXX7

A47

PEX_TXX7*

A48

PEX_RX7

B45

PEX_RX7*

B46

PEX_TXX8

A52

PEX_TXX8*

A53

PEX_RX8

B50

PEX_RX8*

B51

PEX_TXX9PEX_TXX9*

A56

PEX_TXX9*

A57

PEX_RX9

B54

PEX_RX9*

B55

PEX_TXX10

A60

PEX_TXX10*

A61

PEX_RX10

B58

PEX_RX10*

B59

PEX_TXX11

A64

PEX_TXX11*

A65

PEX_RX11

B62

PEX_RX11*

B63

PEX_TXX12

A68

PEX_TXX12*

A69

PEX_RX12

B66

PEX_RX12*

B67

PEX_TXX13

A72

PEX_TXX13*

A73

PEX_RX13

B70

PEX_RX13*

B71

PEX_TXX14

A76

PEX_TXX14*

A77

PEX_RX14

B74

PEX_RX14*

B75

PEX_TXX15

A80

PEX_TXX15*

A81

PEX_RX15

B78

PEX_RX15*

B79

X5R 10% 10VCOMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

X5RCOMMON

COMMON X5R 10% 10V

COMMON

COMMON 0402X5R

COMMON

MAKE CUTTABLE TRACE

C692

10V

COMMON 10%

C685

C672 .1UF

COMMON X5R 10% 10V

C659

COMMON X5R

C649

COMMON

C636

COMMON

C624

C607

COMMON 0402X5R 10%

C594

COMMON

C580

COMMON

C564

COMMON

C560

C550

10%COMMON

COMMON

C548

COMMON

C545

10V10%

COMMON

C542

COMMON

ASSEMBLY

PAGE DETAIL

OUT

R519 200

04025%COMMON

.1UF

C689

.1UF

0402X5R 10V

.1UF

C682

.1UF

0402COMMON

X5R 10% 10V

C669

.1UF

0402

.1UF

C656

.1UF

0402

040210% 10V

.1UF

C647

.1UF

0402X5R 10% 10V

0402X5R 10% 10V

.1UF

C632

.1UF

0402X5R 10% 10V

0402X5R 10% 10V

.1UF

C621

.1UF

0402X5R 10% 10V

X5R

040210V10%COMMON

.1UF

C600

.1UF

040210% 10VX5R

10V

.1UF

C586

.1UF

0402X5R 10% 10V

0402X5R 10% 10V

.1UF

C576

.1UF

0402X5R 10% 10V

0402X5R 10% 10V

.1UF

C563

.1UF

040210% 10V

0402X5R 10% 10V

.1UF

C559

.1UF

0402

10VCOMMON

0402X5R 10%

.1UF

C549

.1UF

0402X5R 10V

0402X5R 10% 10V

.1UF

C546

.1UF

0402X5R 10% 10V

0402X5R 10% 10V

.1UF

C543

.1UF

0402X5R 10% 10V

.1UF

C541

.1UF

0402X5R 10% 10V

0402X5R 10% 10V

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

PCI Express Interfac e

PEX_TSTCLK

PEX_TSTCLK*

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

AC6

AF13

AF14

AE3

AE4

AD5

AD6

AF1

AG2

AE6

AE7

AG3

AG4

AD7

AC7

AF4

AF5

AE9

AE10

AG6

AG7

AD10

AC10

AF7

AF8

AE12

AE13

AG9

AG10

AD13

AC13

AF10

AF11

AC15

AD15

AG12

AG13

AE15

AE16

AG15

AG16

AC18

AD18

AF16

AF17

AE18

AE19

AG18

AG19

AC21

AD21

AF19

AF20

AE21

AE22

AG21

AG22

AD22

AD23

AF22

AF23

AF25

AE25

AG24

AG25

AE24

AD24

AG26

AF27

E GC

U2A

BGA533_P08_23X23MM_G3-64

COMMON

1/12 PCI_EXPRESS

PEX_RST

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_REFCLK

PEX_REFCLK

PEX_TX0

PEX_TX0

PEX_RX0

PEX_RX0

PEX_TX1

PEX_TX1

PEX_RX1

PEX_RX1

PEX_TX2

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX3

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX4

PEX_TX4

PEX_RX4

PEX_RX4

PEX_TX5

PEX_TX5

PEX_RX5

PEX_RX5

PEX_TX6

PEX_TX6

PEX_RX6

PEX_RX6

PEX_TX7

PEX_TX7

PEX_RX7

PEX_RX7

PEX_TX8

PEX_TX8

PEX_RX8

PEX_RX8

PEX_TX9

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX10

PEX_TX10

PEX_RX10

PEX_RX10

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX13

PEX_TX13

PEX_RX13

PEX_RX13

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX15

PEX_TX15

PEX_RX15

PEX_RX15

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

VDD_LP

VDD_LP

VDD_LP

VDD_LP

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

PEX_PLLAVDD

PEX_PLLDVDD

PEX_PLLGND

HGFEDCBA

PEX1V2

AB10

AB11

AB14

AB15

W17

W18

AB20

AB21

C604

.022UF

16V

10%

X7R

0402

COMMON

C587

.022UF

16V

10%

X7R

0402

COMMON

PLACE NEAR BALLS PLACE NEAR GPU

C579

.022UF

16V

10%

X7R

0402

COMMON

C597

1UF

6.3V

10%

X5R

0402

COMMON

C671

4.7UF

6.3V

10%

X5R

0805

COMMON

1

GND

PEX1V2

AA4

AB5

AB6

AB7

AB8

AB9

AC9

AC11

AB12

AC12

PLACE NEAR BALLS

AB13

AB16

AC16

AB17

AC17

AB18

AB19

AC19

AC20

J9

VDD

M9

VDD

N9

VDD

R9

VDD

T9

VDD

J10

VDD

J11

VDD

M11

VDD

N11

VDD

R11

VDD

T11

VDD

L12

VDD

M12

VDD

T12

VDD

U12

VDD

L13

VDD

M13

VDD

T13

VDD

U13

VDD

W13

VDD

M14

VDD

T14

VDD

L15

VDD

M15

VDD

T15

VDD

U15

VDD

W15

VDD

L16

VDD

M16

VDD

T16

VDD

U16

VDD

W16

VDD

M17

VDD

N17

VDD

VDD

VDD

R17

T17

W9

W10

W11

W12

J12

F13

J13

F14

J15

J16

PLACE NEAR BALLS

C577

.022UF

16V

10%

X7R

0402

COMMON

C572

100PF

50V

5%

C0G

0402

COMMON

C612

220PF

50V

5%

COG

0402

COMMON

C584

220PF

50V

5%

COG

0402

COMMON

C619

220PF

50V

5%

COG

0402

COMMON

C617

.022UF

16V

10%

X7R

0402

COMMON

C618

.01UF

16V

10%

X7R

0402

COMMON

C585

100PF

50V

5%

C0G

0402

COMMON

C614

.01UF

16V

10%

X7R

0402

COMMON

C603

220PF

50V

5%

COG

0402

COMMON

C592

.1UF

10V

10%

X5R

0402

COMMON

C606

.01UF

16V

10%

X7R

0402

COMMON

C599

.01UF

16V

10%

X7R

0402

COMMON

C615

220PF

50V

5%

COG

0402

COMMON

C613

220PF

50V

5%

COG

0402

COMMON

C602

.01UF

16V

10%

X7R

0402

COMMON

C593

4700PF

25V

10%

X7R

0402

COMMON

C591

.01UF

16V

10%

X7R

0402

COMMON

C581

100PF

50V

5%

C0G

0402

COMMON

C598

100PF

50V

5%

C0G

0402

COMMON

C608

1UF

6.3V

10%

X5R

0402

COMMON

C668

10UF

6.3V

20%

X5R

0805

COMMON

C601

.022UF

16V

10%

X7R

0402

COMMON

F3V3

GND

C610

1UF

6.3V

10%

X5R

0402

COMMON

C611

.01UF

16V

10%

X7R

0402

COMMON

C571

1UF

6.3V

10%

X5R

0402

COMMON

C28

10UF

6.3V

20%

X5R

0805

COMMON

C684

10UF

6.3V

20%

X5R

0805

COMMON

C609

1UF

10V

10%

X7R

0603

COMMON

C679

10UF

6.3V

20%

X5R

0805

COMMON

GND

NVVDD

2

GND

GND

GND

3

GND

4

PLACE NEAR BALLS

Y6

PEX_PLL_DVDD

AA5

AA6

D12

NC

E12

NC

F12

NC

C13

NC

SNN_NC1

SNN_NC2

SNN_NC3

SNN_NC4

C635

4700PF

25V

10%

X7R

0402

COMMON

PLACE NEAR BALLS

C616

.1UF

10V

10%

X5R

0402

COMMON

C651

.01UF

16V

10%

X7R

0402

COMMON

PLACE NEAR GPU

C661

1UF

6.3V

10%

X5R

0402

COMMON

220R@100MHz

C657

1UF

6.3V

10%

X5R

0402

COMMON

COMMON

PEX1V2

LB505

0402

GND

5

www.vinafix.vn

Page 3

GPU: FB-Interface

U2B

BGA533_P08_23X23MM_G3-64

A26

C24

B24

A24

C22

A25

B25

D23

G22

J23

E24

F23

J24

F24

G23

H24

D16

E16

D17

F18

E19

E18

D20

D19

A18

B18

A19

B19

D18

C19

C16

C18

N26

N25

R25

R26

R27

T25

T27

T26

AB23

Y24

AB24

AB22

AC24

AC22

AA23

AA22

T24

T23

R24

R23

R22

T22

N23

P24

AA24

AA27

AA26

AB25

AB26

AB27

AA25

W25

D21

F22

F20

A21

V27

W22

V22

V24

B22

D22

E21

C21

V25

W24

U24

W26

A22

E22

F21

B21

V26

W23

V23

W27

A16

COMMON

2/12 FRAME_BUFFER

FB_DQ0

FB_DQ1

FB_DQ2

FB_DQ3

FB_DQ4

FB_DQ5

FB_DQ6

FB_DQ7

FB_DQ8

FB_DQ9

FB_DQ10

FB_DQ11

FB_DQ12

FB_DQ13

FB_DQ14

FB_DQ15

FB_DQ16

FB_DQ17

FB_DQ18

FB_DQ19

FB_DQ20

FB_DQ21

FB_DQ22

FB_DQ23

FB_DQ24

FB_DQ25

FB_DQ26

FB_DQ27

FB_DQ28

FB_DQ29

FB_DQ30

FB_DQ31

FB_DQ32

FB_DQ33

FB_DQ34

FB_DQ35

FB_DQ36

FB_DQ37

FB_DQ38

FB_DQ39

FB_DQ40

FB_DQ41

FB_DQ42

FB_DQ43

FB_DQ44

FB_DQ45

FB_DQ46

FB_DQ47

FB_DQ48

FB_DQ49

FB_DQ50

FB_DQ51

FB_DQ52

FB_DQ53

FB_DQ54

FB_DQ55

FB_DQ56

FB_DQ57

FB_DQ58

FB_DQ59

FB_DQ60

FB_DQ61

FB_DQ62

FB_DQ63

FB_DQM0

FB_DQM1

FB_DQM2

FB_DQM3

FB_DQM4

FB_DQM5

FB_DQM6

FB_DQM7

FB_DQS_WP0

FB_DQS_WP1

FB_DQS_WP2

FB_DQS_WP3

FB_DQS_WP4

FB_DQS_WP5

FB_DQS_WP6

FB_DQS_WP7

FB_DQS_RN0

FB_DQS_RN1

FB_DQS_RN2

FB_DQS_RN3

FB_DQS_RN4

FB_DQS_RN5

FB_DQS_RN6

FB_DQS_RN7

FB_VREF

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VTT

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_VDDQ

FB_CMD0

FB_CMD1

FB_CMD2

FB_CMD3

FB_CMD4

FB_CMD5

FB_CMD6

FB_CMD7

FB_CMD8

FB_CMD9

FB_CMD10

FB_CMD11

FB_CMD12

FB_CMD13

FB_CMD14

FB_CMD15

FB_CMD16

FB_CMD17

FB_CMD18

FB_CMD19

FB_CMD20

FB_CMD21

FB_CMD22

FB_CMD23

FB_CMD24

FB_CMD25

FB_CMD26

FB_CLK0

FB_CLK0

FB_CLK1

FB_CLK1

FB_CAL_PD_VDDQ

FB_CAL_PU_GND

FB_CAL_TERM_GND

FB_DEBUG

FB_REFCLK

FB_REFCLK

FB_PLLVDD

FB_PLLAVDD

FB_PLLGND

E15

F15

F16

J17

J18

L19

N19

R19

U19

W19

F17

F19

J19

M19

T19

J22

L22

P22

U22

Y22

FB_CMD[26..0]

FB_CMD0

G27

FB_CMD1

D25

FB_CMD2

F26

FB_CMD3

F25

FB_CMD4

G25

FB_CMD5

J25

FB_CMD6

J27

FB_CMD7

M26

FB_CMD8

C27

FB_CMD9

C25

FB_CMD10

D24

FB_CMD11

N27

FB_CMD12

G24

FB_CMD13

J26

FB_CMD14

M27

FB_CMD15

C26

FB_CMD16

M25

FB_CMD17

D26

FB_CMD18

D27

FB_CMD19

K26

FB_CMD20

K25

FB_CMD21

K24

FB_CMD22

F27

FB_CMD23

K27

FB_CMD24

G26

FB_CMD25

B27

FB_CMD26

N24

FBACLK0

L24

FBACLK0*

K23

FBACLK1

M22

FBACLK1*

N22

FBCAL_PD_VDDQ

D15

FBCAL_PU_GND

E13

FBCAL_TERM_GND

H22

SNN_FBA_DEBUG

K22

SNN_FBA_REFCLK

M23

SNN_FBA_REFCLK*

M24

FBA_PLLVDD

D14

FBA_PLLAVDD

D13

C15

OUT

OUT

OUT

OUT

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

4,4,4,4

5,5,5,5

5,5,5,5

R514

0402 COMMON

5%

4,4,4,4

0

OUT

FBVDDQ

GND GND

R516

49.9

1%

0402

COMMON

R518

49.9

1%

0402

COMMON

4,5

GND

4,4,4,4,4,5,5,5,5,5,5

FBD[31..0]

BI

FBD[63..32]

BI

FBDQM[7..0]

OUT

FBDQS[7..0]

BI

FBD0

0

FBD1

1

FBD2

2

FBD3

3

FBD4

4

FBD5

5

FBD6

6

FBD7

7

FBD8

8

FBD9

9

FBD10

10

FBD11

11

FBD12

12

FBD13

13

FBD14

14

FBD15

15

FBD16

16

FBD17

17

FBD18

18

FBD19

19

FBD20

20

FBD21

21

FBD22

22

FBD23

23

FBD24

24

FBD25

25

FBD26

26

FBD27

27

FBD28

28

FBD29

29

FBD30

30

FBD31

31

FBD32

32

FBD33

33

FBD34

34

FBD35

35

FBD36

36

FBD37

37

FBD38

38

FBD39

39

FBD40

40

FBD41

41

FBD42

42

FBD43

43

FBD44

44

FBD45

45

FBD46

46

FBD47

47

FBD48

48

FBD49

49

FBD50

50

FBD51

51

FBD52

52

FBD53

53

FBD54

54

FBD55

55

FBD56

56

FBD57

57

FBD58

58

FBD59

59

FBD60

60

FBD61

61

FBD62

62

FBD63

63

FBDQM0

0

FBDQM1

1

FBDQM2

2

FBDQM3

3

FBDQM4

4

FBDQM5

5

FBDQM6

6

FBDQM7

7

FBDQS0

0

FBDQS1

1

FBDQS2

2

FBDQS3

3

FBDQS4

4

FBDQS5

5

FBDQS6

6

FBDQS7

7

SNN_FBDQS0*

SNN_FBDQS1*

SNN_FBDQS2*

SNN_FBDQS3*

SNN_FBDQS4*

SNN_FBDQS5*

SNN_FBDQS6*

SNN_FBDQS7*

4,4

1

2

5,5

3

4

FBVDDQ

R515

1K

1%

Rt

0402

COMMON

R517

1K

1%

Rb

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFEREN CE BOARDS, FI LES, DRAWINGS, DIAGNOSTICS , LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLAT IONS OR DEVIATIONS OF INDUSTRY STANDARDS AND S PECIFICATIONS. NVIDIA MAKES NO WARRANT IES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

0402

COMMON

GND

FBVREF = FBVDDQ * Rb/(Rt + Rb)

VREF = 0.5 * FBVDDQ

DDR: 1.25V = 2.5V * 1K/(1K + 1K)

A B D F

C590

.1UF

10V

10%

X5R

0402

COMMON

FBVREF

PLACE NEAR BGA

C570

.01UF

16V

10%

X7R

0402

COMMON

FBVTT connected to FBVDDQ for unterminate d DDR1

PLACE BELOW GPU

C562

4700PF

25V

10%

X7R

0402

COMMON

C582

4700PF

25V

10%

X7R

0402

COMMON

C566

4700PF

25V

10%

X7R

0402

COMMON

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

Frame Buffer Interf ace

C583

.01UF

16V

10%

X7R

0402

COMMON

C578

.022UF

16V

10%

X7R

0402

COMMON

C556

.022UF

16V

10%

X7R

0402

COMMON

C557

.022UF

16V

10%

X7R

0402

COMMON

C568

.01UF

16V

10%

X7R

0402

COMMON

C554

.1UF

10V

10%

X5R

0402

COMMON

C551

.1UF

10V

10%

X5R

0402

COMMON

C553

.1UF

10V

10%

X5R

0402

COMMON

PLACE NEAR BALLS

C589

.01UF

16V

10%

X7R

0402

COMMON

C596

.01UF

16V

10%

X7R

0402

COMMON

E GC

C569

.01UF

16V

10%

X7R

0402

COMMON

C573

4700PF

25V

10%

X7R

0402

COMMON

C574

4700PF

25V

10%

X7R

0402

COMMON

C567

.022UF

16V

10%

X7R

0402

COMMON

C547

4.7UF

6.3V

10%

X5R

0805

COMMON

C558

.1UF

10V

10%

X5R

0402

COMMON

C555

.022UF

16V

10%

X7R

0402

COMMON

C561

.1UF

10V

10%

X5R

0402

COMMON

C552

.1UF

10V

10%

X5R

0402

COMMON

C588

1UF

6.3V

10%

X5R

0402

COMMON

C595

1UF

6.3V

10%

X5R

0402

COMMON

FBVDDQ

GND

FBVDDQ

GND

GND

GND

C38

4.7UF

6.3V

10%

X5R

0805

COMMON

C565

1UF

6.3V

10%

X5R

0402

COMMON

C575

1UF

6.3V

10%

X5R

0402

COMMON

PLACE NEAR GPU

LB501 220R@100MHz

C37

4.7UF

6.3V

10%

X5R

0805

COMMON

LB502 220R@100MHz

C35

4.7UF

6.3V

10%

X5R

0805

COMMON

FBA_PLLAVDD not needed for MEP19/NV37MCM

HGFEDCBA

Net Name NET_SPACING_RULE

FBCAL_PD_VDDQ

IN

FBCAL_PU_GND

IN

FBCAL_TERM_GND

IN

FB_DLLVDD

IN

FBA_PLLAVDD

IN

FBVREF

IN

10MIL

10MIL

10MIL

10MIL

10MIL

10MIL

1

2

LABTESTPOINTS

FBDQS0

FBDQS1

TP504

FBDQS2

TP503

FBDQS3

FBDQS4

TP5

FBDQS5

TP502

FBDQS6

TP501

FBDQS7

TP4

TP3

TP2

3

F3V3

COMMON0402

4

GND

NVVDD

COMMON0402

GND

5

www.vinafix.vn

Page 4

1

Memory Bit 0..31

FB_CMD[26..0]

3,5

1

A A

2

B B

IN

NV_USE

FB_CMD15

FB_RAS*

15

FB_CMD25

FB_CAS*

25

FB_CMD9

FB_WE*

9

FB_CMD8

FB_CS0*

8

FB_CMD1

FB_A0

1

FB_CMD3

FB_A1

3

FB_CMD2

FB_A2

2

FB_CMD0

FB_A3

0

FB_CMD24

FB_A4

24

FB_CMD22

FB_A5

22

FB_CMD21

FB_A6

21

FB_CMD23

FB_A7

23

FB_CMD19

FB_A8

19

FB_CMD20

FB_A9

20

FB_CMD17

FB_A10

17

FB_CMD16

FB_A11

16

FB_CMD14

FB_A12

14

FB_CMD10

FB_BA0

10

FB_CMD18

FB_BA1

18

FB_CMD11

FB_CKE

11

3,4,4,4

IN

3,4,4,4

IN

2

U3A

16M66

XSOP66_P065W400MIL

COMMON

23

RAS

22

CAS

21

WE

24

CS

29

A<0>

30

A<1>

31

A<2>

32

A<3>

35

A<4>

36

A<5>

37

A<6>

38

A<7>

39

A<8>

40

A<9>

28

AP/A<10>

41

A<11>

42

A<12>

26

BA<0>

27

BA<1>

44

FBACLK0 FBACLK0

FBACLK0* FBACLK0*

CKE

45

CLK

46

CLK

NC

NC

NC

14

17

19

1

VDD

18

VDD

33

VDD

3

VDDQ

9

VDDQ

15

VDDQ

55

VDDQ

61

VDDQ

34

VSS

48

VSS

66

VSS

6

VSSQ

12

VSSQ

52

VSSQ

58

VSSQ

64

VSSQ

49

Vref

NC

NC

NC

NC

25

43

50

53

3

FBVDDQ

16V

10%

X7R

COMMON

FBVDDQ

R31

1K

5%

0402

COMMON

C68

R33

.047UF

1K

5%

0402

COMMON

0402

GND

MVREFA0 MVREFA1

FB_CMD15

15

25

9

8

1

3

2

0

24

22

21

23

19

20

17

16

14

10

18

11

FB_RAS*

FB_CMD25

FB_CAS*

FB_CMD9

FB_WE*

FB_CMD8

FB_CS0*

FB_CMD1

FB_A0

FB_CMD3

FB_A1

FB_CMD2

FB_A2

FB_CMD0

FB_A3

FB_CMD24

FB_A4

FB_CMD22

FB_A5

FB_CMD21

FB_A6

FB_CMD23

FB_A7

FB_CMD19

FB_A8

FB_CMD20

FB_A9

FB_CMD17

FB_A10

FB_CMD16

FB_A11

FB_CMD14

FB_A12

FB_CMD10

FB_BA0

FB_CMD18

FB_BA1

FB_CMD11

FB_CKE

3,4,4,4

IN

3,4,4,4

IN

GND

SNN_MEM1_14

SNN_MEM1_17

SNN_MEM1_19

SNN_MEM1_25

SNN_MEM1_43

SNN_MEM1_50

SNN_MEM1_53

4

U501A

16M66

XSOP66_P065W400MIL

COMMON

23

RAS

22

CAS

21

WE

24

CS

29

A<0>

30

A<1>

31

A<2>

32

A<3>

35

A<4>

36

A<5>

37

A<6>

38

A<7>

39

A<8>

40

A<9>

28

AP/A<10>

41

A<11>

42

A<12>

26

BA<0>

27

BA<1>

44

CKE

45

CLK

46

CLK

NC

NC

14

17

SNN_MEM2_14

SNN_MEM2_17

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

Vref

NC

NC

NC

NC

NC

19

25

43

50

53

SNN_MEM2_19

SNN_MEM2_25

SNN_MEM2_43

SNN_MEM2_50

SNN_MEM2_53

5

6

Net Name

3,4,4,4

3,4,4,4,4,5

3,4

3,4,4,4,4,4,5

FBACLK0

IN

FBACLK0*

3,4,4,4

IN

FBD[31..0]

IN

FBDQM[3..0]

IN

FBDQS[3..0]

IN

FBCMD[26..0]

IN

7

Diffpair NET_SPACING_RULE

FBACLK0 25MIL

FBACLK0 25MIL

10MIL

15MIL

15MIL

10MIL

HGFEDCBA

8

FBVDDQ

1

18

33

3

9

15

55

61

34

48

66

GND

6

12

52

58

64

49

C510

.047UF

16V

10%

X7R

0402

COMMON

FBVDDQ

R508

1K

5%

0402

COMMON

R506

1K

5%

0402

COMMON

GND GND

FBVDDQ

FBVDDQ

C536

.022UF

25V

10%

X7R

0402

COMMON

C517

220PF

50V

5%

COG

0402

COMMON

C534

.047UF

16V

10%

X7R

0402

COMMON

C519

4700PF

25V

10%

X7R

0402

COMMON

C533

220PF

50V

5%

COG

0402

COMMON

C529

4700PF

25V

10%

X7R

0402

COMMON

C506

.022UF

25V

10%

X7R

0402

COMMON

C520

220PF

50V

5%

COG

0402

COMMON

C539

4700PF

25V

10%

X7R

0402

COMMON

C508

4700PF

25V

10%

X7R

0402

COMMON

C526

220PF

50V

5%

COG

0402

COMMON

C524

4700PF

25V

10%

X7R

0402

COMMON

C515

.022UF

25V

10%

X7R

0402

COMMON

C530

220PF

50V

5%

COG

0402

COMMON

C522

.047UF

16V

10%

X7R

0402

COMMON

C513

4700PF

25V

10%

X7R

0402

COMMON

C503

4.7UF

6.3V

10%

X5R

0805

COMMON

C540

4.7UF

6.3V

10%

X5R

0805

COMMON

GND

C502

47UF

6.3V

20%

X5R

1206

COMMON

GND

1

2

FBD[31..0] FBD[31..0]

FBD0

0

FBD1 FBD1

1

FBD2

2

3

C C

4

D D

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFEREN CE BOARDS, FI LES, DRAWINGS, DIAGNOSTICS , LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLAT IONS OR DEVIATIONS OF INDUSTRY STANDARDS AND S PECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

FBD3

3

FBD4

4

FBD5

5

FBD6

6

FBD7

7

FBD8

8

FBD9

9

FBD10

10

FBD11

11

FBD12

12

FBD13

13

FBD14

14

FBD15

15

FBD16

16

FBD17

17

FBD18

18

FBD19

19

FBD20

20

FBD21

21

FBD22

22

FBD23

23

FBD24

24

FBD25

25

FBD26

26

FBD27

27

FBD28

28

FBD29

29

FBD30

30

FBD31

31

1

3,4

BI

RP5D

15

4 5

RPAK_8P4R_0402X4_2010

COMMON

5%

RP4C

3 6

RPAK_8P4R_0402X4_2010

5%

RP4A

1 8

RPAK_8P4R_0402X4_2010

5%

RP5C

3 6

RPAK_8P4R_0402X4_2010

5%

RP505C

3 6

RPAK_8P4R_0402X4_2010

5%

RP504D

4 5

RPAK_8P4R_0402X4_2010

5%

RP505B

2 7

RPAK_8P4R_0402X4_2010

5%

RP504A

1 8

RPAK_8P4R_0402X4_2010

5%

RP501D

4 5

RPAK_8P4R_0402X4_2010

5%

RP501B

2 7

RPAK_8P4R_0402X4_2010

5%

RP502C

3 6

RPAK_8P4R_0402X4_2010

5%

RP502A

1 8

RPAK_8P4R_0402X4_2010

5%

RP1D

4 5

RPAK_8P4R_0402X4_2010

5%

RP2B

2 7

RPAK_8P4R_0402X4_2010

5%

RP2A

1 8

RPAK_8P4R_0402X4_2010

5%

RP1A

1 8

RPAK_8P4R_0402X4_20105%COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

RP5A

1 8

RPAK_8P4R_0402X4_20105%COMMON

RP4D

4 5

RPAK_8P4R_0402X4_2010

5%

RP5B

2 7

RPAK_8P4R_0402X4_20105%COMMON

RP4B

2 7

RPAK_8P4R_0402X4_20105%COMMON

RP505A

1 8

RPAK_8P4R_0402X4_20105%COMMON

RP504B

2 7

RPAK_8P4R_0402X4_2010

5%

RP504C

3 6

RPAK_8P4R_0402X4_20105%COMMON

RP505D

4 5

RPAK_8P4R_0402X4_20105%COMMON

RP501C

3 6

RPAK_8P4R_0402X4_20105%COMMON

RP502D

4 5

RPAK_8P4R_0402X4_2010

5%

RP501A

1 8

RPAK_8P4R_0402X4_20105%COMMON

RP502B

2 7

RPAK_8P4R_0402X4_2010

5%

RP1C

3 6

RPAK_8P4R_0402X4_20105%COMMON

RP2C

3 6

RPAK_8P4R_0402X4_20105%COMMON

RP2D

4 5

RPAK_8P4R_0402X4_20105%COMMON

RP1B

2 7

RPAK_8P4R_0402X4_2010

5%

15

15

COMMON

15

15

15

15

COMMON

15

15

15

15

COMMON

15

15

COMMON

15

15

15

15

COMMON

A B D F H

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

3,4,4,4,4,4,5,5,5,5,5,5

15

14

13

12

11

10

9

8

3,4,4,5

31

30

29

28

27

26

25

24

3,4,4,5

FBDQM[7..0]

IN

2

FBD15

FBD14

FBD13

FBD12

FBD11

FBD10

FBD9

FBD8

FBDQM1

IN

BI

FBD31

FBD30

FBD29

FBD28

FBD27

FBD26

FBD25

FBD24

FBDQM3

3,4,4,5

IN

FBDQS3

BI

FBDQM0

0

FBDQM1

1

FBDQM2

2

FBDQM3

3

3

60

59

56

63

57

54

65

62

47

51

63

65

54

59

56

57

62

60

47

51

RP3C

3 6

RPAK_8P4R_0402X4_2010

5%

RP503C

3 6

RPAK_8P4R_0402X4_20105%COMMON

C

U501C

XSOP66_P065W400MIL

COMMON

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

U3C

XSOP66_P065W400MIL

COMMON

DQ<0>

DQ<1>

DQ<2>

DQ<3>

DQ<4>

DQ<5>

DQ<6>

DQ<7>

DQM

DQS

15

COMMON

15

RP503B

2 7

RPAK_8P4R_0402X4_2010

5%

RP3B

2 7

RPAK_8P4R_0402X4_2010

5%

15

COMMON

15

COMMON

4

ASSEMBLY

PAGE DETAIL

0

1

2

3

4

5

6

7

3,4,4,5

3,4,4,5

16

17

18

19

20

21

22

23

3,4,4,5

FBDQS[7..0]

3,4,4,4,4,4,5,5,5,5,5,5

BI

FBDQS0

0

FBDQS1

1

FBDQS2

2

FBDQS3

3

BASE LEVEL GE NERIC SCHEMATIC ONLY, CO MMON & NO_STU FF ASSEMBLY NOTES AND BOM NOT FINAL

Memory 1st bank 0..31

FBD0

FBD2

FBD3

FBD4

FBD5

FBD6

FBD7

FBDQM0

IN

FBDQS0FBDQS1

BI

FBD16

FBD17

FBD18

FBD19

FBD20

FBD21

FBD22

FBD23

FBDQM2

3,4,4,5

IN

FBDQS2

BI

RP3D

15

4 5

RPAK_8P4R_0402X4_2010

COMMON

5%

RP503D

15

4 5

RPAK_8P4R_0402X4_20105%COMMON

E GC

5

B

U3B

XSOP66_P065W400MIL

COMMON

2

DQ<0>

7

DQ<1>

10

DQ<2>

8

DQ<3>

13

DQ<4>

5

DQ<5>

4

DQ<6>

11

DQ<7>

20

DQM

16

DQS

U501B

XSOP66_P065W400MIL

COMMON

2

DQ<0>

4

DQ<1>

5

DQ<2>

8

DQ<3>

10

DQ<4>

7

DQ<5>

13

DQ<6>

11

DQ<7>

20

DQM

16

DQS

RP503A

1 8

RPAK_8P4R_0402X4_20105%COMMON

RP3A

1 8

RPAK_8P4R_0402X4_20105%COMMON

FBVDDQ

C70

.022UF

25V

10%

X7R

0402

COMMON

C64

220PF

50V

5%

COG

0402

COMMON

C47

.047UF

16V

10%

X7R

0402

COMMON

C56

4700PF

25V

10%

X7R

0402

COMMON

C71

4.7UF

6.3V

10%

X5R

0805

COMMON

C40

4.7UF

6.3V

10%

X5R

0805

COMMON

GND

FBVDDQ

C72

.022UF

25V

10%

X7R

0402

COMMON

C54

220PF

50V

5%

COG

0402

COMMON

C58

.047UF

16V

10%

X7R

0402

COMMON

C66

4700PF

25V

10%

X7R

0402

COMMON

C48

220PF

50V

5%

COG

0402

COMMON

C44

4700PF

25V

10%

X7R

0402

COMMON

C42

.022UF

25V

10%

X7R

0402

COMMON

C51

220PF

50V

5%

COG

0402

COMMON

C52

4700PF

25V

10%

X7R

0402

COMMON

C63

4700PF

25V

10%

X7R

0402

COMMON

C61

220PF

50V

5%

COG

0402

COMMON

C73

4700PF

25V

10%

X7R

0402

COMMON

GND

FBVDDQ

R38

120

5%

0402

COMMON

R39

120

5%

0402

COMMON

R365%560

15

15

FBACLK0

3,4,4,4

IN

FBACLK0*

3,4,4,4

IN

GND

R34

120

5%

0402

COMMON

COMMON0402

R35

120

5%

0402

COMMON

GND

Micro-Star International Co., LTD.

MS-V017

Size Document Number Rev

Custom

Memory Bit0..31

Date:

Wednesday, June 15, 2005

6

7

Sheet of

414

8

00A

3

4

5

www.vinafix.vn

Page 5

1

Memory Bit 32..63

FB_CMD[26..0]

1

A A

2

B B

3,4

IN

2

U4A

16M66

XSOP66_P065W400MIL

R37

10K

5%

0402

COMMON

COMMON

23

RAS

22

CAS

21

WE

24

CS

29

A<0>

30

A<1>

31

A<2>

32

A<3>

35

A<4>

36

A<5>

37

A<6>

38

A<7>

39

A<8>

40

A<9>

28

AP/A<10>

41

A<11>

42

A<12>

26

BA<0>

27

BA<1>

44

CKE

45

CLK

46

CLK

NC

NC

NC

NC

14

17

19

25

FB_CMD15

FB_RAS*

15

FB_CMD25

FB_CAS*

25

FB_CMD9

FB_WE*

9

FB_CMD8

FB_CS0*

8

FB_CMD1

FB_A0

1

FB_CMD3

FB_A1

3

FB_CMD13

FB_A2

13

FB_CMD4

FB_A3

4

FB_CMD5

FB_A4

5

FB_CMD6

FB_A5

6

FB_CMD21

FB_A6

21

FB_CMD23

FB_A7

23

FB_CMD19

FB_A8

19

FB_CMD20

FB_A9

20

FB_CMD17

FB_A10

17

FB_CMD16

FB_A11

16

FB_CMD14

FB_A12

14

FB_CMD10

FB_BA0

10

FB_CMD18

FB_BA1

18

FB_CMD11

FB_CKE

11

FBACLK1 FBACLK1

3,5,5,5

IN

FBACLK1* FBACLK1*

3,5,5,5

IN

GND

SNN_MEM3_14

SNN_MEM3_17

SNN_MEM3_19

SNN_MEM3_25

3

FBVDDQ

1

VDD

18

VDD

33

VDD

3

VDDQ

9

VDDQ

15

VDDQ

55

VDDQ

61

VDDQ

34

VSS

48

VSS

66

VSS

GND

6

VSSQ

12

VSSQ

52

VSSQ

58

VSSQ

64

VSSQ

MVREFB0 MVREFB1

49

Vref

NC

NC

NC

43

50

53

C67

.047UF

16V

10%

X7R

0402

COMMON

FBVDDQ

R30

1K

5%

0402

COMMON

R32

1K

5%

0402

COMMON

GND

SNN_MEM3_43

SNN_MEM3_50

SNN_MEM3_53

4

U502A

16M66

XSOP66_P065W400MIL

FB_CMD15

15

25

9

8

1

3

13

4

5

6

21

23

19

20

17

16

14

10

18

11

FB_RAS*

FB_CMD25

FB_CAS*

FB_CMD9

FB_WE*

FB_CMD8

FB_CS0*

FB_CMD1

FB_A0

FB_CMD3

FB_A1

FB_CMD13

FB_A2

FB_CMD4

FB_A3

FB_CMD5

FB_A4

FB_CMD6

FB_A5

FB_CMD21

FB_A6

FB_CMD23

FB_A7

FB_CMD19

FB_A8

FB_CMD20

FB_A9

FB_CMD17

FB_A10

FB_CMD16

FB_A11

FB_CMD14

FB_A12

FB_CMD10

FB_BA0

FB_CMD18

FB_BA1

FB_CMD11

FB_CKE

3,5,5,5

IN

3,5,5,5

IN

COMMON

23

RAS

22

CAS

21

WE

24

CS

29

A<0>

30

A<1>

31

A<2>

32

A<3>

35

A<4>

36

A<5>

37

A<6>

38

A<7>

39

A<8>

40

A<9>

28

AP/A<10>

41

A<11>

42

A<12>

26

BA<0>

27

BA<1>

44

CKE

45

CLK

46

CLK

NC

NC

NC

14

17

19

SNN_MEM4_14

SNN_MEM4_17

SNN_MEM4_19

5

FBVDDQ

1

VDD

18

VDD

33

VDD

3

VDDQ

9

VDDQ

15

VDDQ

55

VDDQ

61

VDDQ

34

VSS

48

VSS

66

VSS

GND

6

VSSQ

12

VSSQ

52

VSSQ

58

VSSQ

64

VSSQ

49

Vref

NC

NC

NC

NC

25

43

50

53

C511

.047UF

16V

10%

X7R

0402

COMMON

FBVDDQ

R509

1K

5%

0402

COMMON

R507

1K

5%

0402

COMMON

GND GND

SNN_MEM4_25

SNN_MEM4_43

SNN_MEM4_50

SNN_MEM4_53

6

3,5,5,5

3,5,5,5

3,5

3,4,5,5,5,5,5

3,4,5,5,5,5,5

FBACLK1

IN

FBACLK1*

IN

FBD[63..32]

IN

FBDQM[7..4]

IN

FBDQS[7..4]

IN

7

NET_SPACING_RULENet Name Diffpair

25MILFBACLK1

25MILFBACLK1

10MIL

15MIL

15MIL

8

HGFEDCBA

FBVDDQ

FBVDDQ

C69

.022UF

25V

10%

X7R

0402

COMMON

C49

220PF

50V

5%

COG

0402

COMMON

C45

.047UF

16V

10%

X7R

0402

COMMON

C62

4700PF

25V

10%

X7R

0402

COMMON

C53

220PF

50V

5%

COG

0402

COMMON

C55

4700PF

25V

10%

X7R

0402

COMMON

C41

.022UF

25V

10%

X7R

0402

COMMON

C46

220PF

50V

5%

COG

0402

COMMON

C43

4700PF

25V

10%

X7R

0402

COMMON

C50

4700PF

25V

10%

X7R

0402

COMMON

C60

220PF

50V

5%

COG

0402

COMMON

C65

4700PF

25V

10%

X7R

0402

COMMON

C74

.022UF

25V

10%

X7R

0402

COMMON

C59

220PF

50V

5%

COG

0402

COMMON

C57

.047UF

16V

10%

X7R

0402

COMMON

C75

4700PF

25V

10%

X7R

0402

COMMON

C501

47UF

6.3V

20%

X5R

1206

COMMON

4.7UF

6.3V

10%

X5R

0805

COMMON

C39

4.7UF

6.3V

10%

X5R

0805

COMMON

GND

C76

GND

FBVDDQ

FBD[63..32] FBD[63..32]

FBD32

32

FBD33

33

FBD34

34

3

35

FBD36

36

FBD37

37

FBD38

38

FBD39

39

FBD40

40

FBD41

41

FBD42

42

FBD43

43

FBD44

C C

D D

44

FBD45

45

FBD46

46

FBD47

47

FBD48

48

FBD49

49

4

FBD50

50

FBD51

51

FBD52

52

FBD53

53

FBD54

54

FBD55

55

FBD56

56

FBD57

57

FBD58

58

FBD59

59

FBD60

60

FBD61

61

FBD62

62

FBD63

63

5

3,5

BI

RP6D

4 5

RPAK_8P4R_0402X4_20105%COMMON

RP6B

2 7

5%

RP7D

4 5

5%

RP7B

2 7

RPAK_8P4R_0402X4_2010COMMON

5%

RP510A

1 8

5%

RP510B 15

2 7

5%

RP510D

4 5

RPAK_8P4R_0402X4_2010COMMON

5%

RP509B

2 7

RPAK_8P4R_0402X4_20105%COMMON

RP507A

1 8

RPAK_8P4R_0402X4_2010

5%

RP506C

3 6

5%

RP507D

4 5

5%

RP506B

2 7

RPAK_8P4R_0402X4_2010

5%

RP10A

1 8

RPAK_8P4R_0402X4_2010

5%

RP9C

3 6

RPAK_8P4R_0402X4_2010

5%

RP10C

3 6

RPAK_8P4R_0402X4_2010

5%

RP9B

2 7

RPAK_8P4R_0402X4_2010

5%

15

15

COMMONRPAK_8P4R_0402X4_2010

15

COMMONRPAK_8P4R_0402X4_2010

15

15

COMMONRPAK_8P4R_0402X4_2010

COMMONRPAK_8P4R_0402X4_2010

15

15

15

COMMON

15

COMMONRPAK_8P4R_0402X4_2010

15

COMMONRPAK_8P4R_0402X4_2010

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

RP6C 15

3 6

RPAK_8P4R_0402X4_2010

5%

RP6A

1 8

RPAK_8P4R_0402X4_2010

5%

RP7C

3 6

RPAK_8P4R_0402X4_2010

5%

RP7A

1 8

RPAK_8P4R_0402X4_2010

5%

A

RP509A

1 8

RPAK_8P4R_0402X4_2010

5%

RP509D

4 5

RPAK_8P4R_0402X4_2010

5%

RP510C

3 6

RPAK_8P4R_0402X4_2010

5%

RP509C

3 6

RPAK_8P4R_0402X4_2010

5%

RP507B

2 7

RPAK_8P4R_0402X4_2010

5%

RP506D

4 5

RPAK_8P4R_0402X4_2010

5%

RP507C

3 6

RPAK_8P4R_0402X4_2010

5%

A

RP506A

1 8

RPAK_8P4R_0402X4_2010

5%

RP9D

4 5

RPAK_8P4R_0402X4_2010

5%

RP10D

4 5

RPAK_8P4R_0402X4_2010

5%

RP10B

2 7

5%

RP9A

1 8

RPAK_8P4R_0402X4_2010

5%

C512

R502

120

5%

0402

COMMON

R501

120

5%

0402

COMMON

C505

.022UF

25V

10%

X7R

0402

COMMON

C518

220PF

50V

5%

COG

0402

COMMON

C527

4700PF

25V

10%

X7R

0402

COMMON

C516

4700PF

25V

10%

X7R

0402

COMMON

.022UF

25V

10%

X7R

0402

COMMON

C523

4700PF

25V

10%

X7R

0402

COMMON

C537

4.7UF

6.3V

10%

X5R

0805

COMMON

GND

C525

C514

220PF

220PF

50V

50V

5%

5%

COG

COG

0402

0402

COMMON

COMMON

C507

4700PF

25V

10%

X7R

0402

COMMON

C521

.047UF

16V

10%

X7R

0402

COMMON

C504

4.7UF

6.3V

10%

X5R

0805

COMMON

GND

R505

120

5%

0402

R503

0402

COMMON

560

COMMON

5%

R504

120

5%

0402

COMMON

GND

C509

C535

4700PF

.022UF

25V

FBVDDQ

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

C531

C528

220PF

220PF

50V

50V

5%

5%

COG

COG

0402

0402

COMMON

COMMON

C538

C532

4700PF

.047UF

16V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

FBVDDQ

FBACLK1

3,5,5,5

IN

FBACLK1*

3,5,5,5

IN

GND

U4C

XSOP66_P065W400MIL

32

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMON

15

COMMONRPAK_8P4R_0402X4_2010

15

COMMON

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

3,4,4,4,4,4,5,5,5,5,5

FBDQM[7..0]

IN

39

38

37

36

35

34

33

32

3,4,5,5

55

54

53

52

51

50

49

48

3,4,5,5

FBDQM4

4

FBDQM5

5

FBDQM6

6

FBDQM7

7

3,4,5,5

IN

BI

IN

BI

RP8B 15

2 7

RPAK_8P4R_0402X4_2010COMMON

5%

RP508B

2 7

RPAK_8P4R_0402X4_2010

5%

FBD39

FBD38

FBD37

FBD36

FBD35

FBD34FBD35

FBD33

FBD32

FBDQM4

FBDQS4

FBD55

FBD54

FBD53

FBD52

FBD51

FBD50

FBD49

FBD48

FBDQM6

FBDQS6

15

COMMON

COMMON

54

DQ<0>

56

DQ<1>

57

DQ<2>

59

DQ<3>

60

DQ<4>

62

DQ<5>

63

DQ<6>

65

DQ<7>

47

DQM

51

DQS

U502B

XSOP66_P065W400MIL

COMMON

2

DQ<0>

4

DQ<1>

10

DQ<2>

8

DQ<3>

7

DQ<4>

5

DQ<5>

11

DQ<6>

13

DQ<7>

20

DQM

16

DQS

RP508C

3 6

RPAK_8P4R_0402X4_2010

5%

RP8C

3 6

RPAK_8P4R_0402X4_2010

5%

15

COMMON

15

COMMON

3,4,4,4,4,4,4,5,5,5,5,5

3,4,5,5

IN

BI

IN

BI

RP8A

1 8

RPAK_8P4R_0402X4_2010

5%

RP508A

1 8

RPAK_8P4R_0402X4_2010

5%

FBD41

FBD40

FBD42

FBD43

FBD44

FBD45

FBD46

FBD47

FBDQM5

FBDQS5

FBD56

FBD57

FBD58

FBD59

FBD60

FBD61

FBD62

FBD63

FBDQM7

FBDQS7

15

COMMON

15

COMMON

41

40

42

43

44

45

46

47

3,4,5,5

3,4,5,5

56

57

58

59

60

61

62

63

3,4,5,5

FBDQS[7..0]

BI

FBDQS4

4

FBDQS5

5

FBDQS6

6

FBDQS7

7

U502C

XSOP66_P065W400MIL

COMMON

54

DQ<0>

60

DQ<1>

62

DQ<2>

59

DQ<3>

65

DQ<4>

63

DQ<5>

56

DQ<6>

57

DQ<7>

47

DQM

51

DQS

U4B

XSOP66_P065W400MIL

COMMON

7

DQ<0>

8

DQ<1>

10

DQ<2>

2

DQ<3>

4

DQ<4>

5

DQ<5>

11

DQ<6>

13

DQ<7>

20

DQM

16

DQS

RP508D

4 5

RPAK_8P4R_0402X4_2010

5%

RP8D

4 5

5%

15

COMMON

15

COMMONRPAK_8P4R_0402X4_2010

1

2

3

4

5

ASSEMBLY

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFEREN CE BOARDS, FI LES, DRAWINGS, DIAGNOSTICS , LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLAT IONS OR DEVIATIONS OF INDUSTRY STANDARDS AND S PECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

1

2

3

PAGE DETAIL

4

www.vinafix.vn

BASE LEVEL GE NERIC SCHEMATIC ONLY, CO MMON & NO_STU FF ASSEMBLY NOTES AND BOM NOT FINAL

Memory 1st bank 32..63

E GC

5

Micro-Star International Co., LTD.

MS-V017

Size Document Number Rev

Custom

Memory Bit 32..63

Date:

Wednesday, June 15, 2005

6

7

Sheet of

8

00A

514

Page 6

1

2

DAC-A, DB15 Connector

3

4

5

6

7

8

HGFEDCBA

1

A A

R535

33

COMMON0402

Net Name

I2CA_SCL

IN

I2CA_SDA

IN

DACA_HSYNC

IN

DACA_VSYNC

IN

DACA_RED

IN

DACA_GREEN

IN

DACA_BLUE

IN

DACA_VDD

IN

DACA_R_F

IN

DACA_G_F

IN

DACA_B_F

IN

DACA_RED_C

8

IN

DACA_GREEN_C

8

IN

DACA_BLUE_C

8

2

IN

NET_SPACING_TYPEMIN_LINE_WIDTH

10MIL

10MIL

10MIL

10MIL

20MIL

20MIL

20MIL

10MIL12MIL

20MIL

20MIL

20MIL

20MIL

20MIL

20MIL

5%

R530

04025%COMMON

33

5V

5V

C711

B B

.100UF

25V

10%

X7R

0603

COMMON

GND

CAP for Sync Buffer

3

U507C

10

8

SO14_150MIL

9

COMMON

7 14

GND

5V

U507D

13

11

SO14_150MIL

12

COMMON

7 14

5V

R580

AHB

R587

0402

AVB

R4

2.2K

5%

0402

COMMON

R3

2.2K

5%

0402

COMMON

15

04025%COMMON

15

COMMON

5%

R579

04025%COMMON

R588

0402 COMMON

5%

33

33

DACA_HSYNC_BUF DACA_HSYNC_C

DACA_VSYNC_BUF DACA_VSYNC_C

GND

LB4

150-220R@100MHz

0603 COMMON

5V

D5

SOT23

3

100V

100MA

COMMON

1 2

GND

LB3

150-220R@100MHz

0603 COMMON

5V

D8

SOT23

3

100V

100MA

COMMON

1 2

GND

L4

27nH

0603 COMMON

5V

D6

SOT23

3

100V

100MA

COMMON

1 2

GND

L3

27nH

0603 COMMON

5V

D7

SOT23

3

100V

100MA

COMMON

1 2

C7

220PF

50V

5%

NPO

0603

COMMON

GND

C6

220PF

50V

5%

NPO

0603

COMMON

GND

C8

12PF

50V

5%

NPO

0603

COMMON

GND

C1

12PF

50V

5%

NPO

0603

COMMON

GND

DDC_5V

GND

DACA_R_F

L509

L508

L504

0603 COMMON

27nH

C749

22PF

50V

5%

NPO

0402

COMMON

GND

27nH

COMMON0603

C743

22PF

50V

5%

NPO

0402

COMMON

GND

27nH

COMMON0603

C750

22PF

50V

5%

NPO

0402

COMMON

GND

R612

0

COMMON0603

R539

F3V3

F3V3

C C

4

GND

LB504

220R@100MHz

COMMON

0402

C643

1UF

6.3V

10%

X5R

0402

COMMON

C663

4.7UF

6.3V

10%

X5R

0805

COMMON

GND

U2C

BGA533_P08_23X23MM_G3-64

DACA

COMMON

3/12 DAC_A

AE2

DAC_A_VDD

AB4

DAC_A_VREF

AD3

DAC_A_RSET

I2CA_SCL

I2CA_SDA

DAC_A_HSYNC

DAC_A_VSYNC

DAC_A_RED

DAC_A_GREEN

DAC_A_BLUE

DAC_A_IDUMP

I2CA_SCL

D10

I2CA_SDA

E10

DACA_HSYNC

AD4

DACA_VSYNC

AC4

DACA_RED

AE1

DACA_GREEN

AD1

DACA_BLUE

AD2

U9

C644

1UF

6.3V

10%

X5R

0402

COMMON

C642

4700PF

25V

10%

X7R

0402

COMMON

C641

470PF

50V

10%

X7R

0402

COMMON

C639

1UF

6.3V

10%

X5R

0402

COMMON

DACA_VDD

DACA_VREF

DACA_RSET

R528

127

1%

0402

COMMON

GND

D D

5

3

GND

3

GND

3

150

1%

0402

D506

COMMON

SOT23

100V

100MA

COMMON

GND

1 2

R538

F3V3

150

1%

0402

D504

COMMON

SOT23

100V

100MA

COMMON

GND

1 2

R537

F3V3

150

1%

0402

D505

COMMON

SOT23

100V

100MA

COMMON

GND

1 2

R603

R607

2.2K

150

5%

1%

0402

0402

COMMON

COMMON

GND

GND

R604

R606

2.2K

150

1%

5%

0402

0402

COMMON

COMMON

GND

GND

R605

R602

150

2.2K

5%

1%

0402

0402

COMMON

COMMON

GND

GND

.05R

C736

22PF

50V

5%

NPO

0402

COMMON

GND

R611 0

0603

C735

22PF

50V

5%

NPO

0402

COMMON

GND

R613

0603 COMMON

C734

22PF

50V

5%

NPO

0402

COMMON

GND

C741

22PF

50V

5%

NPO

0402

COMMON

GND

DACA_G_F

COMMON

.05R

C740

22PF

50V

5%

NPO

0402

COMMON

GND

DACA_B_F

0

.05R

C742

22PF

50V

5%

NPO

0402

COMMON

GND

DACA_RED_C

DACA_GREEN_C

DACA_BLUE_C

SNN_A_ID2

PLACE NEAR OUTPUT FILTERS

8

OUT

I2CA_SCL_CI2CA_SCL_T

8

OUT

I2CA_SDA_CI2CA_SDA_T

8

OUT

8

OUT

J1

CON_WIESON_31796219

COMMON

SHIELD

16

GND-R

6

R

1

GND-G

7

G

2

GND_B

8

B

3

5V

9

ID2

4

GND

10

GND

5

SHIELD

17

1611

ID0

SNN_A_ID0

11

SDA

12

HSYNC

13

VSYNC

14

SCL

15

15105

GND

F3V3

C717

4.7UF

6.3V

10%

X5R

0805

COMMON

GND

5V

C712

4.7UF

6.3V

10%

X5R

0805

COMMON

GND

GND

ASSEMBLY

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFEREN CE BOARDS, FI LES, DRAWINGS, DIAGNOSTICS , LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLAT IONS OR DEVIATIONS OF INDUSTRY STANDARDS AND S PECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

1

2

3

PAGE DETAIL

4

BASE LEVEL GE NERIC SCHEMATIC ONLY, CO MMON & NO_STU FF ASSEMBLY NOTES AND BOM NOT FINAL

DACA, DACB, DACC, Sync Buffers

E GC

5

6

7

Micro-Star International Co., LTD.

MS-V017

Size Document Number Rev

Custom

DAC-A, DB15 C onnector

Date:

Wednesday, June 15, 2005

Sheet of

614

8

00A

1

2

3

4

5

www.vinafix.vn

Page 7

1

2

3

4

5

6

7

8

HGFEDCBA

DAC-B, MUX, DB15

1

A A

I2CB_SCL

I2CB_SDA

DACB_HSYNC

F3V3

2

C664

4.7UF

6.3V

10%

X5R

0805

COMMON

GND

LB503

220R@100MHz

COMMON

0402

C628

1UF

6.3V

10%

X5R

0402

COMMON

C627

1UF

6.3V

10%

X5R

0402

COMMON

GND

DACB_VDD

C620

1UF

6.3V

10%

X5R

0402

COMMON

1G1D1S

127 (84.5)

1%

0402

COMMON

DACB_RSET

R548

G

1

C630

C629

470PF

4700PF

50V

25V

10%

10%

X7R

X7R

0402

0402

COMMON

COMMON

11

HDTV_SEL

IN

DACB_VREF

D

S

1%

0402

COMMON

UNNAMED_7_QFETNENH_I263_D

3

Q501

SOT23

COMMON

2

50V

0.22A@31C

3.5R

0.88A

0.36W@25C

+/-20V

R549

249

U2D

BGA533_P08_23X23MM_G3-64

COMMON

4/12 DAC_B

F8

DAC_B_VDD

E7

DAC_B_VREF

D6

DAC_B_RSET

DACB

I2CB_SCL

I2CB_SDA

DAC_B_HSYNC