Page 1

5

4

3

2

1

D D

MS-V005 VER 10

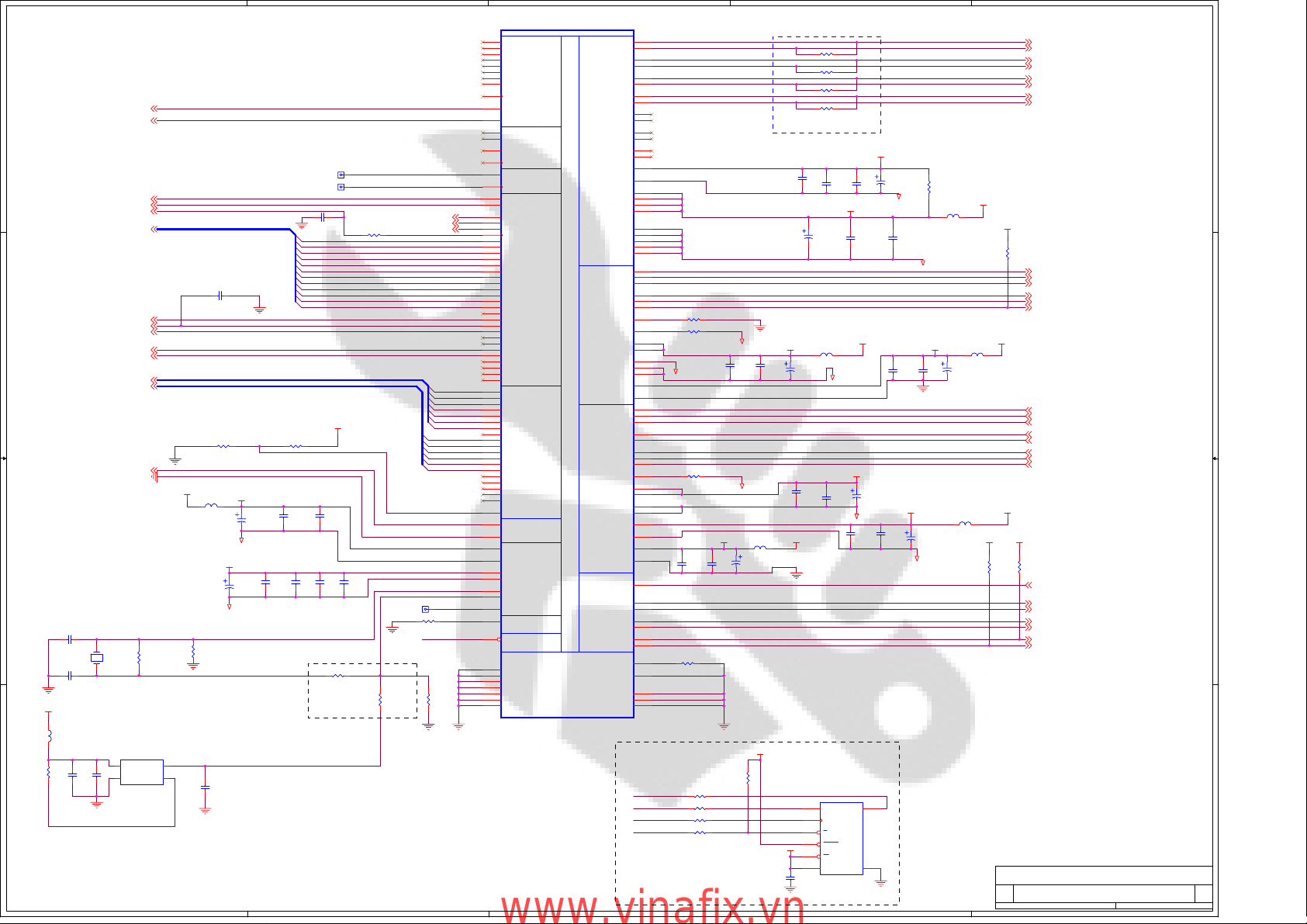

ATI-PCIEXPRESS RV410 BGA 8MX32 DDRIII, VGA, SCART(VIA VT1623M), TV-OUT,DVI

TITLE

C C

B B

COVER

BLOCK

PCI-EXPRESS CONNECTOR

RV410 PCIE_INTERFACE

RV410_MAIN

RV410_POWER

RV410 GND

REGULATOR FOR GPU,MEMORY AND OTHERS

RV410_MEM_A_B

GDDRIII_A_B_Rank0 & Bank1

STRAPPING

FAN

CRT FILTER

DVI-I CONNECTOR

VIA-VT1623M

PAGE

1

2

3

4

5

6

7

8-10

11

12,13

14

15

16

17

18

FREQUENCY

CORE

MEMORY

MHZ

425

430

A A

MS-V005 ATI RV410

Size Document Number Rev

B

5

4

3

2

Date: Sheet

COVER

of

1

1

10

18Tuesday, December 28, 2004

www.vinafix.vn

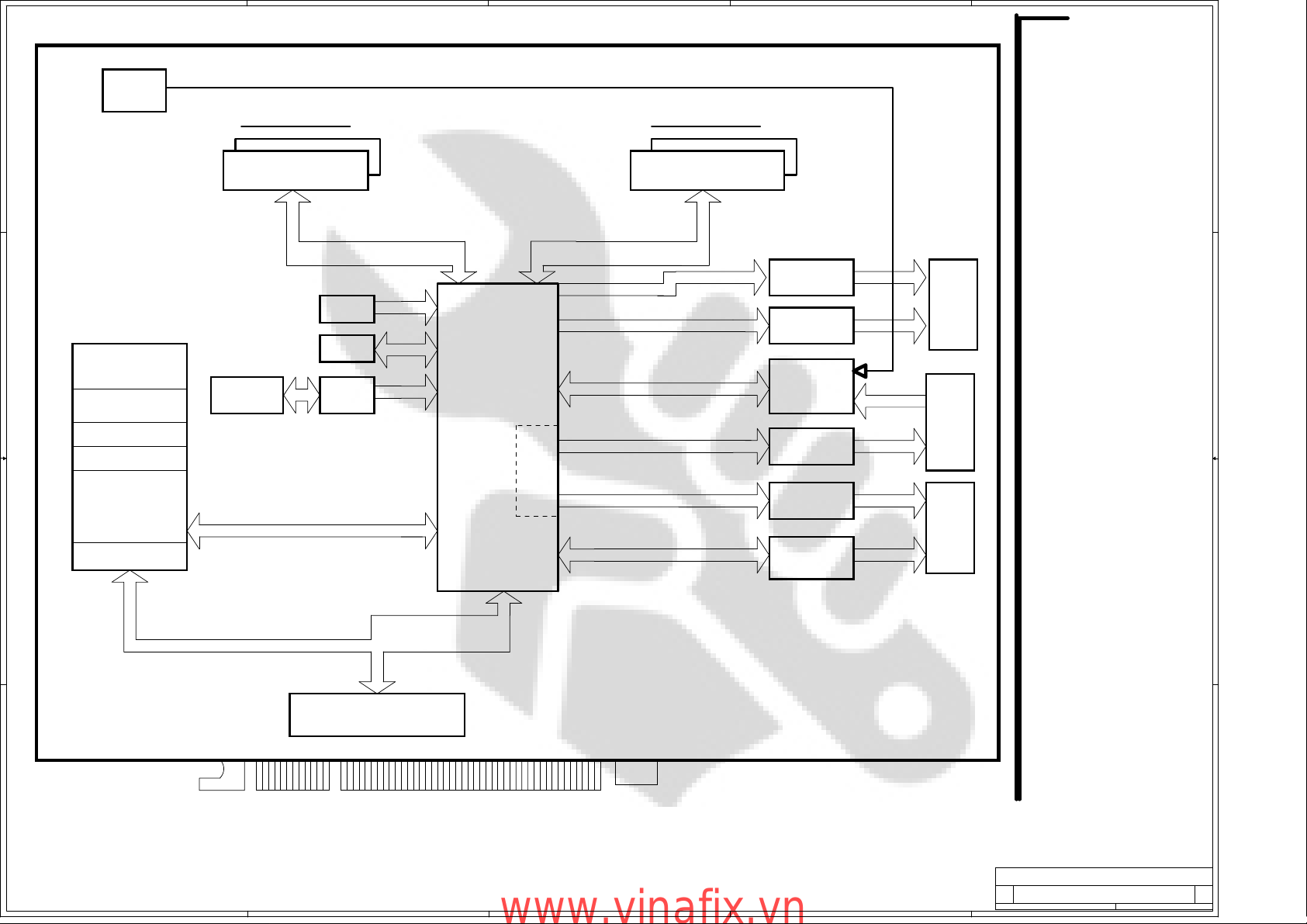

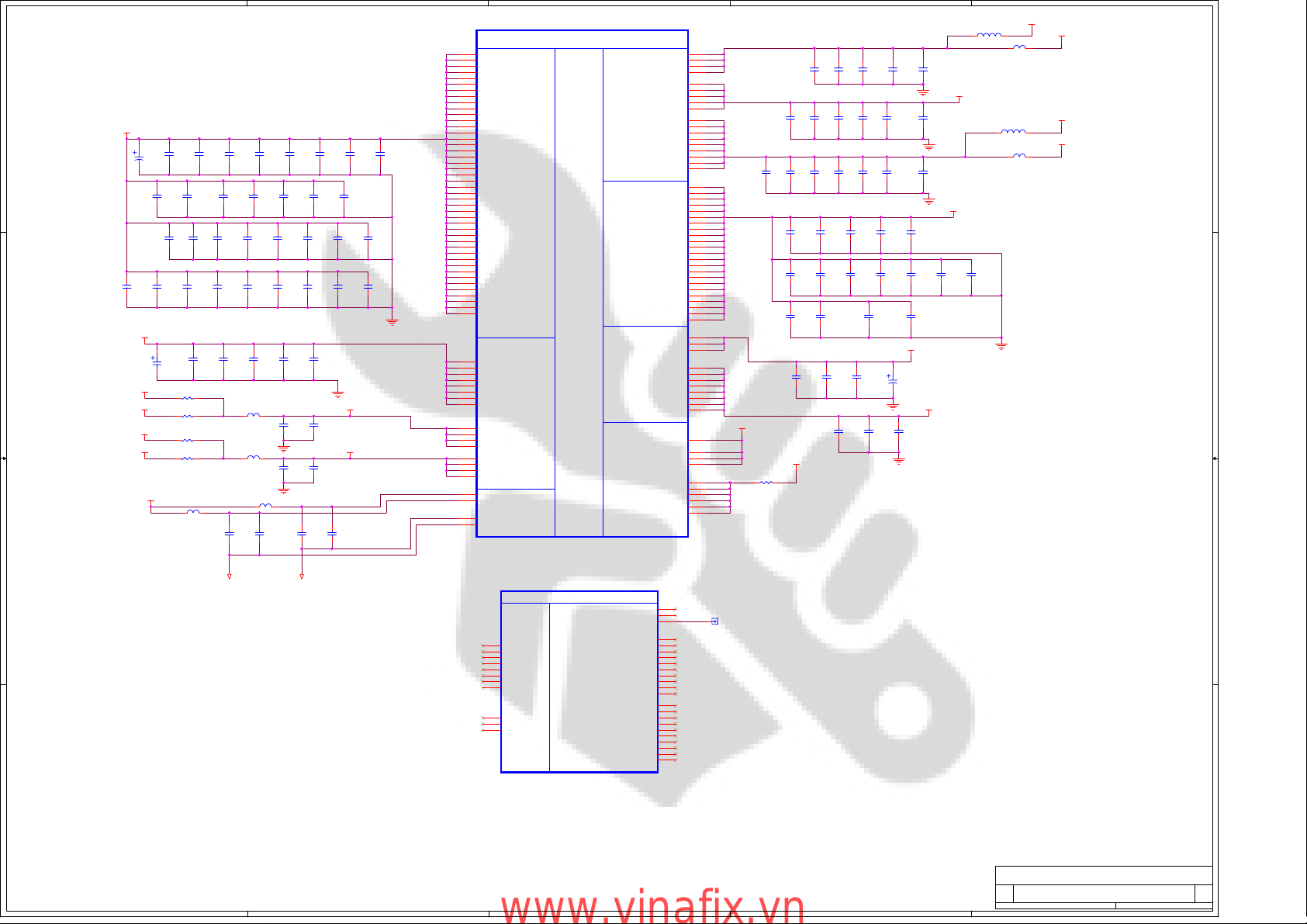

Page 2

5

VIDEO IN

CONNECTOR

SHT 20

D D

MEMORY CHANNEL A

Rank 1

Rank 0

GDDRIII (144 BALL BGA)

SHT 12

4

3

2

1

MEMORY CHANNEL B

Rank 1

Rank 0

GDDRIII (144 BALL BGA)

SHT 13

VIP

TVO

CRT

MAB[14..0]

MAB[14..0]

QSB[7..0]

CASB#

RASB#

QSB#[7..0] RESET

DQMB[0..7]

WEB#

CLKB01#

CSB#01

CKEBCLKB01

DVP

R G B HSY VSY DDC1DATA DDC1CLK

TMDS_TX[C,2..0]N TMDS_TX[C,2..0]P HPD, DDC2CLK DDC2DATA

External TMDS

PRIMARY CRT

FILTERS

SHEET 16

Rage Theater 1

SHT 19

TVOUT

FILTERS

SHT 20

SECONDARY

CRT FILTERS

SHT 16, 17

IMPEDANCE

MATCHING

SHT 4

DVI-I

CONN

SHT 16

TVout/

VIVO

CONN

SHT 20

DVI-I

CONN

SHT 18

MAA[14..0]

QSA[7..0]

CASA#

QSA#[7..0]

RASA#

CLKA01

DQMA[0..7]

WEA#

CLKA01#

RESET

CSA#01MDA[63..0]

CKEA/B

MEM A MEM B

STRAPS

SHT 14

C C

B B

POWER

REGULATION

SHT 5, 6, 7, 8, 9

From +12v

SINGLE PHASE SWITCHING:

VDDC, MVDDC, MVDDQ

From +12V DIRECT:

FAN

From +12V LINEAR:

+5V, RAGE THEATER

From +3.3 V LINEAR:

AVDD, VDD15, VDDRH

TPVDD, TXVDDR, PVDD,

AVDDDI, A2VDD, A2VDDDI,

A2VDDQ, PCIE_VDDR,

PCIE_PVDD_18, VDDC_CT

VDDR4, VDDR5

From +3.3 V DIRECT:

VDDR3

Speed control

& temperature

SHT 15

sense

POWER DELIVERY

BIOS

SHT 4

FAN

SHT 15

ROMCS#

GPIO

DAC1

ROM

RV410

SHEET 3 , 4, 5, 6, 10, 11

DAC2

TMDS

PCI-Express

PCI-Express Bus

SHT 2

RV410 Morpheus Pipecleaner

REV 0.3

A A

Size Docum e n t N u mb er Re v

C

5

4

www.vinafix.vn

3

2

Date: Sheet

MS-V005 ATI RV410

RV410 Block_Diagram

1

2

10

18Tuesday, De ce mber 28, 2004

of

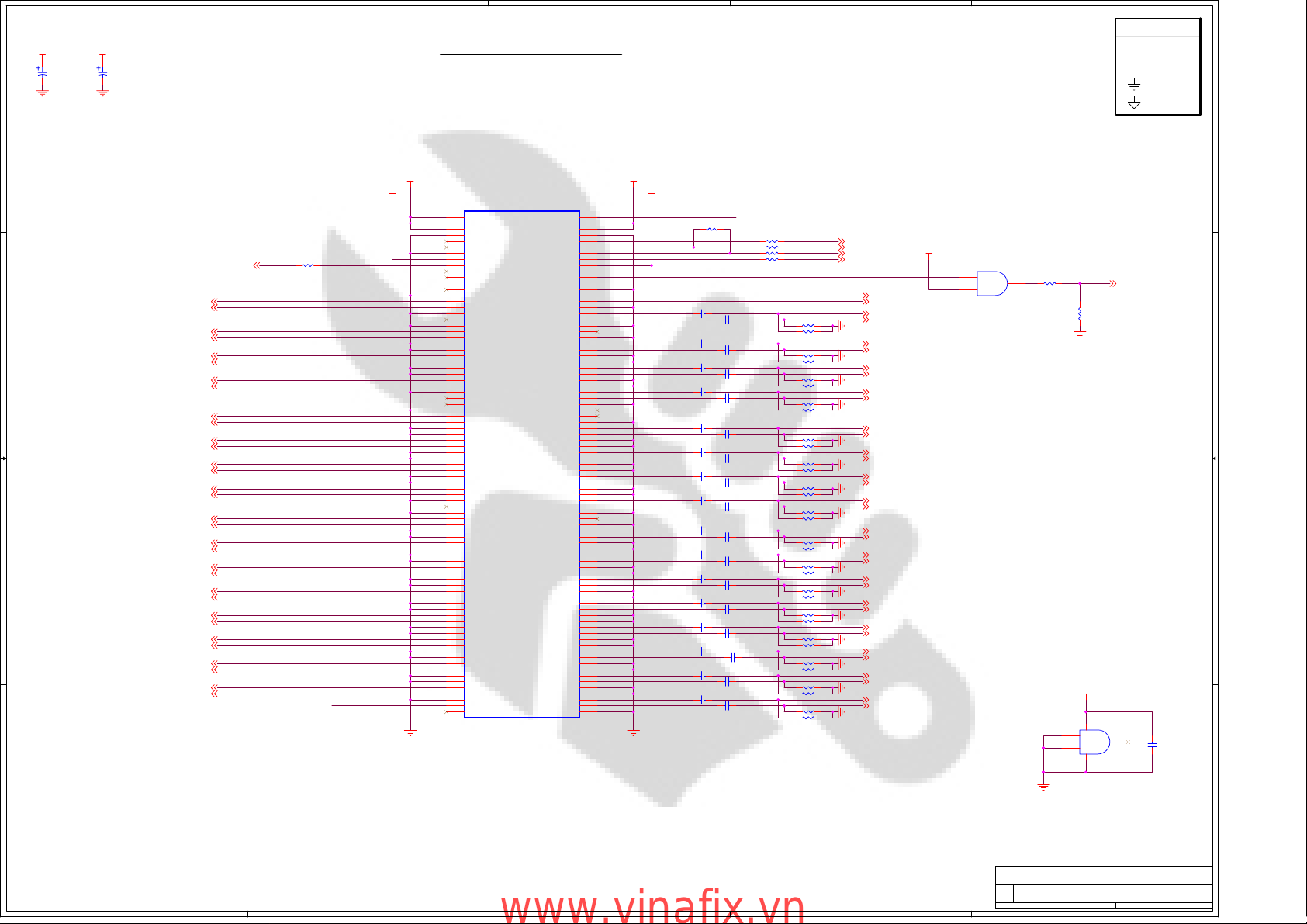

Page 3

5

+12V_BUS +3.3V_BUS

C10

100uF_16V

D D

C3

100uF_16V

4

PCI-EXPRESS BUS

3

2

1

SYMBOL LEGEND

DO NOT

DNI

INSTALL

#

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

+12V_BUS

+3.3V_BUS

MPCIE1

B1

+12V#B1

B2

+12V#B2

B3

RSVD#B3

B4

GND#B4

B5

SMCLK

B6

SMDAT

B7

GND#B7

B8

HSYNC_DAC1(5,14,16)

PETp0_GFXRp0(4) PCIE_REFCLKN (4)

PETn0_GFXRn0(4)

PETp1_GFXRp1(4)

C C

B B

PETn1_GFXRn1(4)

PETp2_GFXRp2(4)

PETn2_GFXRn2(4)

PETp3_GFXRp3(4)

PETn3_GFXRn3(4)

PETp4_GFXRp4(4)

PETn4_GFXRn4(4)

PETp5_GFXRp5(4)

PETn5_GFXRn5(4)

PETp6_GFXRp6(4)

PETn6_GFXRn6(4)

PETp7_GFXRp7(4)

PETn7_GFXRn7(4)

PETp8_GFXRp8(4)

PETn8_GFXRn8(4)

PETp9_GFXRp9(4)

PETn9_GFXRn9(4)

PETp10_GFXRp10(4)

PETn10_GFXRn10(4)

PETp11_GFXRp11(4)

PETn11_GFXRn11(4)

PETp12_GFXRp12(4)

PETn12_GFXRn12(4)

PETp13_GFXRp13(4)

PETn13_GFXRn13(4)

PETp14_GFXRp14(4)

PETn14_GFXRn14(4)

PETp15_GFXRp15(4)

PETn15_GFXRn15(4)

R1008 X_0R

JTAG_TRST#

PRESENCE

B9

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

+3.3V#B8

JTAG1

3.3Vaux

WAKE#

RSVD#B12

GND#B13

PETp0

PETn0

GND#B16

PRSNT2#B17

GND#B18

PETp1

PETn1

GND#B21

GND#B22

PETp2

PETn2

GND#B25

GND#B26

PETp3

PETn3

GND#B29

RSVD#B30

PRSNT2#B31

GND#B32

PETp4

PETn4

GND#B35

GND#B36

PETp5

PETn5

GND#B39

GND#B40

PETp6

PETn6

GND#B43

GND#B44

PETp7

PETn7

GND#B47

PRSNT2#B48

GND#B49

PETp8

PETn8

GND#B52

GND#B53

PETp9

PETn9

GND#B56

GND#B57

PETp10

PETn10

GND#B60

GND#B61

PETp11

PETn11

GND#B64

GND#B65

PETp12

PETn12

GND#B68

GND#B69

PETp13

PETn13

GND#B72

GND#B73

PETp14

PETn14

GND#B76

GND#B77

PETp15

PETn15

GND#B80

PRSNT2#B81

RSVD#B82

x16 PCIe

614NOPN084

Mechanical Key

PRSNT1#A1

+12V#A2

+12V#A3

GND#A4

JTAG2

JTAG3

JTAG4

JTAG5

+3.3V#A9

+3.3V#A10

PERST#

GND#A12

REFCLK+

REFCLKGND#A15

PERp0

PERn0

GND#A18

RSVD#A19

GND#A20

PERp1

PERn1

GND#A23

GND#A24

PERp2

PERn2

GND#A27

GND#A28

PERp3

PERn3

GND#A31

RSVD#A32

RSVD#A33

GND#A34

PERp4

PERn4

GND#A37

GND#A38

PERp5

PERn5

GND#A41

GND#A42

PERp6

PERn6

GND#A45

GND#A46

PERp7

PERn7

GND#A49

RSVD#A50

GND#A51

PERp8

PERn8

GND#A54

GND#A55

PERp9

PERn9

GND#A58

GND#A59

PERp10

PERn10

GND#A62

GND#A63

PERp11

PERn11

GND#A66

GND#A67

PERp12

PERn12

GND#A70

GND#A71

PERp13

PERn13

GND#A74

GND#A75

PERp14

PERn14

GND#A78

GND#A79

PERp15

PERn15

GND#A82

+12V_BUS

+3.3V_BUS

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

PRESENCE

R1835 0R

C300

100nF

C302

100nF

C304

100nF

C306

100nF

C308

100nF

C310

100nF

C312

100nF

C314

100nF

C316

100nF

C318

100nF

C320

100nF

C322

100nF

C324

100nF

C326

100nF

C328

100nF

C330

100nF

RP1D X_0R

RP1C X_0R

RP1B X_0R

RP1A X_0R

C301

100nF

C303

100nF

C305

100nF

C307

100nF

C309

100nF

C311

100nF

C313

100nF

C315

100nF

C317

100nF

C319

100nF

C321

100nF

C323

100nF

C325

100nF

C327

100nF

C329

100nF

C331

100nF

54

63

72

81

R701 1.0K

R702 1.0K

R703 1.0K

R704 1.0K

R705 1.0K

R706 1.0K

R707 1.0K

R708 1.0K

R709 1.0K

R710 1.0K

R711 1.0K

R712 1.0K

R713 1.0K

R714 1.0K

R715 1.0K

R716 1.0K

R717 1.0K

R718 1.0K

R719 1.0K

R720 1.0K

R721 1.0K

R722 1.0K

R723 1.0K

R724 1.0K

R725 1.0K

R726 1.0K

R727 1.0K

R728 1.0K

R729 1.0K

R730 1.0K

R731 1.0K

R732 1.0K

VSYNC_DAC1 (5,14,16)

CRT1DDCDATA (5,16)

SCL (5,15,18)

CRT1DDCCLK (5,16)

PERST#

PCIE_REFCLKP (4)

GFXTp0_PERp0 (4)

GFXTn0_PERn0 (4)

GFXTp1_PERp1 (4)

GFXTn1_PERn1 (4)

GFXTp2_PERp2 (4)

GFXTn2_PERn2 (4)

GFXTp3_PERp3 (4)

GFXTn3_PERn3 (4)

GFXTp4_PERp4 (4)

GFXTn4_PERn4 (4)

GFXTp5_PERp5 (4)

GFXTn5_PERn5 (4)

GFXTp6_PERp6 (4)

GFXTn6_PERn6 (4)

GFXTp7_PERp7 (4)

GFXTn7_PERn7 (4)

GFXTp8_PERp8 (4)

GFXTn8_PERn8 (4)

GFXTp9_PERp9 (4)

GFXTn9_PERn9 (4)

GFXTp10_PERp10 (4)

GFXTn10_PERn10 (4)

GFXTp11_PERp11 (4)

GFXTn11_PERn11 (4)

GFXTp12_PERp12 (4)

GFXTn12_PERn12 (4)

GFXTp13_PERp13 (4)

GFXTn13_PERn13 (4)

GFXTp14_PERp14 (4)

GFXTn14_PERn14 (4)

GFXTp15_PERp15 (4)

GFXTn15_PERn15 (4)

+5V

74ACT08MTC

5

4

R3 100R

6

U2B

1

2

R4

180R

402

+5V

14

+-U2A

74ACT08MTC

7

PERST#_buf (4,18)

3

C1

100nF

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

PERp0

PERn0

PERp1

PERn1

PERp2

PERn2

PERp3

PERn3

PERp4

PERn4

PERp5

PERn5

PERp6

PERn6

PERp7

PERn7

PERp8

PERn8

PERp9

PERn9

PERp10

PERn10

PERp11

PERn11

PERp12

PERn12

PERp13

PERn13

PERp14

PERn14

PERp15

PERn15

A A

Size Docum e n t N u mb er Re v

C

5

4

www.vinafix.vn

3

2

Date: Sheet

Spare gate

MS-V005 ATI RV410

PCI-Express_Connector

1

3

10

of

18Tuesday, De ce mber 28, 2004

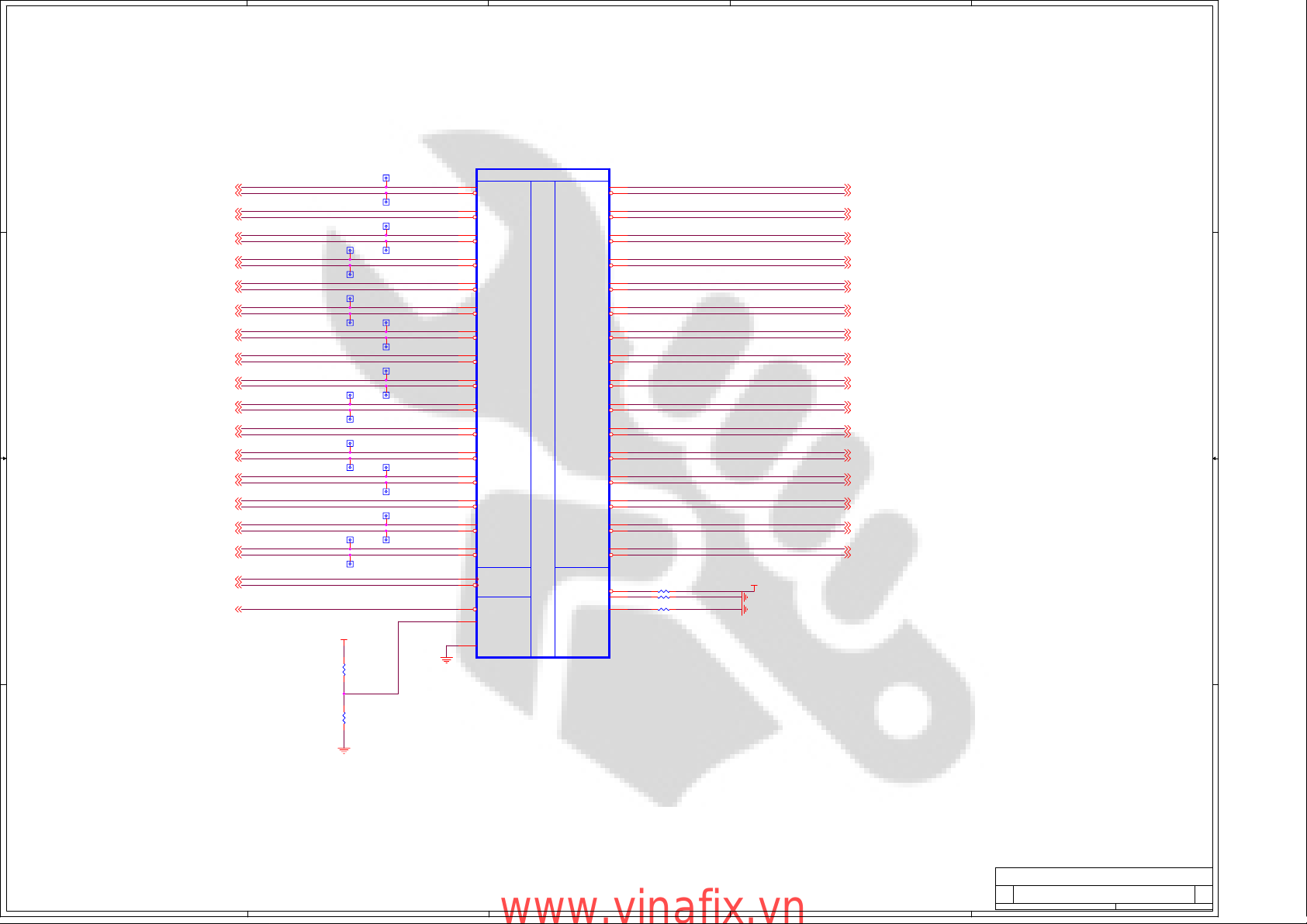

Page 4

5

4

3

2

1

NOTE: some of the PCIE testpoints will

be available trought via on traces.

D D

AH31

AH30

AG30

AG32

AF32

AF31

AE31

AE30

AD30

AD32

AC32

AC31

AB31

AB30

AA30

AA32

AK28

AG24

AA24

AF24

AJ31

W31

W30

AL28

Y32

Y31

V30

V32

U32

U31

T31

T30

R30

R32

P32

P31

N31

U1A

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

PCIE_REFCLKP

PCIE_REFCLKN

PERSTB

PCIE_TEST

MCL_0

RV410

TP34

TP35

TP38

TP39

TP46

TP47

TP50

TP51

TP58

TP59

TP28

TP29

TP32

TP33

TP40

TP41

TP44

TP45

TP52

TP53

TP56

TP57

PETp0_GFXRp0(3)

PETn0_GFXRn0(3)

PETp1_GFXRp1(3)

PETn1_GFXRn1(3)

PETp2_GFXRp2(3)

PETn2_GFXRn2(3)

PETp3_GFXRp3(3)

PETn3_GFXRn3(3)

PETp4_GFXRp4(3)

PETn4_GFXRn4(3)

PETp5_GFXRp5(3)

PETn5_GFXRn5(3)

PETp6_GFXRp6(3)

C C

B B

PETn6_GFXRn6(3)

PETp7_GFXRp7(3)

PETn7_GFXRn7(3)

PETp8_GFXRp8(3)

PETp9_GFXRp9(3)

PETn9_GFXRn9(3)

PETp10_GFXRp10(3)

PETn10_GFXRn10(3)

PETp11_GFXRp11(3)

PETn11_GFXRn11(3)

PETp12_GFXRp12(3)

PETn12_GFXRn12(3)

PETp13_GFXRp13(3)

PETn13_GFXRn13(3)

PETp14_GFXRp14(3)

PETn14_GFXRn14(3)

PETp15_GFXRp15(3)

PETn15_GFXRn15(3)

PCIE_REFCLKP(3)

PCIE_REFCLKN(3)

PERST#_buf(3,18)

+3.3V_BUS

R1007

X_4.7K

Clock

PART 1 OF 7

P

C

I

E

X

P

R

E

S

S

I

N

T

E

R

F

A

C

E

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Calibration

PCIE_CALRN

PCIE_CALRP

PCIE_CALI

AK27

AJ27

AJ25

AH25

AH28

AG28

AG27

AF27

AF25

AE25

AE28

AD28

AD27

AC27

AC25

AB25

AB28

AA28

AA27

Y27

Y25

W25

W28

V28

V27

U27

U25

T25

T28

R28

R27

P27

AE24

AD24

AB24

R1010 100R

R1009 150R

R1011 10K

+PCIE_VDDR

GFXTp0_PERp0 (3)

GFXTn0_PERn0 (3)

GFXTp1_PERp1 (3)

GFXTn1_PERn1 (3)

GFXTp2_PERp2 (3)

GFXTn2_PERn2 (3)

GFXTp3_PERp3 (3)

GFXTn3_PERn3 (3)

GFXTp4_PERp4 (3)

GFXTn4_PERn4 (3)

GFXTp5_PERp5 (3)

GFXTn5_PERn5 (3)

GFXTp6_PERp6 (3)

GFXTn6_PERn6 (3)

GFXTp7_PERp7 (3)

GFXTn7_PERn7 (3)

GFXTp8_PERp8 (3)

GFXTn8_PERn8 (3)PETn8_GFXRn8(3)

GFXTp9_PERp9 (3)

GFXTn9_PERn9 (3)

GFXTp10_PERp10 (3)

GFXTn10_PERn10 (3)

GFXTp11_PERp11 (3)

GFXTn11_PERn11 (3)

GFXTp12_PERp12 (3)

GFXTn12_PERn12 (3)

GFXTp13_PERp13 (3)

GFXTn13_PERn13 (3)

GFXTp14_PERp14 (3)

GFXTn14_PERn14 (3)

GFXTp15_PERp15 (3)

GFXTn15_PERn15 (3)

R1006

4.7K

A A

Size Docum e n t N u mb er Re v

C

5

4

www.vinafix.vn

3

2

Date: Sheet

MS-V005 ATI RV410

PCIE_Interface

1

4

10

18Tuesday, De ce mber 28, 2004

of

Page 5

5

DVALID(14)

2 1

DVOMODE_0(14)

DVOMODE_1(14)

CLK_DVOCLK0(18)

DC_Strap2(14)

DC_Strap3(14,18)

DC_Strap4(14)

PAL/NTSC(14)

DEMUX_SEL(14)

GPIO[6..0](14)

GPIO[13..8](14)

Y3

X_27_MHZ

PSYNC(14)

DVO[11..0]

Install close to ASIC to provide

return path for EMI

R586 499R

D+(15)

+VDD_1.8V

B33 X_Bead

R30

X_1.0M

R65

150R

C52582pF

+PVDD

GND_PVSS

+MPVDD

C46

22uF_16V

GND_MPVSS

XTALIN

C27

22uF_16V

C450 1uF

R587 499R

C26

100nF

C44

C45

1.0uF

100nF

TP12

TP13

DVO0

DVO1

DVO2

DVO3

DVO4

DVO5

DVO6

DVO7

DVO8

DVO9

DVO10

DVO11

R64 X_0R

D D

C C

B B

C71 X_20pF

C79 X_20pF

Overlap pads

+3.3V_BUS

XTAL

B3

X_220R

Oscillator Circuit

Y1

C1522

X_1.0uF

C1523

X_100nF

2

R1625

X_1K

A A

4

VCC

GND

X_27.000MHz

5

3

OUT

1

E/D

C2

X_22pF

+3.3V_BUS

C41

1.0uF

C43

1.0uF

R99 22R

PVDD

PVSS

C42

1.0uF

X_221

4

R61

4

DVOMODE_0

DVOMODE_1

MPVDD

MPVSS

DVO_VSYNC(18)

DVO_HSYNC(18)

DVO_DE(18)DVO[11..0](18)

TP14

R43 1K

ROMCS#

R66

150R

GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

XTALIN

XTALOUT

3

TESTEN

AF10

AG10

AE10

AE13

AF13

AG12

AH12

AJ14

AH14

AL26

AM26

AG14

AG22

AK17

AJ19

AF18

AH17

AG17

AG19

AH19

AH9

AJ8

AH8

AG9

AH7

AG8

AF7

AH6

AF8

AE9

AG7

AF9

AK4

AL4

AF2

AF1

AF3

AG1

AG2

AG3

AH2

AH3

AJ2

AJ1

AK2

AK1

AK3

AL2

AL3

AM3

AE6

AF4

AF5

AG4

AJ3

AH4

AJ4

AG5

AH5

AF6

AE7

AG6

AD4

AD2

AD1

AD3

AC1

AC2

AC3

AB2

AC6

AC5

AC4

AB3

AB4

AB5

AD5

AB8

AA8

AB7

AB6

AC8

A6

A5

AC7

U1B

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

VID_7

VPCLK0

DVALID

PSYNC

VHAD_0

VHAD_1

VPHCTL

VIPCLK

SDA

SCL

DVOVMODE_0

DVOVMODE_1

DVPCNTL_0

DVPCNTL_1

DVPCNTL_2

DVPCLK

DVPDATA_0

DVPDATA_1

DVPDATA_2

DVPDATA_3

DVPDATA_4

DVPDATA_5

DVPDATA_6

DVPDATA_7

DVPDATA_8

DVPDATA_9

DVPDATA_10

DVPDATA_11

DVPDATA_12

DVPDATA_13

DVPDATA_14

DVPDATA_15

DVPDATA_16

DVPDATA_17

DVPDATA_18

DVPDATA_19

DVPDATA_20

DVPDATA_21

DVPDATA_22

DVPDATA_23

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

NC_22

VREFG

DPLUS

DMINUS

PVDD

PVSS

MPVDD

MPVSS

XTALIN

XTALOUT

PLLTEST

TESTEN

ROMCSb

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

RV410

VIP

Capture

VIP

Host

MMI2C

General

Purpose

I/O

Thermal

Diode

PLL &

XTAL

Test

ROM

PART 2 OF 7

V

I

D

E

O

&

M

U

L

T

I

M

E

D

I

A

Zoom Video Port/ VIP Host/External TMDS

Integrated

TMDS

TXVDDR_1

TXVDDR_2

TXVDDR_3

TXVDDR_4

TXVSSR_1

TXVSSR_2

TXVSSR_3

TXVSSR_4

TXVSSR_5

DAC / CRT

GENERICA

GENERICB

AVDD_1

AVDD_2

AVSSN_1

AVSSN_2

DAC2 (TV/CRT2)

H2SYNC

V2SYNC

A2VDD_1

A2VDD_2

A2VSSN_1

A2VSSN_2

A2VDDQ

A2VSSQ

Monitor

Interfa ce

DDC1DATA

DDC1CLK

DDC2DATA

DDC2CLK

DDC3DATA

DDC3CLK

GENERICC

VSS_175

VSS_174

VSS_173

TXCM

TXCP

TX0M

TX0P

TX1M

TX1P

TX2M

TX2P

TX3M

TX3P

TX4M

TX4P

TX5M

TX5P

TPVDD

TPVSS

HSYNC

VSYNC

RSET

AVSSQ

VDD1DI

VSS1DI

COMP

R2SET

VDD2DI

VSS2DI

HPD1

MCL_1

AL9

AM9

AK10

AL10

AL11

AM11

AL12

AM12

AK9

AJ9

AK11

AJ11

AK12

AJ12

AM8

AL8

AJ6

AK6

AL6

AM6

AJ7

AK7

AL7

AM7

AK8

AK24

R

AM24

G

AL24

B

AJ23

AJ22

AK22

R33 1K

AF23

R52 499R

AL22

AL25

AM25

AVDD

AK23

AK25

GND_AVSSQ

AJ24

AM23

AL23

AK15

R2

AM15

G2

AL15

B2

AF15

AG15

AJ15

Y

AJ13

C

AH15

R55 715R

AK14

AM16

AL16

AM17

AL17

AL14

AK13

AJ16

AJ17

AF11

AH22

AH23

AH13

AG13

AE12

AF12

AE23

AE18

AF22

AF17

AF21

GPIO8

GPIO9

GPIO10

ROMCS#

C35

1.0uF

R34 1K

7 2

5 4

6 3

8 1

SERIAL EEPROM 512K/1M

www.vinafix.vn

3

GND_RSET

GND_R2SET

+VDD2DI

C36

100nF

RP193B33R

RP193D33R

RP193C33R

RP193A33R

C7

1.0uF

B8 Bead

C34

22uF_16V

+3.3V_BUS

R91

10K

C40

100nF

ROM_SO

SI/A16

SCK/WEb

CSb

HOLD1

2

R797 330R

R796 330R

R795 330R

R794 330R

INSTALL TERMINATION RESISTORS

CLOSE TO ASIC

C13

C17

C15

1.0uF

+AVDD

+VDD_1.8V

+3.3V_BUS

100nF

82pF

TXVDDR

C9

C8

22uF_16V

82pF

+VDD_1.8V

B5 Bead

C23

22uF_16V

GND_AVSSN

+A2VDD

C31

C33

1.0uF

100nF

GND_A2VSSN

C37

1.0uF

U11

5

Q

D

6

C

1

S

7

HOLD

3

W

8

VCC

VSS

M25P05-VMN6T

C80

100nF

ALTERNATIVE PART :M25P05( 512Kbit)

2

C32

+TPVDD

22uF_16V

2

4

C16

22uF_16V

GND_TPVSS

C21

100nF

C29

1.0uF

+A2VDDQ

C38

100nF

GND_A2VSSQ

C39

22uF_16V

R44

Rk

X_0R

Ba2

B4

Bead

GND_TXVSSR

+VDDDI

C30

100nF

4170010400

B9 Bead

1

TXCM (17)

TXCP (17)

TX0M (17)

TX0P (17 )

TX1M (17)

TX1P (17 )

TX2M (17)

TX2P (17 )

+VDD_1.8V

+3.3V_BUS

R50

4.7K

R_DAC1 (16)

G_DAC1 (16)

B_DAC1 (16)

HSYNC _DAC1 (3,14,16)

VSYNC_DAC1 (3,14,16)

STEREOSYNC (18)

+VDD_1.8V

B7 Bead

C28

22uF_16V

R_DAC2 (16)

G_DAC2 (16)

B_DAC2 (16)

HSYNC_DAC2 (16)

VSYNC_DAC2 (16)

Y_DAC2 (18)

C_DAC2 (18)

COMP_DAC2 (18)

+VDD_1.8V

+3.3V_BUS

+3.3V_BUS

R54

R53

4.7K

4.7K

HPD1 (17)

CRT1DDCDATA (3,16)

CRT1DDCCLK (3,16)

CRT2DDCDATA (16)

CRT2DDCCLK (16)

SDA (15,18)

SCL (3,15,18)

Size Docum e n t N u mb er Re v

C

Date: Sheet

MS-V005 ATI RV410

RV410 Main

1

10

of

18Tuesday, De ce mber 28, 2004

5

Page 6

5

D D

C C

+MVDDQ

C616

1uF

+3.3V_BUS

+VDD_1.8V

+VDD_1.8V

+3.3V_BUS

+MVDDQ

C68

X_47uF_6.3V

C70

10uf

C617

1uF

C67

22uF_16V

C600

C601

1uF

1uF

C64

10uf

C73

C65

10uf

10uf

C618

1uF

C66

1.0uF

R70X_0R

R690R

R68X_0R

R670R

B29 220R

C602

1uF

C608

1uF

C612

1uF

C619

1uF

C624

1uF

B30 220R

C668

1uF

B12

220R

B14

220R

C613

1uF

C620

1uF

C609

1uF

C625

1uF

C603

1uF

C669

1uF

C614

1uF

C621

1uF

C610

1uF

C626

1uF

1.0uF

C74

C75

C604

1uF

1.0uF

C667

1uF

C615

1uF

C622

1uF

C611

1uF

C627

1uF

C709

100nF

C605

1uF

+VDDR4

4170010400

+VDDR5

C710

100nF

4170010400

C670

1uF

1uF

C623

1uF

C707

4

U1E

C1

VDDR1_1

J1

VDDR1_2

M1

VDDR1_3

R1

VDDR1_4

V1

VDDR1_5

AA1

VDDR1_6

A3

VDDR1_7

P9

VDDR1_8

J10

VDDR1_9

N9

VDDR1_10

P10

VDDR1_11

A9

VDDR1_12

Y10

VDDR1_13

P8

VDDR1_14

R9

VDDR1_15

Y9

VDDR1_16

J11

AB10

AC19

AD18

AC20

AD19

AD20

VDDR1_17

A21

VDDR1_18

M10

VDDR1_20

N10

VDDR1_21

Y8

VDDR1_22

J18

VDDR1_23

J19

VDDR1_24

K21

VDDR1_25

A12

VDDR1_26

H13

VDDR1_27

A15

VDDR1_28

J20

VDDR1_29

J13

VDDR1_30

K11

VDDR1_31

K19

VDDR1_32

A18

VDDR1_33

L23

VDDR1_34

K20

VDDR1_35

K24

VDDR1_36

L24

VDDR1_37

H19

VDDR1_38

A24

VDDR1_39

K13

VDDR1_40

J32

VDDR1_41

A30

VDDR1_42

C32

VDDR1_43

F32

VDDR1_45

L32

VDDR1_46

AB9

VDDR3_1

VDDR3_2

AA9

VDDR3_3

VDDR3_4

VDDR3_5

VDDR3_6

VDDR3_7

VDDR3_8

AJ5

VDDR4_1

AM5

VDDR4_2

AL5

VDDR4_3

AK5

VDDR4_4

AE2

VDDR5_1

AE3

VDDR5_2

AE4

VDDR5_3

AE5

VDDR5_4

A27

VDDRH0

F1

VDDRH1

A28

VSSRH0

E1

VSSRH1

RV410

C607

C606

1uF

1uF

C69

1uF

C708

1uF

C676

1uF

Clock

I/O

PART 5 OF 7

Memory I/O

I/0

Memory

3

+VDD_1.8V

+PCIE_V DDR _12

C981

1uF

R714.7K

+A2VDD

C970

1uF

C982

1uF

C632

1uF

C637

1uF

C61

10uf

1uF

VDDC_1

VDDC_2

VDDC_3

VDDC_4

VDDC_5

VDDC_6

VDDC_7

VDDC_8

VDDC_9

VDDC_10

VDDC_11

VDDC_12

VDDC_13

VDDC_14

VDDC_15

VDDC_16

VDDC_17

VDDC_18

VDDC_19

VDDC_20

VDDC_21

VDDC_22

VDDC_23

VDD15_1

VDD15_2

VDD15_3

VDDCI_1

VDDCI_2

VDDCI_3

VDDCI_4

VDDCI_5

VDDCI_6

VDDCI_7

VDDCI_8

VDDL0

VDDL0_1

VDDL0_2

VDDL0_3

VDDL1_1

VDDL1_2

VDDL1_3

VDDL2_1

VDDL2_2

VDDL2_3

V23

N23

P23

U23

N29

N28

N27

N26

N25

AL31

AM31

AM30

AL32

AL30

AM28

AL29

AM29

AM27

AC11

AC12

P14

U15

W14

W15

R17

R15

V15

V16

T16

U16

T17

U17

V14

R18

T18

V18

P18

P19

R19

W19

AD11

AC13

AC16

AC18

W10

T14

W17

P16

AC15

T23

K14

U19

AE19

AF20

AE20

AF19

AC21

AC22

AD22

AE21

AD21

AE22

PCIE_PVDD_12_1

PCIE_PVDD_12_2

PCIE_PVDD_12_3

PCIE_PVDD_12_4

PCIE_PVDD_18_1

PCIE_PVDD_18_2

PCIE_PVDD_18_3

PCIE_PVDD_18_4

PCIE_PVDD_18_5

PCIE_VDDR_12_1

PCIE_VDDR_12_2

PCIE_VDDR_12_3

PCIE_VDDR_12_4

PCIE_VDDR_12_5

PCIE_VDDR_12_6

PCIE_VDDR_12_7

PCI-Express

PCIE_VDDR_12_8

PCIE_VDDR_12_9

P

O

W

E

R

I/O Internal Core

2

+VDDC

ALT: 0R

L7 X_1.8uH

B27 200R

C978

C633

1uF

C638

1uF

C62

10uf

C979

1uF

1uF

C971

C976

1uF

1uF

C972

C973

1uF

1uF

C634

1uF

C639

1uF

C59

10uF_10V

C49

C50

1uF

1uF

C646

C648

1uF

1uF

C977

1uF

C974

1uF

C983

1uF

C48

C1675

10uF_6.3V

C1668

10uF_6.3V

C635

1uF

C640

1uF

C968

1uF

+VDDC_CT

C53

22uF_16V

C60

10uf

C1703

10uF_6.3V

C1704

10uF_6.3V

C1702

10uF_6.3V

C636

1uF

C641

1uF

C63

10uF_10V

+VDDC+3.3V_BUS

+PCIE_PVDD_18

+VDDC

C642

1uF

L6 X_1.8uH

B23 60R

C644

1uF

+PCIE_VDDR

ALT: 0R

+PCIE_VDDR

1

+VDDC

B B

A A

5

GND_VSSRH0

GND_VSSRH1

U1G

Forward

Compatibility

Y23

BBN_4

K15

BBN_3

R10

BBN_2

AC17

BBN_1

AC14

BBP_4

M23

BBP_3

V10

BBP_2

K18

BBP_1

L10

VDD25B_1

K22

VDD25B_2

AA10

VDD25A

RV410

4

www.vinafix.vn

PART 7 OF 7

No Connect

AD12

NC_0

AE11

NC_1

AD23

GENERICD

AJ21

NC_2

AK21

NC_3

AH21

NC_4

AG21

NC_5

AG20

NC_6

AH20

NC_7

AK20

NC_8

AJ20

NC_9

AG18

NC_10

AH18

NC_11

AK19

NC_12

AL19

NC_13

AL20

NC_14

AM20

NC_15

AL21

NC_16

AM21

NC_17

AK18

NC_18

AJ18

NC_19

AL18

NC_20

AM18

NC_21

3

TP11

Size Docum e n t N u mb er Re v

C

2

Date: Sheet

MS-V005 ATI RV410

RV410_Power_and_NC

1

6

10

of

18Tuesday, De ce mber 28, 2004

Page 7

5

GND_TPVSS

GND_MPVSS GND_A2VSSN

GND_PVSS

GND_AVSSN

NOTE: THIS IS A DRAWING. THESE

GROUNDS MUST BE MANUALLY

CONNECTED TO THE GROUND PLANE

D D

C C

B B

A A

GND_TXVSSR

5

GND_A2VSSQ

GND_AVSSQ

GND_RSET

GND_R2SET

GND_VSSRH1

GND_VSSRH0

GND_RT

GND_VIN

GND_TVVSSN

4

U1F

AH27

PCIE_VSS_1

AC23

PCIE_VSS_2

AL27

PCIE_VSS_3

R23

PCIE_VSS_4

P25

PCIE_VSS_5

R25

PCIE_VSS_6

T26

PCIE_VSS_7

U26

PCIE_VSS_8

W26

PCIE_VSS_9

Y26

PCIE_VSS_10

AB26

PCIE_VSS_11

AC26

PCIE_VSS_12

AD25

PCIE_VSS_13

AE26

PCIE_VSS_14

AF26

PCIE_VSS_15

AD26

PCIE_VSS_16

AG25

PCIE_VSS_17

AH26

PCIE_VSS_18

AC28

PCIE_VSS_19

Y28

PCIE_VSS_20

U28

PCIE_VSS_21

P28

PCIE_VSS_22

AH29

PCIE_VSS_23

AF28

PCIE_VSS_24

V29

PCIE_VSS_25

AC29

PCIE_VSS_26

W27

PCIE_VSS_27

AB27

PCIE_VSS_28

V26

PCIE_VSS_29

AJ26

PCIE_VSS_30

AJ32

PCIE_VSS_31

AK29

PCIE_VSS_32

P26

PCIE_VSS_33

P29

PCIE_VSS_34

R29

PCIE_VSS_35

T29

PCIE_VSS_36

U29

PCIE_VSS_37

W29

PCIE_VSS_38

Y29

PCIE_VSS_39

AA29

PCIE_VSS_40

AB29

PCIE_VSS_41

AD29

PCIE_VSS_42

AE29

PCIE_VSS_43

AF29

PCIE_VSS_44

AG29

PCIE_VSS_45

AJ29

PCIE_VSS_46

AK26

PCIE_VSS_47

AK30

PCIE_VSS_48

AG26

PCIE_VSS_49

N30

PCIE_VSS_50

R31

PCIE_VSS_51

AF30

PCIE_VSS_52

AC30

PCIE_VSS_53

V31

PCIE_VSS_54

P30

PCIE_VSS_55

AA31

PCIE_VSS_56

U30

PCIE_VSS_57

AD31

PCIE_VSS_58

AK32

PCIE_VSS_59

AJ28

PCIE_VSS_60

Y30

PCIE_VSS_61

AJ30

PCIE_VSS_62

AK31

PCIE_VSS_63

AA23

PCIE_VSS_64

AG31

PCIE_VSS_65

N24

PCIE_VSS_66

W23

PCIE_VSS_67

AB23

PCIE_VSS_69

P24

PCIE_VSS_70

R24

PCIE_VSS_71

T24

PCIE_VSS_72

U24

PCIE_VSS_73

V24

PCIE_VSS_74

W24

PCIE_VSS_75

Y24

PCIE_VSS_76

AC24

PCIE_VSS_77

AH24

PCIE_VSS_78

V25

PCIE_VSS_79

AA25

PCIE_VSS_80

R26

PCIE_VSS_81

AA26

PCIE_VSS_82

T27

PCIE_VSS_83

AE27

PCIE_VSS_84

B1

VSS_1

H1

VSS_2

L1

VSS_3

P1

VSS_4

U1

VSS_5

Y1

VSS_6

AD7

VSS_7

AE8

VSS_8

AL1

VSS_9

A2

VSS_10

AM2

VSS_11

AD10

VSS_12

E8

VSS_13

H5

VSS_14

K10

VSS_15

M8

VSS_16

T10

VSS_17

E12

VSS_18

AC9

VSS_19

AF14

VSS_20

AD8

VSS_21

C5

VSS_22

F10

VSS_23

J3

VSS_24

L6

VSS_25

M6

VSS_26

P6

VSS_27

AA4

VSS_28

AG11

VSS_29

V3

VSS_30

AG16

VSS_31

R3

VSS_32

C6

VSS_33

C9

VSS_34

F6

VSS_35

H7

VSS_36

J6

VSS_37

RV410

4

Part 6 of 7

PCI-Express GND

CORE GND

www.vinafix.vn

3

AD16

VSS_45

AA6

VSS_44

P7

VSS_43

P5

VSS_42

M3

VSS_41

M9

VSS_40

L7

VSS_39

M7

VSS_38

AD17

VSS_47

AH11

VSS_48

A8

VSS_49

U7

VSS_50

C10

VSS_51

E9

VSS_52

F3

VSS_53

J9

VSS_54

N7

VSS_55

N3

VSS_56

Y5

VSS_57

AM13

VSS_58

AC10

VSS_59

Y6

VSS_60

U6

VSS_61

E5

VSS_62

AL13

VSS_63

A11

VSS_64

U8

VSS_65

U9

VSS_66

U10

VSS_67

R6

VSS_68

AD6

VSS_69

V6

VSS_70

AD14

VSS_71

AD13

VSS_72

D11

VSS_73

J12

VSS_74

K12

VSS_75

A13

VSS_77

F13

VSS_78

E13

VSS_79

F15

VSS_80

K16

VSS_81

J21

VSS_82

H16

VSS_83

T15

VSS_84

V17

VSS_85

C15

VSS_86

C4

VSS_87

U14

VSS_88

P15

VSS_89

A16

VSS_90

E16

VSS_91

G13

VSS_92

G16

VSS_93

P17

VSS_94

R16

VSS_95

R14

VSS_97

W16

VSS_98

C18

VSS_99

F16

VSS_100

W18

VSS_101

U18

VSS_102

AE16

VSS_103

AE17

VSS_104

A19

VSS_105

H32

VSS_106

F19

VSS_107

G19

VSS_108

N8

VSS_109

Y7

VSS_110

T19

VSS_112

V19

VSS_113

G21

VSS_114

C21

VSS_115

F21

VSS_116

AE14

VSS_117

AK16

VSS_118

U5

VSS_119

F22

VSS_120

F18

VSS_121

K30

VSS_122

C24

VSS_124

F24

VSS_125

M24

VSS_126

A25

VSS_127

D30

VSS_128

E25

VSS_129

G25

VSS_130

G20

VSS_131

G22

VSS_132

F27

VSS_133

E28

VSS_134

H21

VSS_135

C27

VSS_136

E32

VSS_137

H28

VSS_138

J30

VSS_139

K17

VSS_140

K27

VSS_141

M32

VSS_142

A22

VSS_143

C20

VSS_144

E19

VSS_145

H20

VSS_146

J24

VSS_147

M28

VSS_148

J28

VSS_149

J16

VSS_150

F30

VSS_151

K23

VSS_152

L29

VSS_153

A31

VSS_154

B32

VSS_155

E30

VSS_156

AE15

VSS_157

AG23

VSS_158

AD9

VSS_159

AF16

VSS_160

AH10

VSS_161

AJ10

VSS_163

AD15

VSS_164

AH16

VSS_165

3

2

Size Docum e n t N u mb er Re v

C

2

Date: Sheet

1

MS-V005 ATI RV410

RV410_Core_GND

1

7

10

18Tuesday, De ce mber 28, 2004

of

Page 8

8

VDDC

7

6

5

4

3

2

1

D D

C C

B B

1.2V/1.2A

+PCIE_VDDR

C1323

470U

+3.3V_BUS

B13

Bead

R1581

X_5.1K

R1582

X_2.4K

+MVDDC

C1329

4.7U

+

1K_1%

1

Q7

X_CMPT3904

R1325

X_0R

R1222

R1224

2K_1%

+3.3V_BUS

R1326

X_0R

DS

+12V_BUS

R1583

X_20K

X_CMPT3904

2 3

B11

X_Bead

Q157

P3055LD

G

C411

X_1500P

1

Q8

+12V_BUS

C1330

1U

R1219

4.7

C1230

1U

10

C410

X_0.01uF

R1207

X_20K

R1206

100K

5

6

2

LDO_DR

LDO_FB

FS_DIS

300Khz

2 3

9

PVCC5

GND7FB

4

8

VCC5

COMP

3

5600pF

R1220

4.7

U7

ISL6549CB

UGATE

VCC12

BOOT

PHASE

LGATE

PGND

C1337

C1339 15pF

C1331

1U/16V

14

C998 100nF

1

13

11

12

R1226

20K

BEAD_4A

R1449 2.2R

R449 2.2R

R1058 0R

L806

+12V_BUS

G

G

B81

X_1.2uH

DS

Q155

0903BLB

TO252

DS

Q156

0903BSB

TO263

C994

+

470UF

1 2

12

C940

+

470UF

L602 2U

R1062

X_4.7R

C946

X_1000P

C1532

C941

+

470UF

1.0uF

C1149

10uF

C1146

10uF

C1147

10uF

C1148

10uF

1.345V, 12AIsat=15A

+VDDC

R1061

1.74KST

1%

R1063

2.55KST

1%

+

C1966

1000UF_6.3V

+

C107

X_1000UF_6.3V

CP12

1 2

X_COPPER

+

C167

1000UF_6.3V

C1402

270pF

C1403

270pF

POWER SEQUENCING CIRCUIT:

A A

MS-V005 ATI RV410

Size Document Number Rev

B

8

7

6

5

4

3

Date: Sheet

Regulator of GPU

2

of

8

1

10

18Tuesday, December 28, 2004

www.vinafix.vn

Page 9

8

D D

7

6

5

4

3

2

1

U815

OCP

PHASE

PGND

+12V_BUS

D60

1N4148_SOD123

BOOT

4

10

1uF

6

DH

5

8

DL

7

OCSET

C101

DH

R1221 2.2R

PHASE

R1223 2.2R

DL

PGND

C99 100nF

C100 1000P

R1166 10K

MVDDC

+12V_BUS

C98

1uF

9

BOOSTH

BOOSTL

GND

14

C95

0.1uF

C97

0.1uF

R165

10R

1

VCC

2

NC

3

NC1

12

VREF

SS

13

SS

FB

11

VSENSE

N2101

C96

C C

B B

220nF

+12V_BUS

G

G

L804

BEAD_4A

DS

Q133

P0903BD

DS

Q134

P0903BD

C1233

1U

C943

470UF_16V

A C

+

1N5817

D130

C172

10uF

Isat=8A

L807 4.7uH

R167

4.7R

1 2

12

C421

1000P

C163

10uF

C1338

1nF

+MVDDC

R1225

2.4KST

1%

R1227

3.6K

1%

2.1V/2.5A

+

C1335

1000UF_6.3V

<P_esr>

<P_mat>

MVDDQ

+

C1336

1000UF_6.3V

<P_esr>

<P_mat>

RP208A 0R

RP208B 0R

RP208C 0R

RP208D 0R

RP207A 0R

RP207B 0R

RP207C 0R

RP207D 0R

C1401

270pF

CP14

1 2

X_COPPER

+MVDDC+MVDDQ

81

72

63

54

+MVDDC+MVDDQ

81

72

63

54

A A

MS-V005 ATI RV410

Size Document Number Rev

B

8

7

6

5

4

3

Date: Sheet

Regulator of Memory

2

of

9

1

10

18Tuesday, December 28, 2004

www.vinafix.vn

Page 10

8

D D

+3.3V_BUS

R1301

2.5V_REF2

C1304

X_100uF

C C

220

U801

L431M

2

C1342

10uF

3 1

R1203

390RST

R1205

1KST

7

+12V_BUS

U804A

LM358/SO8

3

2

U804B

LM358/SO8

5

6

84

+

-

84

+

-

1.798V

C1301

0.1U

Q206

P3055LD

1

G

Q207

2N7002

G

7

6

B16 Bead

DS

C1229

100uF_16V

B17 Bead

DS

C1221

+

10U

C1216

1U

C1322

1U

+3.3V_BUS

+PCIE_PVDD_18

1.8V/0.5A

+3.3V_BUS

+MPVDD

1.8V/0.02A

5

4

2.5V_REF

C1204

X_100uF

+3.3V_BUS

R1201

220

U805

L431M

3

+12V_BUS

2.5V_REF

U802A

R1111

LM324

1KST

1.5V

3

1.798V

U802B

LM324

2

5

6

R1112

1.5KST

C1242

10uF

R1202

390RST

R1204

1KST

2

3 1

2

B10 Bead

C1300

0.1U

Q201

411

2N7002

+

1

-

+

-

G

Q202

P3055LD

411

7

G

DS

C1310

100uF

B1 Bead

DS

B22 Bead

B24 Bead

C1210

100uF

C1202

1U

C1316

1U

+3.3V_BUS

+VDDC_CT

1.5V/0.05A

+3.3V_BUS

+PVDD

+TPVDD

+VDD_1.8V

1.8V/1.5A

1

B2 Bead

U802C

LM324

U802D

LM324

10

R1217

1K

12

13

411

+

9

-

411

+

14

-

2.5V_REF

B B

2.5V_REF

A A

8

R1216

1K

G

G

DS

Q203

P3055LD

C1327

100uF

B40 Bead

DS

Q204

P3055LD

C1227

100uF

C1326

1U

C1311

1U

+3.3V_BUS

+12V_BUS

+5V

5V/0.13A

+A2VDD

2.5V/1A

MS-V005 ATI RV410

Size Document Number Rev

Custom

8

7

6

5

www.vinafix.vn

4

3

Date: Sheet

2

Regulator for Others

10

1

10

of

18Tuesday, December 28, 2004

Page 11

5

4

3

2

1

RV410 MEMORY CHANNELS A and B

D D

MDA[63..0]

MDA[63..0](12,13)

C C

+MVDDQ

R137

40.2R

B B

R138

C149

100nF

100R

+MVDDQ

R148

40.2R

R149

C148

100nF

100R

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

U1C

M31

DQA_0

M30

DQA_1

L31

DQA_2

L30

DQA_3

H30

DQA_4

G31

DQA_5

G30

DQA_6

F31

DQA_7

M27

DQA_8

M29

DQA_9

L28

DQA_10

L27

DQA_11

J27

DQA_12

H29

DQA_13

G29

DQA_14

G27

DQA_15

M26

DQA_16

L26

DQA_17

M25

DQA_18

L25

DQA_19

J25

DQA_20

G28

DQA_21

H27

DQA_22

H26

DQA_23

F26

DQA_24

G26

DQA_25

H25

DQA_26

H24

DQA_27

H23

DQA_28

H22

DQA_29

J23

DQA_30

J22

DQA_31

E23

DQA_32

D22

DQA_33

D23

DQA_34

E22

DQA_35

E20

DQA_36

F20

DQA_37

D19

DQA_38

D18

DQA_39

B19

DQA_40

B18

DQA_41

C17

DQA_42

B17

DQA_43

C14

DQA_44

B14

DQA_45

C13

DQA_46

B13

DQA_47

D17

DQA_48

E18

DQA_49

E17

DQA_50

F17

DQA_51

E15

DQA_52

E14

DQA_53

F14

DQA_54

D13

DQA_55

H18

DQA_56

H17

DQA_57

G18

DQA_58

G17

DQA_59

G15

DQA_60

G14

DQA_61

H14

DQA_62

J14

DQA_63

C31

MVREFD_0

C30

MVREFS_0

RV410

Channel A

Part 3 of 7

MEMORY INTERFACE A

DDR1 DDR2 DDR3

bidir. differential strobe

Not used bidir. strobe

For DDR2

write strobe read strobe

MAA_0

MAA_1

MAA_2

MAA_3

MAA_4

MAA_5

MAA_6

MAA_7

MAA_8

MAA_9

MAA_10

MAA_11

MAA_12

MAA_13

MAA_14

MAA_15

DQMAb_0

DQMAb_1

DQMAb_2

DQMAb_3

DQMAb_4

DQMAb_5

DQMAb_6

DQMAb_7

QSA_0

QSA_1

QSA_2

QSA_3

QSA_4

QSA_5

QSA_6

QSA_7

QSA_0B

QSA_1B

QSA_2B

QSA_3B

QSA_4B

QSA_5B

QSA_6B

QSA_7B

ODTA

ODTA1

CLKA0

CLKA0b

CKEA0

RASA0b

CASA0b

WEA0b

CSA0b_0

CSA0b_1

CLKA1

CLKA1b

CKEA1

RASA1b

CASA1b

WEA1b

CSA1b_0

CSA1b_1

U1D

B12

DQB_0

C12

DQB_1

B11

DQB_2

C11

DQB_3

C8

DQB_4

B7

DQB_5

C7

DQB_6

B6

DQB_7

F12

DQB_8

D12

DQB_9

E11

DQB_10

F11

DQB_11

F9

DQB_12

D8

DQB_13

D7

DQB_14

F7

DQB_15

G12

DQB_16

G11

DQB_17

H12

DQB_18

H11

DQB_19

H9

DQB_20

E7

DQB_21

F8

DQB_22

G8

DQB_23

G6

DQB_24

G7

DQB_25

H8

DQB_26

J8

DQB_27

K8

DQB_28

L8

DQB_29

K9

DQB_30

L9

DQB_31

K5

DQB_32

L4

DQB_33

K4

DQB_34

L5

DQB_35

N5

DQB_36

N6

DQB_37

P4

DQB_38

R4

DQB_39

P2

DQB_40

R2

DQB_41

T3

DQB_42

T2

DQB_43

W3

DQB_44

W2

DQB_45

Y3

DQB_46

Y2

DQB_47

T4

DQB_48

R5

DQB_49

T5

DQB_50

T6

DQB_51

V5

DQB_52

W5

DQB_53

W6

DQB_54

Y4

DQB_55

R8

DQB_56

T8

DQB_57

R7

DQB_58

T7

DQB_59

V7

DQB_60

W7

DQB_61

W8

DQB_62

W9

DQB_63

B3

MVREFD_1

C3

MVREFS_1

AA3

DRAM_RST

AA5

TEST_MCLK

AA2

TEST_YCLK

AA7

MEMTEST

R166243R

RV410

+MVDDQ

+MVDDQ

R158

40.2R

R159

100R

R150

40.2R

R151

100R

MDB[63..0](12,13)

C151

100nF

C150

100nF

R163X_4.7K

R1574.7K

MDB0

MDB1

MDB2

MDB3

MDB4

MDB5

MDB6

MDB7

MDB8

MDB9

MDB10

MDB11

MDB12

MDB13

MDB14

MDB15

MDB16

MDB17

MDB18

MDB19

MDB20

MDB21

MDB22

MDB23

MDB24

MDB25

MDB26

MDB27

MDB28

MDB29

MDB30

MDB31

MDB32

MDB33

MDB34

MDB35

MDB36

MDB37

MDB38

MDB39

MDB40

MDB41

MDB42

MDB43

MDB44

MDB45

MDB46

MDB47

MDB48

MDB49

MDB50

MDB51

MDB52

MDB53

MDB54

MDB55

MDB56

MDB57

MDB58

MDB59

MDB60

MDB61

MDB62

MDB63

TEST_MCLK

TEST_YCLK

R1564.7K

MAA0

D26

MAA1

F28

MAA2

D28

MAA3

D25

MAA4

E24

MAA5

E26

MAA6

D27

MAA7

F25

MAA8

C26

MAA9

B26

MAA10

D29

MAA11

B27

MAA12

B25

MAA13

C25

E27

CSA#1

E29

DQMA#0

H31

DQMA#1

J29

DQMA#2

J26

DQMA#3

G23

DQMA#4

E21

DQMA#5

B15

DQMA#6

D14

DQMA#7

J17

QSA0

J31

QSA1

K29

QSA2

K25

QSA3

F23

QSA4

D20

QSA5

B16

QSA6

D16

QSA7

H15

QSA#0

K31

QSA#1

K28

QSA#2

K26

QSA#3

G24

QSA#4

D21

QSA#5

C16

QSA#6

D15

QSA#7

J15

F29

D24

D31

E31

B30

RASA#

B28

CASA#

C29

WEA#

B31

CSA#0

B29

C28

B20

C19

C22

B24

B22

B21

B23

C23

MAA[13..0] (12,13)

CSA#1 ( 13)

DQMA#[7..0] (12,13)

QSA[7..0] (12,13)

QSA#[7..0] (12,13)

CLKA0 (12,13)

CLKA#0 (12,13)

CKEA (12,13)

RASA# (12,13)

CASA# (12,13)

WEA# (12,13)

CSA#0 ( 12)

CLKA1 (12,13)

CLKA#1 (12,13)

Channel B

Part 4 of 7

MEMORY INTERFACE B

DDR1 DDR2 DDR3

read strobe

Not used bidir. strobe

bidir. differential strobe

write strobe

For DDR2

MAB_0

MAB_1

MAB_2

MAB_3

MAB_4

MAB_5

MAB_6

MAB_7

MAB_8

MAB_9

MAB_10

MAB_11

MAB_12

MAB_13

MAB_14

MAB_15

DQMBb_0

DQMBb_1

DQMBb_2

DQMBb_3

DQMBb_4

DQMBb_5

DQMBb_6

DQMBb_7

QSB_0

QSB_1

QSB_2

QSB_3

QSB_4

QSB_5

QSB_6

QSB_7

QSB_0B

QSB_1B

QSB_2B

QSB_3B

QSB_4B

QSB_5B

QSB_6B

QSB_7B

ODTB

ODTB1

CLKB0

CLKB0b

CKEB0

RASB0b

CASB0b

WEB0b

CSB0b_0

CSB0b_1

CLKB1

CLKB1b

CKEB1

RASB1b

CASB1b

WEB1b

CSB1b_0

CSB1b_1

MAB0

G4

MAB1

E6

MAB2

E4

MAB3

H4

MAB4

J5

MAB5

G5

MAB6

F4

MAB7

H6

MAB8

G3

MAB9

G2

MAB10

D4

MAB11

F2

MAB12

H2

MAB13

H3

F5

CSB#1

D5

DQMB#0

B8

DQMB#1

D9

DQMB#2

G9

DQMB#3

K7

DQMB#4

M5

DQMB#5

V2

DQMB#6

W4

DQMB#7

T9

QSB0

B9

QSB1

D10

QSB2

H10

QSB3

K6

QSB4

N4

QSB5

U2

QSB6

U4

QSB7

V8

QSB#0

B10

QSB#1

E10

QSB#2

G10

QSB#3

J7

QSB#4

M4

QSB#5

U3

QSB#6

V4

QSB#7

V9

D6

J4

B4

B5

C2

RASB#

E2

CASB#

D3

WEB#

B2

CSB#0

D2

E3

N2

P3

L3

J2

L2

M2

K2

K3

MAB[13..0] (12, 13)

CSB#1 (13)

DQMB#[7..0] (12,13)

QSB[7..0] (12,13)

QSB#[7..0] (12,13)

CLKB0 (12,13)

CLKB#0 (12,13)

CKEB (12,13)

RASB# (12,13)

CASB# (12,13)

WEB# (12,13)

CSB#0 ( 12)

CLKB1 (12,13)

CLKB#1 (12,13)

RESET(12,13)

A A

5

4

www.vinafix.vn

RESET

Size Docum e n t N u mb er Re v

C

3

2

Date: Sheet

MS-V005 ATI RV410

RV410_MEM_A_B

1

11

10

18Tuesday, De ce mber 28, 2004

of

Page 12

5

4

256 Mbit GDDRIII Channels A and B Rank 1

3

2

1

Channel A Channel B

R315

2.37K

R316

5.49K

+MVDDQ

MDA[63..0]

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

WEA#

CASA#

RASA#

RESET

CSA#0

CKEA

CLKA0

CLKA1

CLKA#0

CLKA#1

DQMA#0

DQMA#1

DQMA#2

DQMA#3

DQMA#4

DQMA#5

DQMA#6

DQMA#7

QSA#0

QSA#1

QSA#2

QSA#3

QSA#4

QSA#5

QSA#6

QSA#7

QSA0

QSA1

QSA2

QSA3

QSA4

QSA5

QSA6

QSA7

+MVDDQ

R277

2.37K

R281

5.49K

C199

100nF

+MVDDQ +MVDDC

C711

10uf

C712

10uf

R27460.4R

316060R400

R27560.4R

316060R400

R27660.4R

316060R400

R27860.4R

316060R400

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

RESET

CLKA#0

CLKA0

CKEA

CSA#0

WEA#

RASA#

CASA#

DQMA#2

DQMA#3

DQMA#1

QSA#2

QSA#3

QSA#1

QSA#0

QSA2

QSA3

QSA1

QSA0

R938 243R

C208

100nF

+MVDDQ

+MVDDQ

+MVDDQ

U52

M9

BA1

M4

BA0

M3

A11

L3

A10

L10

A9

M10

A8/AP

M12

A7

M11

A6

L11

A5

K11

A4

K2

A3

L2

A2

M2

A1

M1

A0

L5

RESET

M7

CK

M6

CK

L6

CKE

L9

CS

M8

WE

L4

RAS

M5

CAS

B11

DM3

H2

DM2

H11

DM1

B2

DM0

A12

WDQS3

G1

WDQS2

G12

WDQS1

A1

WDQS0

A11

RDQS3

G2

RDQS2

G11

RDQS1

A2

RDQS0

E5

NC/VSS

E6

NC/VSS#E6

E7

NC/VSS#E7

E8

NC/VSS#E8

F5

NC/VSS#F5

F6

NC/VSS#F6

F7

NC/VSS#F7

F8

NC/VSS#F8

G5

NC/VSS#G5

G6

NC/VSS#G6

G7

NC/VSS#G7

G8

NC/VSS#G8

H5

NC/VSS#H5

H6

NC/VSS#H6

H7

NC/VSS#H7

H8

NC/VSS#H8

K8

RFU1

K5

RFU2

D2

RFU3

D11

RFU4

L7

RFU5

L8

ZQ

L1

VREF

L12

VREF#L12

HYB18T256321F-2.0

23CC564402

+MVDDC +MVDDQ +MVDDC

C93

C679

100nF

10uf

+MVDDQ

C216

100nF

4170010400

+MVDDQ +MVDDC

C236

100nF

4170010400

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

VDDQ

VDDQ#B4

VDDQ#B6

VDDQ#B7

VDDQ#B9

VDDQ#B10

VDDQ#G3

VDDQ#G10

VDDQ#E3

VDDQ#E10

VDDQ#F3

VDDQ#F10

VDDQ#H3

VDDQ#H10

VDDQ#J3

VDDQ#J10

VDD#C7

VDD#D3

VDD#D10

VDD#K3

VDD#K6

VDD#K7

VDD#K10

VSSQ

VSSQ#C3

VSSQ#C4

VSSQ#C5

VSSQ#C8

VSSQ#C9

VSSQ#C10

VSSQ#D5

VSSQ#D8

VSSQ#E9

VSSQ#F4

VSSQ#F9

VSSQ#G4

VSSQ#G9

VSSQ#H4

VSSQ#H9

VSSQ#J4

VSSQ#J9

VSSQ#A3

VSSQ#A10

VSS#D6

VSS#D7

VSS#D9

VSS#J5

VSS#J6

VSS#J7

VSS#J8

VSS#K4

VSS#K9

C683

10uf

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

VDD

VSS

C88

100nF

C217

100nF

4170010400

C237

100nF

4170010400

A7

B8

A8

A9

B12

C11

C12

D12

K1

J2

J1

H1

F1

F2

E1

E2

E11

E12

F11

F12

H12

J12

J11

K12

D1

C1

C2

B1

A4

A5

B5

A6

B3

B4

B6

B7

B9

B10

G3

G10

E3

E10

F3

F10

H3

H10

J3

J10

C6

C7

D3

D10

K3

K6

K7

K10

E4

C3

C4

C5

C8

C9

C10

D5

D8

E9

F4

F9

G4

G9

H4

H9

J4

J9

A3

A10

D4

D6

D7

D9

J5

J6

J7

J8

K4

K9

MDA16

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

MDA14

MDA15

MDA0

MDA1

MDA2

MDA3

MDA4

MDA5

MDA6

MDA7

R317

2.37K

R318

5.49K

+MVDDC

C218

100nF

4170010400

C238

100nF

4170010400

MDB[63..0](11,13)

+MVDDC+MVDDQ

C719

10uf

C714

10uf

+MVDDC

C228

100nF

4170010400

C248

100nF

4170010400

DQMB#[7..0](11,13)

QSB#[7..0](11,13)QSA#[7..0](11,13)

C715

10uf

MAB[13..0](11,13)

QSB[7..0](11,13)

C720

10uf

C229

100nF

4170010400

C249

100nF

4170010400

WEB#(11,13)

CASB#(11,13)

RASB#(11,13)

CSB#0(11)

CKEB(11,13)

CLKB0(11,13)

CLKB1(11,13)

CLKB#0(11,13)

CLKB#1(11,13)

C716

10uf

C230

100nF

4170010400

C250

100nF

4170010400

RESET

CLKA#1

CLKA1

CKEA

CSA#0

WEA#

RASA#

CASA#

M9

M4

M3

L3

L10

M10

M12

M11

L11

K11

K2

L2

M2

M1

L5

M7

M6

L6

L9

M8

L4

M5

B11

H2

H11

B2

A12

G1

G12

A1

A11

G2

G11

A2

E5

E6

E7

E8

F5

F6

F7

F8

G5

G6

G7

G8

H5

H6

H7

H8

K8

K5

D2

D11

L7

L8

L1

L12

C222

100nF

4170010400

C242

100nF

4170010400

U53

BA1

BA0

A11

A10

A9

A8/AP

A7

A6

A5

A4

A3

A2

A1

A0

RESET

CK

CK

CKE

CS

WE

RAS

CAS

DM3

VDDQ#B4

DM2

VDDQ#B6

DM1

VDDQ#B7

DM0

VDDQ#B9

VDDQ#B10

VDDQ#G3

VDDQ#G10

WDQS3

VDDQ#E3

WDQS2

WDQS1

VDDQ#E10

WDQS0

VDDQ#F3

VDDQ#F10

VDDQ#H3

RDQS3

VDDQ#H10

RDQS2

VDDQ#J3

RDQS1

VDDQ#J10

RDQS0

VDD#D10

NC/VSS

NC/VSS#E6

NC/VSS#E7

NC/VSS#E8

VDD#K10

NC/VSS#F5

NC/VSS#F6

VSSQ#C3

NC/VSS#F7

VSSQ#C4

NC/VSS#F8

VSSQ#C5

NC/VSS#G5

VSSQ#C8

NC/VSS#G6

VSSQ#C9

NC/VSS#G7

VSSQ#C10

NC/VSS#G8

VSSQ#D5

NC/VSS#H5

VSSQ#D8

NC/VSS#H6

VSSQ#E9

NC/VSS#H7

VSSQ#F4

NC/VSS#H8

VSSQ#F9

VSSQ#G4

VSSQ#G9

VSSQ#H4

RFU1

VSSQ#H9

RFU2

RFU3

VSSQ#J4

RFU4

VSSQ#J9

RFU5

VSSQ#A3

VSSQ#A10

ZQ

VREF

VREF#L12

HYB18T256321F-2.0

23CC564402

C680

10uf

C224

C223

100nF

100nF

4170010400

4170010400

C243

C244

100nF

100nF

4170010400

4170010400

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

VDDQ

VDD

VDD#C7

VDD#D3

VDD#K3

VDD#K6

VDD#K7

VSSQ

VSS#D6

VSS#D7

VSS#D9

VSS#J5

VSS#J6

VSS#J7

VSS#J8

VSS#K4

VSS#K9

C92

100nF

MDA32

A7

MDA33

B8

MDA34

A8

MDA35

A9

MDA36

B12

MDA37

C11

MDA38

C12

MDA39 MDB39

D12

MDA56

K1

MDA57

J2

MDA58

J1

MDA59

H1

MDA60

F1

MDA61

F2

MDA62

E1

MDA63

E2

MDA48

E11

MDA49

E12

MDA50

F11

MDA51

F12

MDA52

H12

MDA53

J12

MDA54

J11

DQ9

MDA55

K12

DQ8

MDA40

D1

DQ7

MDA41

C1

DQ6

MDA42

C2

DQ5

MDA43

B1

DQ4

MDA44

A4

DQ3

MDA45

A5

DQ2

MDA46

B5

DQ1

MDA47

A6

DQ0

B3

B4

B6

B7

B9

+MVDDQ

B10

G3

G10

E3

E10

F3

F10

H3

H10

J3

J10

C6

+MVDDC

C7

D3

D10

K3

K6

K7

K10

E4

C3

C4

C5

C8

C9

C10

D5

D8

E9

F4

F9

G4

G9

H4

H9

J4

J9

A3

A10

D4

VSS

D6

D7

D9

J5

J6

J7

J8

K4

K9

+MVDDC+MVDDQ +MVDDC+MVDDQ

C214

10uf

C225

100nF

4170010400

C245

100nF

4170010400

+MVDDQ

+MVDDQ

C89

100nF

C226

100nF

4170010400

C246

100nF

4170010400

C713

10uf

C227

100nF

4170010400

C247

100nF

4170010400

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

DQMA#4

DQMA#7

DQMA#6

+MVDDQ

+MVDDC

+MVDDQ +MVDDQ

R270

2.37K

R271

5.49K

+MVDDQ

C198

100nF

C219

100nF

4170010400

C239

100nF

4170010400

DQMA#5

QSA#4

QSA#7

QSA#6

QSA#5

QSA4

QSA7

QSA6

QSA5

R939 243R

C200

100nF

+MVDDQ

C220

C221

100nF

100nF

4170010400

4170010400

+MVDDQ +MVDDC +MVDDQ

C241

C240

100nF

100nF

4170010400

4170010400

MDA[63..0](11,13)

MAA[13..0]( 11,13)

D D

WEA#(11,13)

CASA#(11,13)

RASA#(11,13)

RESET(11,13)

CSA#0(11)

CKEA(11,13)

CLKA0(11,13)

CLKA1(11,13)

CLKA#0(11,13)

CLKA#1(11,13)

DQMA#[7..0](11,13)

C C

QSA[7..0](11,13)

B B

CLKA0(11,13)

A A

CLKA#0(11,13)

CLKA1(11,13)

CLKA#1(11,13)

R319

2.37K

R320

5.49K

+MVDDQ

+MVDDQ +MVDDC+MVDDC

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

WEB#

CASB#

RASB#

CSB#0

CKEB

CLKB0

CLKB1

CLKB#0

CLKB#1

DQMB#0

DQMB#1

DQMB#2

DQMB#3

DQMB#4

DQMB#5

DQMB#6DQMA#0

DQMB#7

QSB#0

QSB#1

QSB#2

QSB#3

QSB#4

QSB#5

QSB#6

QSB#7

QSB0

QSB1

QSB2

QSB3

QSB4

QSB5

QSB6

QSB7

C231

100nF

4170010400

C251

100nF

4170010400

MDB[63..0]

C197

100nF

+MVDDQ

R279

2.37K

C210

R283

100nF

5.49K

+MVDDQ +MVDDQ

C212

22uF_16V

C233

C232

100nF

100nF

4170010400

4170010400

C252

C253

100nF

100nF

4170010400

4170010400

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

RESET

CLKB#0

CLKB0

CKEB

CSB#0

WEB#

RASB#

CASB#

DQMB#2

DQMB#3

DQMB#1

DQMB#0

QSB#2

QSB#3

QSB#1

QSB#0

QSB2

QSB3

QSB1

QSB0

R940 243R

+MVDDC+MVDDC

U54

M9

BA1

M4

BA0

M3

A11

L3

A10

L10

A9

M10

A8/AP

M12

A7

M11

A6

L11

A5

K11

A4

K2

A3

L2

A2

M2

A1

M1

A0

L5

RESET

M7

CK

M6

CK

L6

CKE

L9

CS

M8

WE

L4

RAS

M5

CAS

B11

DM3

H2

H11

A12

G1

G12

A11

G2

G11

G5

G6

G7

G8

H5

H6

H7

H8

D2

D11

L12

C215

10uf

C234

100nF

4170010400

C254

100nF

4170010400

B2

A1

A2

E5

E6

E7

E8

F5

F6

F7

F8

K8

K5

L7

L8

L1

VDDQ#B4

DM2

VDDQ#B6

DM1

VDDQ#B7

DM0

VDDQ#B9

VDDQ#B10

VDDQ#G3

VDDQ#G10

WDQS3

VDDQ#E3

WDQS2

WDQS1

VDDQ#E10

WDQS0

VDDQ#F3

VDDQ#F10

VDDQ#H3

RDQS3

VDDQ#H10

RDQS2

VDDQ#J3

RDQS1

VDDQ#J10

RDQS0

VDD#C7

VDD#D3

VDD#D10

NC/VSS

VDD#K3

NC/VSS#E6

VDD#K6

NC/VSS#E7

VDD#K7

NC/VSS#E8

VDD#K10

NC/VSS#F5

NC/VSS#F6

VSSQ#C3

NC/VSS#F7

VSSQ#C4

NC/VSS#F8

VSSQ#C5

NC/VSS#G5

VSSQ#C8

NC/VSS#G6

VSSQ#C9

NC/VSS#G7

VSSQ#C10

NC/VSS#G8

VSSQ#D5

NC/VSS#H5

VSSQ#D8

NC/VSS#H6

VSSQ#E9

NC/VSS#H7

VSSQ#F4

NC/VSS#H8

VSSQ#F9

VSSQ#G4

VSSQ#G9

VSSQ#H4

RFU1

VSSQ#H9

RFU2

RFU3

VSSQ#J4

RFU4

VSSQ#J9

RFU5

VSSQ#A3

VSSQ#A10

ZQ

VSS#D6

VSS#D7

VSS#D9

VSS#J5

VREF

VSS#J6

VSS#J7

VSS#J8

VSS#K4

VREF#L12

VSS#K9

HYB18T256321F-2.0

23CC564402

+MVDDC +MVDDC

C682

10uf

C235

100nF

4170010400

C255

100nF

4170010400

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

VDDQ

VSSQ

C90

100nF

MDB16

A7

MDB17

B8

MDB18

A8

MDB19

A9

MDB20

B12

MDB21

C11

MDB22

C12

MDB23

D12

MDB24

K1

MDB25

J2

MDB26

J1

MDB27

H1

MDB28

F1

MDB29

F2

MDB30

E1

MDB31

E2

MDB8

E11

MDB9

E12

MDB10

F11

MDB11

F12

MDB12

H12

MDB13

J12

MDB14

J11

DQ9

MDB15

K12

DQ8

MDB0

D1

DQ7

MDB1

C1

DQ6

MDB2

C2

DQ5

MDB3

B1

DQ4

MDB4

A4

DQ3

MDB5

A5

DQ2

MDB6

B5

DQ1

MDB7

A6

DQ0

B3

B4

B6

B7

B9

+MVDDQ

B10

G3

G10

E3

E10

F3

F10

H3

H10

J3

J10

C6

VDD

VSS

+MVDDC

C7

D3

D10

K3

K6

K7

K10

E4

C3

C4

C5

C8

C9

C10

D5

D8

E9

F4

F9

G4

G9

H4

H9

J4

J9

A3

A10

D4

D6

D7

D9

J5

J6

J7

J8

K4

K9

R272

2.37K

R273

5.49K

+MVDDQ

R321

2.37K

R322

5.49K

CLKB0(11,13)

CLKB#0(11,13)

CLKB1(11,13)

CLKB#1(11,13)

C196

100nF

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

R941 243R

C201

100nF

+MVDDQ

R26060.4R

316060R400

R26160.4R

316060R400

+MVDDQ

R26260.4R

316060R400

R26360.4R

316060R400

DQMB#4

DQMB#7

DQMB#6

DQMB#5

QSB#4

QSB#7

QSB#6

QSB#5

QSB4

QSB7

QSB6

QSB5

RESET

CLKB#1

CLKB1

CKEB

CSB#0

WEB#

RASB#

CASB#

U55

M9

M4

M3

L3

L10

M10

M12

M11

L11

K11

K2

L2

M2

M1

L5

M7

M6

L6

L9

M8

L4

M5

B11

H2

H11

B2

A12

G1

G12

A1

A11

G2

G11

A2

E5

E6

E7

E8

F5

F6

F7

F8

G5

G6

G7

G8

H5

H6

H7

H8

K8

K5

D2

D11

L7

L8

L1

L12

HYB18T256321F-2.0

23CC564402

+MVDDQ

C681

10uf

BA1

BA0

A11

A10

A9

A8/AP

A7

A6

A5

A4

A3

A2

A1

A0

RESET

CK

CK

CKE

CS

WE

RAS

CAS

DM3

DM2

DM1

DM0

WDQS3

WDQS2

WDQS1

WDQS0

RDQS3

RDQS2

RDQS1

RDQS0

NC/VSS

NC/VSS#E6

NC/VSS#E7

NC/VSS#E8

NC/VSS#F5

NC/VSS#F6

NC/VSS#F7

NC/VSS#F8

NC/VSS#G5

NC/VSS#G6

NC/VSS#G7

NC/VSS#G8

NC/VSS#H5

NC/VSS#H6

NC/VSS#H7

NC/VSS#H8

RFU1

RFU2

RFU3

RFU4

RFU5

ZQ

VREF

VREF#L12

VDDQ#B4

VDDQ#B6

VDDQ#B7

VDDQ#B9

VDDQ#B10

VDDQ#G3

VDDQ#G10

VDDQ#E3

VDDQ#E10

VDDQ#F3

VDDQ#F10

VDDQ#H3

VDDQ#H10

VDDQ#J3

VDDQ#J10

VDD#C7

VDD#D3

VDD#D10

VDD#K3

VDD#K6

VDD#K7

VDD#K10

VSSQ#C3

VSSQ#C4

VSSQ#C5

VSSQ#C8

VSSQ#C9

VSSQ#C10

VSSQ#D5

VSSQ#D8

VSSQ#E9

VSSQ#F4

VSSQ#F9

VSSQ#G4

VSSQ#G9

VSSQ#H4

VSSQ#H9

VSSQ#J4

VSSQ#J9

VSSQ#A3

VSSQ#A10

VSS#D6

VSS#D7

VSS#D9

VSS#K4

VSS#K9

C94

100nF

C717

10uf

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

VDDQ

VSSQ

VSS#J5

VSS#J6

VSS#J7

VSS#J8

MDB32