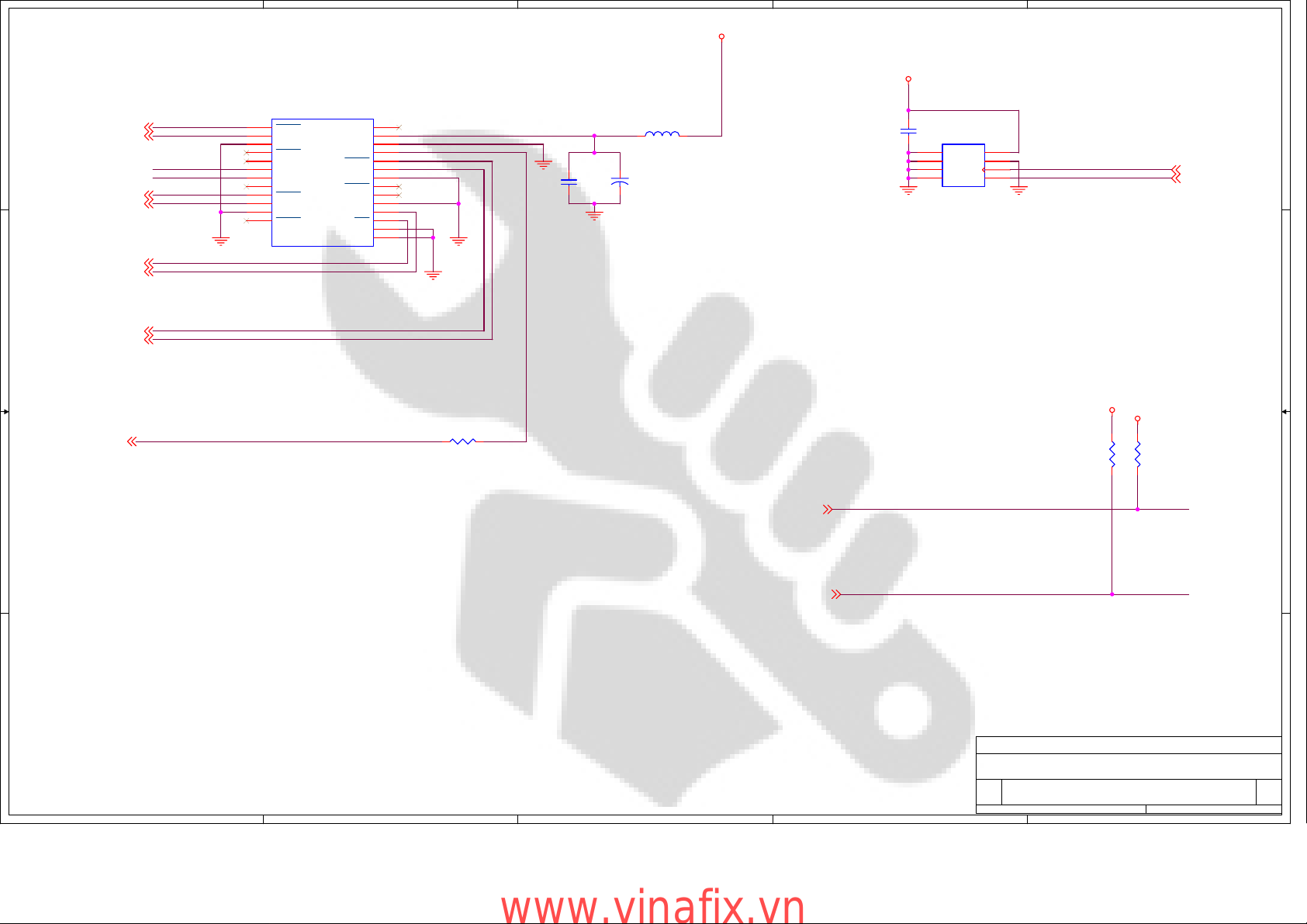

Page 1

5

3.3V

R1

2.5VSDA

D D

2.5VSCL

C C

B B

316,1%

C1

316,1%

C2

0.1uF

C6

0.1uF

SDVO_SCL(2)

SDVO_SDA(2)

1uF

C5

1uF

R7

5.6K

SDVOB_R+(2)

SDVOB_R-(2)

SDVOB_G+(2)

SDVOB_G-(2)

SDVOB_B+(2)

SDVOB_B-(2)

SDVOB_C+(2)

SDVOB_C-(2)

R2

1K,1%

3.3V

R4

R5

1K,1%

12V

3.3V

B1

12V

B2

12V

B3

RSVD

B4

GND

B5

NC(B5)

B6

NC(B6)

B7

GND

B8

3.3V

B9

R8

5.6K

3.3V 12V

NC(B9)

B10

NC(B10)

B11

NC(B11)

KEY KEY

B12

RSVD(B12)

B13

GND

B14

SDVOB_RED+

B15

SDVOB_RED-

B16

GND

B17

SDVO_CtrlCLK

B18

GND

B19

SDVOB_GREEN+

B20

SDVOB_GREEN-

B21

GND

B22

GND

B23

SDVOB_BLUE+

B24

SDVOB_BLUE-

B25

GND

B26

GND

B27

SDVOB_CLK+

B28

SDVOB_CLK-

B29

GND

B30

RSVD(B30)

B31

SDVO_CtrlDATA

B32

GND

C12

0.1uF

C13

CON1

10uF

4

SDVO/PCI-EX4

C14

0.1uF

NC(A1)

12V

12V

GND

NC(A5)

TDO

NC(A8)

3.3V

3.3V

RESET#

GND

NC(A13)

NC(A14)

GND

SDVO_TVCLKin+

SDVO_TVCLKin-

GND

RSVD(A19)

GND

SDVOB_INT+

SDVOB_INT-

GND

GND

SDVO_STALL+

SDVO_STALL-

GND

GND

NC(A29)

NC(A30)

GND

RSVD(A32)

C15

10uF

3

3.3V PVCC POWER SUPPLY

A1

A2

A3

A4

A5

A6

TDI

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

RESET# (2)

SDVOB_INT+ (2)

SDVOB_INT- (2)

5V POWER SUPPLY

1.8V POWER SUPPLY

C102

0.1uF

12V

2

C3

10uF

12V

C7

10uF

3.3V

LM317EMP/SOT-223

U1

3

VIN

OUTPUT

VOUT

ADJ

1

U2

1

VIN

2

VOUT

3 6

VOUT VOUT

4

ADJ

LM317L/SOIC 8

C9

10uF

2

4

R3

240,1%

R6

412,1%

8

NC

7

VOUT

5

NC

U3

3 2

VIN OUTPUT

1

LM1117 1.8/SOT-223

TAB

GND

4

R9

240,1%

R10

732,1%

C4

10uF

1

PVCC

C101

C100

100pF

100pF

5.0V

C8

10uF

1.8V

C10

10uF

A A

PRELIMINARY 64pin-TQFP SDVO ADD2-N REFERENCE DESIGN

SCHEMATICS SUBJECT TO CHANGE AFTER VALIDATION

5

4

3

2

Title

MS-V004

Size Document Number Rev

SiI-SC-0066 A

B

13Friday, April 29, 2005

Date: Sheet

1

of

www.vinafix.vn

Page 2

5

Remove C

A1

TEST

1

2 3

U4

46

47

51

52

54

55

57

58

60

61

49

1

7

6

8

12

11

13

14

40

SII-SDVO

D D

L11

1

2 3

C C

3.3V

B B

R23

R24

NO_STUFF

1K(NP)

1K

4

SDVOB_INT+(1)

SDVOB_INT-(1)

SDAROM(3)

SCLROM(3)

0.1uF

C20

C210.1uF

SDVOB_R+(1)

SDVOB_R-(1)

SDVOB_G+(1)

SDVOB_G-(1)

SDVOB_B+(1)

SDVOB_B-(1)

SDVOB_C+(1)

SDVOB_C-(1)

R22 1K

RESET#(1)

SDVO_SCL(1)

SDVO_SDA(1)

SDADDC(3)

SCLDDC(3)

64PIN TQFP

A A

4

L10

1

2 3

L9

4

L8

1

2 3

TX1-

TX2-

TX1+

TX2+

SDI+

SDI-

SDR+

SDR-

SDG+

SDG-

SDB+

SDB-

SDC+

SDC-

EXT_RES

RESET#

SDSCL

SDSDA

A1

SDADDC

SCLDDC

SDAROM

SCLROM

TEST

RSVD9

RSVD8

3435364243444

RR9

RR8

RR7

3

2

1

JUMPERS JP[7..1] used for test purposes only. Please do not stuff the jumpers at all times.

4

R13

300

R14

300

4

312019232226252928

HTPLG

TX0-

TXC-

TX0+

TXC+

EXT_SWING

RSVD0

RSVD6

PVCC1

PGND1

PVCC2

PGND2

SPVCC

RR5

SPGND

RSVD5

RSVD4

RSVD3

RSVD2

RSVD1

3

RR4

RR3

RR2

RR1

RSVD7

VCC

VCC

VCC

VCC

GND

GND

AVCC

AVCC

AGND

AGND

AGND

OVCC

SVCC

SVCC

GND

GND

SGND

SGND

R15

300

0.1uF

0.1uF

R12

22

39

9

15

48

38

5

10

2

37

21

27

18

24

30

64

17

16

32

33

50

56

41

45

53

59

62

63

C16

C17

0.1uF

22

C18

R11

R18

360

RR0

RR6

R16

300

C19

0.1uF

C49

100pF

C22

100pF

C44

100pF

C50

1nF

C23

1nF

C31

100pF

C45

1nF

SPVCC

C51

10uF

C24

0.1uF

C32

1nF

C46

0.1uF

L6 BEAD

TX2+ (3)

TX2- (3)

TX1+ (3)

TX1- (3)

TX0+ (3)

TX0- (3)

TXC+ (3)

TXC- (3)

C26

C25

0.1uF

1nF

AVCC

C34

C33

1nF

0.1uF

SVCC

C47

1nF

PVCC

C35

10uF

C48

10uF

RULES

Route traces with 100 Ohm Differential Impedance

Avoid placing GND Copper or traces adjacent to TMDS Trace

Put these 4 resistors and 4 capacitors as close as possible

to the TMDS output pins of the SiI1362

1.8V

C27

1nF

L2 BEAD

PVCC2

L5 BEAD

C28

0.1uF

1.8V

3.3V

C41

0.1uF

C29

1nF

C42

1nF

C30

10uF

C43

L1 BEAD

L4 BEAD

1uF

RR0

RR1

RR2

RR3

RR4

RR5

RR6

RR7

RR8

RR9

OVCC

PVCC1

PVCC

C36

1uF

C37

C38

0.1uF

10uF

3.3V

R17

2.2K(NP)

R19

330(NP)

C39

1nF

NO_STUFF

HPDET (3)

3.3V

C40

1uF

PVCC

L3 BEAD

PRELIMINARY 64pin-TQFP SDVO ADD2-N REFERENCE DESIGN

SCHEMATICS SUBJECT TO CHANGE AFTER VALIDATION

5

4

3

www.vinafix.vn

Title

MS-V004-0A

Size Document Number Rev

SiI-SC-0066 A

B

23Friday, April 29, 2005

2

Date: Sheet

1

of

Page 3

5

4

3

5.0V

2

3.3V

1

D D

TX2-(2)

TX2+(2)

SCLDDC

SDADDC

TX1-(2)

TX1+(2)

TXC-(2)

TXC+(2)

C C

TX0+(2)

TX0-(2)

HPDET(2)

B B

CON2

1

2

3

4

5

6

7

8

9

10

11

12

DATA2

DATA2

SHIELD24

DATA4

DATA4

DDCCLK

DDCDATA

NC

DATA1

DATA1

SHIELD13

DATA3

DVI-D

DATA3

VCC5

GND5

HPDET

DATA0

DATA0

SHIELD05

DATA5

DATA5

SHIELDCLK

CLK

CLK

Shell

Shell

13

14

15

16

17

18

19

20

21

22

23

24

31

32

R29

10K

C53

0.1uF

L7 BEAD

C54

10uF

SDADDC(2)

0.1uF

C52

U5

1

A0

VCC

2

A1

WP

3

A2

SCL

4 5

VSS SDA

24LC02

8

7

6

5.0V

5.0V

R30

2.2K

R31

2.2K

SDADDC

SCLROM (2)

SDAROM (2)

SCLDDC(2)

A A

PRELIMINARY 64pin-TQFP SDVO ADD2-N REFERENCE DESIGN

SCHEMATICS SUBJECT TO CHANGE AFTER VALIDATION

5

4

3

2

Title

MS-V004-0A

Size Document Number Rev

SiI-SC-0066 A

B

Date: Sheet

SCLDDC

1

33Friday, April 29, 2005

of

www.vinafix.vn

Page 4

5

D D

4

3

2

1

FM1

SW_FB

1

FM2

C C

B B

SW_FB

1

FM3

SW_FB

1

FM4

SW_FB

1

FM5

SW_FB

1

FM6

SW_FB

1

A A

Title

MS-V004-0A

Size Document Number Rev

SiI-SC-0066 A

A

5

4

3

Date: Sheet

2

33Friday, April 29, 2005

of

1

www.vinafix.vn

Loading...

Loading...