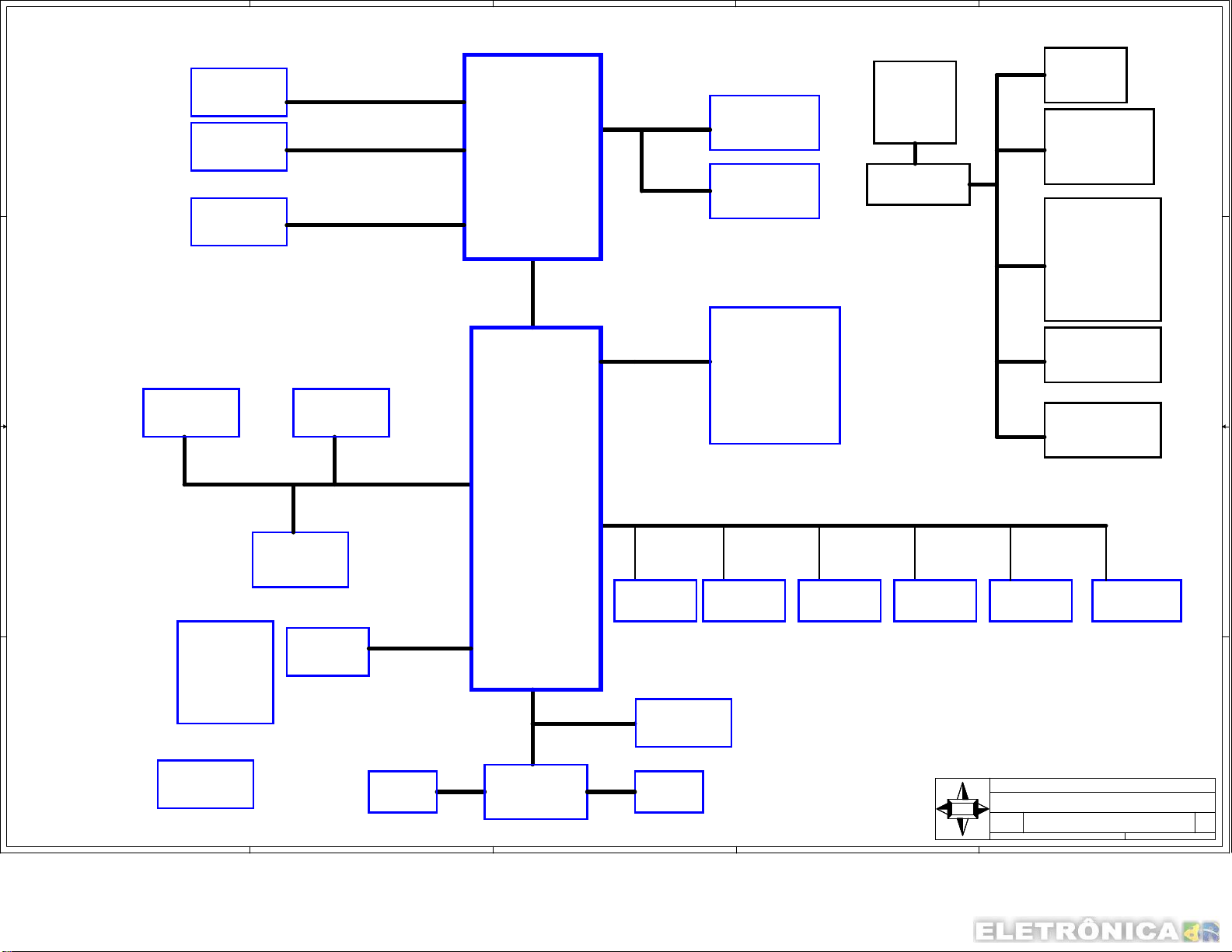

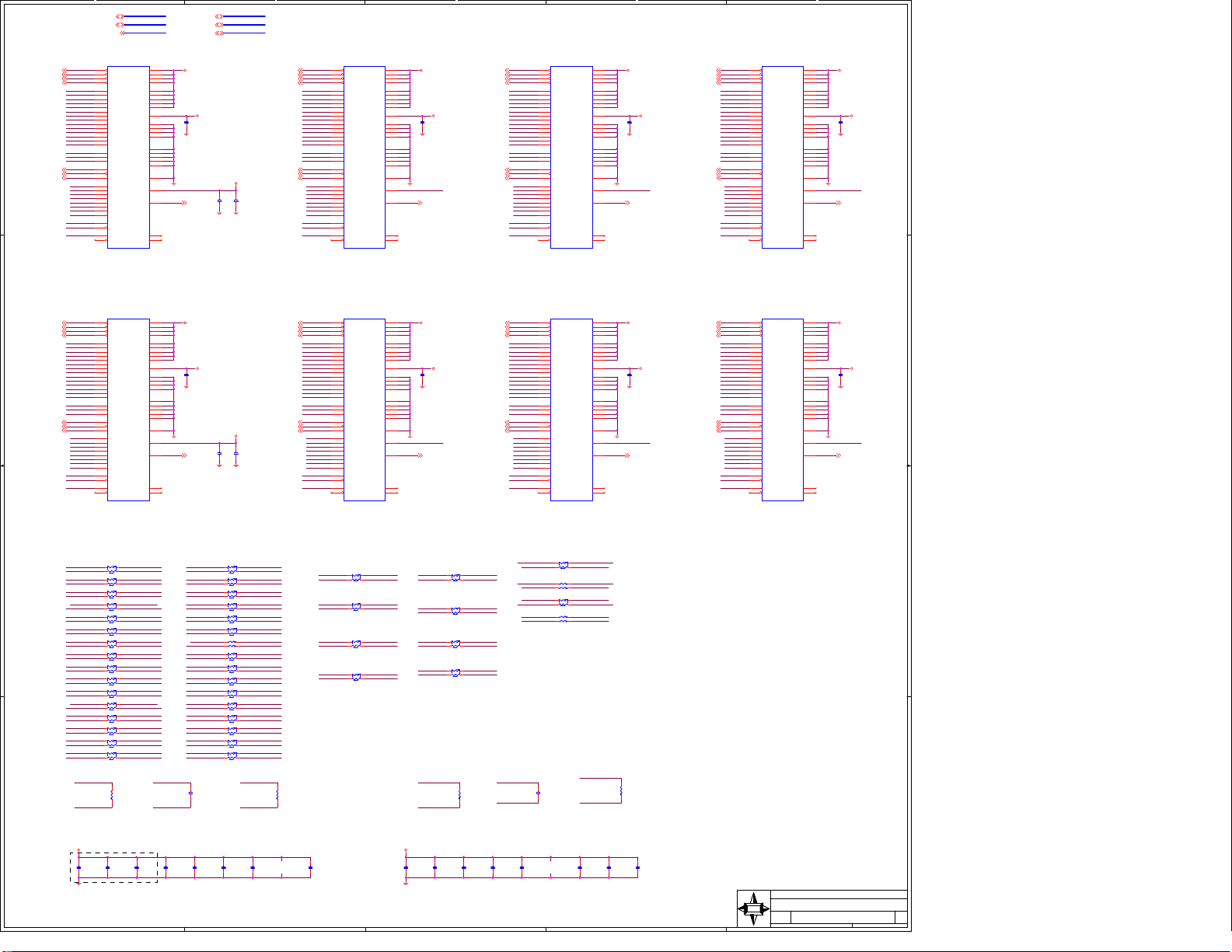

MSI MS-N0141 Schematic

A

B

C

D

E

MS-N01x VER : 0A

+3V +5V

CRT

4 4

Page 8

LVDS

Page 8

XDP

Page 27

RGB

LVDS

Debug Port

Pineview

CPU+GMCH

45nm

512KB L2 cache

559 pin FCBGA

Page 2,3

Signal Channel DDRII

667 MHZ

DDR-SODIMM 1

Page 5

DDR-SODIMM 2

Page 6

DC JACK

&

Selector

Page 20

SYS POWER

DMIx2

3 3

Interface

SATA 160GB HDD

3.5G or TV

MINI PCIE

Conn.

Page 17

Wireless LAN

MINI PCIE

Conn.

Page 17

SATA

Tigerpoint

360 pin VFBGA

OR

JMF 602

NAND FLASH

optional

Page 9

PCI-EXPRESS

TPS51125

Page 22

+1_8VDIMM

+0_89VGFX

UP6111A

Page 23

+1P05V(1.05V)

UP6111A

+1_5VRUN

UP7706

+1_8VRUN

UP7704

Page 24

CPU POWER

ISL6261A

Page 25

CHARGER

ISL6251

Page 21

USB1.1/2.0

2 2

Internal SPK

Internal MIC

MIC

PCIE-LAN

RTL8103EL

Page 15

ALC888S

Page 19

HD

Page 9~11

Mini_PCIE x1

Connectors

USB 0,1,2

Page 18 Page 17 Page 18

3.5G&GPS

USB 3

Blue tooth

USB 4

Page 17

Camera

USB 5

Mini_PCIE x1

Wireless LAN

USB 6

Page 18

Cardreader

USB 7

Page 16

Earphone

Page 20

1 1

CLK ICS3113

Page 12

A

TP & KB

Page 13

B

LPC BUS

KBC

ENE 3926D

Page 13

SPI

C

LPC DUBUG

Page 13

BIOS

Page 13

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N01x

MS-N01x

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Tuesday, May 19, 2009

Tuesday, May 19, 2009

D

Tuesday, May 19, 2009

MS-N01x

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

E

Sheet ofDate:

134

Sheet ofDate:

134

Sheet ofDate:

134

0A

0A

0A

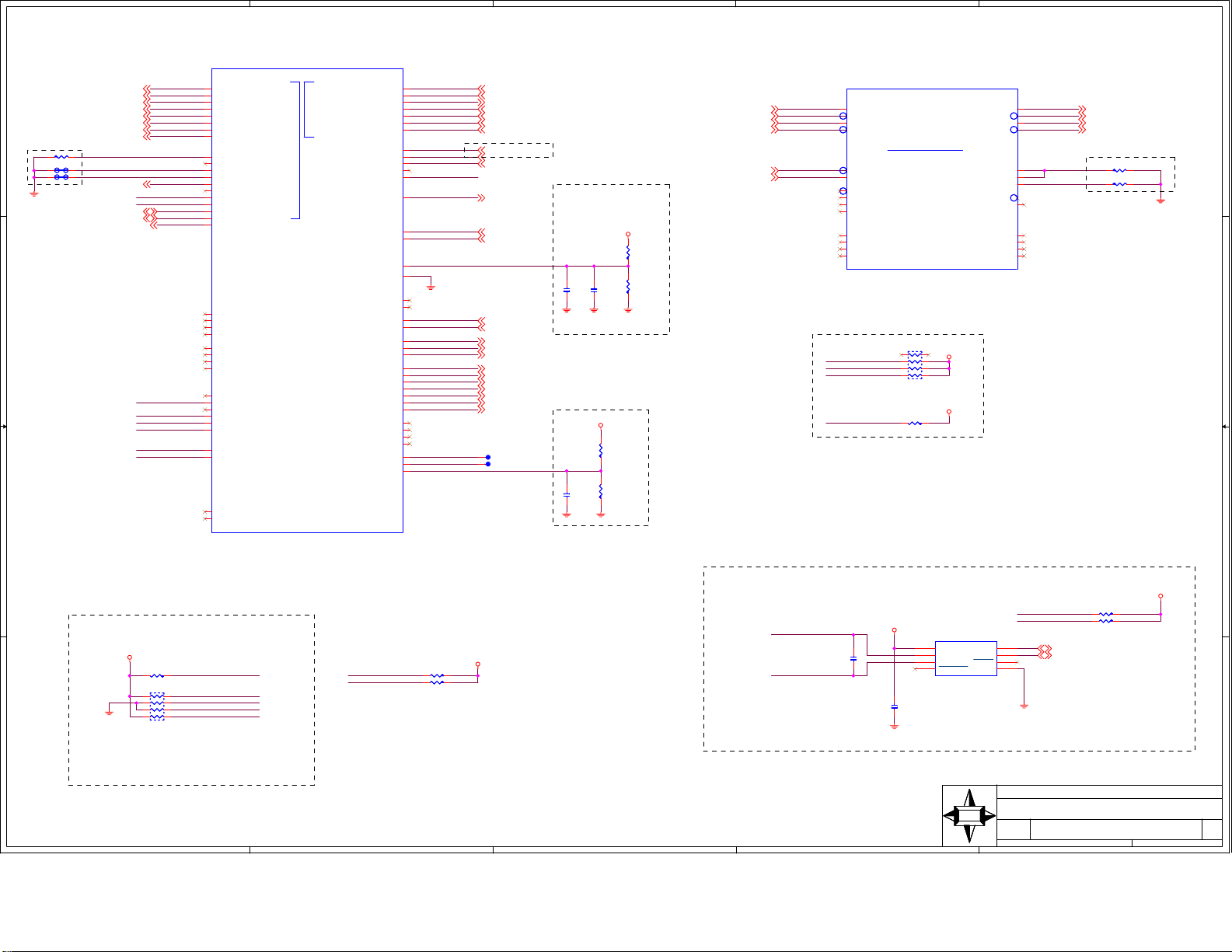

A

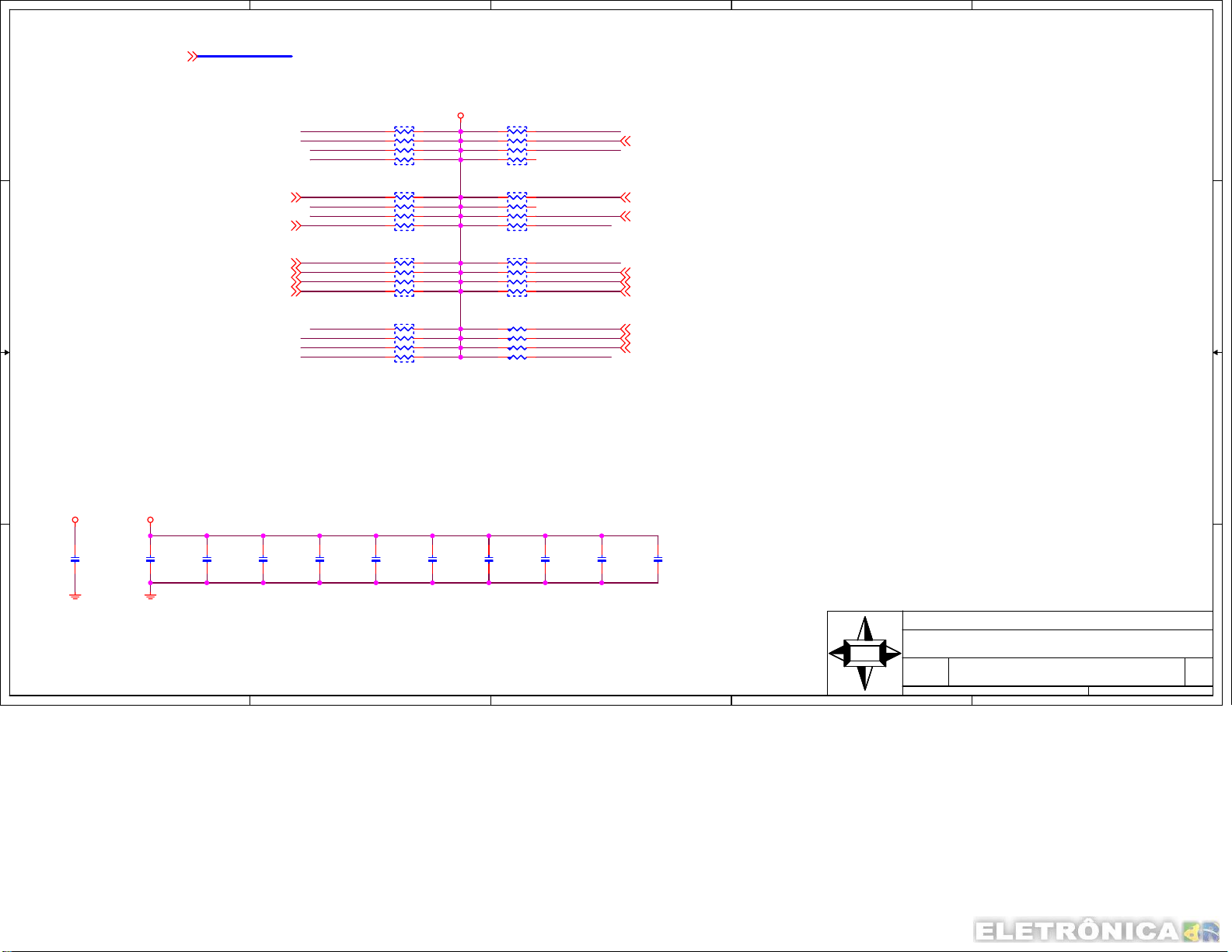

?

resolution

1280x800

LVDS_TXCKN8

LVDS_TXCKP8

LVDS_TX0N8

4 4

Place resistors

close to PNV

R66 2.37K1%4R66 2.37K1%4

R76 X_NCR76 X_NC

R67 X_NCR67 X_NC

3 3

2 2

LVDS_TX0P8

LVDS_TX1N8

LVDS_TX1P8

LVDS_TX2N8

LVDS_TX2P8

LVD_IBG

LVD_VREFL_OUT_R

LVD_VREFH_OUT_R

LVDS_BLON8

LVDS_CLK8

LVDS_DATA8

LVDS_VDDEN8

LCTLA_CLK

LCTLB_DATA

H_TDI

H_TCK

H_TMS

H_TRST

H_THERMDA

H_THDRMDC

U25

U26

R23

R24

N26

N27

R26

R27

R22

J28

N22

N23

L27

L26

L23

K25

K23

K24

H26

G11

E15

G13

F13

B18

B20

C20

B21

G5

D14

D13

B14

C14

C16

D30

E30

C30

D31

CPU1D

CPU1D

LVD_A_CLKM

LVD_A_CLKP

LVD_A_DATAM_0

LVD_A_DATAP_0

LVD_A_DATAM_1

LVD_A_DATAP_1

LVD_A_DATAM_2

LVD_A_DATAP_2

LVD_IBG

LVD_VBG

LVD_VREFH

LVD_VREFL

LBKLT_EN

LBKLT_CTL

LCTLA_CLK

LCTLB_CLK

LDDC_CLK

LDDC_DATA

LVDD_EN

BPM_1B_0

BPM_1B_1

BPM_1B_2

BPM_1B_3

BPM_2B_0

BPM_2B_1

BPM_2B_2

BPM_2B_3

RSVD

TDI

TDO

TCK

TMS

TRST_B

THRMDA_1

THRMDC_1

RSVD_C30

RSVD_D31

PNV

PNV

?

PINEVIEW_M

PINEVIEW_M

REV = 1.1

REV = 1.1

ICH

ICH

LVDS

LVDS

CPU

CPU

? 4 OF 6

? 4 OF 6

B

SMI_B

A20M_B

FERR_B

LINT00

LINT10

IGNNE_B

STPCLK_B

DPRSTP_B

DPSLP_B

INIT_B

PRDY_B

PREQ_B

THERMTRIP_B

PROCHOT_B

CPUPWRGOOD

GTLREF

RSVD

RSVD

BCLKN

BCLKP

BSEL_0

BSEL_1

BSEL_2

VID_0

VID_1

VID_2

VID_3

VID_4

VID_5

VID_6

RSVD

RSVD

RSVD

RSVD

RSVD_TP

RSVD_TP

EXTBGREF

C

E7

H7

H_FERR#

H6

F10

F11

E5

F8

G6

G10

G8

E11

H_BPM5_PREQ

F15

H_THRMTRIP#

E13

H_PROCHOT#

C18

W1

CPU_GTLREF

A13

H27

VSS

L6

E17

H10

J10

CPU_BSEL0

K5

CPU_BSEL1

H5

CPU_BSEL2

K6

H30

H29

H28

G30

G29

F29

E29

L7

D20

H13

D18

K9

D19

EXTBGTLREF

K7

H_SMI# 9

H_A20M# 9

H_FERR# 9

H_INTR 9

H_NMI 9

H_IGNNE# 9

H_STPCLK# 9

H_DPRSTP# 10,26

H_DPSLP# 10

H_INIT# 9

H_THRMTRIP# 9

H_PROCHOT# 26

H_PWRGD 10

CLK_CPU_BCLK# 12

CLK_CPU_BCLK 12

CPU_BSEL0 12

CPU_BSEL1 12

CPU_BSEL2 12

CPU_VID0 26

CPU_VID1 26

CPU_VID2 26

CPU_VID3 26

CPU_VID4 26

CPU_VID5 26

CPU_VID6 26

T10T10

T11T11

H_DPRSTP#: daisy chain

TGP->VRM->PNV

GTLREF

500mil max length

5mil spacing

C127

C127

C116

C116

1u6.3Y4

1u6.3Y4

+1P05V

R93

R93

R91

R91

C126

C126

X_220P50N4

X_220P50N4

1u6.3Y4

1u6.3Y4

+1P05V

R85

R85

976R1%4

976R1%4

R81

R81

3.32K1%4

3.32K1%4

1K1%4

1K1%4

2K1%4

2K1%4

DMI_PNV_RXP09

DMI_PNV_RXN09

DMI_PNV_RXP19

DMI_PNV_RXN19

CLK_PCIE_PNV#12

CLK_PCIE_PNV12

CPU1A

CPU1A

F3

DMI_RXP_0

F2

DMI_RXN_0

H4

DMI_RXP_1

G3

DMI_RXN_1

N7

EXP_CLKINN

N6

EXP_CLKINP

R10

RSVD

R9

RSVD

N10

RSVD

N9

RSVD

K2

RSVD_K2

J1

RSVD_J1

M4

RSVD_M4

L3

RSVD_L3

PNV

PNV

CPU_BSEL1

CPU_BSEL2

CPU_BSEL0

H_PROCHOT#

D

PINEVIEW_M

PINEVIEW_M

REV = 1.1

REV = 1.1

RN53

RN53

1

3

5

7

8P4R-470R/4

8P4R-470R/4

R97 68R/4R97 68R/4

E

?

?

G2

DMI_TXP_0

G1

DMI_TXN_0

H3

DMI_TXP_1

J2

DMI_TXN_1

DMI

DMI

GIRCOMP

EXP_ICOMPI

EXP_RBIAS

RSVD_TP

RSVD_TP

RSVD_K3

RSVD_L2

RSVD_M2

RSVD_N2

1 OF 6?

1 OF 6?

L10

L9

GRBIAS

L8

N11

P11

K3

L2

M2

N2

EXP_RCOMPO

+1P05V

2

4

6

8

+1P05V

DMI_TGP_TXP0 9

DMI_TGP_TXN0 9

DMI_TGP_TXP1 9

DMI_TGP_TXN1 9

within 500mil from PNV.

R73 49.9R1%4R73 49.9R1%4

R78 750R1%4R78 750R1%4

Thermal Sensor

SMB_THRM_CLK

SMB_THRM_DATA

8

7

6

ALERT

5

[Fuqun] Remove THERMAL_INT# in 0A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Monday, June 08, 2009

Monday, June 08, 2009

Monday, June 08, 2009

C120

C120

0.1u10X4

0.1u10X4

D

+3VRUN

U13

U13

1

VDD

2

D+

3

DT_CRIT_A4GND

SNSR-G780P81U

SNSR-G780P81U

SMBCLK

SMBData

MSI

MSI

MSI

Debug Port

+1P05V

R87 51R/4R87 51R/4

RN54

RN54

1

3

5

7

8P4R-51R/4

8P4R-51R/4

1 1

Place TCK/TDI/TMS termination near CPU

H_BPM5_PREQ LCTLB_DATA

H_TDI

2

H_TRST

4

H_TCK

6

H_TMS

8

LCTLA_CLK

[Fuqun] Add R228/R232 in 0A

R70 X_2.2K/4R70 X_2.2K/4

R65 X_2.2K/4R65 X_2.2K/4

[Fuqun] NC BPM in 0A

A

B

+3VRUN

[Fuqun] Thermal sensor change P/N

C

H_THERMDA

H_THDRMDC

on same layer

Trace : 10/10/10

C124

C124

100p16N4

100p16N4

R77 2.2K/4R77 2.2K/4

R72 2.2K/4R72 2.2K/4

SMB_THRM_CLK 13

SMB_THRM_DATA 13

MS-N01x

MS-N01x

MS-N01x

PNV (HOST/LVDS/ DMI)

PNV (HOST/LVDS/ DMI)

PNV (HOST/LVDS/ DMI)

+3VRUN

0A

0A

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

E

0A

235

235

235

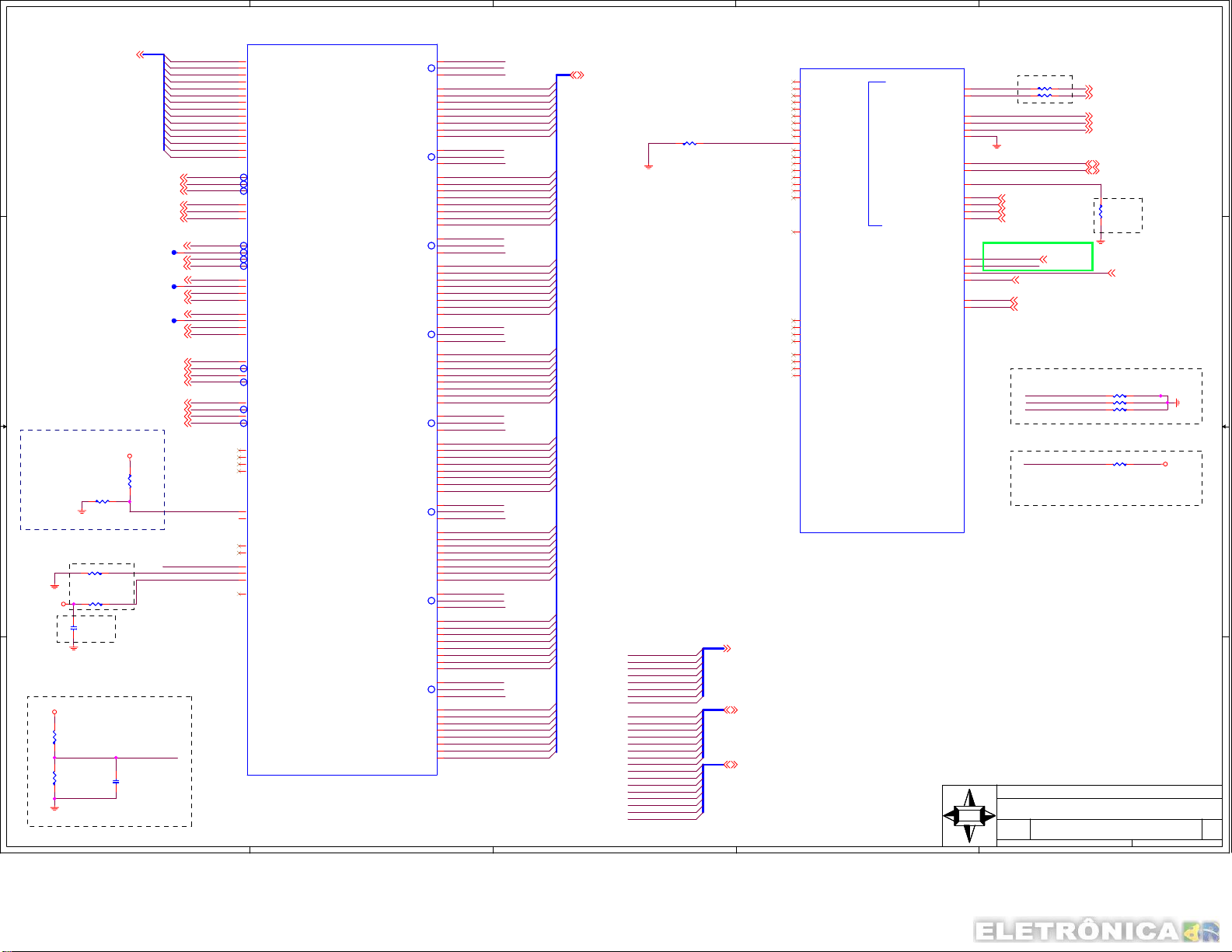

A

PINEVIEW_M

PINEVIEW_M

CPU1B

M_A_A[14:0]5,6,7

4 4

3 3

M_CLK_DDR06

M_CLK_DDR#06

M_CLK_DDR16

M_CLK_DDR#16

M_CLK_DDR35

M_CLK_DDR#35

M_CLK_DDR45

[Fuqun] PT-M ES1-->1.8

ES2-->TBD

R156 X_0R/4R156 X_0R/4

2 2

R151 80.6R1%4R151 80.6R1%4

+1_8VDIMM

R150

R150

1K1%4

1K1%4

R152

R152

1K1%4

1K1%4

R153 80.6R1%4R153 80.6R1%4

C264

C264

0.01u16X4

0.01u16X4

as close as

PVN

+1_8VDIMM

1 1

[Fuqun] Change R328/R331 from 10K to 1K in 0A

M_CLK_DDR#45

+1_8VDIMM

Within 500mil of NPV

as close as

PVN

Trace : 10 mils

SM_VREF

C271

C271

0.1u10X4

0.1u10X4

A

M_A_WE#5,6,7

M_A_CAS#5,6,7

M_A_RAS#5,6,7

R155

R155

10K/4

10K/4

M_A_BS05,6,7

M_A_BS15,6,7

M_A_BS25,6,7

M_CS#06,7

T23T23

M_CS#25,7

M_CS#35,7

M_CKE06,7

T24T24

M_CKE25,7

M_CKE35,7

M_ODT06,7

T4T4

M_ODT25,7

M_ODT35,7

CPU_VSS_AB4

SM_VREF

DDR_RPD

DDR_RPU

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_CS#1

M_CKE1

M_ODT1

Trace : 8 mils

AH19

AJ18

AK18

AK16

AJ14

AH14

AK14

AJ12

AH13

AK12

AK20

AH12

AJ11

AJ24

AJ10

AK22

AJ22

AK21

AJ20

AH20

AK11

AH22

AK25

AJ21

AJ25

AH10

AK10

AK24

AH26

AH24

AK27

AG15

AF15

AD13

AC13

AC15

AD15

AF13

AG13

AD17

AC17

AB15

AB17

AB11

AB13

AL28

AK28

AJ26

AK29

AH9

AJ8

AB4

AK8

CPU1B

DDR_A_MA_0

DDR_A_MA_1

DDR_A_MA_2

DDR_A_MA_3

DDR_A_MA_4

DDR_A_MA_5

DDR_A_MA_6

DDR_A_MA_7

DDR_A_MA_8

DDR_A_MA_9

DDR_A_MA_10

DDR_A_MA_11

DDR_A_MA_12

DDR_A_MA_13

DDR_A_MA_14

DDR_A_WEB

DDR_A_CASB

DDR_A_RASB

DDR_A_BS_0

DDR_A_BS_1

DDR_A_BS_2

DDR_A_CSB_0

DDR_A_CSB_1

DDR_A_CSB_2

DDR_A_CSB_3

DDR_A_CKE_0

DDR_A_CKE_1

DDR_A_CKE_2

DDR_A_CKE_3

DDR_A_ODT_0

DDR_A_ODT_1

DDR_A_ODT_2

DDR_A_ODT_3

DDR_A_CK_0

DDR_A_CKB_0

DDR_A_CK_1

DDR_A_CKB_1

DDR_A_CK_3

DDR_A_CKB_3

DDR_A_CK_4

DDR_A_CKB_4

RSVD_AD17

RSVD_AC17

RSVD_AB15

RSVD_AB17

VSS

RSVD

RSVD_TP

RSVD_TP

DDR_VREF

DDR_RPD

DDR_RPU

RSVD

PNV

PNV

?

?

REV = 1.1

REV = 1.1

DDR_A

DDR_A

B

DDR_A_DQS_0

DDR_A_DQSB_0

DDR_A_DM_0

DDR_A_DQ_0

DDR_A_DQ_1

DDR_A_DQ_2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_DQ_5

DDR_A_DQ_6

DDR_A_DQ_7

DDR_A_DQS_1

DDR_A_DQSB_1

DDR_A_DM_1

DDR_A_DQ_8

DDR_A_DQ_9

DDR_A_DQ_10

DDR_A_DQ_11

DDR_A_DQ_12

DDR_A_DQ_13

DDR_A_DQ_14

DDR_A_DQ_15

DDR_A_DQS_2

DDR_A_DQSB_2

DDR_A_DM_2

DDR_A_DQ_16

DDR_A_DQ_17

DDR_A_DQ_18

DDR_A_DQ_19

DDR_A_DQ_20

DDR_A_DQ_21

DDR_A_DQ_22

DDR_A_DQ_23

DDR_A_DQS_3

DDR_A_DQSB_3

DDR_A_DM_3

DDR_A_DQ_24

DDR_A_DQ_25

DDR_A_DQ_26

DDR_A_DQ_27

DDR_A_DQ_28

DDR_A_DQ_29

DDR_A_DQ_30

DDR_A_DQ_31

DDR_A_DQS_4

DDR_A_DQSB_4

DDR_A_DM_4

DDR_A_DQ_32

DDR_A_DQ_33

DDR_A_DQ_34

DDR_A_DQ_35

DDR_A_DQ_36

DDR_A_DQ_37

DDR_A_DQ_38

DDR_A_DQ_39

DDR_A_DQS_5

DDR_A_DQSB_5

DDR_A_DM_5

DDR_A_DQ_40

DDR_A_DQ_41

DDR_A_DQ_42

DDR_A_DQ_43

DDR_A_DQ_44

DDR_A_DQ_45

DDR_A_DQ_46

DDR_A_DQ_47

DDR_A_DQS_6

DDR_A_DQSB_6

DDR_A_DM_6

DDR_A_DQ_48

DDR_A_DQ_49

DDR_A_DQ_50

DDR_A_DQ_51

DDR_A_DQ_52

DDR_A_DQ_53

DDR_A_DQ_54

DDR_A_DQ_55

DDR_A_DQS_7

DDR_A_DQSB_7

DDR_A_DM_7

DDR_A_DQ_56

DDR_A_DQ_57

DDR_A_DQ_58

DDR_A_DQ_59

DDR_A_DQ_60

DDR_A_DQ_61

DDR_A_DQ_62

DDR_A_DQ_63

B

C

M_A_DQS0

AD3

M_A_DQS#0

AD2

M_A_DM0

AD4

M_A_DQ0

AC4

M_A_DQ1

AC1

M_A_DQ2

AF4

M_A_DQ3

AG2

M_A_DQ4

AB2

M_A_DQ5

AB3

M_A_DQ6

AE2

M_A_DQ7

AE3

M_A_DQS1

AB8

M_A_DQS#1

AD7

M_A_DM1

AA9

M_A_DQ8

AB6

M_A_DQ9

AB7

M_A_DQ10

AE5

M_A_DQ11

AG5

M_A_DQ12

AA5

M_A_DQ13

AB5

M_A_DQ14

AB9

M_A_DQ15

AD6

M_A_DQS2

AD8

M_A_DQS#2

AD10

M_A_DM2

AE8

M_A_DQ16

AG8

M_A_DQ17

AG7

M_A_DQ18

AF10

M_A_DQ19

AG11

M_A_DQ20

AF7

M_A_DQ21

AF8

M_A_DQ22

AD11

M_A_DQ23

AE10

M_A_DQS3

AK5

M_A_DQS#3

AK3

M_A_DM3

AJ3

M_A_DQ24

AH1

M_A_DQ25

AJ2

M_A_DQ26

AK6

M_A_DQ27

AJ7

M_A_DQ28

AF3

M_A_DQ29

AH2

M_A_DQ30

AL5

M_A_DQ31

AJ6

M_A_DQS4

AG22

M_A_DQS#4

AG21

M_A_DM4

AD19

M_A_DQ32

AE19

M_A_DQ33

AG19

M_A_DQ34

AF22

M_A_DQ35

AD22

M_A_DQ36

AG17

M_A_DQ37

AF19

M_A_DQ38

AE21

M_A_DQ39

AD21

M_A_DQS5

AE26

M_A_DQS#5

AG27

M_A_DM5

AJ27

M_A_DQ40

AE24

M_A_DQ41

AG25

M_A_DQ42

AD25

M_A_DQ43

AD24

M_A_DQ44

AC22

M_A_DQ45

AG24

M_A_DQ46

AD27

M_A_DQ47

AE27

M_A_DQS6

AE30

M_A_DQS#6

AF29

M_A_DM6

AF30

M_A_DQ48

AG31

M_A_DQ49

AG30

M_A_DQ50

AD30

M_A_DQ51

AD29

M_A_DQ52

AJ30

M_A_DQ53

AJ29

M_A_DQ54

AE29

M_A_DQ55

AD28

M_A_DQS7

AB27

M_A_DQS#7

AA27

M_A_DM7

AB26

M_A_DQ56

AA24

M_A_DQ57

AB25

M_A_DQ58

W24

M_A_DQ59

W22

M_A_DQ60

AB24

M_A_DQ61

AB23

M_A_DQ62

AA23

M_A_DQ63

W27

2 OF 6?

2 OF 6?

M_A_DQ[63:0] 5,6

[Fuqun] Remove all TP except 09 0A

R166 1K/4R166 1K/4

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

C

XDP_RSVD_09

M_A_DM[7:0] 5,6

M_A_DQS[7:0] 5,6

M_A_DQS#[7:0] 5,6

AA21

W21

D12

A7

D6

C5

C7

C6

D8

B7

A9

D9

C8

B8

C10

D10

B11

B10

B12

C11

L11

AA7

AA6

R5

R6

T21

V21

CPU1C

CPU1C

XDP_RSVD_00

XDP_RSVD_01

XDP_RSVD_02

XDP_RSVD_03

XDP_RSVD_04

XDP_RSVD_05

XDP_RSVD_06

XDP_RSVD_07

XDP_RSVD_08

XDP_RSVD_09

XDP_RSVD_10

XDP_RSVD_11

XDP_RSVD_12

XDP_RSVD_13

XDP_RSVD_14

XDP_RSVD_15

XDP_RSVD_16

XDP_RSVD_17

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

PNV

PNV

D

PINEVIEW_M

PINEVIEW_M

REV = 1.1

REV = 1.1

PM_EXTTS#_1/DPRSLPVR

MISC VGA

MISC VGA

? 3 OF 6

? 3 OF 6

D

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_IRTN

CRT_DDC_DATA

CRT_DDC_CLK

DAC_IREF

DPL_REFCLKINP

DPL_REFCLKINN

DPL_REFSSCLKINP

DPL_REFSSCLKINN

PM_EXTTS#_0

PWROK

RSTINB

HPL_CLKINN

HPL_CLKINP

E

?

?

Within 750mil of NPV

HSYNC

M30

VSYNC

M29

VGA_R

N31

VGA_G

P30

VGA_B

P29

N30

L31

L30

DACREFSET

P28

Y30

CLK_DOT96 12

Y29

CLK_DOT96# 12

AA30

CLK_GFX_REFCLKP 12

AA31

CLK_GFX_REFCLKN 12

Fast C4/C4E Exit

PM_DPRSLPVR

K29

PM_EXTTS#0

J30

L5

AA3

W8

W9

R162 10R/4R162 10R/4

R160 10R/4R160 10R/4

PM_DPRSLPVR 10,26

PNV_RST# 10

CLK_MCH_BCLK# 12

CLK_MCH_BCLK 12

Within 500mil of NPV

POWER must not glitch,

even if RSMRST# is low.

VGA_R

VGA_G

VGA_B

PM_EXTTS#0

HSYNC_3V 8

VSYNC_3V 8

VGA_R 8

VGA_G 8

VGA_B 8

SXGA+ 1400x1050

60Hz

VGA_DATA 8

VGA_CLK 8

R68

R68

665R1%4

665R1%4

Within 250mil of NPV

CHIP_PWRGD 10,13

R161 150R1%4R161 150R1%4

R158 150R1%4R158 150R1%4

R159 150R1%4R159 150R1%4

R82 10K/4R82 10K/4

PM_EXTTS#: memory thermal throttling

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N01x

MS-N01x

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Tuesday, June 02, 2009

Tuesday, June 02, 2009

Tuesday, June 02, 2009

MS-N01x

PNV (DDR /VGA/ MISC)

PNV (DDR /VGA/ MISC)

PNV (DDR /VGA/ MISC)

E

+3VRUN

Sheet ofDate:

335

Sheet ofDate:

335

Sheet ofDate:

335

0A

0A

0A

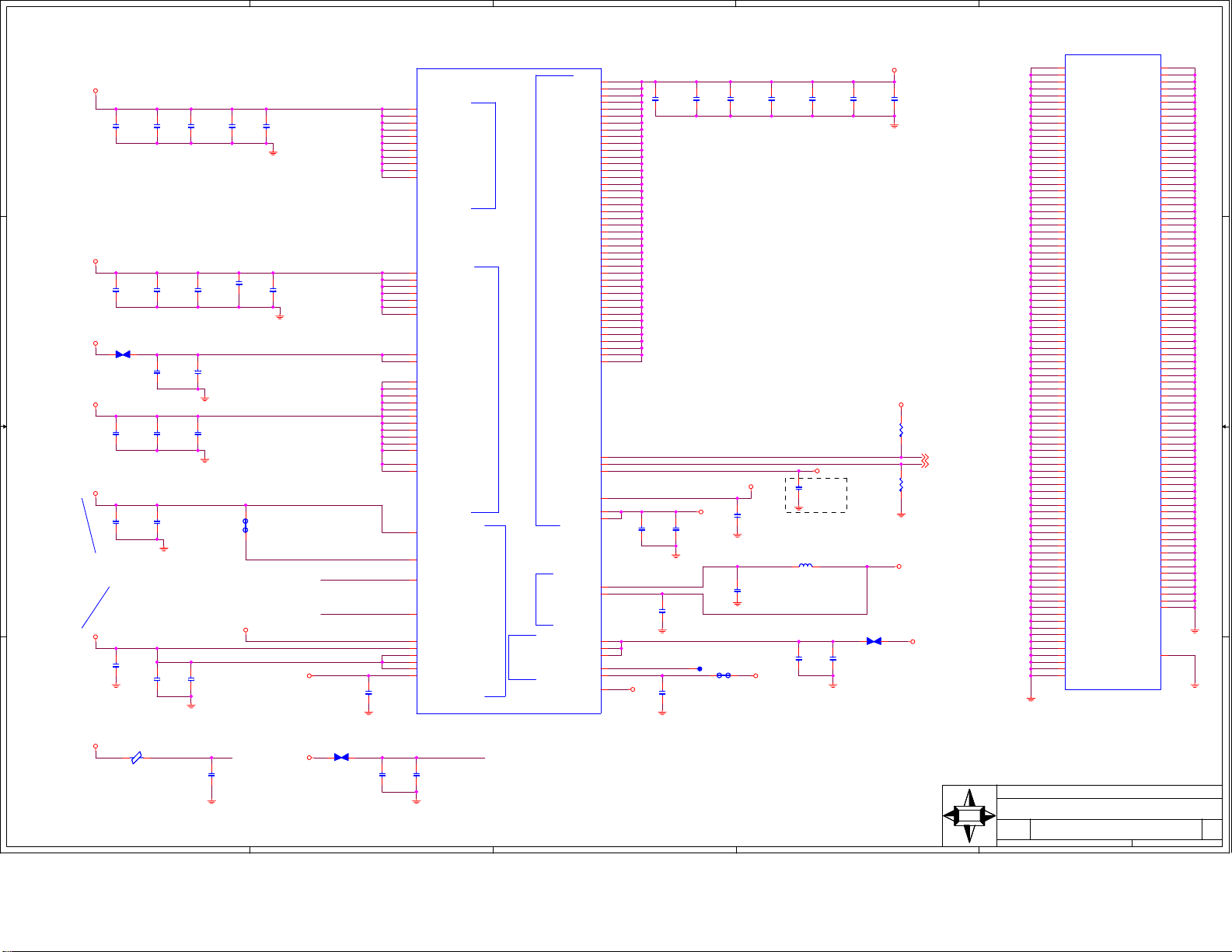

5

4

3

2

1

[Fuqun] CHECK LIST:

1uf--7

2.2uf--1

+0_89VGFX

D D

[Fuqun] CHECK LIST:

2.2uf--4

+1_8VDIMM

C C

B B

+1_8VDIMM

+1P05V

+1P05V

1.05V, 0.33A

0.89V, 1.38A

sustained current, 1.05A

C112

C112

C110

C110

2.2u6.3Y6

2.2u6.3Y6

1u6.3Y4

1u6.3Y4

1.8V, 2.27A

C267

C267

C265

C265

2.2u6.3Y6

2.2u6.3Y6

2.2u6.3Y6

2.2u6.3Y6

[Fuqun] CHECK LIST:

22uf--1

VCCCK_DDR

CP11

CP11

X_COPPER

X_COPPER

C263

C263

10u6.3X8

10u6.3X8

C119

C119

C106

C106

10u6.3X8

10u6.3X8

4.7u6.3X8

4.7u6.3X8

[Fuqun] CHECK LIST:

1uf--2

C100

C100

C99

C99

X_0.1u10X4

X_0.1u10X4

0.1u10X4

0.1u10X4

C111

C111

1u6.3Y4

1u6.3Y4

C266

C266

2.2u6.3Y6

2.2u6.3Y6

C118

C118

1u6.3Y4

1u6.3Y4

C270

C270

0.1u10X4

0.1u10X4

C105

C105

C107

C107

1u6.3Y4

1u6.3Y4

1u6.3Y4

1u6.3Y4

C268

C268

C269

C269

2.2u6.3Y6

2.2u6.3Y6

2.2u6.3Y6

2.2u6.3Y6

1.05V, 1.32A

R69

R69

X_NC

X_NC

1.05V, 0.048A

VCCD_HMPLL

VCCSFR_AB_DPL

W14

W16

W18

W19

AK13

AK19

AL11

AL16

AL21

AL25

W10

W11

AA10

AA11

AA19

AC31

T13

T14

T16

T18

T19

V13

V19

AK9

AK7

AL7

U10

U5

U6

U7

U8

U9

V2

V3

V4

V11

1.8V, 0.154A

VCCACRTDAC

3.3V, 0.006A

CP12

CP12

X_COPPER

X_COPPER C275

C101

C101

X_1u6.3Y4

X_1u6.3Y4

VCCACRTDAC

+3VRUN

C280

C280

1u6.3Y4

1u6.3Y4

+1P05V

+1_8VRUN

+1P05V

C102

C102

1u6.3Y4

1u6.3Y4

C294

C294

1u6.3Y4

1u6.3Y4

A A

+1_8VRUN

L16

L16

600L200mA-500-RH

600L200mA-500-RH

5

C129

C129

X_1u6.3Y4

X_1u6.3Y4

4

C274

C274

1u6.3Y4

1u6.3Y4

T30

T31

J31

C3

B2

C2

A21

PNV

PNV

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCGFX

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCCK_DDR

VCCCK_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCACK_DDR

VCCACK_DDR

VCCD_AB_DPL

VCCD_HMPLL

VCCSFR_AB_DPL

VCCACRTDAC

VCC_GIO

VCCRING_EAST

VCCRING_WEST

VCCRING_WEST

VCCRING_WEST

VCC_LGI_VID

VCCSFR_AB_DPL

C275

X_1u6.3Y4

X_1u6.3Y4

PINEVIEW_M

PINEVIEW_M

REV = 1.1

REV = 1.1

GFX/MCH

GFX/MCH

DDR

DDR

EXP\CRT\PLL

EXP\CRT\PLL

CPU

CPU

POWER

POWER

LVDS

LVDS

DMI

DMI

VCCSFR_DMIHMPLL

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCSENSE

VSSSENSE

VCCA

VCC

VCCP

VCCP

VCCALVD

VCCDLVD

VCCA_DMI

VCCA_DMI

VCCA_DMI

RSVD

VCCP

5 OF 6?

5 OF 6?

?CPU1E

?CPU1E

A23

A25

A27

B23

B24

B25

B26

B27

C24

C26

D23

D24

D26

D28

E22

E24

E27

F21

F22

F25

G19

G21

G24

H17

H19

H22

H24

J17

J19

J21

J22

K15

K17

K21

L14

L16

L19

L21

N14

N16

N19

N21

C29

B29

Y2

D4

B4

B3

V30

W31

T1

T2

T3

P2

AA1

E2

1.5V, 0.08A

C289

C289

1u6.3Y4

1u6.3Y4

1.8V, 0.06A

1.05V, 0.48A

VCCAPLL_DMI

+1P05V

3

1.1V, 3.5A

C296

C296

1u6.3Y4

1u6.3Y4

VCCSENSE

VSSSENSE

C128

C128

1u6.3Y4

1u6.3Y4

C96

C96

1u6.3Y4

1u6.3Y4

C279

C279

1u6.3Y4

1u6.3Y4

(C4 state,0.51A)

C297

C297

C115

1u6.3Y4

1u6.3Y4

C115

1u6.3Y4

1u6.3Y4

C122

C122

1u6.3Y4

1u6.3Y4

+1P05V=> 2.13A

+0_89VGFX=> 1.38A

+1_5VRUN=>0.08A

+1_8VDIMM=> 2.27A

+1_8VRUN=> 0.318A

+3VRUN=> 0.006A

[Fuqun] Change R177/R164 from 10ohm to 100ohm in 0A?

+1P05V

T25T25

R157 X_NCR157 X_NC

1.8V, 0.104A

+1P05V

C125

C125

X_0.01u16X4

X_0.01u16X4

C278

C278

10u6.3X8

10u6.3X8

+1_8VRUN

L15 0.1u300mAL15 0.1u300mA

VCCA_DMI

C281

C281

0.01u16X4

0.01u16X4

Place CAP

close to PNV

C108

C108

1u6.3Y4

1u6.3Y4

[Fuqun] CHECK LIST:

1uf--4

C113

C113

C121

C121

1u6.3Y4

1u6.3Y4

1u6.3Y4

1u6.3Y4

+1_5VRUN

CP6

CP6

X_COPPER

X_COPPER

C109

C109

1u6.3Y4

1u6.3Y4

2

V_CORE

C292

C292

10u6.3X8

10u6.3X8

V_CORE

R92

R92

10R/4

10R/4

VCCSENSE 26

VSSSENSE 26

R88

R88

10R/4

10R/4

[Fuqun] CHECK LIST:

1uf--2

22uf--1

+1_8VRUN

+1P05V

PINEVIEW_M

PINEVIEW_M

CPU1F

CPU1F

REV = 1.1

VSS

VSS

VSS

RSVD_NCTF

A3

RSVD_NCTF

RSVD_NCTF

A4

RSVD_NCTF

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RSVD_NCTF

VSS

VSS

RSVD_NCTF

RSVD_NCTF

VSS

RSVD_NCTF

RSVD_NCTF

VSS

VSS

RSVD_NCTF

VSS

RSVD_NCTF

RSVD_NCTF

RSVD_NCTF

VSS

VSS

VSS

VSS

VSS

RSVD_NCTF

RSVD_NCTF

B5

VSS

B9

VSS

RSVD_NCTF

VSS

VSS

VSS

VSS

RSVD_NCTF

VSS

E1

RSVD_NCTF

VSS

VSS

VSS

VSS

E8

VSS

VSS

VSS

PNV

PNV

PNV Power

PNV Power

PNV Power

REV = 1.1

MS-N01x

MS-N01x

MS-N01x

1

GND

GND

? 6 OF 6

? 6 OF 6

A11

A16

A19

A29

A30

AA13

AA14

AA16

AA18

AA2

AA22

AA25

AA26

AA29

AA8

AB19

AB21

AB28

AB29

AB30

AC10

AC11

AC19

AC2

AC21

AC28

AC30

AD26

AD5

AE1

AE11

AE13

AE15

AE17

AE22

AE31

AF11

AF17

AF21

AF24

AF28

AG10

AG3

AH18

AH23

AH28

AH4

AH6

AH8

AJ1

AJ16

AJ31

AK1

AK2

AK23

AK30

AK31

AL13

AL19

AL2

AL23

AL29

AL3

AL30

AL9

B13

B16

B19

B22

B30

B31

C1

C12

C21

C22

C25

C31

D22

E10

E19

E21

E25

F17

F19

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Monday, June 08, 2009

Monday, June 08, 2009

Monday, June 08, 2009

?

?

F24

VSS

F28

VSS

F4

VSS

G15

VSS

G17

VSS

G22

VSS

G27

VSS

G31

VSS

H11

VSS

H15

VSS

H2

VSS

H21

VSS

H25

VSS

H8

VSS

J11

VSS

J13

VSS

J15

VSS

J4

VSS

K11

VSS

K13

VSS

K19

VSS

K26

VSS

K27

VSS

K28

VSS

K30

VSS

K4

VSS

K8

VSS

L1

VSS

L13

VSS

L18

VSS

L22

VSS

L24

VSS

L25

VSS

L29

VSS

M28

VSS

M3

VSS

N1

VSS

N13

VSS

N18

VSS

N24

VSS

N25

VSS

N28

VSS

N4

VSS

N5

VSS

N8

VSS

P13

VSS

P14

VSS

P16

VSS

P18

VSS

P19

VSS

P21

VSS

P3

VSS

P4

VSS

R25

VSS

R7

VSS

R8

VSS

T11

VSS

U22

VSS

U23

VSS

U24

VSS

U27

VSS

V14

VSS

V16

VSS

V18

VSS

V28

VSS

V29

VSS

W13

VSS

W2

VSS

W23

VSS

W25

VSS

W26

VSS

W28

VSS

W30

VSS

W4

VSS

W5

VSS

W6

VSS

W7

VSS

Y28

VSS

Y3

VSS

Y4

VSS

T29

VSS

Sheet ofDate:

435

Sheet ofDate:

435

Sheet ofDate:

435

0A

0A

0A

A

B

C

D

E

DIMM1A

M_A_DQ[63:0]3,6

1 1

2 2

3 3

4 4

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

DIMM1_SA1

DIMM1_SA0

DIMM1A

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DIMM-200P_BLACK-1

DIMM-200P_BLACK-1

R140 10K/4R140 10K/4

R138 10K/4R138 10K/4

A10/AP

A16_BA2

BA0

BA1

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

A11

A12

A13

A14

A15

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

85

107

106

110

115

30

32

164

166

79

80

113

108

109

198

200

197

195

114

119

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

+3VRUN

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

DIMM1_SA0

DIMM1_SA1

RUN_SMBCLK

RUN_SMBDATA

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_A[14:0] 3,6,7

M_A_BS2 3,6,7

M_A_BS0 3,6,7

M_A_BS1 3,6,7

M_CS#2 3,7

M_CS#3 3,7

M_CLK_DDR3 3

M_CLK_DDR#3 3

M_CLK_DDR4 3

M_CLK_DDR#4 3

M_CKE2 3,7

M_CKE3 3,7

M_A_CAS# 3,6,7

M_A_RAS# 3,6,7

M_A_WE# 3,6,7

RUN_SMBCLK 10,12

RUN_SMBDATA 10,12

M_ODT2 3,7

M_ODT3 3,7

M_A_DM[7:0] 3,6

M_A_DQS[7:0] 3,6

M_A_DQS#[7:0] 3,6

(H=5.2mm)

N13-2000180-K06

Bottom

[Fuqun] CHECK LIST:

0.1uf--1

2.2uf--1

+1_8VDIMM

R27

R27

1K1%4

1K1%4

R25

R25

1K1%4

1K1%4

as close as

SO-DIMM

SMDDR_VREF

SMDDR_VREF

C39

C39

0.1u10X4

0.1u10X4

+3VRUN

SMDDR_VREF

C217

C217

C216

C216

X_0.1u10X4

X_0.1u10X4

Trace : 10 mils

C214

C214

C223

C223

2.2u6.3Y6

2.2u6.3Y6

0.1u10X4

0.1u10X4

+1_8VDIMM

+1_8VDIMM

+1_8VDIMM

DIMM1B

DIMM1B

112

VDD1

111

VDD2

117

VDD3

96

VDD4

95

VDD5

118

VDD6

81

VDD7

82

VDD8

0.1u10X4

0.1u10X4

Layout note: Place capacitors between and

near DDR connector if possible.

C215

C215

0.1u10X4

0.1u10X4

C250

C250

X_2.2u6.3Y6

X_2.2u6.3Y6

87

103

88

104

199

83

120

50

69

163

203

204

MEC1

MEC2

47

133

183

77

12

48

184

78

71

72

121

122

196

193

C248

C248

0.1u10X4

0.1u10X4

C212

C212

2.2u6.3Y6

2.2u6.3Y6

VDD9

VDD10

VDD11

VDD12

VDDSPD

NC1

NC2

NC3

NC4

NCTEST

1

VREF

GND

GND

MEC1

MEC2

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

8

VSS15

DIMM-200P_BLACK-1

DIMM-200P_BLACK-1

C219

C219

X_0.1u10X4

X_0.1u10X4

C213

C213

2.2u6.3Y6

2.2u6.3Y6

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

C246

C246

0.1u10X4

0.1u10X4

C251

C251

X_2.2u6.3Y6

X_2.2u6.3Y6

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

[Fuqun] CHECK LIST:

0.1uf--4

2.2uf--5

ADDRESS: 001

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

0xA2

MSI

MSI

MSI

A

B

C

D

MICRO-STAR INT'L CO.,LTD

MS-N01x

MS-N01x

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

B

B

B

Date:

Tuesday, June 02, 2009

Date:

Tuesday, June 02, 2009

Date:

Tuesday, June 02, 2009

MS-N01x

DDR SODIMM1

DDR SODIMM1

DDR SODIMM1

Sheet of

Sheet of

Sheet of

E

535

535

535

0A

0A

0A

A

M_A_DQ[63:0]

M_A_DQ[63:0]3,5

M_A_A[13:0]

M_A_BS[2:0]

M_A_BS[2:0]3,5,7

U20

U20

M_A_RAS#

M_A_CAS#

M_A_WE#

M_CS#0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BS0

M_A_BS1

M_A_BS2

M_CLK_DDR0

M_CLK_DDR#0

M_CKE0

A_DQ0

A_DQ1

A_DQ2

A_DQ3

A_DQ4

A_DQ5

A_DQ6

A_DQ7

A_DQS0

A_DQS#0

A_DM0

M_A_RAS#

M_A_CAS#

M_A_WE#

M_CS#0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BS0

M_A_BS1

M_A_BS2

M_CLK_DDR1

M_CLK_DDR#1

M_CKE0

A_DQ32

A_DQ33

A_DQ34

A_DQ35

A_DQ36

A_DQ37

A_DQ38

A_DQ39

A_DQS4

A_DQS#4

A_DM4

F7

RAS#

G7

CAS#

F3

WE#

G8

CS#

H8

A0

H3

A1

H7

A2

J2

A3

J8

A4

J3

A5

J7

A6

K2

A7

K8

A8

K3

A9

H2

A10/AP

K7

A11

L2

A12

L8

A13

G2

BA0

G3

BA1

G1

BA2

E8

CK

F8

CK#

F2

CKE

C8

DQ0

C2

DQ1

D7

DQ2

D3

DQ3

D1

DQ4

D9

DQ5

B1

DQ6

B9

DQ7

B7

DQS

A8

DQS#

B3

RDQS/DM

A2

NU/RDQS#

K4T1G084QQ-HCF7-HF

K4T1G084QQ-HCF7-HF

U18

U18

F7

RAS#

G7

CAS#

F3

WE#

G8

CS#

H8

A0

H3

A1

H7

A2

J2

A3

J8

A4

J3

A5

J7

A6

K2

A7

K8

A8

K3

A9

H2

A10/AP

K7

A11

L2

A12

L8

A13

G2

BA0

G3

BA1

G1

BA2

E8

CK

F8

CK#

F2

CKE

C8

DQ0

C2

DQ1

D7

DQ2

D3

DQ3

D1

DQ4

D9

DQ5

B1

DQ6

B9

DQ7

B7

DQS

A8

DQS#

B3

RDQS/DM

A2

NU/RDQS#

K4T1G084QQ-HCF7-HF

K4T1G084QQ-HCF7-HF

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSDL

VREF

ODT0

NC1

NC2

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSDL

VREF

ODT0

NC1

NC2

M_A_RAS#3,5,7

M_A_CAS#3,5,7 M_A_CAS#3,5,7

M_A_WE#3,5,7

M_CS#03,7

1 1

M_CLK_DDR03

M_CLK_DDR#03

M_CKE03,7

M_A_RAS#3,5,7

M_A_CAS#3,5,7 M_A_CAS#3,5,7

M_A_WE#3,5,7

M_CS#03,7

2 2

M_CLK_DDR13

M_CLK_DDR#13

M_CKE03,7

M_A_DM[7:0]3,5

M_A_DQS[7:0]3,5M_A_A[13:0]3,5,7

M_A_DQS#[7:0]3,5

A1

+1_8VDIMM

E9

H9

L1

A9

C1

C3

C7

C9

E1

A3

J1

E3

K9

A7

B2

B8

D2

D8

E7

E2

F9

L3

L7

A1

E9

H9

L1

A9

C1

C3

C7

C9

E1

A3

J1

E3

K9

A7

B2

B8

D2

D8

E7

E2

F9

L3

L7

M_ODT0

M_ODT0

SMDDR_VREF

+1_8VDIMM

SMDDR_VREF

+1_8VDIMM

C202

C202

1u6.3Y4

1u6.3Y4

M_ODT0 3,7

+1_8VDIMM

C221

C221

1u6.3Y4

1u6.3Y4

M_ODT0 3,7

SMDDR_VREF

C42

C42

0.1u10X4

0.1u10X4

Trace : 10 mils

SMDDR_VREF

C41

C41

0.1u10X4

0.1u10X4

Trace : 10 mils

M_A_DM[7:0]

M_A_DQS[7:0]

M_A_DQS#[7:0]

C40

C40

2.2u6.3Y6

2.2u6.3Y6

C44

C44

2.2u6.3Y6

2.2u6.3Y6

B

U4

U4

M_A_RAS#

M_A_CAS#

M_A_WE#

M_CS#0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BS0

M_A_BS1

M_A_BS2

M_CLK_DDR0

M_CLK_DDR#0

M_CKE0

A_DQ8

A_DQ9

A_DQ10

A_DQ11

A_DQ12

A_DQ13

A_DQ14

A_DQ15

A_DQS1

A_DQS#1

A_DM1

M_A_RAS#

M_A_CAS#

M_A_WE#

M_CS#0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BS0

M_A_BS1

M_A_BS2

M_CLK_DDR1

M_CLK_DDR#1

M_CKE0

A_DQ40

A_DQ41

A_DQ42

A_DQ43

A_DQ44

A_DQ45

A_DQ46

A_DQ47

A_DQS5

A_DQS#5

A_DM5

F7

G7

F3

G8

H8

H3

H7

J2

J8

J3

J7

K2

K8

K3

H2

K7

L2

L8

G2

G3

G1

E8

F8

F2

C8

C2

D7

D3

D1

D9

B1

B9

B7

A8

B3

A2

F7

G7

F3

G8

H8

H3

H7

J2

J8

J3

J7

K2

K8

K3

H2

K7

L2

L8

G2

G3

G1

E8

F8

F2

C8

C2

D7

D3

D1

D9

B1

B9

B7

A8

B3

A2

M_A_RAS#3,5,7

M_A_CAS#3,5,7

M_A_WE#3,5,7

M_CS#03,7

M_CLK_DDR03

M_CLK_DDR#03

M_CKE03,7

M_A_RAS#3,5,7

M_A_CAS#3,5,7

M_A_WE#3,5,7

M_CS#03,7

M_CLK_DDR13

M_CLK_DDR#13

M_CKE03,7

RAS#

CAS#

WE#

CS#

A0

VDDQ

A1

VDDQ

A2

VDDQ

A3

VDDQ

A4

VDDQ

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

BA0

BA1

BA2

CK

CK#

CKE

VSSDL

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQS

DQS#

RDQS/DM

NU/RDQS#

K4T1G084QQ-HCF7-HF

K4T1G084QQ-HCF7-HF

U6

U6

RAS#

CAS#

WE#

CS#

A0

VDDQ

A1

VDDQ

A2

VDDQ

A3

VDDQ

A4

VDDQ

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

BA0

BA1

BA2

CK

CK#

CKE

VSSDL

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQS

DQS#

RDQS/DM

NU/RDQS#

K4T1G084QQ-HCF7-HF

K4T1G084QQ-HCF7-HF

A1

VDD

E9

VDD

H9

VDD

L1

VDD

A9

C1

C3

C7

C9

E1

VDDL

A3

VSS

J1

VSS

E3

VSS

K9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

E2

VREF

M_ODT0

F9

ODT0

L3

NC1

L7

NC2

A1

VDD

E9

VDD

H9

VDD

L1

VDD

A9

C1

C3

C7

C9

E1

VDDL

A3

VSS

J1

VSS

E3

VSS

K9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

E2

VREF

M_ODT0

F9

ODT0

L3

NC1

L7

NC2

+1_8VDIMM

1u6.3Y4

1u6.3Y4

SMDDR_VREF

M_ODT0 3,7

+1_8VDIMM

1u6.3Y4

1u6.3Y4

SMDDR_VREF

M_ODT0 3,7

C193

C193

C207

C207

+1_8VDIMM

+1_8VDIMM

C

U19

U19

M_A_RAS#

M_A_RAS#3,5,7

M_A_WE#3,5,7

M_CS#03,7

M_CLK_DDR03

M_CLK_DDR#03

M_CKE03,7

M_A_RAS#3,5,7

M_A_WE#3,5,7

M_CS#03,7

M_CLK_DDR13

M_CLK_DDR#13

M_CKE03,7

F7

RAS#

G7

CAS#

F3

WE#

G8

CS#

H8

A0

H3

A1

H7

A2

J2

A3

J8

A4

J3

A5

J7

A6

K2

A7

K8

A8

K3

A9

H2

A10/AP

K7

A11

L2

A12

L8

A13

G2

BA0

G3

BA1

G1

BA2

E8

CK

F8

CK#

F2

CKE

C8

DQ0

C2

DQ1

D7

DQ2

D3

DQ3

D1

DQ4

D9

DQ5

B1

DQ6

B9

DQ7

B7

DQS

A8

DQS#

B3

RDQS/DM

A2

NU/RDQS#

K4T1G084QQ-HCF7-HF

K4T1G084QQ-HCF7-HF

U17

U17

F7

RAS#

G7

CAS#

F3

WE#

G8

CS#

H8

A0

H3

A1

H7

A2

J2

A3

J8

A4

J3

A5

J7

A6

K2

A7

K8

A8

K3

A9

H2

A10/AP

K7

A11

L2

A12

L8

A13

G2

BA0

G3

BA1

G1

BA2

E8

CK

F8

CK#

F2

CKE

C8

DQ0

C2

DQ1

D7

DQ2

D3

DQ3

D1

DQ4

D9

DQ5

B1

DQ6

B9

DQ7

B7

DQS

A8

DQS#

B3

RDQS/DM

A2

NU/RDQS#

K4T1G084QQ-HCF7-HF

K4T1G084QQ-HCF7-HF

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSDL

VREF

ODT0

NC1

NC2

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSDL

VREF

ODT0

NC1

NC2

M_A_CAS#

M_A_WE#

M_CS#0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BS0

M_A_BS1

M_A_BS2

M_CLK_DDR0

M_CLK_DDR#0

M_CKE0

A_DQ16

A_DQ17

A_DQ18

A_DQ19

A_DQ20

A_DQ21

A_DQ22

A_DQ23

A_DQS2

A_DQS#2

A_DM2

M_A_RAS#

M_A_CAS#

M_A_WE#

M_CS#0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BS0

M_A_BS1

M_A_BS2

M_CLK_DDR1

M_CLK_DDR#1

M_CKE0

A_DQ48

A_DQ49

A_DQ50

A_DQ51

A_DQ53

A_DQ54 A_DQ62

A_DQ55

A_DQS6

A_DQS#6

A_DM6

D

U5

U5

A1

+1_8VDIMM

E9

H9

L1

A9

C1

C3

C7

C9

E1

A3

J1

E3

K9

A7

B2

B8

D2

D8

E7

E2

F9

L3

L7

A1

E9

H9

L1

A9

C1

C3

C7

C9

E1

A3

J1

E3

K9

A7

B2

B8

D2

D8

E7

E2

F9

L3

L7

M_ODT0

M_ODT0

1u6.3Y4

1u6.3Y4

SMDDR_VREF

M_ODT0 3,7

+1_8VDIMM

1u6.3Y4

1u6.3Y4

SMDDR_VREF

M_ODT0 3,7

C192

C192

C194

C194

+1_8VDIMM

+1_8VDIMM

M_A_RAS#

M_A_CAS#

M_A_WE#

M_CS#0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BS0

M_A_BS1

M_A_BS2

M_CLK_DDR0

M_CLK_DDR#0

M_CKE0

A_DQ24

A_DQ25

A_DQ26

A_DQ27

A_DQ28

A_DQ29

A_DQ30

A_DQ31

A_DQS3

A_DQS#3

A_DM3

M_A_RAS#

M_A_CAS#

M_A_WE#

M_CS#0

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_BS0

M_A_BS1

M_A_BS2

M_CLK_DDR1

M_CLK_DDR#1

M_CKE0

A_DQ56

A_DQ57

A_DQ58

A_DQ59

A_DQ60A_DQ52

A_DQ61

A_DQ63

A_DQS7

A_DQS#7

A_DM7

F7

RAS#

G7

CAS#

F3

WE#

G8

CS#

H8

A0

H3

A1

H7

A2

J2

A3

J8

A4

J3

A5

J7

A6

K2

A7

K8

A8

K3

A9

H2

A10/AP

K7

A11

L2

A12

L8

A13

G2

BA0

G3

BA1

G1

BA2

E8

CK

F8

CK#

F2

CKE

C8

DQ0

C2

DQ1

D7

DQ2

D3

DQ3

D1

DQ4

D9

DQ5

B1

DQ6

B9

DQ7

B7

DQS

A8

DQS#

B3

RDQS/DM

A2

NU/RDQS#

K4T1G084QQ-HCF7-HF

K4T1G084QQ-HCF7-HF

U7

U7

F7

RAS#

G7

CAS#

F3

WE#

G8

CS#

H8

A0

H3

A1

H7

A2

J2

A3

J8

A4

J3

A5

J7

A6

K2

A7

K8

A8

K3

A9

H2

A10/AP

K7

A11

L2

A12

L8

A13

G2

BA0

G3

BA1

G1

BA2

E8

CK

F8

CK#

F2

CKE

C8

DQ0

C2

DQ1

D7

DQ2

D3

DQ3

D1

DQ4

D9

DQ5

B1

DQ6

B9

DQ7

B7

DQS

A8

DQS#

B3

RDQS/DM

A2

NU/RDQS#

K4T1G084QQ-HCF7-HF

K4T1G084QQ-HCF7-HF

M_A_RAS#3,5,7

M_A_CAS#3,5,7

M_A_WE#3,5,7

M_CS#03,7

M_CLK_DDR03

M_CLK_DDR#03

M_CKE03,7

M_A_RAS#3,5,7

M_A_CAS#3,5,7

M_A_WE#3,5,7

M_CS#03,7

M_CLK_DDR13

M_CLK_DDR#13

M_CKE03,7

E

A1

+1_8VDIMM

VDD

E9

VDD

H9

VDD

L1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E1

VDDL

A3

VSS

J1

VSS

E3

VSS

K9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSDL

E2

VREF

F9

ODT0

L3

NC1

L7

NC2

A1

VDD

E9

VDD

H9

VDD

L1

VDD

A9

VDDQ

C1

VDDQ

C3

VDDQ

C7

VDDQ

C9

VDDQ

E1

VDDL

A3

VSS

J1

VSS

E3

VSS

K9

VSS

A7

VSSQ

B2

VSSQ

B8

VSSQ

D2

VSSQ

D8

VSSQ

E7

VSSDL

E2

VREF

F9

ODT0

L3

NC1

L7

NC2

M_ODT0

M_ODT0

1u6.3Y4

1u6.3Y4

SMDDR_VREF

M_ODT0 3,7

+1_8VDIMM

1u6.3Y4

1u6.3Y4

SMDDR_VREF

M_ODT0 3,7

C32

C32

C273

C273

+1_8VDIMM

+1_8VDIMM

[Fuqun] DATA/DQS/DM from 10ohm to 22ohm in 0A

1u6.3Y4

1u6.3Y4

C38

C38

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

M_CLK_DDR#1

M_CLK_DDR1

C48

C48

2.2u6.3Y6

2.2u6.3Y6

[Fuqun] Swap pin in 0A

A_DQ32

A_DQ33

A_DQ34

A_DQ35

A_DQ37

A_DQ36

A_DQ39

A_DQ38

A_DQ40

A_DQ41

A_DQ42

A_DQ43

A_DQ47M_A_DQ47

A_DQ46

A_DQ48

A_DQ51

A_DQ50

A_DQ52

A_DQ54

A_DQ55

A_DQ56

A_DQ57

A_DQ58

A_DQ59

A_DQ60A_DQ28

A_DQ63

A_DQ62

M_A_DQS0

M_A_DQS#0

M_A_DQS#1

M_A_DQS1

M_A_DQS2

M_A_DQS#2

M_A_DQS3

M_A_DQS#3

R26

R26

200R/4

200R/4

C43

C43

1u6.3X8

1u6.3X8

B

RN17

RN17

A_DQS0

132

A_DQS#0

4

4P2R-22R

4P2R-22R

RN21

RN21

A_DQS#1

132

A_DQS1A_DQ6M_A_DQ6

4

4P2R-22R

4P2R-22R

RN3

RN3

A_DQS2

132

A_DQS#2

4

4P2R-22R

4P2R-22R

RN38

RN38

A_DQS3

132

A_DQS#3

4

4P2R-22R

4P2R-22R

[Fuqun] Remove SPD EEROM in 0A

+1_8VDIMM

C31

C31

2.2u6.3Y6

2.2u6.3Y6

M_A_DQS4

M_A_DQS#4

M_A_DQS5

M_A_DQS6

M_A_DQS#6

M_A_DQS7

M_CLK_DDR#0

M_CLK_DDR0

C45

C45

2.2u6.3Y6

2.2u6.3Y6

RN7

RN7

132

4P2R-22R

4P2R-22R

RN44

RN44

132

4P2R-22R

4P2R-22R

RN12

RN12

132

4P2R-22R

4P2R-22R

RN41

RN41

132

4P2R-22R

4P2R-22R

A_DQS4

A_DQS#4

4

A_DQS5

A_DQS#5M_A_DQS#5

4

A_DQS6

A_DQS#6

4

A_DQS7

A_DQS#7M_A_DQS#7

4

M_CLK_DDR#0

R23

R23

200R/4

200R/4

M_CLK_DDR0

C210

C210

C34

C34

2.2u6.3Y6

2.2u6.3Y6

2.2u6.3Y6

2.2u6.3Y6

C

4P2R-22R

4P2R-22R

4P2R-22R

132

132

132

132

132

132

132

132

132

132

132

132

132

132

132

132

C33

C33

100p16N4

100p16N4

A_DQ0

A_DQ1

4

A_DQ2

A_DQ3

4

A_DQ4

A_DQ5

4

4

A_DQ8

A_DQ9

4

A_DQ11

A_DQ10

4

A_DQ13

A_DQ12

4

A_DQ15

A_DQ14

4

A_DQ16

A_DQ17

4

A_DQ18

A_DQ19

4

A_DQ20

A_DQ21

4

A_DM2

A_DQ22

4

A_DQ25

A_DQ24

4

A_DQ27

A_DQ26

4

A_DQ29

4

A_DQ30

A_DQ31

4

M_CLK_DDR#1

R22

R22

200R/4

200R/4

M_CLK_DDR1

EMI

C37

C37

C51

C51

0.1u10X4

0.1u10X4

68p50N4

68p50N4

M_A_DQ0

RN16

RN16

M_A_DQ1

RN18RN18

M_A_DQ2

3 3

4 4

M_A_DQ3

RN33RN33

M_A_DQ4

M_A_DQ5

M_A_DM0 A_DM0

RN34RN34

M_A_DQ8

RN19RN19

M_A_DQ9

M_A_DQ11

RN22RN22

M_A_DQ10

RN29RN29

M_A_DQ13

M_A_DQ12

RN35RN35

M_A_DQ15

M_A_DQ14

M_A_DQ16

RN2RN2

M_A_DQ17

M_A_DQ18

RN4RN4

M_A_DQ19

M_A_DQ20

RN46RN46

M_A_DQ21

RN47RN47

M_A_DM2

M_A_DQ22

RN5RN5

M_A_DQ25

M_A_DQ24

M_A_DQ27

RN20RN20

M_A_DQ26

M_A_DQ29

RN48RN48

M_A_DQ28

M_A_DQ30

RN49RN49

M_A_DQ31

M_CLK_DDR#1

M_CLK_DDR1

+1_8VDIMM

C47

C47

100p16N4

100p16N4

A

4P2R-22R

M_A_DQ32

RN6

RN6

132

M_A_DQ33

RN8RN8

M_A_DQ34

132

M_A_DQ35

RN30RN30

M_A_DQ37

132

M_A_DQ36

M_A_DQ39

RN31RN31

132

M_A_DQ38

M_A_DQ40

RN9RN9

132

M_A_DQ41

M_A_DQ42

RN10RN10

132

M_A_DQ43

R29 22R/4R29 22R/4

M_A_DM5 A_DM5

M_A_DQ44 A_DQ44

R35 22R/4R35 22R/4

RN45RN45

132

M_A_DQ46

M_A_DQ49 A_DQ49

RN11RN11

132

M_A_DQ48

M_A_DQ51

RN13RN13

132

M_A_DQ50

M_A_DQ53 A_DQ53

RN39RN39

132

M_A_DQ52

RN40RN40

M_A_DQ54

132

M_A_DQ55

RN14RN14

M_A_DQ56

132

M_A_DQ57

M_A_DQ58

RN15RN15

132

M_A_DQ59

M_A_DQ61 A_DQ61

RN43RN43

132

M_A_DQ60

M_A_DQ63

RN42RN42

132

M_A_DQ62

C206

C206

3p50N4

3p50N4

C36

C36

0.1u10X4

0.1u10X4

M_A_DQ7

M_A_DM1

M_A_DQ23

M_A_DM3

M_A_DM4

M_A_DQ45

M_A_DM6

M_A_DM7

C198

C198

0.1u10X4

0.1u10X4

RN28

RN28

RN32RN32

C205

C205

3p50N4

3p50N4

4P2R-22R

4P2R-22R

132

R37 22R/4R37 22R/4

R28 22R/4R28 22R/4

132

R36 22R/4R36 22R/4

R30 22R/4R30 22R/4

4

4

A_DM1

A_DM3

A_DM4

A_DM6

A_DM7

M_CLK_DDR#0

M_CLK_DDR0

C46

C46

0.1u10X4

0.1u10X4

A_DQ7

A_DQ23

A_DQ45

C195

C195

0.1u10X4

0.1u10X4

R24

R24

200R/4

200R/4

C56

C56

0.1u10X4

0.1u10X4

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N011

MS-N011

Tuesday, June 02, 2009

Tuesday, June 02, 2009

Tuesday, June 02, 2009

MS-N011

DDR2 64*16 BGA A

DDR2 64*16 BGA A

DDR2 64*16 BGA A

E

Sheet of

Sheet of

Sheet of

635

635

635

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Date:

D

Date:

1.0

1.0

1.0

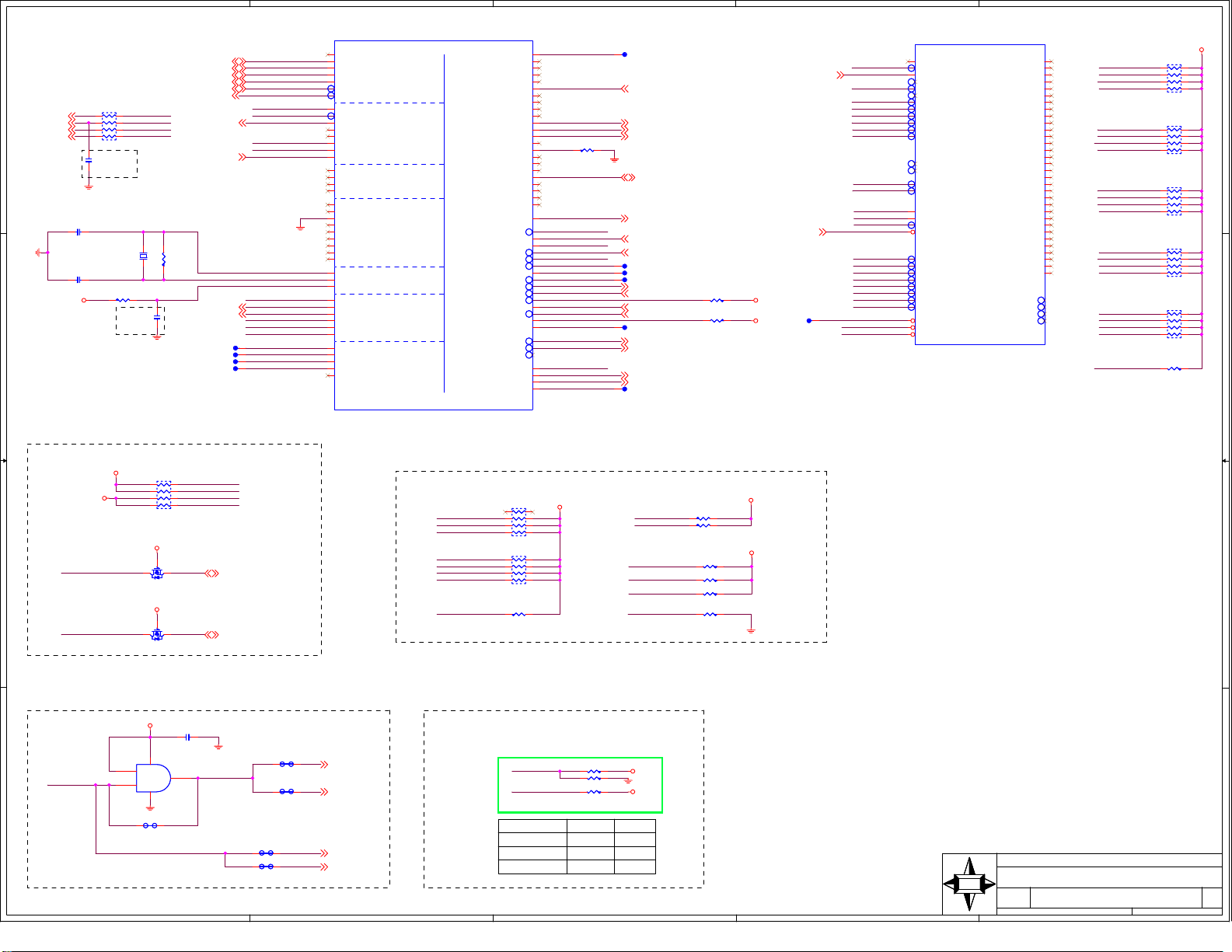

A

B

C

D

E

M_A_A[14:0]3,5,6

1 1

2 2

3 3

M_A_A[14:0]

M_CKE23,5

M_A_BS23,5,6

M_A_BS03,5,6

M_A_WE#3,5,6

M_A_CAS#3,5,6

M_ODT33,5

1

3

5

7

2

4

6

8

2

4

6

8

2

4

6

8

DDR_VTT

RN36

RN36

2

4

6

8

8P4R-33R/4

8P4R-33R/4

RN27

RN27

2

4

6

8

8P4R-33R/4

8P4R-33R/4

RN37

RN37

2

4

6

8

8P4R-33R/4

8P4R-33R/4

R34 47R/4R34 47R/4

R32 47R/4R32 47R/4

R33 47R/4R33 47R/4

R31 33R/4R31 33R/4

1

3

5

7

1

3

5

7

1

3

5

7

M_A_A11

M_CKE3

M_A_A14

M_A_RAS#

M_A_BS1

M_A_A13

M_CS#2

M_ODT2

M_CS#3

M_ODT0

M_CKE0

M_CS#0

M_A_A8

RN26

M_A_A7

M_A_A6

M_A_A4

M_A_A2

M_CKE2

M_A_A12

M_A_A9

M_A_BS2 M_A_A0

M_A_BS0

M_A_WE#

M_A_CAS#

M_ODT3

M_A_A5

M_A_A3

M_A_A1

M_A_A10

RN26

2

4

6

8

8P4R-33R/4

8P4R-33R/4

RN24

RN24

1

3

5

7

8P4R-33R/4

8P4R-33R/4

RN23

RN23

1

3

5

7

8P4R-33R/4

8P4R-33R/4

RN25

RN25

1

3

5

7

8P4R-33R/4

8P4R-33R/4

M_CKE3 3,5

M_A_RAS# 3,5,6

M_A_BS1 3,5,6

M_CS#2 3,5

M_ODT2 3,5

M_CS#3 3,5

M_ODT0 3,6

M_CKE0 3,6

M_CS#0 3,6

[Fuqun] ADD/BS/RAS/CAS/WE--33ohm

[Fuqun] CS/CKE/ODT--47ohm

[Fuqun] Swap pin in 0A

[Fuqun] NC C62 in 0A

DDR_VTT

C68

C68

X_10u10Y8

X_10u10Y8

4 4

DDR_VTT

C55

C55

0.1u10VX7R

0.1u10VX7R

C66

C66

0.1u10VX7R

0.1u10VX7R

Layout note: Place one cap close to every 2 pullup resistors terminated to +0.9V.

VTT_DDR cap re-placement

A

[Fuqun] Change 1uf to 0.1uf IN 0A

C58

C58

X_0.1u10VX7R

X_0.1u10VX7R

C60

C60

0.1u10VX7R

0.1u10VX7R

C65

C65

X_0.1u10VX7R

X_0.1u10VX7R

B

C64

C64

0.1u10VX7R

0.1u10VX7R

C67

C67

X_0.1u10VX7R

X_0.1u10VX7R

C54

C54

0.1u10VX7R

0.1u10VX7R

C59

C59

X_0.1u10VX7R

X_0.1u10VX7R

C

C63

C63

0.1u10VX7R

0.1u10VX7R

MSI

MSI

MSI

D

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N01x

MS-N01x

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Tuesday, June 02, 2009

Date:

Tuesday, June 02, 2009

Date:

Tuesday, June 02, 2009

MS-N01x

DDR TERMINATION

DDR TERMINATION

DDR TERMINATION

Sheet of

Sheet of

Sheet of

E

735

735

735

0A

0A

0A

5

4

3

2

1

VGA

+5VRUN

D5

D5

S-SCS551V-TG_SOD323

75 ohm

S-SCS551V-TG_SOD323

C197

C197

12p50N4

12p50N4

C199

C199

C203

C203

12p50N4

12p50N4

D D

C201

C201

X_22p50N4

X_22p50N4

L9 0.12u300mAL9 0.12u300mA

L8 0.12u300mAL8 0.12u300mA

L7 0.12u300mAL7 0.12u300mA

C204

C204

X_22p50N4

X_22p50N4

VGA_R3

VGA_G3

VGA_B3

C196

50 ohm

C C

R130

R130

150R1%4

150R1%4

R131

R131

150R1%4

150R1%4

R132

R132

150R1%4

150R1%4

C196

X_22p50N4

X_22p50N4

1A

C200

C200

X_0.1u16Y4

X_0.1u16Y4

RED_L

GREEN_L

BLUE_L

12p50N4

12p50N4

CRT5V

CRT5V

6

1

7

2

8

3

9

4

10

5

+3VRUN

R128

R128

X_1K/4

VGA1

VGA1

1617

11

DDC_DATA_5V DDC_DATA_5V

12

HSYNC_3V

13

VSYNC_3V

14

DDC_CLK_5V DDC_CLK_5V

15

VGAF_BLUE-RH-11

VGAF_BLUE-RH-11

X_1K/4

C189

C189

C191

C191

X_22p50N4

X_22p50N4

X_22p50N4

X_22p50N4

[Fuqun] Need change to 30~50pf follow Intel

R129

R129

X_1K/4

X_1K/4

HSYNC_3V 3

VSYNC_3V 3

CRT5V

+3VRUN

+3VRUN

246

8

RN1

RN1

8P4R-2.2K/4

8P4R-2.2K/4

135

VGA_DATA VGA_CLK

7

Q8

Q8

N-BSS138_SOT23

N-BSS138_SOT23

D S

G

G

D S

N-BSS138_SOT23

N-BSS138_SOT23

Q7

Q7

VGA_DATA

+3VRUN

VGA_CLK

VGA_DATA 3

VGA_CLK 3

LVDS

LVDS POWER 3.3V

Hall Switch

VOUT

OCB

+3V_LCD

C169

C169

C168

C168

1

3

X_0.1u10X4

X_0.1u10X4

10u6.3X8

10u6.3X8

+3VRUN

U16

U16

5

VIN

2

GND

4

EN

APL3511ABI-TRG_SOT23-5-HF

APL3511ABI-TRG_SOT23-5-HF

R117

R117

X_100K/4

X_100K/4

B B

R116

R116

10K/4

10K/4

LID#13

C164

C164

X_1000p50X4

X_1000p50X4

+3VRUN

LID#

U15

U15

X

VDD

Z

GND

Y

VOUT

.APX9131AI-TRL_SOT23-3-RH

.APX9131AI-TRL_SOT23-3-RH

JLVDS1

JLVDS1

1

GND

LVDS_TXCKN2

LVDS_TXCKP2

LVDS_TX0N2

LVDS_TX0P2

LVDS_TX1N2

LVDS_TX1P2LVDS_VDDEN2

LVDS_TX2N2

LVDS_TX2P2

3

RXCLKIN-

5

RXCLKIN+

7

GND

9

RXIN0-

11

RXIN0+

13

GND

15

RXIN1-

17

RXIN1+

19

GND

21

RXIN2-

23

RXIN2+

25

GND

27

RXIN3-/NC

29

RXIN3+/NC

31

GND

34

34

BH2X15S-1PITCH_WHITE-RH-1

BH2X15S-1PITCH_WHITE-RH-1

250~350mA

VDD

VDD

V_EDID

GND

GND

VLED

VLED

VLED

NC1

NC2

NC3

NC4

ADJ

CLK_EDID

DATA_EDID

GND

33

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

33

LED Backlight POWER 5V

[Fuqun] PWR_SRC for 10.1 panel

[Fuqn] Remove ADJ_FRQ0/ADJ_FRQ1 in 0A

+3VRUN

+3V_LCD

BKLT_EN_R BKLT_EN

LVDS_CLK

LVDS_DATA

C4

0.1u16Y4C40.1u16Y4

R5 X_0R/4R5 X_0R/4

C1

C1

BR-ADJ-PWM 13

X_10p25N4

X_10p25N4

[Fuqun] BKLT_EN for 10.1 panel

450~500mA

C6

X_0.1u25Y4C6X_0.1u25Y4

C5

0.1u25Y4C50.1u25Y4

+5V_LED

+5V_LED

L1

X_80L700mA-150-RH

X_80L700mA-150-RH

1

VOUT

3

OCB

L1

C3

10u6.3X8C310u6.3X8

LVDS_CLK2

LVDS_DATA2

3

+5VRUN

[Fuqun] Change +3VSUS to +3VRUN for layout in 0A

LID#

A A

LVDS_BLON2

5

R3

100K/4R3100K/4

2

1

+3VRUN

3 5

4

U1

U1

NC7S08_SC70_5

NC7S08_SC70_5

BKLT_EN

R2

X_100K/4R2X_100K/4

4

PWR_SRC

U2

U2

5

VIN

2

GND

4

EN

APL3511ABI-TRG_SOT23-5-HF

APL3511ABI-TRG_SOT23-5-HF

R79

R79

2.2K/4

2.2K/4

+3VRUN

R74

R74

2.2K/4

2.2K/4

LVDS_CLK

LVDS_DATA

[EMI]

LVDS_TXCKN

LVDS_TX1N

MSI

MSI

MSI

2

R10 X_200R/4R10 X_200R/4

R9 X_200R/4R9 X_200R/4

R8 X_200R/4R8 X_200R/4

R7 X_200R/4R7 X_200R/4

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Tuesday, June 02, 2009

Tuesday, June 02, 2009

Tuesday, June 02, 2009

LVDS_TXCKP

LVDS_TX0PLVDS_TX0N

LVDS_TX1P

LVDS_TX2PLVDS_TX2N

MS-N01x

MS-N01x

MS-N01x

CRT, LVDS CONN

CRT, LVDS CONN

CRT, LVDS CONN

1

Sheet ofDate:

835

Sheet ofDate:

835

Sheet ofDate:

835

0A

0A

0A

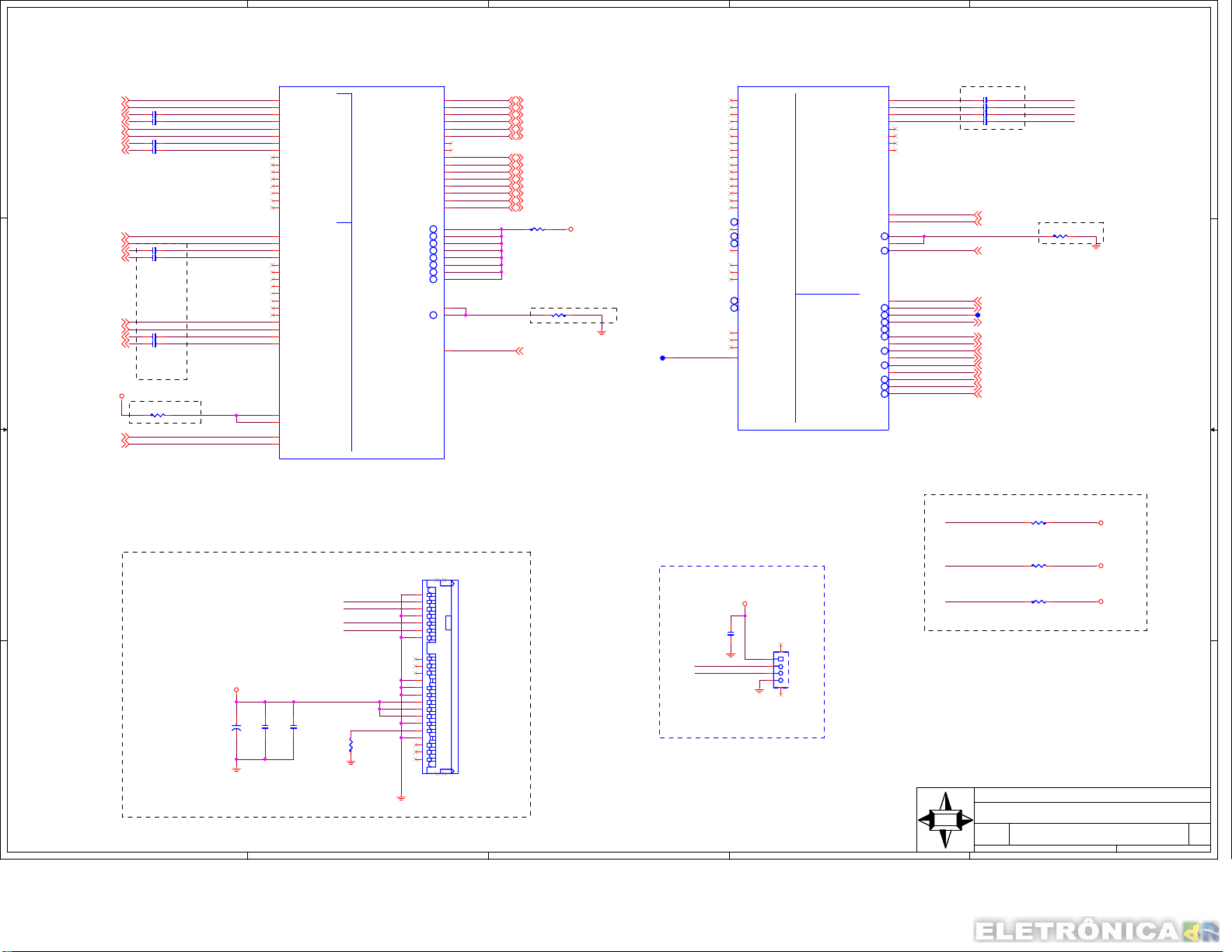

5

AC couple

TGP transmit to PNV

DMI_TGP_TXN02

DMI_TGP_TXP02

D D

DMI_PNV_RXN02

DMI_PNV_RXP02

DMI_TGP_TXN12

DMI_TGP_TXP12

DMI_PNV_RXN12

DMI_PNV_RXP12

C300 0.1u10X4C300 0.1u10X4

C301 0.1u10X4C301 0.1u10X4

C298 0.1u10X4C298 0.1u10X4

C299 0.1u10X4C299 0.1u10X4

DMI_TGP_RXN0

DMI_TGP_RXP0

DMI_TGP_RXN1

DMI_TGP_RXP1

[Fuqun] Remove 3G_PCIE bus in 0A

place Cap close to

PCIE_MINI_RXN217

PCIE_MINI_RXP217

PCIE_MINI_TXN217

PCIE_MINI_TXP217

C C

PCIE_LAN_RXN15

PCIE_LAN_RXP15

PCIE_LAN_TXN15

PCIE_LAN_TXP15

CLK_DMI_TGP#12

CLK_DMI_TGP12

TGP within 10intch

C305 0.1u10X4C305 0.1u10X4

C304 0.1u10X4C304 0.1u10X4

[Fuqun] Change port2/3

to port1/4 for

layoutin 0A

C302 0.1u10X4C302 0.1u10X4

C303 0.1u10X4C303 0.1u10X4

place Cap close to

+1_5VRUN

TGP within 500mils

R102 24.9R1%4R102 24.9R1%4

PCIE_MINI_TXN2_C

PCIE_MINI_TXP2_C

PCIE_LAN_TXN_C

PCIE_LAN_TXP_C

DMICOMP

M18

M19

M21

W23

W24

R23

R24

P21

P20

T21

T20

T24

T25

T19

T18

U23

U24

V21

V20

V24

V23

K21

K22

J23

J24

K24

K25

L23

L24

L22

P17

P18

N25

N24

H24

J22

U23B

U23B

DMI0RXN

DMI0RXP

DMI0TXN

DMI0TXP

DMI1RXN

DMI1RXP

DMI1TXN

DMI1TXP

DMI2RXN

DMI2RXP

DMI2TXN

DMI2TXP

DMI3RXN

DMI3RXP

DMI3TXN

DMI3TXP

PERN1

PERP1

PETN1

PETP1

PERN2

PERP2

PETN2

PETP2

PERN3

PERP3

PETN3

PETP3

PERN4

PERP4

PETN4

PETP4

DMI_ZCOMP

DMI_IRCOMP

DMI_CLKN

DMI_CLKP

TPT

TPT

TPT

TPT

DMI

DMI

PCI-E

PCI-E

4

U1LB

U1LB

USB

USB

USBP0N

USBP0P

USBP1N

USBP1P

USBP2N

USBP2P

USBP3N

USBP3P

USBP4N

USBP4P

USBP5N

USBP5P

USBP6N

USBP6P

USBP7N

USBP7P

OC0#

OC1#

OC2#

OC3#

OC4#

OC5#/GPIO29

OC6#/GPIO30

OC7#/GPIO31

USBRBIAS

USBRBIAS#

CLK48

2

2

H7

H6

H3

H2

J2

J3

K6

K5

K1

K2

L2

L3

M6

M5

N1

N2

OC0#

D4

C5

D3

D2

E5

E6

C2

C3

G2

USBRBIAS

G3

F4

USB 0 : USB CONN.

USB 1 : USB CONN.

USB 2 : USB CONN.

USB 3 : MINI PCIE1

USB 4 : Blue tooth

USB 5 : CAMERA

USB 6 : MINI PCIE2

USB 7 : CardReader

?

?

3

USB0N 18

USB0P 18

USB1N 18

USB1P 18

USB2N 16

USB2P 16

USB4N 18

USB4P 18

USB5N 18

USB5P 18

USB6N

USB6P

USB7N 18

USB7P 18

R193 1K/4R193 1K/4

CLK_USB48 12

+3VSUS

[Fuqun] Change R406 from

10Kohm to 1Kohm in 0A

place Cap close to

TGP within 200mils

R197 22.6R1%4R197 22.6R1%4

2

TPT

TPT

U1LBU23C

U1LBU23C

R12

RSVD

AE20

RSVD

AD17

RSVD

AC15

RSVD

AD18

RSVD

Y12

RSVD

AA10

RSVD

AA12

RSVD

Y10

RSVD

AD15

RSVD

W10

RSVD

V12

RSVD

AE21

RSVD

AE18

RSVD

AD19

RSVD

U12

RSVD

AC17

RSVD

AB13

RSVD

AC13

RSVD

AB15

RSVD

Y14

RSVD

AB16

RSVD

AE24

RSVD

AE23

RSVD

AA14

RSVD

V14

RSVD

AD16

RSVD

AB11

RSVD

AB10

T26T26

AD23

RSVD

GPIO36

TPT

TPT

SATA

SATA

HOST

HOST

SATA0RXN

SATA0RXP

SATA0TXN

SATA0TXP

SATA1RXN

SATA1RXP

SATA1TXN

SATA1TXP

SATA_CLKN

SATA_CLKP

SATARBIAS#

SATARBIAS

SATALED#

A20GATE

A20M#

CPUSLP#

IGNNE#

INIT3_3V#

INIT#

INTR

FERR#

RCIN#

SERIRQ

SMI#

STPCLK#

THERMTRIP#

3

3

?

?

SATA0RXN_C

AE6

SATA0RXP_C

AD6

SATA0TXN_C

AC7

SATA0TXP_C

AD7

AE8

AD8

AD9

AC9

AD4

AC4

SATARBIAS

AD11

AC11

AD25

U16

Y20

Y21

Y18

AD21

AC25

AB24

H_FERR#

Y22

T17

NMI

AC21

SIRQ

AA16

AA21

V18

H_THRMTRIP#

AA20