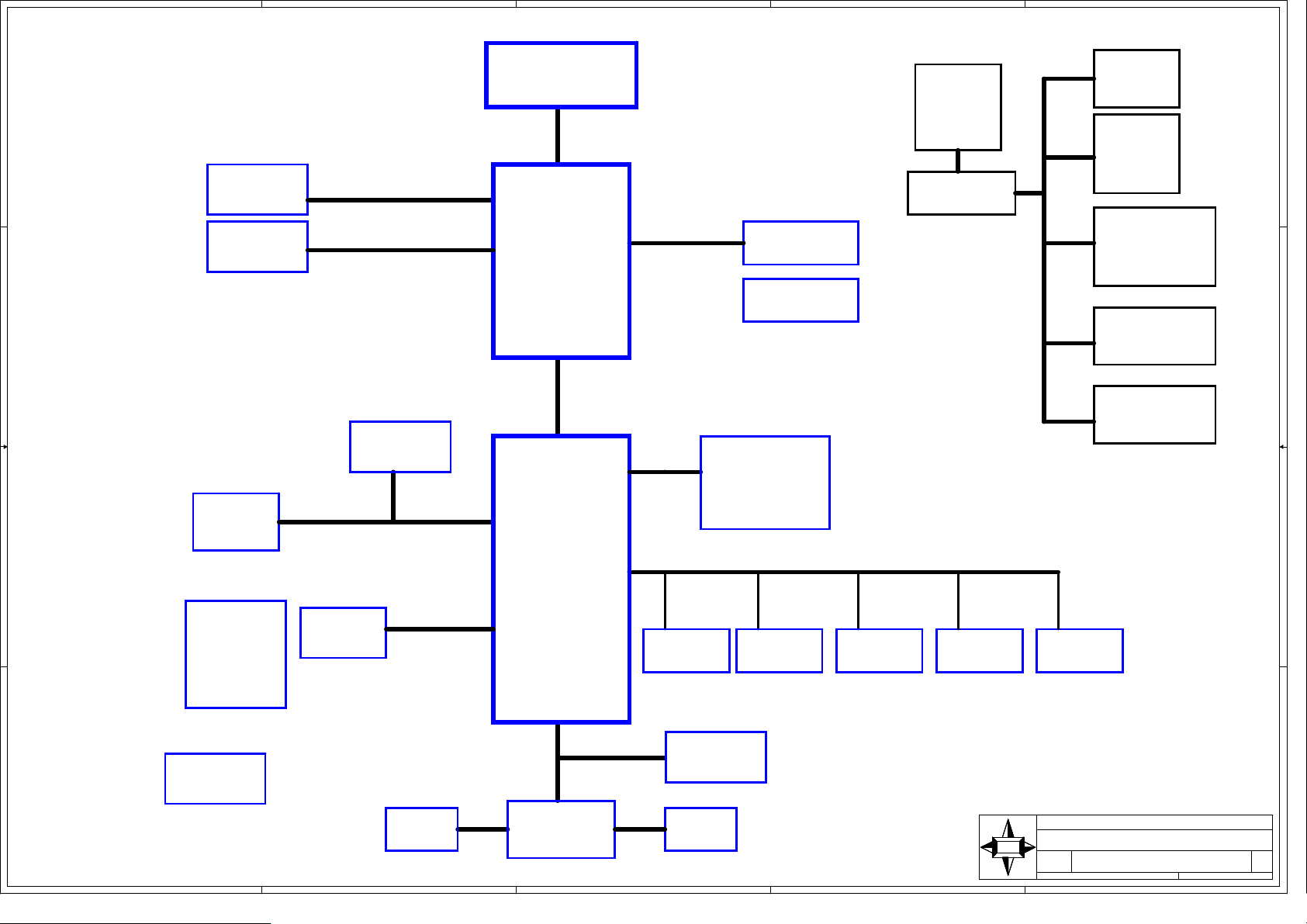

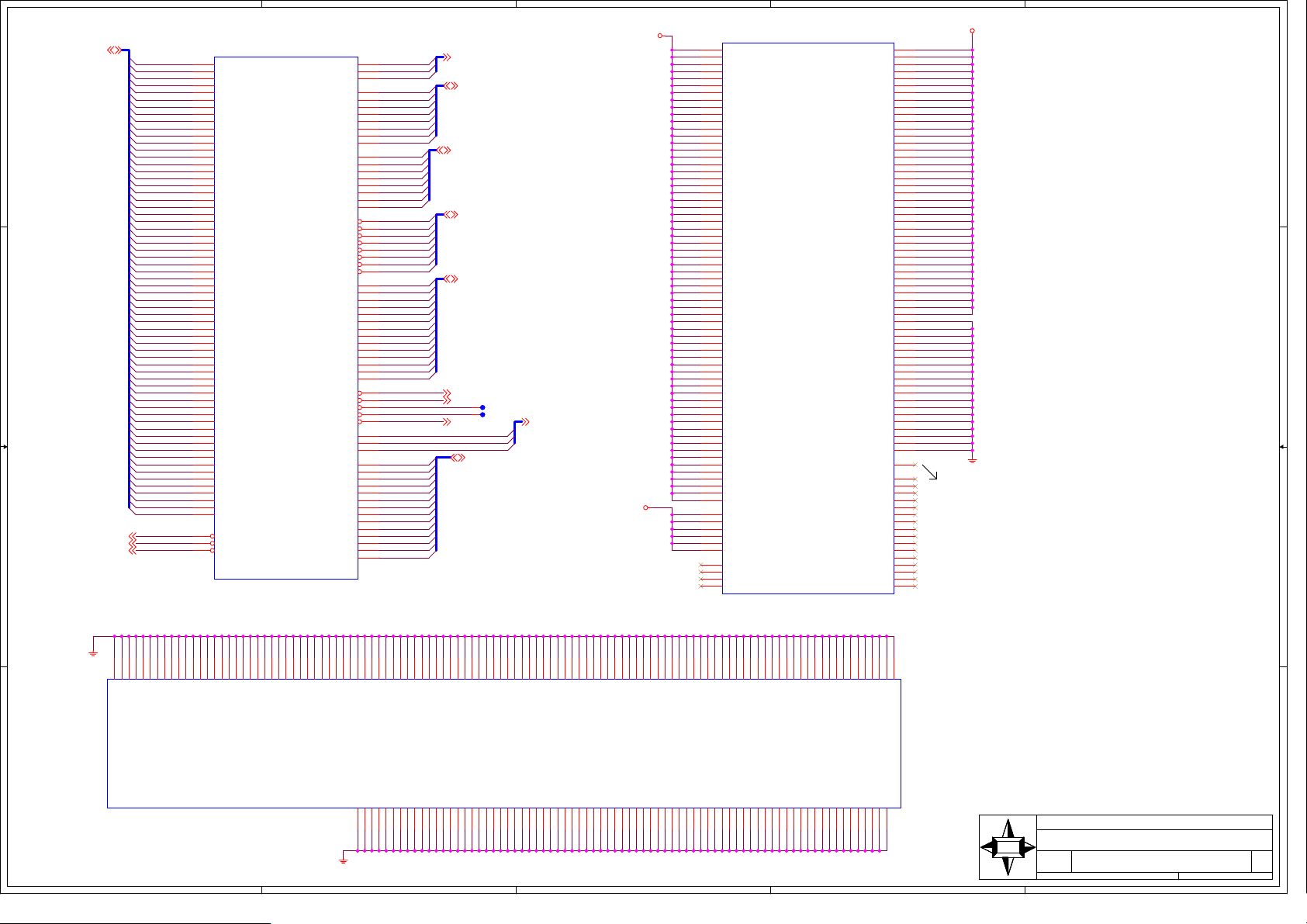

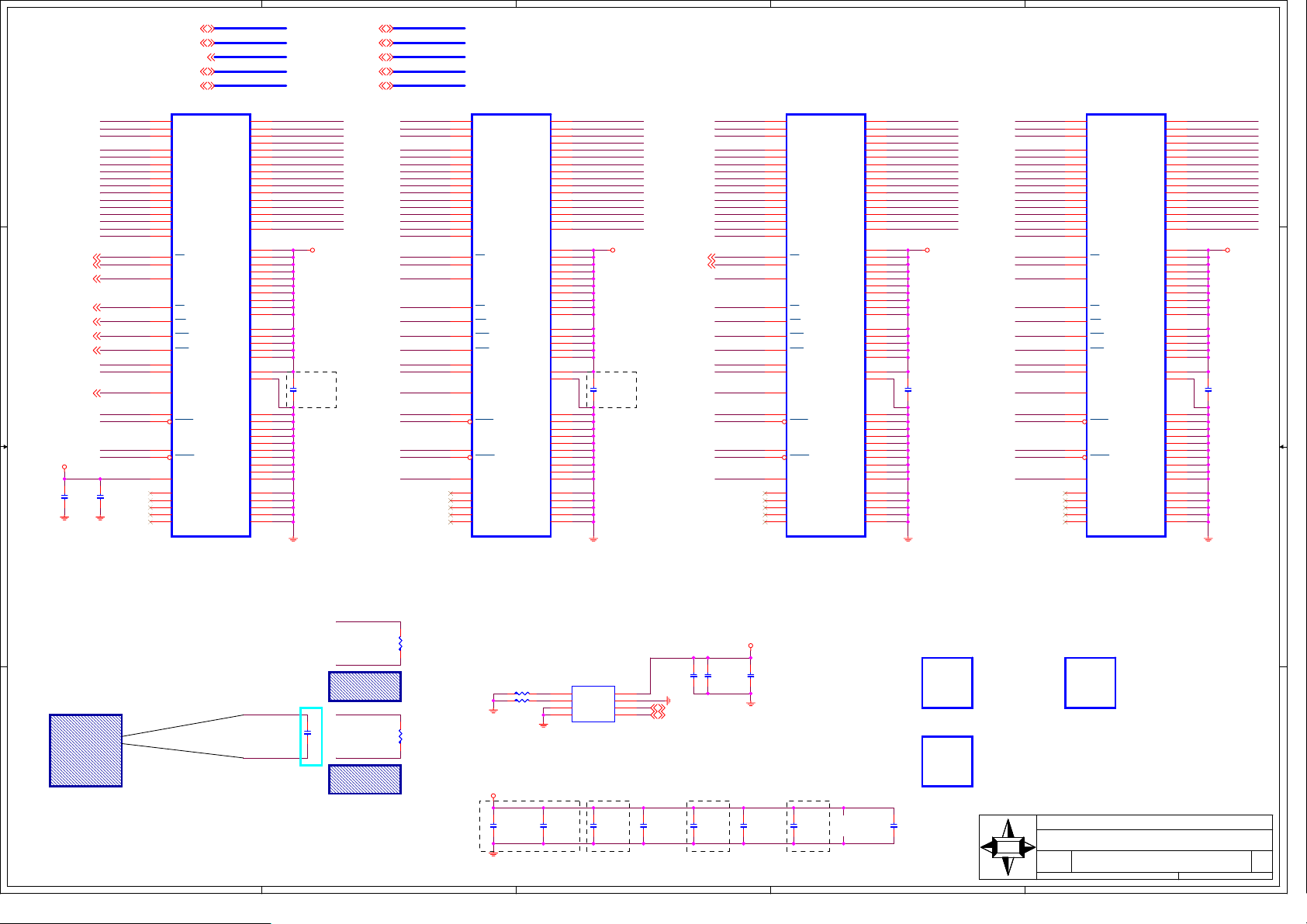

MSI MS-N011 BLOCK DIAGRAM

A

B

C

D

E

MS-N011 VER : 1.0

4 4

CRT

Page 21

LVDS

Page 21

RGB

LVDS

Diamondville

Page 2,3

HOST

133MHZ 4X

NORTH

BRIDGE

Signal Channel DDRII

400/533 MHZ

onboard DDR

Page 9,10

DC JACK

&

Selector

Page 25

SYS POWER

INTEL

945GMS

3 3

Page 4~7

DDR-SODIMM1

Page 8

+3V +5V

TPS51120

Page 27

+1_8VDIMM

SC412

Page 28

VTT(1.05V)

+1_5VRUN

+2_5VRUN

SC412

Page 29

CPU POWER

ISL6261

Page 30

DMIx2

Wireless LAN

MINI PCIE

Conn.

Page 33

Interface

SATA

SATA 80GB HDD

OR

CHARGER

MAX 8724

Page 26

JMF 602

NAND FLASH

PCIE-LAN

RTL8102E

Page 18

2 2

PCI-EXPRESS

SOUTH

BRIDGE

optional

USB1.1/2.0

Page 22

INTEL

Internal SPK

Internal MIC

MIC

Earphone

Page 20

ALC888S

Page 19

Azalia

ICH7-M

Page 12~15

Connectors

USB 0,1,2

Page 23 Page 23 Page 23

Mini_PCIE x1

Wireless LAN

USB 3

Camera

USB 4

Cardreader

USB 5

Page 22

Blue tooth

USB 6

Page 22

optional

LPC BUS

A

CLK ICS113

Page 16

TP & KB

Page 24

B

KBC

ENE 3310

Page 17

1 1

SPI

C

LPC DUBUG

Page 24

BIOS

Page 24

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N011

MS-N011

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Friday, March 28, 2008

Date:

Friday, March 28, 2008

Date:

D

Friday, March 28, 2008

MS-N011

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

E

Sheet of

Sheet of

Sheet of

139

139

139

1.0

1.0

1.0

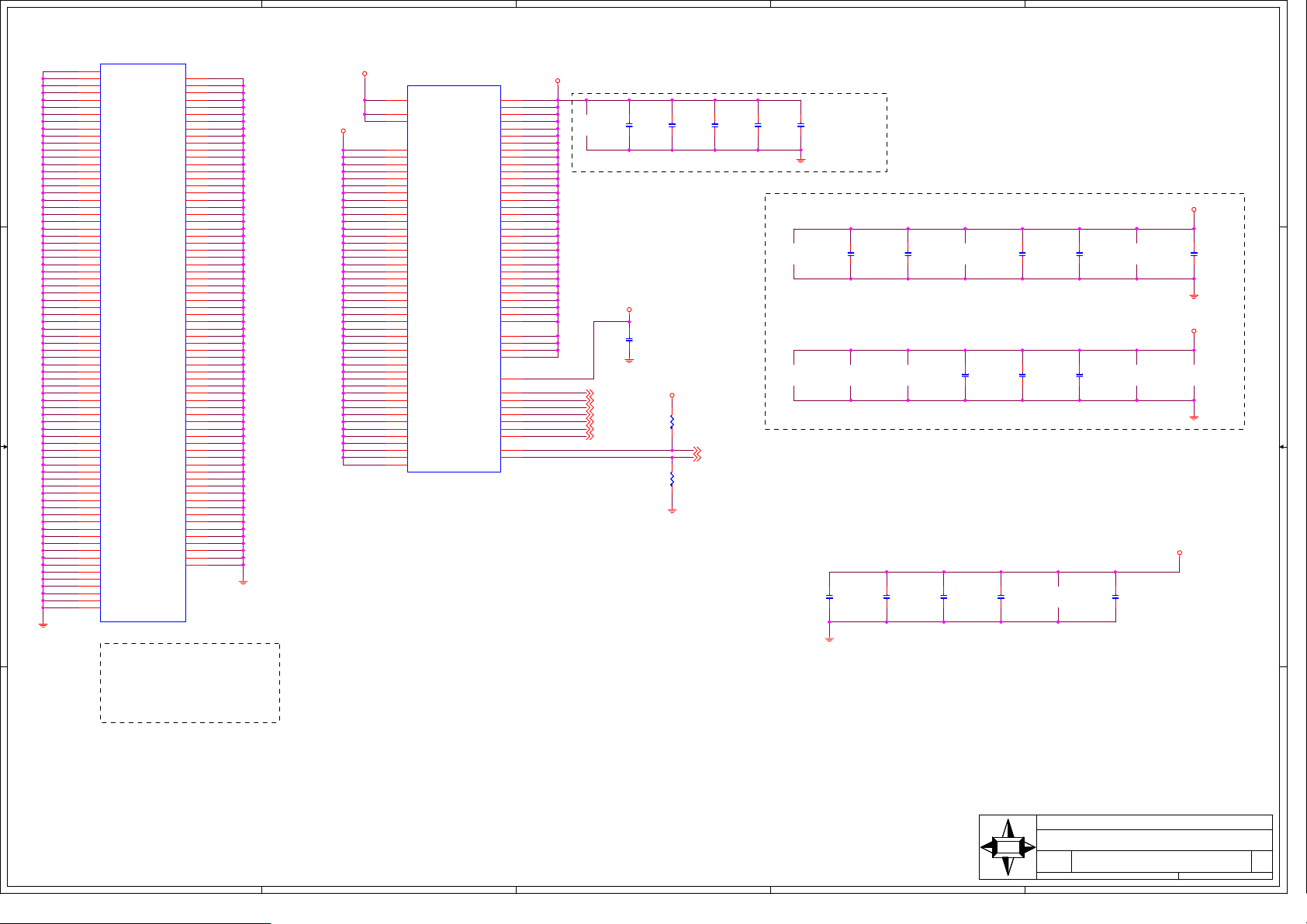

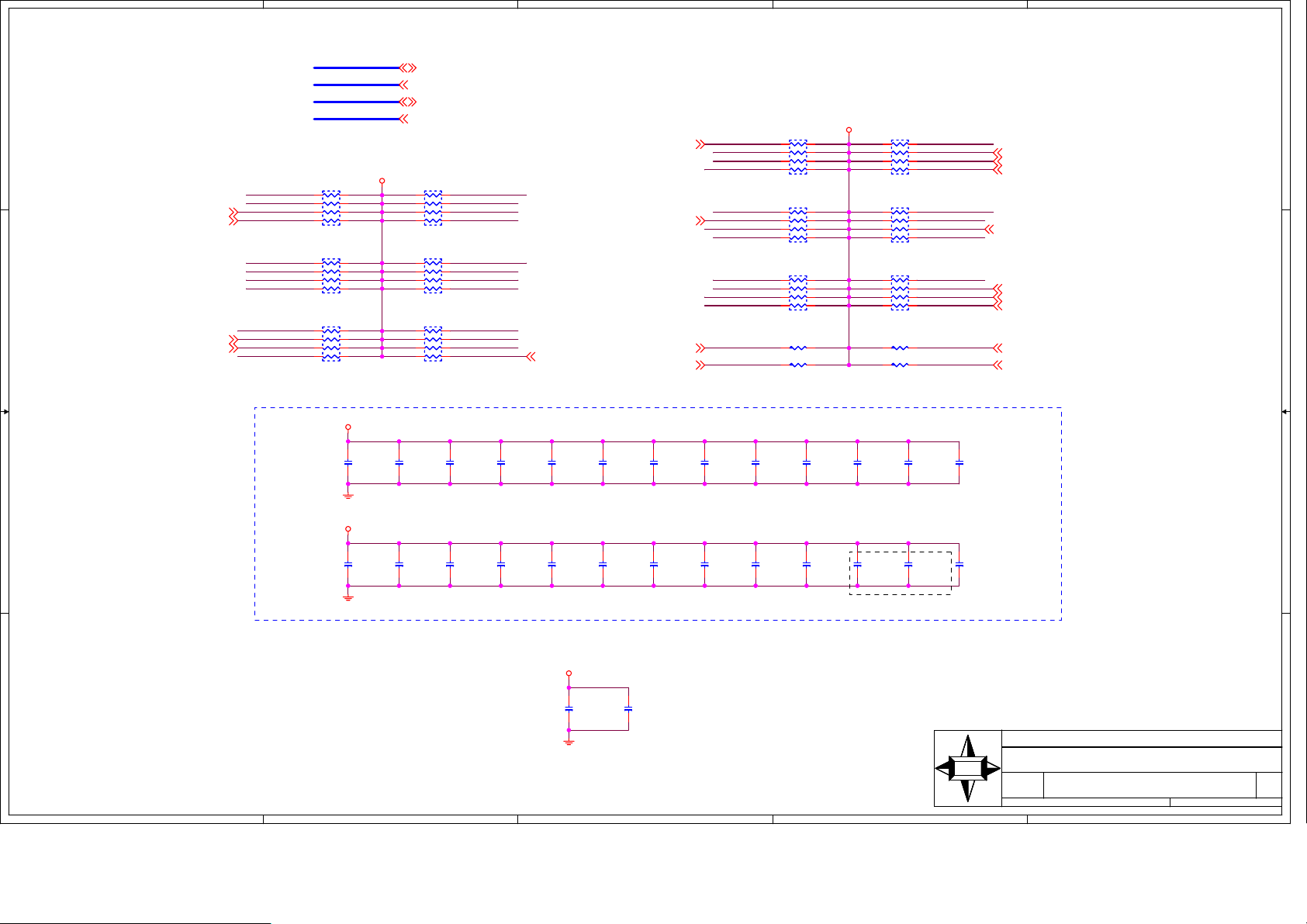

A

B

C

D

E

H_A#32

H_A#34

H_A#33

H_A#35

H_A20M#12

H_FERR#12

H_IGNNE#12

H_STPCLK#12

H_INTR12

H_NMI12

H_SMI#12

H_A20M#

H_IGNNE#

H_INTR

H_NMI

H_SMI#

H_A#[31:3]

H_RS#[2:0]

H_REQ#[4:0]

T19T19

T21T21

PM_THRMTRIP#

H_A#3

P21

H_A#4

H20

H_A#5

N20

H_A#6

R20

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

J19

N19

G20

M19

H21

L20

M20

K19

J20

L21

K20

AP0

D17

N21

J21

G19

P20

R19

C19

F19

E21

A16

D19

C14

C18

C20

E20

D20

B18

C15

B16

B17

C16

A17

B14

B15

A14

B19

AP1

M18

U18

T16

J4

R16

T15

R15

U17

D6

G6

H6

K4

K5

M15

L16

Cap close to

thermal

sensor

Trace : 10/4/10

THERMDA

THERMDC

R144 X_0R/4R144 X_0R/4

U28A

U28A

A[3]#

ADDR GROUP

0

ADDR GROUP

0

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

AP0

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

ADDR GROUP 1

ADDR GROUP 1

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

AP1

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

NC1

NC2

NC3

NC4

NC5

NC6

NC7

Diamondville

Diamondville

C119

C119

100p16N4

100p16N4

C116

C116

0.1u10X4

0.1u10X4

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

BR1#

XDP/ITP SIGNALSTHERM

XDP/ITP SIGNALSTHERM

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

BCLK[0]

BCLK[1]

H CLK

H CLK

RSVD3

RSVD2

RSVD1

+3VRUN

V19

Y19

U21

T21

T19

Y18

T20

IERR#

F16

V16

W20

D15

H_RS#0

W18

H_RS#1

Y17

H_RS#2

U20

W19

AA17

V20

K17

J18

H15

J15

K18

PREQ#

J16

HTCK

M17

HTDI

N16

M16

HTMS

L17

HTRST#

K16

V15

G17

E4

E5

H17

V11

V12

C21

C1

A3

THERMDA

THERMDC

PROCHOT#

PM_THRMTRIP# 12

Close to CPU socket

U11

U11

1

VDD

SMBCLK

2

D+

SMBData

3

D-

ALERT

T_CRIT_A4GND

SNSR-LM95245CIMM-RH

SNSR-LM95245CIMM-RH

H_ADS# 4

H_BNR# 4

H_BPRI# 4

H_DEFER# 4

H_DRDY# 4

H_DBSY# 4

H_BREQ# 4

H_INIT#_R

H_LOCK# 4

H_CPURST# 4

H_TRDY# 4

H_HIT# 4

H_HITM# 4

CLK_CPU_BCLK 16

CLK_CPU_BCLK# 16

SMB_CPU_CLK

SMB_CPU_DATA

THERMAL_INT#

8

7

6

5

R362 1K1%4R362 1K1%4

R201

R201

22R/4

22R/4

IERR#

PREQ#

HTMS

HTDI

HTCK

HTRST#

SMB_CPU_CLK 17

SMB_CPU_DATA 17

THERMAL_INT# 17

VTT

R202

R202

68R/4

68R/4

R124 2.2K/4R124 2.2K/4

R134 2.2K/4R134 2.2K/4

R137 2.2K/4R137 2.2K/4

VTT

R363

R363

330R/4

330R/4

R185 56R/4R185 56R/4

RN57

RN57

1

3

5

7

8P4R-56R/4

8P4R-56R/4

R370 56R/4R370 56R/4

H_INIT# 12

H_PROCHOT# 30

VTT

2

4

6

8

+3VRUN

H_D#[63:0]4

H_DSTBN#04

H_DSTBP#04

H_DINV#04

H_D#[63:0]4

H_DSTBN#14

H_DSTBP#14

H_DINV#14

CPU_BSEL016,17

CPU_BSEL116,17

VTT VTT

0.5" max

length

R319

R319

1K1%4

1K1%4

2K1%4

2K1%4

R321

R321

EXTBGREF

C401

C401

1u6.3Y4

1u6.3Y4

R343 X_1K/4R343 X_1K/4

R352 X_1K/4R352 X_1K/4

T18T18

T15T15

T12T12

T17T17

T14T14

T20T20

T13T13

CPU_BSEL2

T9T9

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

T16T16

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

T7T7

GTLREF

BINIT#

EDM

EXTBGREF

FORCEPR#

HFPLL

MCERR#

RSP#

DP#0

DP#1

W10

AA14

AA11

W12

AA16

W15

AA13

W13

AA9

W16

AA5

AA6

AA8

Y11

Y12

Y10

Y13

Y16

W9

Y14

Y15

W3

W7

W6

W2

W4

T17

M6

N15

P17

G5

Y9

V9

Y8

U1

Y7

Y3

V3

U2

T3

V2

Y4

Y5

Y6

R4

A7

U5

V5

R6

N6

T6

J6

H5

U28B

U28B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

DP#0

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

DP#1

GTLREF

ACLKPH

DCLKPH

BINIT#

EDM

EXTBGR

FORCEPR#

HFPLL

MCERR#

RSP#

BSEL[0]

BSEL[1]

BSEL[2]

Diamondville

Diamondville

R326

R326

1K1%4

1K1%4

R333

R333

2K1%4

2K1%4

D[32]#

D[33]#

D[34]#

DATA GRP0

DATA GRP0

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

DATA GRP2DATA GRP3

DATA GRP2DATA GRP3

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

DSTBN[3]#

DSTBP[3]#

PWRGOOD

0.5" max

length

GTLREF

C415

C415

X_0.1u10X4

X_0.1u10X4

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

CORE_D

CMREF

DATA GRP1

DATA GRP1

MISC

MISC

DP#2

DP#3

SLP#

R3

R2

P1

N1

M2

P2

J3

N3

G3

H2

N2

L2

M3

J2

H1

J1

K2

K3

L1

M4

C2

G2

F1

D3

B4

E1

A5

C3

A6

F2

C6

B6

B3

C4

C7

D2

E2

F3

C5

D4

T1

T2

F20

F21

R18

R17

U4

V17

N18

A13

B7

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

DP#2

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

DP#3

HCOMP0

HCOMP1

HCOMP2

HCOMP3

H_DPRSTP#

H_DPSLP#

H_DPWR#

CPU_PWRGD

CPUSLP#

CORE_D

CPU_CMREF

T8T8

T11T11

0.5" max

length

H_DPRSTP# 12,30

H_DPSLP# 12

H_DPWR# 4

CPU_PWRGD 12

CPUSLP# 4

T33T33

CPU_CMREF

C416

C416

0.1u10X4

0.1u10X4

H_D#[63:0] 4

H_DSTBN#2 4

H_DSTBP#2 4

H_DINV#2 4

H_D#[63:0] 4

H_DSTBN#3 4

H_DSTBP#3 4

H_DINV#3 4

R318 27.4R1%6R318 27.4R1%6

R323 54.9R1%4R323 54.9R1%4

R372 27.4R1%6R372 27.4R1%6

R371 54.9R1%4R371 54.9R1%4

VTT

R327

R327

1K1%4

1K1%4

R334

R334

2K1%4

2K1%4

0.5" max length

25 MIL AWAY FROM HIGH

SPEED SIGNAL

HCOMP0,2==>18MIL

HCOMP1,3==>5MIL

VTT

R154

R154

X_1K/4

X_1K/4

H_DPWR#

R150

R150

X_1K/4

X_1K/4

VTT

R188

R188

X_1K/4

X_1K/4

CPU_PWRGD

H_A#[31:3]4

H_RS#[2:0]4

H_REQ#[4:0]4

4 4

H_ADSTB#04

VTT

3 3

2 2

1 1

VTT

RN54

RN54

1

2

3

4

5

6

7

8

8P4R-1K/4

8P4R-1K/4

H_ADSTB#14

R365 X_1K/4R365 X_1K/4

R322 X_1K/4R322 X_1K/4

R356 X_51R/4R356 X_51R/4

R361 X_51R/4R361 X_51R/4

R366 X_1K/4R366 X_1K/4

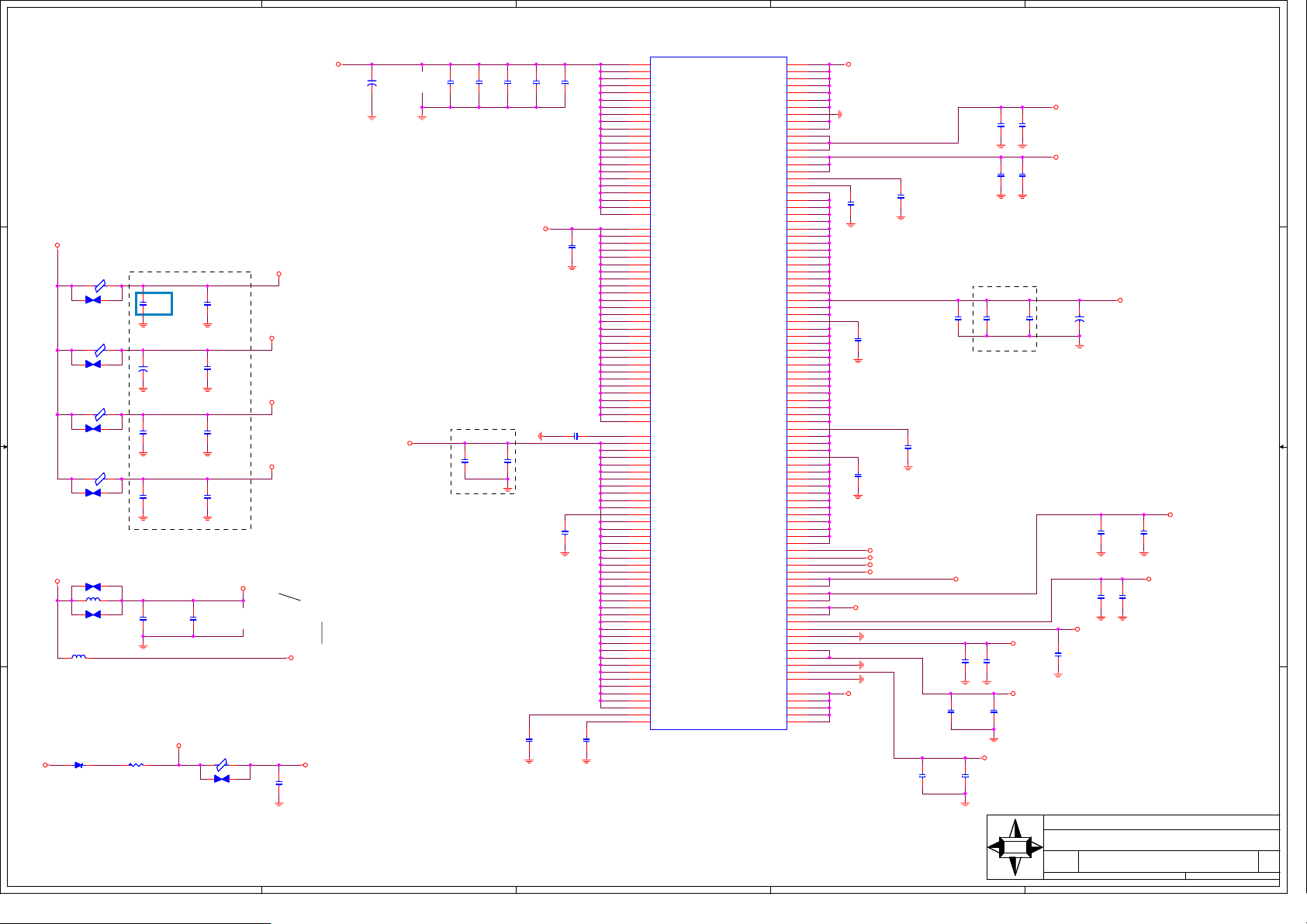

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N011

MS-N011

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Friday, April 11, 2008

Date:

Friday, April 11, 2008

Date:

A

B

C

D

Friday, April 11, 2008

MS-N011

Diamondville signal

Diamondville signal

Diamondville signal

E

Sheet of

Sheet of

Sheet of

239

239

239

1.0

1.0

1.0

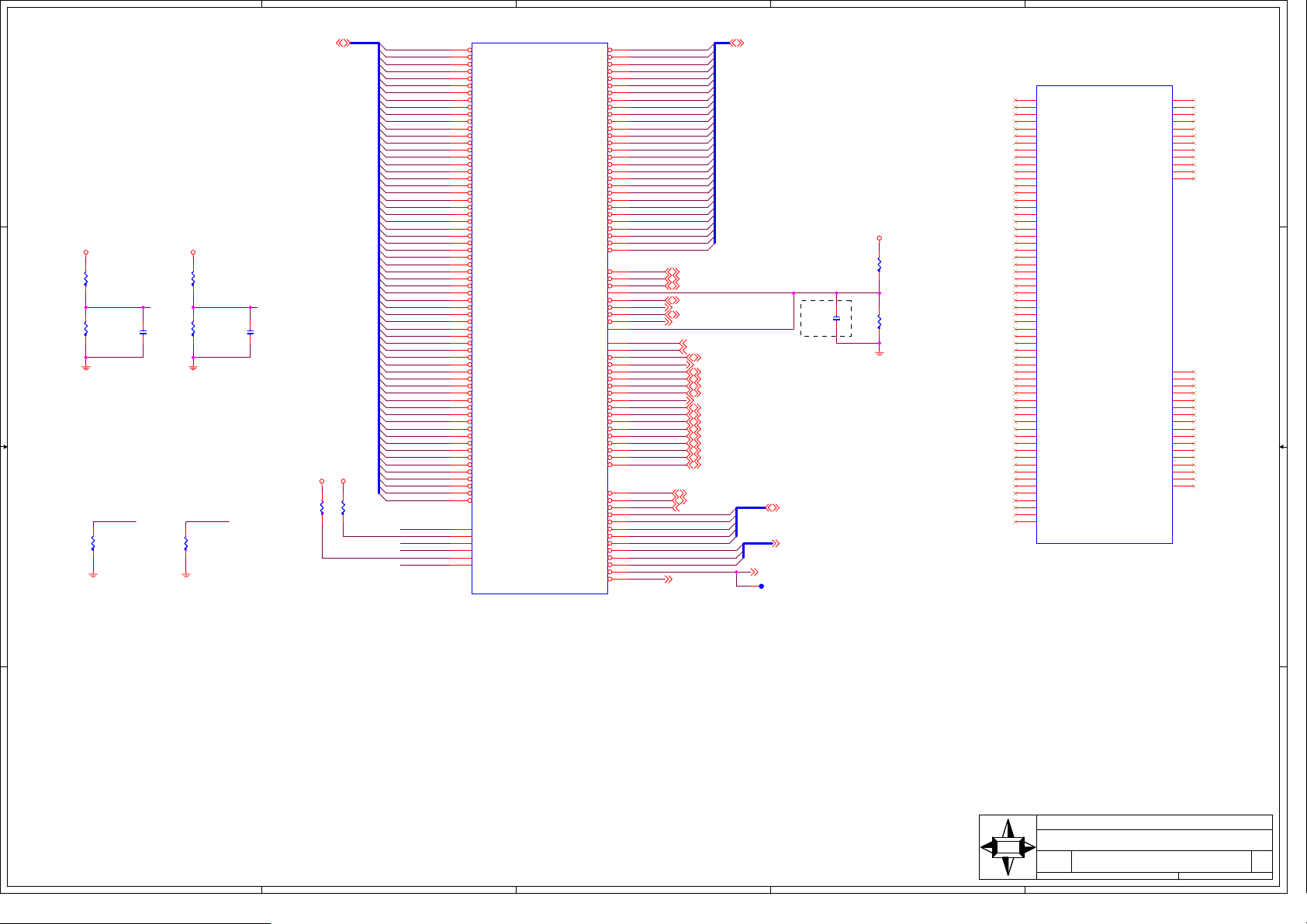

A

U28D

U28D

A2

VSS

A4

VSS

A8

VSS

A15

VSS

A18

VSS

A19

VSS

A20

VSS

4 4

3 3

2 2

B1

VSS

B2

VSS

B5

VSS

B8

VSS

B13

VSS

B20

VSS

B21

VSS

C8

VSS

C17

VSS

D1

VSS

D5

VSS

D8

VSS

D14

VSS

D18

VSS

D21

VSS

E3

VSS

E6

VSS

E7

VSS

E8

VSS

E15

VSS

E16

VSS

E19

VSS

F4

VSS

F5

VSS

F6

VSS

F7

VSS

F17

VSS

F18

VSS

G1

VSS

G4

VSS

G7

VSS

G9

VSS

G13

VSS

G21

VSS

H3

VSS

H4

VSS

H7

VSS

H9

VSS

H13

VSS

H16

VSS

H18

VSS

H19

VSS

J5

VSS

J7

VSS

J9

VSS

J13

VSS

J17

VSS

K1

VSS

K6

VSS

K7

VSS

K9

VSS

K13

VSS

K15

VSS

K21

VSS

L3

VSS

L4

VSS

L5

VSS

L6

VSS

L7

VSS

L9

VSS

L13

VSS

L15

VSS

L18

VSS

L19

VSS

M1

VSS

M5

VSS

M7

VSS

M9

VSS

M13

VSS

Diamondville

Diamondville

LAYOUT NOTE:

Route VCCSENSE and VSSSENSE

traces at 27.4Ohms with 50

mil spacing.

Place PU and PD within 1

inch of CPU.

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N9

N7

N5

N4

M21

N13

N17

P3

P4

P5

P6

P7

P9

P13

P15

P16

P18

P19

R1

R5

R7

R9

R13

R21

T4

T5

T7

T9

T10

T11

T12

T13

T18

U3

U6

U7

U15

U16

U19

V1

V4

V6

V7

V8

V13

V14

V18

V21

W1

W5

W8

W11

W14

W17

W21

Y1

Y2

Y20

Y21

AA2

AA3

AA4

AA7

AA10

AA12

AA15

AA18

AA19

AA20

2.5A: before VCC stable

1.5A: after VCC stable

1.05V

V_CORE

1.1V

B

VTT

M10

M11

M12

U28C

U28C

V10

VCCF

A9

VCCQ1

B9

VCCQ2

A10

VCCP1

A11

VCCP2

A12

VCCP3

B10

VCCP4

B11

VCCP5

B12

VCCP6

C10

VCCP7

C11

VCCP8

C12

VCCP9

D10

VCCP10

D11

VCCP11

D12

VCCP12

E10

VCCP13

E11

VCCP14

E12

VCCP15

F10

VCCP16

F11

VCCP17

F12

VCCP18

G10

VCCP19

G11

VCCP20

G12

VCCP21

H10

VCCP22

H11

VCCP23

H12

VCCP24

J10

VCCP25

J11

VCCP26

J12

VCCP27

K10

VCCP28

K11

VCCP29

K12

VCCP30

L10

VCCP31

L11

VCCP32

L12

VCCP33

VCCP34

VCCP35

VCCP36

N10

VCCP37

N11

VCCP38

N12

VCCP39

P10

VCCP40

P11

VCCP41

P12

VCCP42

R10

VCCP43

R11

VCCP44

R12

VCCP45

Diamondville

Diamondville

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

POWER

POWER

VTT32

VCCPC64

VCCPC63

VCCPC62

VCCPC61

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

C9

D9

E9

F8

F9

G8

G14

H8

H14

J8

J14

K8

K14

L8

L14

M8

M14

N8

N14

P8

P14

R8

R14

T8

T14

U8

U9

U10

U11

U12

U13

U14

F14

F13

E14

E13

D7

F15

D16

E18

G15

G16

E17

G18

C13

D13

130mA

VTT

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

CPU_VID5

CPU_VID6

CPU_VID0 30

CPU_VID1 30

CPU_VID2 30

CPU_VID3 30

CPU_VID4 30

CPU_VID5 30

CPU_VID6 30

+1_5VRUN

C

C141

C141

0.1u10X4

0.1u10X4

C140

C140

0.1u16X6

0.1u16X6

V_CORE

C175

C175

1u6.3X4

1u6.3X4

C142

C142

1u6.3X4

1u6.3X4

Place in cavity

R359

R359

100R1%4

100R1%4

VCCSENSE 30

VSSSENSE 30

R358

R358

100R1%4

100R1%4

C171

C171

X_10u6.3X8

X_10u6.3X8

C139

C139

10u6.3X8

10u6.3X8

Place in cavity

C163

C163

1u6.3X4

1u6.3X4

C160

C160

10u6.3X8

10u6.3X8

D

C159

C159

1u6.3X4

1u6.3X4

Place in cavity

C153

C153

10u6.3X8

10u6.3X8

C154

C154

10u6.3X8

10u6.3X8

C148

C148

1u6.3X4

1u6.3X4

C164

C164

10u6.3X8

10u6.3X8

C152

C152

1u6.3X4

1u6.3X4

C151

C151

1u6.3X4

1u6.3X4

C169

C169

1u6.3X4

1u6.3X4

C161

C161

1u6.3X4

1u6.3X4

C170

C170

10u6.3X8

10u6.3X8

E

V_CORE

V_CORE

V_CORE

C162

C162

X_1u6.3X4

X_1u6.3X4

close to cpu socket

1 1

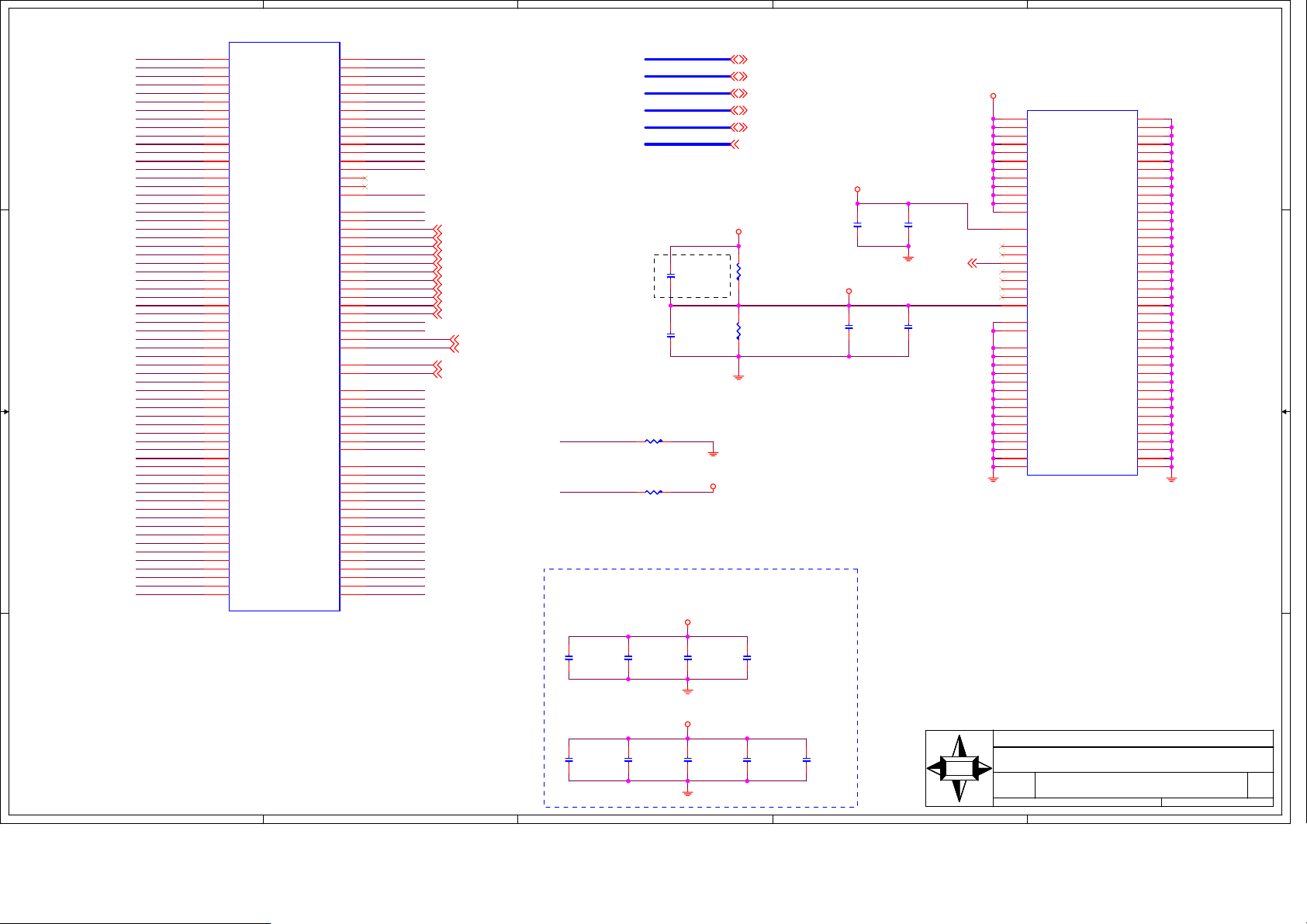

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N011

MS-N011

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Friday, April 11, 2008

Date:

Friday, April 11, 2008

Date:

A

B

C

D

Friday, April 11, 2008

MS-N011

Diamondville Pown/GND

Diamondville Pown/GND

Diamondville Pown/GND

E

Sheet of

Sheet of

Sheet of

1.0

1.0

1.0

339

339

339

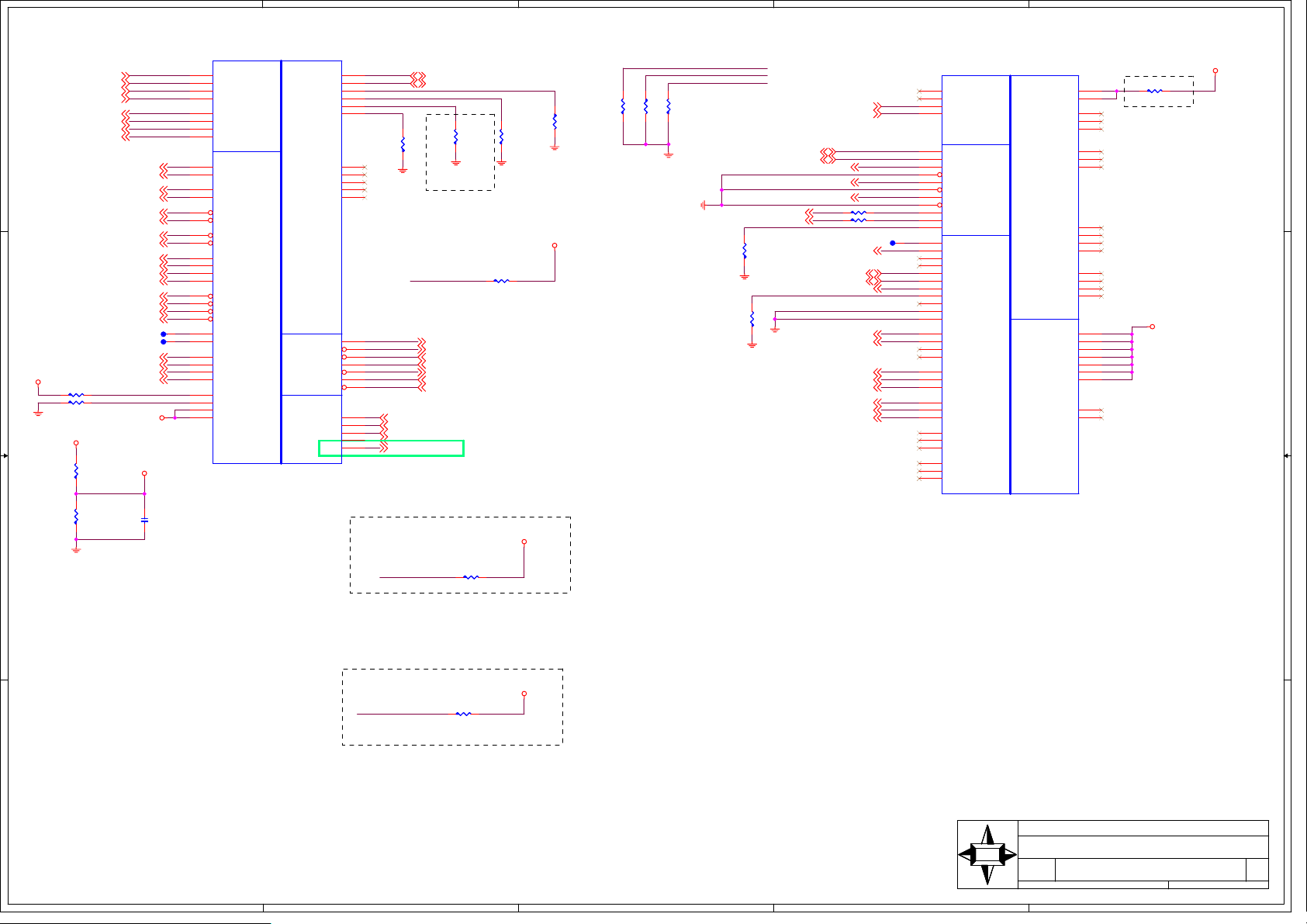

5

H_D#[63:0]2

D D

0.3125 * VTT

Trace wide/spacing=10/20

VTT VTT

R336

R336

221R1%4

221R1%4

HXSWING HYSWING

R335

R335

100R1%4

C C

100R1%4

C408

C408

0.1u10X4

0.1u10X4

Trace wide/spacing=10/20

R329

R329

24.9R1%4

B B

24.9R1%4

R315

R315

221R1%4

221R1%4

R316

R316

100R1%4

100R1%4

HYRCOMPHXRCOMP

R313

R313

24.9R1%4

24.9R1%4

C395

C395

0.1u10X4

0.1u10X4

54.9R1%4

54.9R1%4

R312

R312

VTT

VTT

R328

R328

54.9R1%4

54.9R1%4

4

U26A

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

HXRCOMP

HXSCOMP

HXSWING

HYRCOMP

HYSCOMP

HYSWING

C4

F6

H9

H6

F7

E3

C2

C3

K9

F5

K7

H8

E5

K8

N1

M5

K5

H3

N3

M4

M3

N8

N6

K3

N9

M1

V8

V9

R6

T8

R2

N5

N2

R5

U7

R8

T4

T7

R3

T5

V6

V3

W2

W1

V2

W4

W7

W5

V5

AB4

AB8

W8

AA9

AA8

AB1

AB7

AA2

AB5

A10

A6

C15

K1

H1

J7

J8

J2

J3

J5

J4

J1

U26A

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

H_XRCOMP

H_XSCOMP

H_XSWING

H_YRCOMP

H_YSCOMP

H_YSWING

945GSE

945GSE

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_VREF0

H_BNR#

H_BPRI#

H_BREQ0#

H_CPURST#

H_VREF1

HOST

HOST

H_DBSY#

H_DEFER#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DPWR#

H_DRDY#

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_HITM#

H_LOCK#

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

H_SLPCPU#

H_TRDY#

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

HCLKN

HCLKP

H_HIT#

3

H_DBSY# 2

H_DEFER# 2

H_DINV#0 2

H_DINV#1 2

H_DINV#2 2

H_DINV#3 2

H_DPWR# 2

H_DRDY# 2

H_DSTBN#0 2

H_DSTBN#1 2

H_DSTBN#2 2

H_DSTBN#3 2

H_DSTBP#0 2

H_DSTBP#1 2

H_DSTBP#2 2

H_DSTBP#3 2

H_A#[31:3] 2

place <100mils from pin.

HVREF

C405

C405

0.1u10X4

0.1u10X4

H_REQ#[4:0] 2

H_RS#[2:0] 2

CPUSLP# 2

T6T6

H_A#3

F8

H_A#4

D12

H_A#5

C13

H_A#6

A8

H_A#7

E13

H_A#8

E12

H_A#9

J12

H_A#10

B13

H_A#11

A13

H_A#12

G13

H_A#13

A12

H_A#14

D14

H_A#15

F14

H_A#16

J13

H_A#17

E17

H_A#18

H15

H_A#19

G15

H_A#20

G14

H_A#21

A15

H_A#22

B18

H_A#23

B15

H_A#24

E14

H_A#25

H13

H_A#26

C14

H_A#27

A17

H_A#28

E15

H_A#29

H17

H_A#30

D17

H_A#31

G17

F10

C12

H16

E2

B9

C7

G8

B10

E1

AA6

AA5

C10

H_DEFER#

C6

H_DINV#0

H5

H_DINV#1

J6

H_DINV#2

T9

H_DINV#3

U6

H_DPWR#

G7

H_DRDY#

E6

H_DSTBN#0

F3

H_DSTBN#1

M8

H_DSTBN#2

T1

H_DSTBN#3

AA3

H_DSTBP#0

F4

H_DSTBP#1

M7

H_DSTBP#2

T2

H_DSTBP#3

AB3

C8

B4

C5

H_REQ#0

G9

H_REQ#1

E9

H_REQ#2

G12

H_REQ#3

B8

H_REQ#4

F12

H_RS#0

A5

H_RS#1

B6

H_RS#2

G10

CPUSLP#

E8

E10

H_DBSY#

H_ADS# 2

H_ADSTB#0 2

H_ADSTB#1 2

H_BNR# 2

H_BPRI# 2

H_BREQ# 2

H_CPURST# 2

CLK_MCH_BCLK# 16

CLK_MCH_BCLK 16

H_HIT# 2

H_HITM# 2

H_LOCK# 2

H_TRDY# 2

2

U26G

U26G

W33

NC1

AM33

NC2

AL33

NC3

C33

NC4

B33

NC5

AN32

NC6

A32

NC7

AN31

NC8

W28

NC9

V27

NC10

W29

NC11

J24

NC12

H24

NC13

W32

NC14

G24

NC15

F24

NC16

E24

NC17

D24

NC18

K33

AN19

AM19

AL19

AK19

AJ19

AH19

AN3

G19

G16

AN2

AM4

AD4

AK4

W31

AH4

AG4

AE4

AM1

A31

E21

C23

J19

H19

F19

E19

D19

C19

B19

A19

F16

E16

D16

C16

B16

A16

AF4

AL4

AJ4

Y9

Y8

Y7

945GSE

945GSE

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC26

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC38

NC39

NC40

NC41

NC42

NC43

NC44

NC45

NC46

NC47

NC48

NC49

NC50

NC51

NC52

NC53

NC54

NC55

NC56

NC57

NC58

NC59

NC60

VTT

R325

R325

100R1%4

100R1%4

R324

R324

200R1%4

200R1%4

NC

NC

RESERVED26

RESERVED27

RESERVED28

RESERVED29

RESERVED30

RESERVED31

RESERVED32

RESERVED33

RESERVED34

RESERVED35

RESERVED36

RESERVED37

RESERVED38

RESERVED39

RESERVED40

RESERVED41

RESERVED42

1

NC61

NC62

NC63

NC64

NC65

NC66

NC67

NC68

NC69

NC70

NC71

NC72

W30

Y6

AL1

Y5

Y10

W10

W25

V24

U24

V10

U10

K18

Y25

Y24

AB22

AB21

AB19

AB16

AB14

AA12

W24

AA24

AB24

AB20

AB18

AB15

AB13

AB12

AB17

A A

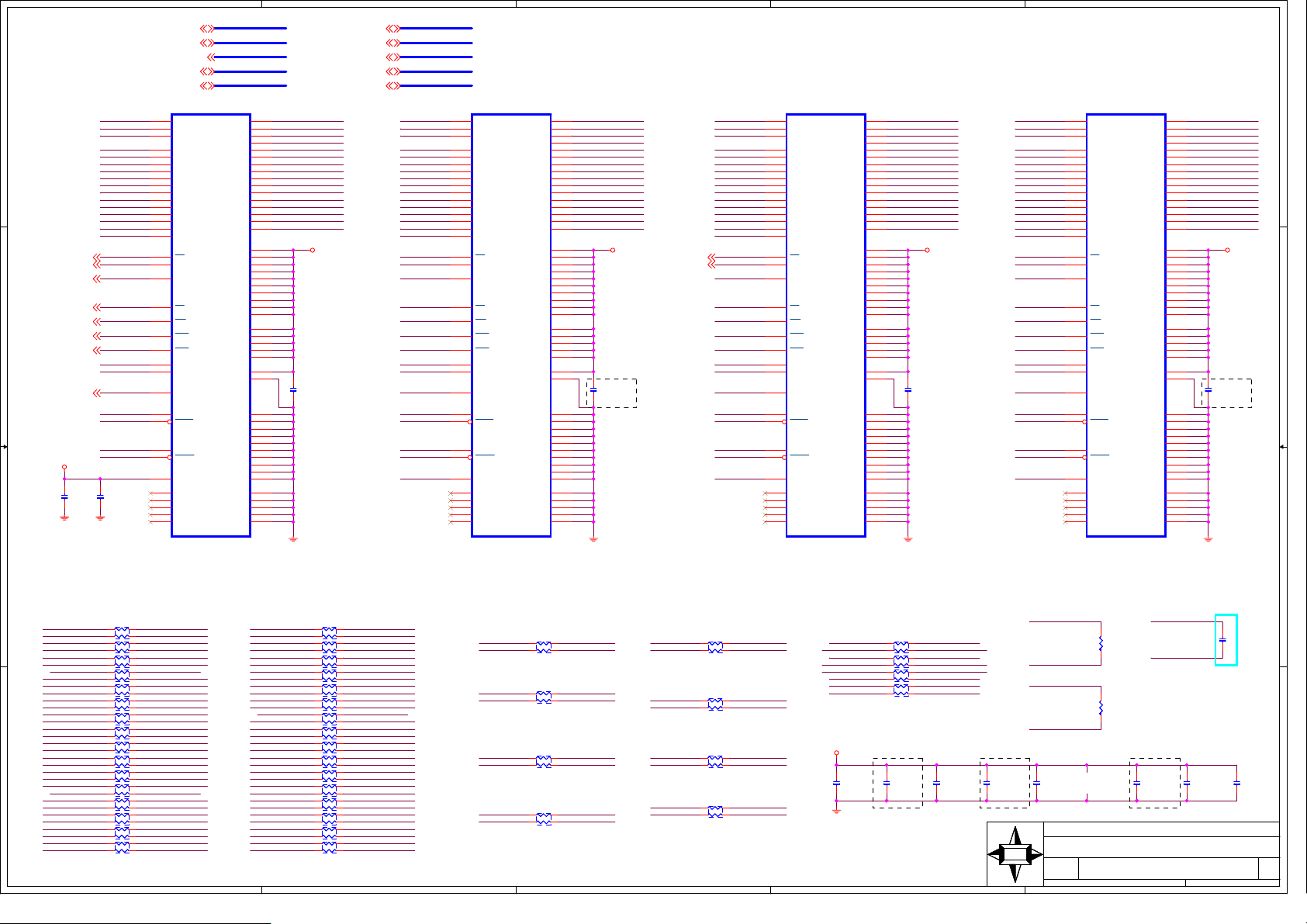

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N011

MS-N011

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Friday, April 11, 2008

Date:

Friday, April 11, 2008

Date:

5

4

3

2

Friday, April 11, 2008

MS-N011

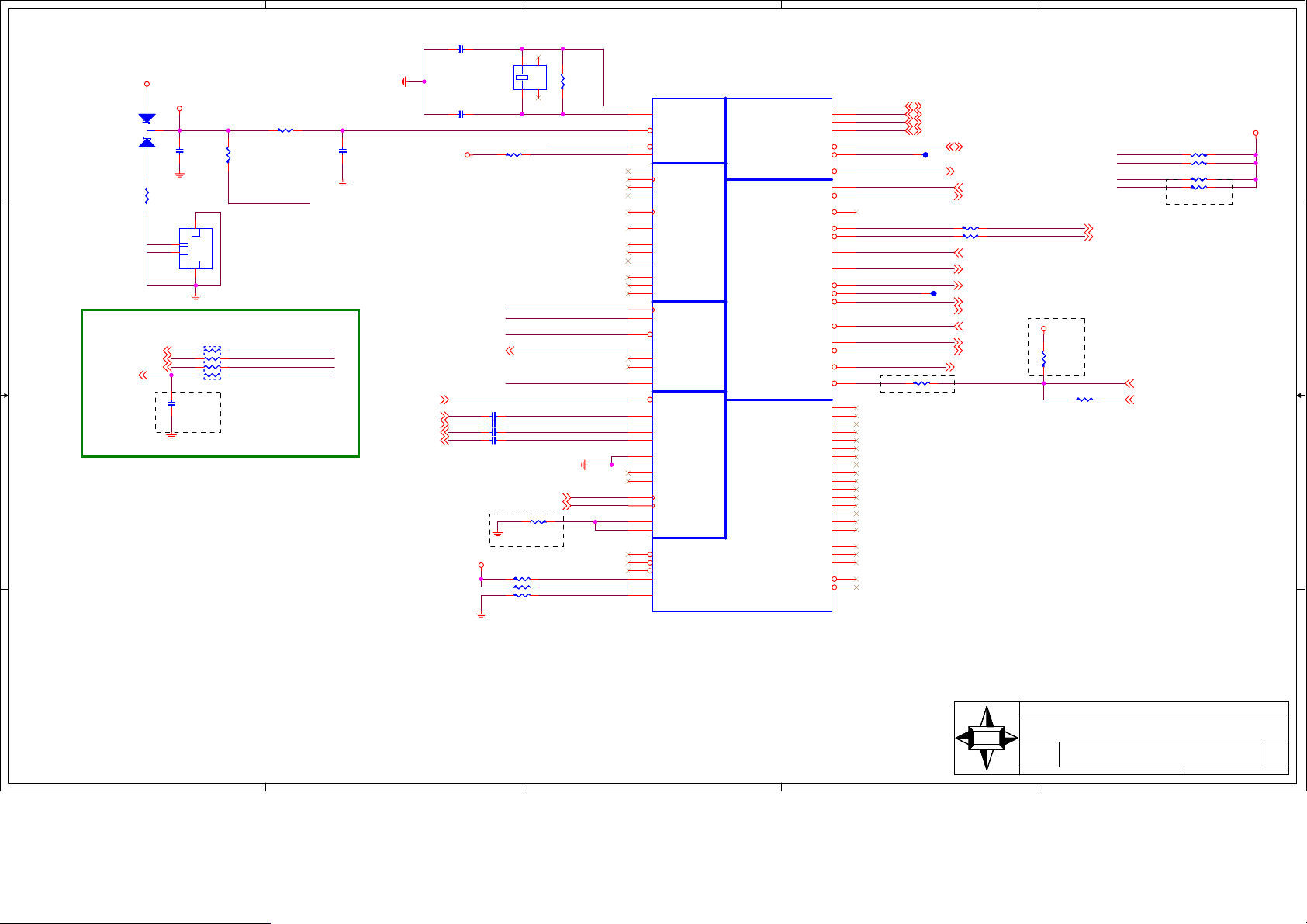

945GMS_HOST

945GMS_HOST

945GMS_HOST

1

Sheet of

Sheet of

Sheet of

439

439

439

1.0

1.0

1.0

5

U26B

Y29

Y32

Y28

Y31

V28

V31

V29

V32

AF33

AG1

AJ1

AM30

AG33

AF1

AK1

AN30

AN21

AN22

AF26

AF25

AG14

AF12

AK14

AH12

AJ21

AF11

AE12

AF14

AJ14

AJ12

AN12

AN14

AA33

AE1

U26B

DMI_RXN_0

DMI_RXN_1

DMI_RXP_0

DMI_RXP_1

DMI_TXN_0

DMI_TXN_1

DMI_TXP_0

DMI_TXP_1

SM_CK_0

SM_CK_1

SM_CK_2

SM_CK_3

SM_CK#_0

SM_CK#_1

SM_CK#_2

SM_CK#_3

SM_CKE_0

SM_CKE_1

SM_CKE_2

SM_CKE_3

SM_CS#_0

SM_CS#_1

SM_CS#_2

SM_CS#_3

SM_OCDCOMP_0

SM_OCDCOMP_1

SM_ODT_0

SM_ODT_1

SM_ODT_2

SM_ODT_3

SM_RCOMPN

SM_RCOMPP

SM_VREF_0

SM_VREF_1

945GSE

945GSE

CFG_0

CFG_1

CFG_2

CFG_3

CFG_5

CFG_6

DMI

DMI

RESERVED1

RESERVED2

RESERVED7

RESERVED8

RESERVED9

CFG/RSVD

CFG/RSVD

DDR2 MUXING

DDR2 MUXING

PM_ICHSYNC#

PM_BMBUSY#

PM_EXTTS#_0

PM_EXTTS#_1

THRMTRIP#

PWROK

RSTIN#

PM

PM

CLK

CLK

D_REFCLKN

D_REFCLKP

D_REFSSCLKN

D_REFSSCLKP

CLKREQ#

CLKREQ#: Driven by GMCH to control the PCIe clock

to External Graphics and the DMI clock.

CLK_SDRAM09,10

CLK_SDRAM19,10

CLK_SDRAM28

CLK_SDRAM38

CLK_SDRAM-09,10

CLK_SDRAM-19,10

CLK_SDRAM-28

CLK_SDRAM-38

DMI_TXN0

DMI_TXN1

DMI_TXP0

DMI_TXP1

DMI_RXN0

DMI_RXN1

DMI_RXP0

DMI_RXP1

CKE09,11

CKE110,11

CKE28,11

CKE38,11

SM_CS-09,11

SM_CS-110,11

SM_CS-28,11

SM_CS-38,11

SM_ODT09,11

SM_ODT110,11

SM_ODT28,11

SM_ODT38,11

SM_VREF

SM_VREF

T4T4

T5T5

M_RCOMPN

M_RCOMPP

C384

C384

0.1u10X4

0.1u10X4

DMI_TXN013

DMI_TXN113

DMI_TXP013

DMI_TXP113

DMI_RXN013

D D

C C

+1_8VDIMM

B B

DMI_RXN113

DMI_RXP013

DMI_RXP113

R306 80.6R1%4R306 80.6R1%4

R305 80.6R1%4R305 80.6R1%4

+1_8VDIMM

R308

R308

10K1%4

10K1%4

R309

R309

10K1%4

10K1%4

as close as

945GM

C18

E18

G20

G18

J20

J18

K32

K31

C17

F18

A3

E31

G21

F26

H26

J15

AB29

W27

A27

A26

J33

H33

J22

X_2.2K/4

X_2.2K/4

4

MCH_BSEL0 16

R136

R136

MCH_BSEL1 16

CFG_5

R138

R138

2.2K/4

2.2K/4

MCH_BSEL2

R141

R141

X_2.2K/4

X_2.2K/4

LOW=DMIX2

PM_EXTTS#0

R146 10K/4R146 10K/4

PM_EXTTS#0: memory thermal throttling

MCH_ICH_SYNC# 13

PM_BMBUSY# 14

PM_EXTTS#0 8

PM_DPRSLPVR 14,30

THERMTRIP_GMCH# 12

CHIP_PWRGD 14,17,19

NB_RST# 13

CLK_DOT96# 16

CLK_DOT96 16

CLK_GFX_REFCLKN 16

CLK_GFX_REFCLKP 16

MCH_CLKREQ# 16

+3VRUN

MCH_CLKREQ#

R149 10K/4R149 10K/4

+3VRUN

1K/4

1K/4

R142

R142

3

R331

R331

R332

R332

R330

R330

150R1%4

150R1%4

150R1%4

150R1%4

150R1%4

150R1%4

SXGA+ 1400x1050

60Hz

R145

R145

255R1%4

255R1%4

R311

R311

1.5K1%4

1.5K1%4

800x480

VGA_B

VGA_G

VGA_R

2

U26F

U26F

H27

SDVO_CTRLDATA

J27

SDVO_CTRLCLK

CLK_PCIE_3GPLL#16

CLK_PCIE_3GPLL16

VGA_CLK21

VGA_DATA21

VGA_B21

VGA_G21

VGA_VSYNC21

VGA_HSYNC21

VGA_R21

LVDS_CLK21

LVDS_DATA21

LVDS_VDDEN21

LVDS_TXCKN21

LVDS_TXCKP21

R153 39R/4R153 39R/4

R152 39R/4R152 39R/4

LVDS_BLON21

LVDS_TX0N21

LVDS_TX1N21

LVDS_TX2N21

LVDS_TX0P21

LVDS_TX1P21

LVDS_TX2P21

VGA_B

VGA_G

VGA_R

Y26

G_CLKN

AA26

G_CLKP

H20

CRT_DDC_CLK

H22

CRT_DDC_DATA

A24

CRT_BLUE

A23

CRT_BLUE#

E25

CRT_GREEN

F25

CRT_GREEN#

C25

CRT_RED

D25

CRT_RED#

F27

CRT_VSYNC

D27

CRT_HSYNC

H25

CRT_IREF

H30

T31T31

G29

F28

E28

G28

H28

K30

K27

K29

D30

C30

A30

A29

G31

F32

D31

H31

G32

C31

F33

D33

F30

E33

D32

F29

J29

J30

L_BKLTCTL

L_BKLTEN

L_CLKCTLA

L_CTLBDATA

L_DDC_CLK

L_DDC_DATA

L_VDDEN

L_IBG

L_VBG

L_VREFH

L_VREFL

LA_CLKN

LA_CLKP

LB_CLKN

LB_CLKP

LA_DATAN_0

LA_DATAN_1

LA_DATAN_2

LA_DATAP_0

LA_DATAP_1

LA_DATAP_2

LB_DATAN_0

LB_DATAN_1

LB_DATAN_2

LB_DATAP_0

LB_DATAP_1

LB_DATAP_2

945GSE

945GSE

EXP_A_COMPI

EXP_A_ICOMPO

SDVO_TVCLKIN#

SDVO_FLDSTALL#

MISC

MISC

SDVO_TVCLKIN

SDVO_FLDSTALL

SDVO

SDVO

SDVO_RED#

SDVO_GREEN#

SDVO_BLUE#

SDVO_CLKN

SDVO_GREEN

SDVO_BLUE

SDVO_CLKP

TV

TV

LVDS VGA

LVDS VGA

TV_DCONSEL0

TV_DCONSEL1

SDVO_INT#

SDVO_RED

SDVO_INT

TV_DACA

TV_DACB

TV_DACC

TV_IREF

TV_IRTNA

TV_IRTNB

TV_IRTNC

R28

M28

N30

R30

T29

M30

P30

T30

P28

N32

P32

T32

N28

M32

P33

R32

A21

C20

E20

G23

B21

C21

D21

G26

J26

1

+1_5VRUN_PCIE

R122 24.9R1%4R122 24.9R1%4

Layout within 500mil

of GMCH pin out.

+1_5VRUN

Disable TV

DPRSLPVR: Enable power savings by speeding up the C4 exit latency.

+3VRUN

PM_DPRSLPVR

R148 X_10K/4R148 X_10K/4

un-stuffed, if support C4E feature.

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N011

MS-N011

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Friday, April 11, 2008

Date:

Friday, April 11, 2008

Date:

Friday, April 11, 2008

5

4

3

2

MS-N011

945GMS_DMI/ VGA

945GMS_DMI/ VGA

945GMS_DMI/ VGA

1

Sheet of

Sheet of

Sheet of

539

539

539

1.0

1.0

1.0

5

SA_MD[0..63]8,9

D D

C C

SB_CAS-8,11

SB_RAS-8,11

B B

SB_WE-8,11

SA_MD0

SA_MD1

SA_MD2

SA_MD3

SA_MD4

SA_MD5

SA_MD6

SA_MD7

SA_MD8

SA_MD9

SA_MD10

SA_MD11

SA_MD12

SA_MD13

SA_MD14

SA_MD15

SA_MD16

SA_MD17

SA_MD18

SA_MD19

SA_MD20

SA_MD21

SA_MD22

SA_MD23

SA_MD24

SA_MD25

SA_MD26

SA_MD27

SA_MD28

SA_MD29

SA_MD30

SA_MD31

SA_MD32

SA_MD33

SA_MD34

SA_MD35

SA_MD36

SA_MD37

SA_MD38

SA_MD39

SA_MD40

SA_MD41

SA_MD42

SA_MD43

SA_MD44

SA_MD45

SA_MD46

SA_MD47

SA_MD48

SA_MD49

SA_MD50

SA_MD51

SA_MD52

SA_MD53

SA_MD54

SA_MD55

SA_MD56

SA_MD57

SA_MD58

SA_MD59

SA_MD60

SA_MD61

SA_MD62

SA_MD63

SB_CASSB_RAS-

SB_WE-

AC31

AB28

AE33

AF32

AC33

AB32

AB31

AE31

AH31

AK31

AL28

AK27

AH30

AL32

AJ28

AJ27

AH32

AF31

AH27

AF28

AJ32

AG31

AG28

AG27

AN27

AM26

AJ26

AJ25

AL27

AN26

AH25

AG26

AM12

AL11

AH9

AK9

AM11

AK11

AM8

AK8

AG9

AK6

AG11

AH6

AN6

AM6

AK3

AM5

AG2

AE7

AH5

AG3

AG5

AG19

AG21

AG20

AF9

AF8

AF7

AJ6

AL2

AL5

AJ3

AJ2

AF3

AF6

AF5

U26C

U26C

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SB_CAS#

SB_RAS#

SB_WE#

945GSE

945GSE

SA_BS_0

SA_BS_1

SA_BS_2

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_CAS#

DDR2 SYSTEM MEMORY

DDR2 SYSTEM MEMORY

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

SB_BS_0

SB_BS_1

SB_BS_2

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

AK12

AH11

AG17

AB30

AL31

AF30

AK26

AL9

AG7

AK5

AH3

AC28

AJ30

AK33

AL25

AN9

AH8

AM2

AE3

AC29

AK30

AJ33

AM25

AN8

AJ8

AM3

AE2

AJ15

AM17

AM15

AH15

AK15

AN15

AJ18

AF19

AN17

AL17

AG16

AL18

AG18

AL14

AJ17

AK18

AN28

AM28

AH17

AH21

AJ20

AE27

AN20

AL21

AK21

AK22

AL22

AH22

AG22

AF21

AM21

AE21

AL20

AE22

AE26

AE20

4

SA_BS-0

SA_BS-1

SA_BS-2

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS-0

SA_DQS-1

SA_DQS-2

SA_DQS-3

SA_DQS-4

SA_DQS-5

SA_DQS-6

SA_DQS-7

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS-

SA_RASSA_RCVENIN-

SA_RCVENOUT-

SA_WESB_BS-0

SB_BS-1

SB_BS-2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SA_BS-[0..2] 9,10,11

SA_DM[0..7] 8,9

SA_DQS[0..7] 8,9

SA_DQS-[0..7] 8,9

SA_MA[0..13] 9,10,11

SA_CAS- 9,10,11

SA_RAS- 9,10,11

T2T2

T3T3

SA_WE- 9,10,11

SB_MA[0..13] 8,11

SB_BS-[0..2] 8,11

3

VTT

VTT

W22

W21

W20

W14

AB10

AA10

M25

P24

N24

M24

Y22

V22

U22

R22

P22

N22

M22

Y21

V21

U21

R21

P21

N21

M21

Y20

V20

U20

R20

P20

N20

M20

Y19

P19

N19

M19

Y18

P18

N18

M18

Y17

P17

N17

M17

Y16

P16

N16

M16

Y15

P15

N15

M15

Y14

V14

U14

R14

P14

N14

M14

R10

P10

N10

M10

A18

T25

R25

P25

N25

T22

T21

T20

T14

T10

L10

D1

U26H

U26H

VCC_NCTF1

VCC_NCTF2

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VTT_NCTF1

VTT_NCTF2

VTT_NCTF3

VTT_NCTF4

VTT_NCTF5

VTT_NCTF6

RSVD_3

RSVD_4

RSVD_5

RSVD_6

NCTF

NCTF

945GSE

945GSE

VCCAUX_NCTF1

VCCAUX_NCTF2

VCCAUX_NCTF3

VCCAUX_NCTF4

VCCAUX_NCTF5

VCCAUX_NCTF6

VCCAUX_NCTF7

VCCAUX_NCTF8

VCCAUX_NCTF9

VCCAUX_NCTF10

VCCAUX_NCTF11

VCCAUX_NCTF12

VCCAUX_NCTF13

VCCAUX_NCTF14

VCCAUX_NCTF15

VCCAUX_NCTF16

VCCAUX_NCTF17

VCCAUX_NCTF18

VCCAUX_NCTF19

VCCAUX_NCTF20

VCCAUX_NCTF21

VCCAUX_NCTF22

VCCAUX_NCTF23

VCCAUX_NCTF24

VCCAUX_NCTF25

VCCAUX_NCTF26

VCCAUX_NCTF27

VCCAUX_NCTF28

VCCAUX_NCTF29

VCCAUX_NCTF30

VCCAUX_NCTF31

VCCAUX_NCTF32

VCCAUX_NCTF33

VCCAUX_NCTF34

VCCAUX_NCTF35

VCCAUX_NCTF36

VCCAUX_NCTF37

VCCAUX_NCTF38

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VSS_NCTF13

VSS_NCTF14

VSS_NCTF15

VSS_NCTF16

VSS_NCTF17

VSS_NCTF18

VSS_NCTF19

RESERVED10

RESERVED11

RESERVED12

RESERVED13

RESERVED14

RESERVED15

RESERVED16

RESERVED17

RESERVED18

RESERVED19

RESERVED20

RESERVED21

RESERVED22

RESERVED23

RESERVED24

RESERVED25

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

CFG_19

2

+1_5VRUN

AD25

AC25

AB25

AD24

AC24

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

K14

AD13

Y13

W13

V13

U13

T13

R13

P13

N13

M13

AD12

Y12

W12

V12

U12

T12

R12

P12

N12

M12

AD11

AD10

K10

AN33

AA25

V25

U25

AA22

AA21

AA20

AA19

AA18

AA17

AA16

AA15

AA14

AA13

A4

A33

B2

AN1

C1

K28

CFG_19: DMI Lane Reversal

K25

K26

0= default (internal pull-down)

R24

1= Reversal Lanes

T24

(945GMS does not support)

K21

K19

K20

K24

K22

J17

K23

K17

K12

K13

K16

K15

1

U16

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

A A

5

VSS_104

VSS_105

VSS_101

VSS_102

VSS_103

AH18

AM18

VSS_99

VSS_98

VSS_100

W19

R19

VSS_97

D20

VSS_96

VSS_95

AF20

AH20

VSS_94

AK20

VSS_92

VSS_93

F21

AM20

VSS_90

VSS_91

J21

H21

VSS_89

E22

VSS_87

VSS_88

AF22

G22

VSS_86

VSS_85

AJ22

AM22

VSS_84

B23

VSS_82

VSS_83

H23

F23

VSS_81

A25

VSS_79

VSS_80

G25

J25

AE25

VSS_77

VSS_78

R1

AK25

AG25

VSS_74

VSS_75

VSS_76

VSS_183

VSS_184

VSS_185

F2

V1

U26

AN25

VSS_72

VSS_73

VSS_181

VSS_182

K2

H2

4

W26

M2

AL26

AH26

VSS_69

VSS_71

VSS_70

VSS_178

VSS_179

VSS_180

AF2

AB2

C27

B27

VSS_67

VSS_68

VSS_176

VSS_177

AK2

AH2

G27

E27

VSS_65

VSS_66

VSS_174

VSS_175

T3

B3

M27

VSS_64

VSS_173

W3

P27

N27

VSS_62

VSS_63

VSS_171

VSS_172

AL3

AD3

T27

R27

VSS_60

VSS_61

VSS_169

VSS_170

E4

H4

Y27

U27

VSS_58

VSS_59

VSS_167

VSS_168

K4

N4

AA27

VSS_57

VSS_166

R4

AM27

AF27

AB27

VSS_54

VSS_55

VSS_56

VSS

VSS

VSS_163

VSS_164

VSS_165

B5

V4

AA4

J28

D28

VSS_52

VSS_53

VSS_161

VSS_162

AJ5

AN5

U28

T28

VSS_50

VSS_51

VSS_159

VSS_160

K6

M6

AE28

AA28

VSS_48

VSS_49

VSS_157

VSS_158

T6

W6

AK28

AH28

VSS_46

VSS_47

VSS_155

VSS_156

AE6

AB6

E29

B29

VSS_44

VSS_45

VSS_153

VSS_154

AL6

AG6

H29

VSS_43

VSS_152

B7

N29

M29

VSS_41

VSS_42

VSS_150

VSS_151

E7

H7

R29

P29

VSS_39

VSS_40

VSS_148

VSS_149

R7

N7

AA29

U29

VSS_37

VSS_38

VSS_146

VSS_147

V7

AA7

B30

VSS_36

VSS_145

U8

3

G30

E30

VSS_34

VSS_35

VSS_143

VSS_144

AE8

AG8

V30

U30

VSS_32

VSS_33

VSS_141

VSS_142

A9

AL8

AA30

Y30

VSS_30

VSS_31

VSS_139

VSS_140

F9

C9

AC30

VSS_29

VSS_138

J9

AG30

AE30

VSS_27

VSS_28

VSS_136

VSS_137

R9

M9

F31

AL30

VSS_25

VSS_26

VSS_134

VSS_135

W9

AB9

M31

J31

VSS_23

VSS_24

VSS_132

VSS_133

AJ9

AM9

N31

VSS_22

VSS_131

AE11

R31

P31

VSS_20

VSS_21

VSS_129

VSS_130

AJ11

AN11

U31

T31

VSS_18

VSS_19

VSS_127

VSS_128

B12

H12

AJ31

AA31

VSS_16

VSS_17

VSS_125

VSS_126

AL12

AG12

AM31

VSS_15

VSS_124

D13

E32

C32

VSS_13

VSS_14

VSS_122

VSS_123

F13

B14

U32

H32

VSS_11

VSS_12

VSS_120

VSS_121

H14

AE14

AC32

AA32

VSS_9

VSS_10

VSS_118

VSS_119

AH14

AM14

AE32

VSS_8

VSS_117

D15

AK32

AG32

VSS_6

VSS_7

VSS_115

VSS_116

F15

R15

R33

G33

VSS_4

VSS_5

VSS_113

VSS_114

W15

AG15

Y33

V33

VSS_2

VSS_3

VSS_111

VSS_112

J16

AL15

AH33

VSS_1

2

U26E

U26E

945GSE

945GSE

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N011

MS-N011

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Friday, April 11, 2008

Date:

Friday, April 11, 2008

Date:

Friday, April 11, 2008

MS-N011

945GMS_DDR

945GMS_DDR

945GMS_DDR

1

Sheet of

Sheet of

Sheet of

639

639

639

1.0

1.0

1.0

AF18

U18

H18

D18

AK17

V17

T17

F17

B17

AH16

5

4

3

2

1

2940mA

C407

945 GMS Power

VTT

C220u6.3-RH

C220u6.3-RH

EC16

EC16

C407

C406

C385

+

+

12

C385

C406

4.7u6.3X8

4.7u6.3X8

X_0.1u10X4

4.7u6.3X8

4.7u6.3X8

X_0.1u10X4

C388

C388

C100

C100

0.1u10X4

0.1u10X4

X_0.1u10X4

X_0.1u10X4

VTT=> 3.72A

D D

+1_5VRUN=> 1.98A

+1_8VDIMM=> 1.72A

+2_5VRUN=>142mA

+3VRUN=> 40mA

+1_5VRUN

L26

L26

X_120L600mA-250

X_120L600mA-250

CP21

CP21

X_COPPER

X_COPPER

L25

C C

L25

X_120L600mA-250

X_120L600mA-250

CP20

CP20

X_COPPER

X_COPPER

L3

L3

X_120L600mA-250

X_120L600mA-250

CP6

CP6

X_COPPER

X_COPPER

L2

L2

X_120L600mA-250

X_120L600mA-250

CP5

CP5

X_COPPER

X_COPPER

C256

C256

12

+

+

EC10

EC10

X_C100U6.3PT

X_C100U6.3PT

C97

C97

X_22u6.3X8

X_22u6.3X8

C88

C88

X_22u6.3X8

X_22u6.3X8

X_10u25X12

X_10u25X12

50mA

45mA

50mA

45mA

C412

C412

0.1u10X4

0.1u10X4

C393

C393

0.1u10X4

0.1u10X4

C95

C95

0.1u10X4

0.1u10X4

C89

C89

0.1u10X4

0.1u10X4

+1_5VRUN_DPLLA

+1_5VRUN_DPLLB

+1_5VRUN_HPLL

780mA

VTT

+1_5VRUN_MPLL

Place in cavity

Place close to 945GMS

B B

VTT

A A

X_COPPER

X_COPPER

CP19

CP19

+1_5VRUN

L22

L22

X_91n1.5A_1210

X_91n1.5A_1210

CP18

CP18

X_COPPER

X_COPPER

L4

L4

1u500mA_0805

1u500mA_0805

D26

D26

S-RB551V-30_SOD323

S-RB551V-30_SOD323

R157

R157

10R/4

10R/4

+1_5VRUN_PCIE

400mA

C387

C387

10u6.3X8

10u6.3X8

5

+2_5VRUN

C386

C386

X_4.7u6.3X8

X_4.7u6.3X8

L7

L7

X_100L3A-30-RH

X_100L3A-30-RH

CP14

CP14

X_COPPER

X_COPPER

+1_5VRUN_3GPLL

70mA

C135

C135

10u6.3X8

10u6.3X8

+2_5VRUN_CRT

4

1250mA

DDR2 DLL

DDR2

FSB HSIO

C109

C109

X_4.7u6.3X8

X_4.7u6.3X8

0.47u10X6

0.47u10X6

+1_5VRUN

C99

C99

X_0.1u10X4

X_0.1u10X4

C104

C104

4.7u6.3X8

4.7u6.3X8

0.47u10X6

0.47u10X6

C381

C381

C413 0.47u10X6C413 0.47u10X6

C409

C409

C400

C400

0.47u10X6

0.47u10X6

M26

W18

W17

W16

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AC27

AD26

AC26

AB26

AE19

AE18

AF17

AE17

AF16

AE16

AF15

AE15

AE9

AD9

AD8

AD7

AD6

AA1

T26

R26

P26

N26

V19

U19

T19

V18

T18

R18

U17

R17

V16

T16

R16

V15

U15

T15

H10

A14

D10

J14

J10

U9

P9

L9

D9

P8

L8

D8

P7

L7

D7

A7

P6

L6

G6

D6

U5

P5

L5

G5

D5

Y4

U4

P4

L4

G4

D4

Y3

U3

P3

L3

G3

D3

Y2

U2

P2

L2

G2

D2

F1

U26D

U26D

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCCAUX1

VCCAUX2

VCCAUX3

VCCAUX4

VCCAUX5

VCCAUX6

VCCAUX7

VCCAUX8

VCCAUX9

VCCAUX10

VCCAUX11

VCCAUX12

VCCAUX13

VCCAUX14

VCCAUX15

VCCAUX16

VCCAUX17

VCCAUX18

VCCAUX19

VCCAUX20

VCCAUX21

VCCAUX22

VCCAUX23

VCCAUX24

VCCAUX25

VCCAUX26

VCCAUX27

VCCAUX28

VTT0

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VTT34

VTT36

VTT35

VTT37

VTT38

VTT39

VTT40

3

945GSE

945GSE

VCCATVDACA0

VCCATVDACA1

VCCATVDACB0

VCCATVDACB1

VCCATVDACC0

VCCATVDACC1

VCCATVBG

VSSATVBG

VCCDTVDAC

VCCDQTVDAC

VCCDLVDS0

VCCDLVDS1

VCCDLVDS2

VCCHV0

VCCHV1

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

POWER

POWER

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCAMPLL

VCCAHPLL

VCCADPLLA

VCCADPLLB

VCCDHMPLL1

VCCDHMPLL2

VCCTXLVDS0

VCCTXLVDS1

VCC3G0

VCC3G1

VCCA3GPLL

VCCA3GBG

VSSA3GBG

VCCSYNC

VCCACRTDAC0

VCCACRTDAC1

VSSACRTDAC

VCCALVDS

VSSALVDS

VTT41

VTT42

VTT43

VTT44

VTT45

B20

A20

B22

A22

D22

C22

D23

E23

F20

F22

C28

B28

A28

E26

D26

C26

AB33

AM32

AN29

AM29

AL29

AK29

AJ29

AH29

AG29

AF29

AE29

AN24

AM24

AL24

AK24

AJ24

AH24

AG24

AF24

AE24

AN18

AN16

AM16

AL16

AK16

AJ16

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AN4

AM10

AL10

AK10

AH1

AH10

AG10

AF10

AE10

AN7

AM7

AL7

AK7

AJ7

AH7

AN10

AJ10

AD1

AD2

B26

J32

AE5

AD5

D29

C29

U33

T33

V26

N33

M33

J23

C24

B24

B25

B31

B32

P1

L1

G1

U1

Y1

+1_5VRUN

Disable TV

120mA

C377

C377

1u6.3Y4

1u6.3Y4

C378

C378

1u6.3Y4

1u6.3Y4

C86

C86

1u6.3Y4

1u6.3Y4

+1_5VRUN_MPLL

+1_5VRUN_HPLL

+1_5VRUN_DPLLA

+1_5VRUN_DPLLB

+1_5VRUN_PCIE

VTT

2

C383

C383

1u6.3Y4

1u6.3Y4

10mA

C379

C379

1u6.3Y4

1u6.3Y4

C380

C380

1u6.3Y4

1u6.3Y4

X_0.1u10X4

X_0.1u10X4

C399

C399

X_0.01u16X4

X_0.01u16X4

C389

C389

0.1u10X4

0.1u10X4

0.1u10X4

0.1u10X4

+1_5VRUN

C132

C132

0.022u16X4

0.022u16X4

C136

C376

C376

2.2u6.3Y6

2.2u6.3Y6

C136

X_10u10Y8

X_10u10Y8

C418

C418

10u10Y8

10u10Y8

C375

C375

2.2u6.3Y6

2.2u6.3Y6

C134

C134

C124

C124

Place in cavity

+2_5VRUN

C122

C122

X_10u10Y8

X_10u10Y8

+2_5VRUN_CRT

C137

C137

0.1u10X4

0.1u10X4

+2_5VRUN

C404

C404

X_0.1u10X4

X_0.1u10X4

MSI

MSI

MSI

+1_5VRUN

20mA

+3VRUN

40mA

1720mA

DDR2 One Channel

EC8

EC8

C220u6.3-RH

C220u6.3-RH

C123

C123

X_0.1u10X4

X_0.1u10X4

+1_8VDIMM

+1_5VRUN_3GPLL

C112

C112

X_4.7u6.3X8

X_4.7u6.3X8

C129

C129

4.7u6.3X8

4.7u6.3X8

+2_5VRUN

60mA

0.1u10X4

0.1u10X4

12

+

+

C110

C110

+2_5VRUN

2mA

C390

C390

0.1u10X4

0.1u10X4

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N011

MS-N011

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Friday, April 11, 2008

Date:

Friday, April 11, 2008

Date:

Friday, April 11, 2008

MS-N011

945GMS_POWER

945GMS_POWER

945GMS_POWER

1

Sheet of

Sheet of

Sheet of

739

739

739

1.0

1.0

1.0

5

DIMM1A

DIMM1A

SA_MD0

SA_MD1

SA_MD2

SA_MD3

SA_MD4

SA_MD5

D D

C C

B B

SA_MD6

SA_MD7

SA_MD8

SA_MD9

SA_MD10

SA_MD11

SA_MD12

SA_MD13

SA_MD14

SA_MD15

SA_MD16

SA_MD17

SA_MD18

SA_MD19

SA_MD20

SA_MD21

SA_MD22

SA_MD23

SA_MD24

SA_MD25

SA_MD26

SA_MD27

SA_MD28

SA_MD29

SA_MD30

SA_MD31

SA_MD32

SA_MD33

SA_MD34

SA_MD35

SA_MD36

SA_MD37

SA_MD38

SA_MD39

SA_MD40

SA_MD41

SA_MD42

SA_MD43

SA_MD44

SA_MD45

SA_MD46

SA_MD47

SA_MD48

SA_MD49

SA_MD50

SA_MD51

SA_MD52

SA_MD53

SA_MD54

SA_MD55

SA_MD56

SA_MD57

SA_MD58

SA_MD59

SA_MD60

SA_MD61

SA_MD62

SA_MD63

5

DQ0

7

DQ1

17

DQ2

19

DQ3

4

DQ4

6

DQ5

14

DQ6

16

DQ7

23

DQ8

25

DQ9

35

DQ10

37

DQ11

20

DQ12

22

DQ13

36

DQ14

38

DQ15

43

DQ16

45

DQ17

55

DQ18

57

DQ19

44

DQ20

46

DQ21

56

DQ22

58

DQ23

61

DQ24

63

DQ25

73

DQ26

75

DQ27

62

DQ28

64

DQ29

74

DQ30

76

DQ31

123

DQ32

125

DQ33

135

DQ34

137

DQ35

124

DQ36

126

DQ37

134

DQ38

136

DQ39

141

DQ40

143

DQ41

151

DQ42

153

DQ43

140

DQ44

142

DQ45

152

DQ46

154

DQ47

157

DQ48

159

DQ49

173

DQ50

175

DQ51

158

DQ52

160

DQ53

174

DQ54

176

DQ55

179

DQ56

181

DQ57

189

DQ58

191

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

DIMM-200S_black-1

DIMM-200S_black-1

A10/AP

A11

A12

A13

A14

A15

A16_BA2

BA0

BA1

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

85

107

106

110

115

30

32

164

166

79

80

113

108

109

198

200

197

195

114

119

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

4

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_BS-2

SB_BS-0

SB_BS-1

SM_CS-2

SM_CS-3

CLK_SDRAM3

CLK_SDRAM-3

CLK_SDRAM2

CLK_SDRAM-2

CKE2

CKE3

SB_CASSB_RASSB_WE-

SA_SA0

SA_SA1

RUN_SMBCLK

RUN_SMBDATA

SM_ODT2

SM_ODT3

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS-0

SA_DQS-1

SA_DQS-2

SA_DQS-3

SA_DQS-4

SA_DQS-5

SA_DQS-6

SA_DQS-7

SM_CS-2 5,11

SM_CS-3 5,11

CLK_SDRAM3 5

CLK_SDRAM-3 5

CLK_SDRAM2 5

CLK_SDRAM-2 5

CKE2 5,11

CKE3 5,11

SB_CAS- 6,11

SB_RAS- 6,11

SB_WE- 6,11

RUN_SMBCLK 14,16

RUN_SMBDATA 14,16

SM_ODT2 5,11

SM_ODT3 5,11

3

SA_MD[0..63]

SA_DM[0..7]

SA_DQS[0..7]

SA_DQS-[0..7]

SB_MA[0..13]

SB_BS-[0..2]

CT27

CT27

X_0.01u16X4

X_0.01u16X4

CT24

CT24

0.01u16X4

0.01u16X4

SA_SA1

SA_SA0

R284 10K/4R284 10K/4

R283 10K/4R283 10K/4

Layout note: Place capacitors between and

near DDR connector if possible.

+3VRUN

+1_8VDIMM

+1_8VDIMM

R74

R74

10K1%4

10K1%4

R75

R75

10K1%4

10K1%4

SA_MD[0..63] 6,9

SA_DM[0..7] 6,9

SA_DQS[0..7] 6,9

SA_DQS-[0..7] 6,9

SB_MA[0..13] 6,11

SB_BS-[0..2] 6,11

SMDDR_VREF

+3VRUN

CT35

CT35

2.2u6.3Y6

2.2u6.3Y6

SMDDR_VREF

CT25

CT25

2.2u6.3Y6

2.2u6.3Y6

ADDRESS: 001

0xA2

2

+1_8VDIMM

CT34

CT34

0.1u10X4

0.1u10X4

PM_EXTTS#05

SODIMM thermal sensor pin

CT23

CT23

0.1u10X4

0.1u10X4

DIMM1B

DIMM1B

112

VDD1

111

VDD2

117

VDD3

96

VDD4

95

VDD5

118

VDD6

81

VDD7

82

VDD8

87

VDD9

103

VDD10

88

VDD11

104

VDD12

199

VDDSPD

83

NC1

120

NC2

50

NC3

69

NC4

163

NCTEST

203

NC5

204

NC6

1

VREF

201

GND0

202

GND1

47

VSS1

133

VSS2

183

VSS3

77

VSS4

12

VSS5

48

VSS6

184

VSS7

78

VSS8

71

VSS9

72

VSS10

121

VSS11

122

VSS12

196

VSS13

193

VSS14

8

VSS15

DIMM-200S_black-1

DIMM-200S_black-1

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

1

N13-2000220-A10

Bottom

A A

5

4

CT28

CT28

0.1u10X4

0.1u10X4

CT41

CT41

2.2u6.3Y6

2.2u6.3Y6

CT29

CT29

0.1u10X4

0.1u10X4

CT32

CT32

2.2u6.3Y6

2.2u6.3Y6

3

+1_8VDIMM

CT31

CT31

0.1u10X4

0.1u10X4

CT33

CT33

X_2.2u6.3Y6

X_2.2u6.3Y6

CT30

CT30

0.1u10X4

0.1u10X4

CT42

CT42

2.2u6.3Y6

2.2u6.3Y6

CT43

CT43

2.2u6.3Y6

2.2u6.3Y6

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-N011

MS-N011

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

B

B

B

Date:

Friday, April 11, 2008

Date:

Friday, April 11, 2008

Date:

Friday, April 11, 2008

2

MS-N011

ONBOARD DDR2 memory

ONBOARD DDR2 memory

ONBOARD DDR2 memory

Sheet of

Sheet of

Sheet of

1

1.0

1.0

1.0

839

839

839

A

SA_MD[0..63]6,8 SA_DQS-[0..7]6,8

SA_MA[0..12]6,10,11

SA_BS-[0..2]6,10,11

SA_DM[0..7]6,8

SA_DQS[0..7]6,8

U19

4 4

CLK_SDRAM-05,10

CLK_SDRAM05,10

3 3

SM_ODT05,11

SMDDR_VREF

C45

C45

2.2u6.3Y6

2.2u6.3Y6

SA_BS-0

SA_BS-1

SA_BS-2

SA_MA12

SA_MA11

SA_MA10

SA_MA9

SA_MA8

SA_MA7

SA_MA6

SA_MA5

SA_MA4

SA_MA3

SA_MA2

SA_MA1

SA_MA0

CLK_SDRAM-0

CLK_SDRAM0

CKE0

CKE05,11

SM_CS-0

SM_CS-05,11

SA_WE-

SA_WE-6,10,11

SA_RAS-

SA_RAS-6,10,11

SA_CAS-

SA_CAS-6,10,11

M_SA_DM1 M_SA_DM5

SM_ODT0

M_SA_DQS0

M_SA_DQS-0

M_SA_DQS1

M_SA_DQS-1

SMDDR_VREF SMDDR_VREF SMDDR_VREF SMDDR_VREF

C41

C41

0.1u10X4

0.1u10X4

Trace : 10 mils

2 2

U19

L2

BA0

L3

BA1

L1

BA2

R2

A12

P7

A11

M2

A10/AP

P3

A9

P8

A8

P2

A7

N7

A6

N3

A5

N8

A4

N2

A3

M7

A2

M3

A1

M8

A0

K8

CK

J8

CK

K2

CKE

L8

CS

K3

WE

K7

RAS

L7

CAS

F3

LDM

B3

UDM

K9

ODT

F7

LDQS

E8

LDQS

B7

UDQS

A8

UDQS

J2

VREF

A2

NC#A2

E2

NC#E2

R3

NC#R3

R7

NC#R7

R8

NC

SA_MD[0..63]

SA_MA[0..12]

SA_BS-[0..2]

SA_DM[0..7]

SA_DQS[0..7]

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDD

VDD

VDD

VDD

VDD

VDDL

VSSDL

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

VSS

VSS

VSS

VSS

K4T1G164QQ-HCE6

K4T1G164QQ-HCE6

M_SA_DQS-[0..7]10

M_SA_DQS[0..7]10

M_SA_MD[0..63]10

M_SA_DM[0..7]10

M_SA_MD10

B9

M_SA_MD15

B1

M_SA_MD8

D9

M_SA_MD9

D1

M_SA_MD12

D3

M_SA_MD13

D7

M_SA_MD14

C2

M_SA_MD11

C8

M_SA_MD2

F9

M_SA_MD3

F1

M_SA_MD4

H9

M_SA_MD5

H1

M_SA_MD1

H3

M_SA_MD0

H7

M_SA_MD6

G2

M_SA_MD7

G8

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

A1

E1

J9

M9

R1

J1

J7

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

A3

E3

J3

N1

P9

+1_8VDIMM +1_8VDIMM +1_8VDIMM +1_8VDIMM

C27

C27

1u6.3Y4

1u6.3Y4

B

SA_DQS-[0..7]

M_SA_DQS-[0..7]

M_SA_DQS[0..7]

M_SA_MD[0..63]

M_SA_DM[0..7]

SA_BS-0

SA_BS-1

SA_BS-2

SA_MA12

SA_MA11

SA_MA10

SA_MA9

SA_MA8

SA_MA7

SA_MA6

SA_MA5

SA_MA4

SA_MA3

SA_MA2

SA_MA1

SA_MA0

CLK_SDRAM-0

CLK_SDRAM0

CKE0

SM_CS-0

SA_WESA_RASSA_CASM_SA_DM2M_SA_DM0

M_SA_DM3

SM_ODT0

M_SA_DQS2

M_SA_DQS-2

M_SA_DQS3

M_SA_DQS-3

C

M12-K4T1G05-S02

M12-5PS1G25-H23

U20

U20

L2

BA0

L3

BA1

L1

BA2

R2

A12

P7

A11

M2

A10/AP

P3

A9

P8

A8

P2

A7

N7

A6

N3

A5

N8

A4

N2

A3

M7

A2

M3

A1

M8

A0

K8

CK

J8

CK

K2

CKE

L8

CS

K3

WE

K7

RAS

L7

CAS

F3

LDM

B3

UDM

K9

ODT

F7

LDQS

E8

LDQS

B7

UDQS

A8

UDQS

J2

VREF

A2

NC#A2

E2

NC#E2

R3

NC#R3

R7

NC#R7

R8

NC

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5