Page 1

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

REL

DEVELOPMENT NO. Q/M

A

B

73P9250

A

B

Osprey Pass1 Final

Sheet Contents:

Contents:

C

C

1. TITLE

2. CHANGE LOG

D

D

3. CROW BLOCK DIAGRAM

4. PCI EDGE CONNECTOR

5. PCI & BUFFERS

E

E

6. CORE & I/O POWER, MEMORY INTERFACE, 2MX32 DDR, GPIO/LCD

7. ANALOG VIDEO CONNECTOR

8. CONNECTORS

F

F

9. RS232 DRIVER

10. STRAPS

11. 3.3V CONTINUOUS POWER FOR HARRIER

G

G

12. 2.5V, 1.8V POWER

13. SPARE PARTS

H

H

Raptor's Senses

I

PART NO.

I

TITLE

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

OSPREY

3-27-2003_11:35

James DaltonMike Ragan

Jon Rankin (ATI)

SHEET OF

1

Physical Design

Jeff Davis

JJ

13

108754321

Page 2

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

REL

DEVELOPMENT NO. Q/M

A

73P9250

A

Change Log:

B

B

C

D

C

D

E

F

E

F

G

H

G

H

I

PART NO.

I

CHANGE LOG

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

3-27-2003_11:35

DESIGNER

CHECKED

APPROVED

OSPREY

James Dalton

SHEET OF

Mike Ragan Jeff Davis

Jon Rankin (ATI)

2

108754321

Physical Design

JJ

13

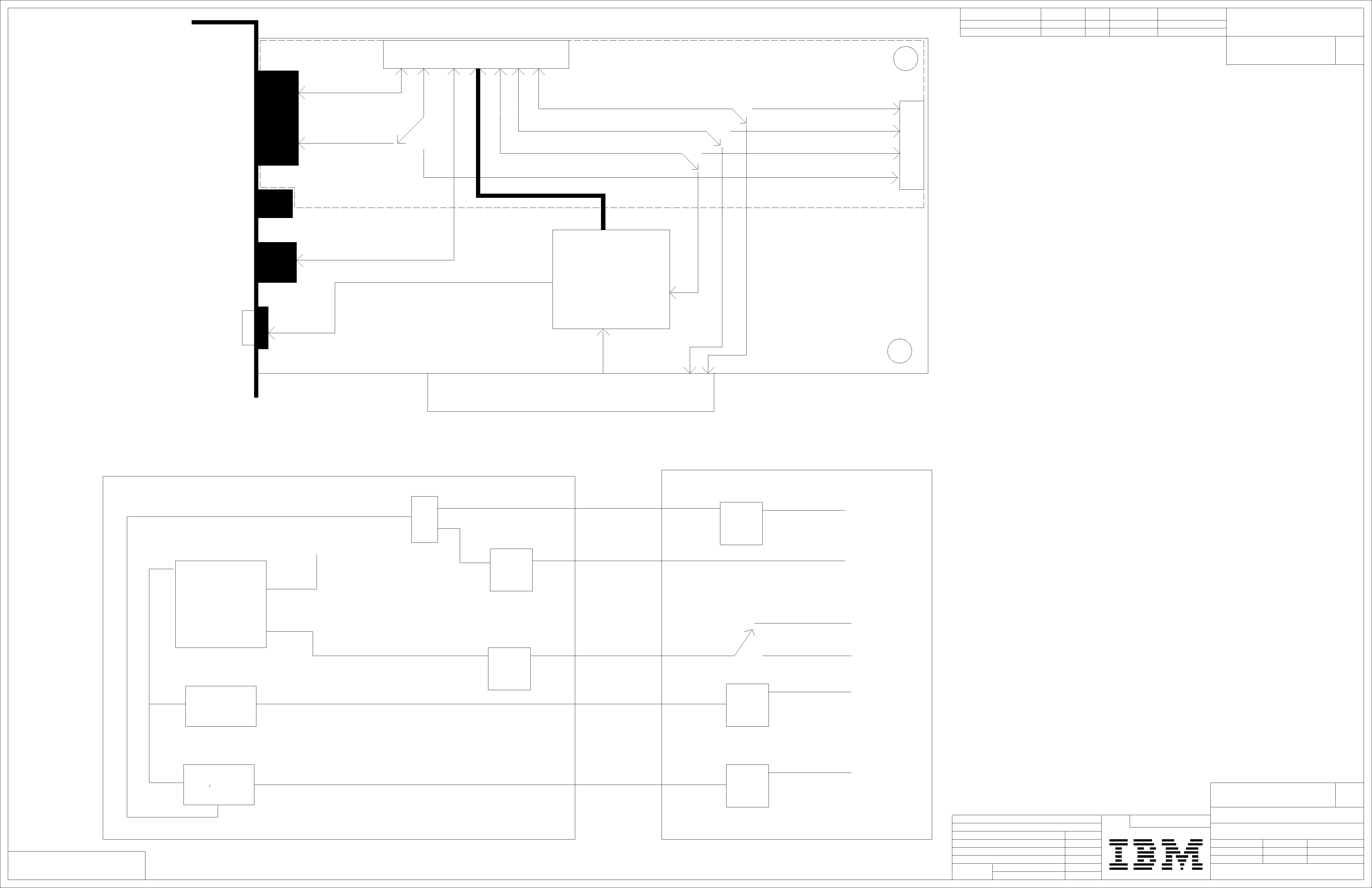

Page 3

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

REL

DEVELOPMENT NO. Q/M

A

73P9250

A

SMP

RS485RS232

RS485

RS232

B

USB

USB

MISC

RS485

I2C

USB

CONDOR

B

Digital Video

Ext Power

C

C

Ethernet

Analog Video

D

Video

I2C

RS485

MISC

D

Video

E

Harrier

F

MUX

Com Port Block Diagram

PCI

Osprey

E

F

RS232 Driver

External

RS485 Driver

Debug Header

Bus A

External

G

G

Com1

405GP

PCI Conn.

Com2

RS485 Driver

Internal

Bus B

H

H

RS232 Driver

Debug Header

Com3

EZUSB

I

RS232 Driver

I

External

Com4

DUART

PART NO.

Osprey Block Diagram

Com5

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

3-27-2003_11:35

DESIGNER

CHECKED

APPROVED

OSPREY

James Dalton

SHEET OF

Mike Ragan

Jon Rankin (ATI)

3

108754321

Physical Design

Jeff Davis

13

JJ

Page 4

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

REL

A

PRIMARY PCI

J31

B

5

5

5

5

5

5

5

5

5

5

5

C

5

5

5

5

5

Maximum PCI Power

Aux3 ±5% 375mA max. =1.237 W

3.3 V ±0.3 V 7.6 A max.

5 V ±5% 5 A max.

D

12 V ±5% 500 mA

-12 V ±10% 100 mA

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

E

PCI_3.3V

5

5

5

5

PPCI_AD0

PPCI_AD1

PPCI_AD2

PPCI_AD3

PPCI_AD4

PPCI_AD5

PPCI_AD6

PPCI_AD7

PPCI_AD8

PPCI_AD9

PPCI_AD10

PPCI_AD11

PPCI_AD12

PPCI_AD13

PPCI_AD14

PPCI_AD15

PPCI_AD16

PPCI_AD17

PPCI_AD18

PPCI_AD19

PPCI_AD20

PPCI_AD21

PPCI_AD22

PPCI_AD23

PPCI_AD24

PPCI_AD25

PPCI_AD26

PPCI_AD27

PPCI_AD28

PPCI_AD29

PPCI_AD30

PPCI_AD31

PPCI_C/BE0_N

PPCI_C/BE1_N

PPCI_C/BE2_N

PPCI_C/BE3_N

A58

B58

A57

B56

A55

B55

A54

B53

B52

A49

B48

A47

B47

A46

B45

A44

A32

B32

A31

B30

A29

B29

A28

B27

A25

B24

A23

B23

A22

B21

A20

B20

A52

B44

B33

B26

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE0#

C/BE1#

C/BE2#

C/BE3#

RSV1

RSV2

RSV3

RSV4

3.3Vaux

PME#

PRSNT1#

PRSNT2#

LOCK#

PERR#

SERR#

REQ64#

ACK64#

SBO#

SDONE

TRST#

TCK

TMS

TDO

TDI

A9

B10

A11

B14

A14

A19

B9

B11

B39

B40

B42

A60

B60

A41

A40

A1

B2

A3

B4

A4

PRSNT1# PRSNT2# Expansion Configuration

R72

NOPOP

NOPOP

5/23/02 JWD - Added 0 OHM NOPOP per ATI request

0

R73

0

R527

PPCI_SERR#

0

485_PCI_N

485_PCI_P

Open Open No expansion board present

Ground Open Expansion board present, 25 W maximum

Open Ground Expansion board present, 15 W maximum

Ground Ground Expansion board present, 7.5 W maximum

5

HOST_PWRGD/RST_PCI#

HOST_PWR_REQ_PCI#

HOST_SMI_PCI#

4/7/02 JWD- Added PRSNT, PME test point, Changed M66EN pull-down to 0-Ohm

3.3VC

U89

VCC

5

S1ININ = 1

1

6

HOST_PWRGD/RST_UMB#

8

HOST_PWR_REQ_UMB#

8

HOST_SMI_UMB#

8

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

U90

S1ININ = 1

1

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

U91

S1ININ = 1

1

S2

3

IN = 0

2

GND

4

VCC

5

6

4

VCC

5

6

4

D

3.3VC

D

3.3VC

D

DEVELOPMENT NO. Q/M

HOST_PWRGD/RST#

HOST_PWR_REQ#

73P9250

8

8

HOST_SMI#

8

A

B

C

D

E

CLK

-12V

A6

B7

A7

B8

B16

A15

B49

B1

A2

B3

B15

B17

A18

B22

A24

B28

A30

B34

A35

A37

B38

A42

B46

A48

A56

B57

PPCI_INTA#

PPCI_CLK

PPCI_RST_N

M66EN

5

5

5

10

High End Servers that use SP signaling through modified

PCI slot have this signal pulled up.

EXA_SLOT_PRSNT

R557

10K

8

8

485_PCI_N

485_INT_N

485_PCI_P

485_INT_P

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

U87

VCC

5

S1ININ = 1

1

6

S2

3

IN = 0PCI_3.3V

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

U86

S1ININ = 1

1

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

4

VCC

5

6

4

D

D

3.3VC

3.3VC

485_N_BUS_B

485_P_BUS_B

F

8

G

8

H

I

5

C185

C194

C174 C173

C169

C183

5

5

0.1U

0.1U 0.1U

0.1U 0.1U

0.1U

5

5

F

5

5

C188

C184

C180 C179

C178 C177

5

5

0.1U

G

H

I

PCI_5V

C42 C526

0.1U

PCI_5V

C172

C525 C524

0.1U 0.1U

C171C170

0.1U0.1U

0.1U 0.1U

C196

0.1U

C195

0.1U

C191

0.1U

0.1U 0.1U

C523

0.1U

C192 C189

C522

0.1U

C190

0.1U

0.1U

0.1U

0.1U0.1U

C39

PCI_3.3V

0.1U

0.1U

PPCI_PAR

PPCI_FRAME_N

PPCI_TRDY_N

PPCI_IRDY_N

PPCI_STOP_N

PPCI_DEVSEL_N

PPCI_IDSEL

PPCI_REQ0_N

PPCI_GNT0_N

PCI_5V

A43

A34

A36

B35

A38

B37

A26

B18

A17

A21

B25

A27

B31

A33

B36

A39

B41

B43

A45

A53

B54

A10

A16

B19

A59

B59

A5

B5

B6

A8

A61

B61

A62

B62

PAR

FRAME#

TRDY#

IRDY#

STOP#

DEVSEL#

IDSEL

REQ#

GNT#

3.3V0

3.3V1

3.3V2

3.3V3

3.3V4

3.3V5

3.3V6

3.3V7

3.3V8

3.3V9

3.3V10

3.3V11

VIO_0

VIO_1

VIO_2

VIO_3

VIO_4

5V0

5V1

5V2

5V3

5V4

5V5

5V6

5V7

INTA#

INTB#

INTC#

INTD#

RESET#

M66EN

+12V

GND0

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND10

GND11

GND12

GND13

GND14

GND15

GND16

CONN2x60

PCI UNIVERSAL

SILKSCREEN:

ADD SILKSCREEN PIN NUMBER EVERY

5 PINS ON BOTH "A" AND "B" SIDES.

6 9

PCI EDGE CONNECTOR

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

0.13

2.0

PART NO.

TITLE

1/1SCALE:

OSPREY

3-27-2003_11:35

DESIGNER

CHECKED

APPROVED

SHEET OF

James Dalton

Jon Rankin (ATI)

4

Mike Ragan

108754321

Physical Design

Jeff Davis

13

JJ

Page 5

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

REL

DEVELOPMENT NO. Q/M

A

PCI Buffers

PCI_3.3V

5/23/02 JWD - Changed R55 to NOPOP per ATI request

73P9250

A

8/18/02 JWD - Added I2C SEEPROM for EDID data

01/15/03 JWD - Brought out DVI DDC lines for testing.

P/D_NUM

PI3C3384Q

PPCI_AD9

4

4

4

4

B

4

4

4

4

4

PPCI_AD7

PPCI_AD6

PPCI_AD2

PPCI_AD1

PPCI_AD0

PPCI_AD3

PPCI_AD4

PPCI_AD5

PPCI_C/BE0_N

R522

1K

P/D_NUM

C

4

4

4

4

4

4

4

4

4

D

4

R521

PI3C3384Q

PPCI_AD14

PPCI_PAR

PPCI_AD15

PPCI_AD12

PPCI_AD10

PPCI_AD8

PPCI_AD11

PPCI_AD13

PPCI_C/BE1_N

PPCI_SERR#

1K

P/D_NUM

PI3C3384Q

4

4

E

4

4

4

4

4

4

4

4

PPCI_AD18

PPCI_C/BE2_N

PPCI_IRDY_N

PPCI_DEVSEL_N

PPCI_CLK

PPCI_INTA#

PPCI_STOP_N

PPCI_TRDY_N

PPCI_FRAME_N

PPCI_AD16

R520

1K

F

P/D_NUM

PI3C3384Q

4

4

4

4

4

4

G

4

4

4

4

PPCI_AD25

PPCI_C/BE3_N

PPCI_AD23

PPCI_AD22

PPCI_AD17

PPCI_AD19

PPCI_AD20

PPCI_AD21

PPCI_IDSEL

PPCI_AD24

R519

1K

P/D_NUM U75

H

4

4

4

4

4

4

4

4

4

PPCI_RST_N

PPCI_GNT0_N

PPCI_AD31

PPCI_AD29

PPCI_AD28

PPCI_AD26

PPCI_AD27

PPCI_AD30

PPCI_REQ0_N

R81

100

U76

24

VCC

3

4

7

8

11

14

17

18

21

22

1A1

1A2

1A3

1A4

1A5

2A1

2A2

2A3

2A4

2A5

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

2

5

6

9

10

15

16

19

20

23

1

1OE#

13 12

2OE# GND

3384

U72

24

VCC

3

4

7

8

11

14

17

18

21

22

1A1

1A2

1A3

1A4

1A5

2A1

2A2

2A3

2A4

2A5

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

2

5

6

9

10

15

16

19

20

23

1

1OE#

13 12

2OE# GND

3384

U73

24

VCC

3

4

7

8

11

14

17

18

21

22

1A1

1A2

1A3

1A4

1A5

2A1

2A2

2A3

2A4

2A5

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

2

5

6

9

10

15

16

19

20

23

1

1OE#

13 12

2OE# GND

3384

U74

24

VCC

3

4

7

8

11

14

17

18

21

22

1A1

1A2

1A3

1A4

1A5

2A1

2A2

2A3

2A4

2A5

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

2

5

6

9

10

15

16

19

20

23

1

1OE#

13 12

2OE# GND

3384

24

VCC

3

4

7

8

11

14

17

18

21

22

1A1

1A2

1A3

1A4

1A5

2A1

2A2

2A3

2A4

2A5

1B1

1B2

1B3

1B4

1B5

2B1

2B2

2B3

2B4

2B5

2

5

6

9

10

15

16

19

20

23

3V_PPCI_AD9

3V_PPCI_AD7

3V_PPCI_AD6

3V_PPCI_AD2

3V_PPCI_AD1

3V_PPCI_AD0

3V_PPCI_AD3

3V_PPCI_AD4

3V_PPCI_AD5

3V_PPCI_C/BE0_N

PCI_3.3V

3V_PPCI_AD14

3V_PPCI_PAR

3V_PPCI_AD15

3V_PPCI_AD12

3V_PPCI_AD10

3V_PPCI_AD8

3V_PPCI_AD11

3V_PPCI_AD13

3V_PPCI_C/BE1_N

3V_PPCI_SERR#

PCI_3.3V

3V_PPCI_AD18

3V_PPCI_C/BE2_N

3V_PPCI_IRDY_N

3V_PPCI_DEVSEL_N

3V_PPCI_CLK

3V_PPCI_INTA#

3V_PPCI_STOP_N

3V_PPCI_TRDY_N

3V_PPCI_FRAME_N

3V_PPCI_AD16

PCI_3.3V

3V_PPCI_AD25

3V_PPCI_C/BE3_N

3V_PPCI_AD23

3V_PPCI_AD22

3V_PPCI_AD17

3V_PPCI_AD19

3V_PPCI_AD20

3V_PPCI_AD21

3V_PPCI_IDSEL

3V_PPCI_AD24

PCI_3.3V

3V_PPCI_RST_N

3V_PPCI_GNT0_N

3V_PPCI_AD31

3V_PPCI_AD29

3V_PPCI_AD28

3V_PPCI_AD26

3V_PPCI_AD27

3V_PPCI_AD30

3V_PPCI_REQ0_N

R80

100

54

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5,8

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5,8

5

5

3V_PPCI_AD05

3V_PPCI_AD15

3V_PPCI_AD25

3V_PPCI_AD35

3V_PPCI_AD45

3V_PPCI_AD55

3V_PPCI_AD65

3V_PPCI_AD75

3V_PPCI_AD85

3V_PPCI_AD95

3V_PPCI_AD105

3V_PPCI_AD115

3V_PPCI_AD125

3V_PPCI_AD135

3V_PPCI_AD145

3V_PPCI_AD155

3V_PPCI_AD165

3V_PPCI_AD175

3V_PPCI_AD185

3V_PPCI_AD195

3V_PPCI_AD205

3V_PPCI_AD215

3V_PPCI_AD225

3V_PPCI_AD235

3V_PPCI_AD245

3V_PPCI_AD255

3V_PPCI_AD265

3V_PPCI_AD275

3V_PPCI_AD285

3V_PPCI_AD295

3V_PPCI_AD305

3V_PPCI_AD315

3V_PPCI_C/BE0_N5

3V_PPCI_C/BE1_N5

3V_PPCI_C/BE2_N5

3V_PPCI_C/BE3_N5

3V_PPCI_DEVSEL_N

3V_PPCI_FRAME_N

3V_PPCI_GNT0_N

3V_PPCI_INTA#

3V_PPCI_IRDY_N

3V_PPCI_PAR

3V_PPCI_REQ0_N

3V_PPCI_IDSEL

3V_PPCI_STOP_N

3V_PPCI_TRDY_N

3V_PPCI_RST_N

3V_PPCI_CLK

3V_PPCI_SERR#

R55

NOPOP

U1

RADEON RV-100

F22

AD1

C22

AD2

F23

AD3

C23

G22

D22

G23

H23

F20

J22

F21

J23

G21

K22

H20

L20

M23

L21

N22

M21

N23

N20

P22

R20

R22

R21

R23

T20

T22

T21

T23

H22

D23

P23

P21

V22

V21

E21

K23

M22

N21

L22

K21

AA21

AB23

L23

H21

AA22

W22

W21

V23

W20

U23

V20

U22

U21

Y23

Y21

Y22

J20

J21

AB22

AA23

W23

E22

E23

Y20

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

AD_STB0

AD_STB0_N

AD_STB1

AD_STB1_N

SB_STB

SB_STB_N

CBE0_N

CBE1_N

CBE2_N

CBE3_N

DEVSEL_N

FRAME_N

GNT_N

INTA_N

IRDY_N

PAR

REQ_N

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

STOP_N

TRDY_N

RST_N

PCICLK

RBF_N

AGPTEST

AGPREF

SERR_N

AGP/PCI

XTAL

TXVDDR_AA13

TMDS INTERFACE DAC2 DAC / CRT

MISC

215R6

0

VENDOR=ATI VEN_P/D_NUM=215R6LAFA12E

PVDDAD0

MPVDD

XTALIN

XTALOUT

PVSS

MPVSS

AVDD

HSYNC

VSYNC

MONID0

MONID1

VGADDCDATA

VGADDCCLK

STEREOSYNC

AUXWIN

RSET

AVSSN

AVSSQ

A2VDD

A2VDDQ

Y_G

C_R

COMP_B

H2SYNC

V2SYNC

CRT2DDCCLK

CRT2DDCDAT

R2SET

A2VSSQ

A2VSSN

TPVDD

TXVDDR_Y13

TX0P

TX0M

TX1P

TX1M

TX2P

TX2M

TXCP

TXCM

DVIDDCDATA

DVIDDCCLK

HPD

TXVSSR_Y12

TXVSSR_AA12

TXVSSR_AB12

TPVSS

TESTEN

R

G

B

AC23B23

A2

AC20

AC21

AC22

A3

AA16

AC19

AC18

AC17

AB17

AB18

AB20

AB21

AB19

AA19

Y18

AA18

AA17

Y16

Y15

AA11

Y10

AC9

AC10

AC8

AB9

AB10

Y9

AA9

AB11

AA10

Y11

AC12

Y13

AA13

AC14

AB14

AC15

AB15

AC16

AB16

AC13

AB13

AA14

Y14

AA15

Y12

AA12

AB12

AC11

AA7

1_8V

R525

C32

100N

R56

0

VIDEO_RED

VIDEO_GREEN

VIDEO_BLUE

VIDEO_HSYNC

VIDEO_VSYNC

ATI_DDCDAT

ATI_DDCCLK

STEREOSYNC

R535

1K

C28

R524

R523 845

C30

10N

0

499

R536

2K

100N

Place all components close to BGA

CAPACITIVE_LOAD=18PF

TOLERANCE=50PPM

STABILITY=50PPM

100N

VEN_P/D_NUM=MA-506_27.0000M-C

VENDOR=EPSON

1

MHz

R57

7

7

7

7

7

7

7

10

5/23/02 JWD - Removed Ferrite per ATI's request

PCI_3.3VPCI_3.3V

PCI_3.3V

2K

VEN_P/D_NUM=M24C01-WMN6T

C534

10N

C536

100N

C535

27

18pF

Y1

423

Place all caps and Inductors as close to BGA as possible!

1Kb for EDID

EEPROM

VCC A0

8 1

WP

7

SDA

5

SERIAL-I2C

VENDOR=ST_MICRO

PCI_3.3V PCI_3.3V1_8V

R554

U82

A1

A2SCL

GND

R555

20K

NOPOP

2

36

4

PCI_3.3V

NOPOP

NOPOP

R529

R530

4.7K

R5372KR538

20K

NOPOP

INT_I2C_SDA

INT_I2C_SCL

NOPOP

R531

4.7K

R539

2K

R64

4.7K

2K

1MEG

8

8

C33

PLACE=POP

C40

10P

10P

DQM[0:3]_N

6

DQ[0:31]

6

DQM3_N

DQM2_N

DQM1_N

DQM0_N

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

RN8

RN8

RN8

RN8

RN7

RN7

RN7

RN7

RN6

RN6

RN6

RN6

RN5

RN5

RN5

RN5

RN4

RN4

RN4

RN4

RN3

RN3

RN3

RN3

RN2

RN2

RN2

RN2

RN1

RN1

RN1

RN1

R70

33

R69

33

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

R71

33

R68

33

33

8

33

7

33

6

33

5

33

8

33

7

33

6

33

5

33

8

33

7

33

6

33

5

33

8

33

7

33

6

33

5

33

8

33

7

33

6

33

5

33

8

33

7

33

6

33

5

33

8

33

7

33

6

33

5

33

8

33

7

33

6

33

5

ATI_DQM3_N

ATI_DQM2_N

ATI_DQM1_N

ATI_DQM0_N

ATI_DQ15

ATI_DQ14

ATI_DQ13

ATI_DQ12

ATI_DQ11

ATI_DQ10

ATI_DQ9

ATI_DQ8

ATI_DQ31

ATI_DQ30

ATI_DQ29

ATI_DQ28

ATI_DQ27

ATI_DQ26

ATI_DQ25

ATI_DQ24

ATI_DQ23

ATI_DQ22

ATI_DQ21

ATI_DQ20

ATI_DQ19

ATI_DQ18

ATI_DQ17

ATI_DQ16

ATI_DQ7

ATI_DQ6

ATI_DQ5

ATI_DQ4

ATI_DQ3

ATI_DQ2

ATI_DQ1

ATI_DQ0

ATI_DQM[0:3]_N

ATI_DQ[0:31]

6

B

6

C

D

E

F

G

H

I

I

R518

1K

1

1OE#

13 12

2OE# GND

3384

-The Clock (PCI_CLK) has been buffered.

PCI & BUFFERS

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

6 9

0.13

2.0

PART NO.

TITLE

OSPREY

1/1SCALE:

3-27-2003_11:35

DESIGNER

CHECKED

James Dalton

Mike Ragan Jeff Davis

Jon Rankin (ATI)

Physical Design

JJ

APPROVED

SHEET OF

5

13

108754321

Page 6

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

REL

DEVELOPMENT NO. Q/M

73P9250

A

A

4/7/02 JWD - Added Series R's to VMA11 & VMA12

5/23/02 JWD - Fixed DDR addressing

5/23/02 JWD - Changed R36 to NOPOP per ATI request

U2

PCI_3.3V

ROMCS_N

6

B

C54

100N

1

CS

7

HOLD

3

WP

8

VCC

VENDOR=ATMEL

SO

SI

SCK

GND

2

5

6

4

ATI_GPIO8

ATI_GPIO9

ATI_GPIO10

6,10

6

6

SMBUS_BUSY_N

8

R546

R547

R548

VEN_P/D_NUM=AT25F1024N-10SI-2.7

capacitor added as per JonRankin-ATI

6,10

C

D

E

PCI_3.3V

F

2_5V

G

H

I

Place decoupling Caps as close to VDDC and VSS pins as possible

1_8V

E7

VDDC_E7

E10

VDDC_E10

E12

VDDC_E12

G5

VDDC_G5

K5

VDDC_K5

M5

VDDC_M5

P5

VDDC_P5

U5

VDDC_U5

W7

VDDC_W7

W10

VDDC_W10

W12

VDDC_W12

E14

VDDC_E14

E17

VDDC_E17

G19

VDDC_G19

K19

VDDC_K19

M19

VDDC_M19

P19

VDDC_P19

U19

VDDC_U19

W14

VDDC_W14

W17

VDDC_W17

Y19

VDDP_Y19

AA20

VDDP_AA20

R19

VDDP_R19

T19

VDDP_T19

D21

VDDP_D21

E20

VDDP_E20

F19

VDDP_F19

G20

VDDP_G20

H19

VDDP_H19

J19

VDDP_J19

K20

VDDP_K20

U20

VDDP_U20

V19

VDDP_V19

W19

VDDP_W19

L19

VDDP_L19

N19

VDDP_N19

E19

VDDP_E19

M20

VDDP_M20

P20

VDDP_P20

D20

VDDR1_D20

E15

VDDR1_E15

E16

VDDR1_E16

E18

VDDR1_E18

E4

VDDR1_E4

E6

VDDR1_E6

E8

VDDR1_E8

E9

VDDR1_E9

F5

VDDR1_F5

G4

VDDR1_G4

H5

VDDR1_H5

J5

VDDR1_J5

K4

VDDR1_K4

L5

VDDR1_L5

M4

VDDR1_M4

N5

VDDR1_N5

P4

VDDR1_P4

C21

VDDR1_C21

D14

VDDR1_D14

D5

VDDR1_D5

D17

VDDR1_D17

D19

VDDR1_D19

D10

VDDR1_D10

D12

VDDR1_D12

D7

VDDR1_D7

E11

VDDR1_E11

E13

VDDR1_E13

22U

22U

C10

+

+

100N

C31

C19

C4

100N

C21

100N

C6

100N

100N

VENDOR_PART=0603YC104JAT2A

C29

C22

C23

100N

100N

RADEON RV-100

POWER

GROUND

VDDR3_R5

VDDR3_T5

VDDR3_U4

VDDR3_V5

VDDR3_W11

VDDR3_W13

VDDR3_W15

VDDR3_W16

VDDR3_W18

VDDR3_W5

VDDR3_W6

VDDR3_W8

VDDR3_W9

VDDR3_Y17

VDDR3_Y4

VDDR3_Y7

VSS_A1

VSS_B2

VSS_C3

VSS_D4

VSS_E5

VSS_K12

VSS_K13

VSS_K14

VSS_K15

VSS_J10

VSS_J11

VSS_J12

VSS_J13

VSS_J14

VSS_J15

VSS_J9

VSS_K10

VSS_K11

VSS_L10

VSS_K9

VSS_L12

VSS_L11

VSS_L14

VSS_L13

VSS_L9

VSS_L15

VSS_M11

VSS_M10

VSS_M13

VSS_M12

VSS_M15

VSS_M14

VSS_N10

VSS_M9

VSS_N12

VSS_N11

VSS_N14

VSS_T13

VSS_N9

VSS_N15

VSS_R12

VSS_R13

VSS_R14

VSS_R15

VSS_P10

VSS_P11

VSS_P12

VSS_P13

VSS_P14

VSS_P15

VSS_P9

VSS_R10

VSS_R11

VSS_R9

R5

T5

U4

V5

W11

W13

W15

W16

W18

W5

W6

W8

W9

Y17

Y4

Y7

A1

B2

C3

D4

E5

K12

K13

K14

K15

J10

J11

J12

J13

J14

J15

J9

K10

K11

L10

K9

L12

L11

L14

L13

L9

L15

M11

M10

M13

M12

M15

M14

N10

M9

N12

N11

N14

N13

N9

N15

R12

R13

R14

R15

P10

P11

P12

P13

P14

P15

P9

R10

R11

R9

22U

+

C27

C24

5

PCI_3.3V

C26

100N

VMA[0:10]6

DQM[0:3]_N

100N

6

C63

VREF

C62

2_5V

100N

Place caps close to mem

100N

Place resistors closer to memory than video

VMA0

VMA1

VMA2

VMA3

VMA4

VMA5

VMA6

VMA7

VMA8

VMA9

VMA10

6

6

VMA13

VMA12

6

6

6

6

6

6

6

6

RN9

4 5

22

RN10

4 5

22

2_5V

C34

2_5V

C35

100N

RN9

2 7

22

RN10

2 7

22

R76

22

100N

3 6

22

3 6

22

EXT_TMDS_VSYNC8

EXT_TMDS_HSYNC

8

EXT_TMDS_DE

8

EXT_TMDS_CLK

8

0

0

NOPOP

0

NOPOP

10

10

10

10

10

10

10

10

6

6

10

10

10

C37

10N

C38

10N

1 8

RN9

22

RN10

1 8

RN10

22

R77

22

R79

22

DQM0_N

DQM1_N

DQM2_N

DQM3_N

ATI_CKE

CLK0

CLK0_N

ATI_QS0

ATI_CS0_N

ATI_RAS_N

ATI_CAS_N

ATI_WE_N

LTGIO0

LTGIO1

LTGIO2

ATI_GPIO0

ATI_GPIO1

ATI_GPIO2

ATI_GPIO3

ATI_GPIO4

ATI_GPIO5

ATI_GPIO6

ATI_GPIO7

ATI_GPIO8

ATI_GPIO9

ATI_GPIO10

ATI_GPIO11

ATI_GPIO12

ATI_GPIO13

RN9

R75

22

R78

22

U1

W2

LCDCNTL0

W3

LCDCNTL1

W4

LCDCNTL2

Y1

LCDCNTL3

AB8

LTGIO0

AA8

LTGIO1

Y8

LTGIO2

V4

GPIO0

V3

GPIO1

V2

GPIO2

V1

GPIO3

U3

GPIO4

U2

GPIO5

U1

GPIO6

T4

GPIO7

T3

GPIO8

T2

GPIO9

T1

GPIO10

R4

GPIO11

R3

GPIO12

R2

GPIO13

15

35

65

96

2

8

14

22

59

67

73

79

86

95

58

31

32

33

34

47

48

49

50

51

45

36

29

30

23

56

24

57

53

55

54

94

28

27

26

25

5

11

19

62

70

76

82

92

99

RADEON RV-100

LCDDATA10

LCDDATA11

LCDDATA12

LCDDATA13

LCDDATA14

LCDDATA15

LCDDATA16

LCDDATA17

LCDDATA18

LCDDATA19

LCDDATA20

LCDDATA21

LCDDATA22

GPIO & LCD

LCDDATA23

215R6

VEN_P/D_NUM=215R6LAFA12E

P/N over-ride: 38L4212 4Mx32

U6

K4D623238B-QC50

VDD_15

DRAM_DDR

VDD_35

VDD_65

VDD_96

VDDQ_2

VDDQ_8

VDDQ_14

VDDQ_22

VDDQ_59

VDDQ_67

VDDQ_73

VDDQ_79

VDDQ_86

VDDQ_95

VREF

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

BA0

BA1

DM0

DM1

DM2

DM3

CKE

CK

CK_N

DQS

CS_N

RAS_N

CAS_N

WE_N

VSSQ_5

VSSQ_11

VSSQ_19

VSSQ_62

VSSQ_70

VSSQ_76

VSSQ_82

VSSQ_92

VSSQ_99

LCDDATA0

LCDDATA1

LCDDATA2

LCDDATA3

LCDDATA4

LCDDATA5

LCDDATA6

LCDDATA7

LCDDATA8

LCDDATA9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

NC_38

NC_39

NC_40

NC_41

NC_42

NC_43

NC_44

NC_87

NC_88

NC_89

NC_90

NC_91

RFU_37

RFU_93

VSS_16

VSS_46

VSS_66

VSS_85

Y2

Y3

AA1

AA2

AA3

AB1

AB2

AC1

AC2

AB3

AC3

AA4

AB4

AC4

Y5

AA5

AB5

AC5

Y6

AA6

AB6

AC6

AB7

AC7

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

MCL

97

98

100

1

3

4

6

7

60

61

63

64

68

69

71

72

9

10

12

13

17

18

20

21

74

75

77

78

80

81

83

84

38

39

40

41

42

43

44

87

88

89

90

91

37

93

52

16

46

66

85

EXT_TMDS_BLU0

EXT_TMDS_BLU1

EXT_TMDS_BLU2

EXT_TMDS_BLU3

EXT_TMDS_BLU4

EXT_TMDS_BLU5

EXT_TMDS_BLU6

EXT_TMDS_BLU7

EXT_TMDS_GRN0

EXT_TMDS_GRN1

EXT_TMDS_GRN2

EXT_TMDS_GRN3

EXT_TMDS_GRN4

EXT_TMDS_GRN5

EXT_TMDS_GRN6

EXT_TMDS_GRN7

EXT_TMDS_RED0

EXT_TMDS_RED1

EXT_TMDS_RED2

EXT_TMDS_RED3

EXT_TMDS_RED4

EXT_TMDS_RED5

EXT_TMDS_RED6

EXT_TMDS_RED7

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

Popped for 4Mx32 (16Mbyte)

POP

R526

22

8

8

8

8

8

8

8

8

8

8

8

8

ATI_DQM[0:3]_N

5

8

8

8

8

8

8

8

8

8

DQ[0:31]

5

6

VMA[0:10]

6

ATI_CS0_N

ATI_QS0

6

6

6

6

2_5V

6

6

6

R38

+1%/-1%

R39

+1%/-1%

1K

1K

C36

VREF

6

6

6

100N

NOPOP

VMA11

6

POWER & GROUND

215R6

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

U1

VEN_P/D_NUM=215R6LAFA12E

CORE & I/O POWER, MEMORY INTERFACE, 2MX32 DDR, GPIO/LCD

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

11/01/02 JWD - Connected LTGIO to 405GP GPIO16

RADEON RV-100

ATI_DQM0_N

ATI_DQM1_N

ATI_DQM2_N

ATI_DQM3_N

6

6

6

R51

33

ATI_RAS_N

ATI_CAS_N

ATI_WE_N

ATI_CKE

ROMCS_N

CLK0

CLK0_N

VREF

VMA0

VMA1

VMA2

VMA3

VMA4

VMA5

VMA6

VMA7

VMA8

VMA9

VMA10

VMA11

VMA12

VMA13

C19

DQM0_N

B19

DQM1_N

C13

DQM2_N

B13

DQM3_N

E3

DQM4_N

F1

DQM5_N

L4

DQM6_N

M1

DQM7_N

C10

A0

B10

A1

A10

A2

D9

A3

C9

A4

B9

A5

A9

A6

D8

A7

C8

A8

B8

A9

A8

A10

C7

A11

B7

A12

A7

A13

D6

CS0_N

C4

CS1_N

D16

QS0

C16

QS1

B16

QS2

A16

QS3

H3

QS4

H4

QS5

J1

QS6

J2

QS7

C6

RAS_N

B6

CAS_N

A6

WE_N

C5

CKE

W1

ROMCS#

A5

CLK0

B5

CLK0_N

A4

CLK1

B4

CLK1_N

B3

CLKFB

P3

VREF

R1

MEMVMODE

1_8V

R37

4.7K

R36

2K

MEMORY

215R6

U1

0.13

2.0

A23

DQ0

B22

DQ1

A22

DQ2

B21

DQ3

A21

DQ4

C20

DQ5

B20

DQ6

A20

DQ7

A19

DQ8

D18

DQ9

C18

DQ10

B18

DQ11

A18

DQ12

C17

DQ13

B17

DQ14

A17

DQ15

D15

DQ16

C15

DQ17

B15

DQ18

A15

DQ19

C14

DQ20

B14

DQ21

A14

DQ22

D13

DQ23

A13

DQ24

C12

DQ25

B12

DQ26

A12

DQ27

D11

DQ28

C11

DQ29

B11

DQ30

A11

DQ31

B1

DQ32

C1

DQ33

C2

DQ34

D1

DQ35

D2

DQ36

D3

DQ37

E1

DQ38

E2

DQ39

F2

DQ40

F3

DQ41

F4

DQ42

G1

DQ43

G2

DQ44

G3

DQ45

H1

DQ46

H2

DQ47

J3

DQ48

J4

DQ49

K1

DQ50

K2

DQ51

K3

DQ52

L1

DQ53

L2

DQ54

L3

DQ55

M2

DQ56

M3

DQ57

N1

DQ58

N2

DQ59

N3

DQ60

N4

DQ61

P1

DQ62

P2

DQ63

VEN_P/D_NUM=215R6LAFA12E

ATI_DQ0

ATI_DQ1

ATI_DQ2

ATI_DQ3

ATI_DQ4

ATI_DQ5

ATI_DQ6

ATI_DQ7

ATI_DQ8

ATI_DQ9

ATI_DQ10

ATI_DQ11

ATI_DQ12

ATI_DQ13

ATI_DQ14

ATI_DQ15

ATI_DQ16

ATI_DQ17

ATI_DQ18

ATI_DQ19

ATI_DQ20

ATI_DQ21

ATI_DQ22

ATI_DQ23

ATI_DQ24

ATI_DQ25

ATI_DQ26

ATI_DQ27

ATI_DQ28

ATI_DQ29

ATI_DQ30

ATI_DQ31

PART NO.

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

ATI_DQ[0:31] 5

OSPREY

3-27-2003_11:35

James Dalton

SHEET OF

Mike Ragan

Jon Rankin (ATI)

6

Physical Design

Jeff Davis

13

B

C

D

E

F

G

H

I

JJ

6 9

108754321

Page 7

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

REL

DEVELOPMENT NO. Q/M

A

4/7/02 JWD Changed 5V symbol, Changed ESD back to 5V

01/15/03 JWD Placed two 0 ohm resistors between chassis ground and signal ground to fix EMC problem.

B

PCI_3.3V

73P9250

A

B

PLEASE REFER TO UPDATED IN DXDATABOOK

J5

L4

5,7

C

5,7

5,7

D

VIDEO_HSYNC5

E

VIDEO_RED

VIDEO_GREEN

VIDEO_BLUE

C59

R63

10P

75

NOPOP

15P

C44

R62

75

AHCT125_SO14N

15P

C41

R61

15P

75

PCI_5V

U7

14

5

7

L2 GREEN_L

FERRITE ACB3216M

P/D_NUM=09G9963

VEN_P/D_NUM=HF30ACB-321611-T

C43

6

4

FERRITE ACB3216M

L3

FERRITE ACB3216M

P/D_NUM=09G9963

VEN_P/D_NUM=HF30ACB-321611-T

HSYNC_BUF

P/D_NUM=09G9963

VEN_P/D_NUM=HF30ACB-321611-T

C60

100P

NOPOP

R49

10

10P

C45

10P

C56 C49

10P

C48

82P

RED_L

BLUE_L

HSYNC_R

VSYNC_R

1

RED

2

GREEN

3

BLUE

13

HSYNC

14

VSYNC/DDC_CLK

6

REDRTN/CGND1

7

GRNRTN/CGND2

8

BLUERTN/CGND3

5

GND1

10

GND2

15 PIN DSHELL NC

VIDEO CONN

"VIDEO"

6

111

MID0

SDA/MID1

MID2

SCL/MID3

SHELL2

SHELL1

11

12

4

15

9

MH1

MH2

VIDEO_P11A

DDCDAT_N_R

VIDEO_P4A

DDCCLK_N_R

VIDEO_VCC_TH

c

R54

TH1

1K

PCI_5V

R59

1K

R53

VENDOR=RAYCHEM

VEN_P/D_NUM=SMD100-2

C55

100N

2.2K

R60

PCI_5V

2.2K

C52

C53

100P

100P

R65

33

R52

33

Q3

Q4

C51

C50

10P

10P

3

D

FET_2N7002

3

D

1

FET_2N7002

G

1

G

R66

2

S

PCI_3.3V

R67

2

S

6.8K

6.8K

ATI_DDCDAT

ATI_DDCCLK

C

5,7

D

5,7

E

PCI_5V

U7

VIDEO_VSYNC5

AHCT125_SO14N

C58

F

G

10P

NOPOP

14

2

3

1

7

R58

VSYNC_BUF

1K

C61

100P

NOPOP

R50

10

C57

82P

0

0

R556

R540

CYA for EMC

F

c

G

H

5,7

VIDEO_RED

I

CR1

2

CR2

3

1

2

3

1

5,7

VIDEO_GREEN

5,7

VIDEO_BLUE

CR3

PCI_5VPCI_5VPCI_5V

HSYNC_BUF

2

CR4

3

1

2

CR5

3

BAV99 BAV99BAV99BAV99 BAV99

1

2

3

1

VSYNC_BUF

5,7

ATI_DDCDAT

CR10

PCI_3.3V

2

CR11

3

BAV99 BAV99

1

2

3

1

ESD Protection

5,7

ATI_DDCCLK

Analog Video Connector

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

0.13

2.0

PART NO.

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

OSPREY

3-27-2003_11:35

James Dalton

SHEET OF

Mike Ragan Jeff Davis

Jon Rankin (ATI)

7

Physical Design

13

H

I

JJ

6 9

108754321

Page 8

961 2 3 4 5 7 8 10

4/7/02 JWD-NOPOP all USB power components.

4/7/02 JWD-Added PCI_3.3V to SMP connector, Will be used to determine if server is on

4/10/02 JWD-Added FAULT_LED signal to SMP

A

Ext I/O Connector

Keep inductor/capacitor filter near connector

01/15/03 JWD-populated R563 and R564 to fix EMC problems.

REL

EC NO.DATEQTYREL FOR ASM

PART NO.

73P9250

DEVELOPMENT NO. Q/M

A

L52

485_EXT_P

BLM21P300S

8

L53

485_EXT_N

External Dongle Connector

J39

CONN2X18_4P

1

B

C

D

USB_EXT_P

8

USB_EXT_N

8

405_BIST_L_N

8

COM5_RTS1#

9

COM5_DTR1#

9

COM5_TX1

9

COM5_DCD1#

9

COM5_CTS1#

9

COM5_DSR1#

9

COM5_232RX1

9

COM4_RX1

9

COM4_DSR1#

9

COM4_CTS1#

9

COM4_CD1#

9

COM4_TX1

9

COM4_DTR1#

9

c

C1

2

C2

4

C4

5

C5

6

C6

7

C7

8

C8

9

C9

10

C10

11

C11

12

C12

13

C13

14

C14

15

C15

16

C16

17

C17

18

C18

MH1

MH1

MH2 MH4

MH2 MH4

C19

C20

C21C3

C22

C23

C24

C25

C26

C27

C28

C29

C30

C31

C32

C33

C34

C35

C36

MH3

19

20

213

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

MH3

USB_GND

COM4_RTS1#

c

9

BLM21P300S

220P

C563

C564

220P

Place separate chassis gnd under connector.

L74

405_BIST_L_N

8

ohms

1000

E

PULSE J0011D21E

J1

F

MH3

MH3

MH4

MH4

G

GRN

GRN

GL_AN

GL_CA

GR_AN

GR_CA

c

MATCHING LENGTHS, SAME LAYER FOR PAIRS (50 Ohm SE, 100 Ohm Diff)

1

A

2

B

3

C

4

D

5

E

6

F

10

12

11

7

8

9

470

470

R32

G

H

ENET_PHY_TX

ENET_PHY_TX_N

ENET_PHY_RX

ENET_PHY_RX_N

3.3VC

R9

R10

8

8

8

8

ENET_PHY_LNK_LED_N

ENET_PHY_ACT_LED_N

3.3VC

C14

10N

8

8

C660

405_BIST_N

220P

R562

8

3.3VC

R563

330

330

CR22

1 2

A1 C1

3 4

A2 C2

553-0123

Green: Top - Pin 3

Yellow: Bottom - Pin 1

405GP_INSANE_N

405_ACT

Ethernet Connector

H

c

ENET_GND is a seperate ground plane under connector

0

that is isolated from GND, but connected to the chassis ground.

8

405_BIST_N

8

4.7K

COM3_RX

COM3_TX

COM3_CTS#

COM3_RTS#

3.3VC

9

9

9

9

Osprey ID = 2

3.3VC

COM4_RTS#

9

R543

Can be used by host in Harrier only implementations.

used for manufacturing test

6

9

9

9

9

9

9

9

9

9

8

8

PCI_3.3V

9

8

8

5

9

8

8

4

4

8

8

9

9

4

9

USB_SMP_P

USB_SMP_N

3V_PPCI_RST_N

RS232_DETECT

SMBUS_BUSY_N

COM5_DTR#

COM5_DSR#

COM5_TX

COM5_CTS#

COM5_232RX

COM5_RI#

COM5_DCD#

COM5_RTS#

COM4_TX

COM4_RX

SMP_I2C_SDA

SMP_I2C_SCL

HOST_PWRGD/RST#

HOST_PWR_REQ#

HOST_I2C_INT#

SMBUS_REQ#

COM4_CTS#

COM4_DTR#

HOST_SMI#

COM4_DSR#

HOST_ID0

HOST_ID1

HOST_ID2

HOST_ID3

HOST_ID4

HOST_ID5

HOST_ID6

HOST_ID7

RS232_ENABLE

P_EXT_ACK#

GPIO1

GPIO16

IRQ4

IRQ1

3.3VC

J35

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

KEY

C71

C72

C73

C74

C75

C76

C77

C78

C79

C80

C81

C82

C83

C84

C85

C86

C87

C88

C89

C90

C91

C92

C93

C94

C95

C96

C97

C98

C99

C100

C101

C102

C103

C104

C105

C106

C107

C108

C109

C110

C111

C112

C113

C114

C115

C116

C117

C118

C119

C120

C121

C122

C123

C124

C125

C126

C127

C128

C129

C130

C131

C132

C133

C134

C135

C136

C137

C138

C139

C140

C1

C2

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

C14

C15

C16

C17

C18

C19

C20

C21

C22

C23

C24

C25

C26

C27

C28

C29

C30

C31

C32

C33

C34

C35

LCD Port (Raw Digital Video)

C36

C37

C38

C39

C40

C41

C42

C43

C44

C45

C46

C47

C48

C49

C50

C51

C52

C53

C54

C55

C56

C57

C58

C59

C60

C61

C62

C63

C64

C65

C66

C67

C68

C69

C70

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

EXT_TMDS_RED6

EXT_TMDS_RED7 6

EXT_TMDS_RED2

EXT_TMDS_RED3

EXT_TMDS_RED4

EXT_TMDS_RED5

EXT_TMDS_GRN6

EXT_TMDS_GRN7

EXT_TMDS_BLU7

EXT_TMDS_HSYNC

EXT_TMDS_VSYNC

EXT_TMDS_DE

EXT_TMDS_CLK

EXT_TMDS_RED1

EXT_TMDS_GRN3

EXT_TMDS_GRN4

EXT_TMDS_GRN5

EXT_TMDS_BLU1

EXT_TMDS_BLU4

EXT_TMDS_GRN1

EXT_TMDS_GRN2

EXT_TMDS_BLU3 6

EXT_TMDS_BLU6 6

EXT_TMDS_BLU2 6

EXT_TMDS_BLU5 6

485_N_BUS_B

485_P_BUS_B

485_EXT_N

485_EXT_P

405GP_INSANE_N

COM4_CD#

ENET_PHY_RX_N

ENET_PHY_RX

ENET_PHY_TX_N

ENET_PHY_TX

ENET_PHY_LNK_LED_N

405_ACT

ENET_PHY_ACT_LED_N

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

Raptor Umbilical Connector

CONT_PWR

B

+

C521

NOPOP

22U

J36

20

8

8

4

4

4

8

4

8

4

8

8

USB_INT_N

USB_INT_P

485_INT_P

485_INT_N

HOST_SMI_UMB#

HOST_I2C_INT#

HOST_PWR_REQ_UMB#

SMBUS_REQ#

HOST_PWRGD/RST_UMB#

HOST_I2C_SCL

HOST_I2C_SDA

C527

0.1U

C528

0.1U

C529

0.1U

NOPOP

NOPOP

NOPOP

Cable must swap pins 16 and 17 to connect to Condor 2000 Header

Cable must swap pins 10 and 18 to connect to Condor 2000 Header

U92

USB_EXT_P

8

4

4

USB_INT_P

8

8

8

9

8

8

+

1

2

8

8

3v

8

BH1

8

8

8

PANASONIC

BR1225-1HC

USB_EXT_N

8

S1ININ = 1

1

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

U93

S1ININ = 1

1

C20

19

C19

18

C18

17

C17

16

C16

15

C15

14

C14

13

C13

12

C12

11

C11

10

C10

9

C9

8

C8

7

C7

6

C6

5

C5

4

C4

3

C3

2

C2

1

C1

Crow 2002

VENDOR=MOLEX

VEN_P/D_NUM=53780-2090

3.3VC

VCC

5

6

D

4

3.3VC

VCC

5

6

USB_SMP_P

EXA_SLOT_PRSNT

8

C

D

E

F

G

H

8

KEY

3.3VC

I

INT_I2C_SDA

5

HOST_I2C_SDA

8

U94

VCC

5

S1ININ = 1

1

6

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

4

INT_I2C_SCL

5

D

SMP_I2C_SDA

8

HOST_I2C_SCL

8

U95

VCC

5

S1ININ = 1

1

6

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

4

3.3VC

VENDOR=MOLEX

VEN_P/D_NUM=52760-1409

SMP Connector

EXA_SLOT_PRSNT

D

SMP_I2C_SCL

8

8

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

CONNECTORS

6 9

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

0.13

2.0

8

USB_INT_N

1/1SCALE:

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

PART NO.

TITLE

OSPREY

3-27-2003_11:35

DESIGNER

CHECKED

APPROVED

SHEET OF

D

4

James Dalton

Jon Rankin (ATI)

USB_SMP_N

Physical Design

Mike Ragan Jeff Davis

8

108754321

13

8

I

JJ

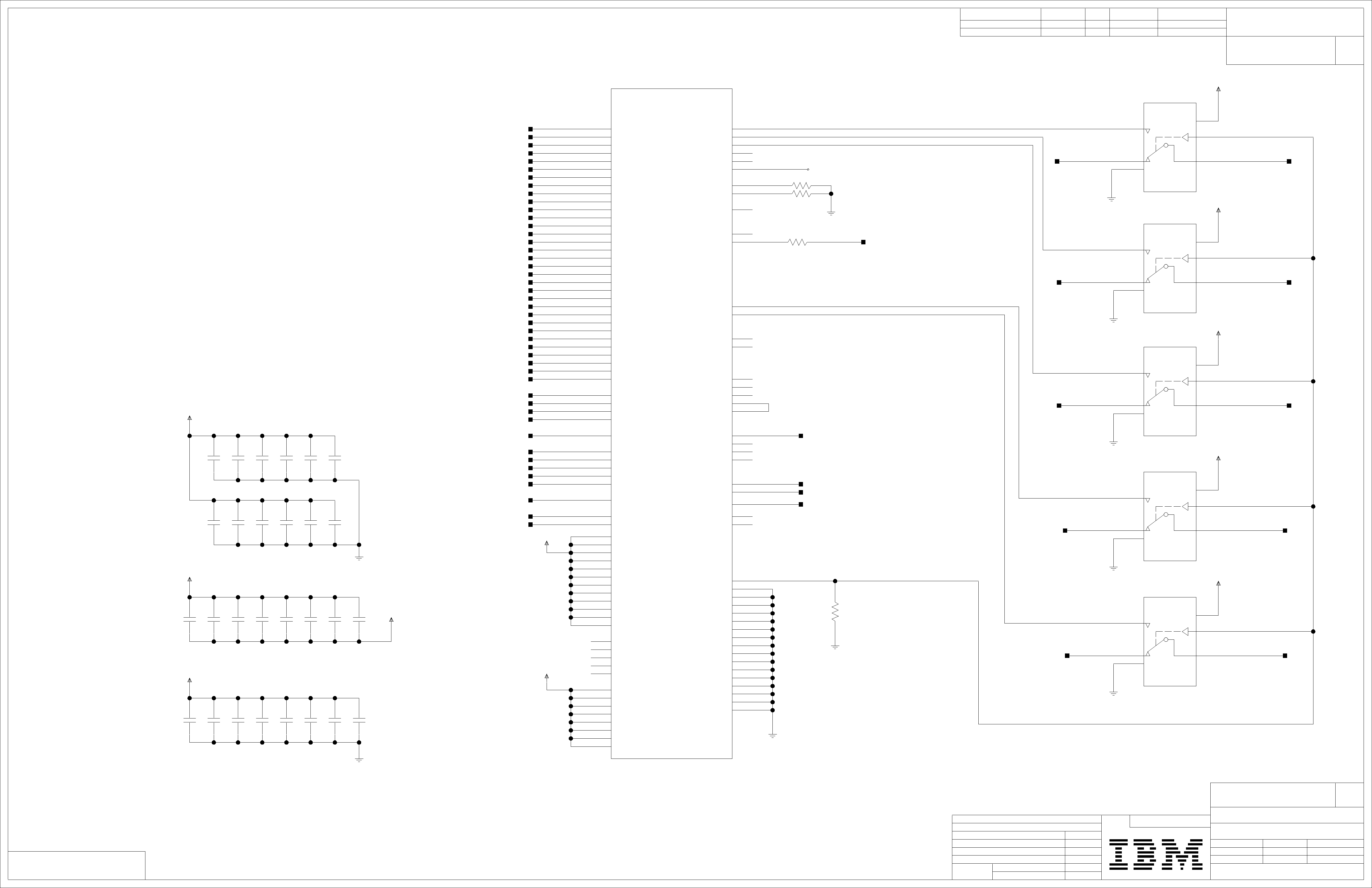

Page 9

01/15/03 JWD- NOPOPed U85,CR132,CR142,CR152,J38

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

73P9250

DEVELOPMENT NO. Q/M

A

A

C553

C552

100N

U83

100N

28

C1

24

C1_N

1

C2

B

8

8

8

8

8

8

C

8

8

COM5_TX

COM5_DTR#

COM5_RTS#

COM5_RI#

COM5_232RX

COM5_DSR#

COM5_CTS#

COM5_DCD#

2

C2_N

14 9

T1IN T1OUT

13 10

T2IN T2OUT

12 11

T3IN T3OUT

20

R2OUTB

ST3243ECTR

V_N

R1INR1OUT

R2INR2OUT

R3INR3OUT

R4INR4OUT

R5INR5OUT

27

V

3

C550

C551

100N

100N

B

3 6

2 7

1 8

419

518

617

716

815

4 5

3 6

2 7

1 8

4 5

120

120

120

120

120

120

120

120

ohms

ohms

ohms

ohms

ohms

ohms

ohms

ohms

L56

COM5_TX1

L56

COM5_DTR1#

L56

COM5_RTS1#

L57

L57

L57

L57

L56

COM5_RI1#

COM5_232RX1

COM5_DSR1#

COM5_CTS1#

COM5_DCD1#

8

8

8

8

8

8

C

8

3.3VC

22

FORCEOFF_N

23

FORCEON

INVALID_N

21

3.3VC

CN4

470P

1 8

CN4

CN4

2 7

3 6

470P

470P

CN4

CN3

470P

4 5

470P

1 8

CN3

470P

CN3

CN3

3 6

2 7

4 5

470P

470P

25

GND

VCC

26

D

D

R550

NOPOP

0

VENDOR=ST_MICRO

VEN_P/D_NUM=ST3243ECTR

C581

C549

10N

RS232_DETECT

8

R551

0

100N

C588

C589

2

E

NOPOP

CR13

For Debug (NOPOP for production)

GREEN

1

Place on Back

100N

100N

C582

C583

100N

100N

F

8

8

G

8

8

COM3_TX

COM3_RTS#

COM3_RX

COM3_CTS#

U85

28

C1

24

C1_N

1

C2

2

C2_N

14 9

T1IN T1OUT

13 10

T2IN T2OUT

12 11

T3IN T3OUT

ST3243ECTR

V_N

R1INR1OUT

R2INR2OUT

R3INR3OUT

R4INR4OUT

R5INR5OUT

27

V

3

419

518

617

716

815

C585

COM3_TX1

COM3_RTS1#

C584

100N

100N

COM3_232RX1

COM3_CTS1#

R533

330

J38

CONN2X5

1

C1

2

C2

3

C3

4

C4

5

C5

6

C6

7

C7

8

C8

9

C9

10

C10

2mm

Debug Port

NOPOP

8

8

8

8

8

8

8

COM4_TX

COM4_DTR#

COM4_RTS#

COM4_RX

COM4_DSR#

COM4_CTS#

COM4_CD#

3.3VC

U88

28

C1

24

C1_N

1

C2

2

C2_N

14 9

T1IN T1OUT

13 10

T2IN T2OUT

12 11

T3IN T3OUT

20

R2OUTB

22

FORCEOFF_N

23

FORCEON

ST3243ECTR

V_N

R1INR1OUT

R2INR2OUT

R3INR3OUT

R4INR4OUT

R5INR5OUT

INVALID_N

27

V

3

419

518

617

716

815

21

C591

3.3VC

C590

100N

100N

Place caps and inductors close to 26 pin connector

CN2

3 6

2 7

1 8

3 6

2 7

1 8

4 5

470P

CN2

CN2

2 7

1 8

3 6

470P

470P

CN2

CN1

4 5

2 7

470P

470P

CN1

CN1

3 6

4 5

470P

470P

120

120

120

120

120

120

120

ohms

ohms

ohms

ohms

ohms

ohms

ohms

L54

COM4_TX1

L54

COM4_DTR1#

L54

COM4_RTS1#

L55

COM4_RX1

L55

COM4_DSR1#

L55

COM4_CTS1#

L54

COM4_CD1#

8

8

8

8

8

8

8

E

F

G

20

3.3VC

H

R552

0

R2OUTB

22

FORCEOFF_N

23

FORCEON

25

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=ST3243ECTR

INVALID_N

VCC

21

26

C587

C586

10N

3.3VC

100N

R553

NOPOP

0

25

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=ST3243ECTR

NOPOP

VCC

26

C593

C592

10N

NOPOP

100N

CR15

H

2

GREEN

For Debug (NOPOP for production)

1

R549

2

I

NOPOP

CR14

For Debug (NOPOP for production)

GREEN

Place on Back

330

I

1

PART NO.

R544

330

RS232 Driver

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

6 9

0.13

2.0

TITLE

OSPREY

1/1SCALE:

3-27-2003_11:35

DESIGNER

CHECKED

James Dalton

Jon Rankin (ATI)

Mike Ragan

Physical Design

Jeff Davis

JJ

APPROVED

SHEET OF

9

13

108754321

Page 10

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

REL

A

B

4/7/02 JWD - Changed pull-up VCC to non-cont.

5/23/02 JWD - changed all pull-downs to nopop due to internal pull-downs

5/23/02 JWD - deleted static GPIO4 logic. GPIO4 is now controlled by an inverter off from M66EN#

DEVELOPMENT NO. Q/M

73P9250

A

B

Radeon VE PinBased BOOTSTRAPS

All signals have internal pull downs

PCI_3.3V

PCI_3.3V

U77

14

21

7

R515

5/23/02 JWD - Added logic to support 66MHz operation

10/31/02 JWD - Replaced inverter (wasn't fast enough)

MH2

1

2

3

M66EN

NOPOP

R528

10K

C547

10N

4

C

D

1

2

3

10K

ATI_GPIO4

6

refclk 2 taps earlier than feedback 1 1

AGPFBSKEW(1:0)

refclk slightly earlier than feedback 0 0

refclk 1 tap earlier than feedback 1 0

refclk 1 tap later than feedback 0 1

X1CLK_XSKEW(1:0)

ATI_GPIO2 ATI_GPIO3

0 Tap Delay 0 0

1 Tap Delay 1 0

2 Taps Delay 0 1

3 Taps Delay 1 1

BUSCFG(2:0)

ATI_GPIO4 ATI_GPIO5 ATI_GPIO6

PCI 33MHz,REF clk 1 0 1

PCI 66MHz,PLL clk 0 0 1

ATI_GPIO0 ATI_GPIO1

6

6

6

6

6

6

ATI_GPIO0

ATI_GPIO1

ATI_GPIO2

ATI_GPIO3

ATI_GPIO5

ATI_GPIO6

NOPOP

NOPOP

NOPOP

NOPOP

NOPOP

POP

R18

R17

R13

R12

R6

R16

10K

10K

10K

10K

10K

10K

Strap: 0

Strap: 0

Strap: 0

Strap: 0

Strap: 0

Strap: 1

C

D

4

4

5

6

7

8

MH1

MH2

5

6

7

8

NOPOP

MH1

TOP

BOTTOM

Dummy part place holder for bom

MECH1

MECH_PART

HEATSINK

Dummy part place holder for bom

MECH2

MECH_PART

BRACKET_SCREW

Stand-Offs

Dummy part place holder for bom

MECH3

MECH_PART

STAND-OFFS

Dummy part place holder for bom

MECH9

MECH_PART

STAND-OFFS

Dummy part place holder for bom

MECH8

MECH_PART

STAND-OFFS

Dummy part place holder for bom

MECH10

MECH_PART

STAND-OFFS

VGA_DISABLE

VGA controller capability enabled 0

VGA controller capability Disabled 1

ID_DISABLE

Normal Op 0

Chip shutdown 1

ROMIDCFG(2:0)

ATI_GPIO11 ATI_GPIO12 ATI_GPIO13

Serial AT25F1024 1 0 1

Enintb

En Interrupt 0

Dis Interrrupt 1

ATI_GPIO7

6

6

6

6

5

ATI_GPIO8

ATI_GPIO11

ATI_GPIO12

ATI_GPIO13

STEREOSYNC

6

NOPOP

NOPOP

POP

NOPOP

POP

NOPOP

R5

R15

R11

R8

R7

R4

10K

10K

10K

10K

10K

10K

Strap: 0

Strap: 0

Strap: 1

Strap: 0

Strap: 1

Strap: 0

E

c

F

c

G

E

F

G

BRACKET

H

Video Connector Screws

Dummy part place holder for bom

MECH11

MECH_PART

JACKSCREW

I

Dummy part place holder for bom

MECH12

MECH_PART

JACKSCREW

Dummy part place holder for bom

Dummy part place holder for bom

Connector Screws

Dummy part place holder for bom

MECH4

MECH_PART

CONNECTOR_SCREW

MECH6

MECH_PART

CONNECTOR_SCREW

CONNECTOR_SCREW

Dummy part place holder for bom

CONNECTOR_SCREW

MECH5

MECH_PART

MECH7

MECH_PART

PART NO.

H

I

STRAPS

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

OSPREY

3-27-2003_11:35

James Dalton

SHEET OF

Mike Ragan

Jon Rankin (ATI)

10

Physical Design

Jeff Davis

JJ

13

108754321

Page 11

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

REL

A

3.3V or 5V

CONT_PWR

B

Vin for

EXT16V CONN (regulated)

C

D

3.3VC

PCI_5V

J34

3

RAPC712

3.0A

MBRS340T3

PCI_5V

CONT_PWR

1

2

VOLTAGE=16

C8

10U

C9

10U

2

DIO_STPS0530Z

30

V

2

EXT16V

DIO_STPS0530Z

30

V

2

DIO_STPS0530Z

30

V

CR18

1

CR19

1

2

ON-SEMI

V

50

2

ON-SEMI

CR16

1

1

D5

CR21

41

DIO_50WQ03FN

3

IR

3.0A

MBRS340T3

1

D4

EXT_CONT+INT_CONT+INT_NON_CONT

Create 3.3VC Power Island under SMP

C642

C639

10UNOPOP

10U

C638

C574

10U

PWR GND - Route on

100N

L59

uH

3.3

IND2P_3_3U

COILCRAFT

DT3316P-332

DIO_STPS0530Z

separate layer from signal ground

1

CR17

U96

1

LDO

SYNC_SHDN_N

10

2

V

30

D

5678

C636

10U

C637

10U

CR20

V

50

DIO_50WQ03FN

3

IR

41

DEVELOPMENT NO. Q/M

R23

PKG_TYPE=1206

73P9250

Vout

3.3VC

3.3VC

R22

0

0

PKG_TYPE=1206

A

B

C

D

2

FREQ

E

4

REF

5

FB

R559

F

C633

110K

C645

220N

1U

MAX669EUB

PGND

Signal GND

VCC

EXTGND

CS

9

R561

83

0

7

6

C643

100N

NOPOP

CR23

30

1

V

2

DIO_STPS0530Z

FET_NCH_SI4442DY

G

4

VISHAY

R560

123

S

0.02

PWR GND - Route on separate layer from signal ground

Q5

uH

3.3

L60

DT3316P-332

COILCRAFT

IND2P_3_3U

R558

NOPOP

16.5K

C635

100U

C634

100U

C641

10U

C640

C554

10U

100N

E

F

G

C644

160P

H

R534

10K

G

H

Signal GND

I

PART NO.

I

3.3V CONTINUOUS POWER FOR HARRIER

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

1/1SCALE:

TITLE

OSPREY

3-27-2003_11:35

DESIGNER

CHECKED

APPROVED

James Dalton

Marshall Stanley

Marshall Stanley

SHEET OF

11

Mike Ragan

108754321

Physical Design

Jeff Davis

Marshall Stanley

Marshall Stanley

13

JJ

Page 12

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

REL

DEVELOPMENT NO. Q/M

A

73P9250

A

2.5V Regulator @ 1.5 amp max (non-cont)

2_5V

PCI_3.3V

B

U79

L6932D2.5

1

2

EN

IN

PGOOD

OUT

3

4

100N

100N

100N

100N

B

C578

C577

P/D_NUM=26P1421

C

D

10U

VEN_P/D_NUM=L6932D2.5TR

VENDOR=ST_MICRO

GND_5

GND_6

5

6

GND_7

GND_8

7

8

P/D_NUM=26P1421

10U

C558

C555

C556

P/D_NUM=40H8328

C557

C

D

E

1.8V Regulator @ 1.5 amp (non-cont)

PCI_3.3V

F

U84

L6932D1.8

3

4

C580

P/D_NUM=26P1421

10U

100N

C561

100N

C559

100N

C560

100N

C562

C579

P/D_NUM=26P1421

10U

1

EN

2

IN

GND_5

GND_6

GND_7

GND_8

5

6

7

8

OUT

PGOOD

1_8V

P/D_NUM=40H8328

E

F

G

H

VEN_P/D_NUM=L6932D1.8TR

VENDOR=ST_MICRO

G

H

I

6 9

2.5V, 1.8V, POWER

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

OUTSIDE MAX

INSIDE MAX

0.13

2.0

PART NO.

TITLE

1/1SCALE:

3-27-2003_11:35

DESIGNER

CHECKED

APPROVED

OSPREY

James Dalton

SHEET OF

Mike Ragan

Doug Evans

Doug Evans Doug Evans

12

108754321

Physical Design

Jeff Davis

Doug Evans

13

I

JJ

Page 13

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

REL

A

CONT_PWR

PCI_5V

VOLTAGE=5

B

1_8V

VOLTAGE=1.8

PCI_3.3V

VOLTAGE=3.3

3.3VC

VOLTAGE=3.3

2_5V

VOLTAGE=2.5

For cap check.

VOLTAGE=5

DEVELOPMENT NO. Q/M

73P9250

A

B

PCI_3.3VPCI_3.3VPCI_3.3VPCI_3.3V

U77

C

AHCT125_SO14N

D

14

7

U7

9

43

14

8

10

7

AHCT125_SO14N

U77

14

65

7

PCI_5VPCI_5V

U7

14

12

11

13

7

U77

14

89

7

U77

14

1011

7

PCI_3.3V

U77

14

7

1213

PCI_3.3V

100N

C594

100N

100N

C595

100N

100N

C596

100N

100N

C597

100N

100N

C598

100N

100N

C599

100N

100N

C600

100N

100N

C601

100N

100N

C602

100N

100N

C603

100N

C

D

C604

E

F

CN1

470P

1 8

4 5

ohms

120

L55

100N

C614

C613

100N

C623

C605

100N

C615

C606

100N

C616

C607

100N

C617

C608

100N

C618

C609

100N

C619

C610

100N

C620

C611

100N

C621

C612

E

100N

C622

F

G

PCI_3.3V

H

100N

100N

3.3VC

C624

C625

PCI_3.3V

100N

100N

2_5V

C629

C628

PCI_3.3V

100N

100N

1_8V

C632

C631

G

H

I

100N

C626

100N

C627

100N

C630

I

Spare Parts

PART NO.

3-27-2003_11:35

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

OSPREY

James Dalton

SHEET OF

Mike Ragan Jeff Davis

13

108754321

Physical Design

JJ

13

Loading...

Loading...