Page 1

A B C

Dell Controlled Print

REV

X00

X01

A00-00

105745

D

REVISIONS

DESCRIPTIONECO DATE

INITIAL PROTOTYPE BUILD

ADD 3.3V FOR FLASH ROM 02/23/01

PRODUCTION RELEASE

05/02/00

06/20/01

APPROVED

B. FET

1

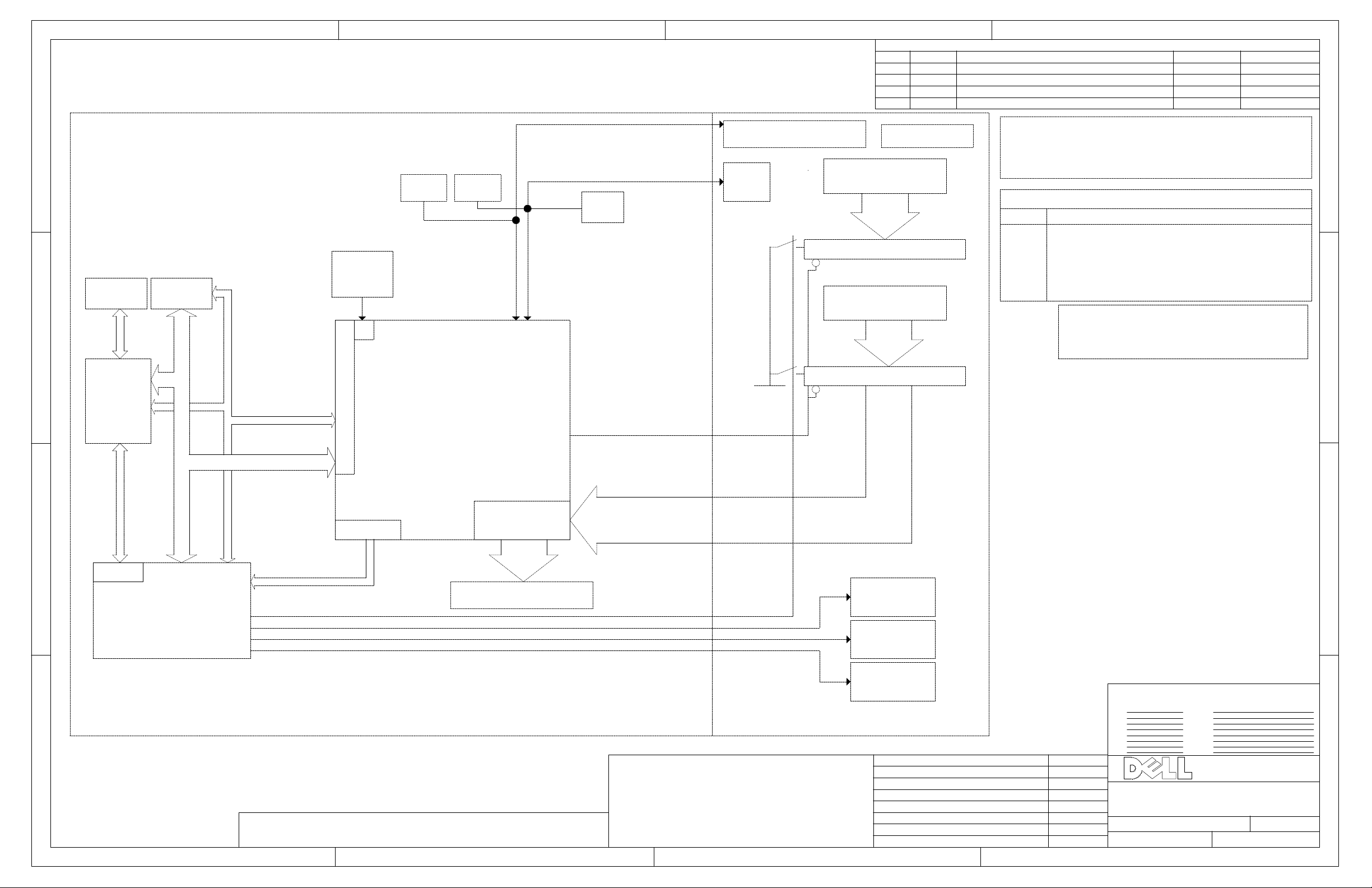

DEBUG PORTS

I2C0

PORT

I2C1

PORT

FRU

20MHZ

JTAG

SMVU

OSC

PORTPORT

MICROCONTROLLER INTERFACE

CLK

2

CTRL PNL/ PLNR

CONNECTOR

LM81

POWER

CONNECTOR

LVD SCSI

CONNECTOR A

SLOT 0

LVD SCSI

CONNECTOR B

1x2 DAUGHTER BOARD

PE6400/4400

TABLE OF CONTENTS

PAGE

1

BLOCK DIAGRAM

BKPLN/DTR MATING CONNECTOR

2

SPARES, DEBUG PORTS, MISC

3

4

GEM359

CPLD & FLASH ROM

5

SCSI LVD TERMINATION

6

SCHEMATIC IS CONFIGURED TO USE

THE XLBOM UTILITY:

BUILD0 IS PRODUCTION BUILD

BUILD1 IS PROTOTYPE BUILD

DESCRIPTION

1

2

SLOT 1

FLASH

ROM

512KX8

DATA BUS

ADDRESS BUS

QLOGIC GEM359

SCSI ID6

DRIVE PRESENCE

PWR

OUTPUT PORT

3

LVD SCSI

3

JTAG

FAULT

LEDS

ACTIVITY

CPLD

LOGIC

CONTROL

DRIVE POWER

SCSI BUS

TERMINATION

LEDS

ONLINE

LEDS

BACKPLANEDAUGHTER

4

THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS

LVD 1x2 SCSI BP

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER

CORP., EXCEPT AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN

ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE

REPRODUCED IN WHOLE OR IN PART AND MUST BE RETURNED TO DELL

COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION

OF THE PURPOSE OF THE LOAN. NEITHER THIS ITEM NOR THE

INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS

NOT HAVING A NEED FOR SUCH USE OR DISCLOSURE CONSISTENT WITH

THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF

DELL COMPUTER CORPORATION.

PROPRIETARY NOTE

DRAWN

DESIGNED

CHECKED

APPROVED

APPROVED

APPROVED

APPROVED

RELEASED

Santha Parameswaran

Bernard Fet

01/26/01

06/20/01

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO

TITLE

SCHEM,BKPLN,DTR,P6400/4400

DWG NO.

DATE

952RY

6/20/01

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

COMPUTER

CORPORATION

AUSTIN,TEXAS

SHEET

REV.

1 OF 6

4

A00-00

DCBA

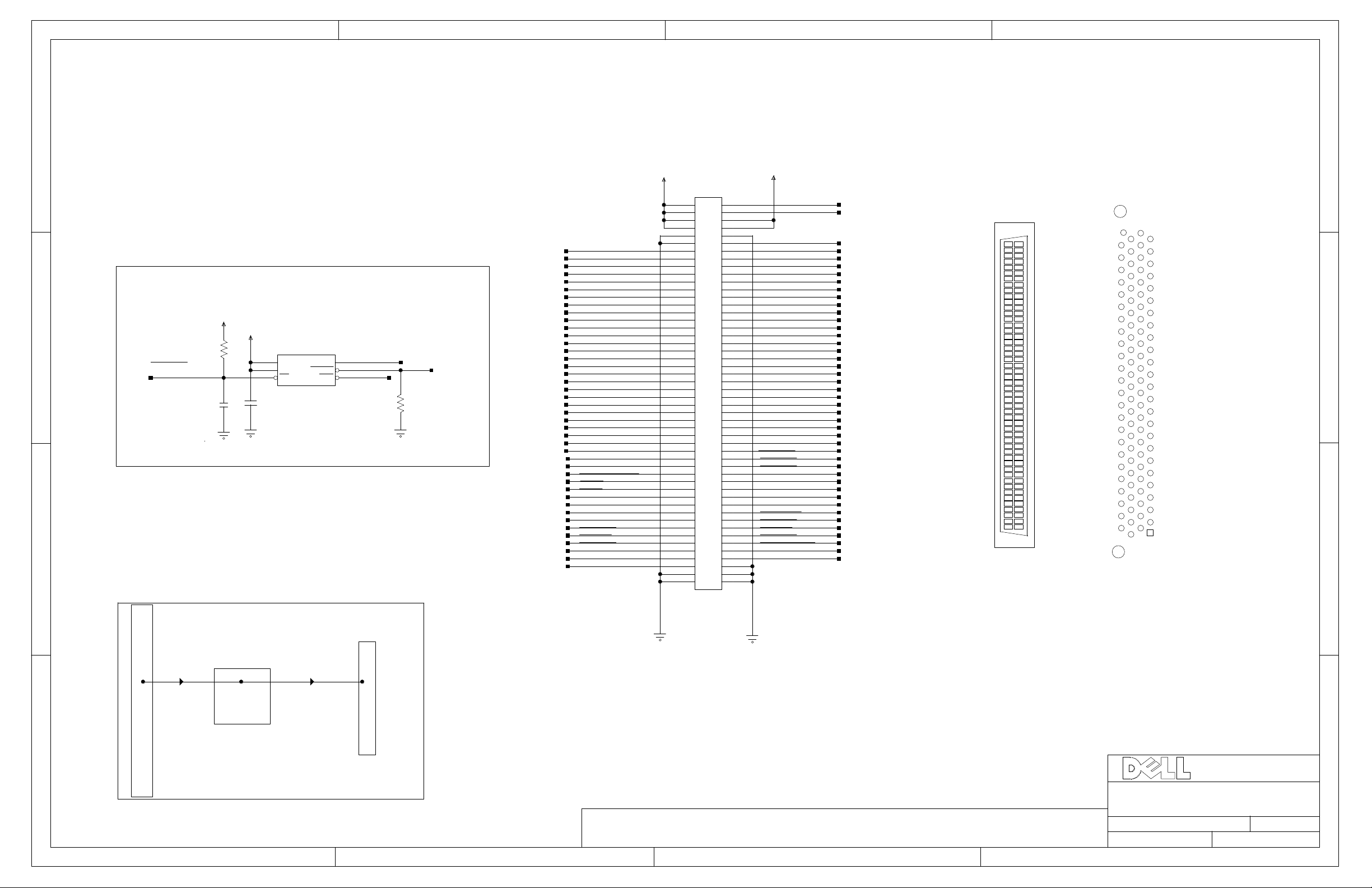

Page 2

A B C

D

1

+5V

DTRCONN

B2B_RTM

PLUG

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

1

2

3

4

5

6

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

7

8

9

B_SD-11

6

B_SD-10

6

B_SD-9

6

4,6

4,6

4,6

4,6

+5V

R82

1 2

12

C106

+5V

12

C23

.01uF 16V 8.2K-5%

2

VCC

4

PFI

.01UF

50V-20%

U1

RESET

RESET

MAX708

NC_RESET

8

7

NC_PFO

51

PFOMR

R81

2 1

PWRGOOD

2-5

100K-5%

2

MANRESET

2

3

POWER GOOD

4,6

4,6

4,6

4,6

4,6

4,6

4,6

4,6

4,6

4,6

4,6 4,6

4,6

4,6

4,6

4,6

2-5

3,4

3,4

4,5

B_SD-8

B_SIOB_SREQB_SCDB_SSELB_SMSGB_SRSTB_SACKB_SBSYB_SATNB_SDP-0

B_SD-7

B_SD-6

B_SD-5

B_SD-12

6

B_SD-13

6

B_SD-14

6

B_SD-15

6

B_SDP-1

6

B_SD-0

B_SD-1

B_SD-2

B_SD-3

B_SD-4

PWRGOOD

HD_PWR0

5

HD_PWR1

5

NC_DTRCONN_37

CONNA

4

CONNB

4

I2C1_D

I2C1_CLK

NC_DTRCONN_42

NC_DTRCONN_43

LEDONLN0

5

LEDACT0

5

LEDFALT0

5

3.3V_OUT

NC_DTRCONN48

DAUGHTER

+5V

NC_DTRCONN51

NC_DTRCONN52

B_DIFFSENSE

B_SD+11

B_SD+10

B_SD+9

B_SD+8

B_SIO+

B_SREQ+

B_SCD+

B_SSEL+

B_SMSG+

B_SRST+

B_SACK+

B_SBSY+

B_SATN+

B_SDP+0

B_SD+7

B_SD+6

B_SD+5

B_SD+12

B_SD+13

B_SD+14

B_SD+15

B_SDP+1

B_SD+0

B_SD+1

B_SD+2

B_SD+3

B_SD+4

MANRESET

HD_PRES0

HD_PRES1

DRIVEID0

DRIVEID1

DRIVEID2

I2C0_D

I2C0_CLK

I2C_ALERT

LEDONLN1

LEDACT1

LEDFALT1

NC_DTRCONN96

NC_DTRCONN97

4,6

6

6

6

4,6

4,6

4,6

4,6

4,6

4,6

4,6

4,6

4,6

4,6

4,6

4,6

4,6

4,6

6

6

6

6

6

4,6

4,6

4,6

4,6

2

4

4

4

4

4

3,4

3,4

4

5

5

5

SIDE VIEW

DPN: 8053C

COMPONENT

DTRCONN

50

100

51

1

BOTTOM VIEW

MOUNTING

HOLE

(NON-PLATED)

MOUNTING

HOLE

(NON-PLATED)

1009950

52

51

49

1

2

1

2

3

SCSIB

GEM359

DTRCONN

4

LVD SCSI TERMINATION B

BKPLN/DTR MATING CONNECTOR

COMPUTER

CORPORATION

TITLE

AUSTIN,TEXAS

4

SCHEM,BKPLN,DTR,P6400/4400

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

DWG NO.

DATE

952RY

6/20/01

SHEET

REV.

A00-00

2 OF 6

DCBA

Page 3

A B C

D

+5V

DEBUG SOCKET

SMVU PORT

3N5464

1

2

+5V

NP0

R40

1 2

8.2K-5%

2,4,5

3-5

3-5

3-5

3-5

3-5

3-5

3-5

3-5

3-5

5

5

PWRGOOD

PU_SMVU_18

SMVU_CS

SMVU_WRITE

A0

A1

D0

D1

D2

D3

D4

D5

D6

VIAS FOR IMPEDANCE COUPON

+5V

18

11

12

13

14

17

16

15

9

3

4

5

1

2

6

8

7

SMVU

VCC

CLR

BLANK

CUE

CUS

CE1

CE2

WR

A0

A1

D0

D1

D2

D3

D4

D5

D6

DLG2416

NP0

C91

+5V

12

NP0

.01UF

50V-20%

3-5

3-5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

+5V

NP0

R41

1 2

3N5468

R27

8.2K-5%

3N5496

21

220

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

FLASH_OE

5

NP0

DEBUG

12

A0

11

A1

10

A2

9

A3

8

A4

7

A5

6

A6

5

A7

27

A8

26

A9

23

A10

25

A11

4

A12

28

A13

29

A14

3

A15

2

A16

22

CE

24

OE

31

WE

28F001BX_TH

SOCKET

NP*

VCC

VPP

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

PWD

VSS

32

1

13

14

15

17

18

19

20

21

30

16

2 1

NP0

3N5497

3N5466

NP0

1206

FERRITE

L2

1206

FERRITE

L3

D0

D1

D2

D3

D4

D5

D6

D7

12

16V-10%

4.7uF

2 1

C105

NP0

50V-20%

.01UF

3-5

3-5

3-5

3-5

3-5

3-5

3-5

4,5

1 2

NP0

NP0

C92

+5V

R42

R26

21

1 2

8.2K-5%

NP0

220

I2C PORTS

NC_KEY_I2C1

2,4

2,4

2,4

2,4

I2C1_D

I2C1_CLK

NC_KEY_I2C0

I2C0_D

I2C0_CLK

Mounting Hole

MH1FLASH_WE

2

3

4

5

6

7

8

9

.150 DRILL

.375 PAD

8 GND VIAS

+5V

+5V

1

2

3

4

5

NP*

1

2

3

4

5

NP*

P2

P1

SPARES

KKEY

KKEY

SPARE PD/PU RESISTORS

+5V +5V

8.2K-5%

1 2

R44

NP*

SP_PU1 SP_PU2

NP*

R29

220

1 2

8.2K-5%

1 2

R43

NP*

SP_PD2SP_PD1

R28

220

1 2

NP*

1

2

L1A

1

L3A

L4A

L6A

L1_SCSI+

2

L1_SCSIL2_GND_REF

3

4

1

L3_SCSI+

2

L3_SCSIL2_GND_REF

3

4

1

L4_SCSI+

2

L4_SCSIL5_5V_REF

3

4

1

L6_SCSI+

2

L6_SCSIL5_5V_REF

3

4

+5V

+5V

TP_1

TP_2

TP_3

TP_4

IMPEDENCE

TEST POINT

TP_1

TP_2

TP_3

3

TP_4

IMPEDENCE

TEST POINT

TP_1

TP_2

TP_3

TP_4

IMPEDENCE

TEST POINT

TP_1

TP_2

TP_3

TP_4

IMPEDENCE

TEST POINT

NOTES ON ROUTING FOR COUPONS:

--> HOLES TO BE ARRANGED ON 100 MIL CENTERS FOR PROBE

--> FINISHED HOLE DIAMETER = 0.029"

4

--> TRACES NEED TO BE AT LEAST 6" LONG

--> AVOID VIAS, PLATED HOLES, AND COPPER EDGE OF PCB BY MIN 50 MILS

NOTES ON SILKSCREEN FOR COUPONS:

--> PLACE REFDES OF COUPON NEAR THE FOOTPRINT OF THE COUPON

--> SILKSCREEN SHOULD BE ON BOTH SIDES OF THE BOARD

L1B

1

TP_1

2

TP_2

3

TP_3

4

TP_4

IMPEDENCE

TEST POINT

L3B

1

TP_1

2

TP_2

3

TP_3

4

TP_4

IMPEDENCE

TEST POINT

L4B

1

TP_1

2

TP_2

3

TP_3

4

TP_4

IMPEDENCE

TEST POINT

L6B

1

TP_1

2

TP_2

3

TP_3

4

TP_4

IMPEDENCE

TEST POINT

STACKUP

LAYER#

OZ/FT^2

THICKNESS

(MILS)

1

0.50

2 1.00

3

4

1.00

1.00

5 1.00

6

0.50

0.7

15.7

1.40

21.0

1.40

9.2

1.40

21.0

1.40

15.7

0.7

GENERAL (NON-SCSI) ROUTING RULES:

--> USE 5 MIL TRACES FOR 60 OHM SIGNALS ON ALL ROUTING LAYERS

--> TRY TO USE ISLANDS FOR ALL POWER SIGNALS WITH NO POWER PLANE.

IF ISLANDS ARE NOT POSSIBLE, USE AT LEAST 25 MIL TRACES.

EG. GND, 3.3V, A_TRMPWR, B_TRMPWR

--> IF POWER SIGNALS DO HAVE A PLANE, USE AT LEAST 25 MIL TRACES WHERE NEEDED

--> USE MINIMUM 10 MIL TRACES FOR THESE SIGNALS:

LEDACT*, LEDFALT*, LEDONLN*

--> USE MINIMUM 20 MIL TRACES FOR THESE SIGNALS:

GATE12V_* & GATE5V_*

--> USE MINIMUM 25 MIL TRACES FOR THESE SIGNALS:

12VBAY_*, 5VCHARGE_*, 5VBAY_*

--> I2C SIGNALS SHOULD BE ROUTED SERIALLY. THERE SHOULD NOT BE ANY LONG

--> I2C1_D & I2C1_CLK SHOULD BE ROUTED TOGETHER

TRY TO KEEP THESE SIGNALS AWAY FROM OTHER SIGNALS.STUBS OR BRANCHES.

NAME

TOP

5V

INNER 1

INNER 2

GND

BOTTOM

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

ref

ref

ref

ref

ref

SCSI ROUTING RULES

LAYER PAIR - PAIR

NAME5VIMPEDANCE

#

1

2

TOP

GND

3

INNER 2

4

(OHMS)

123

120

120

5

BOTTOM6

NOTE ON SCSI ROUTING RULES:

--> SCSI SIGNALS ARE NAMED A(B)_*. THERE ARE 27 DIFFERENTIAL PAIRS

--> AVOID VIAS WHENEVER POSSIBLE.

--> IF VIAS ARE USED, USE THE SAME NUMBER OF VIAS BETWEEN ± DIFFERENTIAL

SIGNAL PAIRS.

--> TRY TO ROUTE ALL THE ± DIFFERENTIAL SIGNALS ON ONE LAYER

IF POSSIBLE, ROUTE THE SCSI BUS ON TWO ADJACENT LAYERS (INNER 1 & 2).

--> IF INNER 1 AND INNER 2 BOTH HAVE PARALLEL TRACES THERE MUST BE A MINIMUM

DISTANCE OF 15 MILS BETWEEN THE PARALLEL TRACES ON INNER 1 & INNER 2.

THEY CANNOT BE OVER EACH OTHER.

--> ROUTE EACH ± DIFFERENTIAL PAIR PARALLEL

--> BUS SPACING TO ANY OTHER SIGNAL SHOULD BE AT LEAST 2X, WHERE X IS THE

EDGE-EDGE SPACING OF THE DIFFERENTIAL PAIR

--> USE ARCS OR 45 DEGREE BEVELS AND AVOID 90 DEGREE BENDS

--> TRY TO ROUTE ALL OF THE LVD SIGNALS ON THE INNER LAYER CLOSEST TO THE

GROUND PLANE

--> STUB LENGTHS TO BE LIMITED TO 3 INCHES

--> PLACE TERMINATORS AT END OF BUS

--> MINIMIZE LENGTH OF STUB & NUMBER OF VIAS TO GEM

123

TRACE

WIDTH

(MILS)

5.0 6.0

5.0INNER 1

5.0

5.0

PAIR

SPACE

(MILS)

11.0

11.0

6.0

SPACE

(MILS)

15.0

15.0

15.0

15.0

TOLERANCES

SCSI Bus = 250 mils

Differential Pair = 50 mils

Stub Lengths (Bus) = 500 mils

Stub Lengths (Pair) = 100 mils

SPARES, DEBUG PORTS, MISC

COMPUTER

CORPORATION

TITLE

AUSTIN,TEXAS

SCHEM,BKPLN,DTR,P6400/4400

DWG NO.

DATE

952RY

6/20/01

SHEET

REV.

A00-00

3 OF 6

3

4

DCBA

Page 4

A B C

D

CPU_STRB

5

WRITE_EN

5

5

2

2

2

2

2

2

2

2

4

5

5

5

FLASH_OE

FLASH_VPP_EN

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

D0

D1

D2

D3

D4

D5

D6

D7

HD_PRES0

HD_PRES1

NC_DEV_INS3

NC_DEV_INS4

NC_DEV_INS5

NC_DEV_INS6

NC_DEV_INS7

NC_DEV_INS8

NC_DEV_INS9

NC_DEV_INS10

NC_DEV_INS11

NC_DEV_INS12

MASTER

CONNA

CONNB

DRIVEID0

DRIVEID1

DRIVEID2

NC_QL_ALERT_IN

NC_STAT7

NC_STAT8

NC_STAT9

NC_STAT10

NC_STAT11

NC_STAT12

NC_STAT13

CPLD_DPORT0

CPLD_DPORT1

CPLD_DPORT2

CPLD_DPORT3

CPLD_DPORT4

CPLD_DPORT5

CPLD_DPORT6

CPLD_DPORT7

MASK_STRB

POWER_STRB

I2C_ALERT

UNIQUE_ID

I2C1_D

I2C1_CLK

LEDONLN_STRB

LEDACT_STRB

LEDFALT_STRB

PWRGOOD

20MCLK

NC_EMUX

NC_LED_STRB

I2C0_CLK

I2C0_D

3,5

3,5

3,5

1

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

3,5

+5V

2

12

220

R30

4,5

4,5

4,5

4,5

4,5

2,3,5

33-5%

.01UF

50V-20%

4,5

4,5

4,5

4,5

4,5

2-4

2-4

2-4

2-4

3

4

R24

1 2

NP*

C93

2 1

NP*

4

136

CPU_STRB

142

PROM_WE

140

PROM_OE

139

PROM_VPP

16

A0

17

A1

18

A2

19

A3

64

A4

65

A5

22

A6

66

A7

67

A8

25

A9

26

A10

27

A11

134

A12

74

A13

75

A14

143

A15

28

D0

29

D1

30

D2

31

D3

32

D4

33

D5

137

D6

138

D7

4

DEV_INS0

5

DEV_INS1

6

DEV_INS2

7

DEV_INS3

44

DEV_INS4

45

DEV_INS5

10

DEV_INS6

53

DEV_INS7

54

DEV_INS8

13

DEV_INS9

59

DEV_INS10

60

DEV_INS11

116

GPIOC0[0]

117

GPIOC0[2]

118

GPIOC0[4]

119

GPIOC1[0]

120

GPIOC1[2]

121

GPIOC1[4]

122

GPIOC0[1]

123

GPIOC0[3]

124

GPIOC0[5]

125

GPIOC1[1]

126

GPIOC1[3]

127

GPIOC1[5]

128

GPIOB1[6]

115

GPIOB1[7]

48

GPIO0

41

GPIO1

52

GPIO2

55

GPIO3

58

GPIO4

63

GPIO5

80

GPIO6

76

GPIO7

83

GPIO8

95

GPIO9

99

GPIO10

87

GPIO11

42

GPIO12

43

GPIO13

131

GPO[0]

132

GPO[1]

133

GPO[2]

35

RESET

2

CLK

141

EMUX

135

LED_STRB

130

SCL

129

SDA

6047T - GEM354

24MYY - GEM359-LG1

63UPU - GEM359-LG2

GEM359

NC

VDD1

VDD2

VDD3

VDD4

SD0+

SD0SD1+

SD1SD2+

SD2SD3+

SD3SD4+

SD4SD5+

SD5SD6+

SD6SD7+

SD7-

SPD0+

SPD0-

SATN+

SATN-

RBIAS-

SBSY+

SBSY-

SACK+

SACK-

SRST+

SRST-

SMSG+

SMSG-

SSEL+

SSEL-

SCD+

SCD-

SREQ+

SREQ-

SIO+

SIO-

ID_ON0+

ID_ON0ID_ON1+

ID_ON1DIFFSENS

SCSI_SFF

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND10

GND11

GND12

GND13

GND14

GND15

GND16

GND17

GND18

GND19

112

1

36

73

108

105

106

101

102

97

98

93

94

89

90

85

86

81

82

77

78

69

70

23

24

113

61

62

20

21

14

15

56

57

11

12

50

51

46

47

39

40

8

9

103

104

111

92

3

34

37

38

49

68

71

72

79

84

88

91

96

100

107

109

110

114

144

NC_GEM359_112

FILGEM359_VCC

B_SD+0

B_SD-0

B_SD+1

B_SD-1

B_SD+2

B_SD-2

B_SD+3

B_SD-3

B_SD+4

B_SD-4

B_SD+5

B_SD-5

B_SD+6

B_SD-6

B_SD+7

B_SD-7

B_SDP+0

B_SDP-0

B_SATN+

B_SATN-

B_RBIASB_SBSY+

B_SBSYB_SACK+

B_SACKB_SRST+

B_SRSTB_SMSG+

B_SMSGB_SSEL+

B_SSELB_SCD+

B_SCDB_SREQ+

B_SREQB_SIO+

B_SIOB_SD+6

B_SD-6

B_SD+8

B_SD-8

B_DIFFSENSE

B_SCSI_ONLY

+5V

C95

12

L1

BLM11A60

.01UF

50V-20%

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,4,6

2,4,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,6

2,4,6

2,4,6

2,6

2,6

2,6

12

C96

C84

1 2

3.01K-1%

R58

1 2

8.2K-5%

12

.01UF

Place close to GEM359

12

C89

2 1

22uF 10V

1 2

R52

3.3V_OUT

C94

2 1

50V-20%

C90

0.1uF 16V

FIL20_VCC

.01UF

50V-20%

0.1uF 16V

2,4,5

R48

1 2

8.2K-5%

C8612C85

2 1

0.1uF 16V

3.3V_OUT

2,4,5

1

Place near GEM

C40

E/D

L4

21

12

C88

0.1uF 16V

0.1uF 16V

FERRITE

1206

3.3V_OUT

12

C87

0.1uF 16V

2,4,5

3.3V POWER

+5V

DPAK

LM1117 3.3V

VIN

21

10uF

16V 10%

TAB

4

Q1

GND

3

1

12

C39

22uF 10V

OSC IS 20 MHz (FTPRINT IS SAME)

U8

40MHZ

4

VCC

3

OUT

GND

2

SUB*_7508T

R20MHZRFIL20

R25

33-5%

21

20MCLK

4

21

R38

21

R35

NP*

R37

10K-5%

NP*

R34

10K-5%

21

21

NP*

NP*

+5V

NP*

21

R36

10K-5%

NP*

21

R33

10K-5%

10K-5%

10K-5%

1

2

3 6

4

FRU DEVICE

NP*

U2

A0

VCC

GND2

A1

A2 SCL

SDA

GND1

24C02

I2C PULL UP (Place near GEM)

+5V

R46

I2C1_D I2C0_D

2-4

I2C1_CLK

2-4

ADD*_42610_BAR

ADD*_42753_REV

ADD*_559RG_PWB

ADD*_952RY_SCHEM

ADD*_78DEP_ASSYDRW

ADD*_494VT_PWA

1 2

R47

8.2K-5%

1 2

8.2K-5%

64bit Unique ID

+5V

VR1

DS2401Z

DATA

GND

4 1

R57

4.7K

1 2

2

UNIQUE_ID

4

8

7

5

NP*

21

R39

GEM359

+5V

50V-20%

.01UF

470

2-4

2-4

4,5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

4,5

1 2

NP*

C97

NP*

R53

1 2

0-5%

NP*

R54

1 2

0-5%

I2C0_CLK

CPLD_DPORT0

CPLD_DPORT1

CPLD_DPORT2

CPLD_DPORT3

CPLD_DPORT4

CPLD_DPORT5

CPLD_DPORT6

CPLD_DPORT7

MASK_STRB

POWER_STRB

SP_RP8K2_6

SP_RP8K2_5

I2C1_CLK

I2C1_D

2-4

2-4

+5V

1 2

R50

8.2K-5%

NP*

8

RN3

7

6

5

8.2K

8

RN1

7

6

5

8.2K

8

RN2

7

6

5

8.2K

R49

NP*

COMPUTER

CORPORATION

AUSTIN,TEXAS

1 2

8.2K-5%

+5V

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

TITLE

SCHEM,BKPLN,DTR,P6400/4400

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

U3

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

DWG NO.

DATE

952RY

6/20/01

SHEET

REV.

A00-00

4 OF 6

DCBA

Page 5

A B C

D

512K x 8 FLASH ROM

R86

1 2

12

R51

+5V

NP*

0-5%

16V-10%

4.7uF

2 1

NP*

8.2K-5%

C83

50V-20%

.01UF

1 2

ROOM=U10

ROOM=U10

ROOM=U10

C63

50V-20%

.01UF

1 2

10

12

13

21

R83

220

R85

1 2

0-5%

5N2621

50V-20%

.01UF

C60

14

U10

4

6

5

74VHC32

14

U10

9

8

74VHC32

14

U10

11

74VHC32

ROOM=U10

3.3V_OUT

1 2

C62

3.3V_OUT

NC_VHC32_8

NC_VHC32_11

NC_VHC32_6

50V-20%

.01UF

1 2

2,4,5

C107

Locate C107 at U10

ROOM=U10

2,4,5

2-5

3-5

1

12

12

U7

3,4

3,4

3-5

3-5

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,5

ROOM=U10

ROOM=U10

3,4

2,4,5

FLASH_WE

2

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

FLASH_OE

3.3V_OUT

1

2

74VHC32

1 2

14

R87

0-5%

U10

3

NP*

21

A0

20

A1

19

A2

18

A3

17

A4

16

A5

15

A6

14

A7

8

A8

7

A9

36

A10

6

A11

5

A12

4

A13

3

A14

2

A15

1

A16

40

A17

13 12

NC DU

22

CE

24

OE

9

WE

28F002BX

SKT

SUB*_2H969

220

R32

2 1

SOCKET P/N = 5688T (PROTOTYPE ONLY)

VCC30

VCC31

VPP

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

PWD

VSS39

VSS23

30

31

11

25

26

27

28

32

33

34

35

10

39

23

D0

D1

D2

D3

D4

D5

D6

D7

PWRGOOD

BTWP

Build Options for ROM:

POP = must populate, DEPOP = must depop., OPT = may be either.

All but U7 are added to previous board.

3

U7, prog'd

U7, blank

U10

R83

R85

R86

R87

C107

5V, ESM2

PE6400/4400

06GNX

9779R

DEPOP

OPT

DEPOP

POP

POP

OPT

3.3V, ESM2

PE6400/4400

2H969

58PDC

POP

POP

POP

DEPOP

DEPOP

POP

NP*

R31

2 1

R56

220

R55

2.7K-5%

NP*

2-5

2.7K-5%

3,4

3,4

3,4

3,4

3,4

3,4

3,4

3,4

2

4

4

2

4

4

2

4

4

4

4

4

4

50V-20%

.01UF

LEDACT1

CPLD_DPORT3

NC_9572_18

NC_LEDACT3

CPLD_DPORT2

LEDFALT1

NC_9572_25

NC_LEDFALT2

LEDFALT_STRB

NC_LEDFALT3

LEDACT_STRB

NC_9572_33

LEDONLN1

LEDONLN_STRB

CPLD_DPORT0

NC_LEDONLN2

CPU_STRB

NC_9572_40

NC_LEDONLN7

MASK_STRB

CPLD_DPORT6

NC_LEDACT6

NC_LEDACT7

CPLD_DPORT7

NC_9572_3

NC_LEDFALT5

PWRGOOD

NC_9572_1

NC_9572_4

NC_LEDFALT6

NC_LEDFALT7

NC_LEDONLN5

A3

NC_9572_10

NC_LEDONLN6

NC_LEDACT5

NC_XILINX1

NC_XILINX2

NC_XILINX3

NC_XILINX4

NC_XILINX5

NC_XILINX6

NC_XILINX7

NC_XILINX8

NC_XILINX9

5

5

5

5

XILINX 9572 CPLD

+5V

1 2

C104

XILINX_TCK

XILINX_TDO

XILINX_TDI

XILINX_TMS

50V-20%

.01UF

50V-20%

.01UF

+5V

1 2

5

VCCINT1

57

VCCINT2

98

VCCINT3

16

IO1/FB1

13

IO2/FB1

18

IO3/FB1

20

IO4/FB1

14

IO5/FB1

15

IO6/FB1

25

IO7/FB1

17

IO8/FB1

22

IO9/GCK1

28

IO10/FB1

23

IO11/GCK2

33

IO12/FB1

36

IO13/FB1

27

IO14/GCK3

29

IO15/FB1

39

IO16/FB1

30

IO17/FB1

40

IO18/FB1

87

IO1/FB2

94

IO2/FB2

91

IO3/FB2

93

IO4/FB2

95

IO5/FB2

96

IO6/FB2

3

IO7/GTS1

97

IO8/FB2

99

IO9/GSR

1

IO10/FB2

4

IO11/GTS2

6

IO12/FB2

8

IO13/FB2

9

IO14/FB2

11

IO15/FB2

10

IO16/FB2

12

IO17/FB2

92

IO18/FB2

2

NC1

7

NC2

19

NC3

24

NC4

34

NC5

43

NC6

46

NC7

73

NC8

80

NC9

J1

1

2

3

4

5

6

NP*

C103

21

+5V +5V

50V-20%

C102

XC9572-15TQ

SUB*_53DJD

.01UF

U9

C98

21

IO1/FB3

IO2/FB3

IO3/FB3

IO4/FB3

IO5/FB3

IO6/FB3

IO7/FB3

IO8/FB3

IO9/FB3

IO10/FB3

IO11/FB3

IO12/FB3

IO13/FB3

IO14/FB3

IO15/FB3

IO16/FB3

IO17/FB3

IO18/FB3

IO1/FB4

IO2/FB4

IO3/FB4

IO4/FB4

IO5/FB4

IO6/FB4

IO7/FB4

IO8/FB4

IO9/FB4

IO10/FB4

IO11/FB4

IO12/FB4

IO13/FB4

IO14/FB4

IO15/FB4

IO16/FB4

IO17/FB4

IO18/FB4

VCCIO1

VCCIO2

VCCIO3

VCCIO4

+5V +5V +5V+5V+5V+5V

50V-20%

.01UF

21

26

38

51

88

41

32

49

50

35

53

54

37

42

60

52

61

63

55

56

65

58

59

66

64

71

72

67

76

77

68

70

81

74

82

85

78

89

86

90

79

48

TCK

45

TDI

83

TDO

47

TMS

50V-20%

C99

NC_9572_41

HD_PWR1

NC_9572_49

NC_HD_POWER3

CPLD_DPORT5

NC_HD_POWER5

NC_9572_54

NC_HD_POWER7

LEDONLN0

NC_9572_60

NC_LEDONLN3

NC_9572_61

FLASH_WE

POWER_STRB

SMVU_CS

WRITE_EN

SMVU_WRITE

NC_9572_59

HD_PWR0

A2

NC_HD_POWER2

NC_9572_72

NC_HD_POWER4

NC_9572_76

NC_HD_POWER6

CPLD_DPORT1

FLASH_VPP_EN

NC_9572_81

NC_LEDONLN4

NC_LEDACT2

NC_LEDACT4

LEDFALT0

CPLD_DPORT4

NC_9572_86

NC_LEDFALT4

LEDACT0

XILINX_TCK

XILINX_TDI

XILINX_TDO

XILINX_TMS

.01UF

1 2

C100

50V-20%

.01UF

BLANK P/N 2348T

PGMD P/N 53DJD

21

C101

2

4

2

3,5

4

3

4

3

2

3-5

4

4

2

4

2

5

5

5

5

1

2

3

CPLD & FLASH ROM

4

TITLE

COMPUTER

CORPORATION

AUSTIN,TEXAS

4

SCHEM,BKPLN,DTR,P6400/4400

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

DWG NO.

DATE

952RY

6/20/01

SHEET

REV.

A00-00

5 OF 6

DCBA

Page 6

A B C

D

SCSI Termination BUS A

+5V

22uF 10V

50V-20%

.01UF

1 2

C12

1

21

C9

50V-20%

.01UF

1 2

C8

1

L1+

L1L2+

L2L3+

L3L4+

L4L5+

L5L6+

L6L7+

L7L8+

L8L9+

L9-

UCC5640PW

L1+

L1L2+

L2L3+

L3L4+

L4L5+

L5L6+

L6L7+

L7L8+

L8L9+

L9-

UCC5640PW

U4

TRMPWR

DISCNCT

DIFFSENSE

DIFF_B

U6

TRMPWR

DISCNCT

DIFFSENSE

DIFF_B

REG

GND

REG

GND

24

13

11

10

1

12

24

13

11

10

1

12

B_DIFFSENSE

B_DIFF_B

B_REG_0

NC_B_DS_2

B_REG_2

16V-10%

4.7uF

1 2

C6

16V-10%

4.7uF

1 2

C3

2,4

21

R23

20K-5%

0.1uF 16V

1 2

C7

2

14

15

16

17

18

19

20

21

22

23

2

3

4

5

6

7

8

9

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2

2

2

2

2

2

2

2

B_SD+4

B_SD-4

B_SD+3

B_SD-3

B_SD+2

B_SD-2

B_SD+1

B_SD-1

B_SD+0

B_SD-0

B_SDP+1

B_SDP-1

B_SD+15

B_SD-15

B_SD+14

B_SD-14

B_SD+13

B_SD-13

2

14

15

16

17

18

19

20

21

22

23

2

3

4

5

6

7

8

9

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2

2

B_SD+12

B_SD-12

B_SD+5

B_SD-5

B_SD+6

B_SD-6

B_SD+7

B_SD-7

B_SDP+0

B_SDP-0

B_SATN+

B_SATNB_SBSY+

B_SBSYB_SACK+

B_SACKB_SRST+

B_SRST-

L1+

L1L2+

L2L3+

L3L4+

L4L5+

L5L6+

L6L7+

L7L8+

L8L9+

L9-

UCC5640PW

U5

TRMPWR

DISCNCT

DIFFSENSE

DIFF_B

REG

GND

24

13

11

10

1

12

NC_B_DS_3

B_REG_3

16V-10%

4.7uF

C4

21

3

14

15

16

17

18

19

20

21

22

23

2

3

4

5

6

7

8

9

3

ALL TERMPWR LINES TO TERMINATORS 50 MILS WIDE

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2,4

2

2

2

2

2

2

B_SMSG+

B_SMSGB_SSEL+

B_SSELB_SCD+

B_SCDB_SREQ+

B_SREQB_SIO+

B_SIOB_SD+8

B_SD-8

B_SD+9

B_SD-9

B_SD+10

B_SD-10

B_SD+11

B_SD-11

SCSI LVD TERMINATION

4

TITLE

COMPUTER

CORPORATION

AUSTIN,TEXAS

4

SCHEM,BKPLN,DTR,P6400/4400

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

DWG NO.

DATE

952RY

6/20/01

SHEET

REV.

A00-00

6 OF 6

DCBA

Loading...

Loading...