MSI MS-9550 9527_10A

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

DEVELOPMENT NO. Q/M

B

A

B

Contents:

C

C

HARRIER PASS5C

1. TITLE

2. CHANGE LOG

3. HARRIER BLOCK DIAGRAM

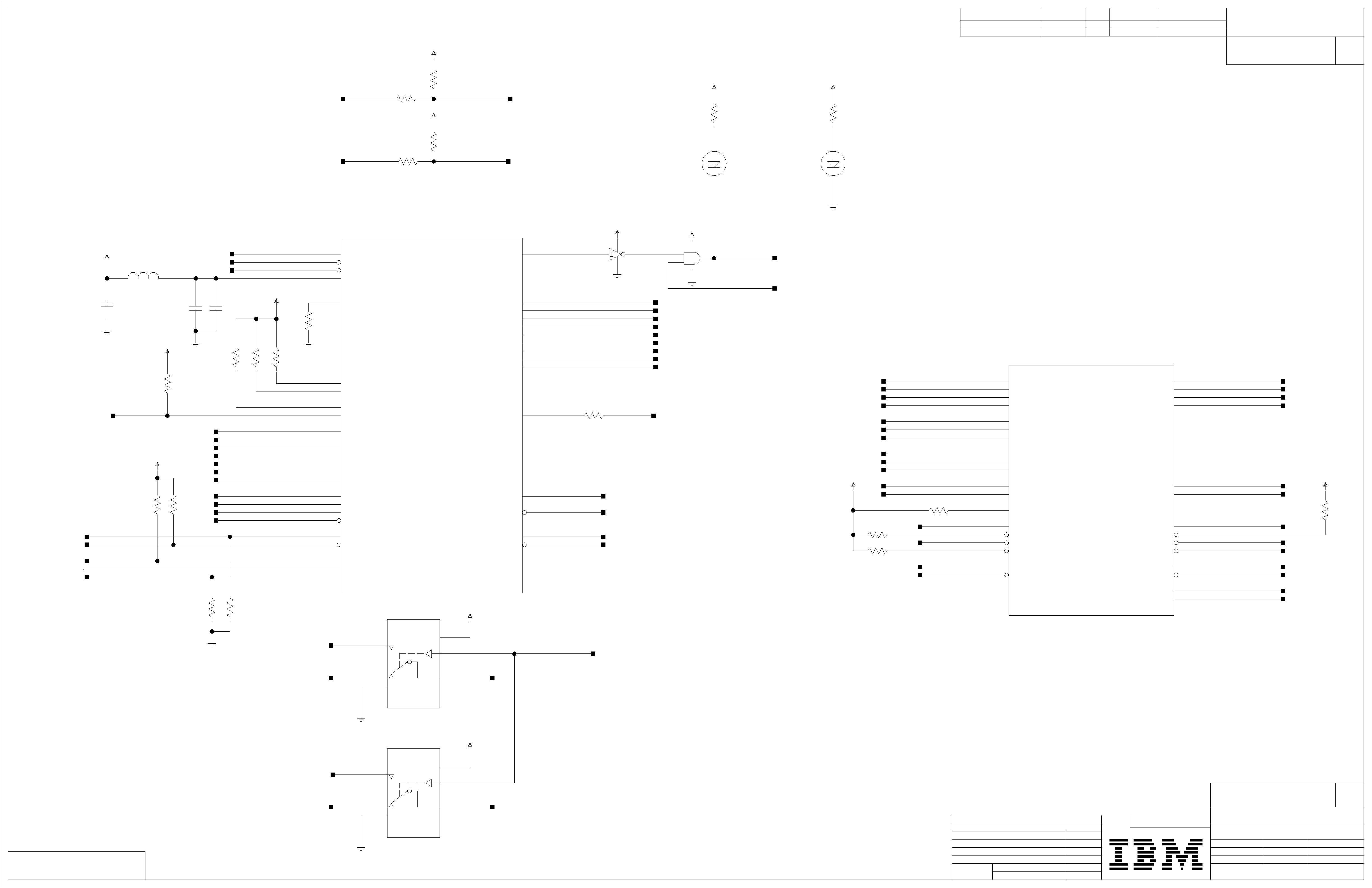

4. 405GP INTERFACE TO SDRAM & PCI

D

5. PPC405 MISC

6. 405GP PWR/GND & JTAG

7. 405GP BOOTSTRAP

D

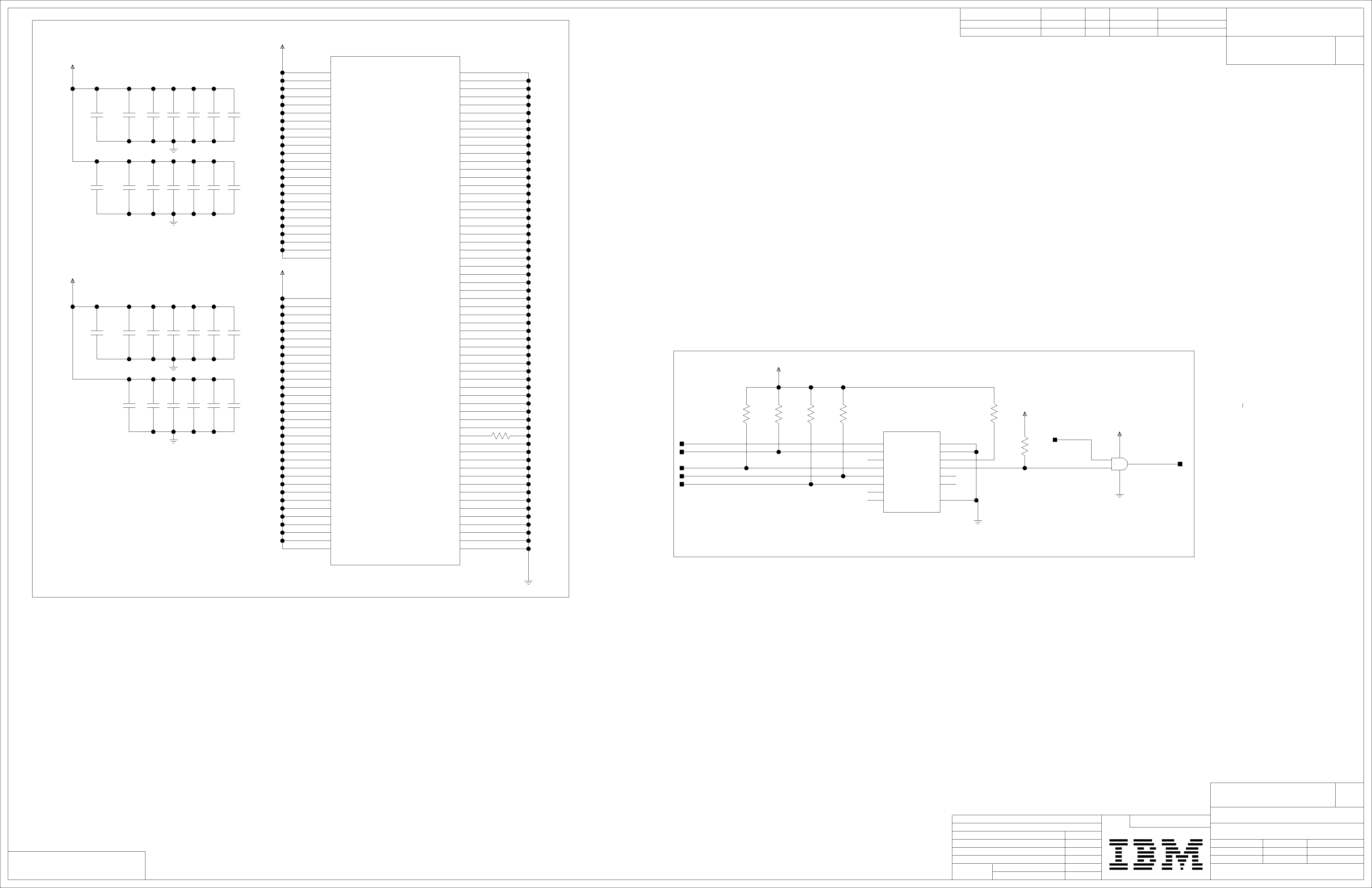

8. 405GP SDRAM

E

E

9. 405GP PERIPHERAL BUS

10. FLASH / RTC

11. CLOCK OSCILLATOR & DRIVER

12. UART

F

F

13. RS485 DRIVERS

14. I2C SEEPROM AND SWITCHES

15. ETHERNET PHY

16. USB & SMP CONNECTOR

G

G

17. VIDEO COMPRESSOR

18. SDRAM 1MX16X4b

19. POWER

20. SPARE PARTS

H

H

Raptor's Intelligence

I

PART NO.

TITLE

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

7-16-2003_12:14

DESIGNER

CHECKED

APPROVED

73P9300

HARRIER

SHEET OF

1

108754321

Physical Design

Jeff Davis

Brandon EllisonJames Dalton

20

I

JJ

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

DEVELOPMENT NO. Q/M

A

Change Log:

04/01/02 - BJE - (Page 4) Added MEM_ADD Bus net.

04/01/02 - BJE - (Page 4) Synched with final Pass 1 of Management Module.

B

C

04/01/02 - BJE - (Page5) Renamed IRQ pins to IRQ to prevent confusion.

04/01/02 - BJE - (Page 5) Synched with final Pass 1 of Management Module.

04/01/02 - BJE - (Page 6) Synched with final Pass 1 of Management Module.

04/01/02 - BJE - (Page 7) Synched with final Pass 1 of Management Module.

04/01/02 - BJE - (Page 7) Changed all resistors to correct values, 3.3k PU, 1k PD.

04/01/02 - BJE - (Page 7) Changed EPB Speed from 25 MHz to 50 MHz

04/01/02 - BJE - (Page 8) Synched with final Pass 1 of Management Module.

04/01/02 - BJE - (Page 9) Synched with final Pass 1 of Management Module.

04/01/02 - BJE - (Page 10) Synched with final Pass 1 of Management Module.

04/01/02 - BJE - (Page 11) Synched with final Pass 1 of Management Module.

Pass 5 Changes

01/15/03 - JWD - added pull-up to R485_A_RTS_N

04/15/03 - JRK - changed U1 to IBM p/n 0798764

04/15/03 - JRK - changed U5, U6 to IBM p/n 77P0048

Pass 5B Changes - 73P9283

6/16/03-RMK-(Page 16) Changed J25 molex part number to 500599-1409 from 53467-1409 for gold plated pins

6/16/03 - RMK - (Page 9) Changed R16 from 3.3k to 10k, do not need a strong pull up

6/16/03 - RMK - (Page 9) Made R62 NOPOP to match what was done on Condor

6/16/03 - RMK - (Page 9) Made R77 NOPOP because CABLE_DETECT# is already pulled up through R544 on page 16

B

C

04/01/02 - BJE - (Page 11) New Clock chip to be entered by James Dalton

04/01/02 - BJE - (Page 12) Synched with final Pass 1 of Management Module.

04/01/02 - BJE - (Page 12) Adjusted a few cap values.

04/01/02 - BJE - (Page 12) Swapped pop options on R21 & R20.

04/01/02 - BJE - (Page 13) Synched with final Pass 1 of Management Module.

D

E

04/02/02 - JWD - (Page 16) Added values for R 528,529,530,531.

04/03/02 - BJE - (Page 5) Condor 2000 Connections on GPIO

04/03/02 - BJE - (Page 9) Condor 2000 Connections on some GPIOs

04/03/02 - BJE - (Page 15) Added Condor 2000 Connections

04/06/02 - JWD -Fixed address bit order

04/07/02 - JWD - (Page 15) Added system on detection

4/8/02 - JWD - (page 18) Removed 1.8V (not required)

04/08/02 - JWD - (Page 15) Moved differential signals around on the SMP connectors

04/11/02 - BJE - (Page 12) Added all COM signals for Modem use.

04/11/02 - BJE - (Page 12) Moved Debug Port to COM1

04/11/02 - BJE - (Page 5) Added SPI Bus to IRQ lines

04/11/02 - BJE - (Page 12) Added BERG header for 485/232 selection

06/18/03 - RMK - Changed U5 and U6 IBM part numbers to 77P0448

Pass 5C Changes - 73P9300

07/15/03-JAD-(Page 16) Changed J25 IBM part number to 23K8778 from 89G3894 to match the correct molex part number

07/15/03-JAD-(Page 16) Changed C521 from NOPOP to POP to fix Cypress reset bug, where bogus USB device shows up on initial power up

*Note: Since the PCB was not changed these chages were

released as pass 5B & 5C as a BOM change only to avoid confusion

D

E

04/11/02 - BJE - (Page 16) Added SPI bus option to Xilinx bus

04/11/02 - BJE - (Page 12) Changed Enable line of 232 Part to GND

Pass 2 Changes

F

06/13/02 - JWD - (Page 15) Removed Inverter from input pin 9 on U75

06/13/02 - JWD - (Page 15) Fixed reflected serial EPROM (U8)

06/13/02 - JWD - (Page 6) Changed U1 to powered symbol

07/26/02 - JWD - Changed DRAM to single chip for cost reduction

07/31/02 - JWD - (Page 15) Changed SMP to single connector

F

Pass 3 Changes

9/23/02 - JWD -Changed RTC data and clk pull-downs to pull-ups. Nopoped CE pull-down.

G

09/23/02 - JWD - (Page 15) Added USB switches.

09/23/02 - RMK - (Page 15) Added pull-up to USB_HUB_INT

9/23/02 RMK Changed micron part number to the full part number

G

9/23/02 RMK - Changed vendor part number of U83 DRAM

09/23/02 - RMK - (Page 16) Added ibm part number (77P0174) to xilinx XC2S150

Pass 4 Changes

10/31/02 -JWD- (Page 4) Using PCI_RESET# for manufacturing test of insane LED

10/31/02 - JWD - (Page 5) Changed signal name from GPIO18 to RS232_DETECT

H

I

10/31/02 - RMK - (Page 5) Changed RTC_INT_N to RTC_DUART_INT_N (sharing Interrupt pin)

10/31/02 - RMK - (Page 9) P_CS1# is now used for USB / DUART with ROM_ADDR12 qualifying

10/31/02 - RMK - (Page 10) Changed RTC Interupt to TIRQ_N

10/31/02 - RMK - Changed flash IBM part number to 02R1640, added coded part number 02R1641, removed socket

10/31/02 - JWD - (Page 11) Added 23.5 MHz frequency for the duart to the clock driver

10/31/02 - RMK - (Page 12) Made new page 12 with DUART circuitry

10/31/02 - RMK - (Page 14) Added nopop resistors between D and S1 on U94 and U95 to test if the switches are needed

10/31/02 - RMK - (Page 16) Made USB_CS# from logical and of P_CS1# and ROM_ADDR12

10/31/02 - JWD - (Page 16) Added com4, changed name of GPIO18 to RS232_DETECT

10-30-02-JWD-P_EXT_ACK# is used to detect BIST mode after reset.

10/31/02 - RMK - Added IBM part number for RTC (77P0248)

10/31/02 - RMK - Added IBM part number for DIALIGHT LED CR2 (26P0055)

10/31/02 - RMK - Added IBM part number for DIALIGHT LED CR3 (29L2476)

10/31/02 - RMK - Added IBM part number for TI multiplexer u96 (77P0242)

H

I

CHANGE LOG

10/31/02 - RMK - Added IBM part number for Cypress clock driver (77P0247)

10/31/02 - RMK - Added IBM part number for ST switches (77P0242)

PART NO.

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

73P9300

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

HARRIER

7-16-2003_12:08

SHEET OF

2

Physical Design

Jeff Davis

Brandon EllisonJames Dalton

JJ

20

108754321

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

DEVELOPMENT NO. Q/M

A

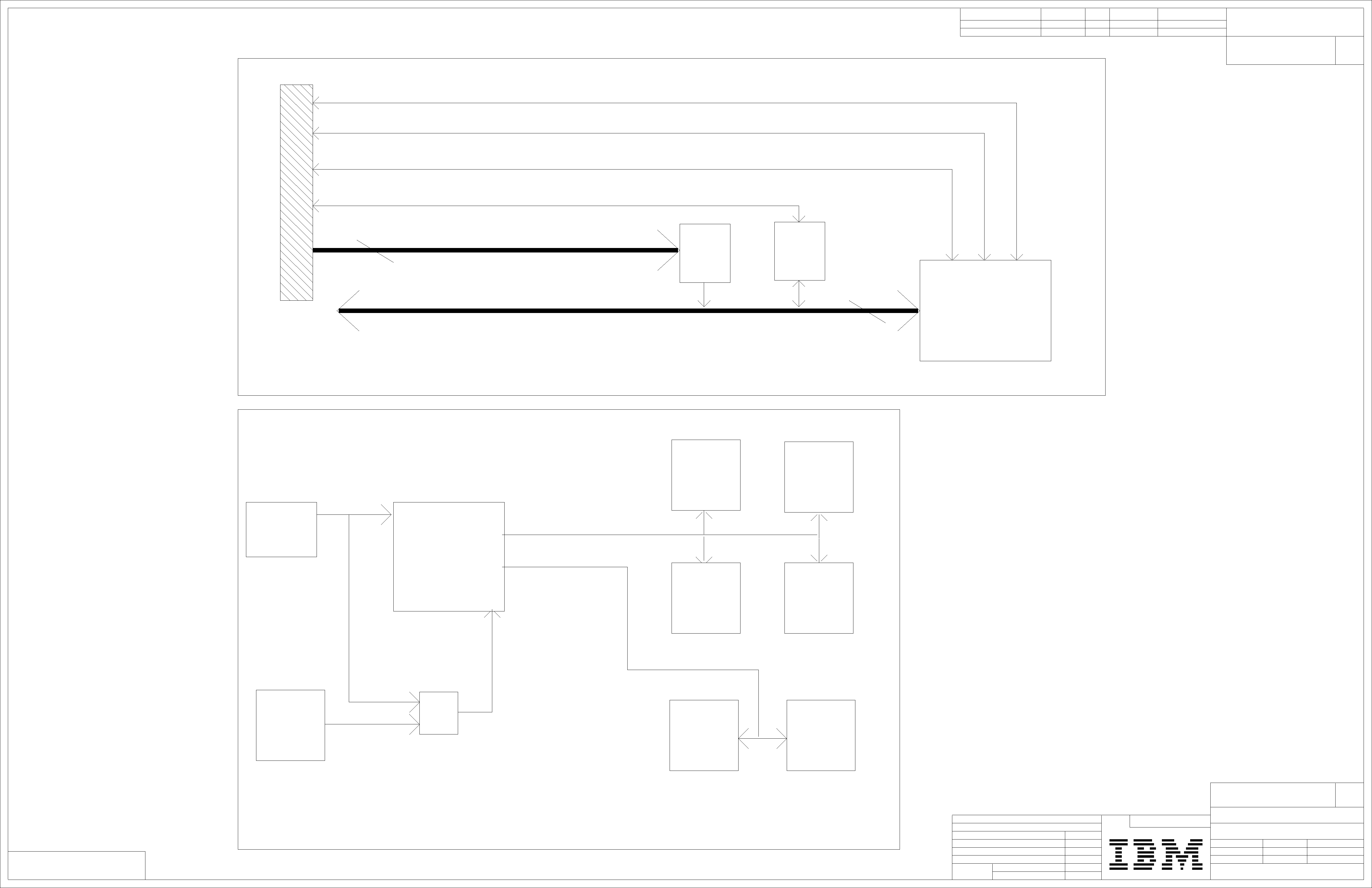

I2C/SMBus

B

SMP

Ethernet

RS485/RS232

B

USB

C

C

28.6 MHz

FPGA

16

USB

50 MHz

D

CPU

32

D

E

E

USBFPGA

F

PPC_RESET_N

SYSTEM

MAX6315

CPU

PERIPHERAL_RESET_N

PPC_NOT_READY_N

F

G

G

I2C

JTAG

DUART

HOST ID

H

TRST_N

JTAG

OR

JTAG_RST_N

H

FLASH

I

ETHERNET

I

Harrier Block Diagram

PART NO.

73P9300

RESET

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

HARRIER

7-16-2003_12:08

SHEET OF

3

Brandon EllisonJames Dalton

JJ

20

108754321

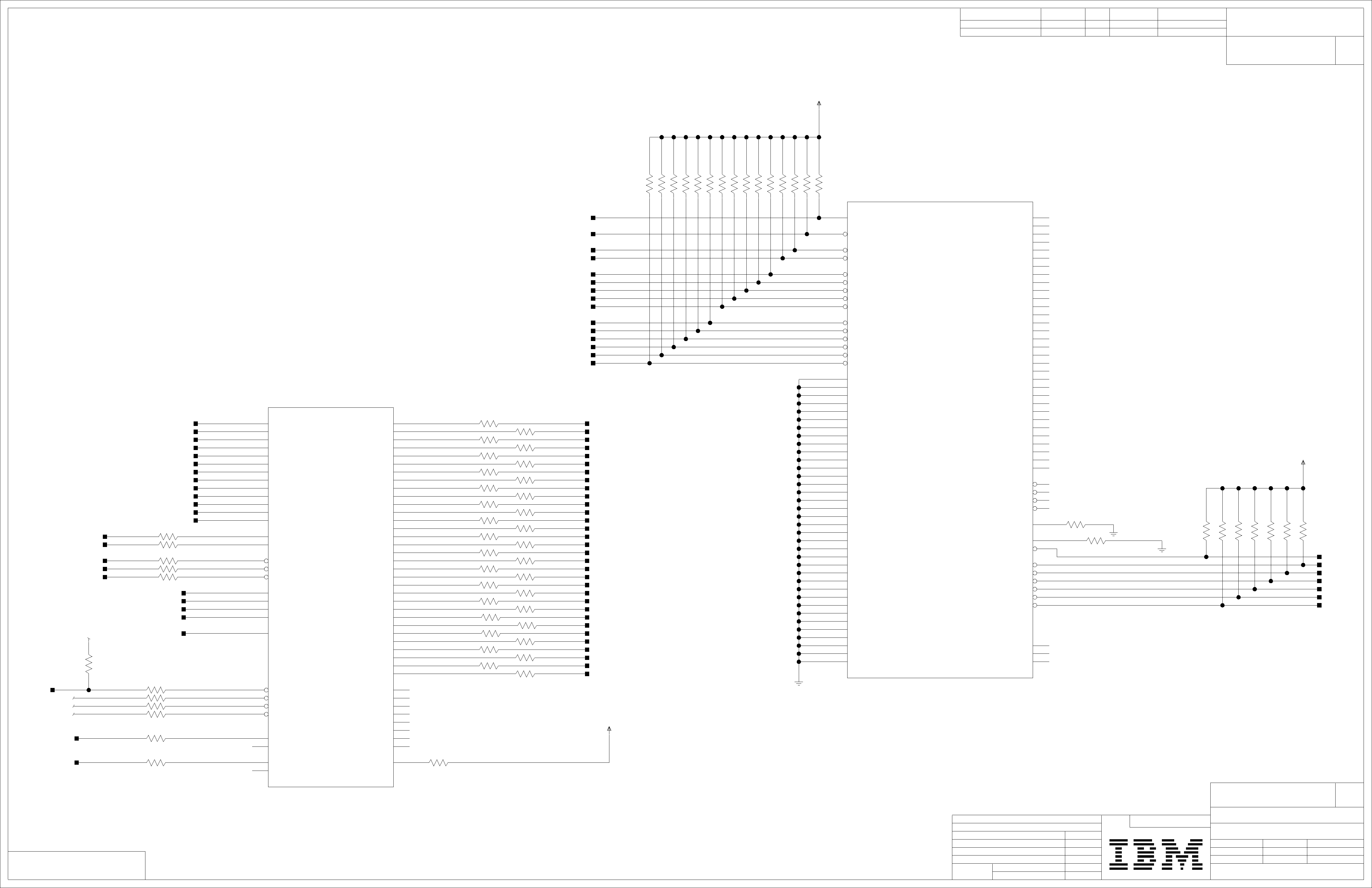

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

04/01/02 - BJE - (Page 4) Added MEM_ADD Bus net.

04/01/02 - BJE - (Page 4) Synched with final Pass 1 of Management Module.

04/11/02 - JWD - (Page 4) deleted PCIADR's

10/31/02 -JWD- (Page 4) Using PCI_RESET# for manufacturing test of insane LED

3.3VC

B

R552

R553

R554

8.2K

R555

8.2K

R556

8.2K

R557

8.2K

R558

8.2K

R559

8.2K

R560

8.2K

R561

8.2K

R562

8.2K

R563

8.2K

R564

8.2K

R565

8.2K

R566

8.2K

8.2K

8.2K

U53

DEVELOPMENT NO. Q/M

A

B

PCI_PAR

C

PCI_FRAME#

PCI_IRDY#

PCI_TRDY#

PCI_STOP#

PCI_DEVSEL#

PCI_SERR#

PCI_PERR#

D

E

PPC405GP-3BE200C

8 MEM_ADD0

8

8

8

8

8

8

8

F

8

8

8

8

G

DQM Lines swapped to match Data Lines

R110

H

MEM_CS0#

8

8

I

8

8

3.3K

NOPOP

MEM_CS1#

MEM_CS2#

MEM_CS3#

MEM_CLKEN0

MEM_CLK0

MEM_BA0

MEM_BA1

MEM_RAS#

MEM_CAS#

MEM_WE#

Up to 4 banks possible - Only using 1

NOPOP resistors to allow for hot wiring later if needed.

NOPOP

NOPOP

NOPOP

R98

R97

R95

R91

R55

R99

R104

R105

R106

R102

R103

8

8

8

22

22

22

22

22

8

8

8

8

22

RES_MEM_BSEL0#

22

RES_MEM_BSEL1#

22

RES_MEM_BSEL2#

22

RES_MEM_BSEL3#

22

22

MEM_ADD1

MEM_ADD2

MEM_ADD3

MEM_ADD4

MEM_ADD5

MEM_ADD6

MEM_ADD7

MEM_ADD8

MEM_ADD9

MEM_ADD10

MEM_ADD11

MEM_ADD12

RES_MEM_BA0

RES_MEM_BA1

RES_MEM_RAS#

RES_MEM_CAS#

RES_MEM_WE#

MEM_DQM3

MEM_DQM2

MEM_DQM1

MEM_DQM0

MEM_DQM_CB

RES_MEM_CLKEN0

RES_MEM_CLK0

AE22

AC21

AE21

AD21

AF22

AE20

AC19

AE19

AD19

AC18

AF19

AD18

AC17

AB24

AC24

AF24

AB23

AC16

AC12

AC10

AC6

AA3

AC15

AD17

AF17

AE15

AC14

AB25

AC25

AC26

AA23

M_ADDR0

M_ADDR1

M_ADDR2

M_ADDR3

M_ADDR4

M_ADDR5

M_ADDR6

M_ADDR7

M_ADDR8

M_ADDR9

M_ADDR10

M_ADDR11

M_ADDR12

M_BA0

M_BA1

M_RAS_N

M_CAS_N

M_WE_N

M_DQM0

M_DQM1

M_DQM2

M_DQM3

M_DQM_CB

M_BANKSEL0_N

M_BANKSEL1_N

M_BANKSEL2_N

M_BANKSEL3_N

M_CLKEN0

M_CLKEN1

M_CLKOUT0

M_CLKOUT1

U53

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_ECC0

M_ECC1

M_ECC2

M_ECC3

M_ECC4

M_ECC5

M_ECC6

M_ECC7

M_CLK_IN

AC13

AE12

AD11

AC11

AF10

AE11

AD10

AF9

AD9

AE9

AD8

AF7

AC8

AD7

AE6

AE5

AE4

AD5

AD4

AC5

AD1

AB2

AA4

AA2

AB1

Y2

W4

W2

W3

V4

W1

V3

AE14

AF15

AF14

AD13

AF13

AF12

AE13

AD12

AF4

RN14

1 8

RES_MEM_DATA30 MEM_DATA30

RES_MEM_DATA29

RES_MEM_DATA28

RES_MEM_DATA27

RES_MEM_DATA26

RES_MEM_DATA25

RES_MEM_DATA24

RES_MEM_DATA23

RES_MEM_DATA22

RES_MEM_DATA20

RES_MEM_DATA18

RES_MEM_DATA16 MEM_DATA16

RES_MEM_DATA14

RES_MEM_DATA12

RES_MEM_DATA10

RES_MEM_DATA8

RES_MEM_DATA7

RES_MEM_DATA6

RES_MEM_DATA5

RES_MEM_DATA4

RES_MEM_DATA3

RES_MEM_DATA2

RES_MEM_DATA1

RES_MEM_DATA0

R365

10K

RN14

3 6

RN21

1 8

RN21

3 6

RN15

1 8

RN15

3 6

RN20

1 8

RN20

3 6

RN16

1 8

RN16

3 6

RN19

1 8

RN19

3 6

RN17

1 8

RN17

3 6

RN18

1 8

RN18

3 6

22RES_MEM_DATA31

2 7

22

4 5

22

2 7

22

4 5

22

2 7

22RES_MEM_DATA21

4 5

22RES_MEM_DATA19

2 7

22RES_MEM_DATA17

4 5

22RES_MEM_DATA15

2 7

22RES_MEM_DATA13

4 5

22RES_MEM_DATA11

2 7

22RES_MEM_DATA9

4 5

22

2 7

22

4 5

22

2 7

22

4 5

RN14

RN14

RN21

RN21

RN15

RN15

RN20

RN20

RN16

RN16

RN19

RN19

RN17

RN18

RN18

Using PCI_RESET# for manufacturing test of insane LED

MEM_DATA31

22

MEM_DATA29

22

MEM_DATA28

MEM_DATA27

22

MEM_DATA26

MEM_DATA25

22

MEM_DATA24

MEM_DATA23

22

MEM_DATA22

MEM_DATA21

22

MEM_DATA20

MEM_DATA19

22

MEM_DATA18

MEM_DATA17

22

MEM_DATA15

22

MEM_DATA14

MEM_DATA13

22

MEM_DATA12

MEM_DATA11

22

MEM_DATA10

MEM_DATA9

22

MEM_DATA8

RN17

MEM_DATA7

22

MEM_DATA6

MEM_DATA5

22

MEM_DATA4

MEM_DATA3

22

MEM_DATA2

MEM_DATA1

MEM_DATA0

22

5

PCI_RESET#

PCI_GNT0#

PCI_GNT1#

PCI_GNT2#

PCI_GNT3#

PCI_GNT4#

PCI_GNT5#

PCI_GNT0# when Internal Arbiter is Used

PCI_REQ# when using External Arbiter

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

3.3VC

E26

J24

J23

G26

H23

H25

G24

G25

B24

U23

T23

F23

H26

N23

M24

L11

L12

L13

L14

L15

L16

M11

M12

M13

M14

M15

M16

N11

N12

N13

N14

N15

N16

P11

P12

P13

P14

P15

P16

R11

R12

R13

R14

R15

R16

T11

T12

T13

T14

T15

T16

PCI_PAR

PCI_FRAME_N

PCI_IRDY_N

PCI_TRDY_N

PCI_STOP_N

PCI_DEVSEL_N

PCI_SERR_N

PCI_PERR_N

PCI_RESET_N

PCI_GNT0_REQ_N

PCI_GNT1_N

PCI_GNT2_N

PCI_GNT3_N

PCI_GNT4_N

PCI_GNT5_N

HS_RTN1

HS_RTN2

HS_RTN3

HS_RTN4

HS_RTN5

HS_RTN6

HS_RTN7

HS_RTN8

HS_RTN9

HS_RTN10

HS_RTN11

HS_RTN12

HS_RTN13

HS_RTN14

HS_RTN15

HS_RTN16

HS_RTN17

HS_RTN18

HS_RTN19

HS_RTN20

HS_RTN21

HS_RTN22

HS_RTN23

HS_RTN24

HS_RTN25

HS_RTN26

HS_RTN27

HS_RTN28

HS_RTN29

HS_RTN30

HS_RTN31

HS_RTN32

HS_RTN33

HS_RTN34

HS_RTN35

HS_RTN36

PPC405GP-3BE200C

PCI_AD0

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD30

PCI_AD31

PCI_C_BE0_N

PCI_C_BE1_N

PCI_C_BE2_N

PCI_C_BE3_N

PCI_IDSEL

PCI_CLK

P_WE_PCI_INT_N

PCI_REQ0_GNT_N

PCI_REQ1_N

PCI_REQ2_N

PCI_REQ3_N

PCI_REQ4_N

PCI_REQ5_N

SPARE_D20

SPARE_Y23

SPARE_Y26

405GP INTERFACE TO SDRAM & PCI

A17

B16

C17

A18

D17

C18

B18

A20

B21

A23

D21

B22

B23

C22

C26

F25

K26

L23

M25

M23

N25

M26

N26

P24

R24

R23

P23

R25

T24

U26

T25

V26

D19

F24

K24

R26

P26

B20

C23

C19

C21

B19

A24

G23

J25

D20

Y23

Y26

R373

5.1K

PCI_REQ0#

PCI_REQ1#

PCI_REQ2#

PCI_REQ3#

PCI_REQ4#

PCI_REQ5#

From Walnut

R366

10K

P_WE#

PCI_REQ0# when Internal Arbiter is Used

PCI_GNT# when using External Arbiter

Asynch Mode Use

R94

R579

8.2K

R587

8.2K

R586

8.2K

R585

8.2K

R584

8.2K

R92

8.2K

C

D

E

3.3VC

F

8.2K

16,17

G

H

I

Listed as Reserved in Datasheet

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

PART NO.

73P9300

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

HARRIER

7-16-2003_12:15

SHEET OF

4

Physical Design

Jeff Davis

Brandon EllisonJames Dalton

JJ

20

108754321

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

HOST_PWR#

5

B

HOST_RST#

5

R594

0

R595

0

R597

R551

3.3VC

3.3VC

1MEG

HOST_PWR_REQ#

1MEG

HOST_PWRGD/RST#

16

Consider bi-directional buffers for next pass.

16

R610

10 mA

330

2CR2

+

VEN_P/D_NUM=597-2401-213

VENDOR=DIALIGHT

COLOR=YELLOW

1

-

R611

10 mA

3.3VC3.3VC

330

2CR3

+

VEN_P/D_NUM=597-2301-213

VENDOR=DIALIGHT

COLOR=GREEN

1

PowerInsane

-

04/01/02 - BJE - (Page5) Renamed IRQ pins to IRQ to prevent confusion.

04/01/02 - BJE - (Page 5) Synched with final Pass 1 of Management Module.

04/03/02 - BJE - (Page 5) Condor 2000 Connections on GPIO

04/11/02 - BJE - (Page 5) Added SPI Bus to IRQ lines

08/16/02 - JWD - (Page 5) Added I2C_SELECT to GPIO6

08/16/02 - JWD - (Page 5) Added power and insane LED's

10/31/02 - JWD - (Page 5) Changed signal name from GPIO18 to RS232_DETECT

10/31/02 - RMK - (Page 5) Changed RTC_INT_N to RTC_DUART_INT_N (sharing Interrupt pin)

DEVELOPMENT NO. Q/M

A

B

C

U53

PULLUP to 2.5V for PLL

2_5V

BLM31A700S

L43

FERRITE

C523

D

E

F

G

Internal Timer Input

Not currently used.

Peripheral Bus Controls

NEEDED?

100N

SYS_TIMER_CLK

R90

P_HOLD_REQ

P_EXT_REQ#

P_HOLD_PRIORITY

P_BUS_REQ

P_ERROR

3.3VC

R522

3.3VC

R578

3.3K

3.3K

3.3K

C522

C534

100N

16

5

16

12

R87

11 33MHZ_405GP

6,10

10U

R520

16

5

16

6

6

6

6

R88

1K

PPC_RESET_N

RISCWATCH_HALT#

6

R518

USB_HUB_INT

HOST_RST#

HOST_PCI_RST_N

SER_CLK

USB_LATCH_EMPTY

RS232_DETECT

RTC_DUART_INT_N

JTAG_TDI

JTAG_TMS

JTAG_TCK

JTAG_RST_N

1K

3.3K

R519

3.3K

3.3VC

R521

3.3K

3.3K

A25

D22

AB26

D25

D26

C25

E23

E24

D24

AA24

Y25

Y24

W25

W24

V23

V25

AE24

AC22

AD22

AE26

V1

Y4

T2

R3

B1

SYS_CLOCK

SYS_RESET_N

SYS_HALT_N

SYS_PLL_VDDA

CE0_TEST

DI1

Symbol is wrong on these three pins

DI2

DI1 DI2 RI - All test pins - No biggie.

RI

SYS_TIMER_CLK

IRQ6

GPIO23

IRQ5

GPIO22

IRQ4

GPIO21

IRQ3

GPIO20

IRQ2

GPIO19

IRQ1

GPIO18

IRQ0

GPIO17

JTAG_TDI

JTAG_TMS

JTAG_TCK

JTAG_TRST_N

P_HOLD_REQ

P_EXT_REQ_N

P_HOLD_PRIORITY

P_BUS_REQ

P_ERROR

U88

PPC405GP-3BE200C

SYS_ERROR

JTAG_TDO

P_EXT_RESET_N

P_HOLD_ACK

P_EXT_ACK_N

3.3VC

GPIO9

GPIO8

GPIO7

GPIO6

GPIO5

GPIO4

GPIO3

GPIO2

GPIO1

P_CLK

AD25

AB3

AC7

AF5

AE8

AC9

AF18

A22

C20

D18

E4

AD23

T3

U2

Y3

ERROR_LED

FPGA = 0, RTC = 1

All GPIO's are high impedance while in reset. refer to 405gp user manual sec 23.5.1

JTAG_TDO

PPC_NOT_READY_N

Output reset to external devices.

P_HOLD_ACK

P_EXT_ACK#

Strapping Pins

PERIPHERAL_RESET_N

U75

HOST_PWR#

X_DONE

I2C_SELECT

R649

49.9

Place close to 405GP

3.3VC

14

7

SER_DATA

FPGA_RTC

X_INIT

X_PROG

GPIO1

6

10,15

7

7,16

ERROR_LED#

43

PERCLK

3.3VC

U1

14

12

13

LVC08_TSSOP14_65MM

5

17

5

14

12,14,16,17

5,7,10

17

7,17

7,16

17

11

7

ERROR_LED_BUF

PCI_reset is being used as a GPIO

PCI_RESET#

16

4

3.3VC

R647

R646

15

15

15

15

15

15

15

15

15

15

15

15

ENET_PHY_RXD3

ENET_PHY_RXD2

ENET_PHY_RXD1

ENET_PHY_RXD0

ENET_PHY_RX_ERR

ENET_PHY_RX_CLK

ENET_PHY_RX_DV

ENET_PHY_CRS

ENET_PHY_TX_CLK

ENET_PHY_COL

ENET_PHY_MDC

ENET_PHY_MDIO

4.7K

4.7K

12 COM1_RX

12 COM1_CTS#

13 COM2_RX

13

UART_DSR_N = UART1_DSR_N

COM2 - DSR = CTS RTS = DTR

R517

3.3K

COM1_DCD#

COM1_RI#

UART_RX = UART1_RX

SERCLK

COM2_CTS#

U53

PPC405GP-3BE200C

AD20

AC20

AF23

AE23

U24

AF20

V24

W23

E25

AA25

H24

AD26

AE17

AE16

AE18

AB4

AD15

AC1

AC3 AD2

EMC_PHY_RXD3

EMC_PHY_RXD2

EMC_PHY_RXD1

EMC_PHY_RXD0

EMC_PHY_RX_ER

EMC_PHY_RX_CLK

EMC_PHY_RX_DV

EMC_PHY_CRS

EMC_PHY_TX_CLK

EMC_PHY_COL

EMC_MDC

EMC_MDIO

UART_SERCLK

UART0_RX

UART0_DCD_N

UART0_CTS_N

UART0_RI_N

UART_RX

UART_DSR_N UART1_DTR_N

EMC_TXD3

EMC_TXD2

EMC_TXD1

EMC_TXD0

EMC_TX_ER

EMC_TX_EN

UART0_TX

UART0_DSR_N

UART0_DTR_N

UART0_RTS_N

UART1_TX

IIC_SCL

IIC_SDA

P25

L24

L25

J26

K25

K23

AF3

AE3

AF2

AD16

AC2

AD6

AE7

Strapping Pins

ENET_PHY_TX_EN

Strapping Pins

COM1_TX

COM1_DSR#

COM1_DTR#

COM1_RTS#

COM2_TX

COM2_RTS#

I2C_SCL

I2C_SDA

7,15ENET_PHY_TXD3

7,15ENET_PHY_TXD2

7,15ENET_PHY_TXD1

7,15ENET_PHY_TXD0

7,15ENET_PHY_TX_ERR

7,15

7,12

7

7,12

7,13

7,13

14

14

3.3VC

4.7K

R648

C

D

E

F

G

VCC

5

10

H

17

I

10

CLK

X_CCLK

DIO

S1ININ = 1

1

6

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

U87

S1ININ = 1

1

4

VCC

5

6

FPGA_RTC

5,7,10

FPGA = 0, RTC = 1

H

D

SER_CLK 5

3.3VC

I

PPC405 MISC

PART NO.

17

X_DOUT 5SER_DATA

S2

3

IN = 0

2

GND

VENDOR=ST_MICRO

VEN_P/D_NUM=STG3157CTR

D

4

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

73P9300

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

HARRIER

7-16-2003_12:15

James Dalton

SHEET OF

5

Physical Design

Jeff Davis

Brandon Ellison

JJ

20

108754321

405GP POWER

REL

961 2 3 4 5 7 8 10

EC NO.DATEQTYREL FOR ASM

PART NO.

A

2_5V

B

C

3.3VC

D

E

F

Place one set of THREE (100nF, 10nF, 2.2nF)

per side within 25mils of 405GP

Place 10uF within 100mils of 405GP

C7

10U

C8

10U

Place one set of THREE (100nF, 10nF, 2.2nF)

per side within 25mils of 405GP

Place 10uF within 100mils of 405GP

C9

10U

C59

C61

C66

C69

100N

100N

100N

100N

C60

C62

C65

C68

C328

100N

C330

100N

C332

100N

C334

100N

C329

10N

C331

10N

C333

10N

C335

10N

10N

C494

10N

10N

C496

10N

C63

C64

C72

2.2N

C495

2.2N

C67

2.2N

C497

2.2N

2.2N

2.2N

2.2N

2.2N

2_5V

3.3VC

AB10

AB11

AB12

AB15

AB16

AB17

E10

E11

E12

E15

E16

E17

K22

K5

L22

L5

M22

M5

R22

R5

T22

T5

U22

U5

AA5

F5

G5

H5

W5

Y5

AB19

AB20

AB21

AB6

AB7

AB8

AA22

F22

G22

H22

W22

Y22

E19

E20

E21

E6

E7

E8

K2

P3

AE10

AD14

U25

N24

B17

C13

P2_5V_AB10

P2_5V_AB11

P2_5V_AB12

P2_5V_AB15

P2_5V_AB16

P2_5V_AB17

P2_5V_E10

P2_5V_E11

P2_5V_E12

P2_5V_E15

P2_5V_E16

P2_5V_E17

P2_5V_K22

P2_5V_K5

P2_5V_L22

P2_5V_L5

P2_5V_M22

P2_5V_M5

P2_5V_R22

P2_5V_R5

P2_5V_T22

P2_5V_T5

P2_5V_U22

P2_5V_U5

P3_3V_AA5

P3_3V_F5

P3_3V_G5

P3_3V_H5

P3_3V_W5

P3_3V_Y5

P3_3V_AB19

P3_3V_AB20

P3_3V_AB21

P3_3V_AB6

P3_3V_AB7

P3_3V_AB8

P3_3V_AA22

P3_3V_F22

P3_3V_G22

P3_3V_H22

P3_3V_W22

P3_3V_Y22

P3_3V_E19

P3_3V_E20

P3_3V_E21

P3_3V_E6

P3_3V_E7

P3_3V_E8

P3_3V_K2

P3_3V_P3

P3_3V_AE10

P3_3V_AD14

P3_3V_U25

P3_3V_N24

P3_3V_B17

P3_3V_C13

U53

PPC405GP-3BE200C

GND_A1

GND_AE1

GND_AF1

GND_A2

GND_B2

GND_AE2

GND_C3

GND_AD3

GND_D4

GND_A11

GND_A16

GND_A21

GND_AC4

GND_E5

GND_A6

GND_J5

GND_AA1

GND_P5

GND_AA26

GND_V5

GND_AB14

GND_AB5

GND_AB18

GND_AB22

GND_AF11

GND_E9

GND_AB9

GND_AF16

GND_AF21

GND_E13

GND_AB13

GND_AF25

GND_AF6

GND_E14

GND_E18

GND_E22

GND_F1

GND_F26

GND_L1

GND_L26

GND_N22

GND_N5

GND_T1

GND_T26

GND_J22

GND_H1

GND_P22

GND_AF8

GND_V22

GND_W26

GND_D23

GND_A19

GND_AC23

GND_C24

GND_AD24

GND_B25

GND_AE25

GND_AF26

GND_A26

GND_B26

A1

AE1

AF1

A2

B2

AE2

C3

AD3

D4

A11

A16

A21

AC4

E5

A6

J5

AA1

P5

AA26

V5

AB14

AB5

AB18

AB22

AF11

E9

AB9

AF16

AF21

E13

AB13

AF25

AF6

E14

E18

E22

F1

F26

L1

L26

N22

N5

T1

T26

J22

H1

P22

AF8

V22

W26

D23

A19

AC23

C24

AD24

B25

AE25

AF26

A26

B26

04/01/02 - BJE - (Page 6) Synched with final Pass 1 of Management Module.

04/10/02 - JWD - (Page 6) Moved LED's to CROW.

08/15/02 - JWD - (Page 6) Changed C7,C8,C9 to 10uF ceramic

3.3VC

R583

10K

0

R628

JTAG_TDO

5

JTAG_TDI

5

JTAG_TCK

5

JTAG_TMS

5

RISCWATCH_HALT#

5

R582

10K

R581

10K

R580

10K

NC

NC

NC

1

9

13

NOPOP

J5

C1

C9

C13

CONN2x8HDR_KEY

42F6867

79282-516

C10

C12C11

KEY

C16C15

C2

C4C3

C6C5

C8C7

2

43

65

87

10

1211

1615

NC

NC

R226

1K

R117

10K

3.3VC

PPC_RESET_N

5,10

DEBUG PORT405 RISCWatch and JTAG

TRST_N

3.3VC

U1

14

1

2

LVC08_TSSOP14_65MM

3

7

JTAG_RST_N

5

DEVELOPMENT NO. Q/M

A

B

C

D

E

F

G

H

G

H

I

I

405GP PWR/GND & JTAG

PART NO.

73P9300

MUST CONFORM TO ENG

SPEC: 80X2324

TOLERANCE UNLESS NOTED

LINEAR

ANGLES

RADII UNLESS NOTED

EDGE/

CORNER

6 9

OUTSIDE MAX

INSIDE MAX

0.13

2.0

TITLE

1/1SCALE:

DESIGNER

CHECKED

APPROVED

HARRIER

7-16-2003_12:15

SHEET OF

6

108754321

Physical Design

Jeff Davis

Brandon EllisonJames Dalton

20

JJ

Loading...

Loading...