Page 1

5

4

3

2

1

2008 06/11

MSI

D D

Table of Contents

C C

B B

A A

MS-91C1 REV 0A

TYLERSBURG 36D + ICH10R Schematics

Page

01

02

03

04

05

06

07

08~11

12~15

16~21

22~27

28

29

30

31

32

33

34

35

36

37

38 CLK_BUFFER

41

42

45

46

47

48

49 CPU0_VTT_POWER

50

51

52

53

54

55

56

57

58

59

60~64

65

66

67

68

5

Title

Cover / Table of SPEC

Block_Diagram

POWER_MAP

Power Sequence

CLK_MAP

SMBUS_MAP

RESET_MAP

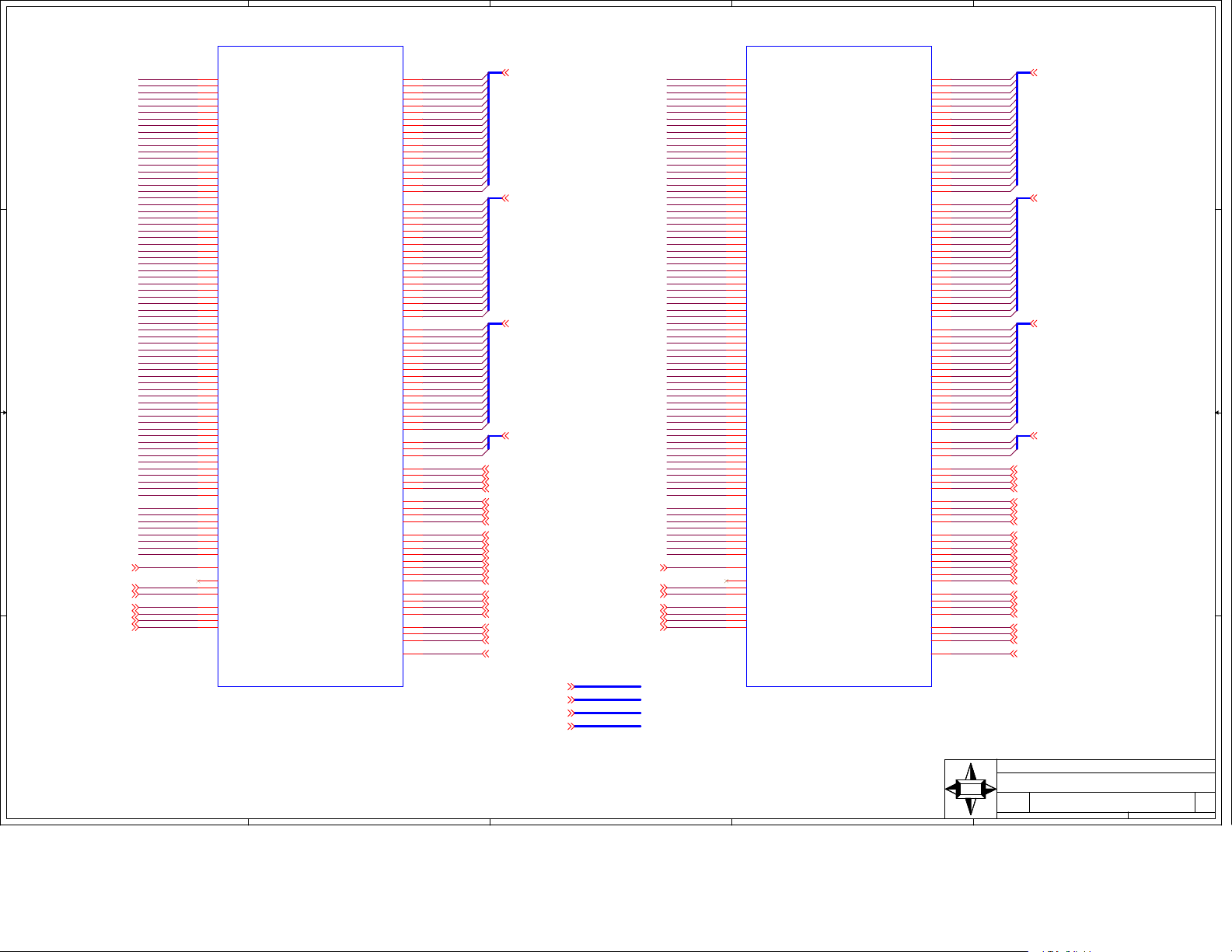

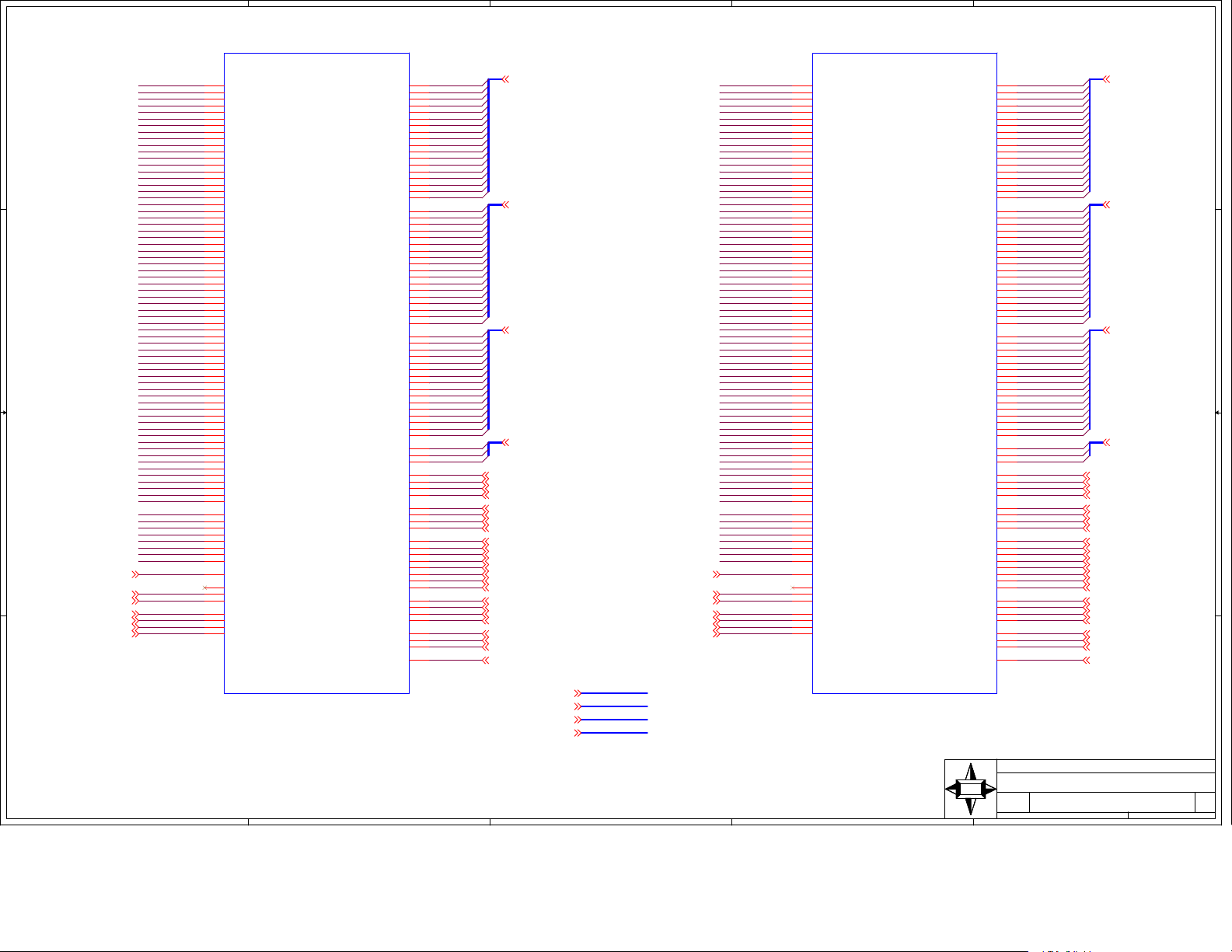

CPU0

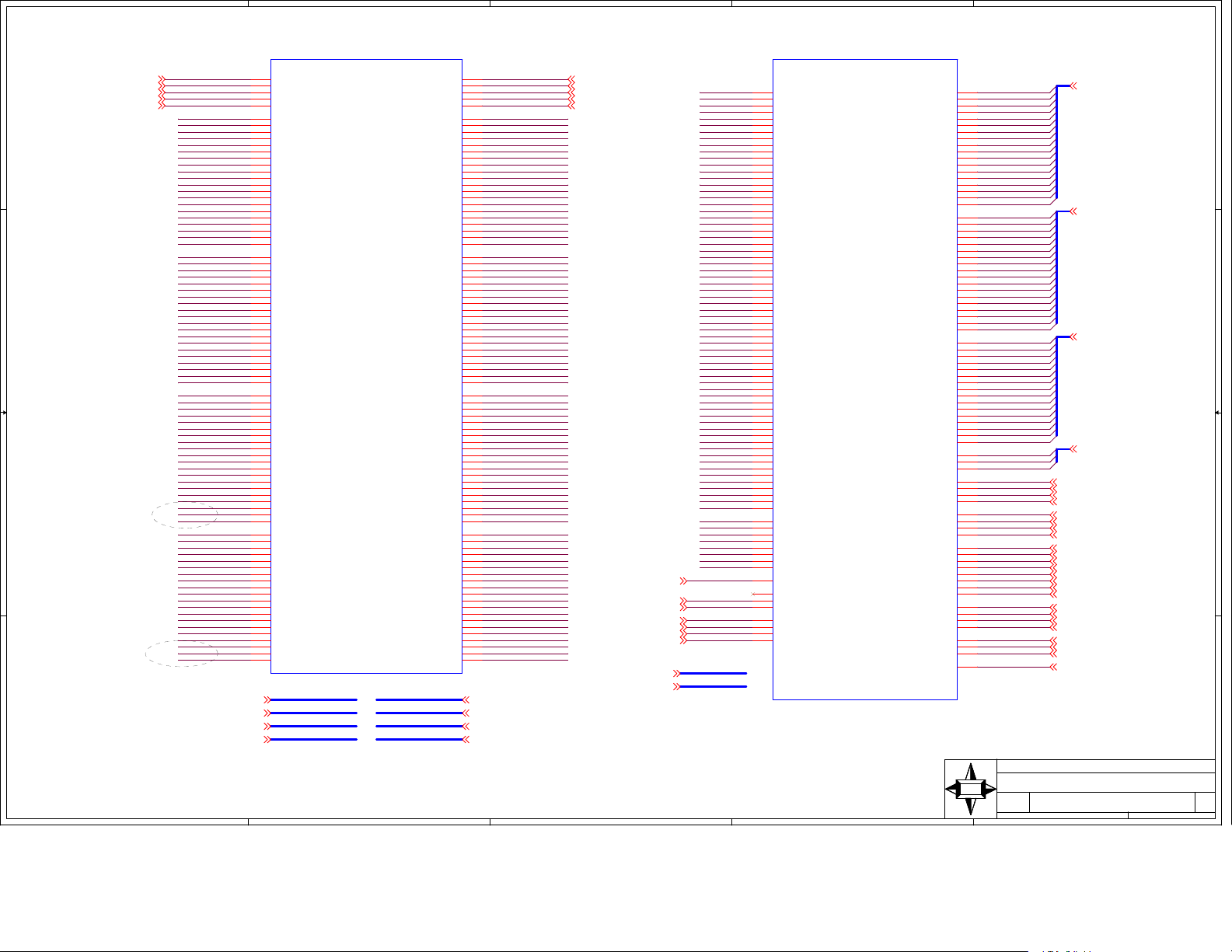

CPU1

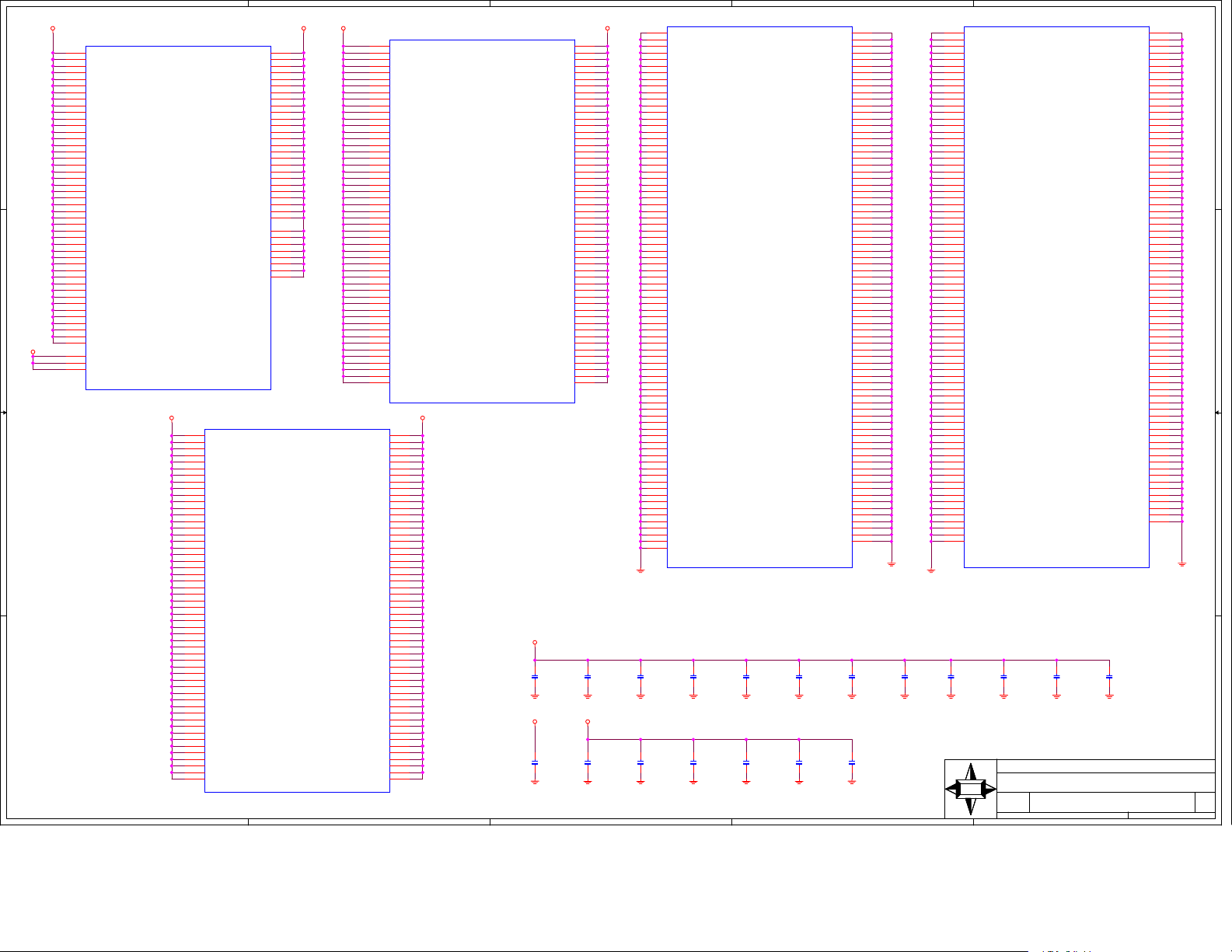

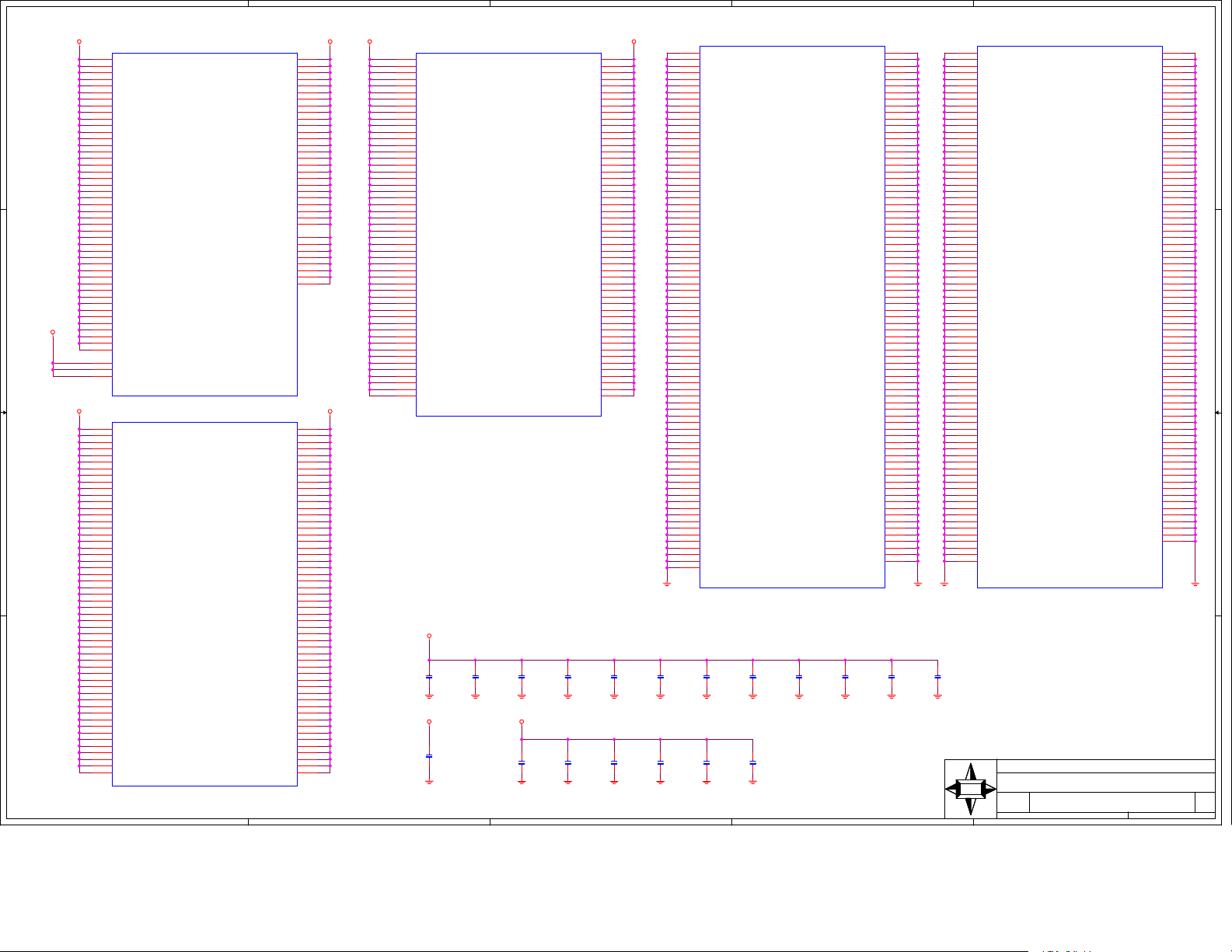

DDR3_CHANNELA~C

DDR3_CHANNELD~F

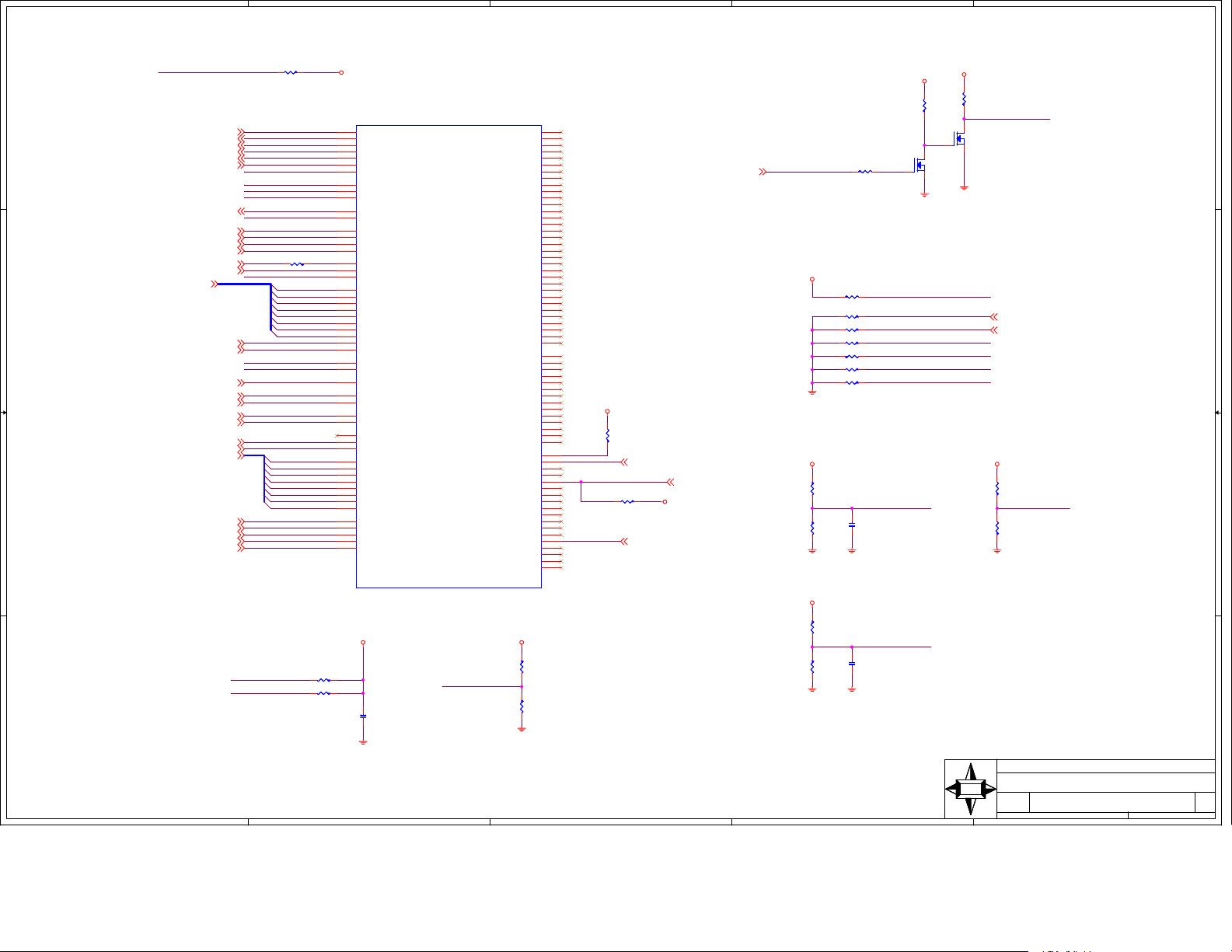

IOH_CSI

IOH_ESI / XDP

IOH_PCI_EXPRESS

IOH_MISCELLANEOUS

32_IOH_POWER

IOH_FILTERS_AND_VSS

ICH10R PEC-E / SATA / PCI

ICH10R LPC / SMB / RTC

ICH10R POWER

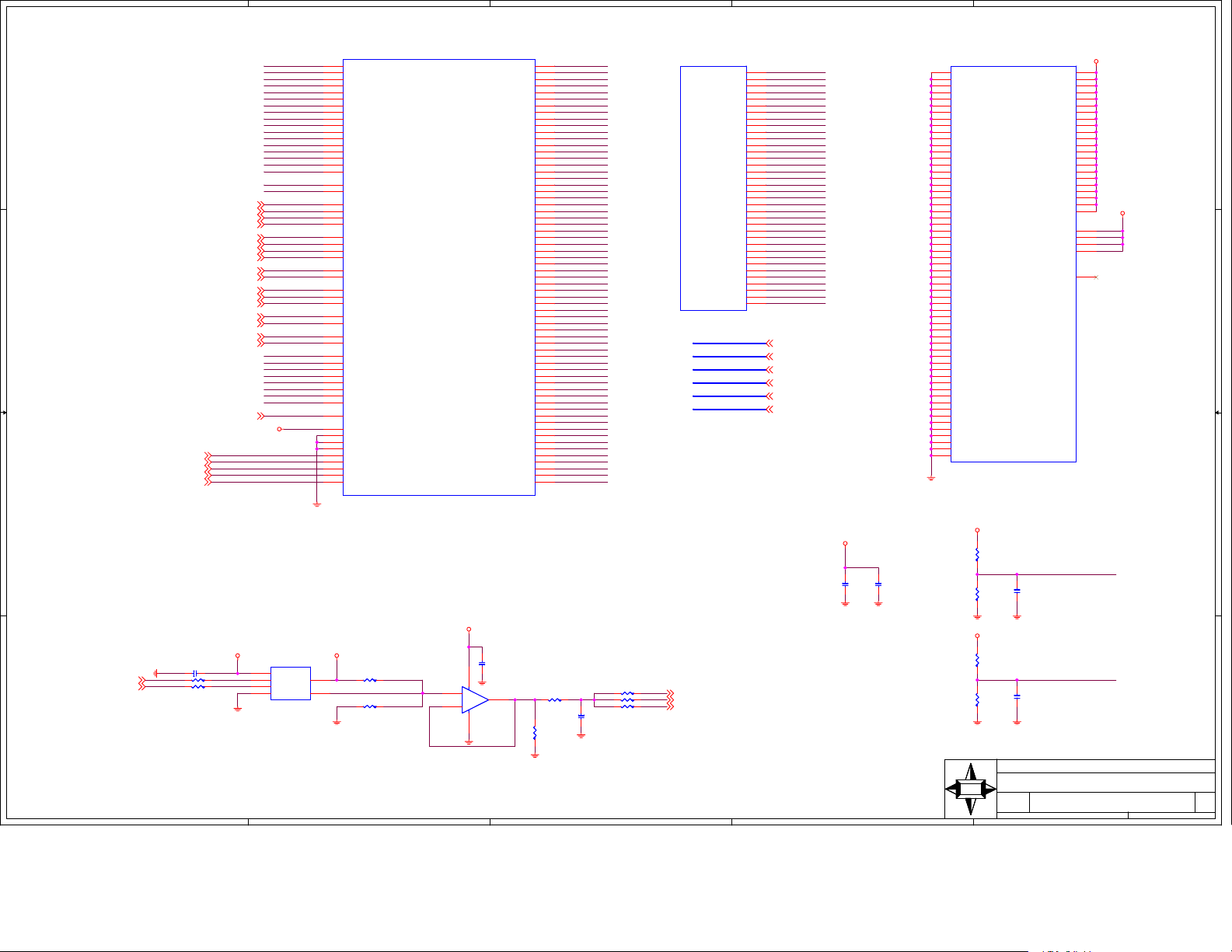

CK410B+_CLOCK_GENERATOR

82576_Kawela39~40

BLADE SIGNAL CONN

Mezzanine Card Signal

SAS LSI 1064E #1~#243~44

SAS Connector

COM PORT & SMBUS_SEL

CPU0_VCORE_ISL6334CRZ

CPU1_VCORE_ISL6334CRZ

CPU1_VTT_POWER

CPU0_DDR3_POWER_ISL6312CR

CPU1_DDR3_POWER_ISL6312CR

CPU0_&_CPU1_DDR3_VTT

CPU0_&_CPU1_SFR_PLL

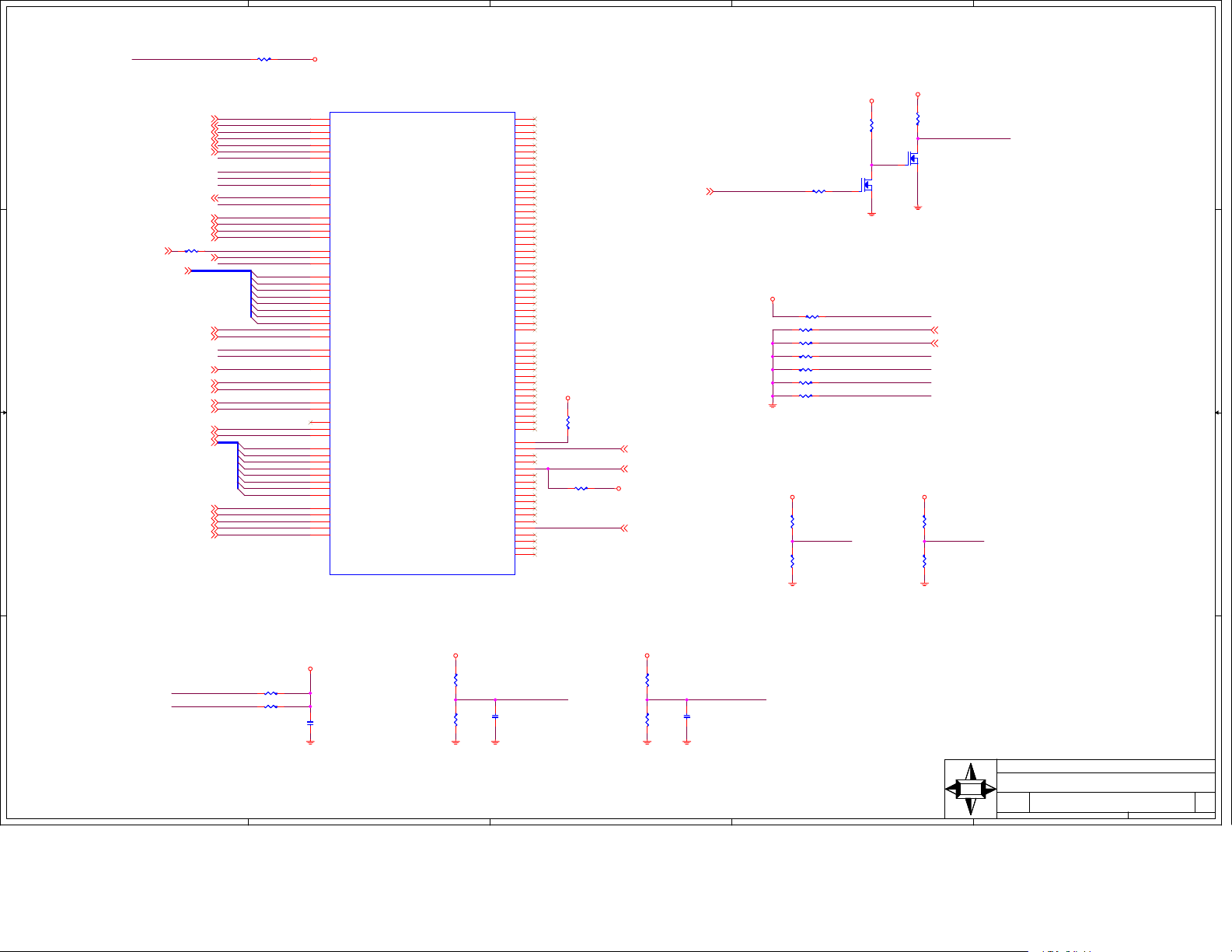

CPLD

1.5V_VR & 3.3_5VDUAL

IOH_1.1V

1.8VDUAL & ICH_POWER

CPU_SIDEBAND

BMC_AST1100

XDP0_CPU_JTAG

XDP0_&_XDP1_JTAG_CKTS

USB & Front Panel

SYSTEM_POWERGOODSEQUENCE

4

TitlePage

69

70

71

72

73

74

75

DEBUG LED

HWM_W83793 & SPI

TPS2490 HOT SWAP

DC-IN power

MISC_PART

HISTORY & GPIO

Placement

Preliminary Spec

* Intel TYLERSBURG 36D / ICH9/10R Chipset

* Intel LGA-1366 Gainstown

* 8 Layer BTX Form Factor (W 285mm X L 275mm)

* 12 DDR3 (2 CPU / 6 Channel)

* USB 2.0 (Rear x1 , Front x2)

* 1PCI Express X8 for Mezzanine card

* 1PCI Express X8 for OPT Blade connector

* 1PCI Express X4 for OPT Blade connector

* Serial ATA (2 channel)

* Serial Attached SCSI (2 channel)

* LAN INTEL PHY 82576 Kawela

* LPC SIO W83627EHG

* HWM W83793

* VCORE_ISL6334CRZ + DDR3_POWER_ISL6312CR + CPU_VTT_ISL6314CRZ

MSI

MSI

MSI

3

2

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-91C1

MS-91C1

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, November 27, 2008

Date:

Thursday, November 27, 2008

Date:

Thursday, November 27, 2008

MS-91C1

01_Cover / Table of SPEC

01_Cover / Table of SPEC

01_Cover / Table of SPEC

Sheet of

Sheet of

Sheet of

1

174

174

174

0A

0A

0A

Page 2

5

4

3

2

1

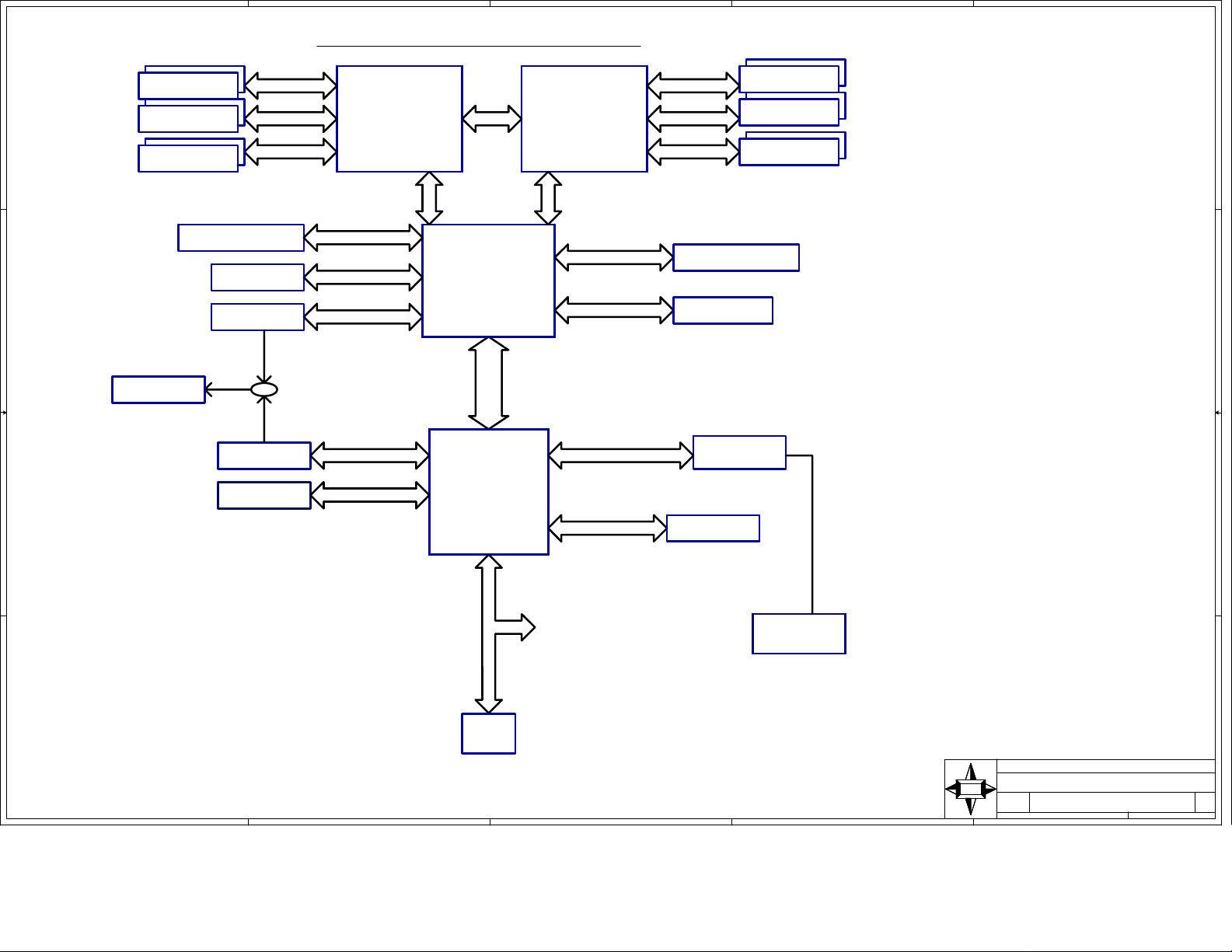

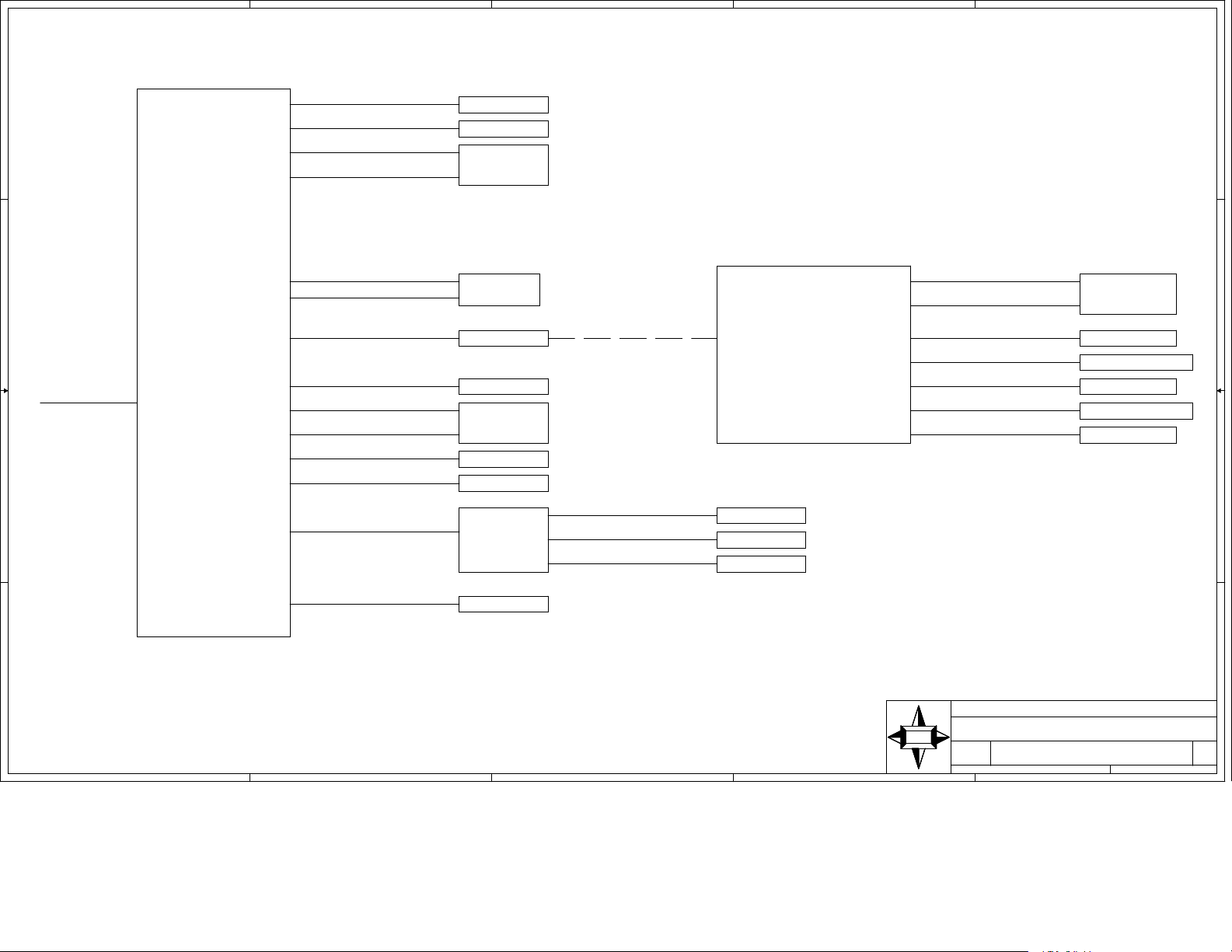

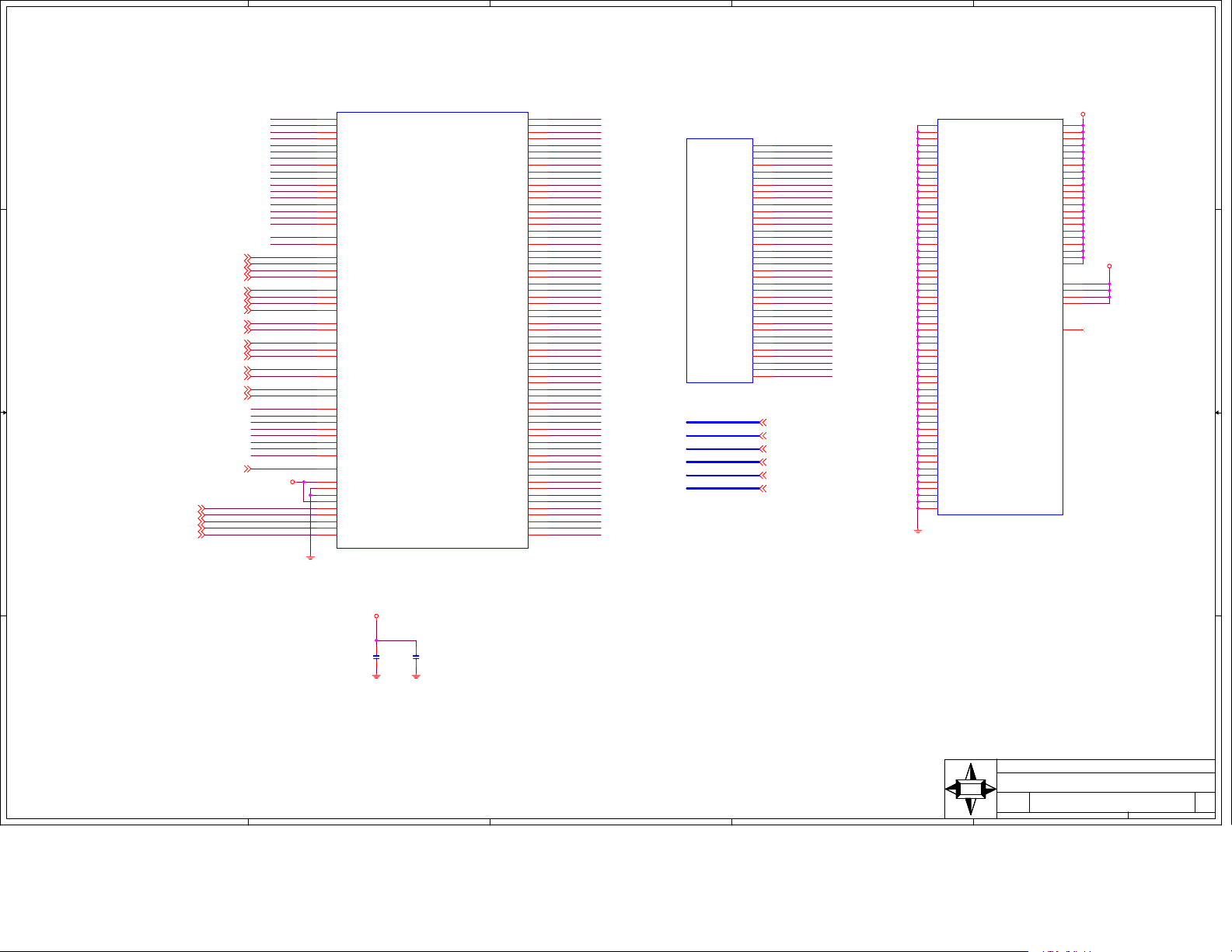

MS-91C1 SYSTEM BLOCK DIAGRAM

DIMM x2

Modules

D D

DIMM x2

Modules

DIMM x2

DDR3 Channel 0

DDR3 Channel 1

DDR3 Channel 2

CPU0

Intel LGA-1366

Nehalem-EP

QPI

CPU1

Intel LGA-1366

Nehalem-EP

DDR3 Channel 0

DDR3 Channel 1

DDR3 Channel 2

Modules

QPI

1066/1333MHz

OPT CPU BLADE

SIGNAL CONNECTOR

MEZZANINE

CARD

C C

LSI1064E

SAS

PCI Express X 8

PCI Express X 8

PCI Express X 4

Tylersburg

36D

QPI

1066/1333MHz

PCI Express X 8

PCI Express X 4

OPT CPU BLADE

SIGNAL CONNECTOR

INTEL 82576 LAN

DIMM x2

Modules

DIMM x2

Modules

DIMM x2

Modules

ESI BUS

SAS SLOT

SATA 0~1

USB2.0

(3 Port:0/1/11)

B B

SATA

USB 2.0

ICH9/10R

PCI BUS

SPI

BMC VGA

ASPEED 2050

SPI Flash BIOS

LPC Bus

A A

5

4

TPM 1.2

SLB9635

3

1 X Serial Port

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-91C1

MS-91C1

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, November 27, 2008

Date:

Thursday, November 27, 2008

Date:

2

Thursday, November 27, 2008

MS-91C1

02_Block_Diagram

02_Block_Diagram

02_Block_Diagram

1

274

274

274

Sheet of

Sheet of

Sheet of

0A

0A

0A

Page 3

5

4

3

2

1

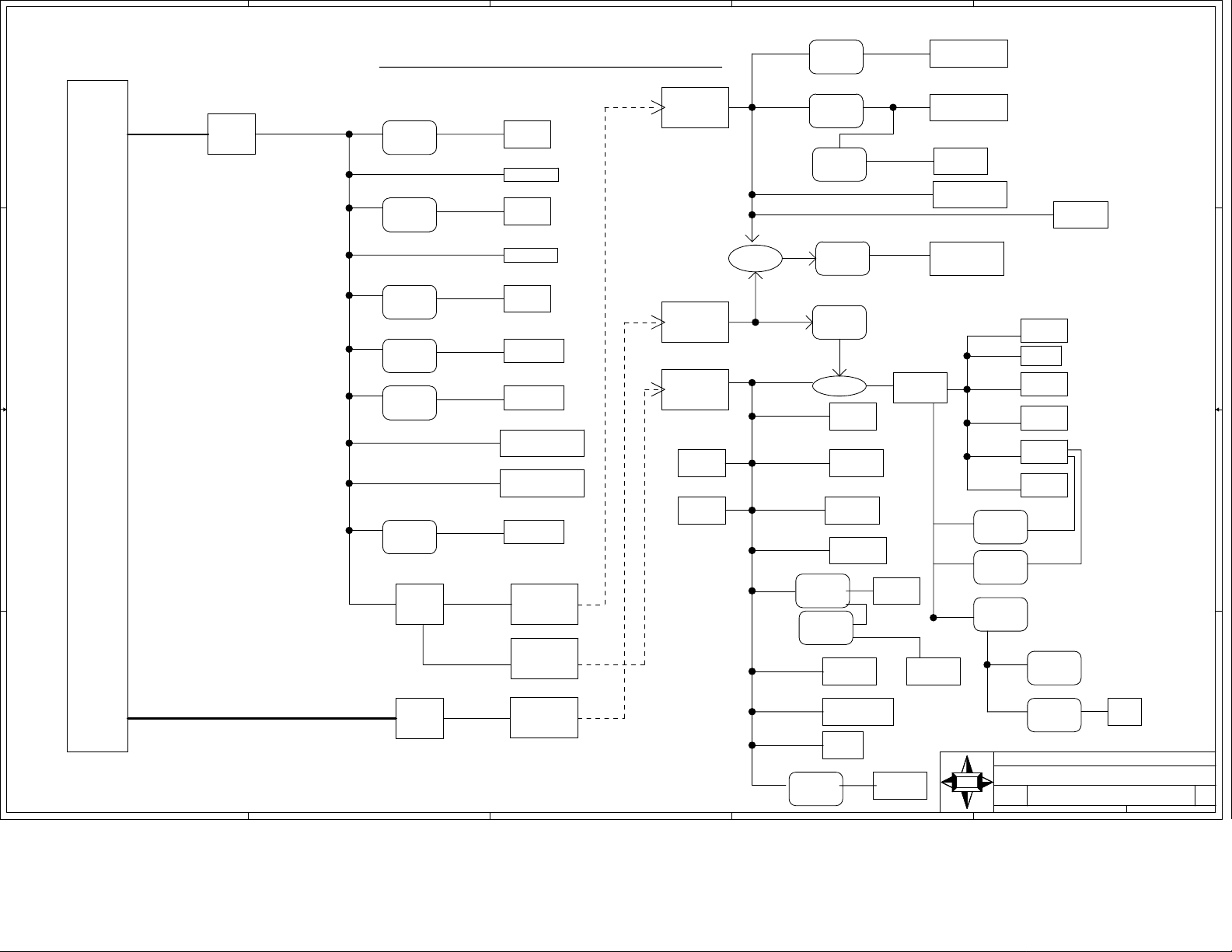

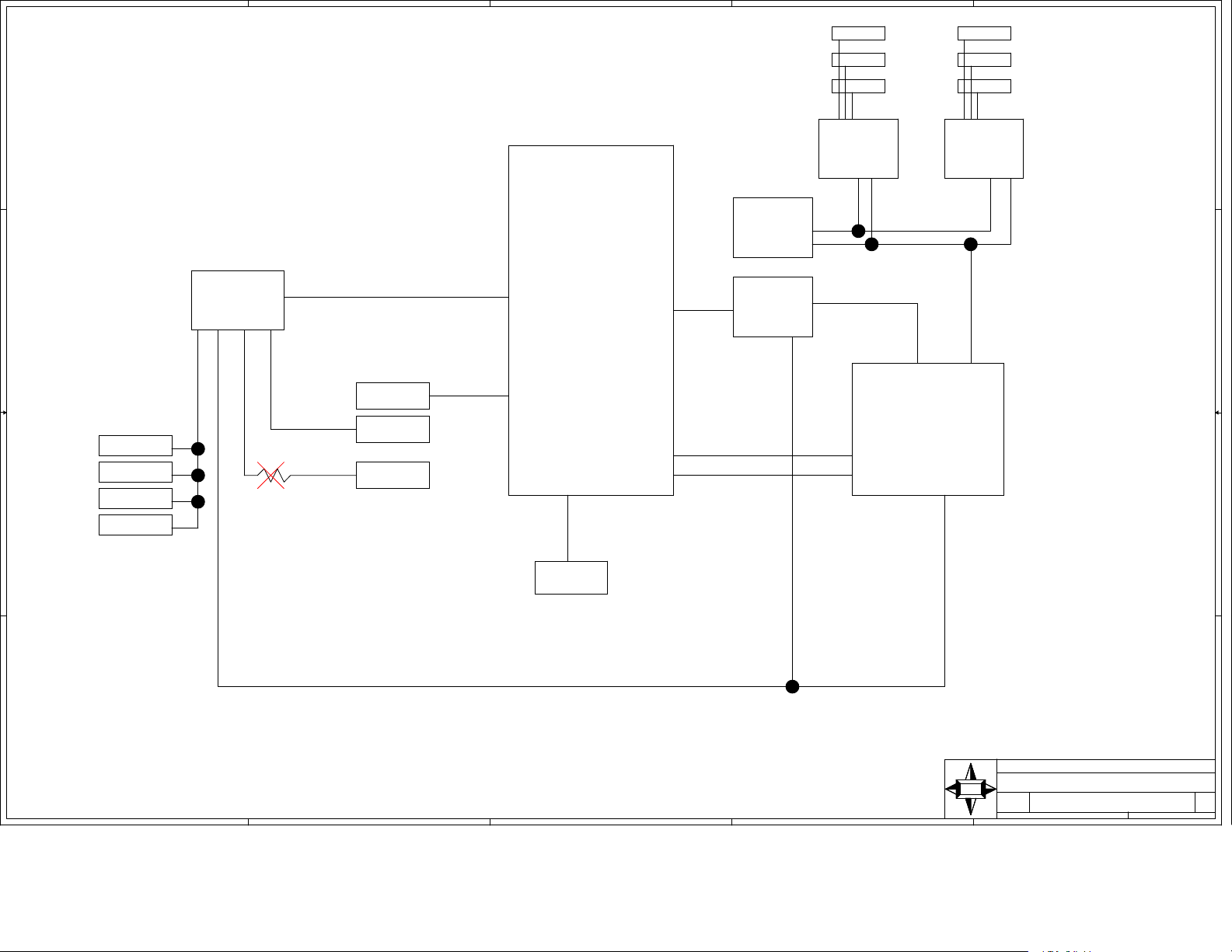

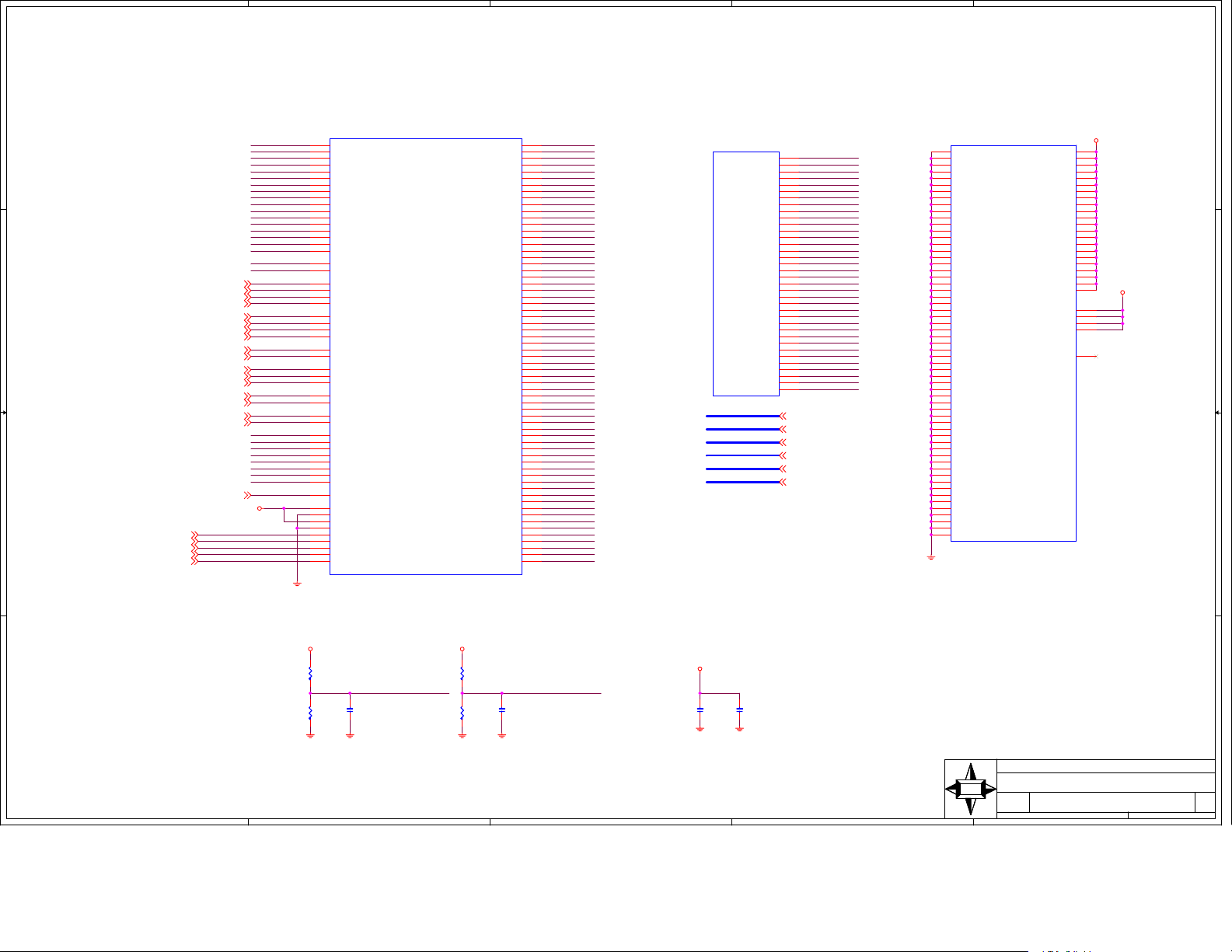

MS-91C1 POWER DELIVERY DIAGRAM

1.4A

1.57A+0.9A

D D

12V_BP

78.7 A

TPS2490

+12V

MAX=22.1 A

18A

VRD11

MAX=150A

PWR Hot Plug

18A

VRD11

MAX=150A

MAX=110A

CPU0

MAX=1.2A

CPUFAN1

MAX=110A

CPU1

MAX=1.2A

MAX=25A

MAX=88A

MAX=88A

MAX=22.9A

2.6A

CPUFAN2

CPU

CPU0_DDR3

CPU0_DDR3

SAS Expand Slot

Mezz Card

IOH

+5V

PSU

2.9A

CPU_VTT

12.5A

12.5A

3.3A

2A

2.6A

4.9A

1.1V/25A

ISL6312

1.5V

ISL6312

1.5V

ISL6545

1.1V

ISL6539

C C

B B

PWM PWR Reg

2.3A

+3.3V

+5V

+5VSB

+3.3V

200mA

IOH

350mA

932S421

7.37

2A

SWITCH

9.95

MAX=396mA

1.32A+1.05A

0.75V

VR

1.5V

VR

1.2V

Linear REG

1A

0.5A

MAX=1.5A

P5V_AUX

MAX=3A

3.3VSB

REG

P3VSB

SWITCH

309mA

200mA

ICH10

9DB803

Super IO

2A

MEZZ CARD

1.2V

Linear REG

TYP/MAX=0.2A/1A

LSI 1064

SAS chip

2.4A

P1V2_RE

MAX=1.94A

IOH+1.8_IOH

1.54A

MAX=4.21A

P1V5

MAX=6.01A

+3.3VDUAL

P1V2_SAS

LSI 1064

SAS chip

DDR3_CPU0/1

ICH10

MAX=2.4A

PCIE

RE-DRIVER

SATA Connector

MAX=1~1.5A

USB X 2 PORT

50mA

309mA

150mA

1.5A

200mA

150mA

334mA

477mA

2.84A

1.26V

0.7A

1.8V

0.9A

2.5V_DUAL

3A

Mezz Card

LAN

ICH10

CLK

9FGP202

MEZZ

BMC

SYSTEM

1A

1.8V_DUAL

1.21A

TYP/MAX=1.55A/1.85A

MAX=3.9AX2

12V_SB_BP

A A

3.3A

ISL6545

P5V_SBY

+5VSB

PWM PWR Reg

5

4

3

MAX=20mA

100mA

1A+1A

BIOS

POST Decode

TPM

1.8V

REG

CPU0/1

2

0.2A

1.5A

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Date:

Date:

548mA

1.0V

1.8V

1.7A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Thursday, November 27, 2008

Thursday, November 27, 2008

Thursday, November 27, 2008

LAN

MS-91C1

MS-91C1

MS-91C1

03_POWER_MAP

03_POWER_MAP

03_POWER_MAP

1

374

374

374

Sheet of

Sheet of

Sheet of

0A

0A

0A

Page 4

5

4

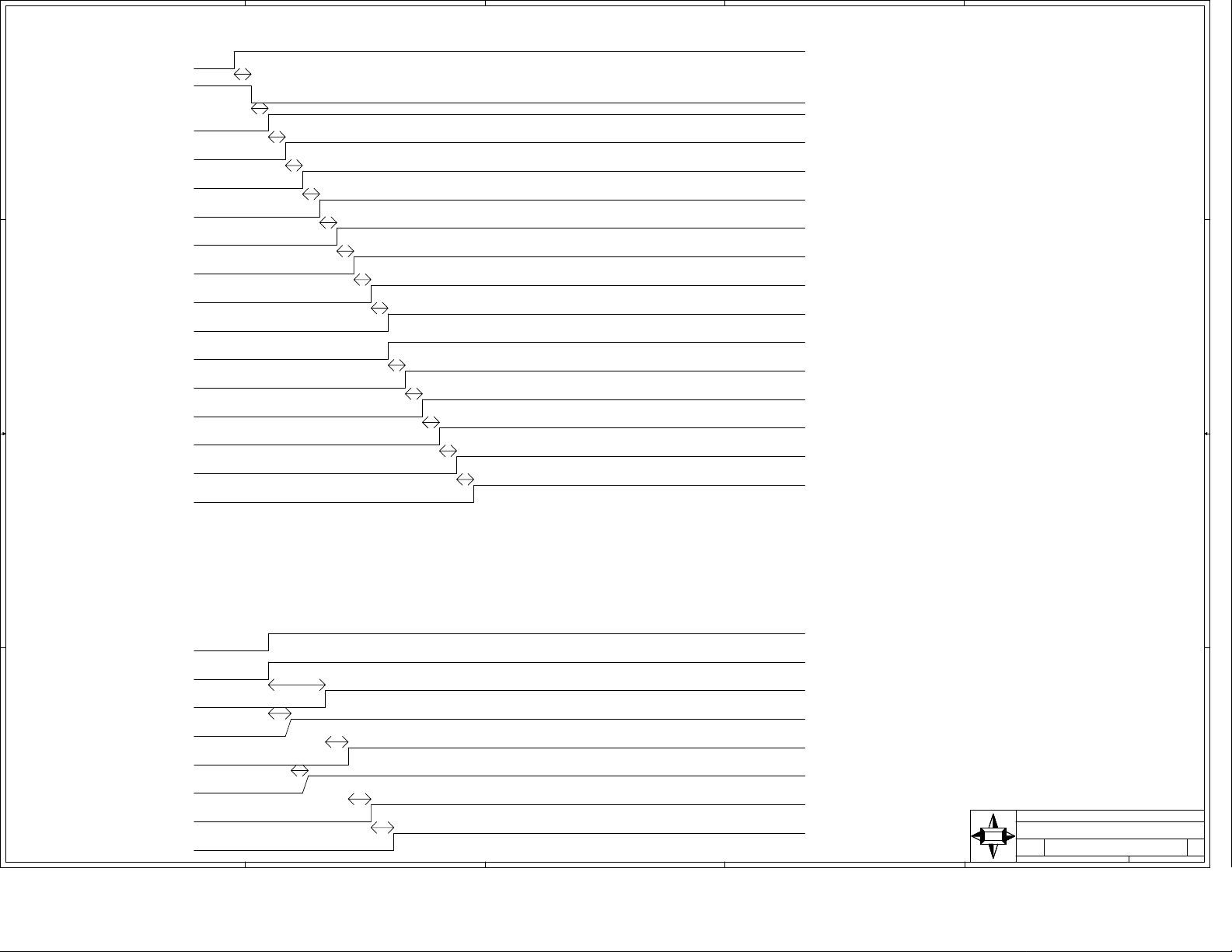

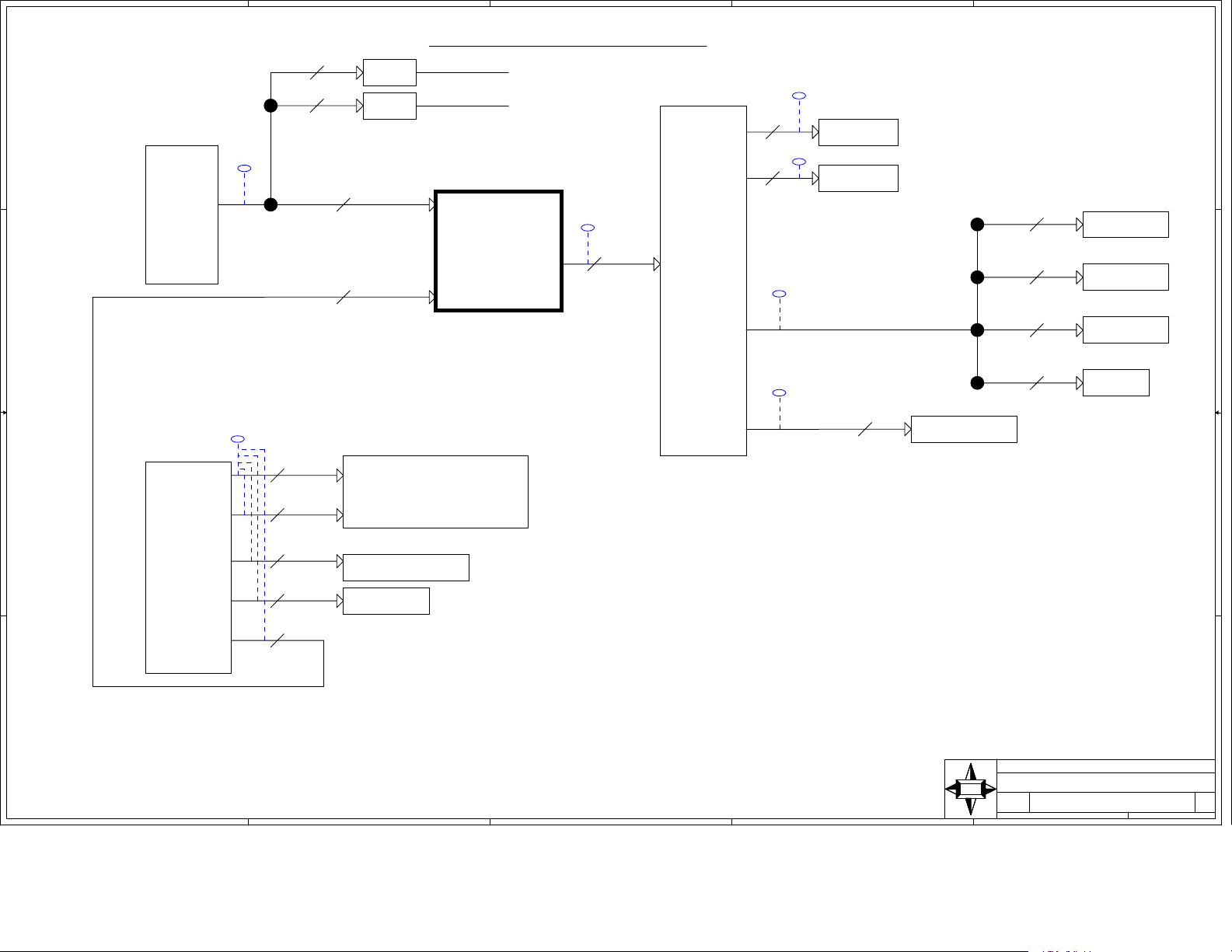

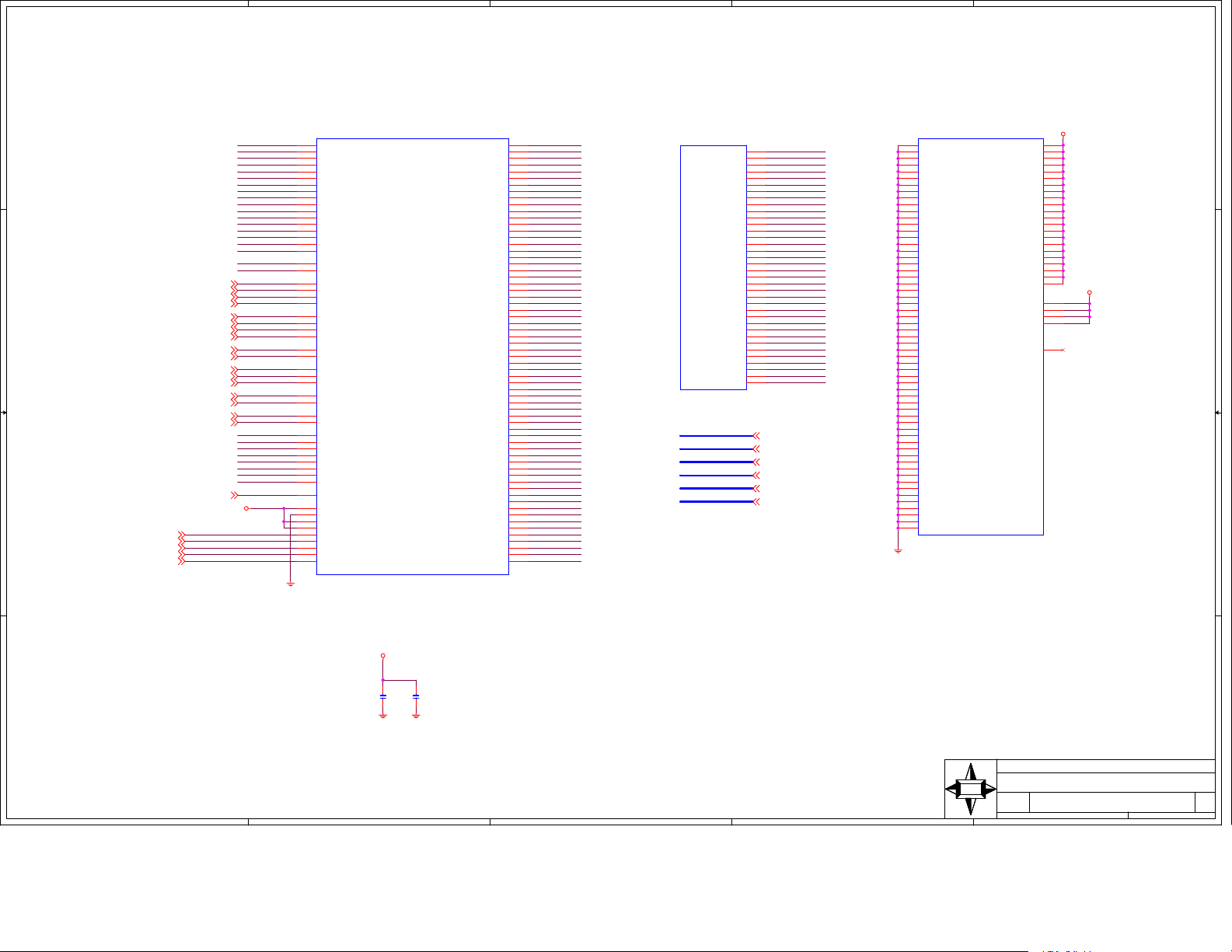

MS-91C1 power sequence (CPLD Version : 0.93)

3

2

1

SLP_S4#

PSON_N

D D

+3.3V

+1.5V_ICH

PWRGD_IOH_P1V1

PWRGD_CPU0_DDR3

PWRGD_PS_O

PWRGD_CPU0_VTT

PWRGD_CPU0_SFR

C C

PWRGD_CPU0_VCCP

PWRGD_IOH_COREPLLPWRDET

PWRGD_IOH_COREPWRGD

PWRGD_SYS

RST_PLTRST_N

RST_IOH_CORERST_DELAYED_N

31us

61ms

13ms

9ms

374ms

82.4ms

4.84ms

3.28ms

4.40ms

880us

141.12ms

1.07ms

9.23ms

5.12ms

RST_CPU_RESET_N

B B

ME unused power sequence

PWRGD_CPU_R1

PWRGD_IOH_COREPLLPWRDET

PWRGD_SYS

PWRGD_IOH_COREPWRGD

(AUXPWRGOOD)

A A

RST_PLTRST_N

PWRGD_IOH_COREPWRGD_RC

(COREPWRGOOD)

RST_IOH_CORERST_DELAYED_N

(CORERSTnn)

RST_CPU_RESET_N

(RESETO_N)

5

880us

3us

142ms

1.07ms

9.23ms

4

5.12ms

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-91C1

MS-91C1

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, November 27, 2008

Date:

Thursday, November 27, 2008

Date:

3

2

Thursday, November 27, 2008

MS-91C1

04_POWER_SEQUENCE

04_POWER_SEQUENCE

04_POWER_SEQUENCE

1

474

474

474

Sheet of

Sheet of

Sheet of

0B

0B

0B

Page 5

5

4

3

2

1

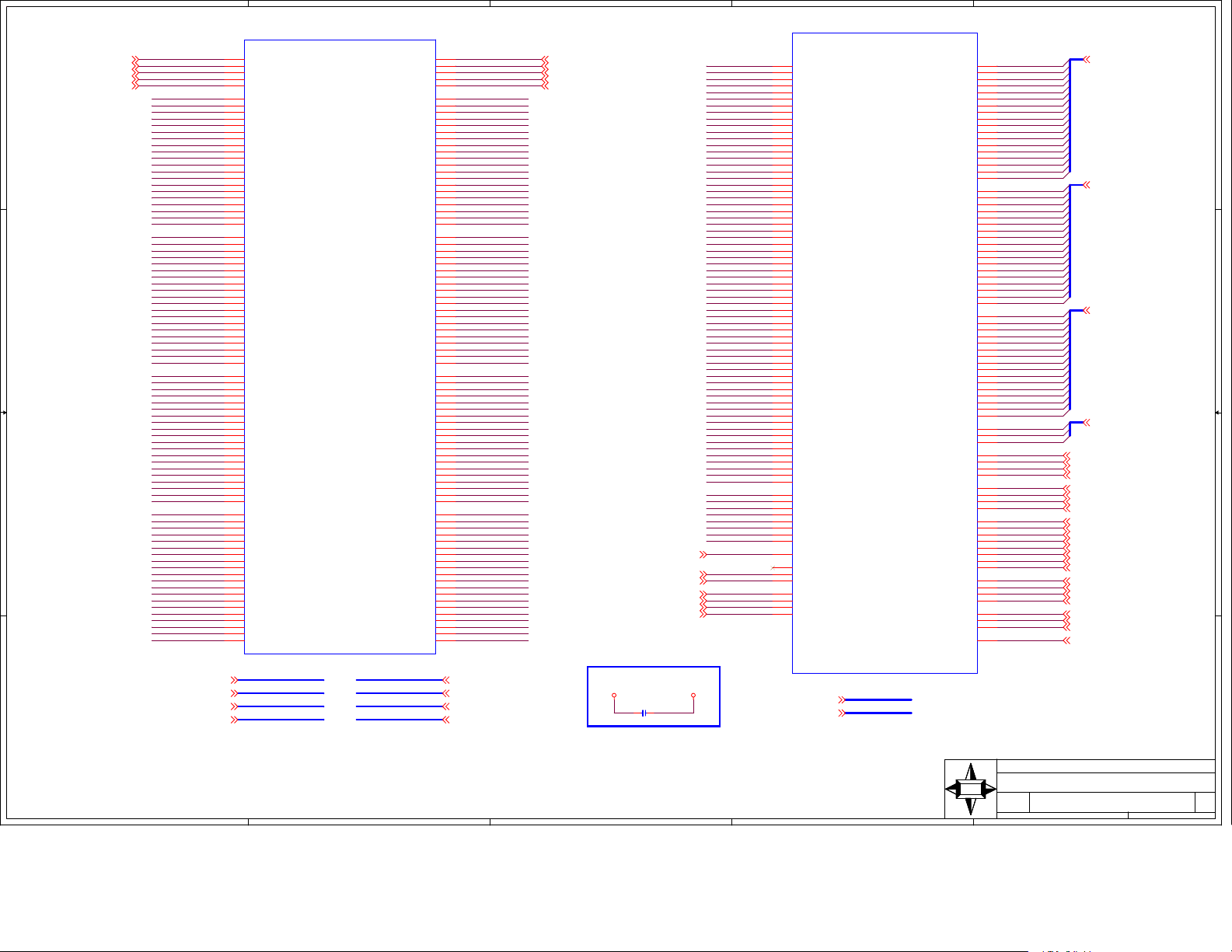

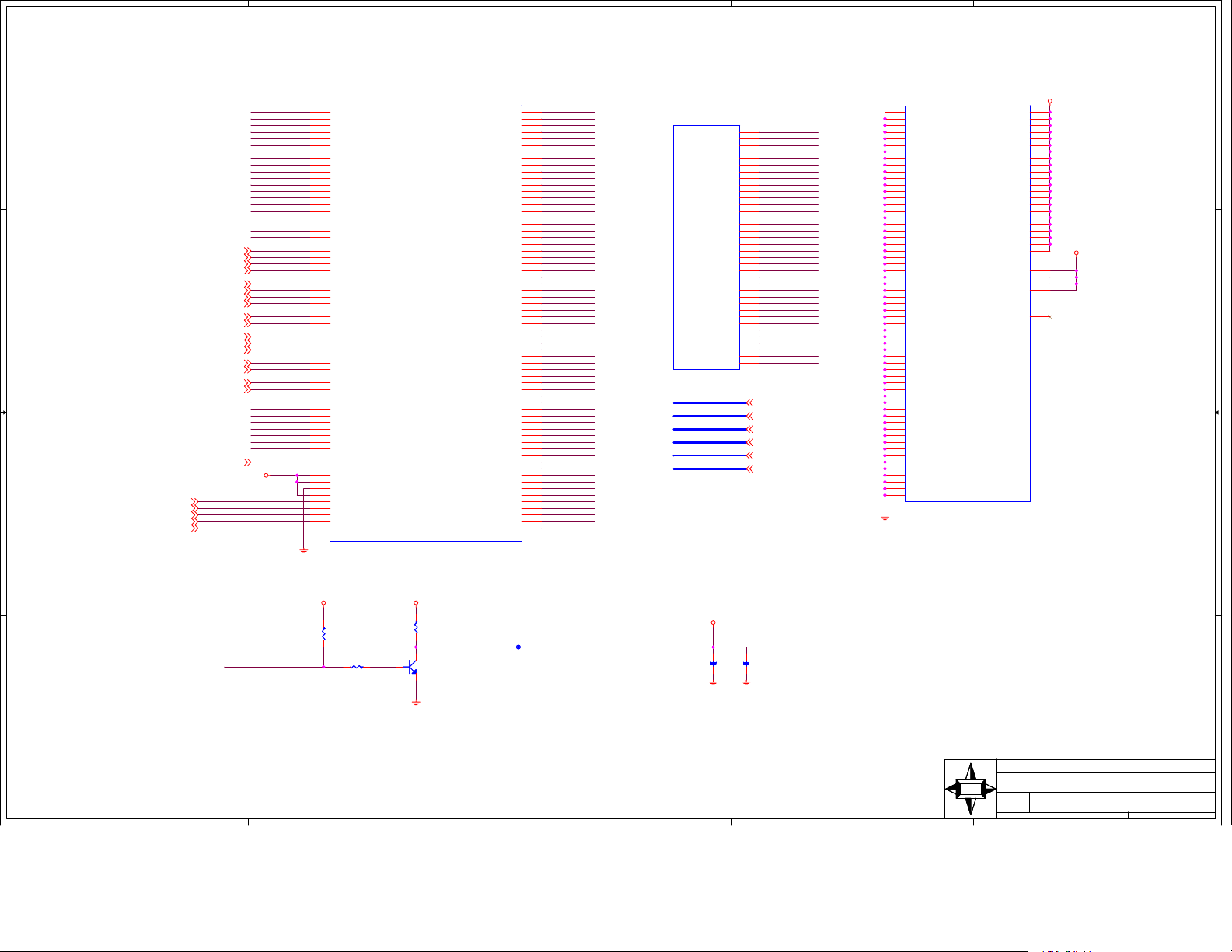

91C1 CLOCK Block

D D

ICS932

133M

CLK_133M_CPU0

CLK_133M_CPU1

CLK_133M_IOH_CSI0

CLK_133M_IOH_CSI1

CPU0

CPU1

IOH

CLK_100M_ICH_ESI

C C

100M33M

CLK_100M_ICH_SATA

CLK_100M_DB800

CK410B+

PCLK_ICH

14.3181MHZ

B B

48M14M

BMC_33M_LPC

CLK_33M_BMC

PCLK_SIO

LPC_PCLK

48M_BUF

ICH_14M

ICH

DB803

ICH

BMC

SIO

DEBUG LED

CY23S05

ICH

CLK_USB_ICH

SIO_48M

HWM_48M

DB803

(100M)

0XDC

ICH

SIO

HMW

CLK_100M_IOH_PE0CLK

CLK_100M_IOH_PE1CLK

CLK_100M_LAN

CLK_100M_X8

CLK_100M_MEZZ

CLK_100M_OPT4

SAS_100CLK

IOH

82576 LAN

OPT BLADE CONN

MEZZ

OPT BLADE CONN

LSI1064E SAS

0XD2

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-91C1

MS-91C1

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

B

B

B

Date:

Thursday, November 27, 2008

Date:

Thursday, November 27, 2008

Date:

5

4

3

2

Thursday, November 27, 2008

MS-91C1

05_CLK_MAP

05_CLK_MAP

05_CLK_MAP

Sheet of

Sheet of

Sheet of

1

0A

0A

0A

574

574

574

Page 6

5

4

3

2

1

MS-91C1 SMBus Block Diagram

2

D D

+3.3V_DUAL

ICH10R

2

ICH10_SMBCLK/DAT(AUX)

SMBDATA

ISL90727

ISL90727

2

SMBCLK

C C

2

CPU0_DDR3_VREF

CPU1_DDR3_VREF

+3.3V_DUAL

SWITCH

QS3126Q

Page 45

SMBus_CONTROL_ICH=High

2

IPMB_A

PCA9545

SCL0

SDA0

SCL1

SDA1

SCL

SDA

SCL2

SDA2

+3.3V

SMB_SPD0

2

+3.3V

SMB_SPD1

2

+3.3V

SMBCLK/DAT(MAIN)

CPU0 DIMM A~C

CPU1 DIMM A~C

2

2

2

CK 410B+

CK DB803

XDP1/XDP2

==>SMBus_ICH connects to SMBus

==>SMBus_BMC open

SCL3

SDA3

+3.3V_DUAL

SMBCLK/DAT(SLOT)

2

2

MEZZ CARD

SMBus_CONTROL_ICH=Low (Default)

==>SMBus_BMC connects to SMBus

+3.3V_DUAL

SCL1

SDA1

B B

BMC

Aspeed

SCL2

SDA2

SCL3

SDA3

SCL4

SDA4

SCL6

SDA6

2

2

2

2

2

IPMB_A

IPMB_B

CMM1_SMbus

CMM2_SMbus

SEEPROM AT24C512

HWM W83793

==>SMBus_ICH open

CPU BLADE SIGNAL CONN

IOH

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-91C1

MS-91C1

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, November 27, 2008

Date:

Thursday, November 27, 2008

Date:

5

4

3

2

Thursday, November 27, 2008

MS-91C1

06_SMBUS_MAP

06_SMBUS_MAP

06_SMBUS_MAP

1

674

674

674

Sheet of

Sheet of

Sheet of

0A

0A

0A

Page 7

5

4

3

2

1

M_A_RESET_N

M_B_RESET_N

D D

M_B_RESET_N

M_D_RESET_N

M_E_RESET_N

M_F_RESET_N

CPU0 CPU1

XDP0

C C

75LVC244

SIO_RST_N

PWRGD_SYS_BMC

RST_PCIE_SLOT_N

RST_PCIE_CLINK_N

82576LAN

BLADE CONN

RST_PLTRST_N

RTC PIN

HEADER

SIO

BMC

RTC_RST#

ICH10

XDP1

RST_LTRESET_N

RST_RSM_N

MEZZ

B B

LSI1064E SAS

PCIRST_ICH10#

JTAG_IOH_TRST_N

JTAG_CPU_TRST_N

RST_CPU_RESET_N

IOH

BMC

VGA Function

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-91C1

MS-91C1

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, November 27, 2008

Date:

Thursday, November 27, 2008

Date:

5

4

3

2

Thursday, November 27, 2008

MS-91C1

07_RESET_MAP

07_RESET_MAP

07_RESET_MAP

1

774

774

774

Sheet of

Sheet of

Sheet of

0A

0A

0A

Page 8

5

CPU0A

CPU0A

CSI_CPU0_IOH_CLK_DP28

CSI_CPU0_IOH_CLK_DN28

CSI_IOH_CPU0_CLK_DP28

CSI_IOH_CPU0_CLK_DN28

D D

C C

B B

A A

CSI_CPU0_IOH_CLK_DP

CSI_CPU0_IOH_CLK_DN

CSI_IOH_CPU0_CLK_DP

CSI_IOH_CPU0_CLK_DN

CSI_CPU0_CMP0

CSI_CPU0_IOH_DN0

CSI_CPU0_IOH_DN1

CSI_CPU0_IOH_DN2

CSI_CPU0_IOH_DN3

CSI_CPU0_IOH_DN4

CSI_CPU0_IOH_DN5

CSI_CPU0_IOH_DN6

CSI_CPU0_IOH_DN7

CSI_CPU0_IOH_DN8

CSI_CPU0_IOH_DN9

CSI_CPU0_IOH_DN10

CSI_CPU0_IOH_DN11

CSI_CPU0_IOH_DN12

CSI_CPU0_IOH_DN13

CSI_CPU0_IOH_DN14

CSI_CPU0_IOH_DN15

CSI_CPU0_IOH_DN16

CSI_CPU0_IOH_DN17

CSI_CPU0_IOH_DN18

CSI_CPU0_IOH_DN19

CSI_CPU0_IOH_DP0

CSI_CPU0_IOH_DP1

CSI_CPU0_IOH_DP2

CSI_CPU0_IOH_DP3

CSI_CPU0_IOH_DP4

CSI_CPU0_IOH_DP5

CSI_CPU0_IOH_DP6

CSI_CPU0_IOH_DP7

CSI_CPU0_IOH_DP8

CSI_CPU0_IOH_DP9

CSI_CPU0_IOH_DP10

CSI_CPU0_IOH_DP11

CSI_CPU0_IOH_DP12

CSI_CPU0_IOH_DP13

CSI_CPU0_IOH_DP14

CSI_CPU0_IOH_DP15

CSI_CPU0_IOH_DP16

CSI_CPU0_IOH_DP17

CSI_CPU0_IOH_DP18

CSI_CPU0_IOH_DP19

CSI_IOH_CPU0_DN19

CSI_IOH_CPU0_DN18

CSI_IOH_CPU0_DN17

CSI_IOH_CPU0_DN16

CSI_IOH_CPU0_DN15

CSI_IOH_CPU0_DN14

CSI_IOH_CPU0_DN13

CSI_IOH_CPU0_DN12

CSI_IOH_CPU0_DN11

CSI_IOH_CPU0_DN10

CSI_IOH_CPU0_DN9

CSI_IOH_CPU0_DN8

CSI_IOH_CPU0_DN7

CSI_IOH_CPU0_DN6

CSI_IOH_CPU0_DN5

CSI_IOH_CPU0_DN4

CSI_IOH_CPU0_DN3

CSI_IOH_CPU0_DN2

CSI_IOH_CPU0_DN1

CSI_IOH_CPU0_DN0

CSI_IOH_CPU0_DP19

CSI_IOH_CPU0_DP18

CSI_IOH_CPU0_DP17

CSI_IOH_CPU0_DP16

CSI_IOH_CPU0_DP15

CSI_IOH_CPU0_DP14

CSI_IOH_CPU0_DP13

CSI_IOH_CPU0_DP12

CSI_IOH_CPU0_DP11

CSI_IOH_CPU0_DP10

CSI_IOH_CPU0_DP9

CSI_IOH_CPU0_DP8

CSI_IOH_CPU0_DP7

CSI_IOH_CPU0_DP6

CSI_IOH_CPU0_DP5

CSI_IOH_CPU0_DP4

CSI_IOH_CPU0_DP3

CSI_IOH_CPU0_DP2

CSI_IOH_CPU0_DP1

CSI_IOH_CPU0_DP0

CSI_CPU0_IOH_DP[19..0]28

CSI_CPU0_IOH_DN[19..0]28

CSI_IOH_CPU0_DP[19..0]28

CSI_IOH_CPU0_DN[19..0]28

AG42

CSI0_CLKTX_DP

AF42

CSI0_CLKTX_DN

AR41

CSI0_CLKRX_DP

AR42

CSI0_CLKRX_DN

AL43

CSI0_COMP

AE40

CSI0_DTX_DP<19>

AD38

CSI0_DTX_DP<18>

AB39

CSI0_DTX_DP<17>

AC39

CSI0_DTX_DP<16>

AC41

CSI0_DTX_DP<15>

AD40

CSI0_DTX_DP<14>

AC43

CSI0_DTX_DP<13>

AD42

CSI0_DTX_DP<12>

AE42

CSI0_DTX_DP<11>

AF43

CSI0_DTX_DP<10>

AG40

CSI0_DTX_DP<9>

AJ43

CSI0_DTX_DP<8>

AK42

CSI0_DTX_DP<7>

AH41

CSI0_DTX_DP<6>

AK40

CSI0_DTX_DP<5>

AH40

CSI0_DTX_DP<4>

AJ38

CSI0_DTX_DP<3>

AK37

CSI0_DTX_DP<2>

AF39

CSI0_DTX_DP<1>

AG38

CSI0_DTX_DP<0>

AF40

CSI0_DTX_DN<19>

AE38

CSI0_DTX_DN<18>

AB38

CSI0_DTX_DN<17>

AC38

CSI0_DTX_DN<16>

AC40

CSI0_DTX_DN<15>

AD39

CSI0_DTX_DN<14>

AB43

CSI0_DTX_DN<13>

AC42

CSI0_DTX_DN<12>

AE41

CSI0_DTX_DN<11>

AE43

CSI0_DTX_DN<10>

AG41

CSI0_DTX_DN<9>

AH43

CSI0_DTX_DN<8>

AJ42

CSI0_DTX_DN<7>

AH42

CSI0_DTX_DN<6>

AK41

CSI0_DTX_DN<5>

AJ40

CSI0_DTX_DN<4>

AJ39

CSI0_DTX_DN<3>

AK38

CSI0_DTX_DN<2>

AG39

CSI0_DTX_DN<1>

AH38

CSI0_DTX_DN<0>

AP38

CSI0_DRX_DP<19>

AN39

CSI0_DRX_DP<18>

AP41

CSI0_DRX_DP<17>

AM42

CSI0_DRX_DP<16>

AN40

CSI0_DRX_DP<15>

AN43

CSI0_DRX_DP<14>

AP42

CSI0_DRX_DP<13>

AT40

CSI0_DRX_DP<12>

AT43

CSI0_DRX_DP<11>

AU42

CSI0_DRX_DP<10>

AU40

CSI0_DRX_DP<9>

AW40

CSI0_DRX_DP<8>

AU39

CSI0_DRX_DP<7>

BA38

CSI0_DRX_DP<6>

AW37

CSI0_DRX_DP<5>

BA36

CSI0_DRX_DP<4>

AW36

CSI0_DRX_DP<3>

AV36

CSI0_DRX_DP<2>

AU38

CSI0_DRX_DP<1>

AT37

CSI0_DRX_DP<0>

AR38

CSI0_DRX_DN<19>

AP39

CSI0_DRX_DN<18>

AP40

CSI0_DRX_DN<17>

AM41

CSI0_DRX_DN<16>

AM40

CSI0_DRX_DN<15>

AM43

CSI0_DRX_DN<14>

AN42

CSI0_DRX_DN<13>

AR40

CSI0_DRX_DN<12>

AR43

CSI0_DRX_DN<11>

AT42

CSI0_DRX_DN<10>

AU41

CSI0_DRX_DN<9>

AV40

CSI0_DRX_DN<8>

AT39

CSI0_DRX_DN<7>

AY38

CSI0_DRX_DN<6>

AW38

CSI0_DRX_DN<5>

BA37

CSI0_DRX_DN<4>

AY36

CSI0_DRX_DN<3>

AV37

CSI0_DRX_DN<2>

AV38

CSI0_DRX_DN<1>

AU37

CSI0_DRX_DN<0>

CSI_CPU0_IOH_DP[19..0]

CSI_CPU0_IOH_DN[19..0]

CSI_IOH_CPU0_DP[19..0]

CSI_IOH_CPU0_DN[19..0]

Gainstown

Gainstown

1/10

1/10

Gainstown

Gainstown

4

CSI1_CLKTX_DP

CSI1_CLKTX_DN

CS1_CLKRX_DP

CSI1_CLKRX_DN

CSI1_COMP

CSI1_DTX_DP<19>

CSI1_DTX_DP<18>

CSI1_DTX_DP<17>

CSI1_DTX_DP<16>

CSI1_DTX_DP<15>

CSI1_DTX_DP<14>

CSI1_DTX_DP<13>

CSI1_DTX_DP<12>

CSI1_DTX_DP<11>

CSI1_DTX_DP<10>

CSI1_DTX_DP<9>

CSI1_DTX_DP<8>

CSI1_DTX_DP<7>

CSI1_DTX_DP<6>

CSI1_DTX_DP<5>

CSI1_DTX_DP<4>

CSI1_DTX_DP<3>

CSI1_DTX_DP<2>

CSI1_DTX_DP<1>

CSI1_DTX_DP<0>

CSI1_DTX_DN<19>

CSI1_DTX_DN<18>

CSI1_DTX_DN<17>

CSI1_DTX_DN<16>

CSI1_DTX_DN<15>

CSI1_DTX_DN<14>

CSI1_DTX_DN<13>

CSI1_DTX_DN<12>

CSI1_DTX_DN<11>

CSI1_DTX_DN<10>

CSI1_DTX_DN<9>

CSI1_DTX_DN<8>

CSI1_DTX_DN<7>

CSI1_DTX_DN<6>

CSI1_DTX_DN<5>

CSI1_DTX_DN<4>

CSI1_DTX_DN<3>

CSI1_DTX_DN<2>

CSI1_DTX_DN<1>

CSI1_DTX_DN<0>

CSI1_DRX_DP<19>

CSI1_DRX_DP<18>

CSI1_DRX_DP<17>

CSI1_DRX_DP<16>

CSI1_DRX_DP<15>

CSI1_DRX_DP<14>

CSI1_DRX_DP<13>

CSI1_DRX_DP<12>

CSI1_DRX_DP<11>

CSI1_DRX_DP<10>

CSI1_DRX_DP<9>

CSI1_DRX_DP<8>

CSI1_DRX_DP<7>

CSI1_DRX_DP<6>

CSI1_DRX_DP<5>

CSI1_DRX_DP<4>

CSI1_DRX_DP<3>

CSI1_DRX_DP<2>

CSI1_DRX_DP<1>

CSI1_DRX_DP<0>

CS1_DRX_DN<19>

CSI1_DRX_DN<18>

CSI1_DRX_DN<17>

CSI1_DRX_DN<16>

CSI1_DRX_DN<15>

CSI1_DRX_DN<14>

CSI1_DRX_DN<13>

CSI1_DRX_DN<12>

CSI1_DRX_DN<11>

CSI1_DRX_DN<10>

CSI1_DRX_DN<9>

CSI1_DRX_DN<8>

CSI1_DRX_DN<7>

CSI1_DRX_DN<6>

CSI1_DRX_DN<5>

CSI1_DRX_DN<4>

CSI1_DRX_DN<3>

CSI1_DRX_DN<2>

CSI1_DRX_DN<1>

CSI1_DRX_DN<0>

CSI_CPU0_CPU1_DP[19..0]

CSI_CPU0_CPU1_DN[19..0]

CSI_CPU1_CPU0_DN[19..0]

CSI_CPU1_CPU0_DP[19..0]

CSI_CPU0_CPU1_CLK_DP

AF6

CSI_CPU0_CPU1_CLK_DN

AE6

CSI_CPU1_CPU0_CLK_DN

AT6

CSI_CPU1_CPU0_CLK_DP

AR6

CSI_CPU0_CMP1

AL6

CSI_CPU0_CPU1_DP19

AC8

CSI_CPU0_CPU1_DP18

AD5

CSI_CPU0_CPU1_DP17

AD6

CSI_CPU0_CPU1_DP16

AB6

CSI_CPU0_CPU1_DP15

AC4

CSI_CPU0_CPU1_DP14

AE3

CSI_CPU0_CPU1_DP13

AC3

CSI_CPU0_CPU1_DP12

AD2

CSI_CPU0_CPU1_DP11

AE1

CSI_CPU0_CPU1_DP10

AF2

CSI_CPU0_CPU1_DP9

AH2

CSI_CPU0_CPU1_DP8

AH3

CSI_CPU0_CPU1_DP7

AK1

CSI_CPU0_CPU1_DP6

AJ3

CSI_CPU0_CPU1_DP5

AG7

CSI_CPU0_CPU1_DP4

AJ4

CSI_CPU0_CPU1_DP3

AK6

CSI_CPU0_CPU1_DP2

AH6

CSI_CPU0_CPU1_DP1

AJ8

CSI_CPU0_CPU1_DP0

AG8

CSI_CPU0_CPU1_DN19

AD8

CSI_CPU0_CPU1_DN18

AE5

CSI_CPU0_CPU1_DN17

AD7

CSI_CPU0_CPU1_DN16

AC6

CSI_CPU0_CPU1_DN15

AD4

CSI_CPU0_CPU1_DN14

AE4

CSI_CPU0_CPU1_DN13

AB3

CSI_CPU0_CPU1_DN12

AD3

CSI_CPU0_CPU1_DN11

AD1

CSI_CPU0_CPU1_DN10

AF3

CSI_CPU0_CPU1_DN9

AG2

CSI_CPU0_CPU1_DN8

AH4

CSI_CPU0_CPU1_DN7

AJ1

CSI_CPU0_CPU1_DN6

AJ2

CSI_CPU0_CPU1_DN5

AG6

CSI_CPU0_CPU1_DN4

AK4

CSI_CPU0_CPU1_DN3

AK5

CSI_CPU0_CPU1_DN2

AJ6

CSI_CPU0_CPU1_DN1

AJ7

CSI_CPU0_CPU1_DN0

AH8

CSI_CPU1_CPU0_DN0

AM8

CSI_CPU1_CPU0_DN1

AM6

CSI_CPU1_CPU0_DN2

AN5

CSI_CPU1_CPU0_DN3

AM4

CSI_CPU1_CPU0_DN4

AP3

CSI_CPU1_CPU0_DN5

AM2

CSI_CPU1_CPU0_DN6

AN1

CSI_CPU1_CPU0_DN7

AP2

CSI_CPU1_CPU0_DN8

AR4

CSI_CPU1_CPU0_DN9

AT1

CSI_CPU1_CPU0_DN10

AT3

CSI_CPU1_CPU0_DN11

AU4

CSI_CPU1_CPU0_DN12

AW4

CSI_CPU1_CPU0_DN13

AU7

CSI_CPU1_CPU0_DN14

AY6

CSI_CPU1_CPU0_DN15

BA7

CSI_CPU1_CPU0_DN16

AV5

CSI_CPU1_CPU0_DN17

AY8

CSI_CPU1_CPU0_DN18

AV7

CSI_CPU1_CPU0_DN19

AU8

CSI_CPU1_CPU0_DP0

AL8

CSI_CPU1_CPU0_DP1

AM7

CSI_CPU1_CPU0_DP2

AN6

CSI_CPU1_CPU0_DP3

AN4

CSI_CPU1_CPU0_DP4

AP4

CSI_CPU1_CPU0_DP5

AM3

CSI_CPU1_CPU0_DP6

AM1

CSI_CPU1_CPU0_DP7

AN2

CSI_CPU1_CPU0_DP8

AR5

CSI_CPU1_CPU0_DP9

AR1

CSI_CPU1_CPU0_DP10

AT2

CSI_CPU1_CPU0_DP11

AU3

CSI_CPU1_CPU0_DP12

AW3

CSI_CPU1_CPU0_DP13

AU6

CSI_CPU1_CPU0_DP14

AY5

CSI_CPU1_CPU0_DP15

BA6

CSI_CPU1_CPU0_DP16

AW5

CSI_CPU1_CPU0_DP17

BA8

CSI_CPU1_CPU0_DP18

AW7

CSI_CPU1_CPU0_DP19

AV8

CSI_CPU0_CPU1_DP[19..0] 12

CSI_CPU0_CPU1_DN[19..0] 12

CSI_CPU1_CPU0_DN[19..0] 12

CSI_CPU1_CPU0_DP[19..0] 12

3

CSI_CPU0_CPU1_CLK_DP 12

CSI_CPU0_CPU1_CLK_DN 12

CSI_CPU1_CPU0_CLK_DN 12

CSI_CPU1_CPU0_CLK_DP 12

CSI_CPU0_CMP1 10CSI_CPU0_CMP010

+3.3V +12V

C748 0.1u_0402C748 0.1u_0402

M_A_PAR_ERR_N117

M_A_PAR_ERR_N016

EMI

2

CPU0B

CPU0B

Gainstown

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ59

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ50

M_A_DQ49

M_A_DQ48

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ38

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ28

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ22

M_A_DQ21

M_A_DQ20

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ10

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ6

M_A_DQ5

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ0

M_A_ECC7

M_A_ECC6

M_A_ECC5

M_A_ECC4

M_A_ECC3

M_A_ECC2

M_A_ECC1

M_A_ECC0

M_A_MA_PAR16,17

M_A_ODT317

M_A_ODT217

M_A_ODT116

M_A_ODT016

M_A_MA_PAR

M_A_PAR_ERR_N1

M_A_PAR_ERR_N0

M_A_ODT3

M_A_ODT2

M_A_ODT1

M_A_ODT0

W4

DDR0_DQ<63>

V4

DDR0_DQ<62>

U3

DDR0_DQ<61>

U1

DDR0_DQ<60>

Y3

DDR0_DQ<59>

Y2

DDR0_DQ<58>

V1

DDR0_DQ<57>

U4

DDR0_DQ<56>

T3

DDR0_DQ<55>

R4

DDR0_DQ<54>

N3

DDR0_DQ<53>

M3

DDR0_DQ<52>

T2

DDR0_DQ<51>

T1

DDR0_DQ<50>

N2

DDR0_DQ<49>

N1

DDR0_DQ<48>

L2

DDR0_DQ<47>

L3

DDR0_DQ<46>

H3

DDR0_DQ<45>

G1

DDR0_DQ<44>

M1

DDR0_DQ<43>

L1

DDR0_DQ<42>

H1

DDR0_DQ<41>

H2

DDR0_DQ<40>

F2

DDR0_DQ<39>

F3

DDR0_DQ<38>

C6

DDR0_DQ<37>

B6

DDR0_DQ<36>

G3

DDR0_DQ<35>

F1

DDR0_DQ<34>

C4

DDR0_DQ<33>

B5

DDR0_DQ<32>

B38

DDR0_DQ<31>

C38

DDR0_DQ<30>

D42

DDR0_DQ<29>

D41

DDR0_DQ<28>

D37

DDR0_DQ<27>

A38

DDR0_DQ<26>

C41

DDR0_DQ<25>

D40

DDR0_DQ<24>

F42

DDR0_DQ<23>

F43

DDR0_DQ<22>

J41

DDR0_DQ<21>

J42

DDR0_DQ<20>

E43

DDR0_DQ<19>

E42

DDR0_DQ<18>

H43

DDR0_DQ<17>

H41

DDR0_DQ<16>

L42

DDR0_DQ<15>

L43

DDR0_DQ<14>

P41

DDR0_DQ<13>

P42

DDR0_DQ<12>

K43

DDR0_DQ<11>

K42

DDR0_DQ<10>

N43

DDR0_DQ<9>

N41

DDR0_DQ<8>

T42

DDR0_DQ<7>

U41

DDR0_DQ<6>

W42

DDR0_DQ<5>

W40

DDR0_DQ<4>

R42

DDR0_DQ<3>

R43

DDR0_DQ<2>

V41

DDR0_DQ<1>

W41

DDR0_DQ<0>

C34

DDR0_ECC<7>

B34

DDR0_ECC<6>

A37

DDR0_ECC<5>

C37

DDR0_ECC<4>

C33

DDR0_ECC<3>

F32

DDR0_ECC<2>

A36

DDR0_ECC<1>

C36

DDR0_ECC<0>

B20

DDR0_MA_PAR

A27

DDR0_PAR_ERR_N<2>

B28

DDR0_PAR_ERR_N<1>

D25

DDR0_PAR_ERR_N<0>

C7

DDR0_ODT<3>

B11

DDR0_ODT<2>

C9

DDR0_ODT<1>

F12

DDR0_ODT<0>

M_A_DQ[63..0]16,17

M_A_ECC[7..0]16,17

Gainstown

DDR0_CS_N7_DDR_ODT<5>

DDR0_CS_N6_DDR_ODT<4>

2/10

2/10

Gainstown

Gainstown

M_A_DQ[63..0]

M_A_ECC[7..0]

DDR0_DQS_P<17>

DDR0_DQS_P<16>

DDR0_DQS_P<15>

DDR0_DQS_P<14>

DDR0_DQS_P<13>

DDR0_DQS_P<12>

DDR0_DQS_P<11>

DDR0_DQS_P<10>

DDR0_DQS_P<9>

DDR0_DQS_P<8>

DDR0_DQS_P<7>

DDR0_DQS_P<6>

DDR0_DQS_P<5>

DDR0_DQS_P<4>

DDR0_DQS_P<3>

DDR0_DQS_P<2>

DDR0_DQS_P<1>

DDR0_DQS_P<0>

DDR0_DQS_N<17>

DDR0_DQS_N<16>

DDR0_DQS_N<15>

DDR0_DQS_N<14>

DDR0_DQS_N<13>

DDR0_DQS_N<12>

DDR0_DQS_N<11>

DDR0_DQS_N<10>

DDR0_DQS_N<9>

DDR0_DQS_N<8>

DDR0_DQS_N<7>

DDR0_DQS_N<6>

DDR0_DQS_N<5>

DDR0_DQS_N<4>

DDR0_DQS_N<3>

DDR0_DQS_N<2>

DDR0_DQS_N<1>

DDR0_DQS_N<0>

DDR0_MA<15>

DDR0_MA<14>

DDR0_MA<13>

DDR0_MA<12>

DDR0_MA<11>

DDR0_MA<10>

DDR0_MA<9>

DDR0_MA<8>

DDR0_MA<7>

DDR0_MA<6>

DDR0_MA<5>

DDR0_MA<4>

DDR0_MA<3>

DDR0_MA<2>

DDR0_MA<1>

DDR0_MA<0>

DDR0_BA<2>

DDR0_BA<1>

DDR0_BA<0>

DDR0_CLK_P<3>

DDR0_CLK_P<2>

DDR0_CLK_P<1>

DDR0_CLK_P<0>

DDR0_CLK_N<3>

DDR0_CLK_N<2>

DDR0_CLK_N<1>

DDR0_CLK_N<0>

DDR0_CS_N<5>

DDR0_CS_N<4>

DDR0_CS_N<3>

DDR0_CS_N<2>

DDR0_CS_N<1>

DDR0_CS_N<0>

DDR0_CKE<3>

DDR0_CKE<2>

DDR0_CKE<1>

DDR0_CKE<0>

DDR0_WE_N

DDR0_RAS_N

DDR0_CAS_N

DDR0_RESET_N

B36

V2

P2

J2

D5

D39

H42

N42

V43

D34

W2

R2

K2

E3

B39

F41

L41

T43

B35

V3

P1

J1

D4

C39

G43

M43

V42

D35

W1

R3

K3

E4

B40

G41

M41

U43

B29

A28

A10

B26

A26

B19

C26

B25

A25

C24

B24

B23

D24

C23

B21

A20

C28

A16

B16

E20

F18

D19

J19

E19

E18

C19

K19

B8

C11

A7

B15

B9

C13

B10

G15

B31

B30

A30

C29

B13

A15

C12

D32

M_A_DQS_DP17

M_A_DQS_DP16

M_A_DQS_DP15

M_A_DQS_DP14

M_A_DQS_DP13

M_A_DQS_DP12

M_A_DQS_DP11

M_A_DQS_DP10

M_A_DQS_DP9

M_A_DQS_DP8

M_A_DQS_DP7

M_A_DQS_DP6

M_A_DQS_DP5

M_A_DQS_DP4

M_A_DQS_DP3

M_A_DQS_DP2

M_A_DQS_DP1

M_A_DQS_DP0

M_A_DQS_DN17

M_A_DQS_DN16

M_A_DQS_DN15

M_A_DQS_DN14

M_A_DQS_DN13

M_A_DQS_DN12

M_A_DQS_DN11

M_A_DQS_DN10

M_A_DQS_DN9

M_A_DQS_DN8

M_A_DQS_DN7

M_A_DQS_DN6

M_A_DQS_DN5

M_A_DQS_DN4

M_A_DQS_DN3

M_A_DQS_DN2

M_A_DQS_DN1

M_A_DQS_DN0

M_A_MA15

M_A_MA14

M_A_MA13

M_A_MA12

M_A_MA11

M_A_MA10

M_A_MA9

M_A_MA8

M_A_MA7

M_A_MA6

M_A_MA5

M_A_MA4

M_A_MA3

M_A_MA2

M_A_MA1

M_A_MA0

M_A_BA2

M_A_BA1

M_A_BA0

M_A_CK_DP3

M_A_CK_DP2

M_A_CK_DP1

M_A_CK_DP0

M_A_CK_DN3

M_A_CK_DN2

M_A_CK_DN1

M_A_CK_DN0

M_A_CS_N7

M_A_CS_N6

M_A_CS_N5

M_A_CS_N4

M_A_CS_N3

M_A_CS_N2

M_A_CS_N1

M_A_CS_N0

M_A_CKE3

M_A_CKE2

M_A_CKE1

M_A_CKE0

M_A_WE_N

M_A_RAS_N

M_A_CAS_N

M_A_RESET_N

1

M_A_DQS_DP[17..0] 16,17

M_A_DQS_DN[17..0] 16,17

M_A_MA[15..0] 16,17

M_A_BA[2..0] 16,17

M_A_CK_DP3 17

M_A_CK_DP2 16

M_A_CK_DP1 17

M_A_CK_DP0 16

M_A_CK_DN3 17

M_A_CK_DN2 16

M_A_CK_DN1 17

M_A_CK_DN0 16

M_A_CS_N7 17

M_A_CS_N6 17

M_A_CS_N5 17

M_A_CS_N4 17

M_A_CS_N3 16

M_A_CS_N2 16

M_A_CS_N1 16

M_A_CS_N0 16

M_A_CKE3 17

M_A_CKE2 16

M_A_CKE1 17

M_A_CKE0 16

M_A_WE_N 16,17

M_A_RAS_N 16,17

M_A_CAS_N 16,17

M_A_RESET_N 16,17

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-91C1

MS-91C1

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, November 27, 2008

Date:

Thursday, November 27, 2008

Date:

5

4

3

2

Thursday, November 27, 2008

MS-91C1

08_CPU0(1/4) CSI / DDR3_A

08_CPU0(1/4) CSI / DDR3_A

08_CPU0(1/4) CSI / DDR3_A

1

Sheet of

Sheet of

Sheet of

0A

0A

0A

874

874

874

Page 9

5

CPU0C

CPU0C

Gainstown

M_B_DQ63

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

D D

C C

B B

M_B_MA_PAR18,19

M_B_PAR_ERR_N119

M_B_PAR_ERR_N018

M_B_ODT319

M_B_ODT219

M_B_ODT118

M_B_ODT018

A A

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ48

M_B_DQ47

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ0

M_B_ECC7

M_B_ECC6

M_B_ECC5

M_B_ECC4

M_B_ECC3

M_B_ECC2

M_B_ECC1

M_B_ECC0

M_B_MA_PAR

M_B_PAR_ERR_N1

M_B_PAR_ERR_N0

M_B_ODT3

M_B_ODT2

M_B_ODT1

M_B_ODT0

W9

DDR1_DQ<63>

AA7

DDR1_DQ<62>

W5

DDR1_DQ<61>

V9

DDR1_DQ<60>

W10

DDR1_DQ<59>

Y10

DDR1_DQ<58>

W7

DDR1_DQ<57>

W6

DDR1_DQ<56>

R7

DDR1_DQ<55>

R8

DDR1_DQ<54>

M6

DDR1_DQ<53>

J4

DDR1_DQ<52>

T5

DDR1_DQ<51>

R5

DDR1_DQ<50>

K5

DDR1_DQ<49>

K4

DDR1_DQ<48>

J5

DDR1_DQ<47>

G5

DDR1_DQ<46>

H9

DDR1_DQ<45>

G9

DDR1_DQ<44>

H4

DDR1_DQ<43>

G4

DDR1_DQ<42>

J6

DDR1_DQ<41>

H8

DDR1_DQ<40>

F6

DDR1_DQ<39>

D6

DDR1_DQ<38>

G8

DDR1_DQ<37>

F10

DDR1_DQ<36>

F5

DDR1_DQ<35>

E5

DDR1_DQ<34>

E8

DDR1_DQ<33>

E9

DDR1_DQ<32>

K30

DDR1_DQ<31>

L32

DDR1_DQ<30>

H34

DDR1_DQ<29>

J34

DDR1_DQ<28>

J32

DDR1_DQ<27>

K32

DDR1_DQ<26>

L33

DDR1_DQ<25>

H33

DDR1_DQ<24>

H36

DDR1_DQ<23>

J36

DDR1_DQ<22>

M36

DDR1_DQ<21>

N34

DDR1_DQ<20>

J35

DDR1_DQ<19>

K35

DDR1_DQ<18>

M34

DDR1_DQ<17>

M35

DDR1_DQ<16>

N38

DDR1_DQ<15>

N37

DDR1_DQ<14>

R35

DDR1_DQ<13>

R34

DDR1_DQ<12>

N39

DDR1_DQ<11>

P39

DDR1_DQ<10>

P35

DDR1_DQ<9>

P34

DDR1_DQ<8>

Y39

DDR1_DQ<7>

Y40

DDR1_DQ<6>

AB36

DDR1_DQ<5>

AA35

DDR1_DQ<4>

Y34

DDR1_DQ<3>

Y35

DDR1_DQ<2>

AA36

DDR1_DQ<1>

AA37

DDR1_DQ<0>

G35

DDR1_ECC<7>

E34

DDR1_ECC<6>

F37

DDR1_ECC<5>

E37

DDR1_ECC<4>

G36

DDR1_ECC<3>

E33

DDR1_ECC<2>

F36

DDR1_ECC<1>

D36

DDR1_ECC<0>

D20

DDR1_MA_PAR

F25

DDR1_PAR_ERR_N<2>

E25

DDR1_PAR_ERR_N<1>

C22

DDR1_PAR_ERR_N<0>

F11

DDR1_ODT<3>

D14

DDR1_ODT<2>

C8

DDR1_ODT<1>

D11

DDR1_ODT<0>

Gainstown

DDR1_CS_N7_DDR_ODT<5>

DDR1_CS_N6_DDR_ODT<4>

3/10

3/10

Gainstown

Gainstown

4

DDR1_DQS_P<17>

DDR1_DQS_P<16>

DDR1_DQS_P<15>

DDR1_DQS_P<14>

DDR1_DQS_P<13>

DDR1_DQS_P<12>

DDR1_DQS_P<11>

DDR1_DQS_P<10>

DDR1_DQS_P<9>

DDR1_DQS_P<8>

DDR1_DQS_P<7>

DDR1_DQS_P<6>

DDR1_DQS_P<5>

DDR1_DQS_P<4>

DDR1_DQS_P<3>

DDR1_DQS_P<2>

DDR1_DQS_P<1>

DDR1_DQS_P<0>

DDR1_DQS_N<17>

DDR1_DQS_N<16>

DDR1_DQS_N<15>

DDR1_DQS_N<14>

DDR1_DQS_N<13>

DDR1_DQS_N<12>

DDR1_DQS_N<11>

DDR1_DQS_N<10>

DDR1_DQS_N<9>

DDR1_DQS_N<8>

DDR1_DQS_N<7>

DDR1_DQS_N<6>

DDR1_DQS_N<5>

DDR1_DQS_N<4>

DDR1_DQS_N<3>

DDR1_DQS_N<2>

DDR1_DQS_N<1>

DDR1_DQS_N<0>

DDR0_MA<15>

DDR0_MA<14>

DDR0_MA<13>

DDR0_MA<12>

DDR1_MA<11>

DDR1_MA<10>

DDR1_MA<9>

DDR1_MA<8>

DDR1_MA<7>

DDR1_MA<6>

DDR1_MA<5>

DDR1_MA<4>

DDR1_MA<3>

DDR1_MA<2>

DDR1_MA<1>

DDR1_MA<0>

DDR1_BA<2>

DDR1_BA<1>

DDR1_BA<0>

DDR1_CLK_P<3>

DDR1_CLK_P<2>

DDR1_CLK_P<1>

DDR1_CLK_P<0>

DDR1_CLK_N<3>

DDR1_CLK_N<2>

DDR1_CLK_N<1>

DDR1_CLK_N<0>

DDR1_CS_N<5>

DDR1_CS_N<4>

DDR1_CS_N<3>

DDR1_CS_N<2>

DDR1_CS_N<1>

DDR1_CS_N<0>

DDR1_CKE<3>

DDR1_CKE<2>

DDR1_CKE<1>

DDR1_CKE<0>

DDR1_WE_N

DDR1_RAS_N

DDR1_CAS_N

DDR1_RESET_N

F35

Y4

M5

H7

F8

K34

L37

P36

AA40

G33

Y8

L6

H6

E7

L30

L35

R38

Y38

E35

Y5

M4

J7

F7

K33

K37

P37

AA41

G34

Y9

L5

G6

D7

L31

L36

R37

Y37

F26

H26

B14

E24

E23

H14

G24

E22

D22

J27

F22

K28

L28

J17

J16

J14

H27

K13

C18

H18

K18

G19

C21

H19

L18

G20

D21

E12

C14

E10

C17

E13

E15

A8

D12

C27

D27

E27

H28

G13

G14

E14

D29

M_B_DQS_DP17

M_B_DQS_DP16

M_B_DQS_DP15

M_B_DQS_DP14

M_B_DQS_DP13

M_B_DQS_DP12

M_B_DQS_DP11

M_B_DQS_DP10

M_B_DQS_DP9

M_B_DQS_DP8

M_B_DQS_DP7

M_B_DQS_DP6

M_B_DQS_DP5

M_B_DQS_DP4

M_B_DQS_DP3

M_B_DQS_DP2

M_B_DQS_DP1

M_B_DQS_DP0

M_B_DQS_DN17

M_B_DQS_DN16

M_B_DQS_DN15

M_B_DQS_DN14

M_B_DQS_DN13

M_B_DQS_DN12

M_B_DQS_DN11

M_B_DQS_DN10

M_B_DQS_DN9

M_B_DQS_DN8

M_B_DQS_DN7

M_B_DQS_DN6

M_B_DQS_DN5

M_B_DQS_DN4

M_B_DQS_DN3

M_B_DQS_DN2

M_B_DQS_DN1

M_B_DQS_DN0

M_B_MA15

M_B_MA14

M_B_MA13

M_B_MA12

M_B_MA11

M_B_MA10

M_B_MA9

M_B_MA8

M_B_MA7

M_B_MA6

M_B_MA5

M_B_MA4

M_B_MA3

M_B_MA2

M_B_MA1

M_B_MA0

M_B_BA2

M_B_BA1

M_B_BA0

M_B_CK_DP3

M_B_CK_DP2

M_B_CK_DP1

M_B_CK_DP0

M_B_CK_DN3

M_B_CK_DN2

M_B_CK_DN1

M_B_CK_DN0

M_B_CS_N7

M_B_CS_N6

M_B_CS_N5

M_B_CS_N4

M_B_CS_N3

M_B_CS_N2

M_B_CS_N1

M_B_CS_N0

M_B_CKE3

M_B_CKE2

M_B_CKE1

M_B_CKE0

M_B_WE_N

M_B_RAS_N

M_B_CAS_N

M_B_RESET_N

M_B_DQS_DP[17..0] 18,19

M_B_DQS_DN[17..0] 18,19

M_B_MA[15..0] 18,19

M_B_BA[2..0] 18,19

M_B_CK_DP3 19

M_B_CK_DP2 18

M_B_CK_DP1 19

M_B_CK_DP0 18

M_B_CK_DN3 19

M_B_CK_DN2 18

M_B_CK_DN1 19

M_B_CK_DN0 18

M_B_CS_N7 19

M_B_CS_N6 19

M_B_CS_N5 19

M_B_CS_N4 19

M_B_CS_N3 18

M_B_CS_N2 18

M_B_CS_N1 18

M_B_CS_N0 18

M_B_CKE3 19

M_B_CKE2 18

M_B_CKE1 19

M_B_CKE0 18

M_B_WE_N 18,19

M_B_RAS_N 18,19

M_B_CAS_N 18,19

M_B_RESET_N 18,19

M_B_DQ[63..0]18,19

M_B_ECC[7..0]18,19

M_C_DQ[63..0]20,21

M_C_ECC[7..0]20,21

3

M_C_PAR_ERR_N121

M_C_PAR_ERR_N020

M_B_DQ[63..0]

M_B_ECC[7..0]

M_C_DQ[63..0]

M_C_ECC[7..0]

2

CPU0D

CPU0D

Gainstown

M_C_DQ63

M_C_DQ62

M_C_DQ61

M_C_DQ60

M_C_DQ59

M_C_DQ58

M_C_DQ57

M_C_DQ56

M_C_DQ55

M_C_DQ54

M_C_DQ53

M_C_DQ52

M_C_DQ51

M_C_DQ50

M_C_DQ49

M_C_DQ48

M_C_DQ47

M_C_DQ46

M_C_DQ45

M_C_DQ44

M_C_DQ43

M_C_DQ42

M_C_DQ41

M_C_DQ40

M_C_DQ39

M_C_DQ38

M_C_DQ37

M_C_DQ36

M_C_DQ35

M_C_DQ34

M_C_DQ33

M_C_DQ32

M_C_DQ31

M_C_DQ30

M_C_DQ29

M_C_DQ28

M_C_DQ27

M_C_DQ26

M_C_DQ25

M_C_DQ24

M_C_DQ23

M_C_DQ22

M_C_DQ21

M_C_DQ20

M_C_DQ19

M_C_DQ18

M_C_DQ17

M_C_DQ16

M_C_DQ15

M_C_DQ14

M_C_DQ13

M_C_DQ11

M_C_DQ10

M_C_DQ9

M_C_DQ8

M_C_DQ7

M_C_DQ6

M_C_DQ5

M_C_DQ4

M_C_DQ3

M_C_DQ2

M_C_DQ1

M_C_DQ0

M_C_ECC7

M_C_ECC6

M_C_ECC5

M_C_ECC4

M_C_ECC3

M_C_ECC2

M_C_ECC1

M_C_ECC0

M_C_MA_PAR20,21

M_C_ODT321

M_C_ODT221

M_C_ODT120

M_C_ODT020

M_C_MA_PAR

M_C_PAR_ERR_N1

M_C_PAR_ERR_N0

M_C_ODT3

M_C_ODT2

M_C_ODT1

M_C_ODT0

U9

DDR2_DQ<63>

V8

DDR2_DQ<62>

T7

DDR2_DQ<61>

T6

DDR2_DQ<60>

U10

DDR2_DQ<59>

T10

DDR2_DQ<58>

U6

DDR2_DQ<57>

U5

DDR2_DQ<56>

R9

DDR2_DQ<55>

R10

DDR2_DQ<54>

N7

DDR2_DQ<53>

N8

DDR2_DQ<52>

P10

DDR2_DQ<51>

P9

DDR2_DQ<50>

N6

DDR2_DQ<49>

P7

DDR2_DQ<48>

M8

DDR2_DQ<47>

L8

DDR2_DQ<46>

M10

DDR2_DQ<45>

L11

DDR2_DQ<44>

N9

DDR2_DQ<43>

M9

DDR2_DQ<42>

K10

DDR2_DQ<41>

L10

DDR2_DQ<40>

L12

DDR2_DQ<39>

H12

DDR2_DQ<38>

G10

DDR2_DQ<37>

G11

DDR2_DQ<36>

L13

DDR2_DQ<35>

H13

DDR2_DQ<34>

J12

DDR2_DQ<33>

K12

DDR2_DQ<32>

E38

DDR2_DQ<31>

F38

DDR2_DQ<30>

G39

DDR2_DQ<29>

H39

DDR2_DQ<28>

H37

DDR2_DQ<27>

J37

DDR2_DQ<26>

F40

DDR2_DQ<25>

G40

DDR2_DQ<24>

K38

DDR2_DQ<23>

L40

DDR2_DQ<22>

N36

DDR2_DQ<21>

P40

DDR2_DQ<20>

J39

DDR2_DQ<19>

J40

DDR2_DQ<18>

M40

DDR2_DQ<17>

M39

DDR2_DQ<16>

R40

DDR2_DQ<15>

T41

DDR2_DQ<14>

V39

DDR2_DQ<13>

W39

DDR2_DQ<12>

T36

DDR2_DQ<11>

R39

DDR2_DQ<10>

U39

DDR2_DQ<9>

U38

DDR2_DQ<8>

V38

DDR2_DQ<7>

V37

DDR2_DQ<6>

V34

DDR2_DQ<5>

U34

DDR2_DQ<4>

U36

DDR2_DQ<3>

V36

DDR2_DQ<2>

W35

DDR2_DQ<1>

W34

DDR2_DQ<0>

F30

DDR2_ECC<7>

F31

DDR2_ECC<6>

J30

DDR2_ECC<5>

J31

DDR2_ECC<4>

E30

DDR2_ECC<3>

E29

DDR2_ECC<2>

F33

DDR2_ECC<1>

H32

DDR2_ECC<0>

B18

DDR2_MA_PAR

F23

DDR2_PAR_ERR_N<2>

J25

DDR2_PAR_ERR_N<1>

F21

DDR2_PAR_ERR_N<0>

D10

DDR2_ODT<3>

D15

DDR2_ODT<2>

F13

DDR2_ODT<1>

L16

DDR2_ODT<0>

Gainstown

DDR2_CS_N7_DDR2_ODT<5>

DDR2_CS_N6_DDR2_ODT<4>

4/10

4/10

Gainstown

Gainstown

DDR1_DQS_P<17>

DDR1_DQS_P<16>

DDR1_DQS_P<15>

DDR1_DQS_P<14>

DDR1_DQS_P<13>

DDR1_DQS_P<12>

DDR2_DQS_P<11>

DDR2_DQS_P<10>

DDR2_DQS_P<9>

DDR2_DQS_P<8>

DDR2_DQS_P<7>

DDR2_DQS_P<6>

DDR2_DQS_P<5>

DDR2_DQS_P<4>

DDR2_DQS_P<3>

DDR2_DQS_P<2>

DDR2_DQS_P<1>

DDR2_DQS_P<0>

DDR2_DQS_N<17>

DDR2_DQS_N<16>

DDR2_DQS_N<15>

DDR2_DQS_N<14>

DDR2_DQS_N<13>

DDR2_DQS_N<12>

DDR2_DQS_N<11>

DDR2_DQS_N<10>

DDR2_DQS_N<9>

DDR2_DQS_N<8>

DDR2_DQS_N<7>

DDR2_DQS_N<6>

DDR2_DQS_N<5>

DDR2_DQS_N<4>

DDR2_DQS_N<3>

DDR2_DQS_N<2>

DDR2_DQS_N<1>

DDR2_DQS_N<0>

DDR0_MA<15>

DDR0_MA<14>

DDR0_MA<13>

DDR0_MA<12>

DDR2_MA<11>

DDR2_MA<10>

DDR2_MA<9>

DDR2_MA<8>

DDR2_MA<7>

DDR2_MA<6>

DDR2_MA<5>

DDR2_MA<4>

DDR2_MA<3>

DDR2_MA<2>

DDR2_MA<1>

DDR2_MA<0>

DDR2_BA<2>

DDR2_BA<1>

DDR2_BA<0>

DDR2_CLK_P<3>

DDR2_CLK_P<2>

DDR2_CLK_P<1>

DDR2_CLK_P<0>

DDR2_CLK_N<3>

DDR2_CLK_N<2>

DDR2_CLK_N<1>

DDR2_CLK_N<0>

DDR2_CS_N<5>

DDR2_CS_N<4>

DDR2_CS_N<3>

DDR2_CS_N<2>

DDR2_CS_N<1>

DDR2_CS_N<0>

DDR2_CKE<3>

DDR2_CKE<2>

DDR2_CKE<1>

DDR2_CKE<0>

DDR2_WE_N

DDR2_RAS_N

DDR2_CAS_N

DDR2_RESET_N

H31

V6

N4

K9

H11

H38

M38

U40

U35

G29

U8

P6

L7

J10

E39

K40

T37

W37

G31

V7

P4

K8

J11

G38

L38

T40

T35

G30

T8

P5

K7

J9

E40

K39

T38

W36

G25

H24

F15

G23

H23

H17

H22

L25

J24

K22

K23

F20

J20

G18

K17

A18

L26

F17

A17

L22

H21

L20

J22

L21

G21

K20

J21

J15

L17

D9

E17

H16

D16

K14

G16

L27

D26

G26

J26

C16

D17

F16

E32

M_C_DQS_DP17

M_C_DQS_DP16

M_C_DQS_DP15

M_C_DQS_DP14

M_C_DQS_DP13

M_C_DQS_DP12

M_C_DQS_DP11

M_C_DQS_DP10

M_C_DQS_DP9

M_C_DQS_DP8

M_C_DQS_DP7

M_C_DQS_DP6

M_C_DQS_DP5

M_C_DQS_DP4

M_C_DQS_DP3

M_C_DQS_DP2

M_C_DQS_DP1

M_C_DQS_DP0

M_C_DQS_DN17

M_C_DQS_DN16

M_C_DQS_DN15

M_C_DQS_DN14

M_C_DQS_DN13

M_C_DQS_DN12

M_C_DQS_DN11

M_C_DQS_DN10

M_C_DQS_DN9

M_C_DQS_DN8

M_C_DQS_DN7

M_C_DQS_DN6

M_C_DQS_DN5

M_C_DQS_DN4

M_C_DQS_DN3

M_C_DQS_DN2

M_C_DQS_DN1

M_C_DQS_DN0

M_C_MA15

M_C_MA14

M_C_MA13

M_C_MA12

M_C_MA11

M_C_MA10

M_C_MA9

M_C_MA8

M_C_MA7

M_C_MA6

M_C_MA5

M_C_MA4

M_C_MA3

M_C_MA2M_C_DQ12

M_C_MA1

M_C_MA0

M_C_BA2

M_C_BA1

M_C_BA0

M_C_CK_DP3

M_C_CK_DP2

M_C_CK_DP1

M_C_CK_DP0

M_C_CK_DN3

M_C_CK_DN2

M_C_CK_DN1

M_C_CK_DN0

M_C_CS_N7

M_C_CS_N6

M_C_CS_N5

M_C_CS_N4

M_C_CS_N3

M_C_CS_N2

M_C_CS_N1

M_C_CS_N0

M_C_CKE3

M_C_CKE2

M_C_CKE1

M_C_CKE0

M_C_WE_N

M_C_RAS_N

M_C_CAS_N

M_C_RESET_N

M_C_DQS_DP[17..0] 20,21

M_C_DQS_DN[17..0] 20,21

M_C_MA[15..0] 20,21

M_C_BA[2..0] 20,21

M_C_CK_DP3 21

M_C_CK_DP2 20

M_C_CK_DP1 21

M_C_CK_DP0 20

M_C_CK_DN3 21

M_C_CK_DN2 20

M_C_CK_DN1 21

M_C_CK_DN0 20

M_C_CS_N7 21

M_C_CS_N6 21

M_C_CS_N5 21

M_C_CS_N4 21

M_C_CS_N3 20

M_C_CS_N2 20

M_C_CS_N1 20

M_C_CS_N0 20

M_C_CKE3 21

M_C_CKE2 20

M_C_CKE1 21

M_C_CKE0 20

M_C_WE_N 20,21

M_C_RAS_N 20,21

M_C_CAS_N 20,21

M_C_RESET_N 20,21

1

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-91C1

MS-91C1

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, November 27, 2008

Date:

Thursday, November 27, 2008

Date:

5

4

3

2

Thursday, November 27, 2008

MS-91C1

09_CPU0(2/4) DDR3_B & C

09_CPU0(2/4) DDR3_B & C

09_CPU0(2/4) DDR3_B & C

1

Sheet of

Sheet of

Sheet of

0A

0A

0A

974

974

974

Page 10

5

4

3

2

1

PECI_CPU14,62,70

VID_CPU0[7..0]

close to CPU0

R585 100_1%R585 100_1%

RST_CPU_RESET_N

CSI_CATERR_N

CSI_CPU0_THERMTRIP_N

CSI_CPU0_PRCHT_N

CSI_CPU0_SKTOCC_N

IRQ_CPU0_RDIMM_EVENT_N

CSI_CPU0_CMPSTH

M_CPU0_DDR_COMP[2]

M_CPU0_DDR_COMP[1]

M_CPU0_DDR_COMP[0]

PECI_CPU

FM_PECI_CPU0_ID

CLK_133M_CPU0_DP

CLK_133M_CPU0_DN

CLK_133M_CPU0_ITP_DP

CLK_133M_CPU0_ITP_DN

R1188 0RR1188 0R

PWRGD_CPU0_VDD_GTL

PWRGD_CPU0_VTT_GTL

CPU0_VTT_VID

FM_CPU0_PSI_N

P1V5_DDR3_VREF_CPU0

PV_VTT_VREF_CPU0

VR_CPU0_IOUT

VSENSE_DIE_CPU0_P

VSENSE_DIE_CPU0_N

VSENSE_DIE_CPU0_VTT_P

VSENSE_DIE_CPU0_VTT_N

XDP_CPU0_PRDY_N

XDP_CPU0_PREQ_N

XDP_CPU0_MBP_N7

XDP_CPU0_MBP_N6

XDP_CPU0_MBP_N5

XDP_CPU0_MBP_N4

XDP_CPU0_MBP_N3

XDP_CPU0_MBP_N2

XDP_CPU0_MBP_N1

XDP_CPU0_MBP_N0

JTAG_CPU_TRST_N

JTAG_CPU_TCLK

JTAG_CPU_TMS

JTAG_CPU0_TDI

JTAG_CPU0_TDO

RST_CPU_RESET_N

CSI_CATERR_N

VID_CPU07

VID_CPU06

VID_CPU05

VID_CPU04

VID_CPU03

VID_CPU02

VID_CPU01

VID_CPU00

R593 X_49.9_1%R593 X_49.9_1%

R596 75R_0402R596 75R_0402

+1.1V_CPU0

AL39

AC37

AG37

AG35

AG36

AB5

AB41

AC1

Y7

AA8

AH36

AK35

AJ35

AH35

AA5

AA4

AR7

AA6

AB35

AN8

AP8

AP9

AN10

AM10

AN9

AL9

AL10

AV6

AP7

L23

AJ37

AK8

AR9

AR8

AE36

AE37

AF10

B41

C42

E2

D2

C3

D1

B4

C2

A5

B3

AH9

AH10

AG10

AJ9

AJ10

+1.1V_CPU0

RESET_N

CAT_ERR_N

THERMTRIP_N

PROCHOT_N

SKTOCC_N

DDR_THERM_N

COMP0

DDR_COMP<2>

DDR_COMP<1>

DDR_COMP<0>

PECI

PECI_ID

BCLK_DP

BCLK_DN

BCLK_ITP_DP

BCLK_ITP_DN

VCCPWRGOOD

VDDPWRGOOD

VTTPWRGOOD

VID<7>

VID<6>

VID5_CSC<2>

VID4_CSC<1>

VID3_CSC<0>

VID2_MSID<2>

VID1_MSID<1>

VID0_MSID<0>

VTT_VID

PSI_N

DDR_VREF

GTLREF

ISENSE

VCC_SENSE

VSS_SENSE

VTTD_SENSE

VSS_SENSE_VTTD

DBR_N

PRDY_N

PREQ_N

BPM_N<7>

BPM_N<6>

BPM_N<5>

BPM_N<4>

BPM_N<3>

BPM_N<2>

BPM_N<1>

BPM_N<0>

TRST_N

TCK

TMS

TDI

TDO

C603

C603

0.1u_0402

0.1u_0402

CPU0E

CPU0E

Gainstown

Gainstown

5/10

5/10

Gainstown

Gainstown

FM_PECI_CPU0_ID

RSVD<66>

RSVD<65>

RSVD<64>

RSVD<63>

RSVD<62>

RSVD<61>

RSVD<60>

RSVD<59>

RSVD<58>

RSVD<57>

RSVD<56>

RSVD<55>

RSVD<54>

RSVD<53>

RSVD<52>

RSVD<51>

RSVD<50>

RSVD<49>

RSVD<48>

RSVD<47>

RSVD<46>

RSVD<45>

RSVD<44>

RSVD<43>

RSVD<42>

RSVD<41>

RSVD<40>

RSVD<39>

RSVD<38>

RSVD<37>

RSVD<36>

RSVD<35>

RSVD<34>

RSVD<32>

RSVD<31>

RSVD<30>

RSVD<29>

RSVD<28>

RSVD<27>

RSVD<26>

RSVD<25>

RSVD<24>

RSVD<23>

RSVD<22>

RSVD<21>

RSVD<20>

RSVD<19>

RSVD<17>

RSVD<16>

RSVD<15>

RSVD<14>

RSVD<13>

RSVD<12>

RSVD<11>

RSVD<10>

RSVD<9>

RSVD<8>

RSVD<7>

RSVD<6>

RSVD<5>

RSVD<4>

RSVD<3>

RSVD<2>

RSVD<1>

RSVD<0>

+1.1V_CPU0

B33

F27

K25

K27

D30

K29

J29

G28

H29

E28

F28

A31

C32

C31

D31

AL3

AL38

AG1

AF1

AK7

AT5

AT4

V11

U11

A40

AL4

AL5

AL41

AL40

K24

AK36

K15

L15

AU2

BA40

AY40

AW41

AY41

AW42

AV43

AV42

AV1

AY3

AW2

AV2

AY4

BA4

AF4

AF7

AG4

AG5

AH5

AK2

AM36

AM38

AN36

AN38

AR36

AR37

AT36

AV3

AV35

AW39

AY35

AY39

R590

R590

49.9_1%

49.9_1%

R591

R591

X_49.9_1%

X_49.9_1%

+1.1V_CPU0

CPU0_VTT_VID2

XDP_CPU_TAPPWRGD

R1179 X_1K_1%R1179 X_1K_1%

CPU0_VTT_VID1

R1178

R1178

1K_1%

1K_1%

CPU0_VTT_VID2 49

CPU0_VTT_VID1 49

PWRGD_CPU0_VTT37,49,53,55,57

XDP_CPU_TAPPWRGD 14,66

+1.1V_CPU0

+5V

R581

R581

1K_1%

1K_1%

G

DS

Q61

PWRGD_CPU0_VTT

R582 0_0402R582 0_0402

+3.3VDUAL

R595 4.7K_0402R595 4.7K_0402

R1154 21_1%R1154 21_1%

R592 21_1%R592 21_1%

R584 49.9_1%_0402R584 49.9_1%_0402

R1155 130_1%R1155 130_1%

R1152 24.9_1%R1152 24.9_1%

R1147 100_1%R1147 100_1%

+1.5V_DDR3_CPU0 +1.1V_CPU0

R1124

R1124

X_100_1%

X_100_1%

R1144

R1144

C1135

C1135

X_100_1%

X_100_1%

X_0.1u_0402

X_0.1u_0402

+1.1V_CPU0

R589

R589

X_100_1%

X_100_1%

PV_VTT_VREF_CPU0

R588

R588

C605

C605

X_100_1%

X_100_1%

X_0.1u_0402

X_0.1u_0402

Q61

2N7002

2N7002

G

CSI_CPU0_SKTOCC_N

CSI_CPU0_CMP1

CSI_CPU0_CMP0

CSI_CPU0_CMPSTH

M_CPU0_DDR_COMP[2]

M_CPU0_DDR_COMP[1]

M_CPU0_DDR_COMP[0]

+1.1V_CPU0

R587

R587

100

100

PWRGD_CPU0_VTT_GTL

DS

Q60

Q60

2N7002

2N7002

CSI_CPU0_CMP1 8

CSI_CPU0_CMP0 8

R871

R871

X_1K_1%

X_1K_1%

FM_CPU0_PSI_NP1V5_DDR3_VREF_CPU0

R879

R879

X_1K_1%

X_1K_1%

CSI_CPU0_THERMTRIP_N

D D

RST_CPU_RESET_N14,29,66

CSI_CATERR_N14,59

CSI_CPU0_THERMTRIP_N59

CSI_CPU0_PRCHT_N59

CSI_CPU0_SKTOCC_N55,68

IRQ_CPU0_RDIMM_EVENT_N16,17,18,19,20,21,34

CLK_133M_CPU0_DP37

CLK_133M_CPU0_DN37

CLK_133M_CPU0_ITP_DP65

CLK_133M_CPU0_ITP_DN65

PWRGD_CPU_GTL14,35,66

PWRGD_CPU0_VDD_GTL54

VID_CPU0[7..0]47,70

C C

CPU0_VTT_VID49

FM_CPU0_PSI_N47

VR_CPU0_IOUT47

VSENSE_DIE_CPU0_P47

VSENSE_DIE_CPU0_N47

VSENSE_DIE_CPU0_VTT_P49

VSENSE_DIE_CPU0_VTT_N49

XDP_CPU0_PRDY_N66

XDP_CPU0_PREQ_N66

XDP_CPU0_MBP_N[7..0]65

B B

A A

JTAG_CPU_TRST_N14,66

JTAG_CPU_TCLK14,66

JTAG_CPU_TMS14,66

JTAG_CPU0_TDI66

JTAG_CPU0_TDO66

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-91C1

MS-91C1

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, November 27, 2008

Date:

Thursday, November 27, 2008

Date:

5

4

3

2

Thursday, November 27, 2008

MS-91C1

10_CPU0(3/4) XDP / VID

10_CPU0(3/4) XDP / VID

10_CPU0(3/4) XDP / VID

1

Sheet of

Sheet of

Sheet of

10 74

10 74

10 74

0A

0A

0A

Page 11

5

+1.5V_DDR3_CPU0 +1.1V_CPU0

CPU0F

A14

VDDQ<44>

A19

VDDQ<43>

A24

VDDQ<42>

A29

VDDQ<41>

A9

VDDQ<40>

B12

VDDQ<39>

B17

VDDQ<38>

B22

VDDQ<37>

B27

VDDQ<36>

D13

G17

G22

G27

H15

H20

H25

K16

K21

K26

M17

M27

U33

V33

W33

B32

B7

C10

C15

C20

C25

C30

D18

D23

D28

E11

E16

E21

E26

E31

F14

F19

F24

J18

J23

J28

L14

L19

L24

VDDQ<35>

VDDQ<34>

VDDQ<33>

VDDQ<32>

VDDQ<31>

VDDQ<30>

VDDQ<29>

VDDQ<28>

VDDQ<27>

VDDQ<26>

VDDQ<25>

VDDQ<24>

VDDQ<23>

VDDQ<22>

VDDQ<21>

VDDQ<20>

VDDQ<19>

VDDQ<18>

VDDQ<17>

VDDQ<16>

VDDQ<15>

VDDQ<14>

VDDQ<13>

VDDQ<12>

VDDQ<11>

VDDQ<10>

VDDQ<9>

VDDQ<8>

VDDQ<7>

VDDQ<6>

VDDQ<5>

VDDQ<4>

VDDQ<3>

VDDQ<2>

VDDQ<1>

VDDQ<0>

VCCPLL<2>

VCCPLL<1>

VCCPLL<0>

D D

C C

+1.8V_CPU0_PLL

B B

A A

CPU0F

Gainstown

Gainstown

6/10

6/10

Gainstown

Gainstown

PV_VCCP_CPU0 PV_VCCP_CPU0

AH11

VCC<209>

AH33

VCC<208>

AJ11

VCC<207>

AJ33

VCC<206>

AK11

VCC<205>

AK12

VCC<204>

AK13

VCC<203>

AK15

VCC<202>

AK16

VCC<201>

AK18

VCC<200>

AK19

VCC<199>

AK21

VCC<198>

AK24

VCC<197>

AK25

VCC<196>

AK27

VCC<195>

AK28

VCC<194>

AK30

VCC<193>

AK31

VCC<192>

AK33

VCC<191>

AL12

VCC<190>

AL13

VCC<189>

AL15

VCC<188>

AL16

VCC<187>

AL18

VCC<186>

AL19

VCC<185>

AL21

VCC<184>

AL24

VCC<183>

AL25

VCC<182>

AL27

VCC<181>

AL28

VCC<180>

AL30

VCC<179>

AL31

VCC<178>

AL33

VCC<177>

AL34

VCC<176>

AM12

VCC<175>

AM13

VCC<174>

AM15

VCC<173>

AM16

VCC<172>

AM18

VCC<171>

AM19

VCC<170>

AM21

VCC<169>

AM24

VCC<168>

AM25

VCC<167>

AM27

VCC<166>

AM28

VCC<165>

AM30

VCC<164>

AM31

VCC<163>

AM33

VCC<162>

AM34

VCC<161>

AN12

VCC<160>

AN13

VCC<159>

AN15

VCC<158>

AN16

VCC<157>

5

AF37

VTTD<25>

AA10

VTTD<24>

AA11

VTTD<23>

AA33

VTTD<22>

AB10

VTTD<21>

AB11

VTTD<20>

AB33

VTTD<19>

AB34

VTTD<18>

AB8

VTTD<17>

AB9

VTTD<16>

AC10

VTTD<15>

AC11

VTTD<14>

AC33

VTTD<13>

AC34

VTTD<12>

AC35

VTTD<11>

AD34

VTTD<10>

AD35

VTTD<9>

AD36

VTTD<8>

AD9

VTTD<7>

AE34

VTTD<6>

AE35

VTTD<5>

AE8

VTTD<4>

AE9

VTTD<3>

AF36

VTTD<2>

AF8

VTTD<1>

AF9

VTTD<0>

AG34

VTTA<7>

AF34

VTTA<6>

AF33

VTTA<5>

AF11

VTTA<4>

AE33

VTTA<3>

AE11

VTTA<2>

AE10

VTTA<1>

AD10

VTTA<0>

Gainstown

Gainstown

7/10

7/10

Gainstown

Gainstown

CPU0G

CPU0G

4

PV_VCCP_CPU0 PV_VCCP_CPU0

AT28

VCC<103>

AT30

VCC<102>

AT31

VCC<101>

AT33

VCC<100>

AT34

VCC<99>

AT9

VCC<98>

AU10

VCC<97>

AU12

VCC<96>

AU13

VCC<95>

AU15

VCC<94>

AU16

VCC<93>

AU18

VCC<92>

AU19

VCC<91>

AU21

VCC<90>

AU24

VCC<89>

AU25

VCC<88>

AU27

VCC<87>

AU28

VCC<86>

AU30

VCC<85>

AU31

VCC<84>

AU33

VCC<83>

AU34

VCC<82>

AU9

VCC<81>

AV10

VCC<80>

AV12

VCC<79>

AV13

VCC<78>

AV15

VCC<77>

AV16

VCC<76>

AV18

VCC<75>

AV19

VCC<74>

AV21

VCC<73>

AV24

VCC<72>

AV25

VCC<71>

AV27

VCC<70>

AV28

VCC<69>

AV30

VCC<68>

AV31

VCC<67>

AV33

VCC<66>

AV34

VCC<65>

AV9

VCC<64>

AW10

VCC<63>

AW12

VCC<62>

AW13

VCC<61>

AW15

VCC<60>

AW16

VCC<59>

AW18

VCC<58>

AW19

VCC<57>

AW21

VCC<56>

AW24

VCC<55>

AW25

VCC<54>

AW27

VCC<53>

AW28

VCC<52>

AN18

VCC<156>

AN19

VCC<155>

AN21

VCC<154>

AN24

VCC<153>

AN25

VCC<152>

AN27

VCC<151>

AN28

VCC<150>

AN30

VCC<149>

AN31

VCC<148>

AN33

VCC<147>

AN34

VCC<146>

AP12

VCC<145>

AP13

VCC<144>

AP15

VCC<143>

AP16

VCC<142>

AP18

VCC<141>

AP19

VCC<140>

AP21

VCC<139>

AP24

VCC<138>

AP25

VCC<137>

AP27

VCC<136>

AP28

VCC<135>

AP30

VCC<134>

AP31

VCC<133>

AP33

VCC<132>

AP34

VCC<131>

AR10

VCC<130>

AR12

VCC<129>

AR13

VCC<128>

AR15

VCC<127>

AR16

VCC<126>

AR18

VCC<125>

AR19

VCC<124>

AR21

VCC<123>

AR24

VCC<122>

AR25

VCC<121>

AR27

VCC<120>

AR28

VCC<119>

AR30

VCC<118>

AR31

VCC<117>

AR33

VCC<116>

AR34

VCC<115>

AT10

VCC<114>

AT12

VCC<113>

AT13

VCC<112>

AT15

VCC<111>

AT16

VCC<110>

AT18

VCC<109>

AT19

VCC<108>

AT21

VCC<107>

AT24

VCC<106>

AT25

VCC<105>

AT27

VCC<104>

4

CPU0H

CPU0H

Gainstown

Gainstown

8/10

8/10

Gainstown

Gainstown

VCC<51>

VCC<50>

VCC<49>

VCC<48>

VCC<47>

VCC<46>

VCC<45>

VCC<44>

VCC<43>

VCC<42>

VCC<41>

VCC<40>

VCC<39>

VCC<38>

VCC<37>

VCC<36>

VCC<35>

VCC<34>

VCC<33>

VCC<32>

VCC<31>

VCC<30>

VCC<29>

VCC<28>

VCC<27>

VCC<26>

VCC<25>

VCC<24>

VCC<23>

VCC<22>

VCC<21>

VCC<20>

VCC<19>

VCC<18>

VCC<17>

VCC<16>

VCC<15>

VCC<14>

VCC<13>

VCC<12>

VCC<11>

VCC<10>

VCC<9>

VCC<8>

VCC<7>

VCC<6>

VCC<5>

VCC<4>

VCC<3>

VCC<2>

VCC<1>

VCC<0>

+1.1V_CPU0

C1193

C1193

10u_0805

10u_0805

+1.8V_CPU0_PLL +1.5V_DDR3_CPU0

C657

C657

10u_0805

10u_0805

3

AW30

AW31

AW33

AW34

AW9

AY10

AY12

AY13

AY15

AY16

AY18

AY19

AY21

AY24

AY25

AY27

AY28

AY30

AY31

AY33

AY34

AY9

BA10

BA12

BA13

BA15

BA16

BA18

BA19

BA24

BA25

BA27

BA28

BA30

BA9

M11

M13

M15

M19

M21

M23

M25

M29

M31

M33

N11

N33

R11

R33

T11

T33

W11

9 0805 10 UF CAPS AND 2 0805 22UF CAPS AND 1 1206 47UF FOR VTTA

C672

C672

10u_0805

10u_0805

C704

C704

22u_0805

22u_0805

3

Y6

Y41

Y36

Y33

Y11

Y1

W8

W43

W38

W3

V5

V40

V35

V10

U7

U42

U37

U2

T9

T4

T39

T34

R6

R41

R36

R1

P8

P43

P38

P33

P3

P11

N5

N40

N35

N10

M7

M42

M37

M32

M30

M28

M26

M24

M22

M20

M2

M18

M16

M14

M12

L9

L4

L39

L34

L29

K6

K41

K36

K31

K11

K1

J8

J43

J38

J33

J3

J13

H5

H40

H35

H30

H10

G7

G42

G37

G32

G2

G12

C1183

C1183

10u_0805

10u_0805

C693

C693

22u_0805

22u_0805

VSS<309>

VSS<308>

VSS<307>

VSS<306>

VSS<305>

VSS<304>

VSS<303>

VSS<302>

VSS<301>

VSS<300>

VSS<299>

VSS<298>

VSS<297>

VSS<296>

VSS<295>

VSS<294>

VSS<293>

VSS<292>

VSS<291>

VSS<290>

VSS<289>

VSS<288>

VSS<287>

VSS<286>

VSS<285>

VSS<284>

VSS<283>

VSS<282>

VSS<281>

VSS<280>

VSS<279>

VSS<278>

VSS<277>

VSS<276>

VSS<275>

VSS<274>

VSS<273>

VSS<272>

VSS<271>

VSS<270>

VSS<269>

VSS<268>

VSS<267>

VSS<266>

VSS<265>

VSS<264>

VSS<263>

VSS<262>

VSS<261>

VSS<260>

VSS<259>

VSS<258>

VSS<257>

VSS<256>

VSS<255>

VSS<254>

VSS<253>

VSS<252>

VSS<251>

VSS<250>

VSS<249>

VSS<248>

VSS<247>

VSS<246>

VSS<245>

VSS<244>

VSS<243>

VSS<242>

VSS<241>

VSS<240>

VSS<239>

VSS<238>

VSS<237>

VSS<236>

VSS<235>

VSS<234>

VSS<233>

VSS<232>

VSS<231>

Gainstown

Gainstown

9/10

9/10

Gainstown

Gainstown

C1153

C1153

10u_0805

10u_0805

C680

C680

22u_0805

22u_0805

CPU0I

CPU0I

C1137

C1137

10u_0805

10u_0805

C1176

C1176

22u_0805

22u_0805

VSS<230>

VSS<229>

VSS<228>

VSS<227>

VSS<226>

VSS<225>

VSS<224>

VSS<223>

VSS<222>

VSS<221>

VSS<220>

VSS<219>

VSS<218>

VSS<217>

VSS<216>

VSS<215>

VSS<214>

VSS<213>

VSS<212>

VSS<211>

VSS<210>

VSS<209>

VSS<208>

VSS<207>

VSS<206>

VSS<205>

VSS<204>

VSS<203>

VSS<202>

VSS<201>

VSS<200>

VSS<199>

VSS<198>

VSS<197>

VSS<196>

VSS<195>

VSS<194>

VSS<193>

VSS<192>

VSS<191>

VSS<190>

VSS<189>

VSS<188>

VSS<187>

VSS<186>

VSS<185>

VSS<184>

VSS<183>

VSS<182>

VSS<181>

VSS<180>

VSS<179>

VSS<178>

VSS<177>

VSS<176>

VSS<175>

VSS<174>

VSS<173>

VSS<172>

VSS<171>

VSS<170>

VSS<169>

VSS<168>

VSS<167>

VSS<166>

VSS<165>

VSS<164>

VSS<163>

VSS<162>

VSS<161>

VSS<160>

VSS<159>

VSS<158>

VSS<157>

VSS<156>

VSS<155>

VSS<154>

VSS<153>

C1717

C1717

10u_0805

10u_0805

C1164

C1164

22u_0805

22u_0805

2

F9

F4

F39

F34

F29

E6

E41

E36

E1

D8

D43

D38

D33

D3

C5

C43

C40

C35

BA5

BA39

BA35

BA3

BA29

BA26

BA20

BA17

BA14

BA11

B42

B37

B2

AY7

AY42

AY37

AY32

AY29

AY26

AY23

AY22

AY20

AY2

AY17

AY14

AY11

AW8

AW6

AW35

AW32

AW29

AW26

AW23

AW22

AW20

AW17

AW14

AW11

AW1

AV41

AV4

AV39

AV32

AV29

AV26

AV23

AV22

AV20

AV17

AV14

AV11

AU5

AU43

AU36

AU35

AU32

AU29

AU26

AU23

AU22

C1718

C1718

10u_0805

10u_0805

C1168

C1168

22u_0805

22u_0805

2

C1719

C1719

10u_0805

10u_0805

AU20

AU17

AU14

AU11

AT41

AT38

AT35

AT32

AT29

AT26

AT23

AT22

AT20

AT17

AT14

AT11

AR39

AR35

AR32

AR29

AR26

AR23

AR22

AR20

AR17

AR14

AR11

AP43

AP37

AP36

AP35

AP32

AP29

AP26

AP23

AP22

AP20

AP17

AP14

AP11

AP10

AN41

AN37

AN35

AN32

AN29

AN26

AN23

AN22

AN20

AN17

AN14

AN11

AM39

AM37

AM35

AM32

AM29

AM26

AM23

AM22

AM20

AM17

AM14

AM11

AU1

AT8

AT7

AR3

AR2

AP6

AP5

AP1

AN7

AN3

AM9

AM5

AL7

1

CPU0J

VSS<152>

VSS<151>

VSS<150>

VSS<149>

VSS<148>

VSS<147>

VSS<146>

VSS<145>

VSS<144>

VSS<143>

VSS<142>

VSS<141>

VSS<140>

VSS<139>

VSS<138>

VSS<137>

VSS<136>

VSS<135>

VSS<134>

VSS<133>

VSS<132>

VSS<131>

VSS<130>

VSS<129>

VSS<128>

VSS<127>

VSS<126>

VSS<125>

VSS<124>

VSS<123>

VSS<122>

VSS<121>

VSS<120>

VSS<119>

VSS<118>

VSS<117>

VSS<116>

VSS<115>

VSS<114>

VSS<113>

VSS<112>

VSS<111>

VSS<110>

VSS<109>

VSS<108>

VSS<107>

VSS<106>

VSS<105>

VSS<104>

VSS<103>

VSS<102>

VSS<101>

VSS<100>

VSS<99>

VSS<98>

VSS<97>

VSS<96>

VSS<95>

VSS<94>

VSS<93>

VSS<92>

VSS<91>

VSS<90>

VSS<89>

VSS<88>

VSS<87>

VSS<86>

VSS<85>

VSS<84>

VSS<83>

VSS<82>

VSS<81>

VSS<80>

VSS<79>

VSS<78>

VSS<77>

VSS<76>

VSS<75>

C717

C717

22u_0805

22u_0805

MSI

MSI

MSI

CPU0J

Gainstown

Gainstown

10/10

10/10

Gainstown

Gainstown

C649

C1142

C1142

22u_0805

22u_0805

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Date:

Date:

C649

47u_1206

47u_1206

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-91C1

MS-91C1

MS-91C1

11_CPU0 (4/4) POWER / GND

11_CPU0 (4/4) POWER / GND

11_CPU0 (4/4) POWER / GND

Thursday, November 27, 2008

Thursday, November 27, 2008

Thursday, November 27, 2008

1

VSS<74>

VSS<73>

VSS<72>

VSS<71>

VSS<70>

VSS<69>

VSS<68>

VSS<67>

VSS<66>

VSS<65>

VSS<64>

VSS<63>

VSS<62>

VSS<61>

VSS<60>

VSS<59>

VSS<58>

VSS<57>

VSS<56>

VSS<55>

VSS<54>

VSS<53>

VSS<52>

VSS<51>

VSS<50>

VSS<49>

VSS<48>

VSS<47>

VSS<46>

VSS<45>

VSS<44>

VSS<43>

VSS<42>

VSS<41>

VSS<40>

VSS<39>

VSS<38>

VSS<37>

VSS<36>

VSS<35>

VSS<34>

VSS<33>

VSS<32>

VSS<31>

VSS<30>

VSS<29>

VSS<28>

VSS<27>

VSS<26>

VSS<25>

VSS<24>

VSS<23>

VSS<22>

VSS<21>

VSS<20>

VSS<19>

VSS<18>

VSS<17>

VSS<16>

VSS<15>

VSS<14>

VSS<13>

VSS<12>

VSS<11>

VSS<10>

VSS<9>

VSS<8>

VSS<7>

VSS<6>

VSS<5>

VSS<4>

VSS<3>

VSS<2>

VSS<1>

VSS<0>

C1720

C1720

47u_1206

47u_1206

Sheet of

Sheet of

Sheet of

AL42

AL37

AL36

AL35

AL32

AL29

AL26

AL23

AL22

AL20

AL2

AL17

AL14

AL11

AL1

AK9

AK43

AK39

AK34

AK32

AK3

AK29

AK26

AK23

AK22

AK20

AK17

AK14

AK10

AJ5

AJ41

AJ36

AJ34

AH7

AH39

AH37

AH34

AH1

AG9

AG43

AG33

AG3

AG11

AF5

AF41

AF38

AF35

AE7

AE39

AE2

AD43

AD41

AD37

AD33

AD11

AC9

AC7

AC5

AC36

AC2

AB7

AB42

AB40

AB4

AB37

AA9

AA39

AA38

AA34

AA3

A6

A41

A4

A39

A35

11 74

11 74

11 74

0A

0A

0A

Page 12

5

CSI_CPU1_IOH_CLK_DP28

CSI_CPU1_IOH_CLK_DN28

CSI_IOH_CPU1_CLK_DP28

CSI_IOH_CPU1_CLK_DN28

D D

C C

B B

A A

CSI_CPU1_CMP014 CSI_CPU1_CMP1 14

CSI_CPU1_IOH_CLK_DP

CSI_CPU1_IOH_CLK_DN

CSI_IOH_CPU1_CLK_DP