Page 1

1

MSI

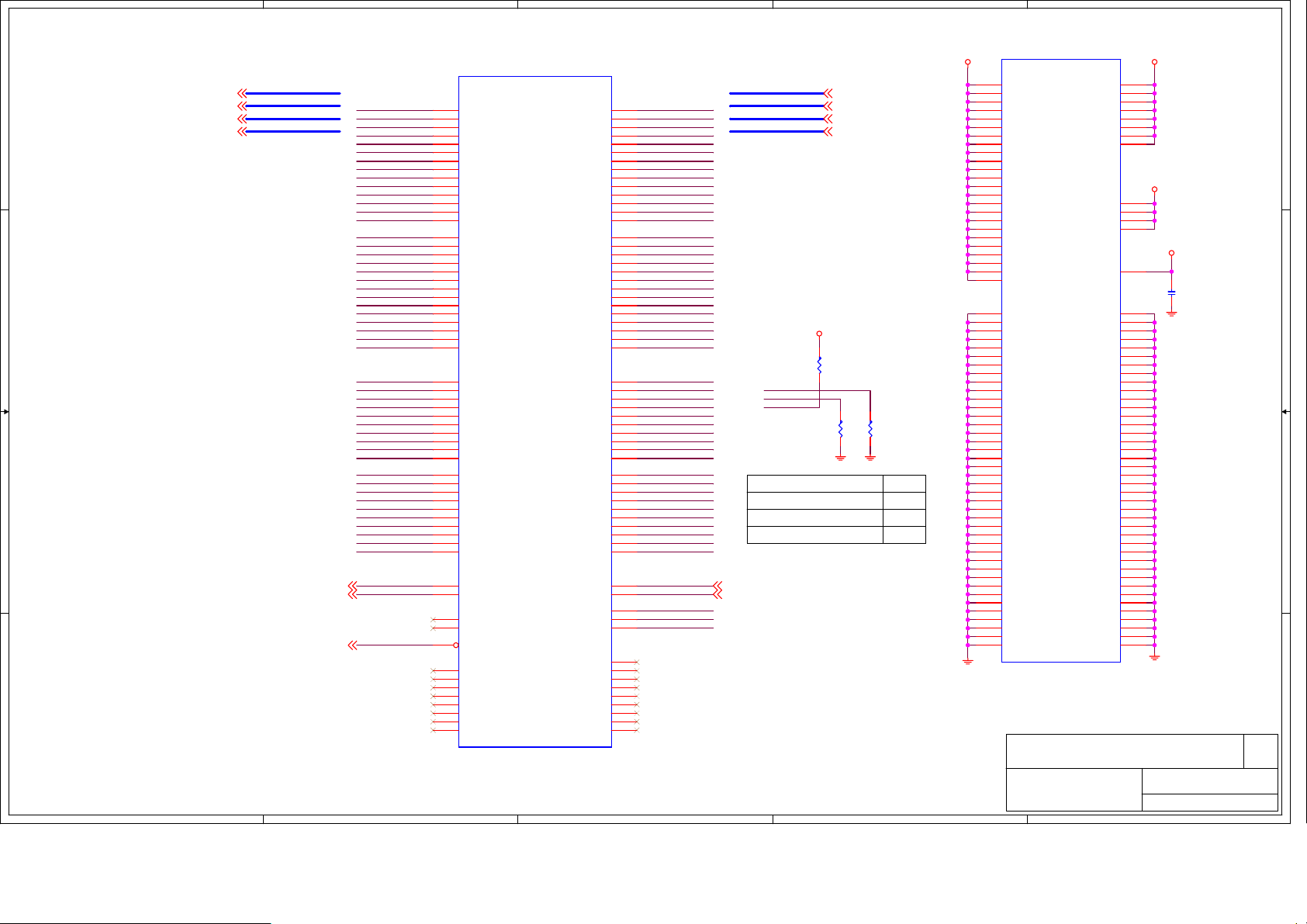

MS-9192 1U & 2U Server

Revision 0A

Intel Dual FC-LGA4 771 Dempsey/Woodcrest/Clovertown Processor

Intel Blackford / ESB2 Chipset

LSI 1068 SAS Controller

Intel Gilgal 82563EB Dual Gb Ethernet PHY

ServerEngines Server Management Controller Pilot

Title Page

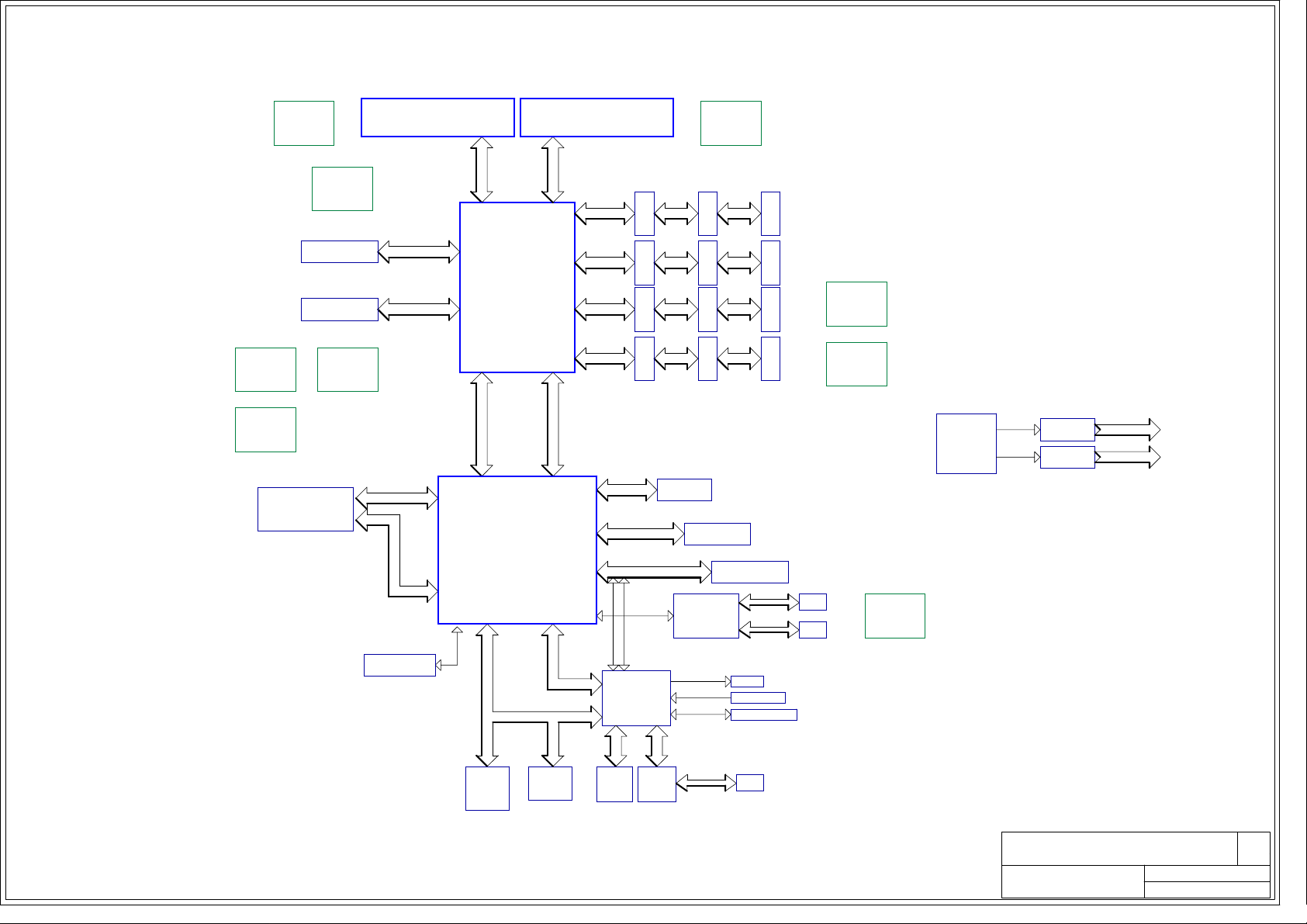

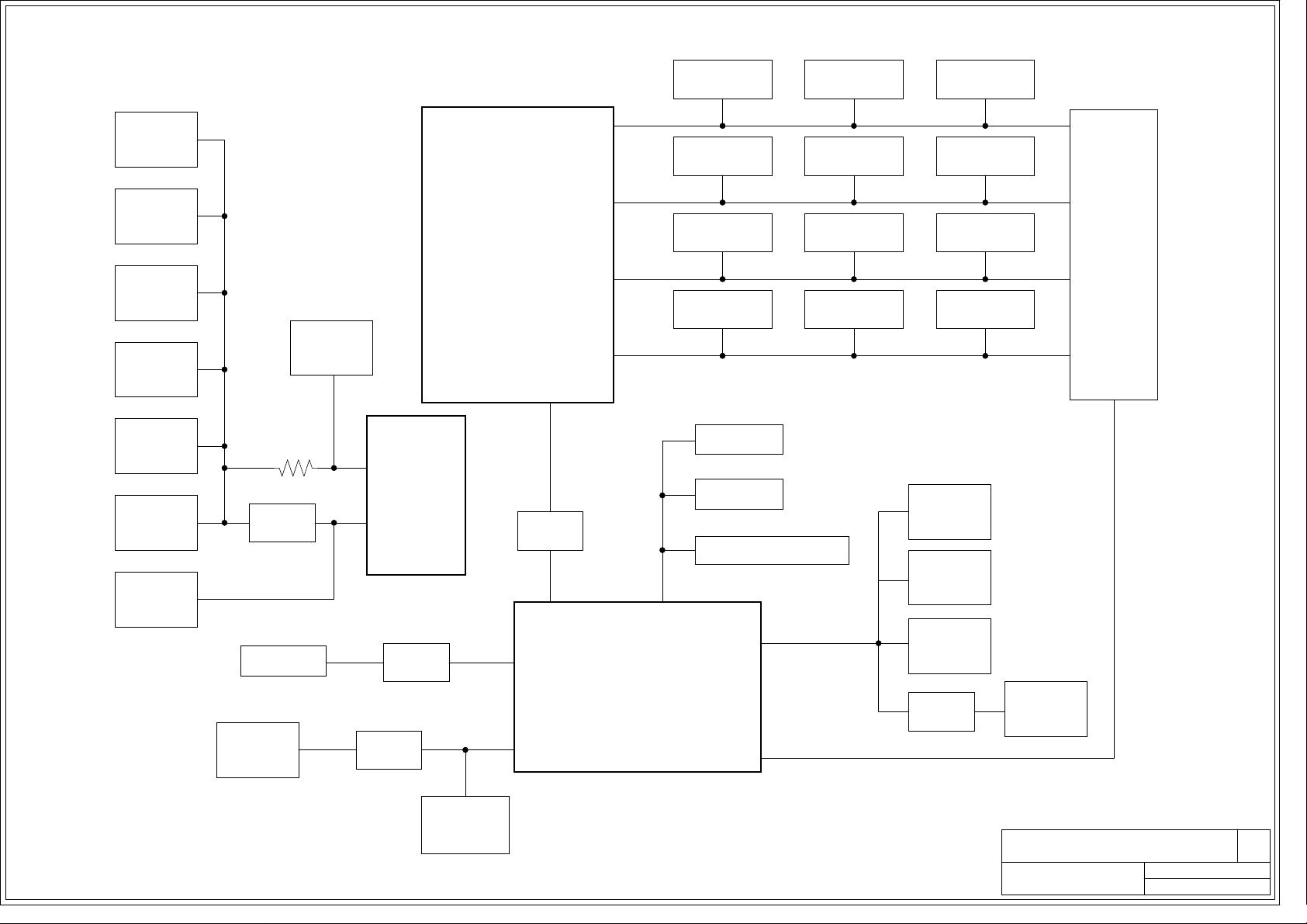

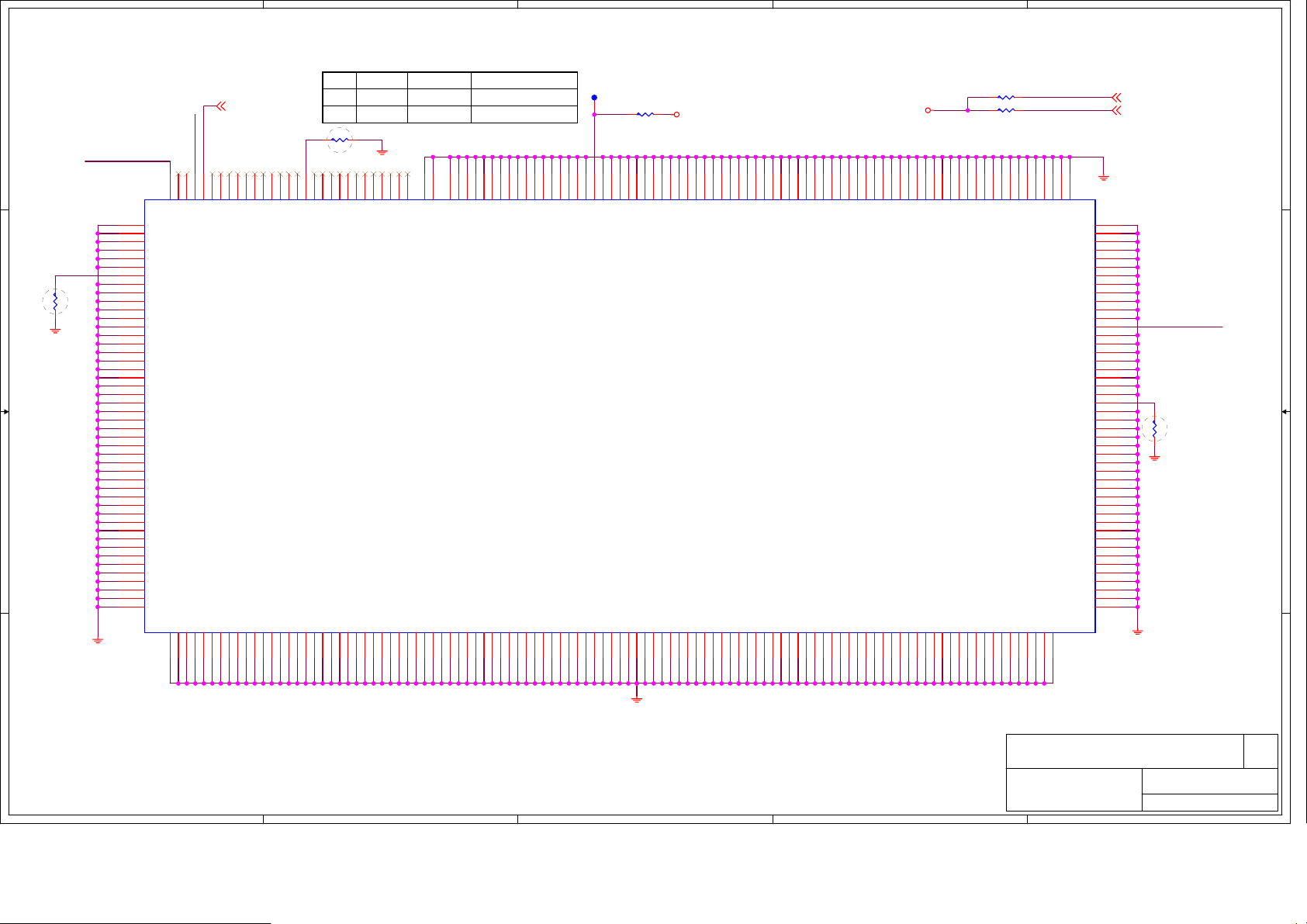

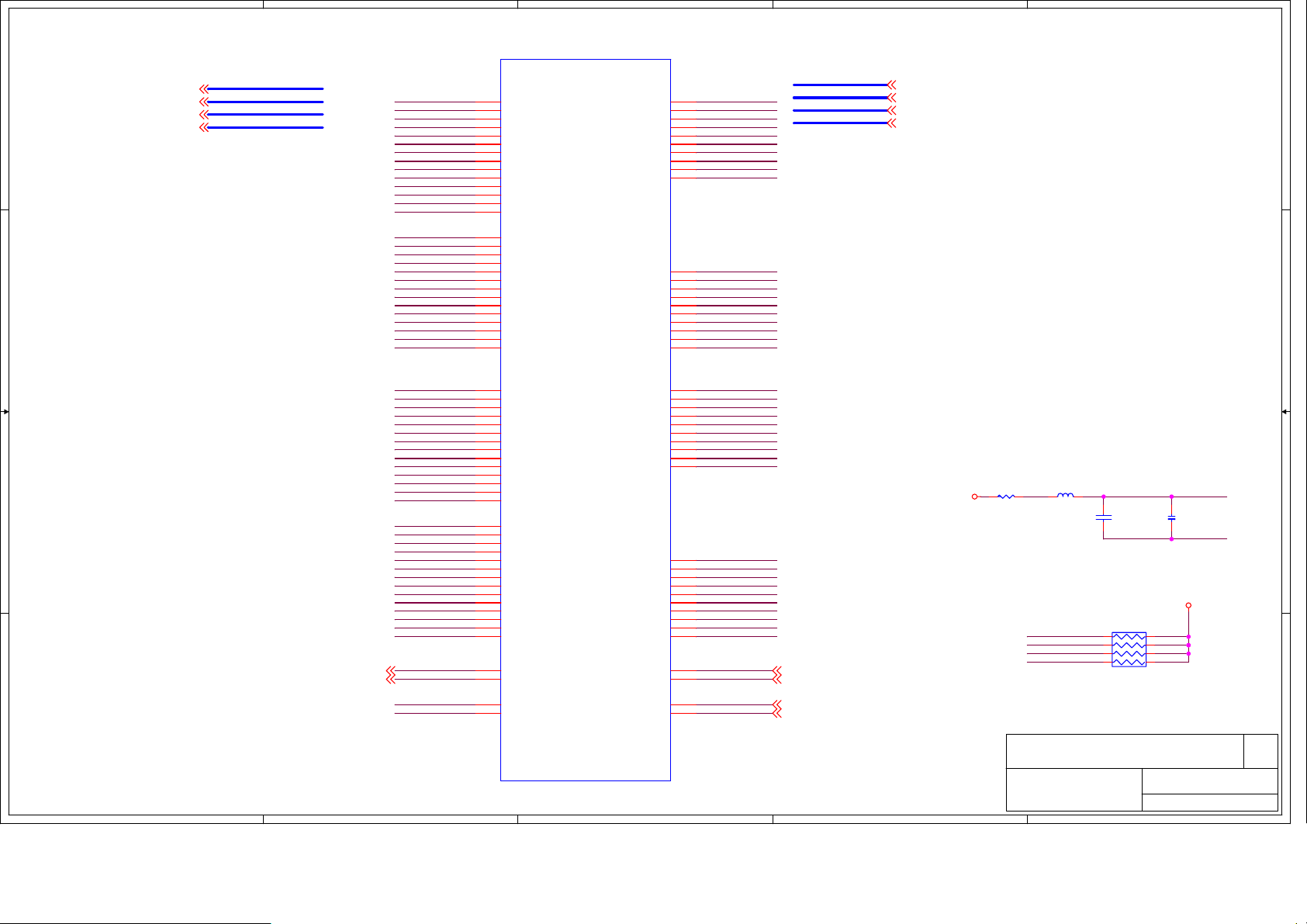

System Block Diagram

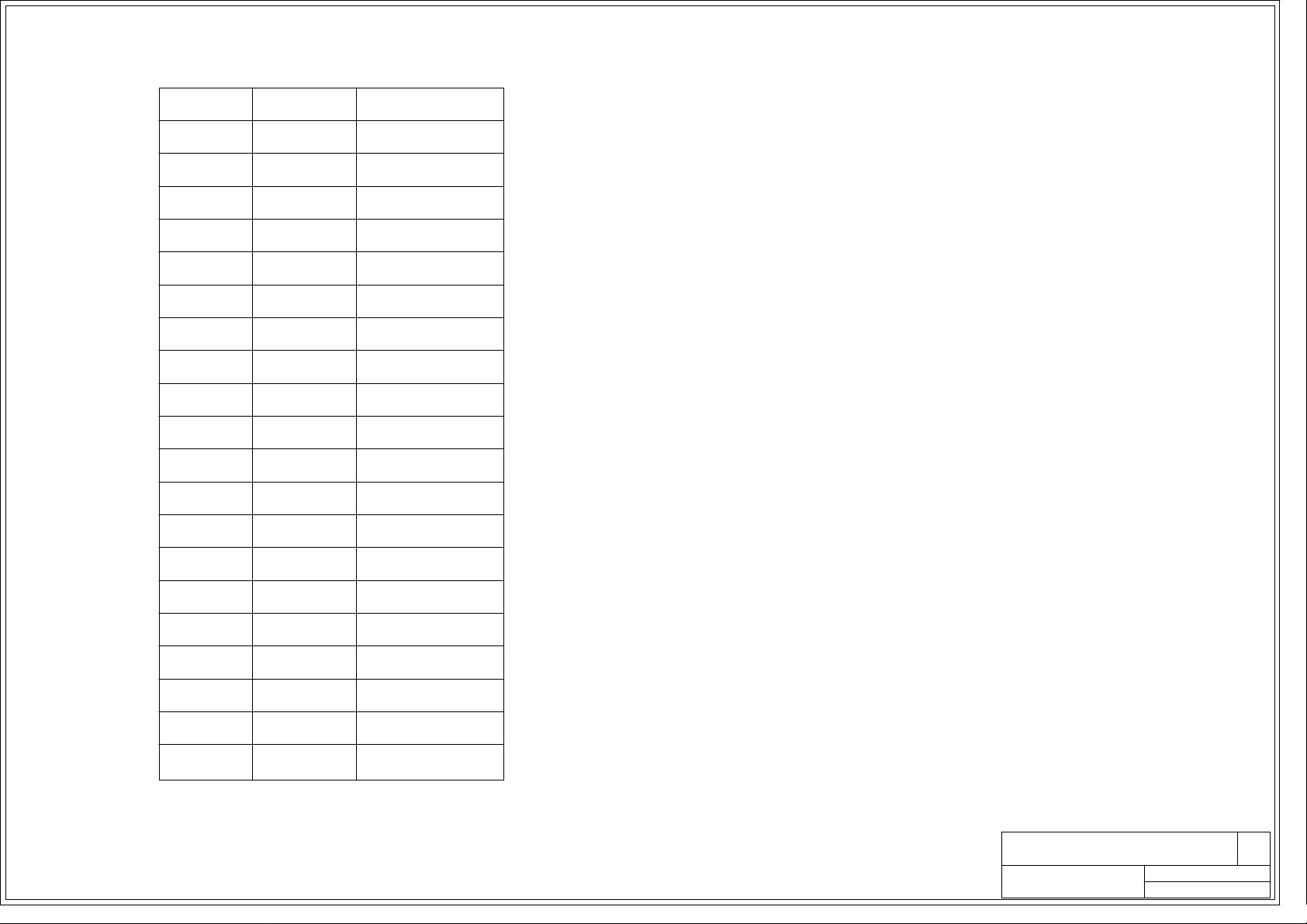

Voltage Table

A A

2

3

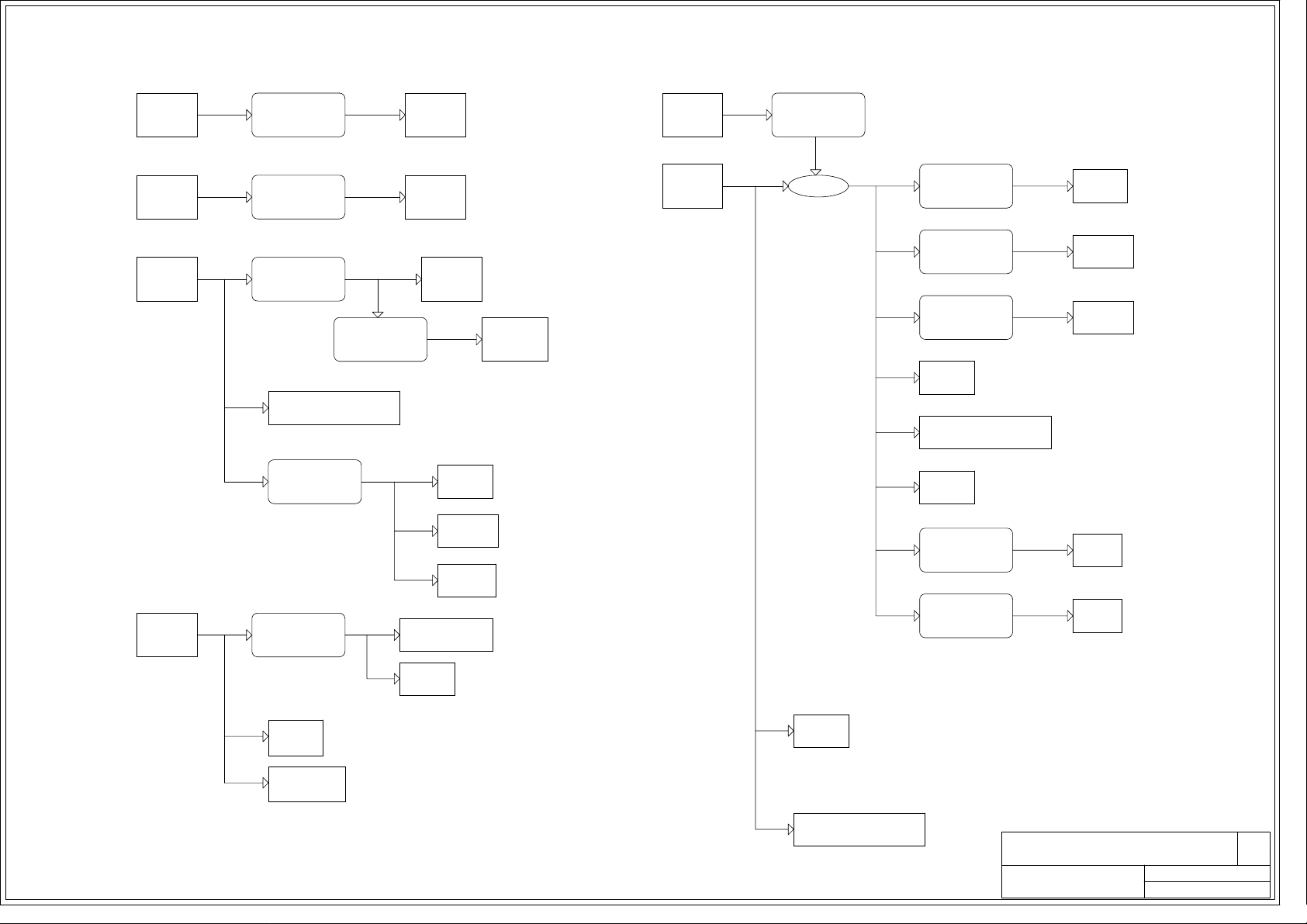

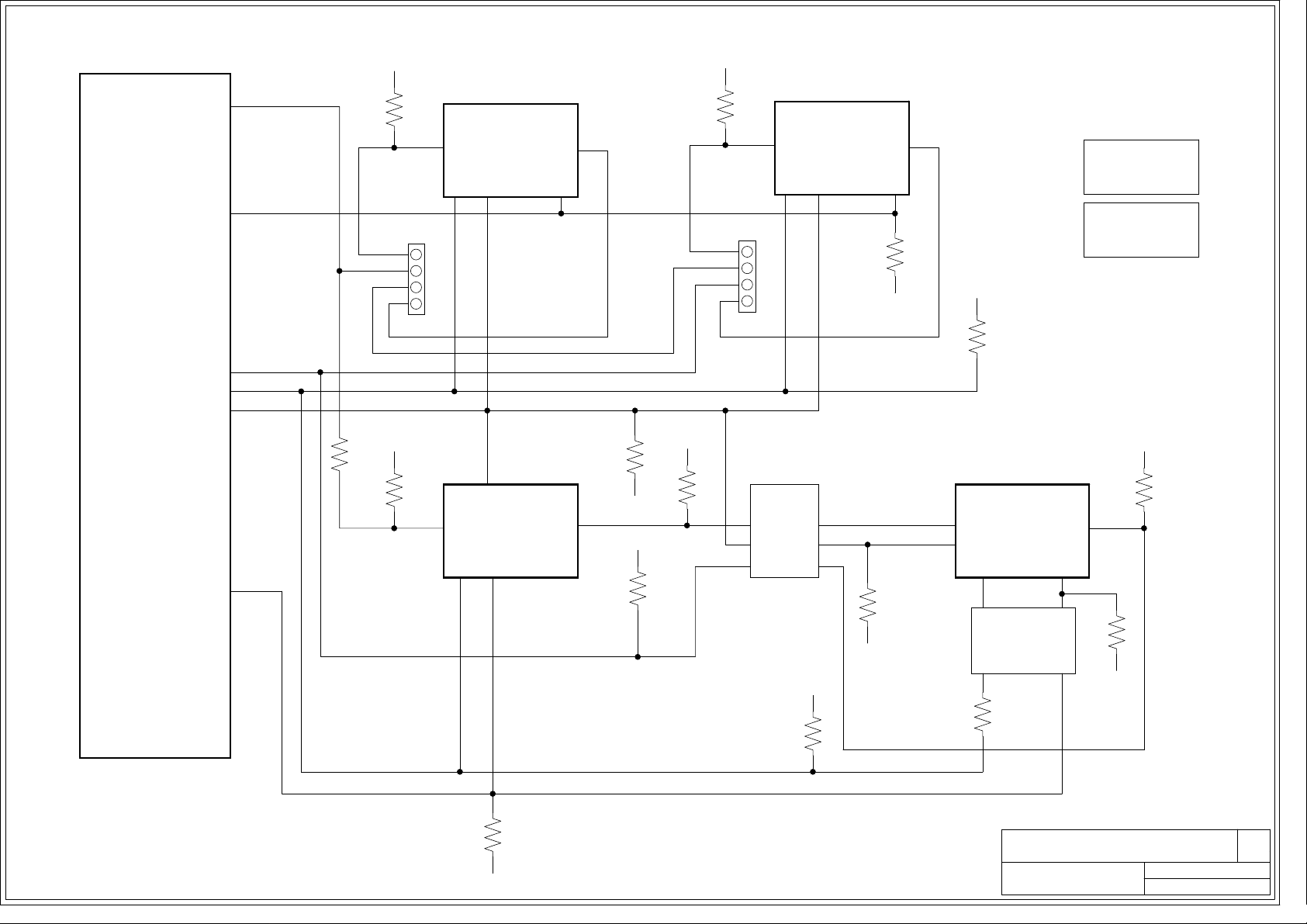

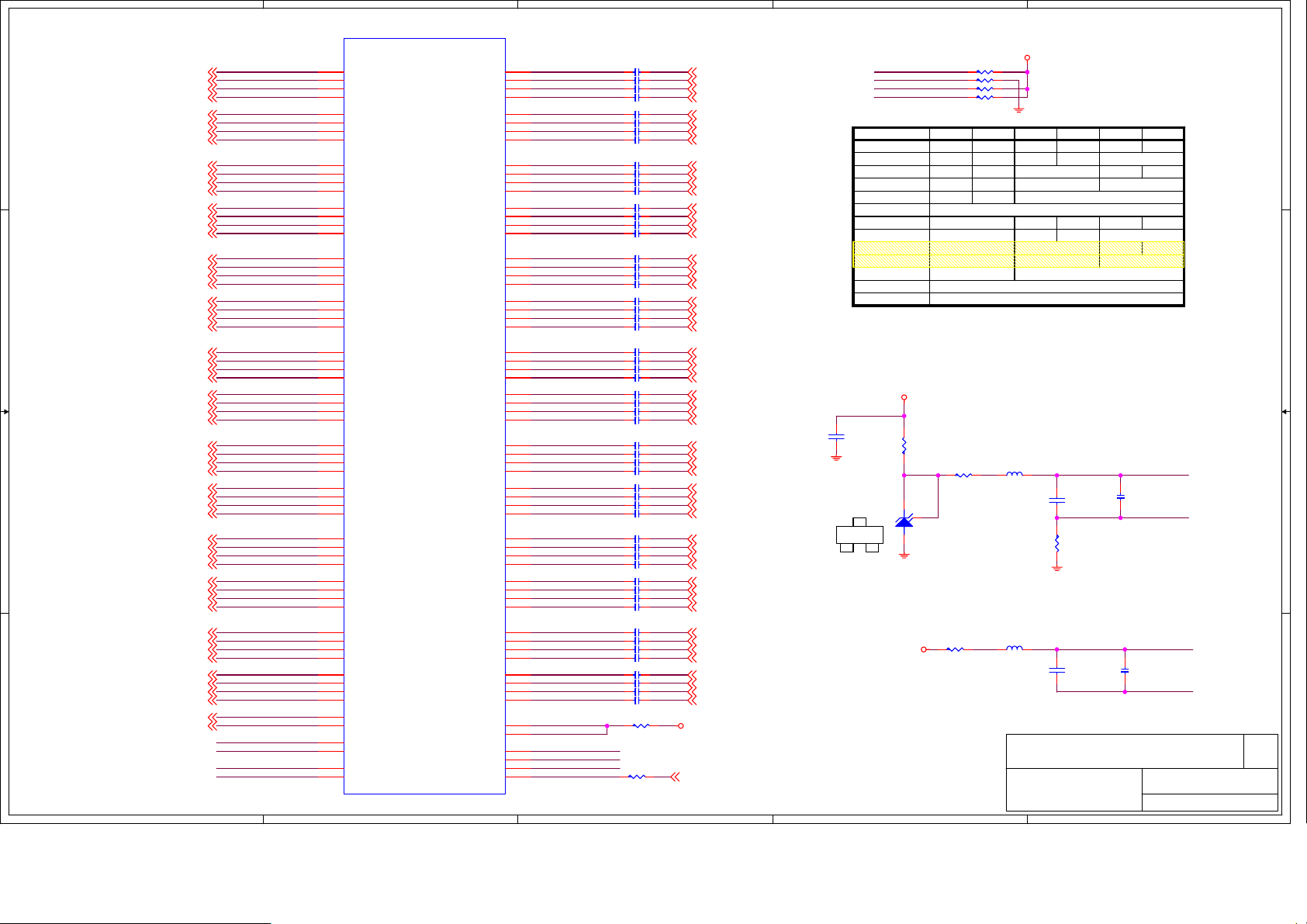

4Power Block Diagram

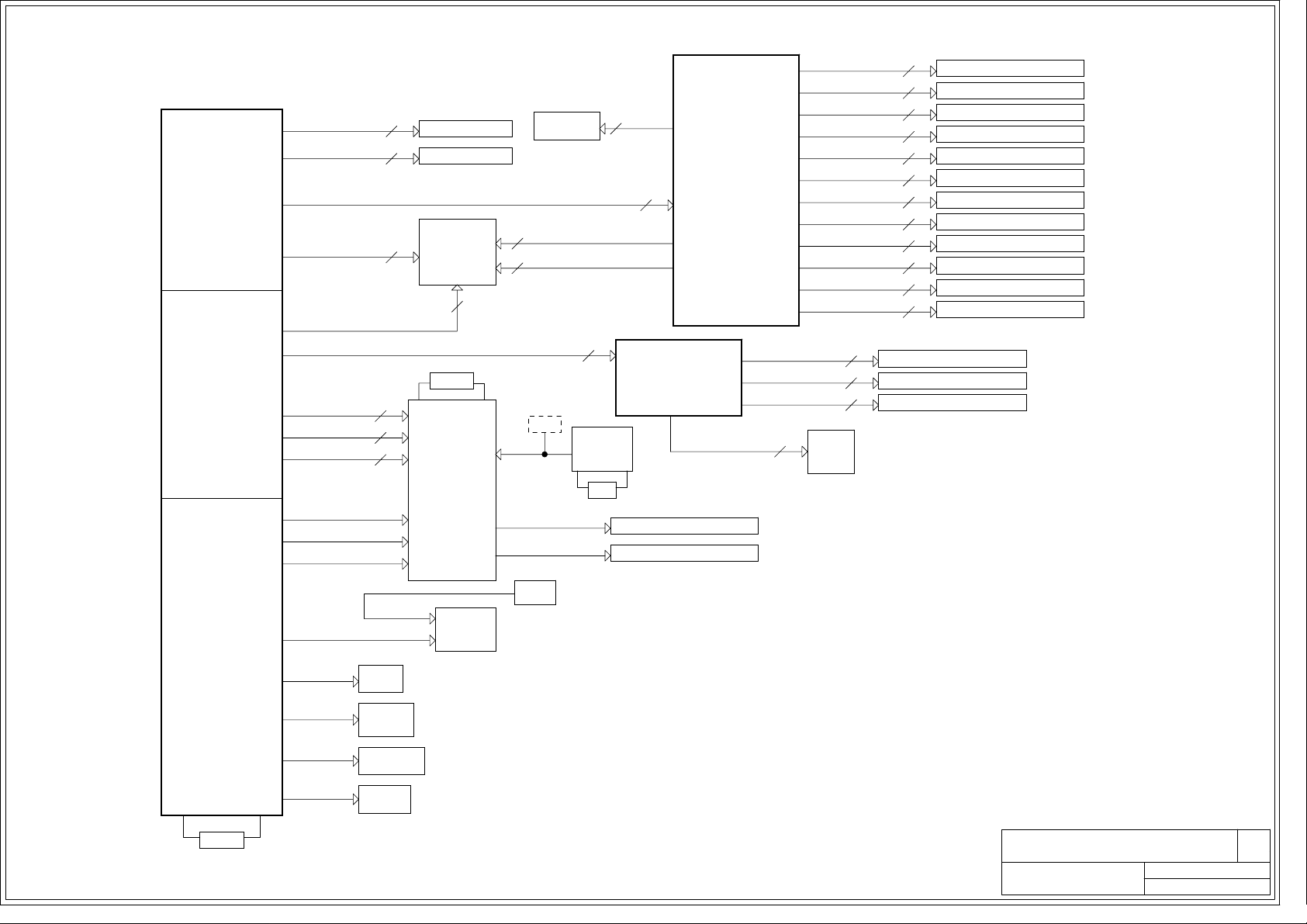

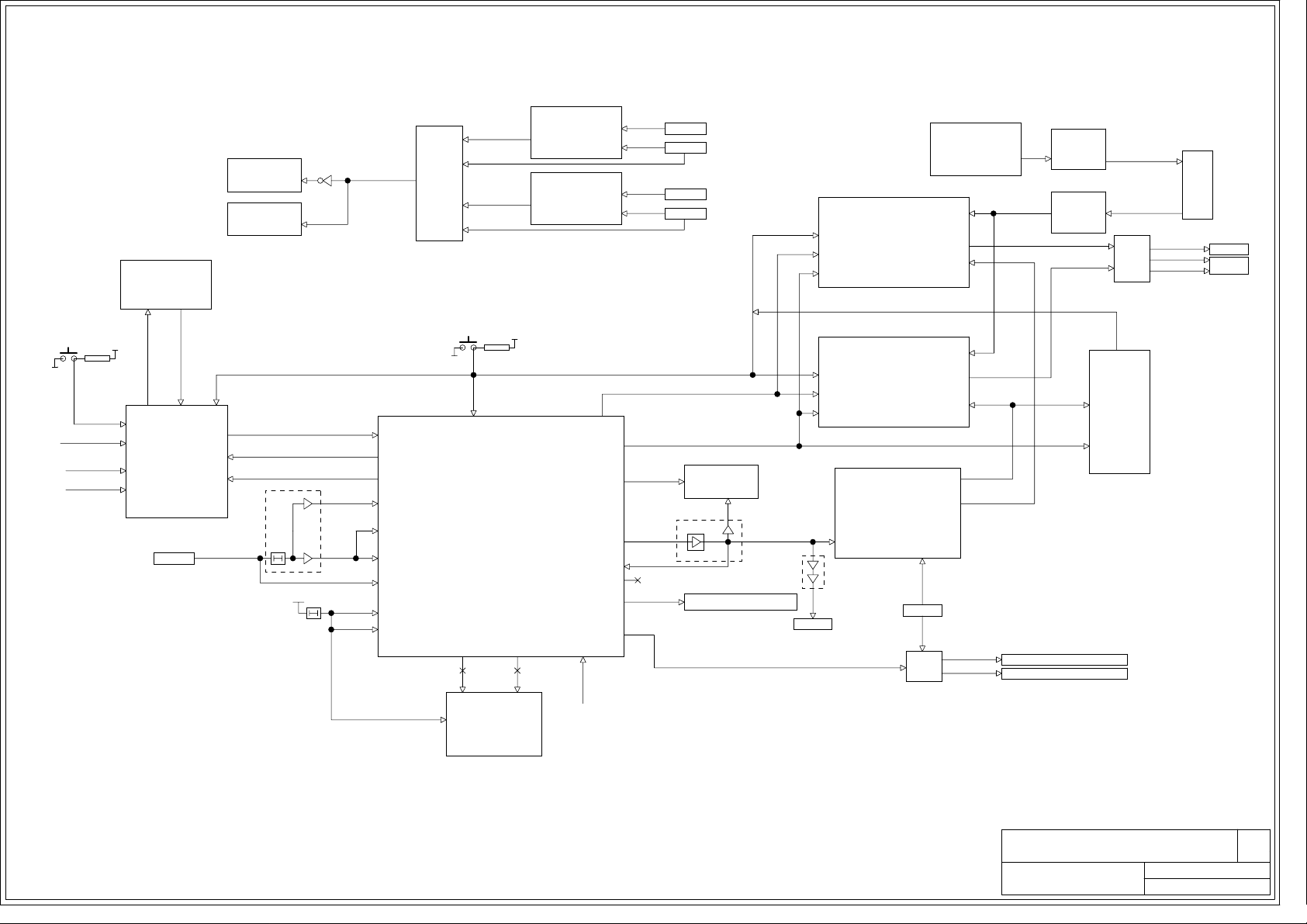

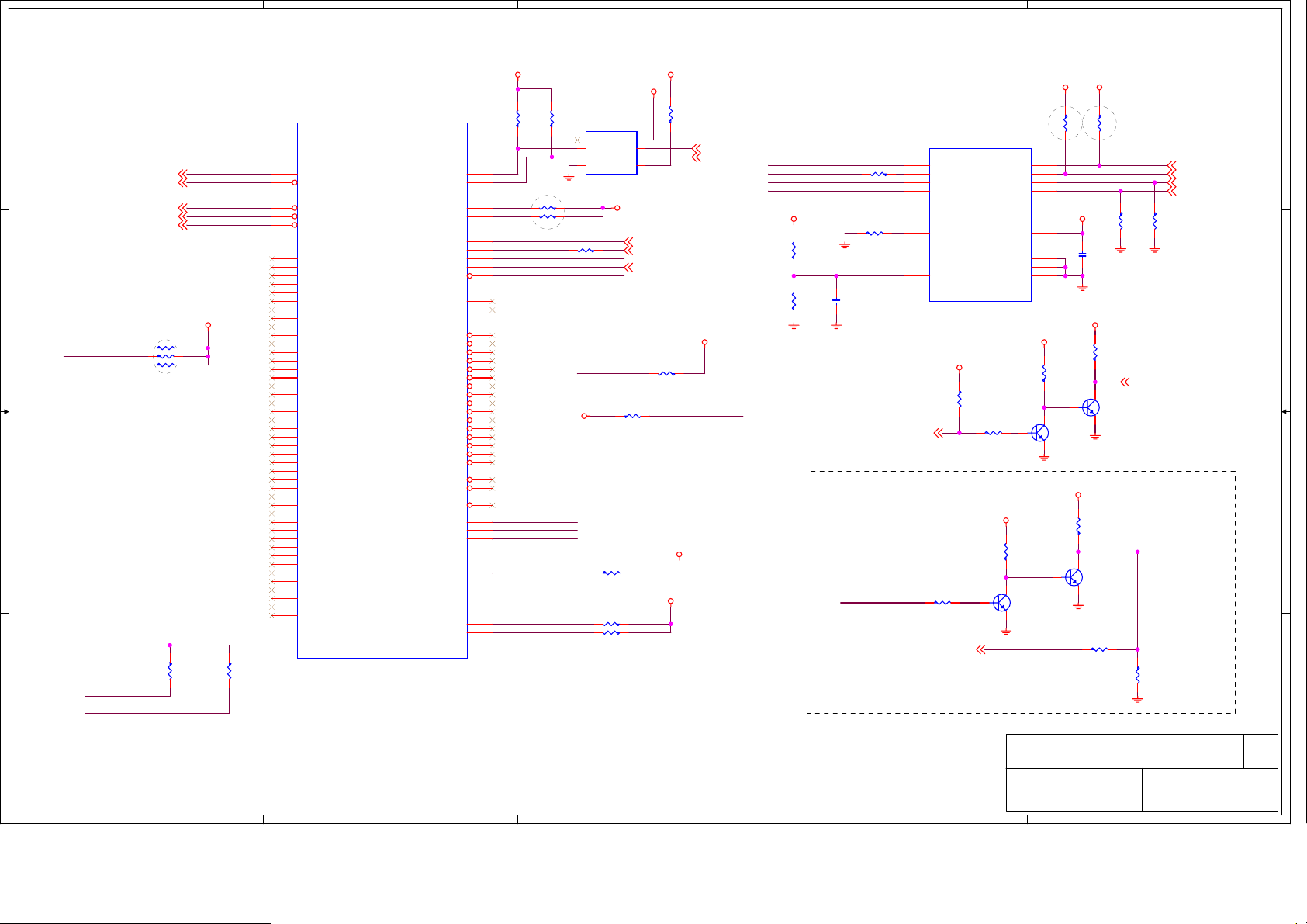

Clock Block Diagram 5

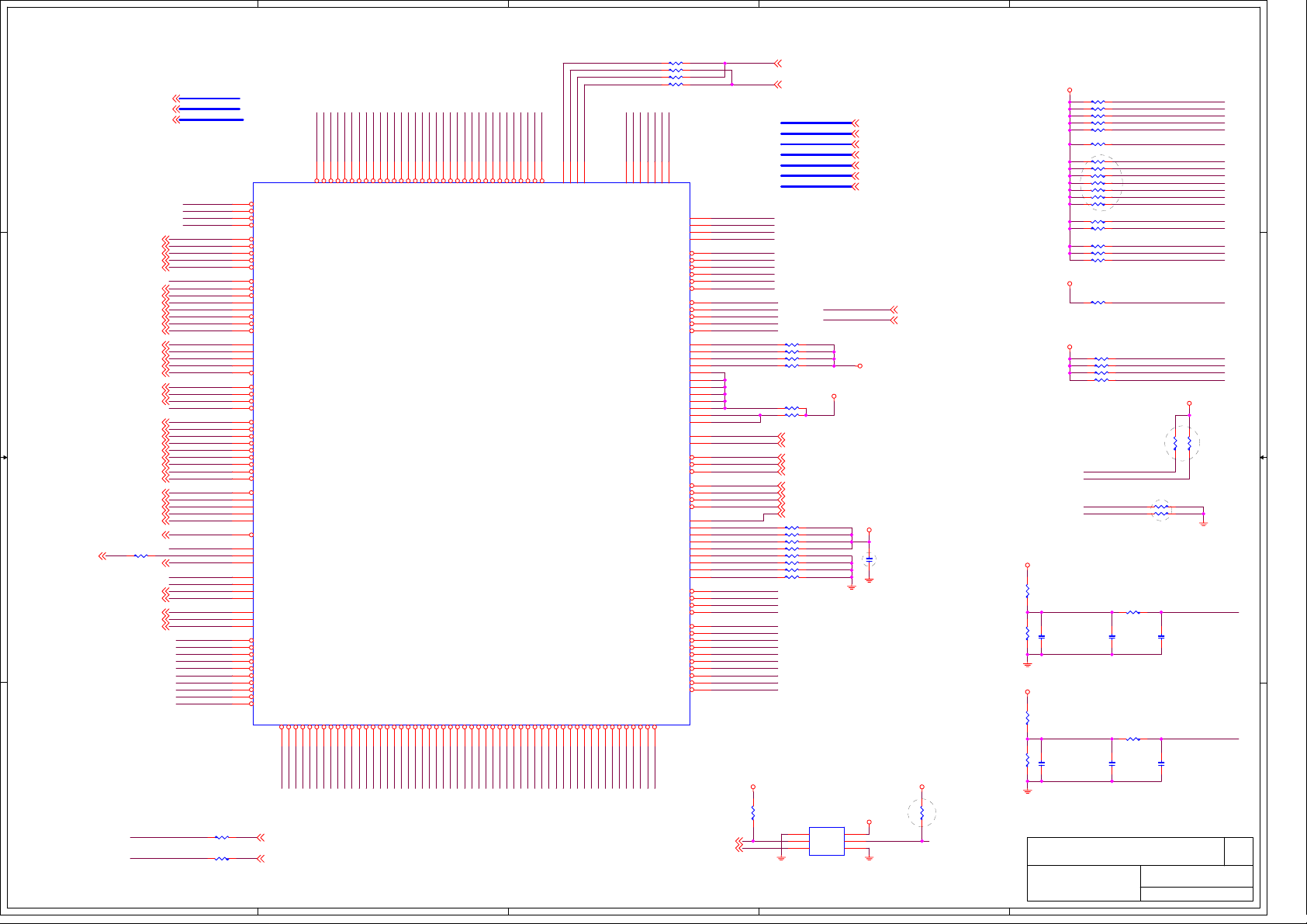

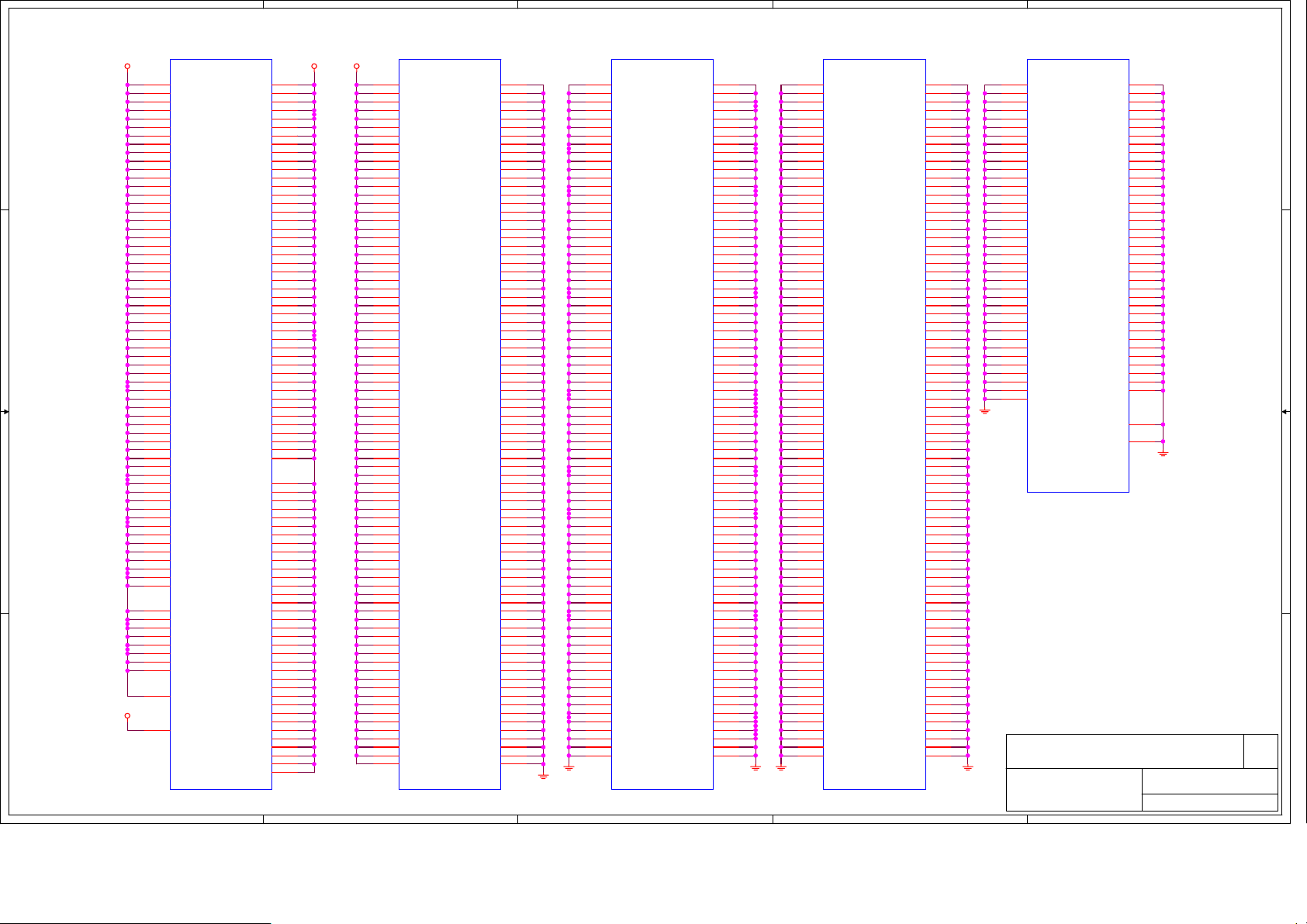

SMBus Block Diagram 6

JTAG Block Diagram

System Reset Block Diagram

Processor 0

Processor 1

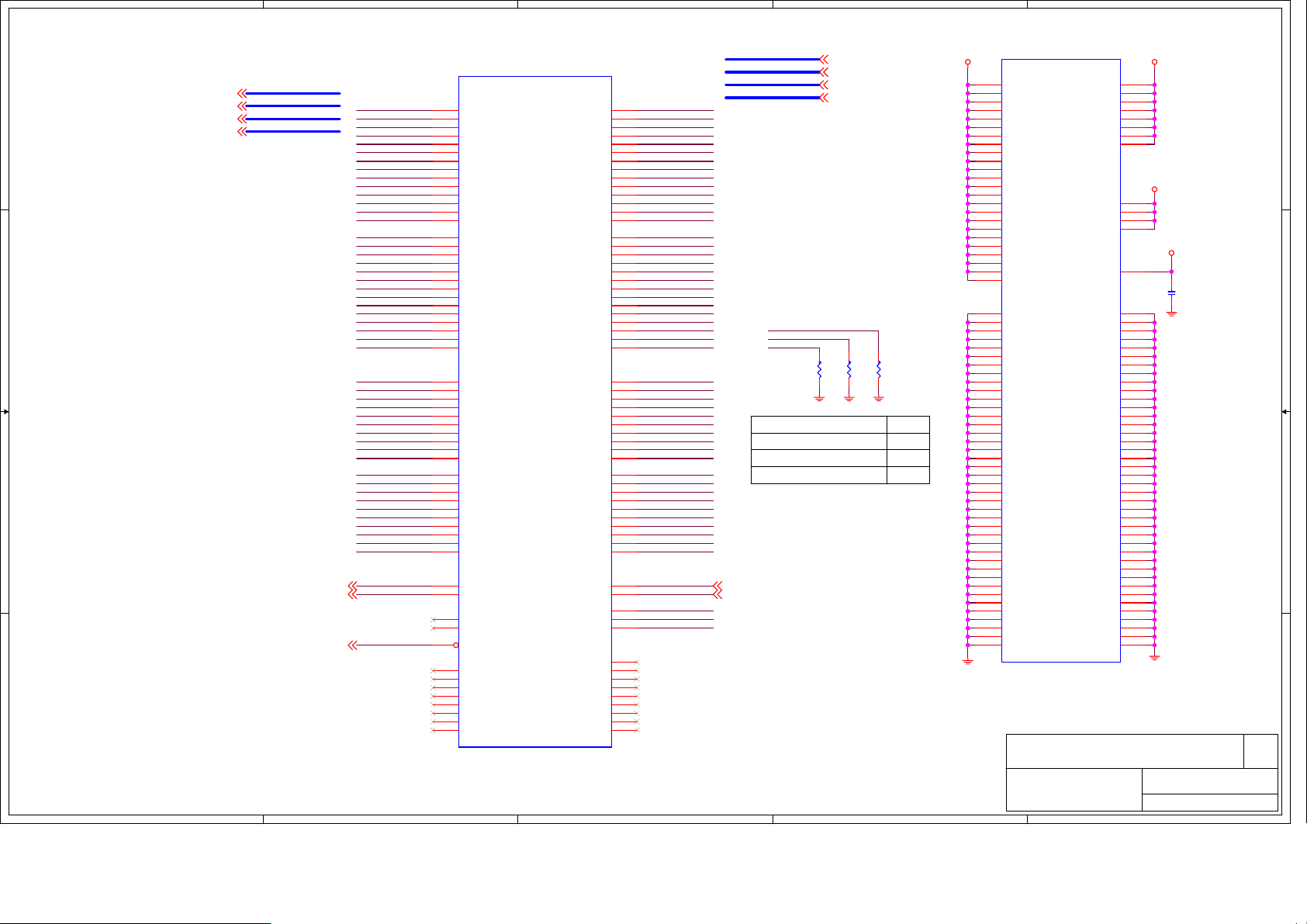

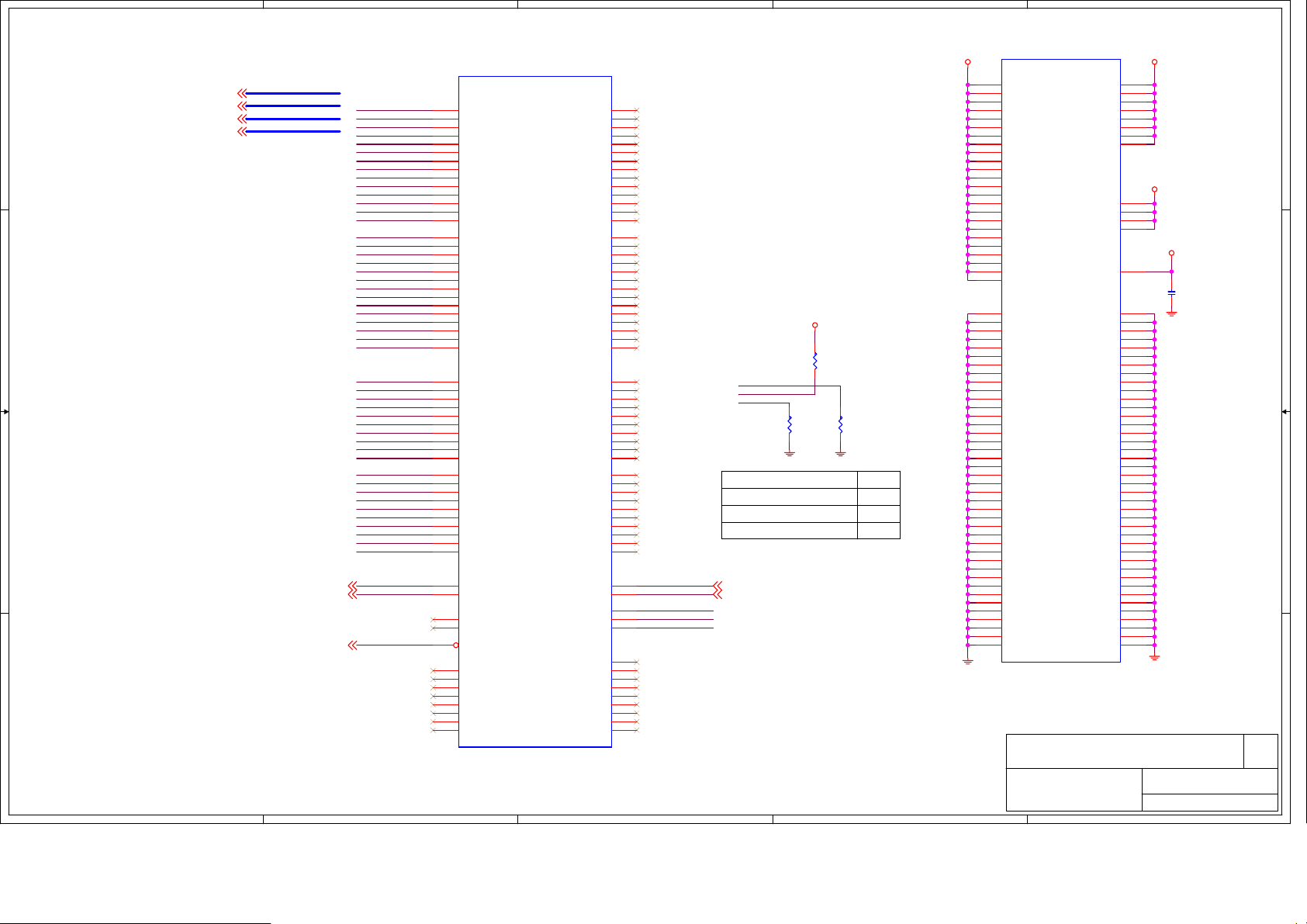

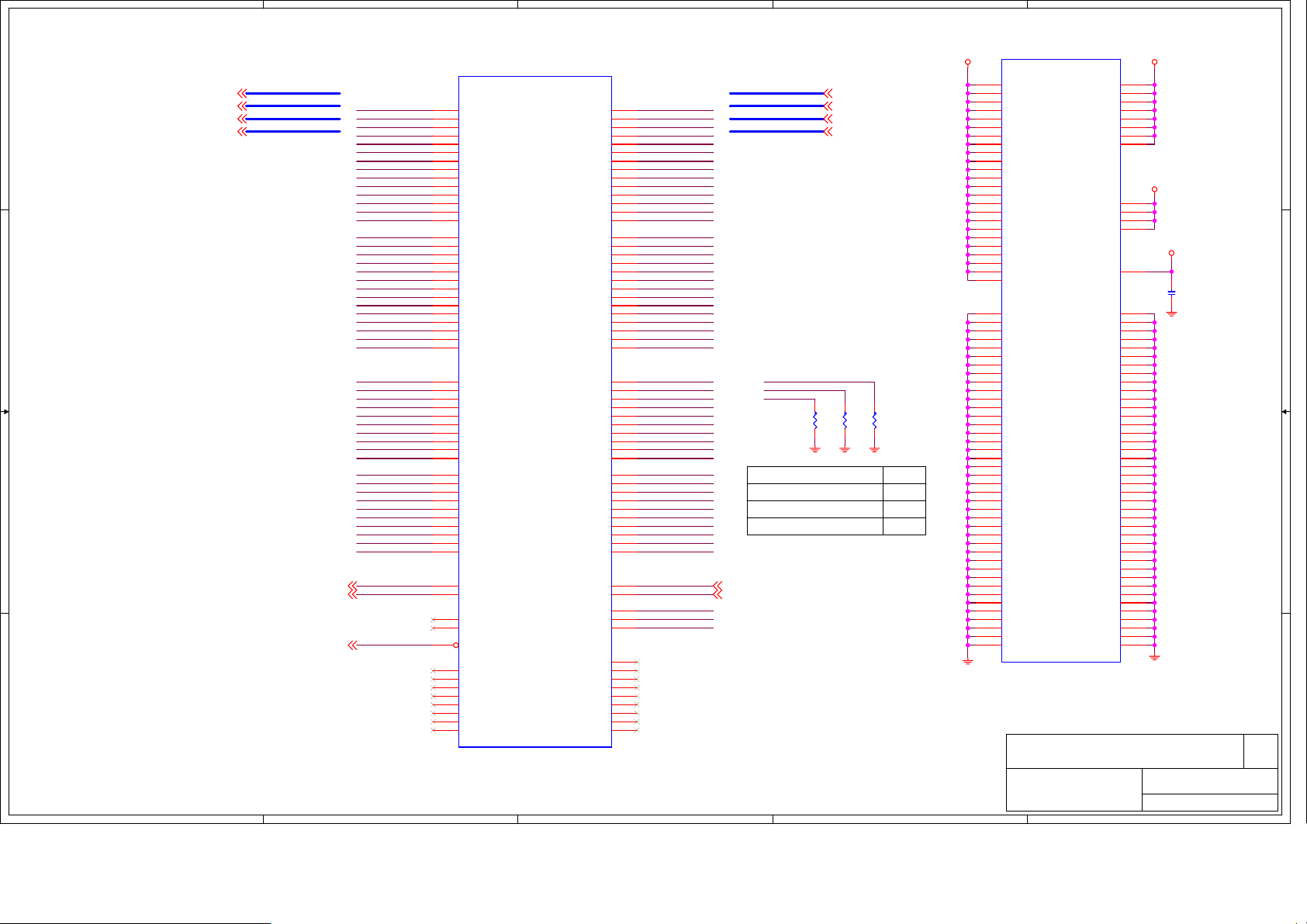

MCH (Blackford)

Fully buffered DIMMs

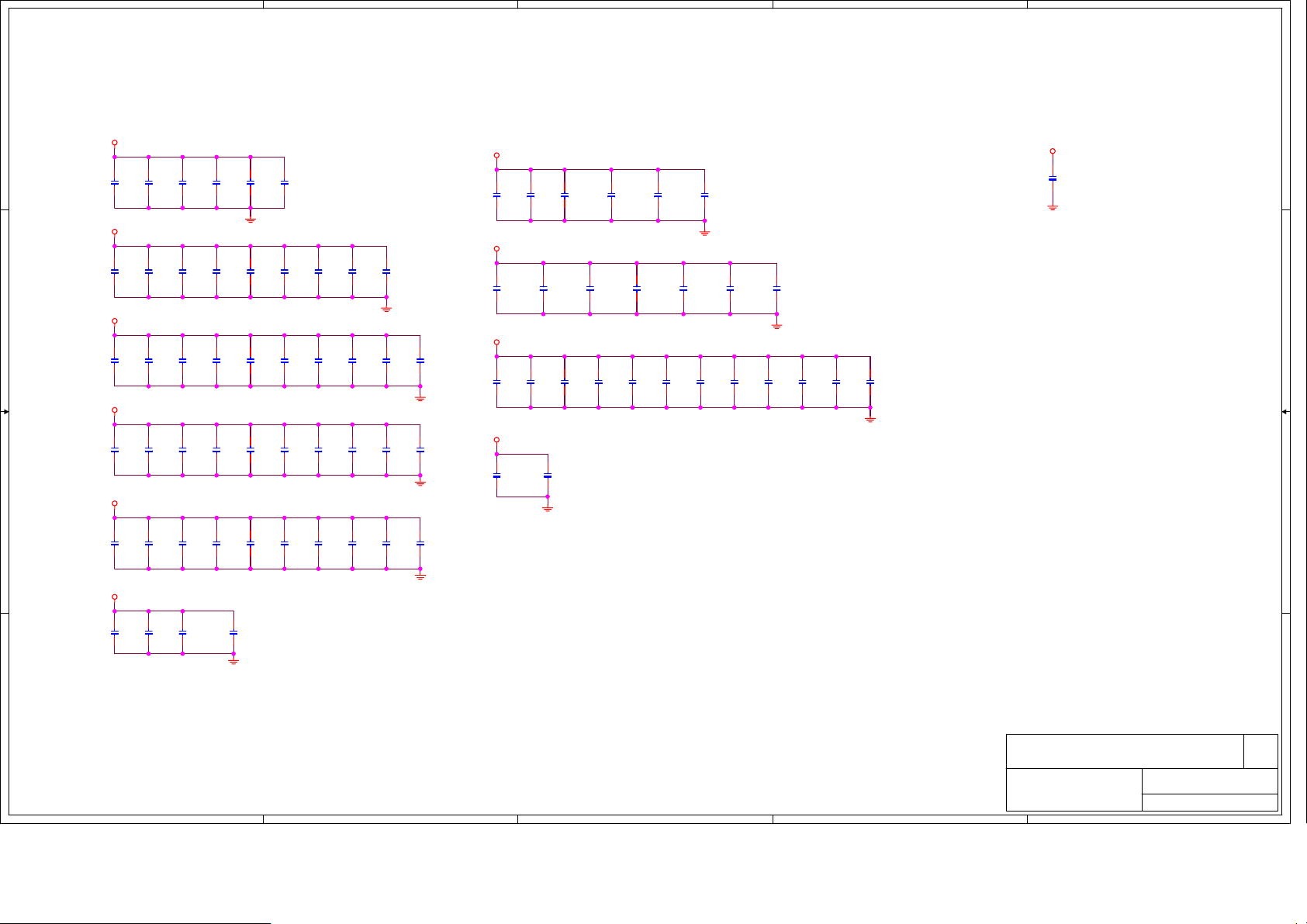

FBDs Reset and Decoupling Caps.

ESB2

Firmware Hub

SATA and USB Connectors

7

8

9-11

12-14

15-22

23-34

35

36-44

45

46

Title Page

LAN (Gilgal)Cover Sheet 1

PCI Express X8 Slots

POLIT2

Clocks (CK410B/DB1900/DB800)

Thermtrip

CPU BSEL Level Translation

EPLD / RSMRST#

Extended Debug Port (XDP)

Hardware monitor

PECI Poller

Back Panel Connector

Power Connector and NMI

Processor 0 VREG (VR11)

Processor 1 VREG (VR11)

VCORE Decoupling Cap.

47-49

50

51-52

53-57

58-60

61

62

63

64

65

66

67

68

69-70

71-72

73

Title Page

FBD 1.8V VREG

1.5V VREG280 Pin PCI-X/PCI-E Slot

FSB VTT 1.2V /FBD VTT 0.9V VREG

Standby / MISC VREG

Impedance Test / mouting hole

Manual Parts

VT1135S Option Parts

GPIO Maping

Reset and Power Good PLD Logic

Power On/Off and Reset Sequence

History

Reserved Page

74

75

76

77

78

79

80-83

84

85

86

88-89

90

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

1

http://www.msi.com.tw

Micro Star Restricted Secret

Cover Sheet

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

190

Rev

0A

of

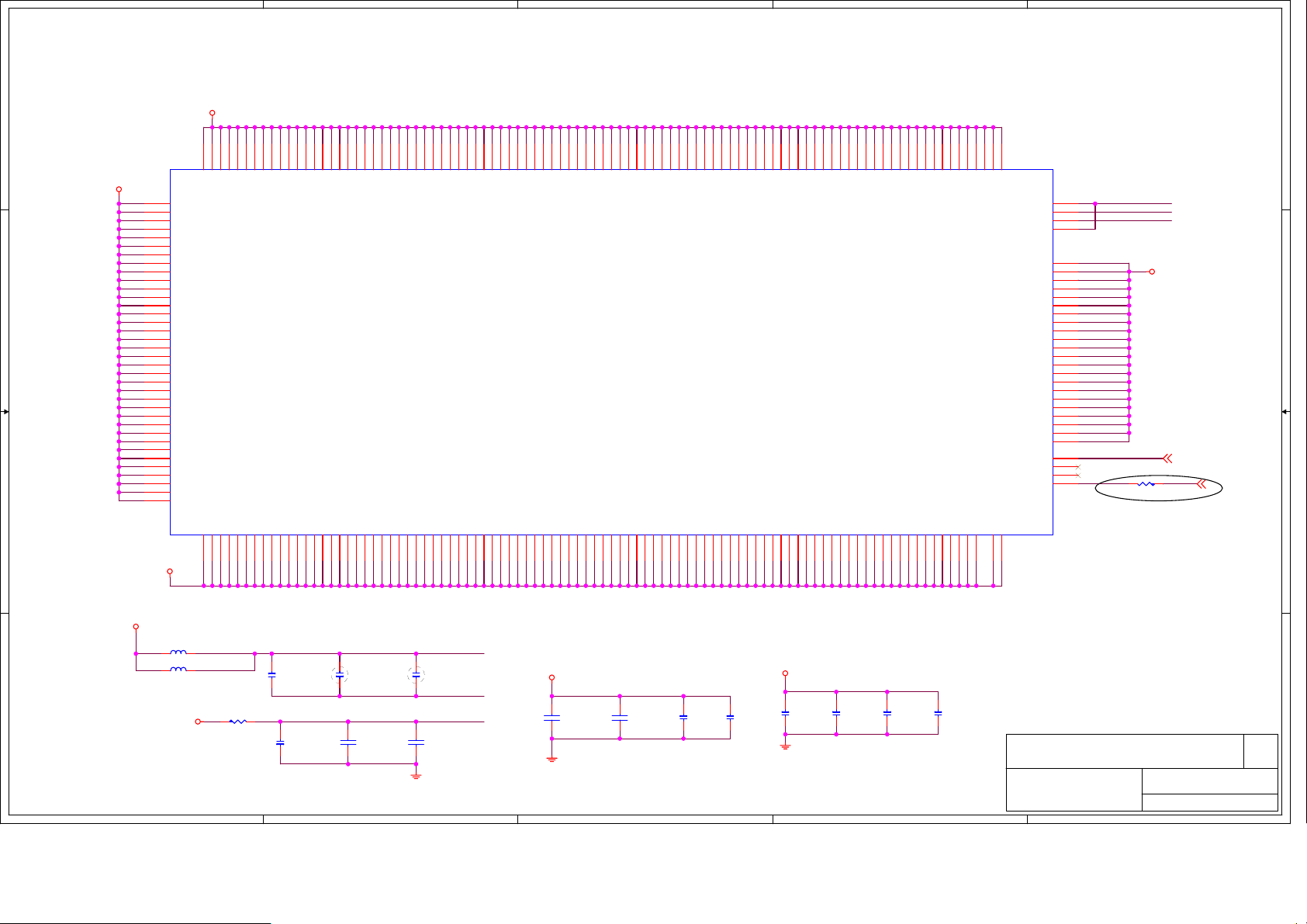

Page 2

System Block Diagram

1

VRM 11

For CPU0

1.2V VRD

FSB VTT

PCI-E X8 Slot

PCI-E X8 Slot

1.5VSBY

VREG

3.3VSBY

VREG

A A

280 PIN SLOT

( PCI-X & PCI-E X8 )

1.5V VRD

BNB+FBD

ESB2

CPU0

FC-LGA4 771 Processor

FSB0 / 1066/1333MHz FSB

PCI Express X8

4GB/s

PCI Express X8

4GB/s

PCI Express X8

PCI-X 100/133

Port #4&5

Port #6&7

PCI Express X8 ESI X4

4GB/s

Port #1&2

(X8)

CPU1

FC-LGA4 771 Processor

Blackford

MCH

FSB1 / 1066/1333MHz FSB

Port #0Port #2&3

2GB/s

Port #3Port #4

(ESI)(X8)

FBD CH0

FBD CH1

FBD CH2

FBD CH3

DIMM #00

DIMM #10

DIMM #20

DIMM #30

SATA

Ultra DMA 66/100

SATA 0~5

ATA Primary

VRM 11

For CPU1

DIMM #01

DIMM #11

DIMM #21

DIMM #31

DIMM #02

DIMM #12

DIMM #22

DIMM #32

NOTE:

Channel 0 & 1 Makes Branch 0

Channel 2 & 3 Makes Branch 1

1.8V VRD

0.9V VRD

CK410B

DB1900

DB800

FBD Clocks

PCI-E Clocks

ESB2

Serial EEPROM

USB2.0

Port #6

Port #0

(X1)

PCI Express X1

KUMERAN

ServerEngines

LPC

Pilot II

USB2.0 Port 0~5

Dual Gb PHY

GILGAL

VGA

PS2 KB/MS

Serial Port *2

Gb LAN

Gb LAN

Port #0,1,4,5 Front

Port #2,3 Rear

RJ45

RJ45

Port #1 Rear

Port #2 Front

Gilgal internal

VREG Circuitry

FWH

TPM 1.2

BMC

Flash

10/100

PHY

1

RJ45

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

System Block Diagram

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

290

Rev

0A

of

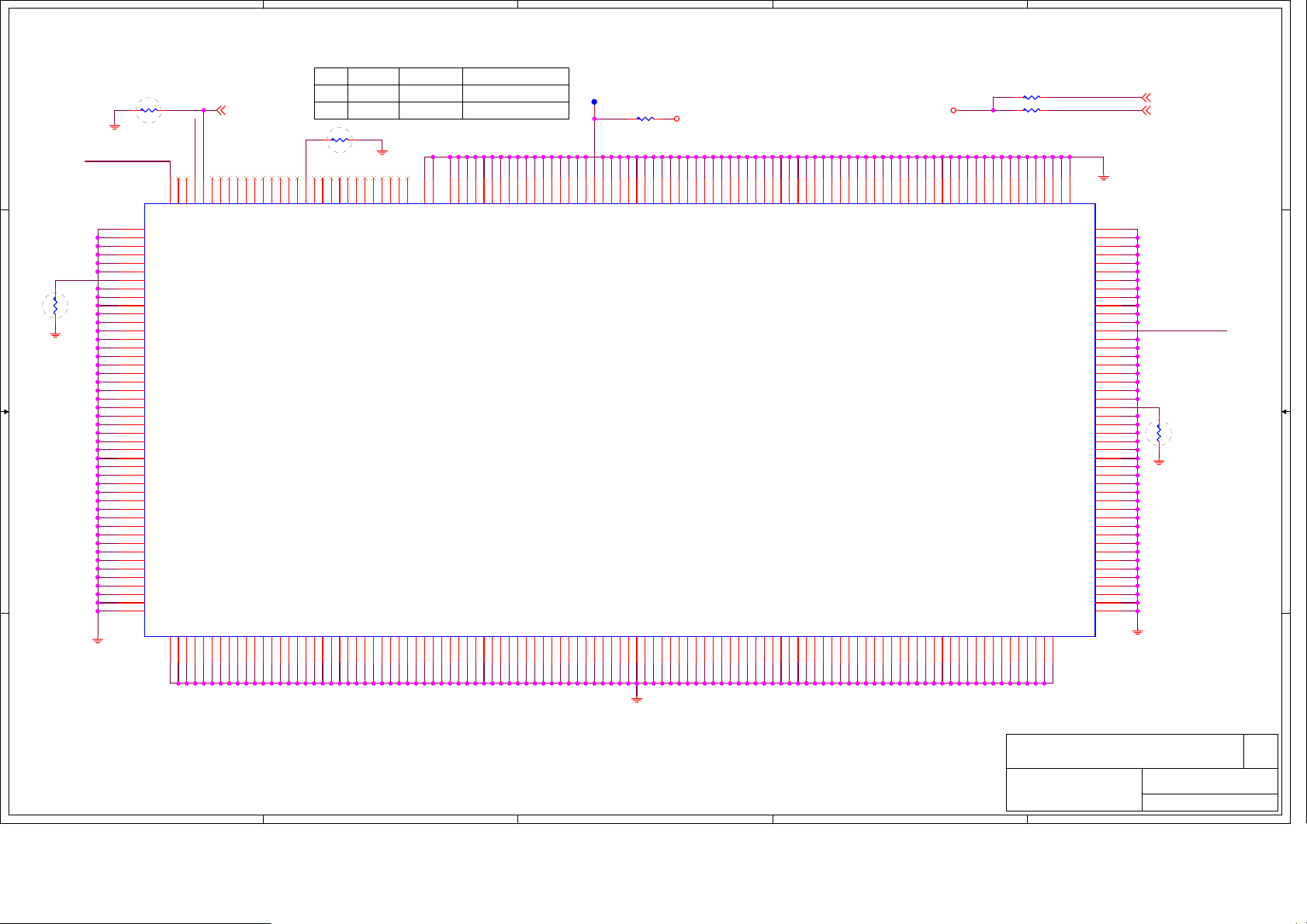

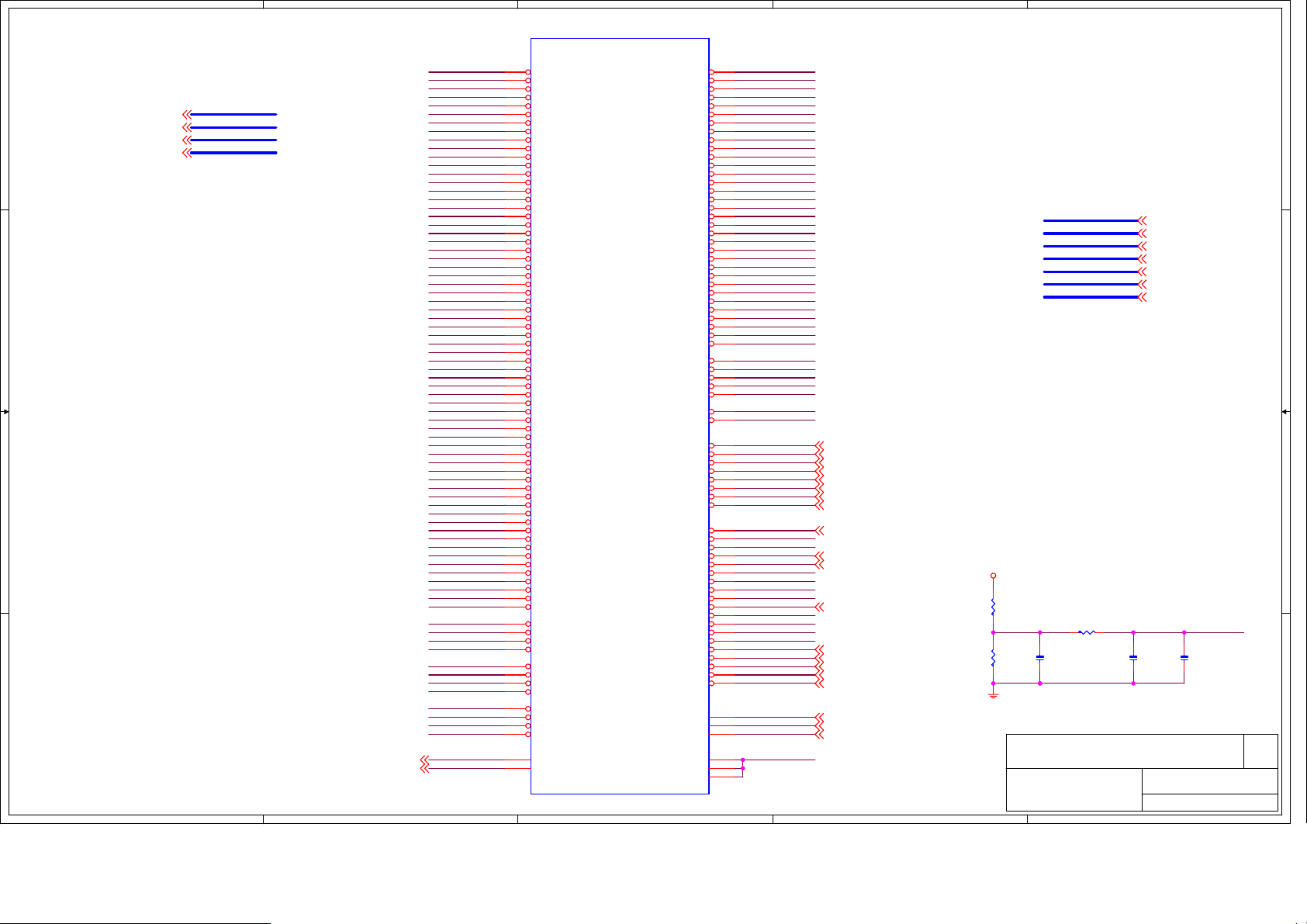

Page 3

Voltage Table

1

Voltage

Level

+3.3V

+5V

+5V

Netname

P3V3

P5V

P5VSB

Generated

From

AC

AC

AC

STBY

-12V

+12V1

+12V2

+12V3

VID_CPU0 P12V_CPU0

VID_CPU1

+1.2V

A A

+1.5V

+1.5V

P-12V

P12V

P12V_CPU1

P12V_CPU0

VCORE0

VCORE1

P_VTT

P1V5

P1V5_AUX

AC

AC

AC

AC

P12V_CPU1

P5V

P12V

P3V3_AUX

AUX

+1.8V

P1V8 P12V

+0.9V

+3.3V

STBY

+3.3V

AUX

+1.8V1

AUX

+1.2V1

AUX

+1.8V2

AUX

+1.2V2

AUX

F_VTT P1V8

P3VSB

P5VSB

P3V3_AUX P3V3 /

P3VSB

P1V8LAN

P1V2LAN

P1V8_AUX

P1V2_AUX

P3V3_AUX

P3V3_AUX

P3V3_AUX

P3V3_AUX

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

1

http://www.msi.com.tw

Micro Star Restricted Secret

Voltage Table

MS-9192

Last Revision Date:

Sheet

Friday, April 27, 2007

390

Rev

0A

of

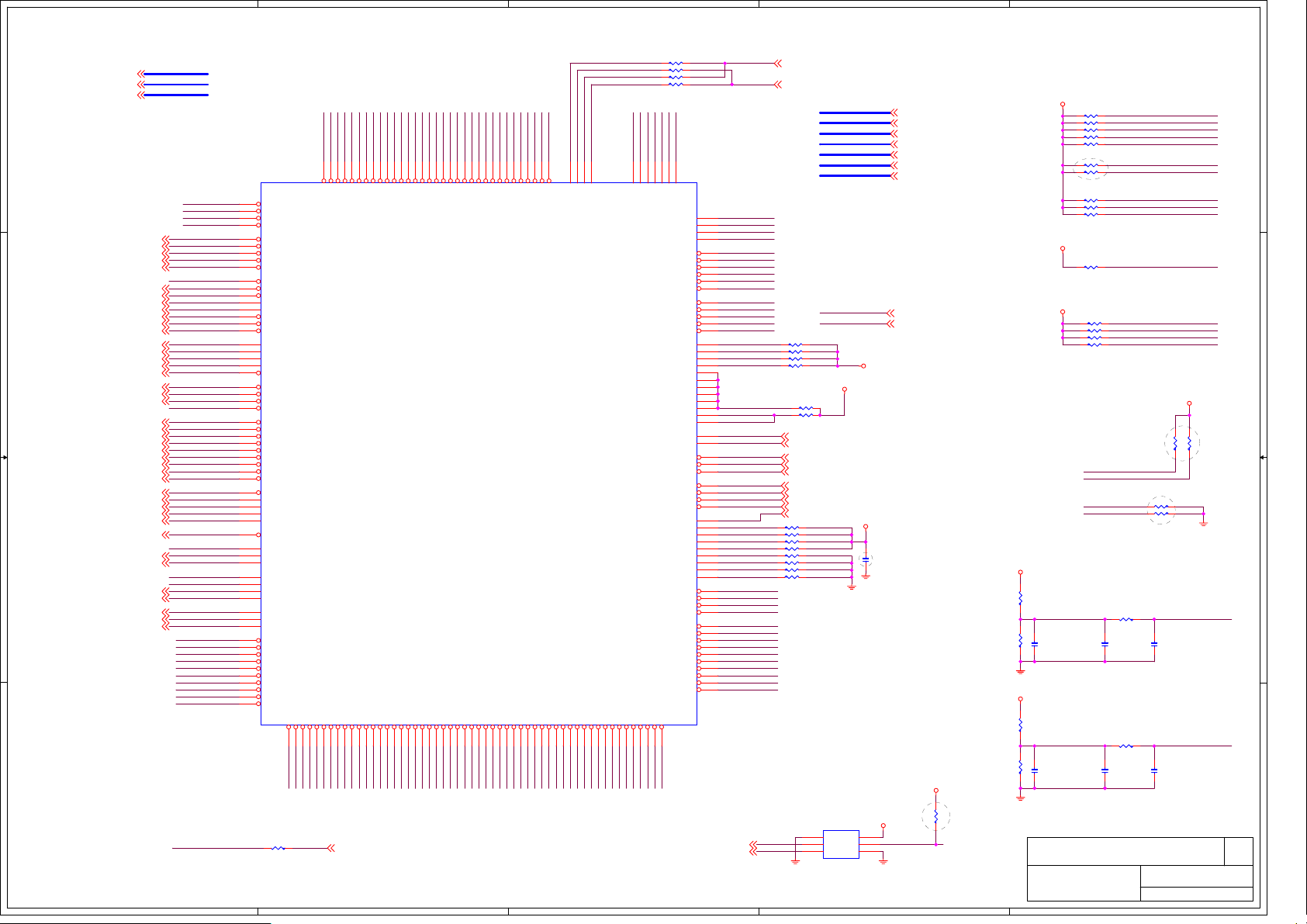

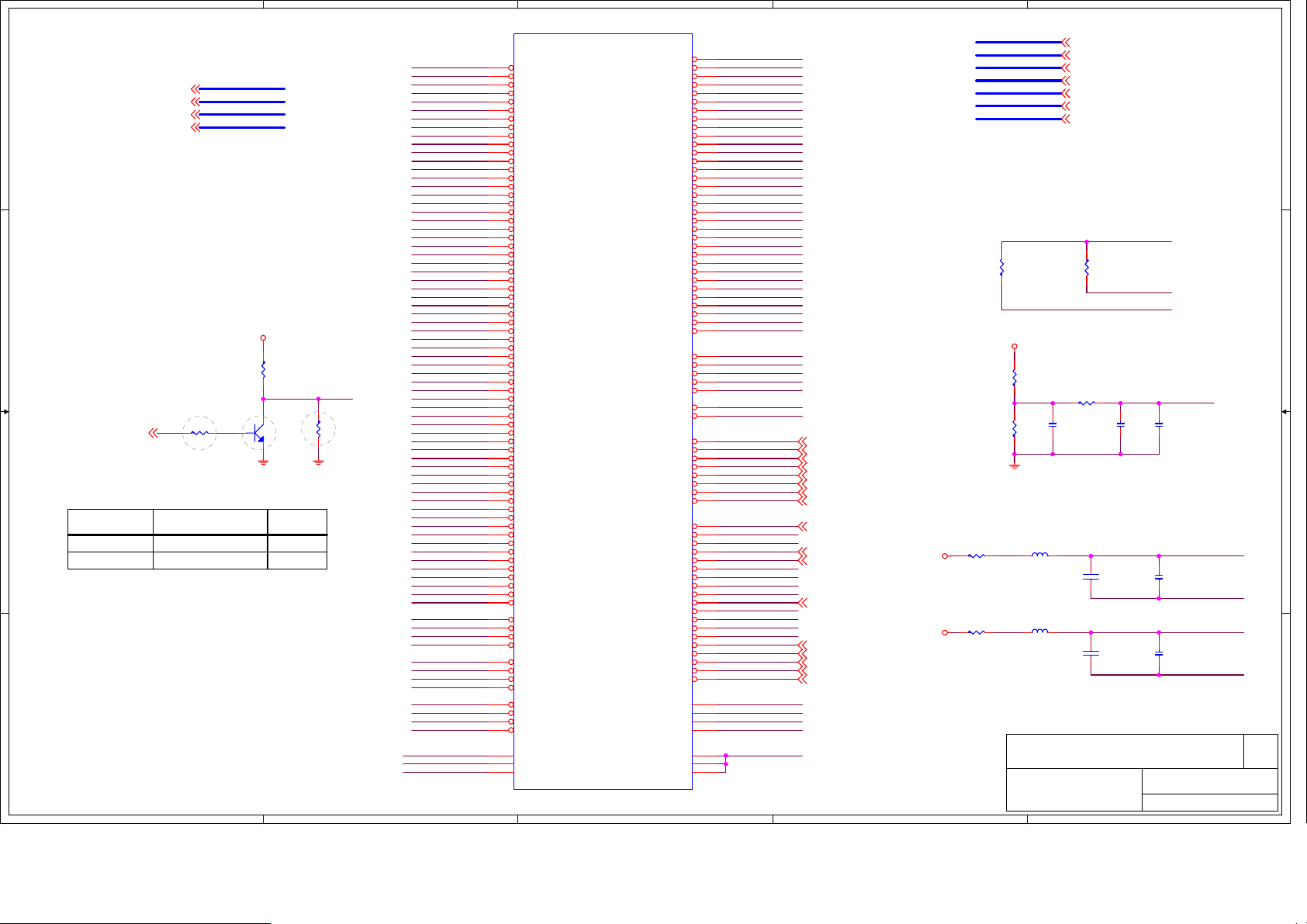

Page 4

Power Block Diagram

1

+12V3

16A/18Apk

+12V2

16A/18Apk

+12V1

16A/18Apk

P12V3 P5VSB

CPU VREG

VR11

P12V2

CPU VREG

VR11

P12V1

1.8V FBD

VREG

VCORE0

VCORE0

P1V8

0.9V FBD

VTT VREG

CPU0

CPU1

12 FBDs

F_VTT

150A

150A

95.52A

FBD VTT

3.48A

5VSBY

3A/3.5Apk

+3V3

24A

P3V3

3.3VSB

VREG

SWITCH

P3VSB

P3V3_AUX

AUX1.5V

VREG

Active:2A

Standby:1A

AUX1.8V1

Active:0.85A

VREG

Standby:0.24A

AUX1.2V1

Active:0.58A

VREG

Standby:0.05A

ESB2

0.066A

P1V5_AUX

P1V8LAN

P1V2LAN

ESB2

1.4A

GILGAL

0.85A

GILGAL

0.58A

PCI-E & PCI-X slots

PCI-E & PCI-X slots

A A

+5V

30A

P5V

1.5V VREG

FSB VTT

VREG

P1V5

P_VTT

1.2V ?A

MCH

12 FBDs

ESB2

CPU 0/1 VTT

19.1A

5.8A

48A

8A

PILOT

0.05A

AUX1.8V2

VREG

AUX1.2V2

VREG

P1V8_AUX

P1V2_AUX

PILOT

PILOT

USB *6

3A

PCI-X Slot

MCH

4.8A

ESB2

1.8A

5A

PCI-E & PCI-X slots

1

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

Power Block Diagram

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

490

Rev

0A

of

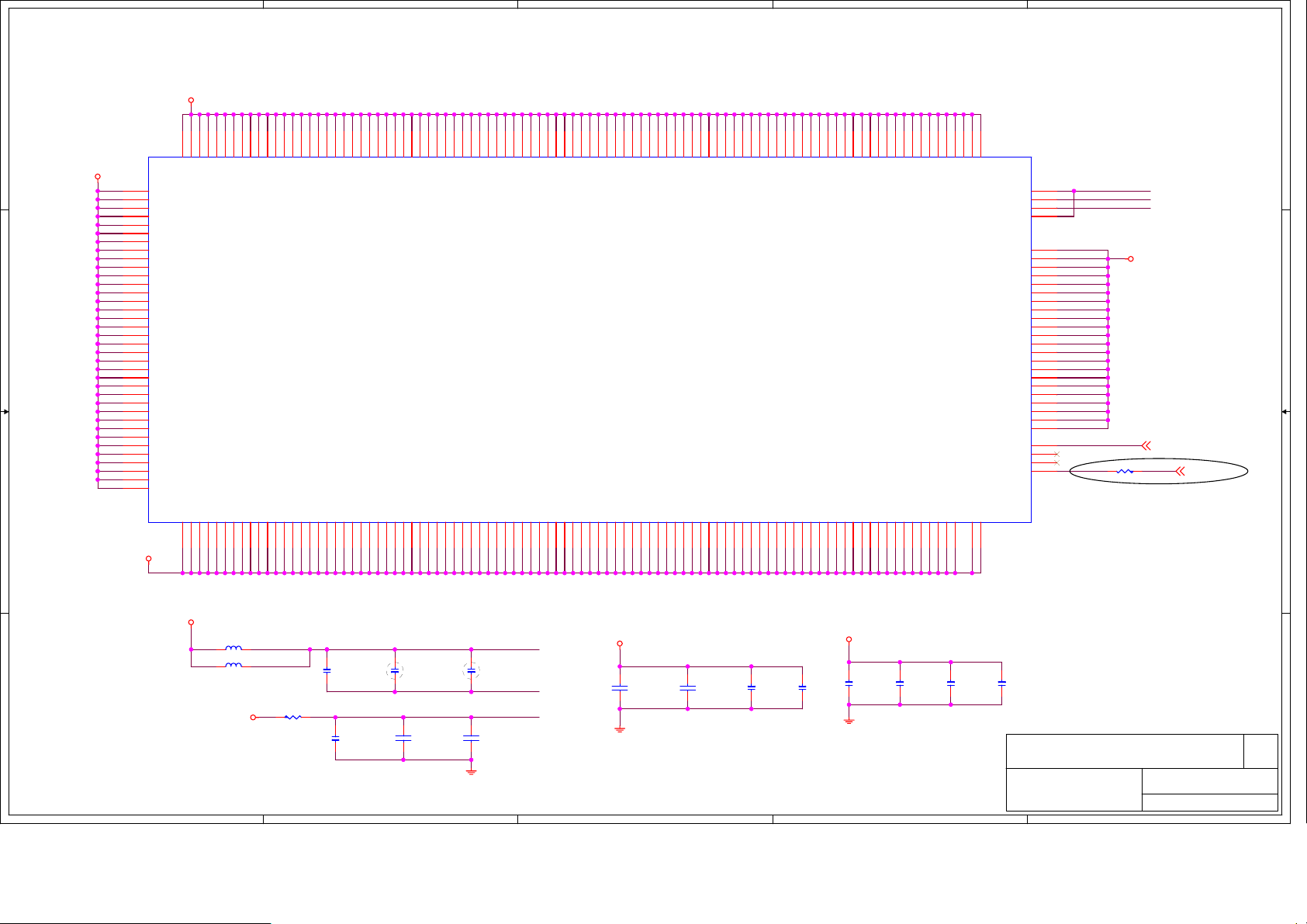

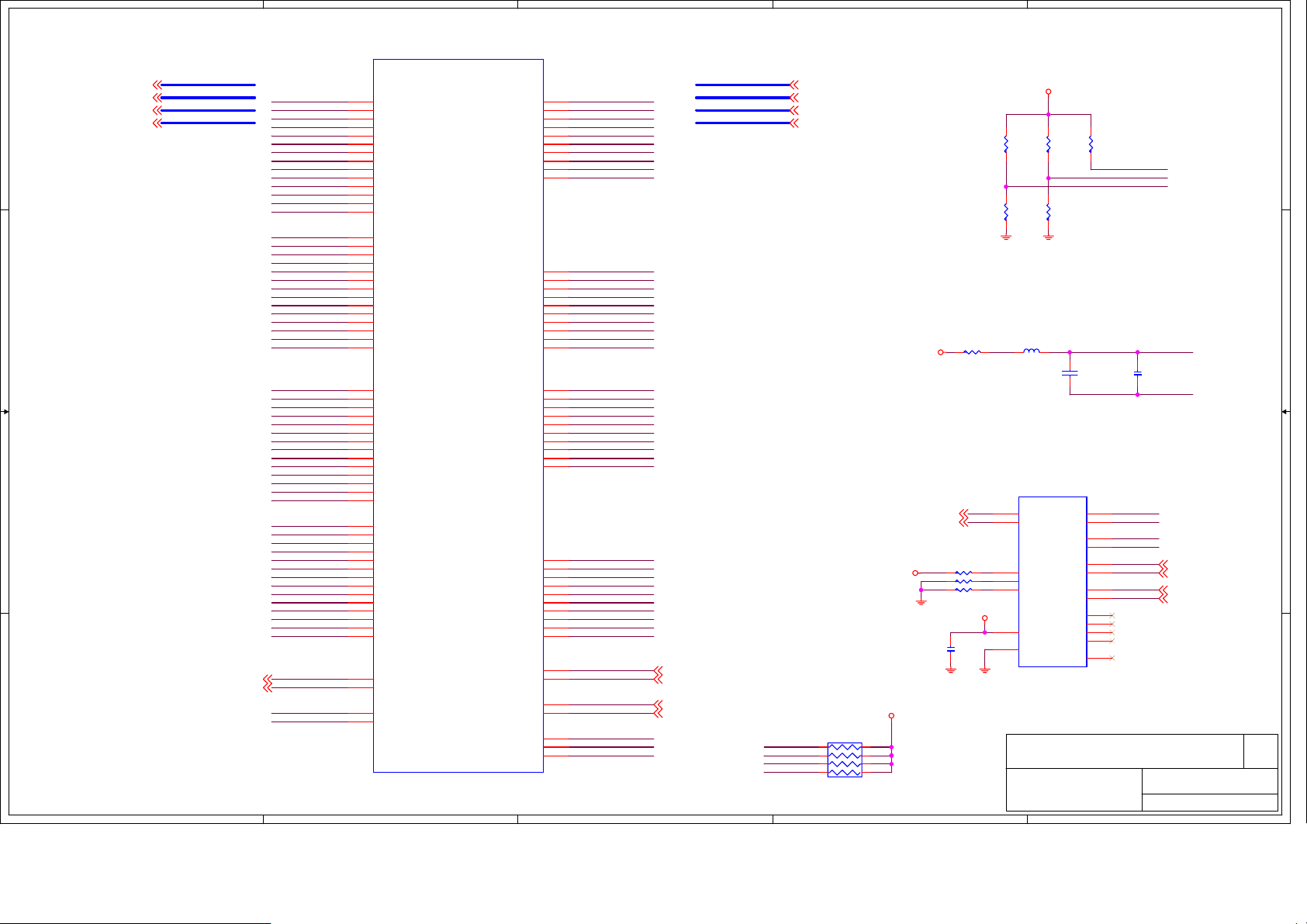

Page 5

Clock Block Diagram

1

2

CK_H_FBD0_P/N

CK_H_FBD1_P/N

CK_H_FBD2_P/N

CK_H_FBD3_P/N

CK_H_FBD4_P/N

CK_H_FBD5_P/N

CK_H_FBD6_P/N

CK_H_FBD7_P/N

CK_H_FBD8_P/N

CK_H_FBD9_P/N

CK_H_FBD10_P/N

CK_H_FBD11_P/N

PILOT

REFCLKP/N

2

REFCLKP/N

2

REFCLKP/N

2

DB1900

DIF_0P/N

DIF_1P/N

CK410B

CPU_1P/N

CPU_2P/N

CK_H_P0 (267/333MHz)

CK_H_P1 (267/333MHz)

BCLK0/1

2

BCLK0/1

2

CPU0

CPU1

XDP (CPU)

XDP0_BCLK_P/N

CLK

2

DIF_17P/N

DIF_2P/N

DIF_3P/N

DIF_4P/N

DIF_5P/N

USB_48

PCIF_1

REF_1

CK_H_FBD (267/333MHz)

CK_H_MCH (267/333MHz)

MCH_100CLK_P/N (100MHz)

SRC_100CLK_P/N (100MHz)

ESI_100CLK_P/N (100MHz)

ESB2_100CLK_P/N (100MHz)

SATA_100CLK_P/N (100MHz)

CK_48M_ESB

ESB2_PCLK

ESB_14MHZ

Blackford

FBD01CLKP/N

CORECLKP/N

2

2

2

2

PECLKP/N

32.768KHz

Crystal

ESICLK100P/N

PECLKP/N

SATACLKP/N

CLK48

PCICLK

CLK14

FBD23CLKP/N

2

ESB2

SER_CLK_IN

PXPCLKO_0

PXPCLKO_1

2

2

SK_LAN_CLK

PXPCLK0

PXPCLK1

62.5MHz

OSC

FBD01CLK_P/N

FBD23CLK_P/N

2

Gilgal LAN

PHY_CLK_OUT

25MHz

Crystal

SRC_INP/N

DB800

CLK

CLK

CPU_3P/N

CPU_0P/N

BCLK 267/333MHz

SRC_4P/N

SRC_0P/N

SRC_2P/N

SRC_1P/N

A A

SRC_3P/N

Serial Ref Clk 100MHz

CLK_INP/N

2

DIF_15P/N

DIF_16P/N

DIF_5P/N

PCIE_SAS_SRC_P/N

ESB:PCI-X 133

ESB:PCI-X 133

DIF_2P/N

DIF_6P/N

DIF_7P/N

DIF_6P/N

DIF_7P/N

DIF_8P/N

DIF_9P/N

DIF_10P/N

DIF_11P/N

PCIE2_100CLK_P/N0

PCIE1_100CLK_P/N0

PCIE1_100CLK_P/N1

2

2

2

2

2

2

2

2

2

2

2

2

ESB:PCI-E X8

ESB:PCI-E X8

ESB:PCI-E X8

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

SCKP/N

FB DIMM00

FB DIMM01

FB DIMM02

FB DIMM10

FB DIMM11

FB DIMM12

FB DIMM20

FB DIMM21

FB DIMM22

FB DIMM30

FB DIMM31

FB DIMM32

14.318MHz

Crystal

PCIF_2

PCI_0

PCI_3

PCIF_0

PCI_2

SIO_PCLK

FWH_PCLK

PLD_33MHZ_CLK

XDP0_33MHZ_CLK

DEBUG_33MHZ_CLK

CK_48M_PILOT

FWH

CLK

PLD

GCK1

XDP (CPU)

CLK

LPC DBG

CLK

CLKI

LCLK

PILOT

48MHz OSC

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

1

http://www.msi.com.tw

Micro Star Restricted Secret

Clock Block Diagram

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

590

Rev

0A

of

Page 6

SMBus Block Diagram

1

DIMM #00

Serial EEPROM: 0XA0

AMB:ADDR 0XB0

CLK410B

ADDR 0XD2

Blackford

DB800

ADDR 0XDC

DB1900

ADDR 0XDE

CPU XDP

CPU0 VCORE

VRD11

ADDR

CPU1 VCORE

A A

VRD11

ADDR

MAIN_SMB

0 ohm

ADDR

3.3V

ESB2

SDTA/SCLK

(0XC2)

SPD0SDA/SPD0SCL

(Master SPD, 100KHz)

SPD1SDA/SPD1SCL

(Master SPD, 100KHz)

SPD2SDA/SPD2SCL

(Master SPD, 100KHz)

SPD3SDA/SPD3SCL

(Master SPD, 100KHz)

CFGSMBDATA/CFGSMBCLK

(Slave, 100KHz, 0XC0)

3.3V

3.3V

3.3V

3.3V

3.3V

DIMM #10 DIMM #11 DIMM #12

Serial EEPROM: 0XA0

AMB:ADDR 0XB0

DIMM #20

Serial EEPROM: 0XA0

AMB:ADDR 0XB0

DIMM #30 DIMM #31 DIMM #32

Serial EEPROM: 0XA0

AMB:ADDR 0XB0

MCH_SPD0_SMB

MCH_SPD1_SMB

MCH_SPD2_SMB

MCH_SPD3_SMB

PCI-E X8 Slot

PCI-E X8 Slot

1.8V VREG

ADDR

PCA9515

SMBus Isolator

3.3V AUX

SMBDATA/SMBCLK

PCA9515

SMBus Isolator

280 PIN PCI-X & PCI-E Slot

WHEA ROM

ADDR 0XAE

IPMB Header

5VSB

PCA9515

SMBus Isolator

3.3V AUX

3.3V AUX

SDA4/SCL4

SDA0/SCL0

3.3V AUX

SDA1/SCL1

SDA2/SCL2

3.3V AUX

DIMM #01

Serial EEPROM: 0XA2

AMB:ADDR 0XB2

Serial EEPROM: 0XA2 Serial EEPROM: 0XA4

AMB:ADDR 0XB2

DIMM #21

Serial EEPROM: 0XA2

AMB:ADDR 0XB2

Serial EEPROM: 0XA2 Serial EEPROM: 0XA4

AMB:ADDR 0XB2

DIMM #02

Serial EEPROM: 0XA4

AMB:ADDR 0XB4

AMB:ADDR 0XB4

DIMM #22

Serial EEPROM: 0XA4

AMB:ADDR 0XB4

AMB:ADDR 0XB4

HW Monitor

ADT7462

ADDR 0X5C

HW Monitor

ADT7462

ADDR 0X5C

FRU ROM

ADDR 0XAE

SDA0/SCL0

SMBus

Selector

SDA1/SCL1

SDA2/SCL2

SDA3/SCL3

SDA/SCL

BackPanel

Power

ADDR

5VSB

PCA9515

SMBus Isolator

3.3V AUX

Front Panel

Thermal Sensor

ADDR

SDA3/SCL3

PILOT

1

SDA5/SCL5

3.3V AUX

PCA9515

SMBus Isolator

PECI

CY8C21234

ADDR 0X

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

SMBus Block Diagram

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

690

Rev

0A

of

Page 7

JTAG Block Diagram

1

XDP0_TDI_FSB1

P_VTT

51 OHM

P_VTT

51 OHM

1

2

1

3

4

GTL-TTL

Translator

TRST#

TDO

TDI

TMS TRST#

TDI

CPU1

XDP0_TDO_FSB1

TDO

TCK

51 OHM

GND

XDP0_TDI_ESB

XDP0_TRST_ESB#

1K OHM

GND

P_VTT

51 OHM

TDI

TRST#

XDP0_TMS_ESB

TMS

TMS

ESB2

GTL-TTL

Translator

ESB2 in chain

TDO

TCK

XDP0_TCK1_ESB

TCK

JUMPER 0

1-2, 3-4 : CPU0 in chain

2-3 : CPU0 bypass

JUMPER 1

1-2, 3-4 : CPU1 in chain

2-3 : CPU1 bypass

P3V3

1K OHM

1K OHM

P_VTT

XDP0_TDI_MAIN

TDI

TCK0

CPU XDP0

Connector

TDO

TMS

TRST#

A A

TCK1

0 OHM

51 OHM

XDP0_TDI_FSB0

P_VTT

51 OHM

XDP0_TDI_MCH

1

2

3

4

TDI

TMS TRST#

0

TDI

TMS

CPU0

XDP0_TCK0

XDP0_TDO_FSB0

XDP0_TDI_MAIN_JMP

XDP0_TDO_MAIN

XDP0_TMS_MAIN

XDP0_TRST#

TRST#

MCH

TCK

TDO

TCK

TDO

MCH in chain

51 OHM

GND

XDP0_TDO_MCH

P_VTT

51 OHM

51 OHM

GND

XDP0_TCK1

P_VTT

51 OHM

1

XDP0_TMS_GTL

XDP0_TDO_ESB

0 OHM

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

GND

JTAG Block Diagram

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

Rev

0A

of

790

Page 8

System Reset Block Diagram

1

VRM0_PWRGD

CK410B

PWRDOWN

DB800

PWRDOWN_N

CPU_VRD_PWRGD

EPLD

CPU0_SKTOCC#

VRM1_PWRGD

CPU1_SKTOCC#

POWER SUPPLY

PWOK

PSON#

ONCTL#

VDDPWR_GD

EPLD

PS_PWROK_BUF

GPIO8

PWBTOUTn

SLPS3n

SLPS5n

PILOT

CPU_VRD_PWRGD

EPLD

100 ms

Delay

PWR_BT_SSI_#

SYS_PWRGD_BUFF

3.3V STBY

SYS_PWRGD_3_3V

RSMRST#

PWRBTN_N

SLP_S3_N

SLP_S4_N

PERST_N

PXPWROK

PWROK

VRMPWRGD

RSMRST_N

LAN_PWR_GD

PWR BTN

3.3VAUX

10Kohms

GND

PWR_BT_IN#

A A

PLTRST_BUFF1#

THERMTRIP0_N

THERMTRIP1_N

ONCTLn

PWBTINn

PCIRSTn

GPIO19

GPIO20

RST BTN

10Kohms

GND

ESB_SYS_RST_N

SYS_RESET_N

ESB2

PHY_PWR_DOWN PHYRST_0_N

PHY_PWR_GD

Pwrgd

CPU1 VRD

Pwrgd

3.3VAUX

CPU_PWR_GD

PLTRST_IN_N

PXPCIRST_N

THRMTRIP_N

PHY_RESET_NPHY_SLEEP

CPU0 VRD

OE

VID[6..0]

OE

VID[6..0]

INIT_N

INIT3_3V_N

PLTRST_N

PCIRST_N

GPIO33

THERMTRIP_N

VRD0_EN

P0VID[6..0]

VRD1_EN

P1VID[6..0]

CPU_PWRGD

INIT#_3_3V

ESB_PLTRST#

PXPCIRST_N

EPLD

CPU0

EPLD

CPU1

FSB_INIT#

FWH

INIT#

RST_N

PLTRST_BUFF1#

EPLD

280 Pin Slot, SAS 1068

FBD_RESET

ESB_SYS_RST_N

PLTRST_N

DBR_N

INIT_N

PWRGOOD

DBR_N

INIT_N

PWRGOOD

IDE_RSTDRV_N

IDE

CPU0

CPU1

Blackford

PLTRST_N

FSB VTT VRD

VTTPWRGD

THERMTRIP_N

RESET#

VTTPWRGD

THERMTRIP_N

RESET#

FSB1RESET_N

FSB0RESET_N

PWRGOOD

SYS_PWRGD_3_3V

EPLD

SYS_PWRGD_3_3V

FBD_BR0_RST#

GLUE

FBD_BR1_RST#

LOGIC

STAT

VTT_PWRGD

FSB0_THERMTRIP_N

FSB1_THERMTRIP_N

FSB1_RESET_N

FSB0_RESET_N

DIMM#00,01,02,10,11,12

DIMM#20,21,22,30,31,32

Level

Translation

GTL to 3.3V

Level

Translation

3.3V to GTL

ESB_SYS_RST_N

RESET_IN#

PWRGOOD

VTT_PWRGD_3_3V

PLD_VTT_PWRGD_3_3V

GLUE

LOGIC

RESET_OUT#

XDP

EPLD

THERMTRIP_N

THERMTRIP0_N

THERMTRIP1_N

ESB2

PILOT

Gilgal

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

1

http://www.msi.com.tw

Micro Star Restricted Secret

System Reset Block Diagram

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

890

Rev

0A

of

Page 9

5

4

3

2

1

P0 Intel LGA771 Signal

VCC0_SENSE2

VSS0_SENSE2

VCC0_SENSE1

D11

FSB0_D15

D14#

C12

FSB0_D14

FSB0_D13

AL7

AL8

VSS_DIE_SENSE2

VCC_DIE_SENSE2

D13#

D12#D8D11#

B12

FSB0_D12

AN3

VCC_DIE_SENSE

C11

FSB0_D11

AN4

VSS_DIE_SENSE

D10#

B10

FSB0_D10

FSB0_D9

VSS0_SENSE1

D9#

D8#

A11

A10

FSB0_D8

FSB0_A[35..3]15

FSB0_DBI#[3..0]15

FSB0_RESET_N15

FSB0_RSP_N15

FSB0_BPRI_N15

FSB0_TRDY_N15

FSB0_DEFER_N15

FSB0_FORCEPR#69

FSB_IGNNE#12,40

FSB_STPCLK#12,40

XDP0_TDI_FSB064

XDP0_TDO_FSB064

XDP0_TMS_MAIN12,20,64

XDP0_TRST#12,20,64

FSB0_GTL_IERR#62

FSB0_PROCHOT#65

FSB0_ADS_N15

FSB0_BNR_N15

FSB0_HIT_N15

FSB0_DBSY_N15

FSB0_DRDY_N15

FSB0_HITM_N15

FSB0_LOCK_N15

FSB0_BINIT_N15

FSB0_MCERR_N15

CPU0_SKTOCC#54,62,63,65

P0THERMDA265

P0THERMDC265

P0THERMDA65

P0THERMDC65

CPU_DBR_RST#12,64

R1208 0

FSB0_VIDSEL63,69

FSB0_BSEL062

FSB0_BSEL162

FSB0_BSEL262

FSB0_D[63..0]15

FSB_A20M#12,40

FSB_NMI12,40

FSB_INTR12,40

FSB_INIT#12,40,67

XDP0_TCK012,64

FSB_FERR#12,40

P0_MS_ID163

P0_MS_ID063

CPU_DBR_RST#

P0_THERMTRIP_N

D D

C C

CPU1_TESTBUS12

B B

A A

FSB0_A[35..3]

FSB0_DBI#[3..0]

FSB0_D[63..0]

FSB0_DBI#0

FSB0_DBI#1

FSB0_DBI#2

FSB0_DBI#3

FSB0_RESET_N

FSB0_RSP_N

FSB0_BPRI_N

FSB0_TRDY_N

FSB0_DEFER_N

CPU0_SMI_N

FSB_A20M#

FSB0_FORCEPR#

FSB_NMI

FSB_INTR

FSB_IGNNE#

FSB_STPCLK#

FSB_INIT#

XDP0_TCK0

XDP0_TDI_FSB0

XDP0_TDO_FSB0

XDP0_TMS_MAIN

XDP0_TRST#

FSB0_GTL_IERR#

FSB_FERR#

FSB0_PROCHOT#

P0_THERMTRIP_N

FSB0_ADS_N

FSB0_BNR_N

FSB0_HIT_N

FSB0_DBSY_N

FSB0_DRDY_N

FSB0_HITM_N

FSB0_LOCK_N

FSB0_BINIT_N

FSB0_MCERR_N

CPU0_SKTOCC#

P0THERMDA2

P0THERMDC2

P0THERMDA

P0THERMDC

CPU_DBR_RST#

CPU0_BOOT

CPU0_TESTBUS

P0_LL_ID1

P0_LL_ID0

P0_MS_ID1

P0_MS_ID0

FSB0_BSEL0

FSB0_BSEL1

FSB0_BSEL2

FSB0_D63

FSB0_D62

FSB0_D61

FSB0_D60

FSB0_D59

FSB0_D58

FSB0_D57

FSB0_D56

FSB0_D55

FSB0_D54

R712 0

R720 2.2

A8

DBI0#

G11

DBI1#

D19

DBI2#

C20

DBI3#

G23

RESET#

H4

RSP#

G8

BPRI#

E3

TRDY#

G7

DEFER#

P2

SMI#

K3

A20M#

AK6

FORCEPR#

L1

LINT1/NMI

K1

LINT0/INTR

N2

IGNNE#

M3

STPCLK#

P3

INIT#

AE1

TCK

AD1

TDI

AF1

TDO

AC1

TMS

AG1

TRST#

AB2

IERR#

R3

FERR#/PBE#

AL2

PROCHOT#

M2

THERMTRIP#

D2

ADS#

C2

BNR#

D4

HIT#

B2

DBSY#

C1

DRDY#

E4

HITM#

C3

LOCK#

AD3

BINIT#

AB3

MCERR#

AE8

SKTOCC#

AJ7

THERMDA2

AH7

THERMDC2

AL1

THERMDA

AK1

THERMDC

AC2

DBR#

Y1

BOOTSELECT

AH2

TEST_BUS

AN7

VID_SELECT

AA2

LL_ID1

V2

LL_ID0

V1

MS_ID1

W1

MS_ID0

G29

BSEL0

H30

BSEL1

G30

BSEL2

B22

D63#

A22

D62#

A19

D61#

B19

D60#

B21

D59#

C21

D58#

B18

D57#

A17

D56#

B16

D55#

C18

D54#

FSB0_D53

ESB_SYS_RST# 40,54,67,68

FSB0_THERMTRIP_N 61

B15

D53#

FSB0_D52

C14

D52#

FSB0_D51

C15

D51#

A14

FSB0_D50

D50#

D17

FSB0_D49

FSB0_A35

D49#

FSB0_D48

AJ6

D20

A35#

D48#

FSB0_A33

FSB0_A34

AJ5

A34#

D47#

G22

FSB0_D46

FSB0_D47

AH5

D22

FSB0_A32

A33#

D46#

FSB0_D45

AH4

E22

FSB0_A31

A32#

D45#

FSB0_D44

AG5

G21

FSB0_A30

AG4

A31#

D44#

F21

FSB0_D43

FSB0_A29

AG6

A30#

D43#

E21

FSB0_D42

FSB0_A28

A29#

D42#

FSB0_D41

AF4

F20

FSB0_A27

AF5

A28#

D41#

E19

FSB0_D40

A27#

D40#

FSB0_A26

AB4

A26#

D39#

E18

FSB0_D39

FSB0_A25

AC5

A25#

D38#

F18

FSB0_D38

FSB0_A24

AB5

A24#

D37#

F17

FSB0_D37

FSB0_A23

AA5

A23#

D36#

G17

FSB0_D36

FSB0_A22

AD6

A22#

D35#

G18

FSB0_D35

FSB0_A21

FSB0_D34

FSB0_A19

AA4

A21#

A20#Y4A19#Y6A18#W6A17#

FSB0_A17

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

FSB0_A11

FSB0_A12

FSB0_A13

FSB0_A18

FSB0_A14

FSB0_A16

FSB0_A20

FSB0_A15

LGA771

PART 1

FSB Signal

D34#

D33#

D32#

D31#

D30#

D29#

D28#

D27#

D26#

D25#

D24#

F15

F14

FSB0_D30

G14

FSB0_D29

FSB0_D27

FSB0_D28

G13

E13

FSB0_D25

FSB0_D26

D13

F12

FSB0_D24

E16

E15

FSB0_D33

FSB0_D32

G16

G15

FSB0_D31

FSB0_A10

FSB0_A8

FSB0_A9

U6

A9#T5A8#R4A7#M4A6#L4A5#L5A4#P6A3#

D23#

D22#

D21#

F11

E10

D10

FSB0_D22

FSB0_D23

FSB0_D21

FSB0_A7

FSB0_A4

FSB0_A3

FSB0_A6

FSB0_A5

M5

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

FSB0_D17

FSB0_D19

FSB0_D20

FSB0_D18

FSB0_D16

P0VID5

P0VID6

P0VID4

P0VID3

AM5

AL4

AK4

AL6

VID6

VID5

VID4

GTLREF_DATA_C1

GTLREF_ADD_C1

GTLREF_DATA_C0

GTLREF_ADD_C0

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

FSB0_D5

FSB0_D7

FSB0_D2

FSB0_D3

FSB0_D4

FSB0_D1

FSB0_D6

R1273 0

R1274 0

R1275 0

R1276 0

P0VID1

P0VID0

P0VID2

AM3

AL5

AM2

VID3

VID2

VID1

VID0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1

BCLK0

RS2#

RS1#

RS0#

AP1#

AP0#

BR1#

BR0#

PWRGOOD

COMP7

COMP6

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

TEJAS

B4

FSB0_D0

CPU1A

CPU0_DISABLE_N54,65

P0_GTLREF_DATA1

F2

P0_GTLREF_ADD1

H2

P0_GTLREF_DATA0

G10

P0_GTLREF_ADD0

H1

FSB0_BPM_N5

AG3

FSB0_BPM_N4

AF2

FSB0_BPM_N3

AG2

FSB0_BPM_N2

AD2

FSB0_BPM_N1

AJ1

FSB0_BPM_N0

AJ2

FSB0_REQ_N4

J6

FSB0_REQ_N3

K6

FSB0_REQ_N2

M6

FSB0_REQ_N1

J5

FSB0_REQ_N0

K4

H_TESTHI11

L2

H_TESTHI10

P1

FSB0_BPMB_N2

G4

FSB0_BPMB_N3

G3

F24

G24

G26

G27

G25

F25

W3

F26

CK_H_P0_N

G28

CK_H_P0

F28

FSB0_RS2_N

A3

FSB0_RS1_N

F5

FSB0_RS0_N

B3

FSB0_AP1

U3

FSB0_AP0

U2

FSB0_BR_N1

H5

FSB0_BR_N0

F3

CPU_PWRGD

N1

H_COMP7

AE3

H_COMP6

Y3

H_COMP5

T2

H_COMP4

J2

H_COMP3

R1

H_COMP2

G2

H_COMP1

T1

H_COMP0

A13

FSB0_DP_N3

J17

FSB0_DP_N2

H16

FSB0_DP_N1

H15

FSB0_DP_N0

J16

FSB0_ADSTB_N1

AD5

FSB0_ADSTB_N0

R6

FSB0_DSTBP_N3

C17

FSB0_DSTBP_N2

G19

FSB0_DSTBP_N1

E12

FSB0_DSTBP_N0

B9

FSB0_DSTBN_N3

A16

FSB0_DSTBN_N2

G20

FSB0_DSTBN_N1

G12

FSB0_DSTBN_N0

C8

FSB_SMI#12,40,54

VCC0_SENSE 69

VSS0_SENSE 69

P0VID[6..0]

FSB0_BPM_N[5..0]

FSB0_REQ_N[4..0]

FSB0_DP_N[3..0]

FSB0_ADSTB_N[1..0]

FSB0_DSTBP_N[3..0]

FSB0_DSTBN_N[3..0]

R727 51

R728 51

R729 51

R730 51

H_TESTHI2

R731 51

H_TESTHI1

R732 51

CK_H_P0_N 58

CK_H_P0 58

FSB0_RS2_N 15

FSB0_RS1_N 15

FSB0_RS0_N 15

FSB0_AP1 15

FSB0_AP0 15

FSB0_BR_N1 15

FSB0_BR_N0 15

CPU_PWRGD 12,40,64

R705 49.9RST

R706 49.9RST

R734 49.9RST

R736 49.9RST

R737 49.9RST

R738 49.9RST

R739 49.9RST

R740 49.9RST

P_VTT

CPU0 SMI Voltage Translation

R1385

220

6

1

FSB0_BPMB_N2

FSB0_BPMB_N3

P_VTT

U3026

VCC

A

B4C

BE

GND

PI5C3303

P0VID[6..0] 69

FSB0_BPM_N[5..0] 15,64

FSB0_REQ_N[4..0] 15

FSB0_DP_N[3..0] 15

FSB0_ADSTB_N[1..0] 15

FSB0_DSTBP_N[3..0] 15

FSB0_DSTBN_N[3..0] 15

FSB0_BPMB_N2 64

FSB0_BPMB_N3 64

P_VTT

Place BPMB Termination Near CPU

P_VTT

Max Length 1.2 inches

C1033

X_0.1u

P_VTT

R3387

X_220

2

5

3

P5V

CPU0_SMI_N

49.9RST

100RST

49.9RST

100RST

BE=High, C=B

5

4

3

2

Processor 0 Termination

Place Termination Close to CPU At End of Bus

P_VTT

R713 51

R714 51

R715 51

R717 51

R718 51

R719 51

R716 X_51

R735 X_51

R1380 X_220

R1381 X_220

R1382 X_220

R1383 X_220

R1384 X_220

R1386 220

R1277 300

R3384 510

R3385 510

R3386 510

P3V3_AUX

R1219 4.7K

Place BPM Termination Near CPU

P_VTT

R721 51

R722 51

R723 51

R724 51

P0_LL_ID0

P0_LL_ID1

P0_MS_ID1

P0_MS_ID0

P_VTT

800mV at 1.2V FSB Vtt

Minmum trace and width as wide as possible

12 mils

R742

P0_GTLREF_ADD0

R743

C1034

1u

P_VTT

800mV at 1.2V FSB Vtt

Minmum trace and width as wide as possible

R744

12 mils

P0_GTLREF_ADD1

R751

C1037

1u

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

RB1

0

C1035

220P

RB2

0

C1038

220P

P0 Intel LGA771 Signal

MS-9192

FSB0_BR_N1

FSB0_BR_N0

FSB0_GTL_IERR#

FSB0_THERMTRIP_N

FSB_FERR#

FSB0_RESET_N

FSB0_PROCHOT#

CPU0_BOOT

FSB_A20M#

FSB_STPCLK#

FSB_IGNNE#

FSB_INIT#

FSB_INTR

FSB_NMI

CPU_PWRGD

FSB0_BSEL0

FSB0_BSEL1

FSB0_BSEL2

CPU0_SKTOCC#

FSB0_BPM_N3

FSB0_BPM_N2

FSB0_BPM_N1

FSB0_BPM_N0

R1206

X_4.7K

R703 X_51

R704 X_51

P0_GTLREF_DATA0

C1036

220P

P0_GTLREF_DATA1

C1039

220P

Last Revision Date:

Friday, April 27, 2007

Sheet

990

1

P3V3

R1207

X_4.7K

of

Rev

0A

Page 10

5

P0 Intel LGA771 Power

4

3

2

1

VCORE0

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCORE0

AF22

AF21

VCC

VCC

VCC

VCC

Y8

Y30

AF8

Y29

AF9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y23

Y24

Y25

Y26

Y27

Y28

W30

W29

W28

W27

W26

W25

W24

W23

U25

U26

U27

U28

U29

U30

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCIOPLL

LGA771

PART 2

Power

VTTPWRGD

VTT_OUT1

VTT_OUT0

VCC

VCC

NONE

NONE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCT8VCC

VCC

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

T30

U23

U24

N29

N30

N23

N24

N25

N26

N27

N28

M29

M30

M23

M24

M25

M26

M27

M28

K30

K29

K28

K27

K26

T23

T24

T25

T26

T27

T28

T29

K25

K24

K23

J30

AN8

AN9

AN25

AN26

AN29

AN30

VCCA

VSSA

VCCPLL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT_SEL

TEJAS

A23

B23

D23

C23

F30

E30

A25

A26

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

H0_VCCA

H0_VSSA

H0_VCCPLL

VTT_PWRGD

R3472 0

P_VTT

VTT_PWRGD 13,63

VTT_SELVTT_SEL0

Support

Harpertown

&

Wolfdale

CPU

VTT_SEL 13,76

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

D D

VCORE0

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

C C

B B

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

P_VTT

L17 10uH-0805-0.1A

L18 10uH-0805-0.1A

A A

5

Minmum trace and width as wide as possible

< 12 mils

C3128

22u-1206

P1V5

R62

0

C1020

103P

C3129

X_10u-1206

C1021

4.7u-0805

H0_VCCA

C1019

X_1u

H0_VSSA

H0_VCCPLL

C1022

4.7u-0805

4

P_VTT

C1029

10u-1206

C1030

10u-1206

3

C1031

0.1u

C1032

0.1u

P_VTT

C1025

0.1u

C1026

0.1u

C1027

0.1u

2

C1028

0.1u

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

P0 Intel LGA771 Power

Micro Star Restricted Secret

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

1

10 90

of

Rev

0A

Page 11

5

P0 Intel LGA771 GND

4

3

2

1

R702

B13

RESVDF6RESVD

VSS

VSS

AF3

AF30

R702

X_49.9RST

P5

E1

RESVDJ3RESVDN4RESVD

RESVD

VSS

VSS

VSS

AF6

AF7

AG10

AG13

Nocona-T

Optional

VSS

AG16

D D

R555

C C

B B

X_0-0402

R1212

X_0

FSB0_BPMB_N1

F1

A12

A15

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D16

RESVDC9RESVD

VSS

VSS

AE29

AE30

A20

AE5

P0TESTIN

W2

RESVD

VSS

AE7

VSS

AC4

AE4

D14

E23

RESVD

VSS

VSS

AF24

AF25

F23

RESVDE5RESVDE6RESVDE7RESVD

VSS

VSS

VSS

AF26

AF27

AF28

AF29

VSS

E24

RESVD

RESVD

RESVDD1RESVD

RESVDG6RESVD

RESVDG5RESVD

VSS

VSS

VSS

VSS

VSS

VSS

AF10

AF13

AF16

AF17

AF20

AF23

Dempsey-T Dempsey/Woodcrest

Stuffed No Stuffed

AN27

AN6

RESVD

VSS

AG23

AJ3

RESVD

VSS

AG24

AK3

RESVD

VSS

AG7

F29

RESVD

VSS

AH1

AN28

NONE

NONE

VSS

VSS

VSS

AH10

AH13

AH16

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

AH17

AH20

AH23

AE6

AN5

RESVDN5RESVD

RESVD

VSS

VSS

VSS

AG17

AG20

TP92

V30

V29

VSSV3VSS

V28

VSS

V27

VSS

V26

V25

VSS

P0TESTIN

V24

V23

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

R733 51

P_VTT

R30

R29

R28

R27

R26

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

P23

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

L30

L29

VSSL3VSS

L28

VSS

L27

VSS

L26

L25

VSS

LGA771

PART 3

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AH3

AH6

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AH24

AJ30

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

AL24

AL27

AL28

AL3

AM1

AM10

AM13

AM16

AM17

AM20

AM23

AN1

AM4

AM7

AN10

AM24

AM27

AN13

AM28

Place BPMB Termination Near CPU

R745 51

VSS

VSS

AN24

R746 51

VSSB5VSS

VSSB1VSS

B8

B11

B14

VSS

VSS

B17

P_VTTRSVD_PECI 14,55,66

L24

L23

VSS

VSS

VSS

VSSK7VSSK5VSSK2VSSJ7VSSJ4VSSH9VSSH8VSSH7VSSH6VSSH3VSS

VSS

VSS

VSS

VSS

VSS

AN2

AN16

AN17

AN20

AN23

H29

VSS

B20

H28

B24

H27

VSS

VSS

FSB0_BPMB_N1

FSB0_BPMB_N0

H26

H25

H24

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSC4VSS

TEJAS

C7

CPU1C

H23

H22

H21

H20

H19

H18

H17

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C24

C22

C19

C16

C13

C10

FSB0_BPMB_N1 64

FSB0_BPMB_N0 64

FSB0_BPMB_N0

R556

X_0-0402

A A

Intel Document Title: Enterprise System Design Conference - Taipei

REV. NO. 1.0 REF, NO. 19091

Page 142: For each Socket change new RSVD lands A24 and E29

Page 142: Connect W2 and U1 together on each Socket,

from VSS to no-connects on the motherboard

and terminate with a 51ohms resistor to VTT.

5

4

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

P0 Intel LGA771 GND

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

1

11 90

Rev

0A

of

Micro Star Restricted Secret

Page 12

5

4

3

2

1

P1 Intel LGA771 Signal

VCC1_SENSE2

D11

FSB1_D15

FSB1_D14

D14#

C12

AL8

VCC_DIE_SENSE2

D13#

B12

FSB1_D12

FSB1_D13

AL7

AN3

VCC_DIE_SENSE

VSS_DIE_SENSE2

D12#D8D11#

C11

FSB1_D11

VSS1_SENSE2

VCC1_SENSE1

VSS1_SENSE1

AN4

VSS_DIE_SENSE

D10#

D9#

B10

A11

FSB1_D10

FSB1_D9

FSB1_A[35..3]16

FSB1_DBI#[3..0]16

FSB1_D[63..0]16

D D

FSB1_FORCEPR#71

C C

FSB1_GTL_IERR#62

FSB1_PROCHOT#65

B B

A A

FSB1_A[35..3]

FSB1_DBI#[3..0]

FSB1_D[63..0]

FSB1_A29

A30#

D43#

FSB1_D42

AG6

E21

FSB1_A28

AF4

A29#

D42#

F20

FSB1_D41

A28#

D41#

FSB1_A27

AF5

A27#

D40#

E19

FSB1_D40

FSB1_A26

AB4

A26#

D39#

E18

FSB1_D39

FSB1_A25

AC5

A25#

D38#

F18

FSB1_D38

FSB1_A24

AB5

A24#

D37#

F17

FSB1_D37

FSB1_A23

AA5

A23#

D36#

G17

FSB1_D36

FSB1_A22

FSB1_D35

FSB1_A15

FSB1_A18

FSB1_A14

FSB1_A20

AD6

AA4

A22#

A21#

FSB1_A17

FSB1_A19

AB6

A20#Y4A19#Y6A18#W6A17#

FSB1_A13

FSB1_A12

FSB1_A16

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

LGA771

PART 1

FSB Signal

D35#

D34#

D33#

D32#

D31#

D30#

D29#

D28#

D27#

D26#

F15

F14

E16

G18

FSB1_D33

FSB1_D34

E15

G16

FSB1_D32

G15

FSB1_D31

FSB1_D30

G14

FSB1_D29

FSB1_D28

G13

FSB1_D26

FSB1_D27

E13

D13

FSB1_D25

FSB1_A33

FSB1_A31

FSB1_A30

FSB1_A32

FSB1_A34

FSB1_A35

AJ6

AJ5

AH5

AH4

AG5

AG4

A35#

A34#

A33#

A32#

D50#

D49#

D48#

D47#

D46#

A14

E22

D17

D20

D22

G22

FSB1_D47

FSB1_D46

FSB1_D48

FSB1_D49

FSB1_D45

FSB1_THERMTRIP_N 61

D45#

G21

FSB1_D44

A31#

D44#

F21

FSB1_D43

FSB1_DBI#0

FSB1_DBI#1

FSB1_DBI#2

FSB1_DBI#3

FSB1_RESET_N16,64

FSB1_RSP_N16

FSB1_BPRI_N16

FSB1_TRDY_N16

FSB1_DEFER_N16

FSB_A20M#9,40

FSB_NMI9,40

FSB_INTR9,40

FSB_IGNNE#9,40

FSB_STPCLK#9,40

FSB_INIT#9,40,67

XDP0_TCK09,64

XDP0_TDI_FSB164

XDP0_TDO_FSB164

XDP0_TMS_MAIN9,20,64

XDP0_TRST#9,20,64

FSB_FERR#9,40

FSB1_ADS_N16

FSB1_BNR_N16

FSB1_HIT_N16 CK_H_P1_N 58

FSB1_DBSY_N16

FSB1_DRDY_N16

FSB1_HITM_N16

FSB1_LOCK_N16

FSB1_BINIT_N16

FSB1_MCERR_N16

CPU1_SKTOCC#54,63,65

P1THERMDA265

P1THERMDC265

P1THERMDA65

P1THERMDC65

CPU_DBR_RST#9,64

CPU1_TESTBUS9

FSB1_VIDSEL63,71

P1_MS_ID163

P1_MS_ID063

FSB1_BSEL062

FSB1_BSEL162

FSB1_BSEL262

FSB1_RESET_N

FSB1_RSP_N

FSB1_BPRI_N

FSB1_TRDY_N

FSB1_DEFER_N

CPU1_SMI_N

FSB_A20M#

FSB1_FORCEPR#

FSB_NMI

FSB_INTR

FSB_IGNNE#

FSB_STPCLK#

FSB_INIT#

XDP0_TCK0

XDP0_TDI_FSB1

XDP0_TDO_FSB1

XDP0_TMS_MAIN

XDP0_TRST#

FSB1_GTL_IERR#

FSB_FERR#

FSB1_PROCHOT#

P1_THERMTRIP_N

FSB1_ADS_N

FSB1_BNR_N

FSB1_HIT_N

FSB1_DBSY_N

FSB1_DRDY_N

FSB1_HITM_N

FSB1_LOCK_N

FSB1_BINIT_N

FSB1_MCERR_N

CPU1_SKTOCC#

P1THERMDA2

P1THERMDC2

P1THERMDA

P1THERMDC

CPU_DBR_RST#

CPU1_BOOT

CPU1_TESTBUS

P1_LL_ID1

P1_LL_ID0

P1_MS_ID1

P1_MS_ID0

FSB1_BSEL0

FSB1_BSEL1

FSB1_BSEL2

FSB1_D63

FSB1_D62

FSB1_D61

FSB1_D60

FSB1_D59

FSB1_D58

FSB1_D57

FSB1_D56

FSB1_D55

FSB1_D54

P1_THERMTRIP_N

A8

G11

D19

C20

G23

H4

G8

E3

G7

P2

K3

AK6

L1

K1

N2

M3

P3

AE1

AD1

AF1

AC1

AG1

AB2

R3

AL2

M2

D2

C2

D4

B2

C1

E4

C3

AD3

AB3

AE8

AJ7

AH7

AL1

AK1

AC2

Y1

AH2

AN7

AA2

V2

V1

W1

G29

H30

G30

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

R674 2.2

DBI0#

DBI1#

DBI2#

DBI3#

RESET#

RSP#

BPRI#

TRDY#

DEFER#

SMI#

A20M#

FORCEPR#

LINT1/NMI

LINT0/INTR

IGNNE#

STPCLK#

INIT#

TCK

TDI

TDO

TMS

TRST#

IERR#

FERR#/PBE#

PROCHOT#

THERMTRIP#

ADS#

BNR#

HIT#

DBSY#

DRDY#

HITM#

LOCK#

BINIT#

MCERR#

SKTOCC#

THERMDA2

THERMDC2

THERMDA

THERMDC

DBR#

BOOTSELECT

TEST_BUS

VID_SELECT

LL_ID1

LL_ID0

MS_ID1

MS_ID0

BSEL0

BSEL1

BSEL2

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

B15

FSB1_D53

D52#

C14

FSB1_D52

D51#

C15

FSB1_D51

FSB1_D50

FSB1_A21

FSB1_A11

D25#

FSB1_D24

U6

D24#

F12

F11

FSB1_D23 FSB1_A10

FSB1_A7

FSB1_A6

FSB1_A9

FSB1_A8

A9#T5A8#R4A7#M4A6#L4A5#L5A4#P6A3#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

E10

D10

FSB1_D19

FSB1_D20

FSB1_D21

FSB1_D22

FSB1_A5

FSB1_D18

FSB1_A4

FSB1_D17

FSB1_A3

M5

FSB1_D16

P1VID6

P1VID5

AM5

AL4

VID6

GTLREF_DATA_C1

GTLREF_ADD_C1

GTLREF_DATA_C0

GTLREF_ADD_C0

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A10

FSB1_D4

FSB1_D3

FSB1_D8

FSB1_D6

FSB1_D5

FSB1_D7

R1269 0

R1270 0

R1271 0

R1272 0

P1VID3

P1VID2

P1VID4

AK4

AL6

VID5

VID4

VID3

PWRGOOD

FSB1_D0

FSB1_D2

FSB1_D1

P1VID1

P1VID0

AM3

AL5

AM2

VID2

VID1

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1

BCLK0

RS2#

RS1#

RS0#

AP1#

AP0#

BR1#

BR0#

COMP7

COMP6

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

B4

CPU2A

VID0

TEJAS

F2

H2

G10

H1

AG3

AF2

AG2

AD2

AJ1

AJ2

J6

K6

M6

J5

K4

L2

P1

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

G28

F28

A3

F5

B3

U3

U2

H5

F3

N1

AE3

Y3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

CPU1_DISABLE_N54,65

P1_GTLREF_DATA1

P1_GTLREF_ADD1

P1_GTLREF_DATA0

P1_GTLREF_ADD0

FSB1_BPM_N5

FSB1_BPM_N4

FSB1_BPM_N3

FSB1_BPM_N2

FSB1_BPM_N1

FSB1_BPM_N0

FSB1_REQ_N4

FSB1_REQ_N3

FSB1_REQ_N2

FSB1_REQ_N1

FSB1_REQ_N0

FSB1_TESTHI11

FSB1_TESTHI10

FSB1_BPMB_N2

FSB1_BPMB_N3

FSB1_TESTHI2

FSB1_TESTHI1

CK_H_P1_N

CK_H_P1

FSB1_RS2_N

FSB1_RS1_N

FSB1_RS0_N

FSB1_AP1

FSB1_AP0

FSB1_BR_N1

FSB1_BR_N0

H1_COMP7

H1_COMP6

H1_COMP5

H1_COMP4

H1_COMP3

H1_COMP2

H1_COMP1

H1_COMP0

FSB1_DP_N3

FSB1_DP_N2

FSB1_DP_N1

FSB1_DP_N0

FSB1_ADSTB_N1

FSB1_ADSTB_N0

FSB1_DSTBP_N3

FSB1_DSTBP_N2

FSB1_DSTBP_N1

FSB1_DSTBP_N0

FSB1_DSTBN_N3

FSB1_DSTBN_N2

FSB1_DSTBN_N1

FSB1_DSTBN_N0

FSB_SMI#9,40,54

VCC1_SENSE 71

VSS1_SENSE 71

P1VID[6..0]

FSB1_BPM_N[5..0]

FSB1_REQ_N[4..0]

FSB1_DP_N[3..0]

FSB1_ADSTB_N[1..0]

FSB1_DSTBP_N[3..0]

FSB1_DSTBN_N[3..0]

FSB1_BPMB_N2

FSB1_BPMB_N3

R681 51

R682 51

R683 51

R684 51

R685 51

R686 51

CK_H_P1 58

FSB1_RS2_N 16

FSB1_RS1_N 16

FSB1_RS0_N 16

FSB1_AP1 16

FSB1_AP0 16

FSB1_BR_N1 16

FSB1_BR_N0 16

CPU_PWRGD 9,40,64

R658 49.9RST

R657 49.9RST

R688 49.9RST

R690 49.9RST

R691 49.9RST

R692 49.9RST

R693 49.9RST

R694 49.9RST

P_VTT

P_VTT

Place BPMB Termination Near CPU

P_VTT

CPU1 SMI Voltage Translation

U3027

A

B4C

BE

PI5C3303

VCC

GND

2

5

3

6

1

P1VID[6..0] 71

FSB1_BPM_N[5..0] 16,64

FSB1_REQ_N[4..0] 16

FSB1_DP_N[3..0] 16

FSB1_ADSTB_N[1..0] 16

FSB1_DSTBP_N[3..0] 16

FSB1_DSTBN_N[3..0] 16

FSB1_BPMB_N2 64

FSB1_BPMB_N3 64

Max Length 1.2 inches

C1012

X_0.1u

P_VTT

P5V

CPU1_SMI_N

R3391

X_220

49.9RST

100RST

49.9RST

100RST

BE=High, C=B

5

4

3

2

Processor 1 Termination

Place Termination Close to CPU At End of Bus

P_VTT

R673 51

R670 51

R672 51

R669 51

R671 51

R668 X_51

R689 X_51

R3388 510

R3389 510

R3390 510

P3V3_AUX

R1218 4.7K

Place BPM Termination Near CPU

P_VTT

R675 51

R676 51

R677 51

R678 51

P1_LL_ID0

P1_LL_ID1

P1_MS_ID1

P1_MS_ID0

P_VTT

800mV at 1.2V FSB Vtt

Minmum trace and width as wide as possible

R696

12 mils

P1_GTLREF_ADD0

R697

C1013

1u

P_VTT

800mV at 1.2V FSB Vtt

Minmum trace and width as wide as possible

12 mils

R698

P1_GTLREF_ADD1

R701

C1016

1u

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

R1196

C1014

220P

R699

C1017

220P

Micro Star Restricted Secret

P1 Intel LGA771 Signal

FSB1_BR_N1

FSB1_BR_N0

FSB1_GTL_IERR#

FSB1_THERMTRIP_N

FSB1_RESET_N

FSB1_PROCHOT#

CPU1_BOOT

FSB1_BSEL0

FSB1_BSEL1

FSB1_BSEL2

CPU1_SKTOCC#

FSB1_BPM_N3

FSB1_BPM_N2

FSB1_BPM_N1

FSB1_BPM_N0

R1194

X_4.7K

R655 X_51

R656 X_51

0

0

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

1

P3V3

R1195

X_4.7K

P1_GTLREF_DATA0

C1015

220P

P1_GTLREF_DATA1

C1018

220P

of

12 90

Rev

0A

Page 13

5

4

3

2

1

P1 Intel LGA771 Power

VCORE1

D D

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

VCORE1

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

C C

B B

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCORE1

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

Y29

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y24

Y25

Y26

Y27

Y28

Y23

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

W26

W27

W28

W29

W30

VCC

VCC

VCC

VCC

VCC

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

U30

W23

W24

W25

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

U25

U26

U27

U28

U29

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

CPU2B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

LGA771

PART 2

Power

VCC

VCCA

VSSA

VCCPLL

VCCIOPLL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTPWRGD

VTT_OUT1

VTT_OUT0

VTT_SEL

A23

B23

D23

C23

F30

E30

A25

A26

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

H1_VCCA

H1_VSSA

H1_VCCPLL

P_VTT

VTT_PWRGD

VTT_SEL1 VTT_SEL

R3473 0

VTT_PWRGD 10,63

VTT_SEL 10,76

Support

VCC

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

T30

U23

U24

N29

N30

N23

N24

N25

N26

N27

N28

M29

M30

M23

M24

M25

M26

M27

M28

K30

K29

K28

K27

K26

T23

T24

T25

T26

T27

T28

T29

K25

K24

K23

J30

AN8

AN9

AN25

AN26

TEJAS

AN29

AN30

VCC

VCC

NONE

NONE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCT8VCC

Harpertown

&

Wolfdale

CPU

P_VTT

L15 10uH-0805-0.1A

L16 10uH-0805-0.1A

A A

5

Minmum trace and width as wide as possible

< 12 mils

C3130

22u-1206

P1V5

R55

0

C999

103P

4

C3131

X_10u-1206

C1000

4.7u-0805

H1_VCCA

C998

X_1u

H1_VSSA

H1_VCCPLL

C1001

4.7u-0805

P_VTT

C1008

10u-1206

3

C1009

10u-1206

C1010

0.1u

C1011

0.1u

P_VTT

C1004

0.1u

2

C1005

0.1u

C1006

0.1u

C1007

0.1u

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

P1 Intel LGA771 Power

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

1

13 90

of

Rev

0A

Page 14

5

P1 Intel LGA771 GND

4

3

2

1

R654

R654

X_49.9RST

E1

RESVDJ3RESVDN4RESVD

RESVD

VSS

VSS

VSS

AF6

AF7

VSS

AG10

P5

AG13

Nocona-T

Optional

AE6

RESVDN5RESVD

VSS

VSS

AG16

AG17

VSS

A20

AE5

P1TESTIN

W2

RESVD

VSS

AE7

VSS

RESVDG5RESVD

VSS

AF10

RSVD_PECI 11,55,66

AC4

AE4

D14

E24

VSS

AF13

E23

RESVD

RESVD

RESVDD1RESVD

RESVD

RESVDG6RESVD

VSS

VSS

VSS

VSS

VSS

VSS

AF16

AF17

AF20

AF23

AF24

AF25

AF26

F23

RESVDE5RESVDE6RESVDE7RESVD

RESVDF6RESVD

VSS

VSS

VSS

VSS

VSS

AF3

AF27

AF28

AF29

B13

AF30

D D

FSB1_BPMB_N1

D16

F1

VSS

A12

A15

A18

A21

A24

R567

C C

B B

X_0-0402

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

RESVDC9RESVD

VSS

VSS

VSS

A2

VSS

VSS

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

AE30

Dempsey-T Dempsey/Woodcrest

Stuffed No Stuffed

AN27

AN6

RESVD

VSS

AG23

AJ3

RESVD

VSS

AG24

AK3

AG7

F29

RESVD

RESVD

VSS

VSS

AH1

AN28

NONE

NONE

VSS

VSS

VSS

AH10

AH13

AH16

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

AH3

AH17

AH20

AH23

AH24

VSS

AN5

RESVD

VSS

AG20

VSS

V30

V29

V28

VSSV3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH6

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

TP101

R741 51

P1TESTIN

V27

V26

V25

V24

V23

VSS

VSS

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

LGA771

PART 3

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ24

AJ27

AJ28

AJ29

AJ30

AK10

AK13

AK16

AK17

AK2

VSS

VSS

AK20

R30

VSS

AK23

R29

VSS

VSS

AK24

R28

VSS

VSS

AK27

R27

VSS

VSS

AK28

P_VTT

R26

R25

VSS

VSS

AK29

AK30

R24

VSS

VSS

AK5

VSS

VSS

R23

AK7

VSS

VSS

AL10

P30

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

AL13

AL16

AL17

P29

VSS

VSS

AL20

P28

VSS

VSS

AL23

P27

VSS

VSS

AL24

P26

VSS

VSS

AL27

P25

VSS

VSS

AL28

P24

VSS

VSS

AL3

P23

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM1

AM10

AM13

AM16

AM17

AM20

AM23

VSS

L30

L29

VSSL3VSS

VSS

VSS

VSS

VSS

AM4

AM24

AM27

AM28

Place BPMB Termination Near CPU

R747 51

R748 51

L23

VSS

VSSK7VSSK5VSSK2VSSJ7VSSJ4VSSH9VSSH8VSSH7VSSH6VSSH3VSS

VSS

VSSB5VSS

VSS

VSS

VSS

VSSB1VSS

B8

AN20

AN23

AN24

VSS

AN2

AN17

L28

AM7

P_VTT

L27

VSS

VSS

AN1

VSS

VSS

L26

AN10

VSS

VSS

L25

AN13

VSS

VSS

L24

VSS

VSS

AN16

B11

B14

VSS

VSS

B17

FSB1_BPMB_N1

FSB1_BPMB_N0

H29

H28

H27

H26

VSS

VSS

VSS

VSS

VSS

VSSC4VSS

C7

B20

B24

H25

H24

VSS

TEJAS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

CPU2C

H23

H22

H21

H20

H19

H18

H17

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C24

C22

C19

C16

C13

C10

FSB1_BPMB_N1 64

FSB1_BPMB_N0 64

FSB1_BPMB_N0

R568

X_0-0402

A A

Intel Document Title: Enterprise System Design Conference - Taipei

REV. NO. 1.0 REF, NO. 19091

Page 142: For each Socket change new RSVD lands A24 and E29

Page 142: Connect W2 and U1 together on each Socket,

from VSS to no-connects on the motherboard

and terminate with a 51ohms resistor to VTT.

5

4

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

P1 Intel LGA771 GND

MS-9192

Last Revision Date:

Friday, April 27, 2007

Sheet

1

14 90

Rev

0A

of

Micro Star Restricted Secret

Page 15

5

4

3

2

1

Blackford FSB0

FSB0_D63

FSB0_D62

FSB0_D61

FSB0_D60

D D

C C

B B

A A

FSB0_D[63..0]9

FSB0_DBI#[3..0]9

FSB0_DSTBP_N[3..0]9

FSB0_DSTBN_N[3..0]9

5

FSB0_D[63..0]

FSB0_DBI#[3..0]

FSB0_DSTBP_N[3..0]

FSB0_DSTBN_N[3..0]

CK_H_MCH58

CK_H_MCH_N58

4

FSB0_D59

FSB0_D58

FSB0_D57

FSB0_D56

FSB0_D55

FSB0_D54

FSB0_D53

FSB0_D52

FSB0_D51

FSB0_D50

FSB0_D49

FSB0_D48

FSB0_D47

FSB0_D46

FSB0_D45

FSB0_D44

FSB0_D43

FSB0_D42

FSB0_D41

FSB0_D40

FSB0_D39

FSB0_D38

FSB0_D37

FSB0_D36

FSB0_D35

FSB0_D34

FSB0_D33

FSB0_D32

FSB0_D31

FSB0_D30

FSB0_D29

FSB0_D28

FSB0_D27

FSB0_D26

FSB0_D25

FSB0_D24

FSB0_D23

FSB0_D22

FSB0_D21

FSB0_D20

FSB0_D19

FSB0_D18

FSB0_D17

FSB0_D16

FSB0_D15

FSB0_D14

FSB0_D13

FSB0_D12

FSB0_D11

FSB0_D10

FSB0_D9

FSB0_D8

FSB0_D7

FSB0_D6

FSB0_D5

FSB0_D4

FSB0_D3

FSB0_D2

FSB0_D1

FSB0_D0

FSB0_DBI#3

FSB0_DBI#2

FSB0_DBI#1

FSB0_DBI#0

FSB0_DSTBP_N3

FSB0_DSTBP_N2

FSB0_DSTBP_N1

FSB0_DSTBP_N0

FSB0_DSTBN_N3

FSB0_DSTBN_N2

FSB0_DSTBN_N1

FSB0_DSTBN_N0

CK_H_MCH

CK_H_MCH_N

AE37

AE36

AH36

AG36

AF38

AE38

AH38

AJ38

AJ37

AG35

AK36

AL37

AL36

AL38

AJ34

AF37

AE28

AD29

AF28

AC31

AE29

AC30

AD30

AE31

AE32

AD35

AF33

AG32

AF31

AE34

AG30

AG33

AM37

AK35

AM34

AM38

AP38

AN36

AL35

AN35

AP36

AT37

AU36

AP34

AT36

AP35

AL34

AN33

AJ33

AG27

AG29

AM33

AH31

AJ30

AH32

AJ31

AL31

AK30

AN32

AH29

AK29

AH28

AL29

AJ28

AH37

AF30

AP37

AL32

AH35

AD33

AR38

AK33

AH34

AD32

AR37

AK32

AN17

AP17

BLACKFORD 4/11

FSB0_D63

FSB0_D62

FSB0_D61

FSB0_D60

FSB0_D59

FSB0_D58

FSB0_D57

FSB0_D56

FSB0_D55

FSB0_D54

FSB0_D53

FSB0_D52

FSB0_D51

FSB0_D50

FSB0_D49

FSB0_D48

FSB0_D47

FSB0_D46

FSB0_D45

FSB0_D44

FSB0_D43

FSB0_D42

FSB0_D41

FSB0_D40

FSB0_D39

FSB0_D38

FSB0_D37

FSB0_D36

FSB0_D35

FSB0_D34

FSB0_D33

FSB0_D32

FSB0_D31

FSB0_D30

FSB0_D29

FSB0_D28

FSB0_D27

FSB0_D26

FSB0_D25

FSB0_D24

FSB0_D23

FSB0_D22

FSB0_D21

FSB0_D20

FSB0_D19

FSB0_D18

FSB0_D17

FSB0_D16

FSB0_D15

FSB0_D14

FSB0_D13

FSB0_D12

FSB0_D11

FSB0_D10

FSB0_D9

FSB0_D8

FSB0_D7

FSB0_D6

FSB0_D5

FSB0_D4

FSB0_D3

FSB0_D2

FSB0_D1

FSB0_D0

FSB0_DBI3

FSB0_DBI2

FSB0_DBI1

FSB0_DBI0

FSB0_DSTBP3

FSB0_DSTBP2

FSB0_DSTBP1

FSB0_DSTBP0

FSB0_DSTBN3

FSB0_DSTBN2

FSB0_DSTBN1

FSB0_DSTBN0

CORECLKP

CORECLKN

FSB 0

U45D

FSB0_A35

FSB0_A34

FSB0_A33

FSB0_A32

FSB0_A31

FSB0_A30

FSB0_A29

FSB0_A28

FSB0_A27

FSB0_A26

FSB0_A25

FSB0_A24

FSB0_A23

FSB0_A22

FSB0_A21

FSB0_A20

FSB0_A19

FSB0_A18

FSB0_A17

FSB0_A16

FSB0_A15

FSB0_A14

FSB0_A13

FSB0_A12

FSB0_A11

FSB0_A10

FSB0_A9

FSB0_A8

FSB0_A7

FSB0_A6

FSB0_A5

FSB0_A4

FSB0_A3

FSB0_REQ4

FSB0_REQ3

FSB0_REQ2

FSB0_REQ1

FSB0_REQ0

FSB0_ADSTB1

FSB0_ADSTB0

FSB0_BPRI_N

FSB0_DEFER_N

FSB0_RESET_N

FSB0_RS2

FSB0_RS1

FSB0_RS0

FSB0_RSP_N

FSB0_TRDY_N

FSB0_ADS_N

FSB0_AP1

FSB0_AP0

FSB0_BINIT_N

FSB0_BNR_N

FSB0_BPM5

FSB0_BPM4

FSB0_BREQ1

FSB0_BREQ0

FSB0_DBSY_N

FSB0_DP3

FSB0_DP2

FSB0_DP1

FSB0_DP0

FSB0_DRDY_N

FSB0_HIT_N

FSB0_HITM_N

FSB0_LOCK_N

FSB0_MCERR_N

PSEL2

PSEL1

PSEL0

FSB0_VREF

FSB0_VREF

FSB0_VREF

BLACKFORD G1

3

AV22

AU22

AR22

AP22

AV24

AT23

AU23

AV25

AT24

AR25

AU26

AT26

AT27

AU25

AU28

AR24

AR27

AP25

AV28

AF22

AG23

AF25

AH22

AL22

AJ22

AG24

AM22

AH23

AP26

AN26

AM25

AN24

AL25

AJ25

AJ24

AK24

AH25

AL26

AP23

AL23

AU34

AV34

AN30

AU31

AL28

AV31

AN27

AT32

AU29

AK26

AH26

AK27

AV30

AP29

AR28

AG26

AM28

AR30

AN29

AP31

AT33

AR31

AT29

AU32

AV33

AT30

AJ27

AB1

AB2

AC1

AF34

AM30

AM27

FSB0_A35

FSB0_A34

FSB0_A33

FSB0_A32

FSB0_A31

FSB0_A30

FSB0_A29

FSB0_A28

FSB0_A27

FSB0_A26

FSB0_A25

FSB0_A24

FSB0_A23

FSB0_A22

FSB0_A21

FSB0_A20

FSB0_A19

FSB0_A18

FSB0_A17

FSB0_A16

FSB0_A15

FSB0_A14

FSB0_A13

FSB0_A12

FSB0_A11

FSB0_A10

FSB0_A9

FSB0_A8

FSB0_A7

FSB0_A6

FSB0_A5

FSB0_A4

FSB0_A3

FSB0_REQ_N4

FSB0_REQ_N3

FSB0_REQ_N2

FSB0_REQ_N1

FSB0_REQ_N0

FSB0_ADSTB_N1

FSB0_ADSTB_N0

FSB0_BPRI_N

FSB0_DEFER_N

FSB0_RESET_N

FSB0_RS2_N