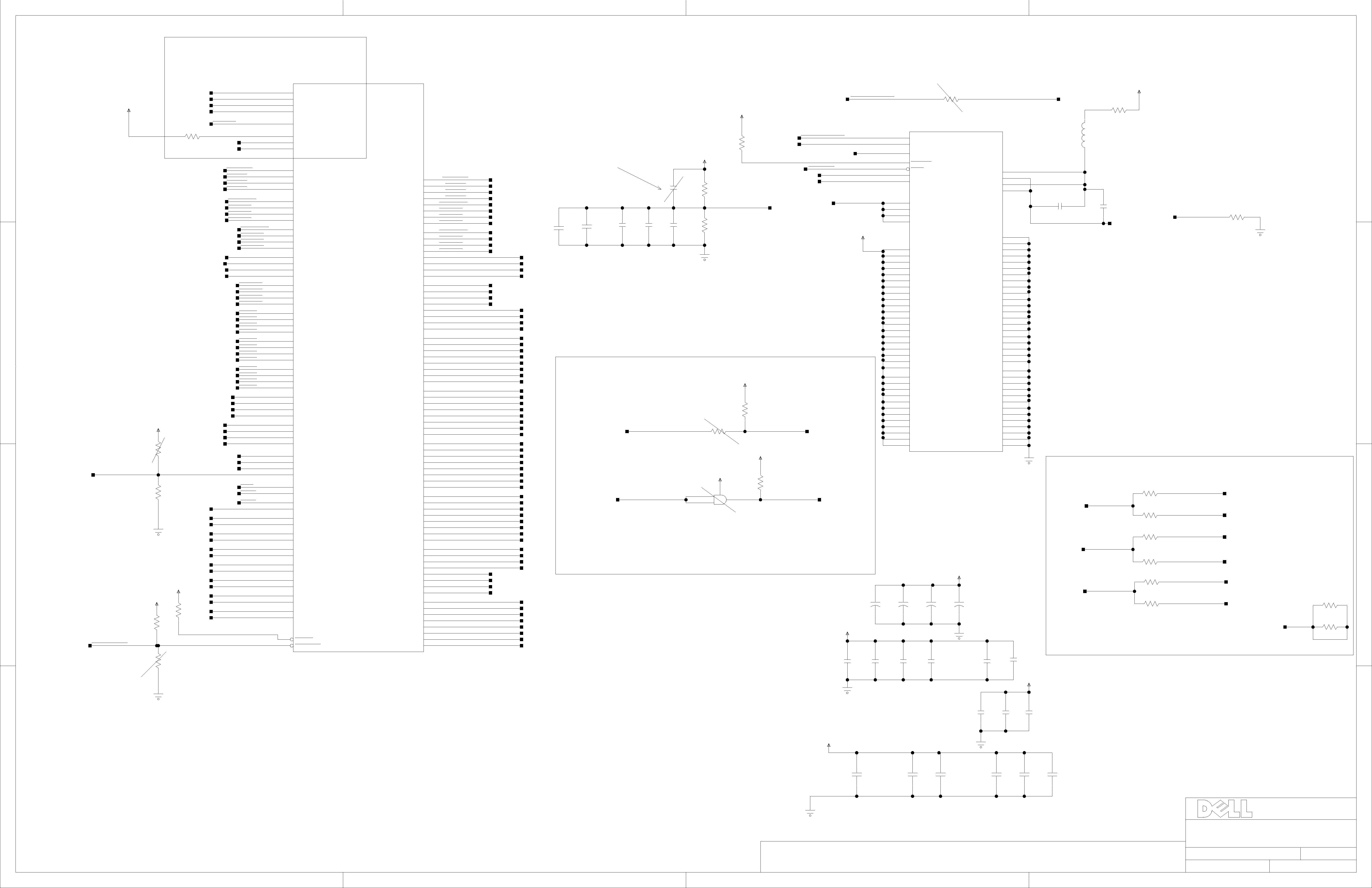

Page 1

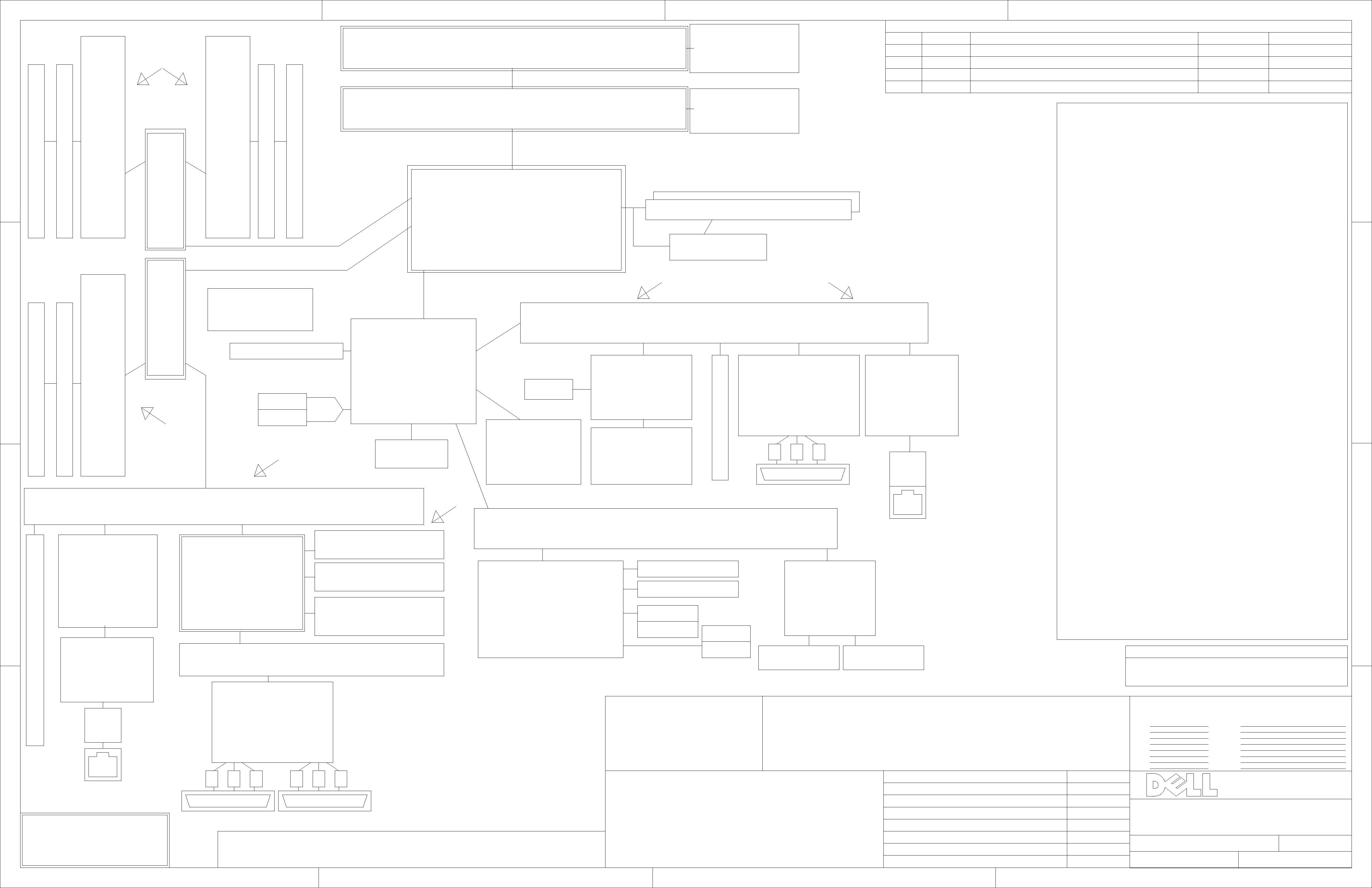

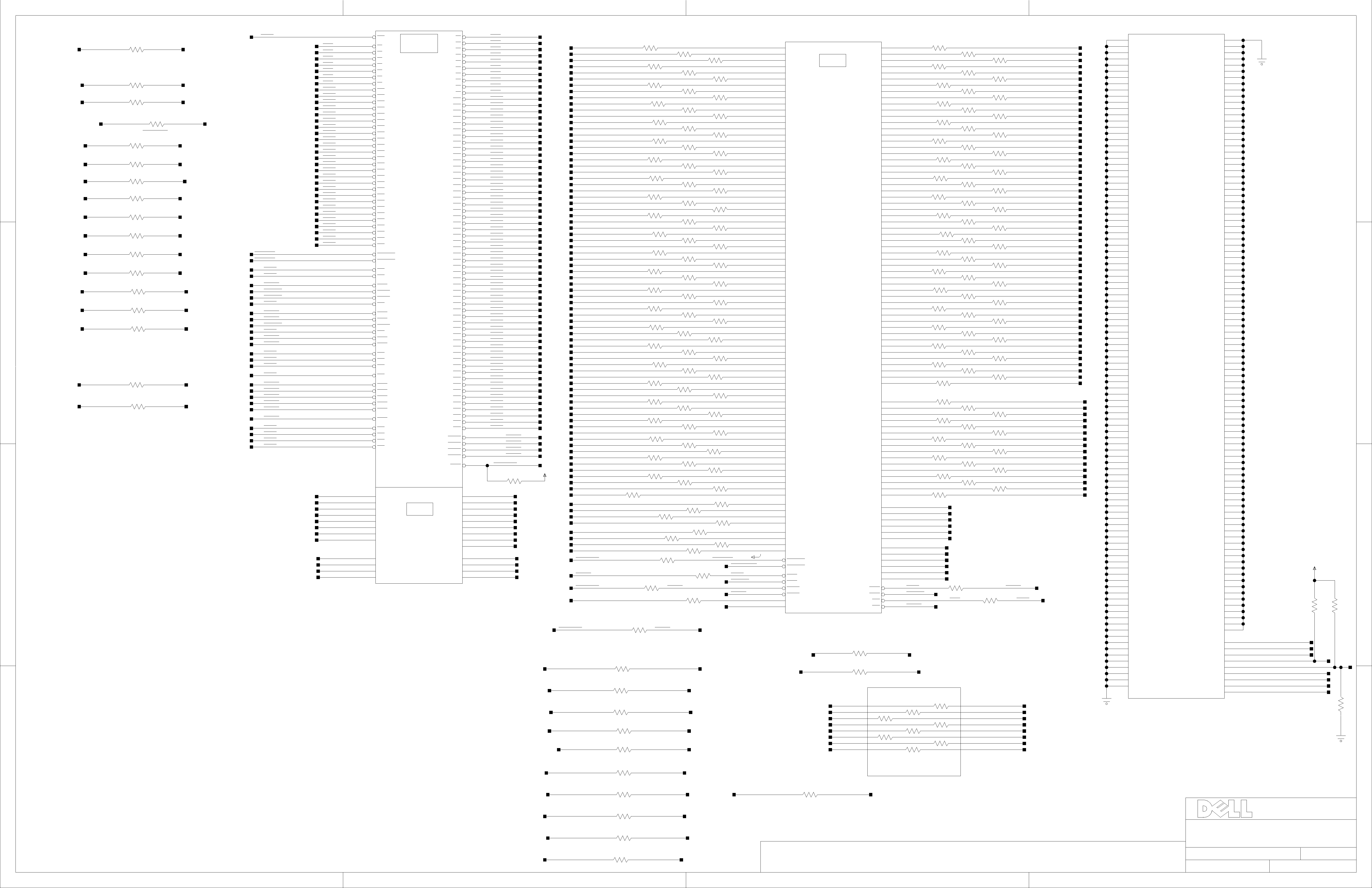

A B C

Dell Controlled Print

D

12-5-2003_15:26

1

2

3

100/66/33

3.3V

PCI-X BUS 5

HOT

PCI-X BUS 4

PLUG

PCI7 - 3.3V

U121

CIOB-X CIOB-X

352 ABGA 352 ABGA

100/66/33

3.3V

64bit

PCI2 - 3.3VPCI6 - 3.3V

PCI3 - 3.3V

PCI BUS 1 - 64/66 3.3V

BREAKOUT ON i80303

BROADCOM

BCM5700

10/100/1000

MAC/MEM

388 PBGA

PCI-X BUS 3

HP CONTROL

FOR PCIX2

THRU PCIX7

FLOPPY/IDE

U123

HOT

PLUG

INTEL

U135

i80303

XOR/P2P/I20

64bit RAID

CONTROLLER

540 HL-PBGA

100/66/33

3.3V

64bit64bit

PCI4 - 3.3V

PCI5 - 3.3V

USB1

USB2

NOT HOT

PLUG

U134

PROCESSOR 1 - SKT603

PROCESSOR 2 - SKT603

IMB_B

IMB_A

U61

SOUTH

BRIDGE

"CSB5"

LPC BRIDGE

& IDE/USB

272 PBGA

PORTXX

DIMM_RAID

BATTERY

16MBx8 RAID

FLASH

FOSTER/PRESTONIA HOST BUS

U118

ADDR DOUBLE PUMPED, DATA QUAD PUMPED

SERVERWORKS

GCHE "CMIC"

CHAMPION MEMORY

& I/O CONTROLLER

899 FCBGA

THIN IMB_D

8MBx8

SYSTEM

PC100 UNBUFFERED DIMM

FLASH

U26

EMBEDDED LPC BUS

NATIONAL

PC87414

SUPER I/O

U129

& RTC

VGA

VRM1(9.1)

VRM2(9.1)

MEMORY CARDS SUPPORT TWELVE

PC200 REG DDR DIMMS(MIN 512MB/MAX 12GB)

MEMORY CARD SLOTS

REMC

U117

NOT HOT PLUG

PCI BUS 0 - 32/33 5V

PCI1 - 5V

ADAPTEC

AIC-7890

32bit ULTRA2

SE/LVD

272 BGA

SCSI_C

COM1

U62

RAGE XL

272 BGA

U78

8MB

SDRAM

DRAC3 SLOT

ATI

VGA

FLOPPY/IDE

PARALLEL

MOUSE

KEYBD

U96 U25

QLOGIC

Zircon

BMC

160 LQFP

REV

X00 9/8/03

A01

A02

MECA

MECB

INTEL

82559

10/100 ENET

196 BGA

MAG

ENET_100Mb

U147

ESM3

REVISIONS

DESCRIPTIONECO DATE

Changes from F0055 - A01

152750A00 11/11/03

155050 12/4/03

Promotion to A00 from X00

Corrected and Updated A00 SCH

Component change to correct manufac issue

12/5/03155112

TABLE OF CONTENTS

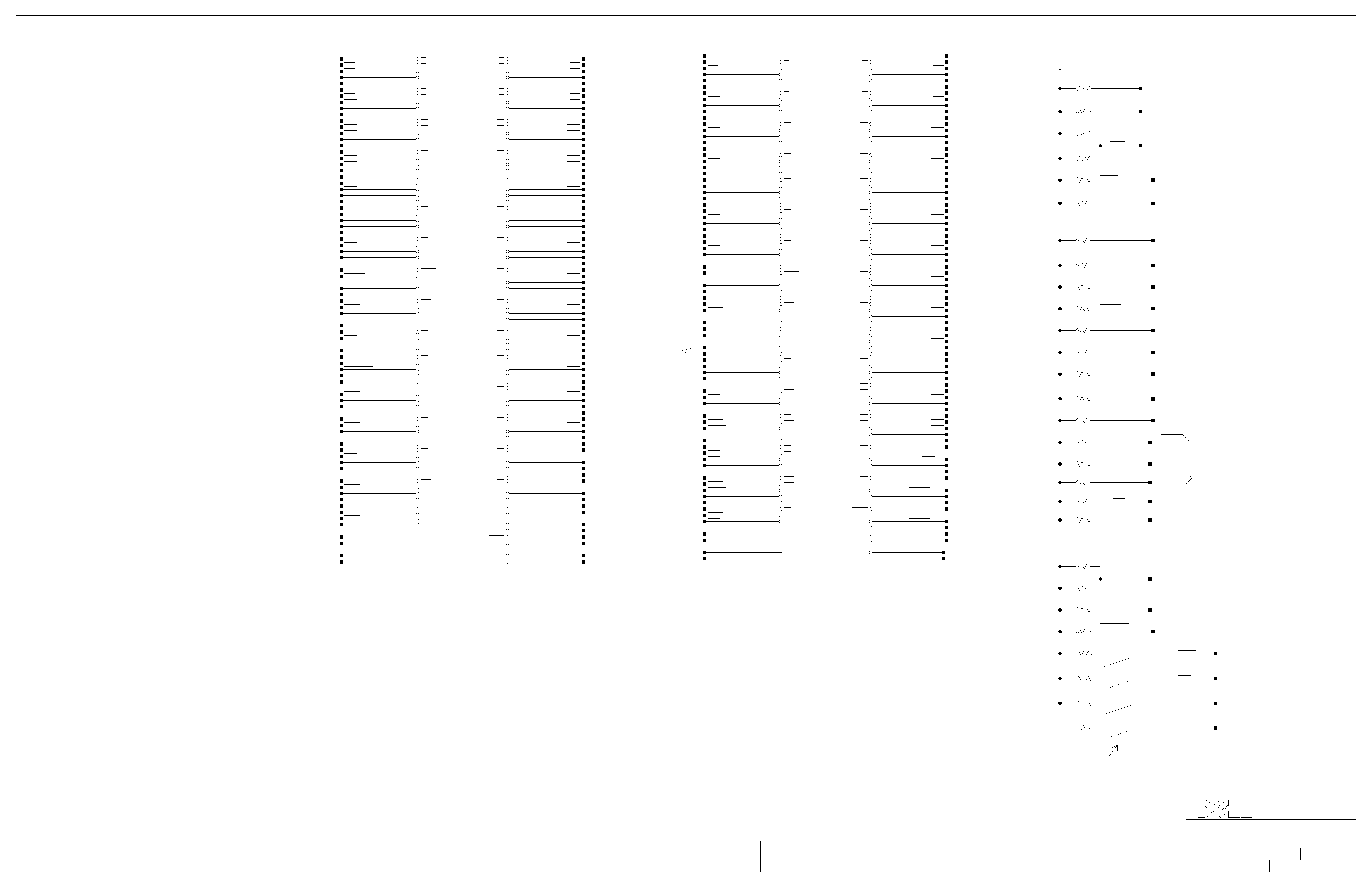

BLOCK DIAGRAMPage 1.

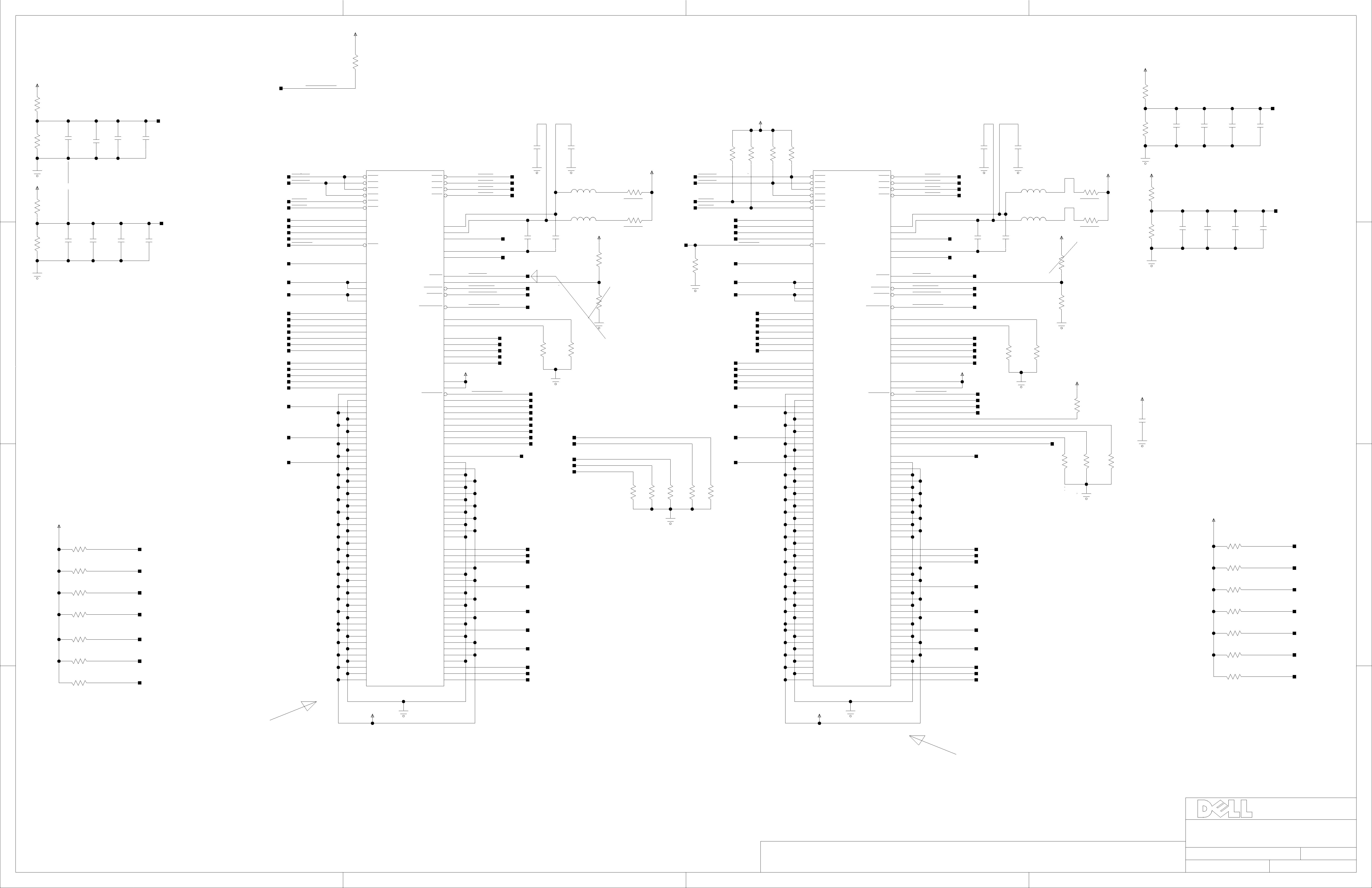

Page 2. CLOCK DIAGRAM

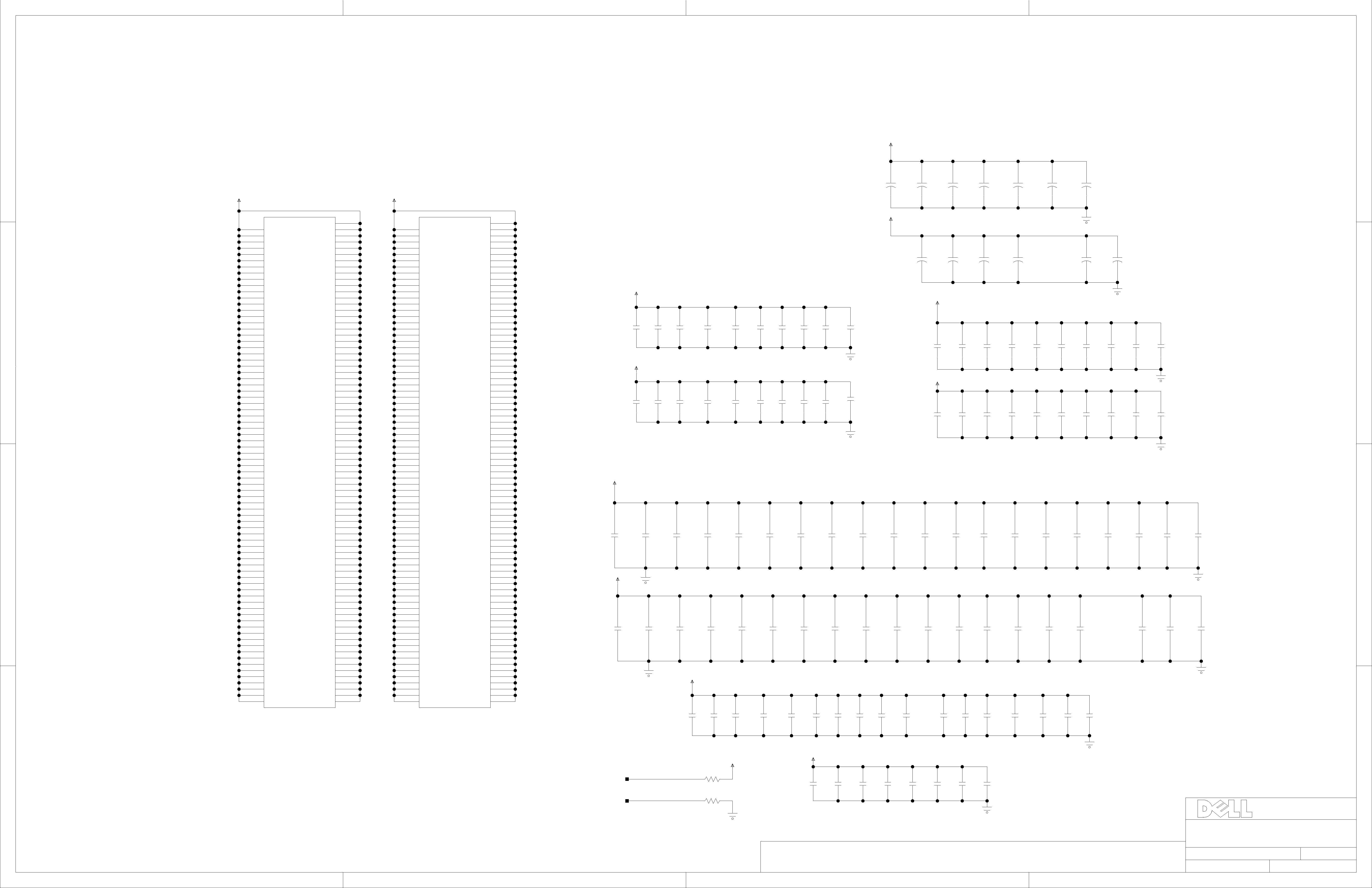

Page 3. RESET DIAGRAM & PCI DEVICES CHART

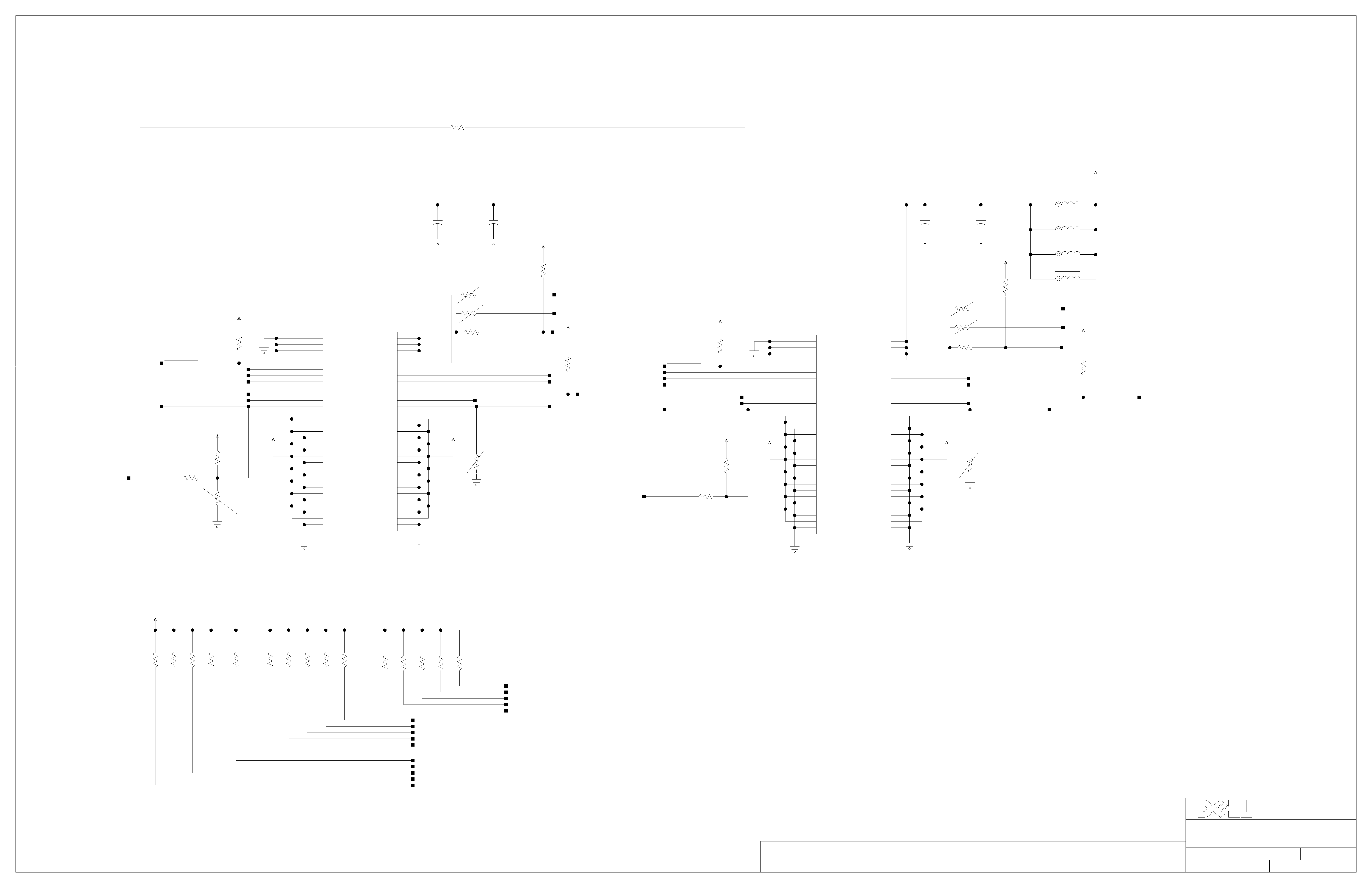

CLOCKS & PCI-X CLK BUFFERPage 4.

Page 5. PROCESSORS

Page 6.

Page 7. PROCESSORS

Page 8.

Page 9.

Page 10.

Page 11.

Page 12.

Page 13.

Page 14.

Page 15.

Page 16.

Page 17.

Page 18.

Page 19.

Page 20.

Page 21.

Page 22.

Page 23.

Page 24.

Page 25.

Page 26.

Page 27.

Page 28.

Page 29.

Page 30.

Page 31.

Page 32.

Page 33.

Page 34.

Page 36.

Page 37.

Page 38.

Page 39.

Page 40.

Page 41.

Page 44.

Page 45.

Page 46.

Page 47. AIC-7890

Page 48. RAGE XL VIDEO

Page 49. RAGE XL VIDEO CONTINUED

Page 50. INTEL 82559 10/100 ENET

Page 51.

Page 52.

Page 53.

Page 54.

Page 55.

Page 56.

Page 57.

Page 58.

Page 59.

Page 60.

Page 61.

Page 62. Spares

Page 63 Schematic Revisions Overview

PROCESSORS

VRM

ITP 32 & LEVEL TRANSLATION CIRCUITS

CMIC

CMIC

REMC PLL

MEC A

MEC B

REMC

REMC RESISTORS & PCI-X BUFFERS

CIOB 1

HOTPLUG SLOT 2

PCI-X 100/66/33 SLOTS 2

HOTPLUG SLOT 3

PCI-X 100/66/33 SLOTS 3

BROADCOM 5700 10/100/1000 MAC

BROADCOM 5401 PHY

INTEL 80303 "ZION" RAID PROCESSOR

RAID CONTINUED

RAID CONTINUED, DEBUG CIRCUITS

ADAPTEC AIC-7899 U160 SCSI

AIC-7899 CONTINUED

U160 SCSI TERMINATION & CONNECTORS

CIOB 2

HOTPLUG SLOT 4

PCI-X 100/66/33 SLOTS 4

HOTPLUG SLOT 5

PCI-X 100/66/33 SLOTS 5

HOTPLUG SLOT 6Page 35.

PCI-X 100/66/33 SLOTS 6

HOTPLUG SLOT 7

PCI-X 100/66/33 SLOTS 7

CSB5

PIRQ SERIALIZING & X-BUS LATCH

SYSTEM CPLD

IDE, USB, ETCPage 42.

SYSTEM FLASHPage 43.

SIO

PARALLEL PORT, SERIAL PORTS

PCI 32/33 SLOT 1

ESM3: Zircon and CPLD

ESM3: Memory

ESM3: Misc

ESM3: Fans, Analog

Hotplug PCI FPGA

RAID Battery Charger

Backplane, CtrlPnl, Buttons, Etc.

VR FOR 2.5V

3.3V_AUX VR, PCIRST CIRCUITS

PowerGood Circuit

Decoupling, Power Conns

APPROVED

1

2

3

10/100/1000

4

DOUBLE BOXED

MEANS HEATSINK

IS REQUIRED

BCM5401

PHY

256 TBGA

MAG

ENET_1Gb

U27

PCI BUS 2 - 64/66 3.3V

ADAPTEC

AIC-7899W

PIN FOR PIN COMPATIBLE PART

DUAL U160

SE/LVD

456 BGA

SCSI_A SCSI_B

Directory: R: \ Schematic_Projects\ PowerEdge\ Jaguar \ Planar_H3007\ A02

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

U156

FOR MIGRATION PLAN

TO AIC-7902 FOR DUAL U320

128 PQFP

U20

COM2

PWA:

PWB:

SCHEM:

ASSY DWG:

H3009

H3008

H3007

H3006

PROPRIETARY NOTE

THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER

CORP., EXCEPT AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN

ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE

REPRODUCED IN WHOLE OR IN PART AND MUST BE RETURNED TO DELL

COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION

OF THE PURPOSE OF THE LOAN. NEITHER THIS ITEM NOR THE

INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS

NOT HAVING A NEED FOR SUCH USE OR DISCLOSURE CONSISTENT WITH

THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF

DELL COMPUTER CORPORATION.

NVRAMFLASH

8MBx16

U160 U148

128KB

JAGUAR PLANAR

DRAWN

DESIGNED

CHECKED

APPROVED

APPROVED

APPROVED

APPROVED

RELEASED

Haseeb Bhutta

SHAWN DUBE,LIBBY MCTEER,WILL SMITH,ROBERTO LAGO

KEVIN MILLER,CLAY PHENNICIE

Danny King

12/5/03

10/25/02

12/5/03

XLBOM Build option table

0 Production Build

9 Prototype Build

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO

TITLE

DWG NO.

134552 11/3/02

152750 11/11/03

155050 12/4/03

SCHEM,PLN,PE4600,2P

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

COMPUTER

CORPORATION

AUSTIN,TEXAS

H3007

DATE

SHEET

12/5/03155112

4

REV.

A02

1 OF 6312/5/2003

DCBA

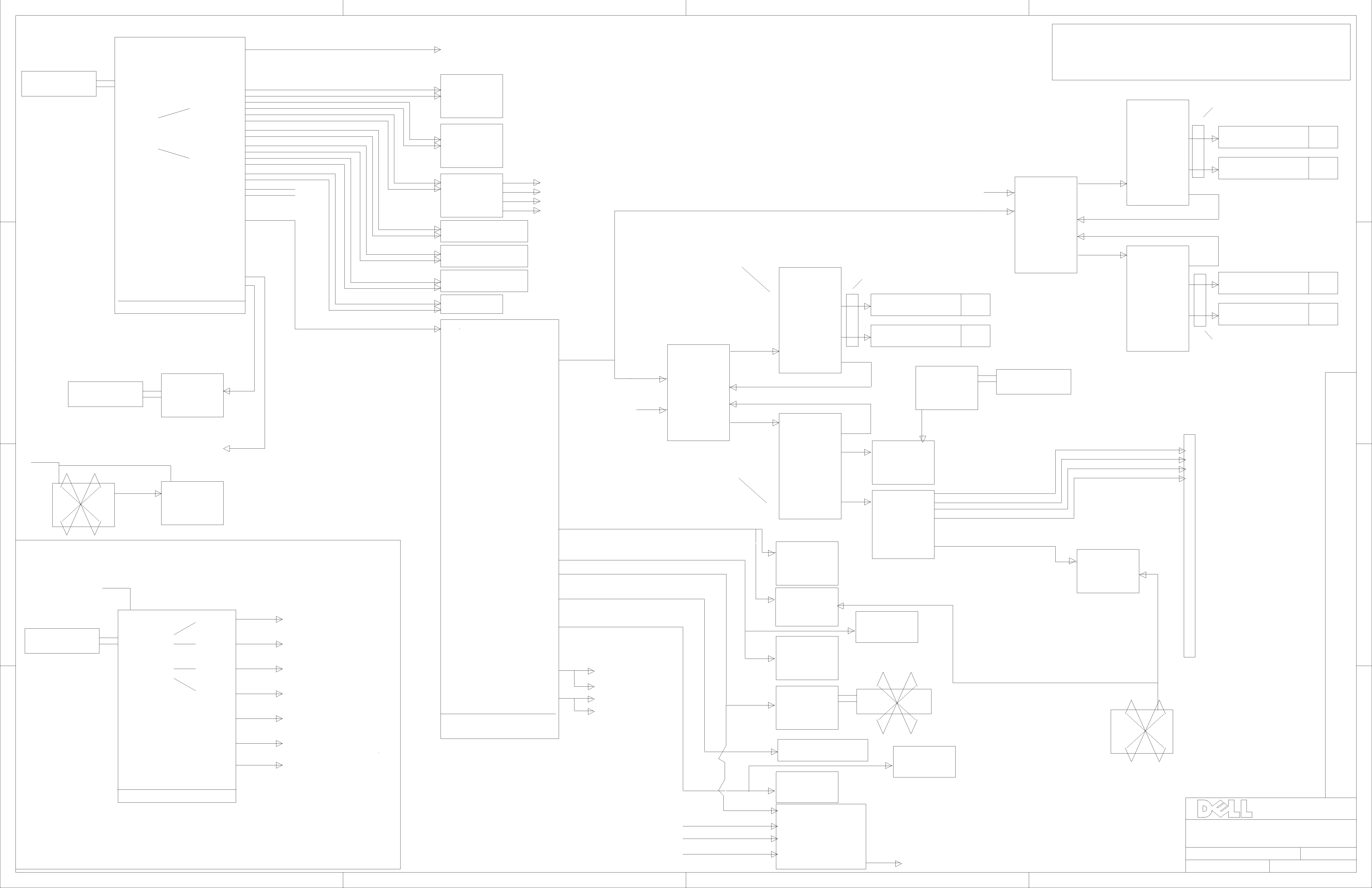

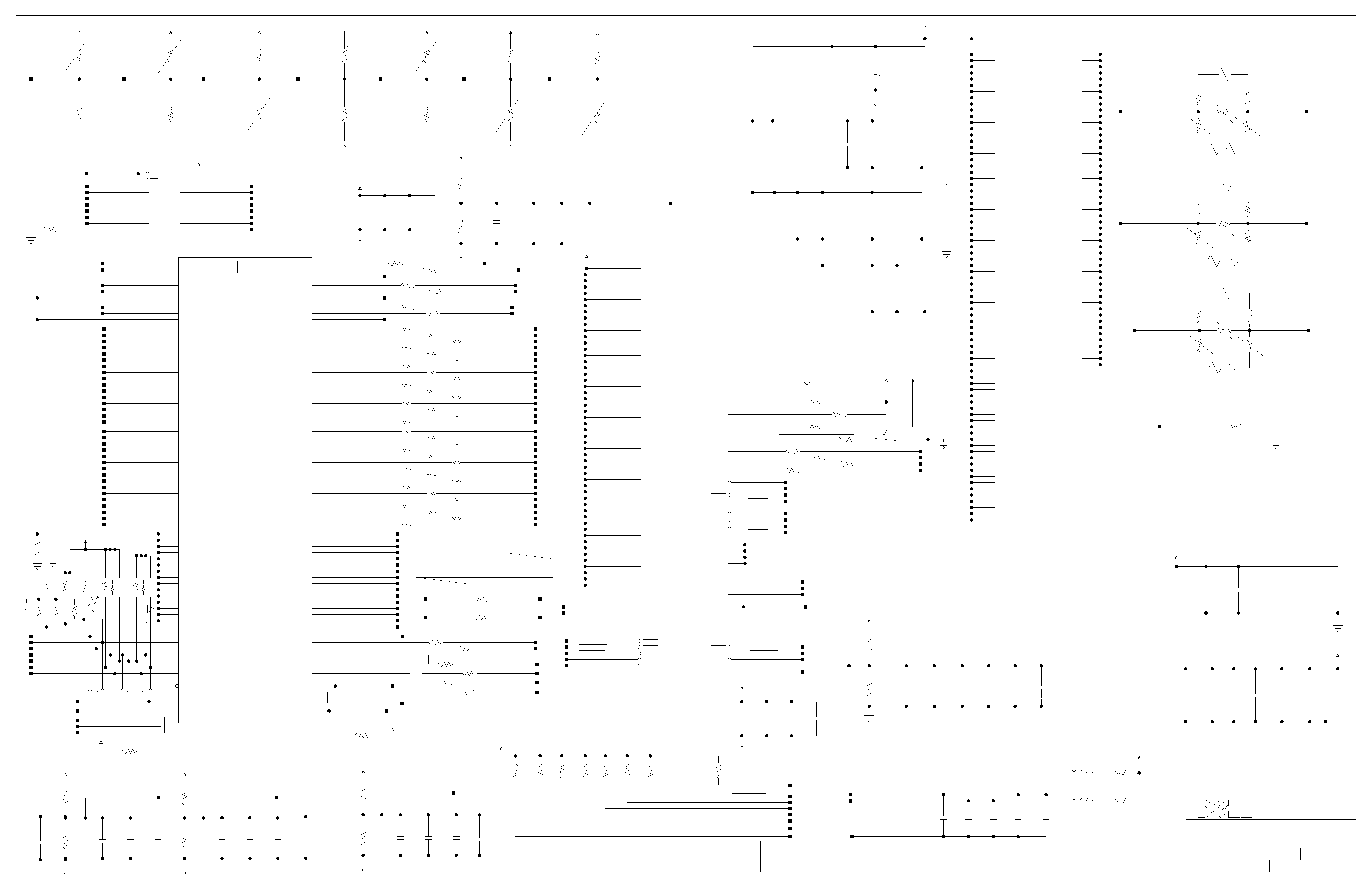

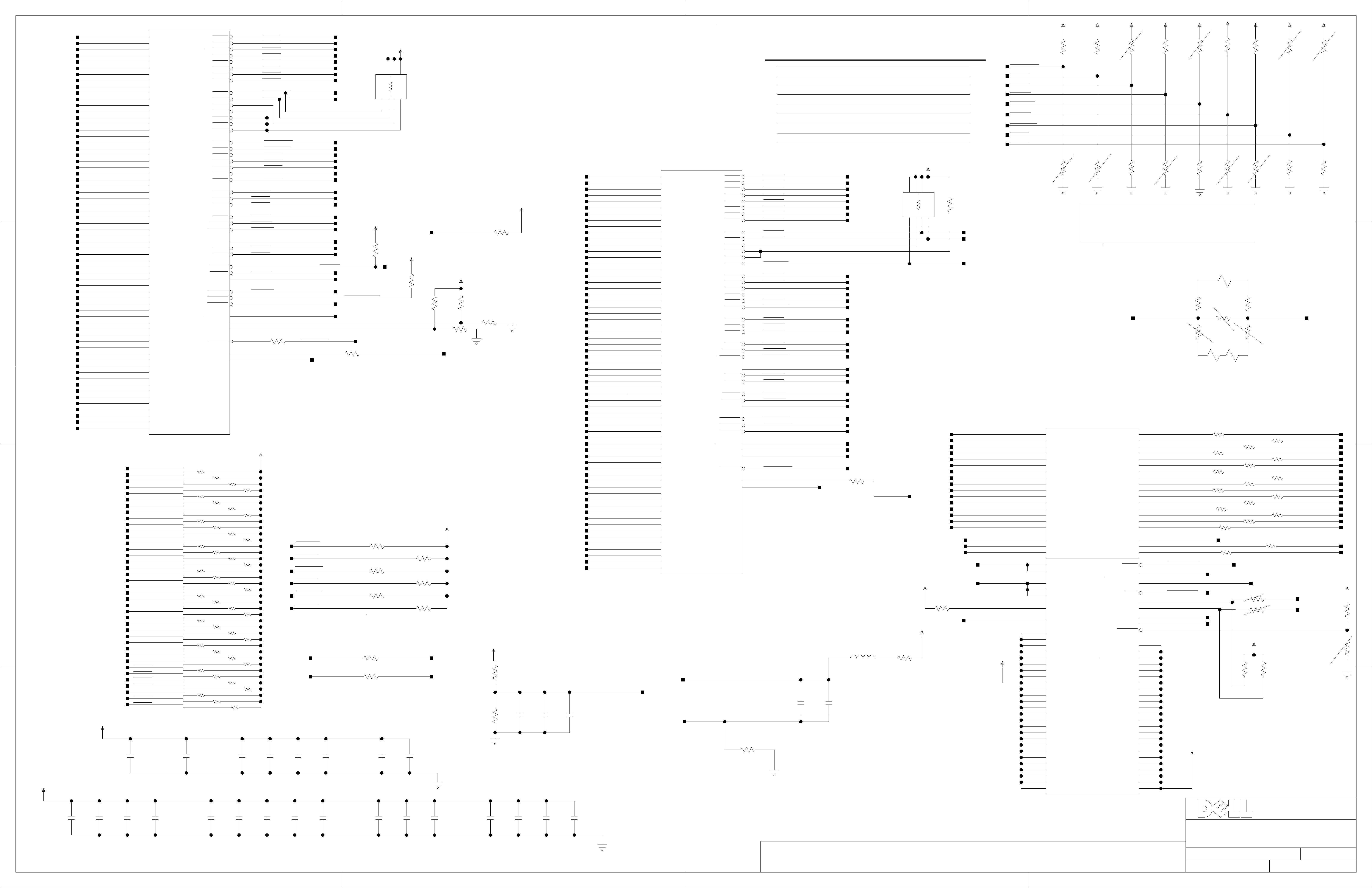

Page 2

B D

CA

12-5-2003_10:50

1

14.318MHZ

XTAL

100MHZ

DIFF CLKS

14.318 MHZ

14.318 MHZ

CPU CLK

CPU CLK

CPU CLK

CPU CLK

CPU CLK

CPU CLK

CPU CLK

CPU CLK

33.3 MHZ

CSB5

FOSTER

PROCESSOR

1

FOSTER

PROCESSOR

2

GCHE

CMIC

IMB CLK_A

IMB CLK_B IMB CLK_A

IMB CLK_C

IMB CLK_D

CIOB-X

CLOCK DISTRIBUTION

BLOCK DIAGRAM

TI CDCV304

FETSWITCH

BUFFER

100/66/33MHZ

100/66/33MHZ

PCICLKIN

PCICLKFB

1

PCIX SLOT 7

PCIX SLOT 6

2

RCC_SYN

48 MHZ

48 MHZ

MECA

MECB

REMC AP

ITP32B

CLKIN

TI CDCV304

BUFFER

100/66/33MHZ

100/66/33MHZ

PCICLKIN

FETSWITCH

PCIX SLOT 3

PCIX SLOT 2

2

PCICLKIN

PCICLKFB

100/66/33MHZ

100/66/33MHZ

BUFFER

PCIX SLOT 5

PCIX SLOT 4

2

FETSWITCH

AUX_POWER

32KHZ

XTAL

97414

CSB5

USB

PCICLK

PCICLK

IMB CLK_B

CIOB-X

1

TI CDCV304

PCICLKFB

PCICLKIN

PCICLKFB

66MHZ

BROADCOM

BCM5700

BROADCOM

BCM5401

1Gb PHY

125 MHZ

TI CDCV304

25MHZ

XTAL

100MHZ

100MHZ

100MHZ

100MHZ

3

10 MHZ

OSC

AUX_POWER

QLOGIC

BMC

10MHZ

QLOGIC BMC

PCICLK

PCICLK

PCICLK

PCICLK

PCICLK

PCICLK

BUFFER

NATIONAL

PC87417

ADAPTEC

7890

66MHZ

INTEL

i80303

(ZION)

66MHZ

3

ADAPTEC

7899

RAID_MEMORY

XILINX

14.318MHZ

XTAL

ALWAYS

ON

25MHZ

25MHZ

20MHZ

40MHZ

40MHZ

BROADCOM 5700

INTEL 559

CIRRUS 8900A EMP NIC

ADAPTEC 7899

ADAPTEC 7890

PHILIPS PCK2001M

LOW SKEW BUFFER

PCICLK

PCICLK

PCICLK_IRQ0

PCICLK_IRQ1

PCICLK_IRQ2

PCICLK_IRQ3

ATI

RAGE XL

VGA

INTEL

82559

10/100 LOM

PCI SLOT 1

cPLD

25MHZ

XTAL

40 MHZ

40 MHZ

OSC

QLOGIC

14.31818MHZ

ATI RAGE XL

BMC

(80 MHZ NEEDED FOR AIC-7902)

4 4

XILINX

cPLD

(40 MHZ NEEDED FOR AIC-7899 & AIC-7890)

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

CY2922-????

COMPUTER

CORPORATION

AUSTIN,TEXAS

TITLE

48 MHZ

14.318 MHZ

SCHEM,PLN,PE4600,2P

CSB5

REPLACES FIVE CRYSTALS/OSCILLATORS

A B

IMB CLK_D

LPC_CLK

33.3MHZ

DWG NO.

DATE

DC

H3007

SHEET

12/5/2003

REV.

A02

2 OF 63

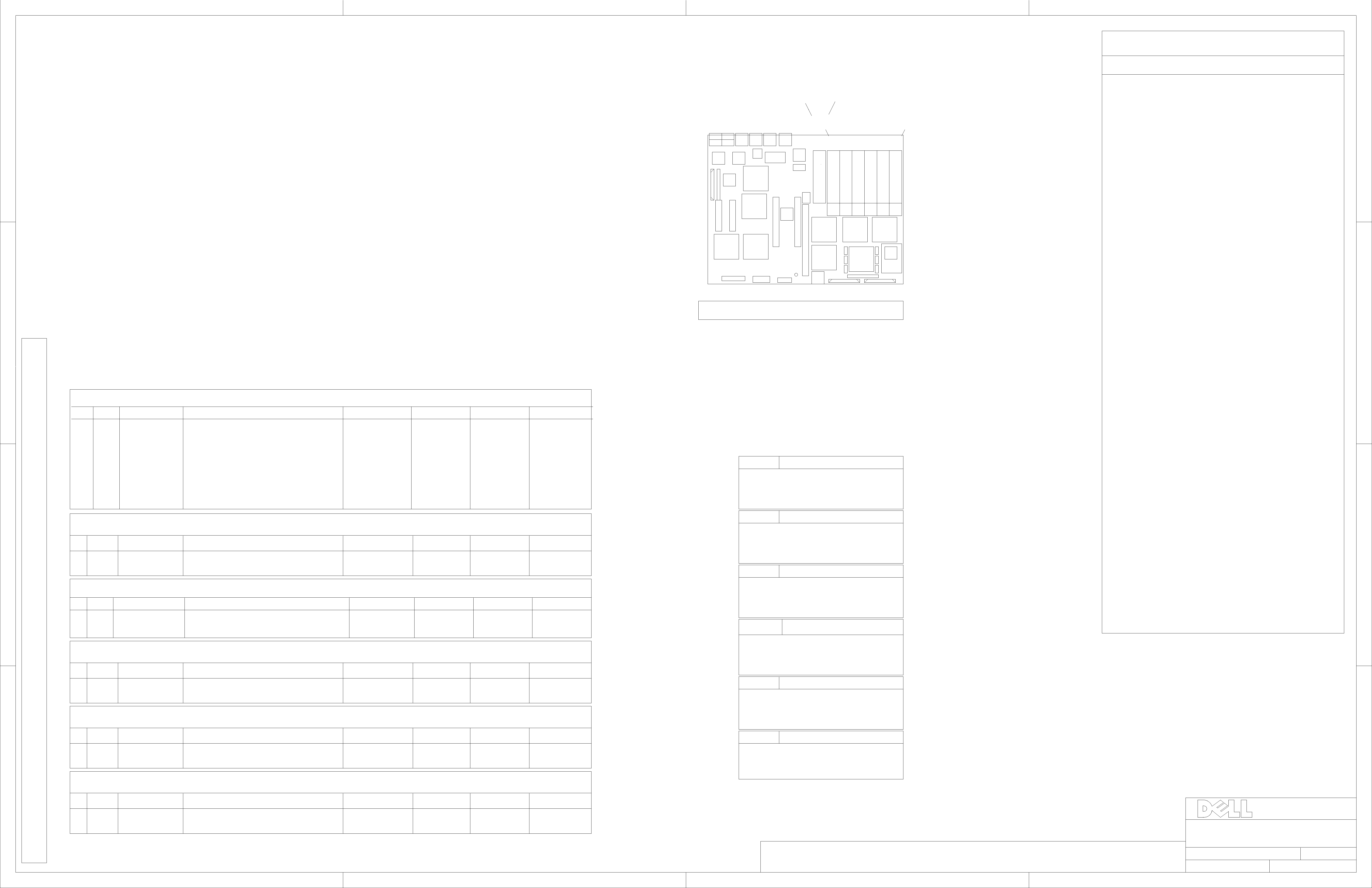

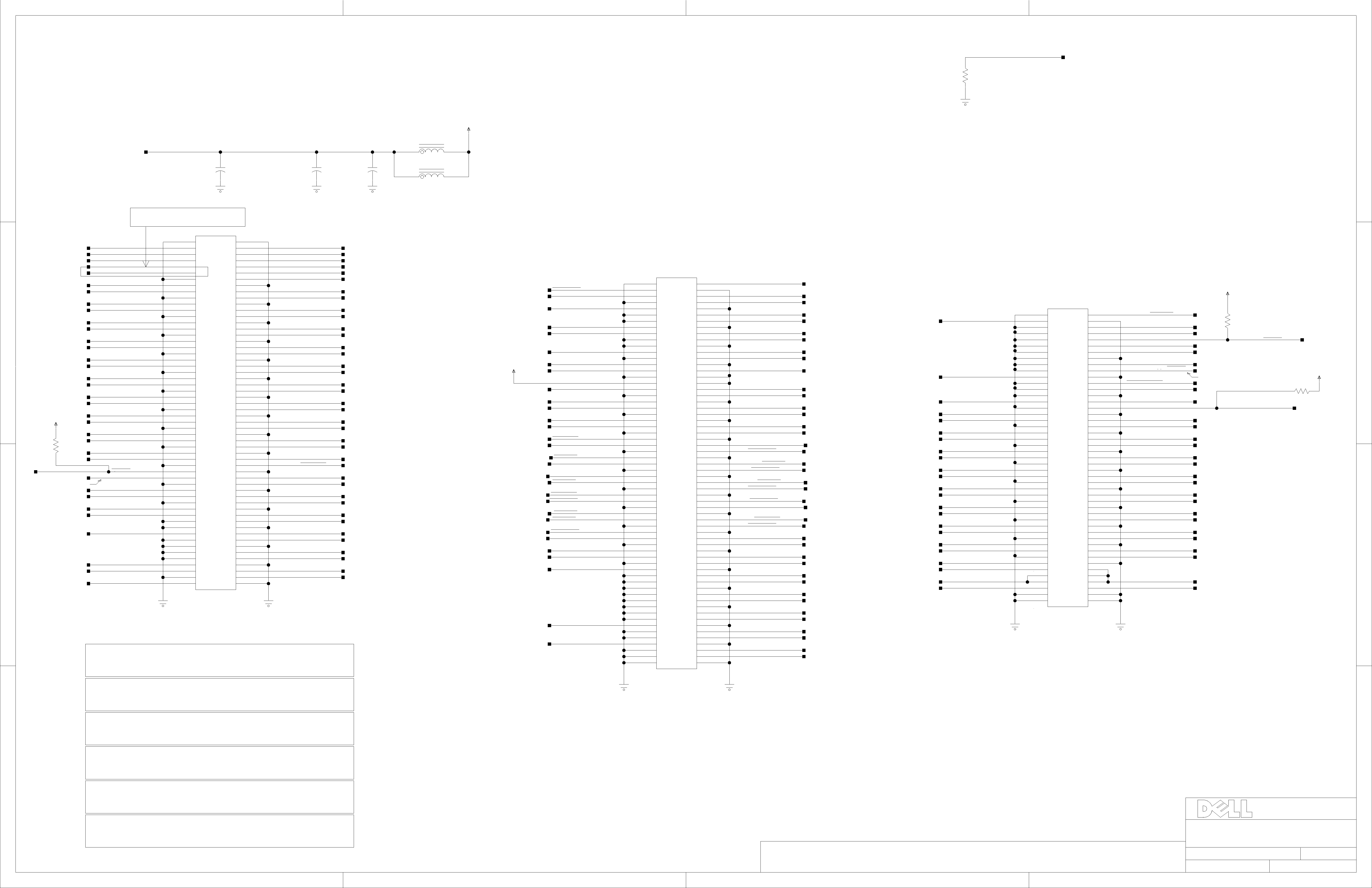

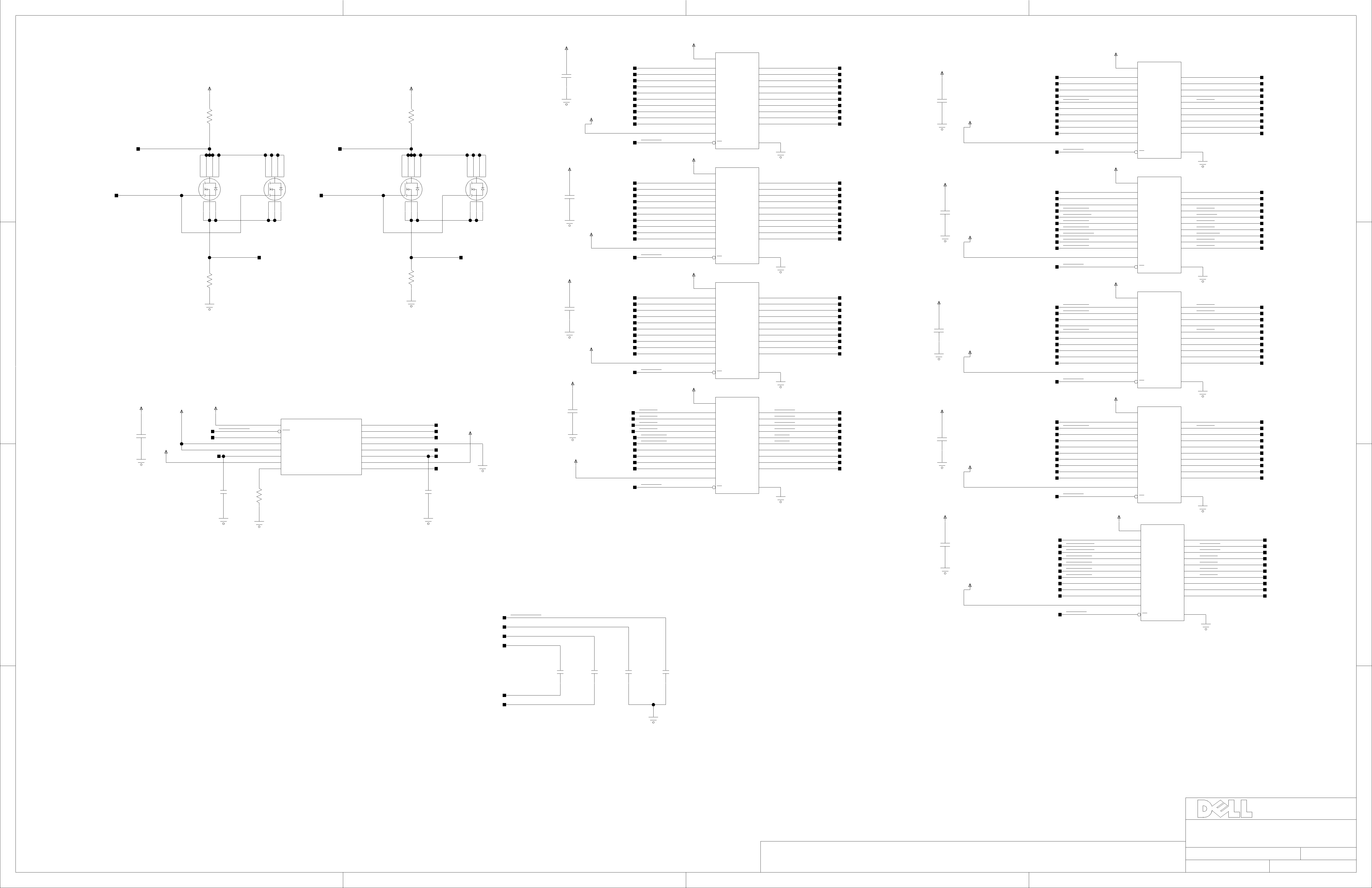

Page 3

To do:

B D

CA

I2C CHART & MAP

12-5-2003_10:50

1

Move RN150 silkscreen up

SAMPLE LAYOUT OF BOARD BELOW

32bit/33MHZ

PCI

5V

SYSTEM BOARD

SIO

FLOPPY/IDE

7890

SCSI_C

MSE/

KYBDPARALLEL

FLASH

i559

CSB5

ENET_100/

USB

ENET_1GB

5401

VGA

XL

CLKS

PCI1

PCIX2

64bit/100MHZ

PCI 3.3V

PCIX3

PCIX4

PCIX5

PCIX6

PCIX7

ADD SEG DEVICE

A0 0 Memory CPU 1

A2 0 Memory CPU 2

30 0 Thermal Sensor CPU 1

32 0 Thermal Sensor CPU 2

C0 0 CMIC Function 0 *

C2 0 CMIC Function 1 *

C4 0 CMIC Function 2 *

C6 0 CMIC Function 3 *

C8 0 CIOB 1 *

CA 0 CIOB 2 *

CC 0 CIOB 3 - RSVD IMB_EXP *

B0 0 CSB5

C0 0 REMC AP *

1

CMIC

REMC

VRM_1

PROC_1 PROC_2

VRM_2

PWR1 PWR2 PWR3

MEC_A

MEC_B

CIOB30

1

ZION

RAID_DIMM

FLASH

5700

BACKPLANE

RESET BLOCK DIAGRAM & PCI DEVICES CHART

7899

CIOB30

SCSI_ASCSI_B

2

FLASH

ESM3

90 0 lm75 planar

98 0 lm75 ambient

AA 0 Control panel

A8 0 CPU card

5E 2 PSPB LM81

AA 2 PDB

14 2 PDB device

A0 2 PS 1

A2 2 PS 2

A4 2 PS 3

A6 2 PS 4

AE 2 AC Switch

A0 1 system event log

AE 1 RAID DIMM (If Present)

2

32BIT PCI DEVICES - BUS 0 - INTERRUPTS

D#

17 0,2

16

15

14

8

6

4 82559 10/100 ETHERNETPCI0_AD20

0 -- CMIC

PCI DEVICES SCANNED

LOW TO HIGH

F#

0,2

0-6

2,3

--

--

(PCI0_AD31)

PCI0_AD30

PCI0_AD24

PCI0_AD22

CIOB-X 2(BUS 4 & 5)

CIOB-X 1(BUS 1 & 3)

CSB5 (SOUTH BRIDGE)

ATI RAGE XL PCI VIDEO

PCI SLOT 1 (PCI1)

ULTRA2 SCSI AIC-7890

4TH3RD2ND1STDEVICEIDSEL

--

--

-- -- --

--

------

------

-- -- -- -PIRQ_0 PIRQ_1

PIRQ_2

PIRQ_3

-- -- --

-- -- --

PIRQ_0 PIRQ_1

-- -- --0,1,

--

REQ/GNT

5

4

3

2

1

0

REQ/GNT

PCIX5 BUS DEVICE

SPARE

SPARE

SPARE

SPARE

PCIX SLOT 7

PCIX SLOT 6

PCIX4 BUS DEVICE

AA 5 ROMB

AC 0 Mem card A

9C 0 Mem card A temp

AC 4 Mem card B

9C 4 Mem card B temp

A8 4 I/O card

E0 4 hot-plug device

EB 3 REMC DP0

EA 3 REMC DP1

EC 7 REMC DP2

EE 7 REMC DP3

A0 3 DIMM 1 Card A

A2 3 DIMM 2 Card A

A4 3 DIMM 3 Card A

A6 3 DIMM 4 Card A

A8 3 DIMM 5 Card A

AA 3 DIMM 6 Card A

AC 3 DIMM 7 Card A

AE 3 DIMM 8 Card A

D2 3 Memory CLKBUF 1

D2 7 Memory CLKBUF 2

2

3

64BIT PCI DEVICES - BUS 1 - INTERRUPTS

D#

8

6

F#

0,1

PCI1_AD24

PCI1_AD22

INTEL GC80303

BROADCOM 5700 1Gb NIC

64BIT PCI DEVICES - BUS 2 - INTERRUPTS

D#

6

F#

0,1

IDSEL DEVICE 1ST 2ND 3RD 4TH

PCI2_AD22

ULTRA160 SCSI AIC-7899

64BIT PCIX DEVICES - BUS 3 - INTERRUPTS

D#

F#

PIRQ_4 PIRQ_5

PIRQ_6

SIRQ_0(A) SIRQ_1(B)

2ND1ST 4TH3RDDEVICEIDSEL

4TH3RD2ND1STDEVICEIDSEL

-- --

------

5 SPARE

SPARE4

3

2

1

0

REQ/GNT

5

4

3

2

1

0

----

REQ/GNT

5 SPARE

4

3

2

1

0

SPARE

SPARE

PCIX SLOT 5

PCIX SLOT 4

PCIX3 BUS DEVICE

SPARE

SPARE

SPARE

SPARE

PCIX SLOT 3

PCIX SLOT 2

PCI2 BUS DEVICE

SPARE

SPARE

SPARE

SPARE

AIC-7899

A0 7 DIMM 1 Card B

A2 7 DIMM 2 Card B

A4 7 DIMM 3 Card B

A6 7 DIMM 4 Card B

A8 7 DIMM 5 Card B

AA 7 DIMM 6 Card B

AC 7 DIMM 7 Card B

AE 7 DIMM 8 Card B

* Removed, but can be reinserted

by reinstalling QB14 & QB 15

3

8

6

PCIX3_AD24

PCIX3_AD22

PCIX SLOT 3 (PCIX3)

PCIX SLOT 2 (PCIX2)

PIRQ_7 PIRQ_8 PIRQ_9 PIRQ_10

PIRQ_11 PIRQ_13

PIRQ_12

PIRQ_14

64BIT PCIX DEVICES - BUS 4 - INTERRUPTS

D#

F#

8

6

4 4

IDSEL DEVICE 3RD

PCIX4_AD24

PCIX4_AD22

PCIX SLOT 5 (PCIX5)

PCIX SLOT 4 (PCIX4)

PIRQ_15 PIRQ_16 PIRQ_17 PIRQ_18

PIRQ_19 PIRQ_20 PIRQ_21 PIRQ_22

4TH1ST 2ND

REQ/GNT

4 SPARE

3

2

1

0

REQ/GNT

4 RESERVED

3

2

1

0

PCI1 BUS DEVICE

SPARE5

SPARE

SPARE

INTEL GC80303 ZION

BROADCOM 5700 1Gb

PCI0 BUS DEVICE

AIC-7890

INTEL i82559 10/100

ATI RAGE XL VGA

PCI SLOT 1

64BIT PCIX DEVICES - BUS 5 - INTERRUPTS

D#

F#

2ND1ST 4TH3RDDEVICEIDSEL

COMPUTER

CORPORATION

8

6

PCIX5_AD24

PCIX5_AD22

PCI DEVICES CHART -- THREE XIOAPIC'S! INPUTS FOR 2ND & 3RD BELOW

PCIX SLOT 7 (PCIX7)

PCIX SLOT 6 (PCIX6)

PIRQ_31 IS SPARE!

PIRQ_23 PIRQ_24 PIRQ_25 PIRQ_26

PIRQ_27 PIRQ_28 PIRQ_29

A B

PIRQ_30

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

TITLE

DWG NO.

DATE

DC

AUSTIN,TEXAS

SCHEM,PLN,PE4600,2P

H3007

SHEET

12/5/2003

REV.

A02

3 OF 63

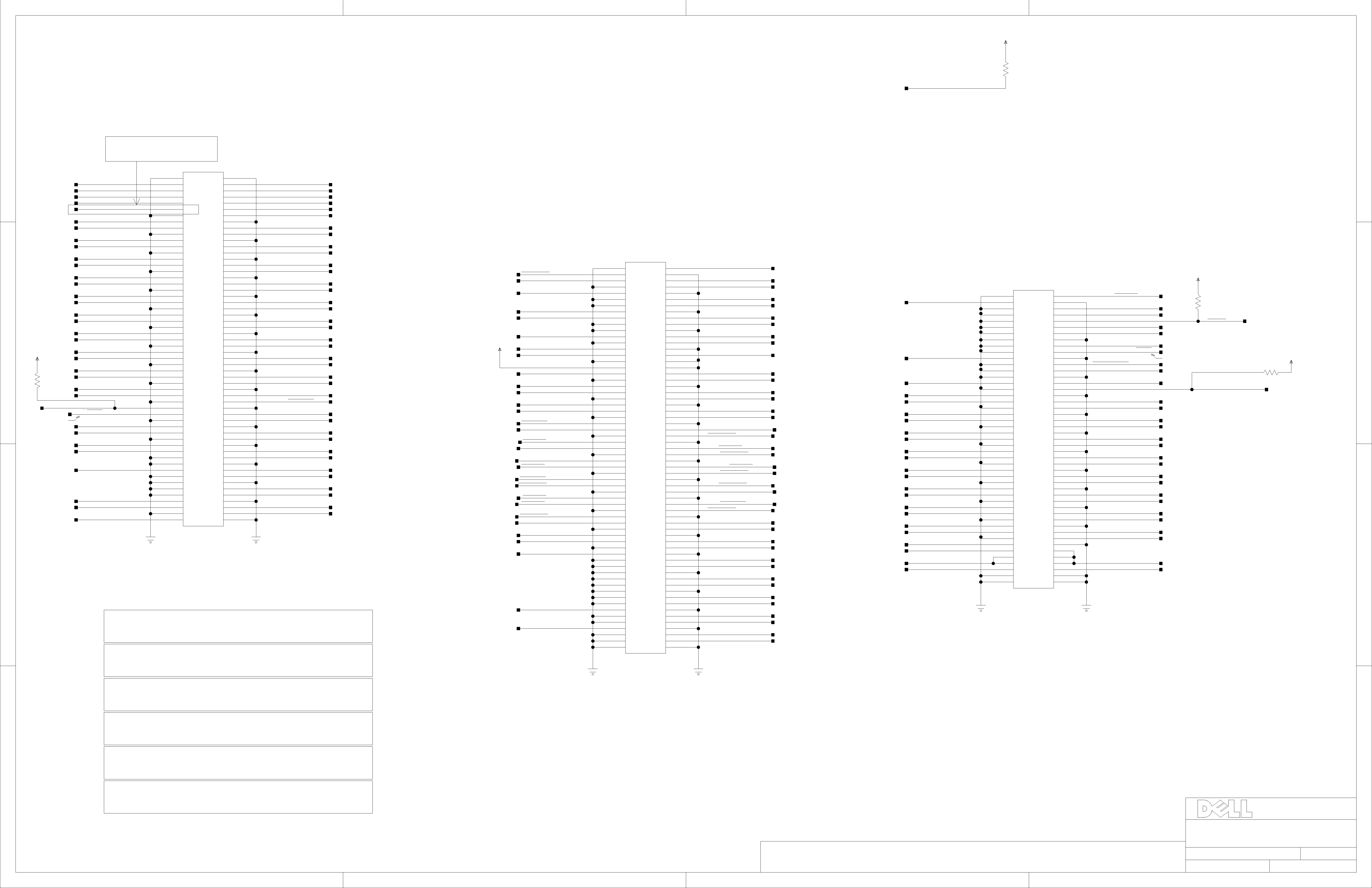

Page 4

1

+3.3V

R321

10K-5%

R270

10K-5%

R318

10K-5%

R326

10K-5%

21

21

21

21

NP*

NP*

R275

1 2

10K-5%

NP*

R314

1 2

10K-5%

R276

1 2

10K-5%

R271

1 2

10K-5%

NP*

NP*

R325

1 2

R274

1K-5%

21

ROOM=MAIN_SYN

21

R269

1K-5%

R315

1K-5%

1 2

220

21

R319

NP*

220

21

R277

NP*

220

R327

1 2

NP*

220

CK_14M_CSB_R

CK_48M_SIO_R

CK_48M_USB_R

SYN_MULTSEL0

SYN_MULTSEL1

SYN_PWRDN

SPREAD

2 1

SUB*_20272

R272

ADD*_81526

220

1 2

4

4

4

4

4

4,41

GPI_SPREAD_EN

GPI_SYN_SEL100

12

SEL100

NP*

R273

22-5%

4,44

4,44

21

1 2

R267

22-5%

R279

1 2

R322

22-5%

B D

ROOM=MAIN_SYN

21

CK_14M_CSB

CK_48M_SIO

CK_48M_USB

CK_33M_PBUF2

39

44

39

4

ROOM=MAIN_SYN_TOP

CA

DIFF PAIR GUIDELINE: 6MIL TRACE/14MIL SPACING

12-5-2003_10:50

ROOMS COMPLETE

1

2

SPREAD IN = SPREAD ENABLED

SPREAD OUT = SPREAD DISABLED

SEL100 IN = 100MHZ

SEL100 OUT = 133MHZ

MULTSEL0 & MULTSEL1 SELECTION

0 0 60ohm, 0.71V

0 1 50ohm, 0.71V

SELA & SELB SELECTION

0 0 H=100M,ACTIVE MODE

1 1 ALL CLOCKS TRI-STATED

+3.3V

L35

21

600mA

21

C275

+3.3V

4.7uF

C277

6.3V-10%

1 2

.01uF 50V.01uF 50V

21

CB331

4.7uF

CB319

6.3V-10%

1 2

1 2

CB330

0.1uF 16V0.1uF 16V

21

CB324

0.1uF 16V

390pF

50V-10%

C314

10pF

1 2

NP*

1 2

CB322

SUB*_32JGM

20272 IS A 2X4

SYN_XIN1

SYN_XIN2

X4

21

14.31818MHz

R323

12

1M-5%

NP*

21

50V-5%

3300pF

50V-20%

C315

NP*

21

CB325

R324

10pF

50V-5%

21

CB315

0.1uF 16V

475-1%

1 2

CB345

0.1uF 16V

4

4

4

21

0.1uF 16V

4,44

4,44

4,41

V_3P3_SYN1

CK_33M_PCI_R

GPI_SYN_SEL100

CK_14M_CSB_R

SYN_IREF_26

CK_48M_USB_R

CK_48M_SIO_R

SYN_MULTSEL0

4

SYN_MULTSEL1

4

GPI_SPREAD_EN

SYN_PWRDN

22-5%

U97

22 7

XIN HCLK0

23

XOUT

1

CLK33

48

SEL100/133

19

REF

26

IREF

3

3V48/SELA

4

3V48B/SELB

30

MULTISEL0

29

MULTISEL1

20

SPREAD

44

PWRDWN

2

VDD0

6

VDD1

12

VDD2

18

VDD3

24

VDD4

25

VDD5

31

VDD6

37

VDD7

43

VDD8

46

VDD9

CDC950/9248

TSSOP48

SUB*_4C853

HCLKB0

HCLK1

HCLKB1

HCLK2

HCLKB2

HCLK3

HCLKB3

HCLK4

HCLKB4

HCLK5

HCLKB5

HCLK6

HCLKB6

HCLK7

HCLKB7

GND0

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

8

10

11

13

14

16

17

42

41

39

38

36

35

33

32

5

9

15

21

27

28

34

40

45

47

R_CK_100M_MECA_P

R_CK_100M_MECA_N

R_CK_100M_AP_P

R_CK_100M_AP_N

R_CK_100M_ITP

R_CK_100M_ITP

R_CK_100M_MECB_P

R_CK_100M_MECB_N

R_CK_100M_CMIC

R_CK_100M_CMIC

NC_CK_100M_SYN33

NC_CK_100M_SYN32

R_CK_100M_CPU0

R_CK_100M_CPU0

R_CK_100M_CPU1

R_CK_100M_CPU1

R283

22-5%

R301

1 2

22-5%

R309

22-5%

R317

1 2

22-5%

R284

1

22-5%

R302

1 2

22-5%

R310

1 2

22-5%

1 2

21

1 2

21

1 2

2

1 2

R278

22-5%

R287

22-5%

R305

22-5%

R313

22-5%

R281

22-5%

R288

22-5%

R306

22-5%

MATCH LENGTH OF ALL THESE CLOCKS

ALL OF BELOW ARE 5W RULE

CK_100M_CPU0

CK_100M_CPU0

21

21

21

21

R280

49.9-1%

R286

21

49.9-1%

21

R304

49.9-1%

R312

21

49.9-1%

21

R418

49.9-1%

21

R289

49.9-1%

CK_100M_AP_FIRST_P

CK_100M_AP_FIRST_N

21

R307

49.9-1%

CK_100M_CPU1

CK_100M_CPU1

CK_100M_MECA_P

CK_100M_MECA_N

CK_100M_ITP

CK_100M_ITP

CK_100M_MECB_P

CK_100M_MECB_N

CK_100M_CMIC

CK_100M_CMIC

5

5

5

5

13

13

12

12

9

9

14

14

11

11

2

ROOM=PCI_BUF1

ROOM=PCI_BUF1_TOP

3

21

C276

4.7uF

C278

6.3V-10%

1 2

L36

1 2

600mA

21

CB300

4.7uF

CB301

6.3V-10%

V_3P3_SYN2

21

390pF

1 2

CB344

50V-10%

21

CB313

3300pF

SUB*_32JGM

50V-20%

1 2

CB308

0.1uF 16V

4C853 IS TSSOP48 ONLY

21

R282

49.9-1%

21

R300

49.9-1%

R308

21

49.9-1%

21

R316

49.9-1%

R285

21

49.9-1%

21

R303

49.9-1%

21

R311

49.9-1%

4C853 RCC_SYN (TSSOP48) IS:

TI CDC950DGG

ICS ICS9248AG-150

PHILIPS PCK2022RDGG

PERICOM PI6C210A

R328

ROOM=PCI_BUF2_TOP

MATCH ALL BELOW CLOCK LENGTHS (SLOTS WILL BE SHORTER)

CK_33M_NICCSB5_R 21

R329

21

22-5%

22-5%

R334

CK_33M_NIC100

CK_33M_CSB5

DELAY_RULE=::1.200N:1.300N

CK_33M_CIOB1

21

50

39

17

3

R361

+3.3V

KLM_X04 -- DELETED EMPNIC RESISTOR R2010

L48

V_3P3_PCK

600mA

21

1 2

CB387

+3.3V_AUX

R398

39,44

4 4

CSB_SLP_S5

14.31818MHz

NP*

15pF 50V

C367

1 2

X6

1 2

R391

1M-5%

0-5%

12

15pF 50V

C369

PER_CLK_XIN

PER_CLK_XOUT

R394

1 2

NP*

8.2K-5%

EN_SLP_S5

+3.3V_AUX

21

R386

P#5E714 IS CY2292SL-1N2 (HAS 20MHZ)

OLD P#12MWW IS CY2292SL-1M1

8.2K-5%

4

XTALIN

5

XTALOUT

15

S2/SUSPEND*

13

S1

12

S0

16

SHUTDWN*/OE

3

GND3

11

GND11

ROOM=PER_CLK

U119

CY2292SL-319

Peripheral CLK

SUB=SUB*_5E714

VDD2

VDD14

XBUF

CPUCLK

CLKA

CLKB

CLKC

CLKD

2

14

6

8

10

9

1

7

CK_14M_XLSYN_R

CK_40M_7890SYN_R

CK_25M_I559SYN_R

CK_20M_CPLD_R CK_20M_CPLD

CK_10M_ZIRCONSYN_R

CB388

0.1uF 16V

CB382

0.1uF 16V

4.7uF

1 2

R187

33-5%

R407

1 2

33-5%

R401

33-5%

R406

22-5%

R385

1 2

33-5%

12

CB383

6.3V-10%

CK_14M_XLSYN

21

CK_40M_7890SYN

CK_25M_I559SYN

21

NP*

21

CK_10M_ZIRCONSYN

.01uF 50V

+3.3V_AUX

21

12

C362

.01uF 50V

21

CB367

48

47

50

41

51

4.7uF

C352

6.3V-10%

1 2

1 2

.01uF 50V

L40

600mA

21

CB359

4.7uF

CB358

6.3V-10%

21

0.1uF 16V

V_3P3_PBUF2

21

CB350

390pF

50V-10%

1 2

CB349

3300pF

SUB*_32JGM

1 2

CB357

50V-20%

1 2

CB346

0.1uF 16V

.01uF 50V

1 2

CB347

.01uF 50V

4

ROOM=PCI_BUF2

R364

10K-5%

R366

10K-5%

NP*

SP_R10K_2

CK_33M_PBUF2

21

21

R363

10K-5%

1

VDD0

5

VDD1

10

VDD2

19

VDD3

24

VDD4

28

VDD5

14

SDATA

21

15

9

4

8

12

17

21

25

SCLOCK

BUF_IN

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

W40S11_02

SUB*_2204T

10K-5%

U110

21

VDDIIC

OE

SDRAM0

SDRAM1

SDRAM2

SDRAM3

SDRAM4

SDRAM5

SDRAM6

SDRAM7

SDRAM8

SDRAM9

VSSIIC

PBUF2_OE

13

20

2

3

6

7

22

23

26

27

11

18

16

CK_33M_CIOBS_R

CK_33M_7890SIO_R

CK_33M_HPCVIDEO_R

CK_33M_ZIRCON_CPLD_R

CK_33M_SLOT1_R

CK_33M_PIRQ01_R

CK_33M_PIRQ23_R

SP_CK_33M_CKBF_11

SP_CK_33M_CKBF_18

R335

21

22-5%

R346

21

22-5%

R352

21

22-5%

R353

21

22-5%

R336

21

22-5%

R331

1 2

22-5%

22-5%

R347

1 2

22-5%

R360

1 2

22-5%

R348

1 2

22-5%

R337

1 2

22-5%

R330

22-5%

DELAY_RULE=::1.200N:1.300N

CK_33M_CIOB2

CK_33M_7890

CK_33M_SIO

CK_33M_HPC

CK_33M_VIDEO

CK_33M_ZIRCON

CK_33M_SLOT1

CK_33M_PIRQ0

CK_33M_PIRQ1

CK_33M_PIRQ2

CK_33M_PIRQ3

21

30

47

44

55

48

51

46

40

40

40

40

12

NP*

12

NP*

P#12MWW USED TO BE CY2292SL-1E5 & ALSO CY2292SL-1K6 & ALSO CY2292SL-1M1

????? IS: CY2292SL-1M1 & ICS ?????

OLD P#57846 IS CY2292F BLANK IF NEEDED

CK_40M_7899SYN_R

ROOM=PER_CLK

PLAN IS TO REMOVE AS MANY DISCRETE XTALS & OSC AS POSSIBLE WHERE POSSIBLE

A B

R402

1 2

33-5%

ROOM=PER_CLK_TOP

CK_40M_7899SYN

27

2204T CKBUF_M (SSOP28) IS:

CYPRESS W40S11-02

PERICOM PI6C182AH

ICS ICS9279AF-03

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

CLOCK CHIPS

TITLE

DWG NO.

DATE

DC

COMPUTER

CORPORATION

AUSTIN,TEXAS

SCHEM,PLN,PE4600,2P

H3007

SHEET

12/5/2003

REV.

A02

4 OF 63

Page 5

B D

CA

12-5-2003_10:50

1

2

3

ROOM=PROC_1

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,41

5,41

5,39

5,39

5,39

5,44

5,9,11

5,41

5,41

H_A3

H_A4

H_A5

H_A6

H_A7

H_A8

H_A9

H_A10

H_A11

H_A12

H_A13

H_A14

H_A15

H_A16

H_A17

H_A18

H_A19

H_A20

H_A21

H_A22

H_A23

H_A24

H_A25

H_A26

H_A27

H_A28

H_A29

H_A30

H_A31

H_A32

H_A33

H_A34

H_A35

H_ADSTB0

H_ADSTB1

H_REQ0

H_REQ1

H_REQ2

H_REQ3

H_REQ4

H_ADS

H_AP0

H_AP1

H_BREQ0

H_BREQ1

5

H_BREQ23_PU

5

H_BREQ23_PU

5

H_BINIT

H0_IERR

5,9

H_BPRI

H_BNR

H_LOCK

H_HIT

H_HITM

H_DEFER

H_RS0

H_RS1

H_RS2

H_RSP

H_TRDY

H_A20M

H_FERR

5,9

H_IGNNE

H_SMI

H_STPCLK

H_SLP

H_INIT

H_RST

H_INTR

H_NMI

CK_100M_CPU0

4

CK_100M_CPU0

4

A22

A20

B18

C18

A19

C17

D17

A13

B16

B14

B13

A12

C15

C14

D16

D15

F15

A10

B10

B11

C12

E14

D13

A9

B8

E13

D12

C11

B7

A6

A7

C9

C8

F17

F14

B19

B21

C21

C20

B22

D19

E10

D9

D20

F12

E11

D10

F11

E5

D23

F20

A17

E22

A23

C23

E21

D22

F21

C6

E19

F27

E27

C26

C27

D4

AE6

D6

Y8

B24

G23

Y4

W5

PROC_1

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

ADSTB0

ADSTB1

REQ0

REQ1

REQ2

REQ3

REQ4

ADS

AP0

AP1

BR0

BR1

BR2

BR3

BINIT

IERR

BPRI

BNR

LOCK

HIT

HITM

DEFER

RS0

RS1

RS2

RSP

TRDY

A20M

FERR

IGNNE

SMI

STPCLK

SLP

INIT

RESET

LINT0

LINT1

BCLK0

BCLK1

FOSTER DP REV 1.0

HETERO 1 OF 3

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

DP0

DP1

DP2

DP3

DSTBN0

DSTBN1

DSTBN2

DSTBN3

DSTBP0

DSTBP1

DSTBP2

DSTBP3

DBSY

DRDY

SUB*_0C997

Y26

AA27

Y24

AA25

AD27

Y23

AA24

AB26

AB25

AB23

AA22

AA21

AB20

AB22

AB19

AA19

AE26

AC26

AD25

AE25

AC24

AD24

AE23

AC23

AA18

AC20

AC21

AE22

AE20

AD21

AD19

AB17

AB16

AA16

AC17

AE13

AD18

AB15

AD13

AD14

AD11

AC12

AE10

AC11

AE9

AD10

AD8

AC9

AA13

AA14

AC14

AB12

AB13

AA11

AA10

AB10

AC8

AD7

AE7

AC6

AC5

AA8

Y9

AB6

AC18

AE19

AC15

AE17

Y21

Y18

Y15

Y12

Y20

Y17

Y14

Y11

F18

E18

H_DP0

H_DP1

H_DP2

H_DP3

H_DSTBN0

H_DSTBN1

H_DSTBN2

H_DSTBN3

H_DSTBP0

H_DSTBP1

H_DSTBP2

H_DSTBP3

H_DBSY

H_DRDY

NEW TOOL-LESS P#0C997

H_D0

H_D1

H_D2

H_D3

H_D4

H_D5

H_D6

H_D7

H_D8

H_D9

H_D10

H_D11

H_D12

H_D13

H_D14

H_D15

H_D16

H_D17

H_D18

H_D19

H_D20

H_D21

H_D22

H_D23

H_D24

H_D25

H_D26

H_D27

H_D28

H_D29

H_D30

H_D31

H_D32

H_D33

H_D34

H_D35

H_D36

H_D37

H_D38

H_D39

H_D40

H_D41

H_D42

H_D43

H_D44

H_D45

H_D46

H_D47

H_D48

H_D49

H_D50

H_D51

H_D52

H_D53

H_D54

H_D55

H_D56

H_D57

H_D58

H_D59

H_D60

H_D61

H_D62

H_D63

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,11

5,11

5,11

5,11

5,11

5,11

5,11

5,11

5,10

5,10

Swizzled.

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,9

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,41

5,9

5,41

5,39

5,39

5,39

5,44

5,9,11

5,41

5,41

H_A3

H_A4

H_A5

H_A6

H_A7

H_A8

H_A9

H_A10

H_A11

H_A12

H_A13

H_A14

H_A15

H_A16

H_A17

H_A18

H_A19

H_A20

H_A21

H_A22

H_A23

H_A24

H_A25

H_A26

H_A27

H_A28

H_A29

H_A30

H_A31

H_A32

H_A33

H_A34

H_A35

H_ADSTB0

H_ADSTB1

H_REQ0

H_REQ1

H_REQ2

H_REQ3

H_REQ4

H_ADS

H_AP0

H_AP1

H_BREQ1

5

H_BREQ0

H_BREQ23_PU

5

H_BREQ23_PU

5

H_BINIT

H1_IERR

H_BPRI

H_BNR

H_LOCK

H_HIT

H_HITM

H_DEFER

H_RS0

H_RS1

H_RS2

H_RSP

H_TRDY

H_A20M

H_FERR

H_IGNNE

H_SMI

H_STPCLK

H_SLP

H_INIT

H_RST

H_INTR

H_NMI

CK_100M_CPU1

4

CK_100M_CPU1

4

A22

A20

B18

C18

A19

C17

D17

A13

B16

B14

B13

A12

C15

C14

D16

D15

F15

A10

B10

B11

C12

E14

D13

A9

B8

E13

D12

C11

B7

A6

A7

C9

C8

F17

F14

B19

B21

C21

C20

B22

D19

E10

D9

D20

F12

E11

D10

F11

E5

D23

F20

A17

E22

A23

C23

E21

D22

F21

C6

E19

F27

E27

C26

C27

D4

AE6

D6

Y8

B24

G23

Y4

W5

PROC_2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

ADSTB0

ADSTB1

REQ0

REQ1

REQ2

REQ3

REQ4

ADS

AP0

AP1

BR0

BR1

BR2

BR3

BINIT

IERR

BPRI

BNR

LOCK

HIT

HITM

DEFER

RS0

RS1

RS2

RSP

TRDY

A20M

FERR

IGNNE

SMI

STPCLK

SLP

INIT

RESET

LINT0

LINT1

BCLK0

BCLK1

FOSTER DP REV 1.0

HETERO 1 OF 3

SUB*_0C997

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

DP0

DP1

DP2

DP3

DSTBN0

DSTBN1

DSTBN2

DSTBN3

DSTBP0

DSTBP1

DSTBP2

DSTBP3

DBSY

DRDY

ROOM=PROC_2OLD TOOL-REQUIRED P#07RGT

Y26

AA27

Y24

AA25

AD27

Y23

AA24

AB26

AB25

AB23

AA22

AA21

AB20

AB22

AB19

AA19

AE26

AC26

AD25

AE25

AC24

AD24

AE23

AC23

AA18

AC20

AC21

AE22

AE20

AD21

AD19

AB17

AB16

AA16

AC17

AE13

AD18

AB15

AD13

AD14

AD11

AC12

AE10

AC11

AE9

AD10

AD8

AC9

AA13

AA14

AC14

AB12

AB13

AA11

AA10

AB10

AC8

AD7

AE7

AC6

AC5

AA8

Y9

AB6

AC18

AE19

AC15

AE17

Y21

Y18

Y15

Y12

Y20

Y17

Y14

Y11

F18

E18

H_DP0

H_DP1

H_DP2

H_DP3

H_DSTBN0

H_DSTBN1

H_DSTBN2

H_DSTBN3

H_DSTBP0

H_DSTBP1

H_DSTBP2

H_DSTBP3

H_DBSY

H_DRDY

H_D0

H_D1

H_D2

H_D3

H_D4

H_D5

H_D6

H_D7

H_D8

H_D9

H_D10

H_D11

H_D12

H_D13

H_D14

H_D15

H_D16

H_D17

H_D18

H_D19

H_D20

H_D21

H_D22

H_D23

H_D24

H_D25

H_D26

H_D27

H_D28

H_D29

H_D30

H_D31

H_D32

H_D33

H_D34

H_D35

H_D36

H_D37

H_D38

H_D39

H_D40

H_D41

H_D42

H_D43

H_D44

H_D45

H_D46

H_D47

H_D48

H_D49

H_D50

H_D51

H_D52

H_D53

H_D54

H_D55

H_D56

H_D57

H_D58

H_D59

H_D60

H_D61

H_D62

H_D63

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,10

5,11

5,11

5,11

5,11

5,11

5,11

5,11

5,11

5,10

5,10

ROOM=PROC_1

VCORE

RB418

12

H0_THERMTRIP

56.2-1%

RB372

2 1

56.2-1%

RB383

2 1

56.2-1%

RB410

2 1

56.2-1%

RB453

56.2-1%

RB390

1 2

56.2-1%

RB368

1 2

301-1%

RB427

1 2

301-1%

RB428

1 2

301-1%

RB452

1 2

301-1%

RB344

1 2

301-1%

RB421

1 2

301-1%

RB425

1 2

301-1%

RB369

1 2

301-1%

RB334

1 2

301-1%

RB447

1 2

150-1%

RB380

1 2

150-1%

RB382

150-1%

RB381

1 2

150-1%

RB391

150-1%

RB435

40.2-1%

RB413

H1_THERMTRIP

H_FERR

H0_IERR

21

H1_IERR

H_A20M

H_IGNNE

H_SMI

H_STPCLK

H_SLP

H_INIT

H_INTR

H_NMI

H_PWRGOOD

21

21

21

21

H_BINIT

H_BNR

H_HITM

H_HIT

H_MCERR

H_BREQ1

6,9

6,9

5,9

ROOM=CSB

1

Put RB424 close to PROC_1

Put RB411 close to FET

5,9

5,9

5,41

5,41

5,39

5,39

5,39

2

5,44

5,41

5,41

6,60

5,10

5,10

Do need for termination!

5,10

5,10

6,9

ROOM=PROC_2

3

5

40.2-1%

RB414

21

40.2-1%

RB446

40.2-1%

R503

150-1%

RB417

1 2

150-1%

R502

150-1%

RB409

1 2

H_BREQ23_PU

12

21

21

H_BREQ0

C457

21

47pF

50V-5%

CB652

1 2

47pF

50V-5%

C456

21

47pF

50V-5%

CB642

1 2

5,10

0-OHM

SUB*_30661

0-OHM

SUB*_30661

0-OHM

SUB*_30661

0-OHM

5

H_BINIT

H_BNR

H_HIT

H_HITM

5,10

5,10

5,10

5,10

150-1%

47pF

50V-5%

SUB*_30661

4 4

PROCESSORS 1 & 2

COMPUTER

CORPORATION

AUSTIN,TEXAS

TITLE

SCHEM,PLN,PE4600,2P

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

DWG NO.

DATE

H3007

REV.

A02

SHEET

5 OF 6312/5/2003

A B

DC

Page 6

B D

CA

12-5-2003_10:50

1

2

3

VCORE

21

R491

R492

1 2

VCORE

21

R508

R509

1 2

PROC_1 GTL VREF

ROOM=PROC1_REF

49.9-1%100-1%

H0_GTLREF01

SUB*_83008

1 2

1 2

RB363

1K-1%

RB365

1K-1%

RB367

1K-1%

RB360

1K-1%

RB355

1K-1%

RB333

1K-1%

RB343

1K-1%

1uF

10V-10%

1uF

CB622

10V-10%

12

12

12

12

12

12

12

CB564

2 1

0.1uF 16V

H0_GTLREF23

2 1

0.1uF 16V

H0_TESTHI0

H0_TESTHI1

H0_TESTHI2

H0_TESTHI3

H0_TESTHI4

H0_TESTHI5

H0_TESTHI6

CB565

CB517

LM_X04--83008 sub for p/n consolidation

SUB*_83008

CB643

100-1% 49.9-1%

VCORE

21

21

CB621

220pF

50V-10%

220pF

50V-10%

21

CB522

21

CB644

6

6

6

6

6

6

6

6

Route <1.5" trace.

Place 220pf caps under CPU

220pF

50V-10%

6

Route <1.5" trace.

Place 220pf caps under CPU

220pF

50V-10%

GALLATIN SUPPORT

6

6,9

6,9

6,9

6,9

6,9

6,9

6,9

5,6,60

+3.3V

HEATSINK P#????? ***NOT PART OF PWA***

HEATSINK CLIPS P#83MGJ (2 PER PROC) ***NOT PART OF PWA***

1 2

8.2K-5%

RB339

HEATSINK CLIP PLASTIC BOAT P#52JXN (2 PER PROC)

PLASTIC BOAT SCREWS P#89JJP (4 PER PROC)

CPU_SMBALERT

ADD=ADD_52JXN_ASSYDWG

ADD1=ADD_52JXN_ASSYDWG

ADD2=ADD_89JJP_ASSYDWG

ADD3=ADD_89JJP_ASSYDWG

ADD4=ADD_89JJP_ASSYDWG

ADD5=ADD_89JJP_ASSYDWG

ADD6=ADD_92GXR_ASSYDWG

DUAL SCREW MOUNTING UNDERNEATH P#92GXR (1 PER PROC)

EMI CLIP P#?????

AMP TOOL-LESS SOCKET P#0C997

ROOM=PROC_1

12

CB521

0.1uF 16V

PROC_1

H_BPM02

H_BPM13

H_BPM4

H_BPM5

ITP_TDI_H0

9

ITP_TDO_H0

9

ITP_TMS

ITP_TRST

H_PWRGOOD

H0_GTLREF01

6

H0_GTLREF23

6

H0_TESTHI0

6

H0_TESTHI1

6

H0_TESTHI2

6

H0_TESTHI3

6

H0_TESTHI4

6

H0_TESTHI5

6

H0_TESTHI6

6

NC_H0_RSVD1 NC_H1_RSVD1

NC_H0_RSVD2

NC_H0_RSVD3

NC_H0_RSVD4

NC_H0_RSVD5

NC_H0_RSVD8

NC_H0_RSVD13

NC_H0_RSVD17

F6

F8

E7

F5

E8

E4

E24

C24

E25

A25

F24

AB7

W23

W9

F23

F9

W6

W7

W8

Y6

AA7

AD5

AE5

A1

A4

A15

A16

A26

A30

A31

B1

B4

B30

B31

C1

C5

C30

C31

D1

D25

D30

D31

E1

E30

E31

F1

F30

F31

G1

G30

G31

H1

H30

H31

J1

J30

J31

K1

K30

K31

L1

L30

L31

M1

M30

M31

N1

N30

N31

P1

P30

P31

R1

R30

R31

BPM0

BPM1

BPM2

BPM3

BPM4

BPM5

TCK

TDI

TDO

TMS

TRST

PWRGOOD

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

DBI0

DBI1

DBI2

DBI3

VCCA

VCCIOPLL

VCCSENSE

VSSA

VSSSENSE

MCERR

ODTEN

PROCHOT

SKTOCC

THERMTRIP

COMP0

COMP1

VID0

VID1

VID2

VID3

VID4

SM_VCC1

SM_VCC2

SM_ALERT

SM_CLK

SM_DATA

SM_WP

SM_EP_A0

SM_EP_A1

SM_EP_A2

SM_TS_A0

SM_TS_A1

RSVD89

RSVD53

RSVD54

RSVD55

RSVD56

RSVD57

RSVD58

RSVD59

RSVD60

RSVD61

RSVD62

RSVD63

RSVD64

RSVD65

RSVD66

RSVD68

RSVD69

RSVD70

RSVD71

RSVD72

RSVD73

RSVD74

RSVD75

RSVD76

RSVD77

RSVD78

RSVD79

RSVD80

RSVD81

RSVD82

RSVD83

RSVD84

RSVD85

RSVD86

RSVD87

RSVD88

FOSTER DP REV 1.0

HETERO 2 OF 3

AC27

AD22

AE12

AB9

AB4

AD4

B27

AA5

D26

D7

B5

B25

A3

F26

AD16

E16

F3

E3

D3

C3

B3

AE28

AE29

AD28

AC28

AC29

AD29

AA29

AB29

AB28

AA28

Y29

W3

T1

T30

T31

U1

U30

U31

V1

V30

V31

W1

W30

W31

Y1

Y3

Y27

Y28

Y30

Y31

AA1

AA3

AA30

AA31

AB1

AB3

AB30

AB31

AC1

AC30

AC31

AD1

AD30

AD31

AE4

AE15

AE16

NC_H0_VCCSENSE

X05_LM--p/n sub for part consolidation

+3.3V

H_DBI0

H_DBI1

H_DBI2

H_DBI3

V_VID_H0_VCCA

V_VID_H0_VPLL

H_MCERR

H0_ODTEN

H0_PROCHOT

H0_CPU_PRES

H0_THERMTRIP

H0_COMP0

H0_COMP1

H0_VID0

H0_VID1

H0_VID2

H0_VID3

H0_VID4

CPU_SMBALERT

ENV_SEG0_SCL

ENV_SEG0_SDA

GPO_SMB_WP

H0_SM_EP_A0

H0_SM_EP_A1

H0_SM_EP_A2

H0_SM_TS_A0

H0_SM_TS_A1

NC_H0_RSVD89

NC_H0_RSVD67

NC_H0_RSVD68

NC_H0_RSVD69

NC_H0_RSVD73

NC_H0_RSVD77

NC_H0_RSVD80

NC_H0_RSVD86 NC_H1_RSVD86

NC_H0_RSVD87

NC_H0_RSVD88

SUB*_83009

8,41

8,41

8,41

8,41

8,41

6,10

6,10

6,10

6,10

22uF 6.3V

1 2

5,6,9

9

41

5,9

22uF 6.3V

CB487

21

R504

6

6,13,39,53,57

6,13,39,53,57

6

6

6

6

6

6

CB520

2 1

0.1uF 16V

LB22

4.7uH 30mA

LB20

1 2

1 2

SUB*_83009

45.3 -1%

4.7uH 30mA

CB533

21

RB340

SUB=SUB*_08DFE

Tsensor = 30h/31h

PI-ROM = A0h/A1h

45.3 -1%

08DFE IS 43.2ohm 1% SM0603

H0_SM_TS_A0

6

H0_SM_TS_A1

6

H0_SM_EP_A0

6

H0_SM_EP_A1

6

H0_SM_EP_A2

6

VCORE

V_VID_H0_VCCA_FB

RB336

21

V_VID_H0_VPLL_FB

VCORE

21

RB411

Should MCERR be NC or pulled up here?

SUB=SUB*_08DFE

1K-1%

On DIE term

enabled

21

220

RB412

NP*

1 2

1-5%

RB331

1-5%

RB348

1 2

SUB*_21873

21

SUB*_21873

1K-1%

RB350

1K-1%

1 2

6,9

RB356

1 2

6,9

6,9

6,9

6,9

1K-1%

RB361

H_BPM02

H_BPM13

H_BPM4

H_BPM5

RB268

1 2

1 2

150-1%

1K-1%

RB353

1 2

RNB85

6,9

6,9

5,6,60

1K-1%

54

RNB85

39 OHM-5%

ITP_TCK

ITP_TDI_H1

9

ITP_TDO_H1

9

ITP_TMS

ITP_TRST

H_PWRGOOD

H1_GTLREF01

6

H1_GTLREF23

6

NC_H1_RSVD2

NC_H1_RSVD3

NC_H1_RSVD4

NC_H1_RSVD5

NC_H1_RSVD8

NC_H1_RSVD13

NC_H1_RSVD17

VCORE

1 8

39 OHM-5%

H1_TESTHI0

6

H1_TESTHI1

6

H1_TESTHI2

6

H1_TESTHI3

6

H1_TESTHI4

6

H1_TESTHI5

6

H1_TESTHI6

6

RNB85

3 6

72

RNB85

39 OHM-5%

39 OHM-5%

ROOM=PROC_2

PROC_2

F6

BPM0

F8

BPM1

E7

BPM2

F5

BPM3

E8

BPM4

E4

BPM5

E24

TCK

C24

TDI

E25

TDO

A25

TMS

F24

TRST

AB7

PWRGOOD

W23

GTLREF0

W9

GTLREF1

F23

GTLREF2

F9

GTLREF3

W6

TESTHI0

W7

TESTHI1

W8

TESTHI2

Y6

TESTHI3

AA7

TESTHI4

AD5

TESTHI5

AE5

TESTHI6

A1

RSVD1

A4

RSVD2

A15

RSVD3

A16

RSVD4

A26

RSVD5

A30

RSVD6

A31

RSVD7

B1

RSVD8

B4

RSVD9

B30

RSVD10

B31

RSVD11

C1

RSVD12

C5

RSVD13

C30

RSVD14

C31

RSVD15

D1

RSVD16

D25

RSVD17

D30

RSVD18

D31

RSVD19

E1

RSVD20

E30

RSVD21

E31

RSVD22

F1

RSVD23

F30

RSVD24

F31

RSVD25

G1

RSVD26

G30

RSVD27

G31

RSVD28

H1

RSVD29

H30

RSVD30

H31

RSVD31

J1

RSVD32

J30

RSVD33

J31

RSVD34

K1

RSVD35

K30

RSVD36

K31

RSVD37

L1

RSVD38

L30

RSVD39

L31

RSVD40

M1

RSVD41

M30

RSVD42

M31

RSVD43

N1

RSVD44

N30

RSVD45

N31

RSVD46

P1

RSVD47

P30

RSVD48

P31

RSVD49

R1

RSVD50

R30

RSVD51

R31

RSVD52

FOSTER DP REV 1.0

HETERO 2 OF 3

DBI0

DBI1

DBI2

DBI3

VCCA

VCCIOPLL

VCCSENSE

VSSA

VSSSENSE

MCERR

ODTEN

PROCHOT

SKTOCC

THERMTRIP

COMP0

COMP1

VID0

VID1

VID2

VID3

VID4

SM_VCC1

SM_VCC2

SM_ALERT

SM_CLK

SM_DATA

SM_WP

SM_EP_A0

SM_EP_A1

SM_EP_A2

SM_TS_A0

SM_TS_A1

RSVD89

RSVD53

RSVD54

RSVD55

RSVD56

RSVD57

RSVD58

RSVD59

RSVD60

RSVD61

RSVD62

RSVD63

RSVD64

RSVD65

RSVD66

RSVD68

RSVD69

RSVD70

RSVD71

RSVD72

RSVD73

RSVD74

RSVD75

RSVD76

RSVD77

RSVD78

RSVD79

RSVD80

RSVD81

RSVD82

RSVD83

RSVD84

RSVD85

RSVD86

RSVD87

RSVD88

AC27

AD22

AE12

AB9

AB4

AD4

B27

AA5

D26

D7

B5

B25

A3

F26

AD16

E16

F3

E3

D3

C3

B3

AE28

AE29

AD28

AC28

AC29

AD29

AA29

AB29

AB28

AA28

Y29

W3

T1

T30

T31

U1

U30

U31

V1

V30

V31

W1

W30

W31

Y1

Y3

Y27

Y28

Y30

Y31

AA1

AA3

AA30

AA31

AB1

AB3

AB30

AB31

AC1

AC30

AC31

AD1

AD30

AD31

AE4

AE15

AE16

ADD=ADD_52JXN_ASSYDWG

ADD1=ADD_52JXN_ASSYDWG

ADD2=ADD_89JJP_ASSYDWG

ADD3=ADD_89JJP_ASSYDWG

ADD4=ADD_89JJP_ASSYDWG

ADD5=ADD_89JJP_ASSYDWG

ADD6=ADD_92GXR_ASSYDWG

CB500

2 1

H_DBI0

H_DBI1

H_DBI2

H_DBI3

V_VID_H1_VCCA

V_VID_H1_VPLLITP_TCK

NC_H1_VCCSENSE

H1_VSSAH0_VSSA

NC_H1_VSSSENSENC_H0_VSSSENSE

X05_LM--p/n sub for part consolidation

H_MCERR

H1_ODTEN

H1_PROCHOT

H1_CPU_PRES

H1_THERMTRIP

H1_COMP0

H1_COMP1

H1_VID0

H1_VID1

H1_VID2

H1_VID3

H1_VID4

CPU_SMBALERT

ENV_SEG0_SCL

ENV_SEG0_SDA

GPO_SMB_WP

NC_H1_RSVD89

NC_H1_RSVD67

NC_H1_RSVD68

NC_H1_RSVD69

NC_H1_RSVD73

NC_H1_RSVD77

NC_H1_RSVD80

NC_H1_RSVD83NC_H0_RSVD83

NC_H1_RSVD87

NC_H1_RSVD88

6,10

6,10

6,10

6,10

+3.3V

22uF 6.3V

1 2

CB490

SUB*_83009

5,6,9

9

41

5,9

8,41

8,41

8,41

8,41

8,41

6

6,13,39,53,57

6,13,39,53,57

6

NC_H1_SM_TS_A1

12

CB540

0.1uF 16V

4.7uH 30mA

1 2

22uF 6.3V

1 2

21

R505

Tsensor = 32h/33h

PI-ROM = A2h/A3h

4.7uH 30mA

CB532

SUB*_83009

45.3 -1%

SUB=SUB*_08DFE

H1_SM_PR_A0

H1_SM_PR_A1

H1_SM_PR_A2

H1_SM_TS_A0

0.1uF 16V

V_VID_H1_VCCA_FB

LB23

21

V_VID_H1_VPLL_FB

LB21

21

RB335

08DFE IS 43.2ohm 1% SM0603

45.3 -1%

SUB=SUB*_08DFE

21873 IS ZERO OHM

RB341

1-5%

RB332

1 2

1-5%

VCORE

21

NP*

RB407

RB419

1K-1%

1K-1%

On DIE term disabled

21

220

+3.3V

100-1%

12

12

1K-1%

RB349

RB351

RB1091

12

VCORE

21

SUB*_21873

SUB*_21873

1K-1%

RB1090

12

VCORE

21

R493

R494

1 2

VCORE

21

RB373

RB374

1 2

+3.3V

0.1uF 16V

1 2

CB515

Jaguar 2.0 Change: Intel recommendation: Changed

address resistors from just 1 (RB349) into 3

separate ones. RB1090 & 1091 should be near RB349

100-1% 49.9-1%

100-1% 49.9-1%

ROOMS COMPLETE

PROC_2 GTL VREF

ROOM=PROC2_REF

H1_GTLREF01

21

1uF

CB510

1 2

SUB*_83008

CB641

1 2

SUB*_83008

CB509

1uF

CB619

10V-10%

2 1

10V-10%

0.1uF 16V

H1_GTLREF23

2 1

0.1uF 16V

VCORE

CB562

RB362

1K-1%

RB364

1K-1%

RB366

1K-1%

RB357

1K-1%

RB354

1K-1%

RB338

1K-1%

RB337

1K-1%

220pF

21

CB620

12

12

12

12

12

12

12

21

CB561

50V-10%

220pF

CB656

50V-10%

H1_TESTHI0

H1_TESTHI1

H1_TESTHI2

H1_TESTHI3

H1_TESTHI4

H1_TESTHI5

H1_TESTHI6

6

220pF

50V-10%

Route <1.5" trace.

Place 220pf caps under CPU

6

21

220pF

50V-10%

Route <1.5" trace.

Place 220pf caps under CPU

6

6

6

6

6

6

6

1

2

3

VCORE

VCORE

CPU-- Misc. & RSVD

GALLATIN SUPPORT

4 4

KLM -- CHANGED RB334, RB328, RB339, RB329 TO 1 OHM

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

PROCESSORS 1 & 2

TITLE

SCHEM,PLN,PE4600,2P

DWG NO.

H3007

DATE

12/5/2003

COMPUTER

CORPORATION

AUSTIN,TEXAS

REV.

A02

SHEET

6 OF 63

A B

DC

Page 7

Length matching groups

1 ADSTB0 REQ[4:0]#,A[16:3]#

2 ADSTB1 A[35:17]#

3 DSTBP0#/N0# D[15:0]#,DBI0#

4 DSTBP1#/N1# D[31:16]#,DBI1#

5 DSTBP2#/N2# D[47:32]#,DBI2#

6 DSTBP3#/N3# D[63:48]#,DBI3#

General routing rule 5mil, 15 mil space

FERR#,PROCHOT#, THRMTRIP

BR[3:0]#

- Proc0 to Proc1 is ~4.5" matched to within 0.5"

B D

CA

12-5-2003_10:50

ROOMS COMPLETE

1

2

3

A2

A8

A14

A18

A24

A28

B6

B12

B20

B26

B29

C2

C4

C10

C16

C22

C28

D8

D14

D18

D24

D29

E2

E6

E12

E20

E26

E28

F4

F10

F16

F22

F29

G2

G4

G6

G8

G24

G26

G28

H3

H5

H7

H9

H23

H25

H27

H29

J2

J4

J6

J8

J24

J26

J28

K3

K5

K7

K9

K23

K25

K27

K29

L2

L4

L6

L8

L24

L26

L28

M3

M5

M7

M9

M23

M25

M27

PROC_1

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

VCC101

VCC102

VCC103

VCC104

VCC105

VCC106

VCC107

VCC108

VCC109

VCC110

VCC111

VCC112

VCC113

VCC114

VCC115

VCC116

VCC117

VCC118

VCC119

VCC120

VCC121

VCC122

VCC123

VCC124

VCC125

VCC126

VCC127

VCC128

VCC129

VCC130

VCC131

VCC132

VCC133

VCC134

VCC135

VCC136

VCC137

VCC138

VCC139

VCC140

VCC141

VCC142

VCC143

VCC144

VCC145

VCC146

VCC147

VCC148

VCC149

VCC150

VCC151

VCC152

VCC153

VCC154

VCC155

M29

N3

N5

N7

N9

N23

N25

N27

N29

P2

P4

P6

P8

P24

P26

P28

R3

R5

R7

R9

R23

R25

R27

R29

T2

T4

T6

T8

T24

T26

T28

U3

U5

U7

U9

U23

U25

U27

U29

V2

V4

V6

V8

V24

V26

V28

W25

W27

W29

Y10

Y16

Y22

AA4

AA6

AA12

AA20

AA26

AB2

AB8

AB14

AB18

AB24

AC3

AC4

AC10

AC16

AC22

AD2

AD6

AD12

AD20

AD26

AE3

AE8

AE14

AE18

AE24

Y2

1

VCORE

ROOM=PROC_2ROOM=PROC_1

4V-20%

Length matching groups

1 ADSTB0 REQ[4:0]#,A[16:3]#

VCOREVCORE

PROC_2

M29

N3

N5

N7

N9

N23

N25

N27

N29

P2

P4

P6

P8

P24

P26

P28

R3

R5

R7

R9

R23

R25

R27

R29

T2

T4

T6

T8

T24

T26

T28

U3

U5

U7

U9

U23

U25

U27

U29

V2

V4

V6

V8

V24

V26

V28

W25

W27

W29

Y10

Y16

Y22

AA4

AA6

AA12

AA20

AA26

AB2

AB8

AB14

AB18

AB24

AC3

AC4

AC10

AC16

AC22

AD2

AD6

AD12

AD20

AD26

AE3

AE8

AE14

AE18

AE24

Y2

A2

A8

A14

A18

A24

A28

B6

B12

B20

B26

B29

C2

C4

C10

C16

C22

C28

D8

D14

D18

D24

D29

E2

E6

E12

E20

E26

E28

F4

F10

F16

F22

F29

G2

G4

G6

G8

G24

G26

G28

H3

H5

H7

H9

H23

H25

H27

H29

J2

J4

J6

J8

J24

J26

J28

K3

K5

K7

K9

K23

K25

K27

K29

L2

L4

L6

L8

L24

L26

L28

M3

M5

M7

M9

M23

M25

M27

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

VCC101

VCC102

VCC103

VCC104

VCC105

VCC106

VCC107

VCC108

VCC109

VCC110

VCC111

VCC112

VCC113

VCC114

VCC115

VCC116

VCC117

VCC118

VCC119

VCC120

VCC121

VCC122

VCC123

VCC124

VCC125

VCC126

VCC127

VCC128

VCC129

VCC130

VCC131

VCC132

VCC133

VCC134

VCC135

VCC136

VCC137

VCC138

VCC139

VCC140

VCC141

VCC142

VCC143

VCC144

VCC145

VCC146

VCC147

VCC148

VCC149

VCC150

VCC151

VCC152

VCC153

VCC154

VCC155

2 ADSTB1 A[35:17]#

3 DSTBP0#/N0# D[15:0]#,DBI0#

4 DSTBP1#/N1# D[31:16]#,DBI1#

5 DSTBP2#/N2# D[47:32]#,DBI2#

6 DSTBP3#/N3# D[63:48]#,DBI3#

General routing rule 5mil, 15 mil space

FERR#,PROCHOT#, THRMTRIP

- 10 mil trace with pullup at each end <1" past ball

A20M#,IGNE#, INIT#, Lint[1:0],SLP#,SMI#, STPCLK#, and H_PWRGOOD

- 10 mil trace with pullup <1" from ball after last processor

BR[3:0]#

- Proc0 to Proc1 is ~4.5" matched to within 0.5"

- pullup at each end with <1" past ball (BR0, BR2, and BR3 only have pullup at end)

ROOM=PROC_1

VCORE

Place 3-4 over Addr\Ctrl

Place 4-6 over data

h1

1 2

CB590

VCORE

1 2

CB585

1 2

CB613

0.1uF 16V

603 pkg

1 2

CB599

0.1uF 16V

1 2

CB612

0.1uF 16V

1 2

CB616

0.1uF 16V

1 2

CB597

0.1uF 16V

C434

1 2

0.1uF 16V

C451

1 2

0.1uF 16V

Place 3-4 over Addr\Ctrl

Place 4-6 over data

1 2

CB611

0.1uF 16V

0.1uF 16V

0.1uF 16V

ROOM=PROC_2

VCORE

+80%-20%

+80%-20%

22uF 10V

1 2

VCORE

+80%-20%

22uF 10V

1 2

CB635

CB558

22uF 10V

1 2

C441

+80%-20%

22uF 10V

1 2

CB575

1210 package

+80%-20%

22uF 10V

1 2

+80%-20%

22uF 10V

1 2

CB589

CB594

VCORE

+80%-20%

22uF 10V

1 2

+80%-20%

22uF 10V

1 2

C440

C442

+80%-20%

22uF 10V

1 2

+80%-20%

22uF 10V

1 2

CB654

C443

1 2

CB580

CB579

+80%-20%

0.1uF 16V

1 2

0.1uF 16V

22uF 10V

1 2

+80%-20%

22uF 10V

C450

CB610

CB632

1 2

CB514

1 2

0.1uF 16V

1 2

0.1uF 16V

+80%-20%

22uF 10V

+80%-20%

22uF 10V

C431

1 2

1 2

CB578

1 2

CB655

1 2

CB581

0.1uF 16V

CB605

0.1uF 16V

+80%-20%

22uF 10V

+80%-20%

CB593

1 2

0.1uF 16V

1 2

0.1uF 16V

1 2

CB606

22uF 10V

1 2

CB636

C432

1 2

C433

1 2

+80%-20%

22uF 10V

+80%-20%

22uF 10V

0.1uF 16V

0.1uF 16V

1 2

CB542

1 2

CB504

1 2

820uF

+

VCORE

+80%-20%

22uF 10V

+80%-20%

22uF 10V

C394

1 2

CB596

1 2

4V-20%

820uF

4V-20%

820uF

+80%-20%

CB634

+

21

+

21

10V-10%

SUB*_83008

10V-10%

22uF 10V

+80%-20%

22uF 10V

4V-20%

C438

C395

SUB*_83008

1uF

1uF

1 2

1 2

820uF

4V-20%

820uF

VCORE

1 2

CB518

805 pkg

VCORE

1 2

CB506

+80%-20%

CB637

CB600

1 2

+

1 2

+

10V-10%

1uF

10V-10%

1uF

SUB*_83008

22uF 10V

+80%-20%

22uF 10V

4V-20%

4V-20%

1 2

CB614

1 2

C454

+80%-20%

CB617

CB653

820uF

820uF

10V-10%

SUB*_83008

10V-10%

+80%-20%

C460

C397

SUB*_83008

1 2

1 2

4V-20%

C416

+

21

4V-20%

C396

+

21

SUB*_83008

10V-10%

1 2

1 2

1 2

CB511

1 2

CB516

1uF

10V-10%

C430

1uF

SUB*_83008

+80%-20%

+80%-20%

CB548

1uF

LM_X04--83008 sub for p/n consolidation

1uF

22uF 10V

22uF 10V

1 2

820uF

+

1 2

820uF

+

10V-10%

1 2

CB574

SUB*_83008

SUB*_83008

10V-10%

1 2

C429

22uF 10V

1 2

CB512

22uF 10V

1 2

CB502

C468

C479

SUB*_83008

1uF

1uF

+80%-20%

+80%-20%

4V-20%

820uF

+

10V-10%

1 2

C453

10V-10%

1 2

CB571

SUB*_83008

22uF 10V

1 2

CB595

22uF 10V

1 2

C498

21

1 2

1uF

1uF

CB513

SUB*_83008

1 2

CB508

+80%-20%

+80%-20%

CB568

4V-20%

820uF

+

4V-20%

820uF

+

SUB*_83008

10V-10%

1uF

SUB*_83008

10V-10%

1uF

22uF 10V

1 2

CB628

22uF 10V

1 2

CB501

1 2

C489

1 2

C467

1 2

CB645

1 2

CB507

SUB*_83008

+80%-20%

4V-20%

820uF

10V-10%

10V-10%

1 2

1uF

SUB*_83008

1 2

1uF

22uF 10V

1 2

CB541

C481

+

21

10V-10%

C427

SUB*_83008

10V-10%

CB629

+80%-20%

SUB*_83008

1 2

1uF

1uF

C428

1 2

CB528

22uF 10V

1 2

CB519

+80%-20%

22uF 10V

1 2

10V-10%

10V-10%

CB494

1 2

1uF

1 2

1uF

+80%-20%

22uF 10V

+80%-20%

22uF 10V

CB573

SUB*_83008

CB572

SUB*_83008

1 2

CB551

1 2

CB650

ROOM=PROC_1

ROOM=PROC_2

ROOM=PROC_1

ROOM=PROC_2

+80%-20%

22uF 10V

1 2

CB582

ROOM=PROC_1

+80%-20%