Page 1

5

MSI

MS-9157 REV 1.0

4

3

2

1

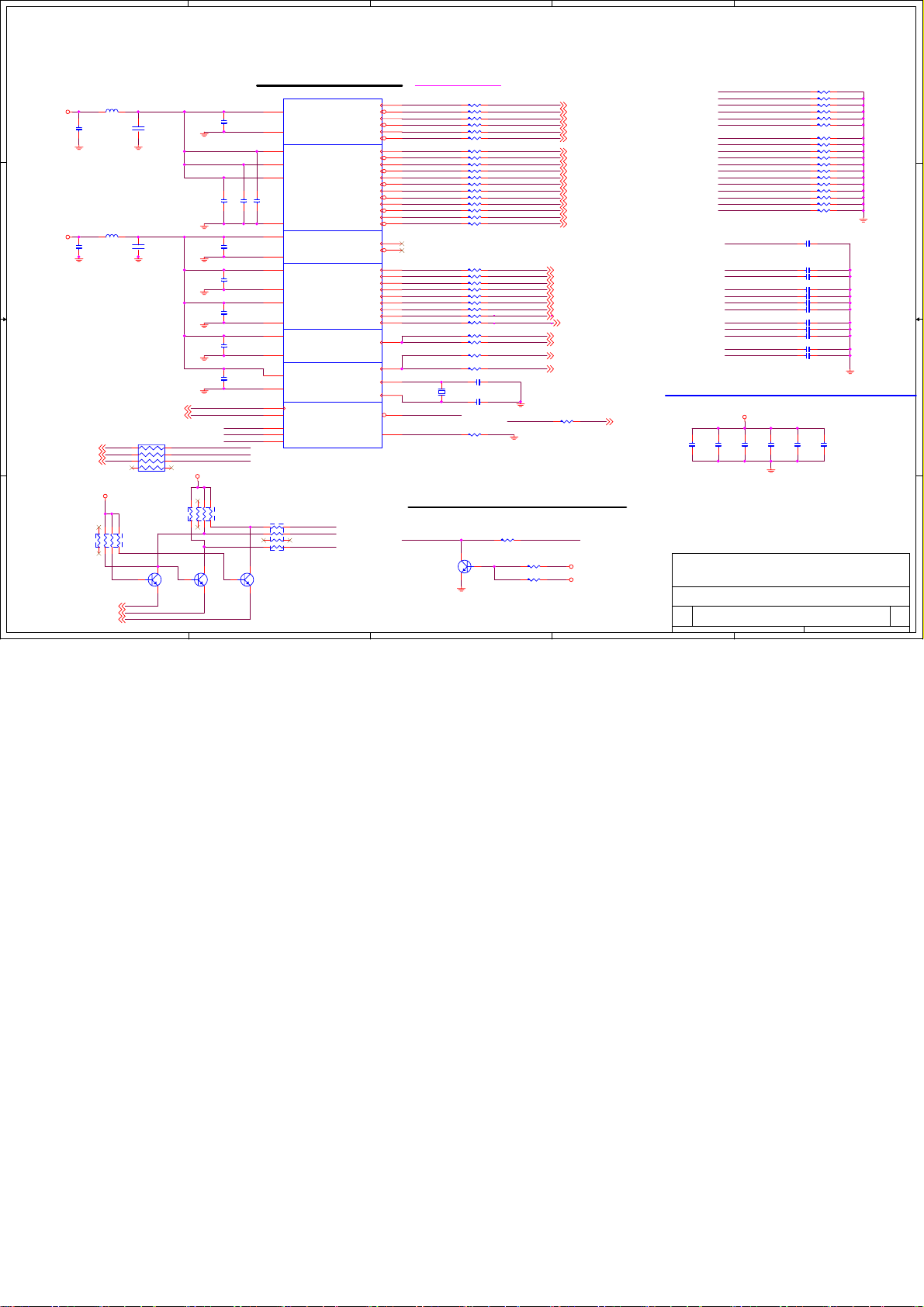

Alderwood + ICH6R Schematics

D D

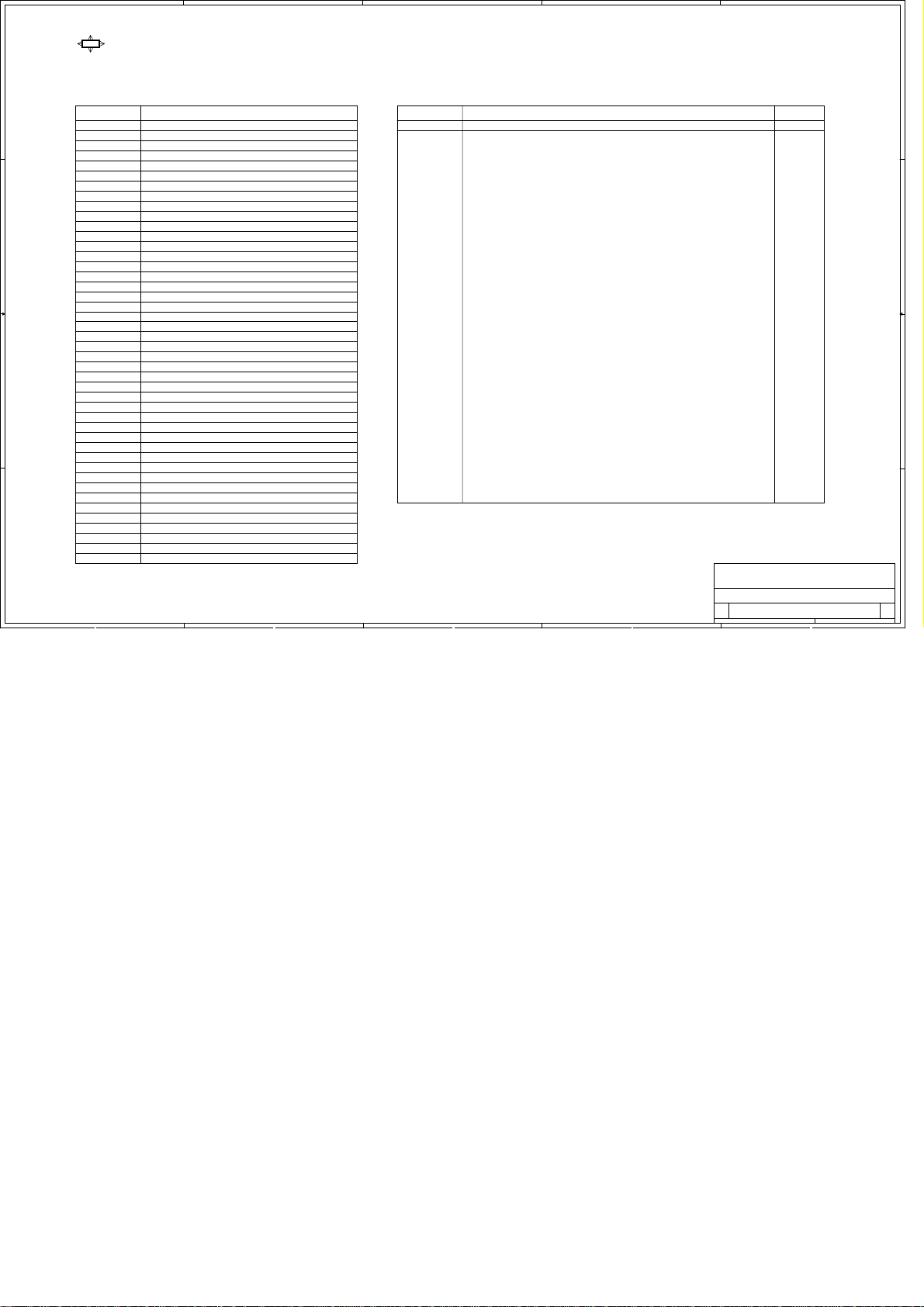

Table of Contents

Page

01

02

03

04

05

06

07

08

09

10

11

C C

B B

A A

12

13

14

15

16

17

18

19

20

21

22

23

24 ICH6 - POWER

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

5

Title

Cover / Table of Contents

System Block Diagram

Power Deliver y Bl o ck Di a g ram

System Clock Block Diagram

System Reset Block Diagr a m

System SMB Block Diagram

DDRII Routing Block Diagram

Inter rupt Block Diagram

Hardwar Monit or Block Digaram

CK410 - CY28410

Intel LGA775 Signal Block

Intel LGA775 Power

Intel LGA775 GND

Alderwood CPU/PCI Signal

Alderwood Memory Signal

Alderwood Misc/Power Signal

Alderwood Power/Gnd

DDR II DIMM 1/2

DDR II DIMM 3/4

DDR II VTT/ICH6 DECOUPLING

PCI -EX PRESS X16-PO RT

ICH6 - PCI, DMI, CPU, IRQ

ICH6 - L PC, ATA, USB, GPIO

PCI Slot1/2

PCI Slot3/4

VIA 6307_1394

82541GLAN

CODEC AD1981B/ALC202

FWH/PS2 Connectors

USB2.0/SATA Connectors

LPC I/O PC87366

Hardware Mo n i to r B MC6 D1 0 1

CPU/SYSTEM FAN

DUMPSWITCH

VRM 10. 1 Intersi l 6561 4PHase

VRM 10.1 Decoupling

DDR2 Power

System P ower Control

PCI Reset & XDP

TPM/SM B U S I S OLATION

BTX&FRONT PANEL

MSIC

GPIO

4

Revision History

Revision

0A - (xx/xx/xx)

History

Start to make up NEC 9157 Schematics - Baggiochen

3

Page

Micro-Star Int'l Co ., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Cover / T ab l e o f C o n t ents

Size Doc u men t Numbe r Re v

MS-9157

2

Date: Sheet of

1

0BCustom

145Wednesday, June 09, 2004

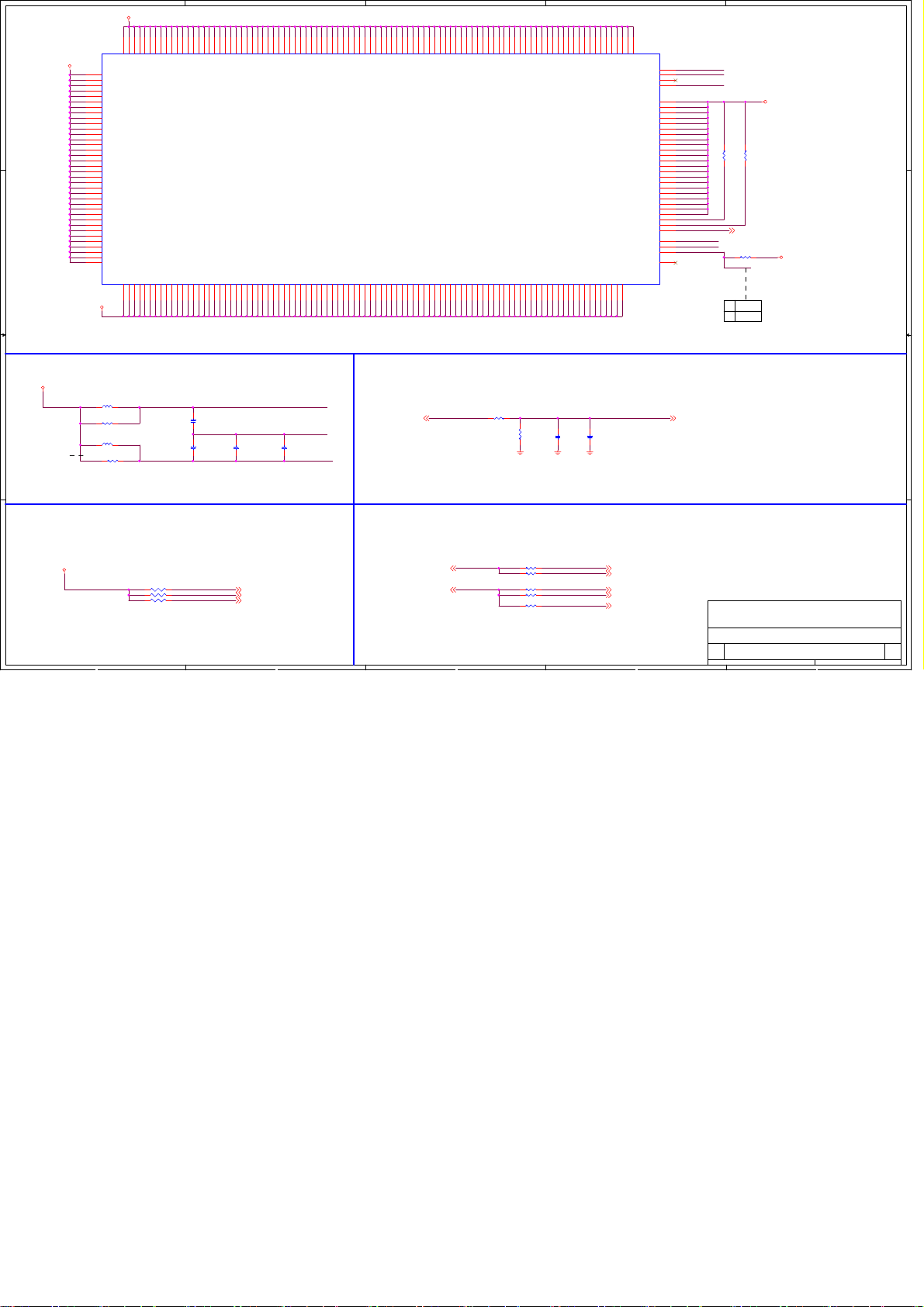

Page 2

5

4

3

2

1

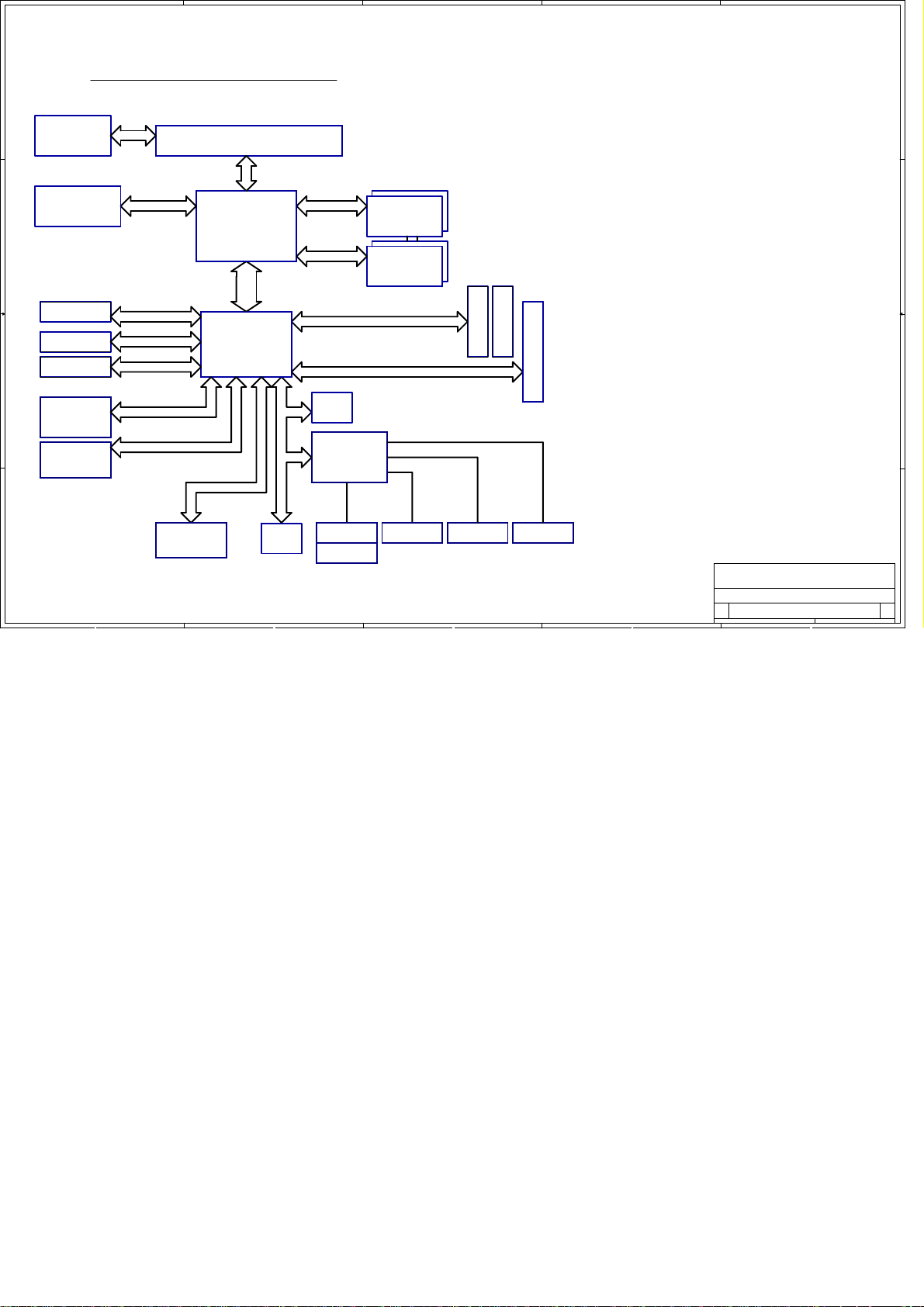

FireBird

D D

External

Graph ics Card

Connector

C C

ATA Primary

SATA 0~3

USB2.0 Port 0~7

B B

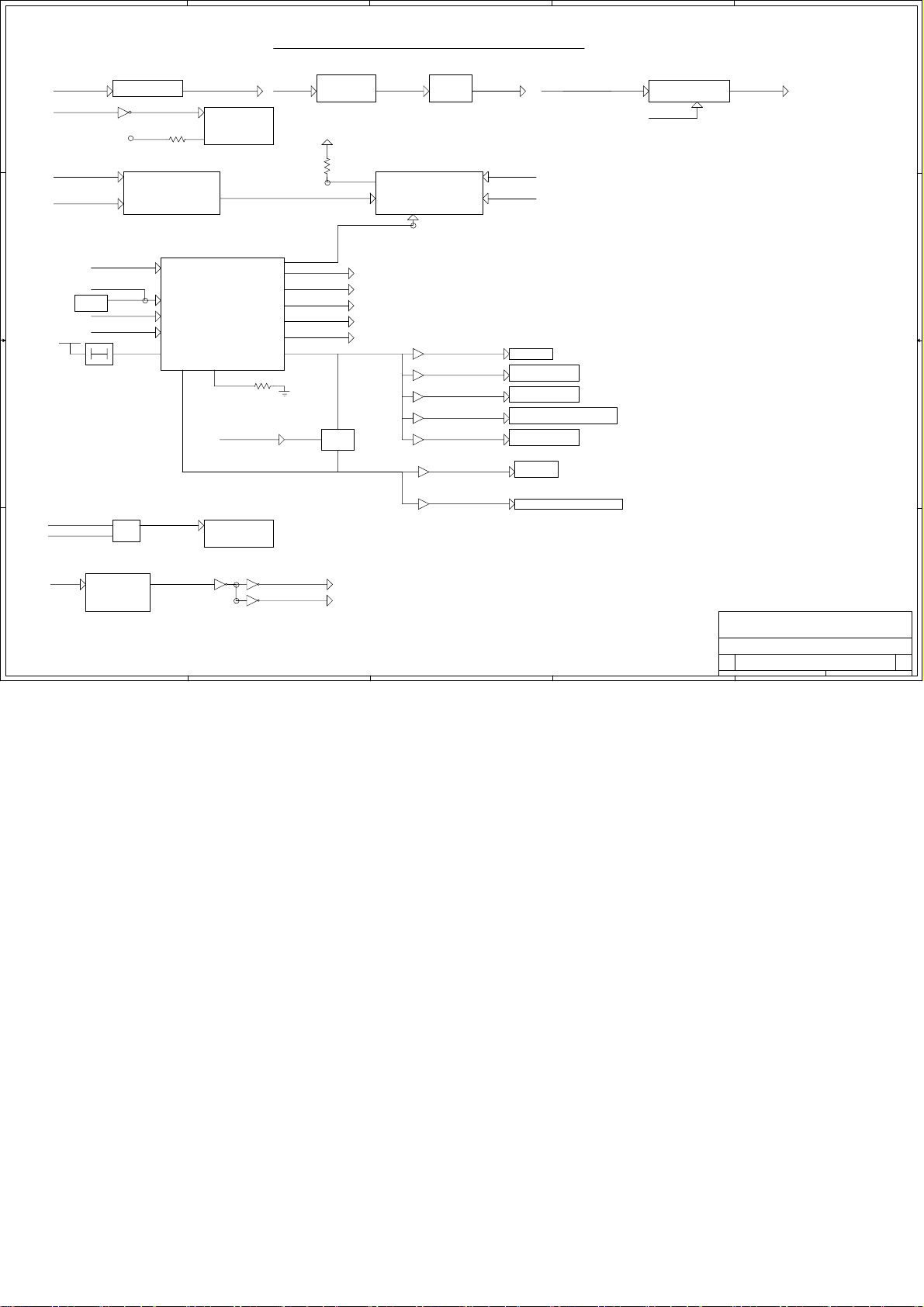

MS-9157 SYSTEM BLOCK DIAGRAM

VRM 10.1

Intersil 6561B

4-Phase PWM

ADI1981B/

ALC202A

AC'97 Code c

GIGA LAN

82541GI

PCI Express X16

BW = 8GB/s

Ultra DMA 66/100

SATA

USB 2.0

AC'97 Link

12.288MHz@1.536MB/s

PCI BUS

Intel LGA-775

Prescott/Tejas

800/533MHz

Alderwood

(MCH)

ICH6

PSB

DMI Bus

DDR2 Channel A

64bit DDR2

400/533MHz

DDR2 Channel B

TPM

LPC Bus

PCI BUS

LPC SIO

NS

PC87366

DDR2 DIMM x2

Modules

DDR2 DIMM x2

Modules

PCI BUS

PCI EXPRESS X1

PCI Slot 3/4

PCI Slot 1/2

Preliminary Spec

* Intel Alderwood / ICH6R Chipset

* Supporting Tejas/Prescott LGA-775 CPUs

* 6 Layer BTX Form F actor (10.5"X10.4")

* 4 DDR 2 unbuffer ed ECC DIMMs (2 Channel)

* PCI Express X16 for Graphic + PCIe X1 Slot

* USB 2. 0 (Rear x2, Front x1)

* 2 PCI slots + 1 Mini PCI slot

* AD1981B AC97 codec

* Serial ATA (4 channel) + RAID 0, 1

* IEEE 1394 Ti chip on-board (Rear x1, Front x1)

* Gigab i t L A N B C M 5721 (Support ASF 2.0)

PCI Express X1

VIA 6307

A A

5

1394

FWH

4

PS2 - KB

PS2 - MS

Floppy

Parallel Port

3

Serial Port

Micro-Star Int'l Co ., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System B l o ck D i agram

Size Doc u men t Numbe r Re v

MS-9157

2

Date: Sheet of

1

0BCustom

245Wednesday, June 09, 2004

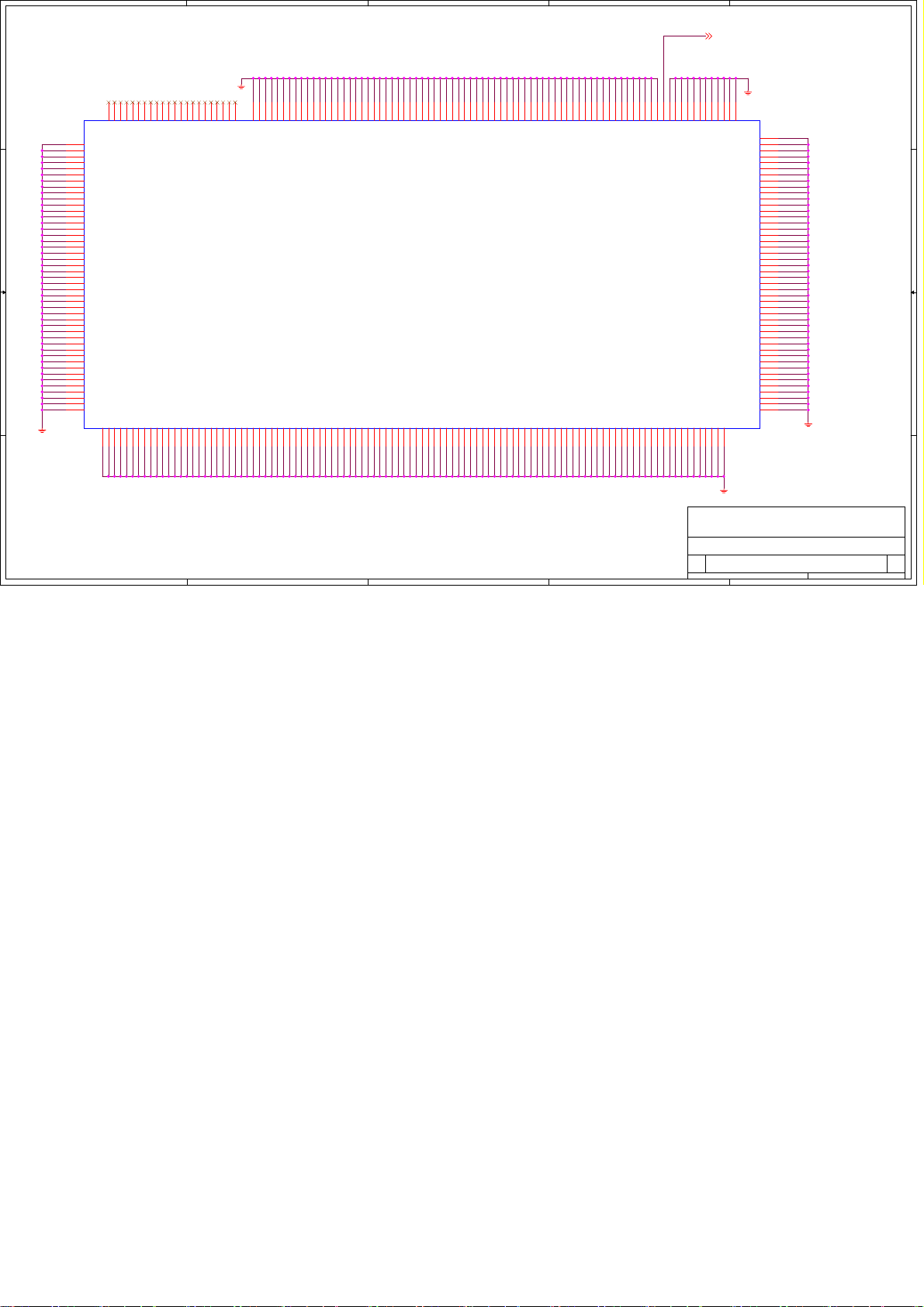

Page 3

5

4

3

2

1

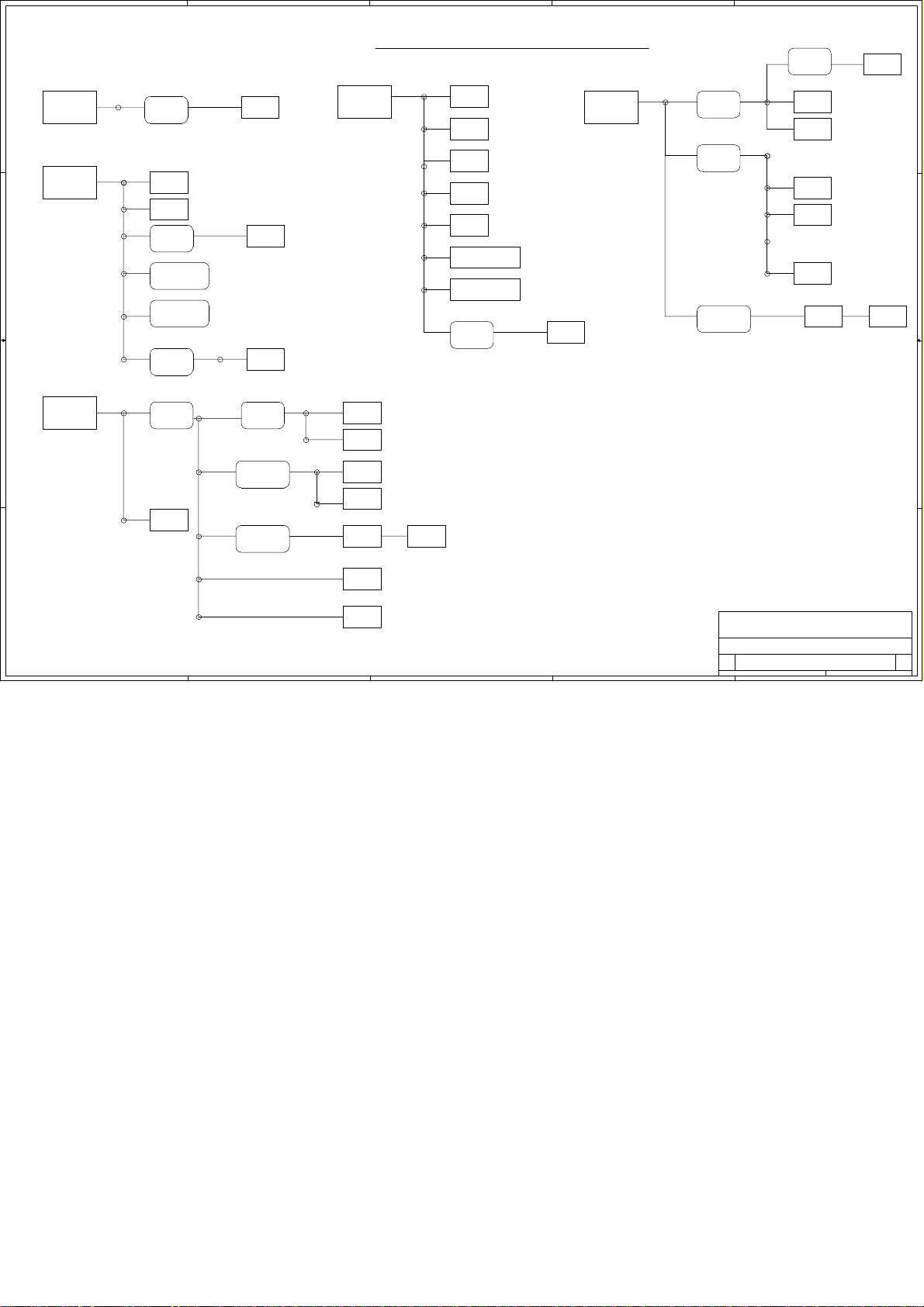

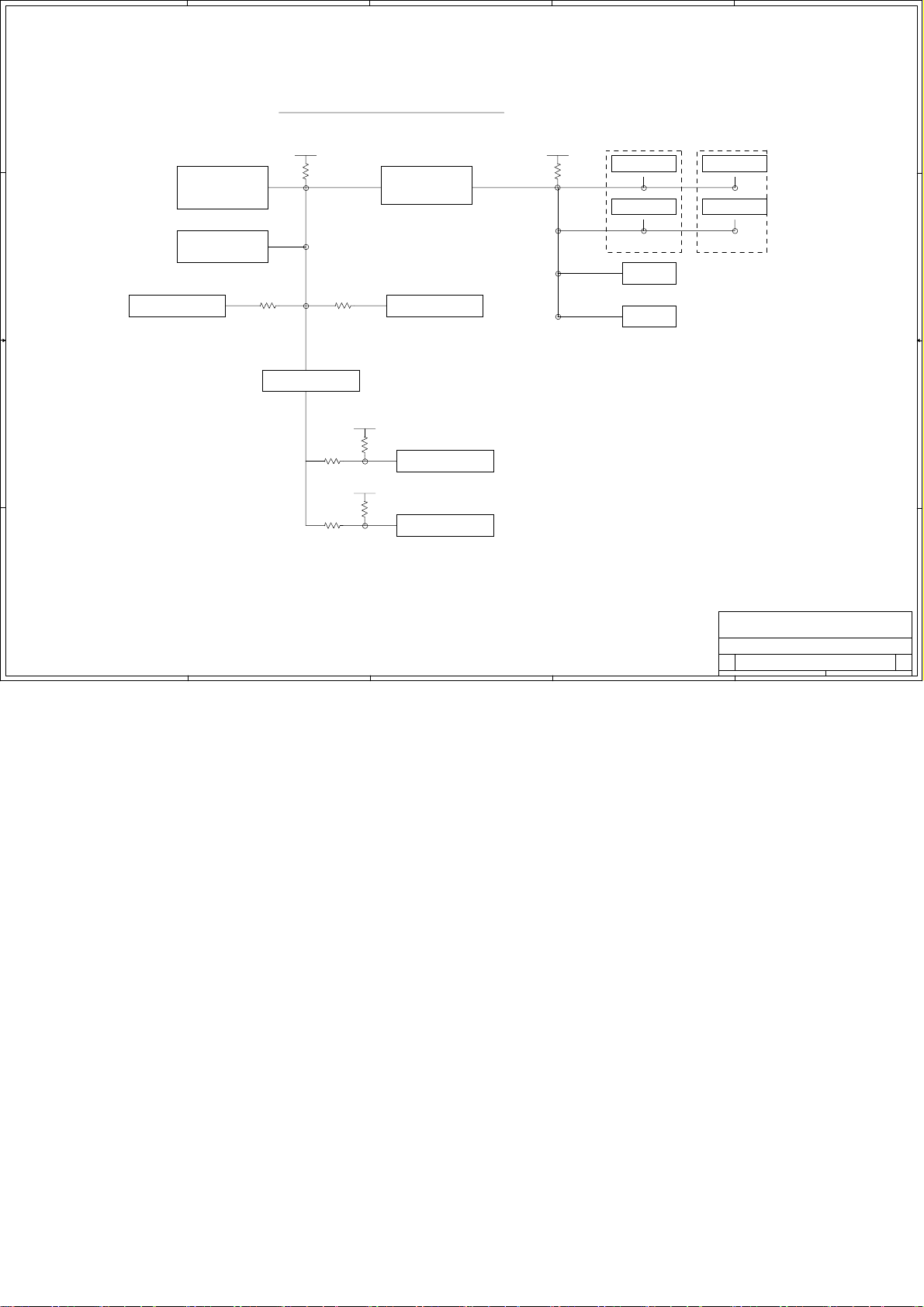

MS-9157 POWER DELIEVERY DIAGRAM

VCC_DDR2

Switch

Keyboard

& Mouse

ICH6

ADT7463*2

PCI[0:3]

82541

GLAN

440mA

3mA

DIMM*4

EEPROM(1M)

93C46

198mA

D D

C C

P12V_CPU

14.875A

+12V

19.7095A

(1.2*95)/(12*0.8)=11.875

14.875A

VRD10.1 CPU

Switch Reg

7A

Fan*4

5.8A

PCI[0:2]

9.5mA+?

P5V_AUD

Linear Reg

5.5A

PCI Express X16

0.5A

PCI Express X1

2A

PWR1394

Power Isolation

119A

AD1981B

J1394CON1

VCC3

9.442A+PCI?A

0.56A

CK410

0.107A

FWH

0.18A

ICH6

95.4mA

1394

7.6A

PCI[0:3]

3A

PCI Express X16

3A

PCI Express X1

FSB_VTT CPU

Linear Reg

250mA

5VSB

1.525A+PCI?A

5A2.5A

5VDUAL USB*8

Switch

1.25A

3VSB

U114

29.5mA

3VDUAL

40mA

(Note 3)

12mA

388mA

6mA

1.5A

(Note 4)

44mA

VCC5

B B

A A

21.067A+PCI?A

21.067A

5VDUAL

Switch

5A

PCI[0:3]

5

2.8012A

363mA

8.8425A

VCC_DDR2

Switch

V_1P5_CORE

3VDUAL

1A

8A

1.65A

MCH

18A

DIMMx4

6.61A

MCH

ICH6

0.86A

3mA

440mA

82541

GLAN

EEPROM(1M)

93C46

KEYBOARD/MOUSE

USBX8

4

3

2

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Power Delivery Block Diagram

Size Document Number R e v

MS-9157

Date: Sheet of

345Wednesday, June 09, 2004

1

0BCustom

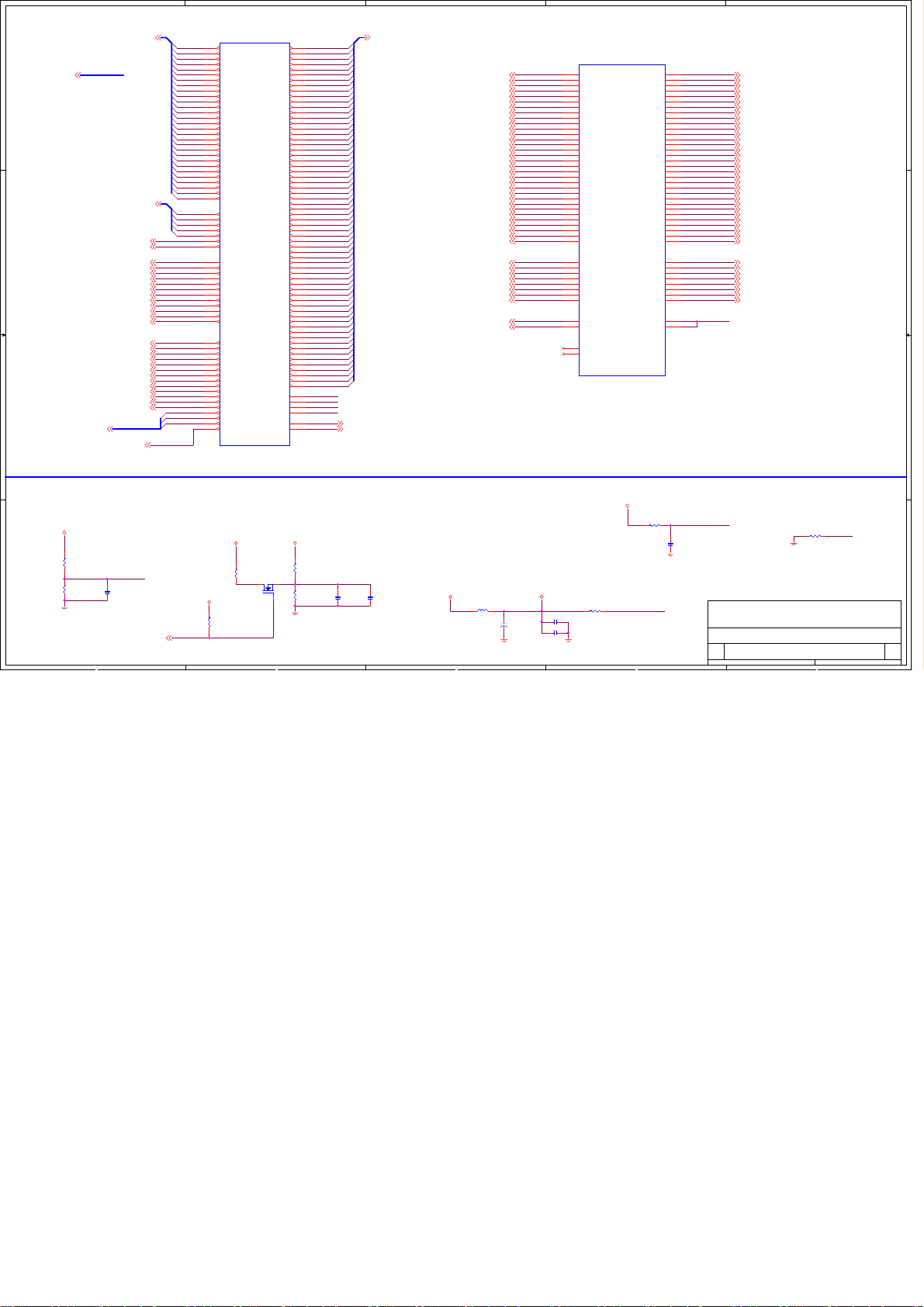

Page 4

5

4

3

2

1

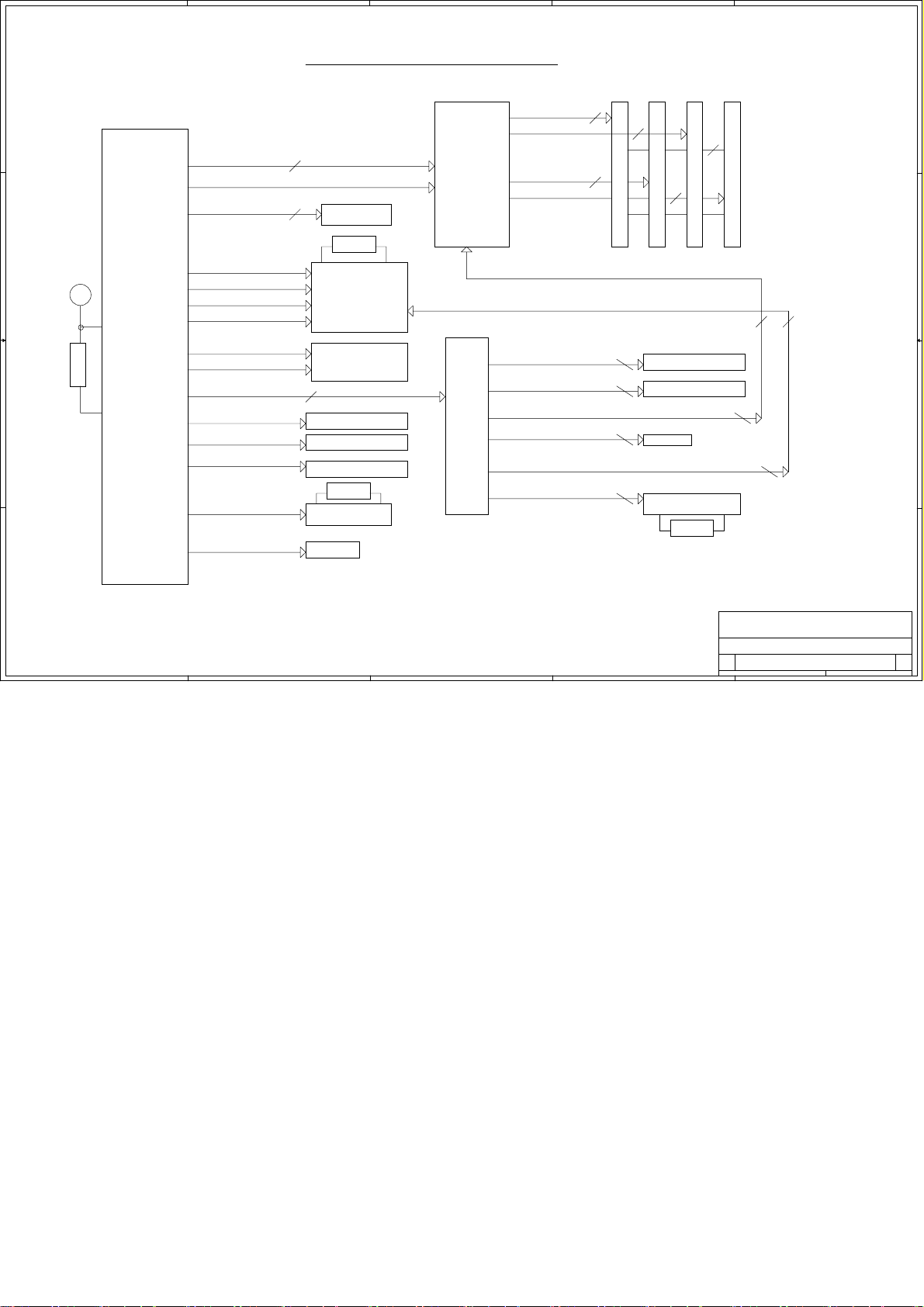

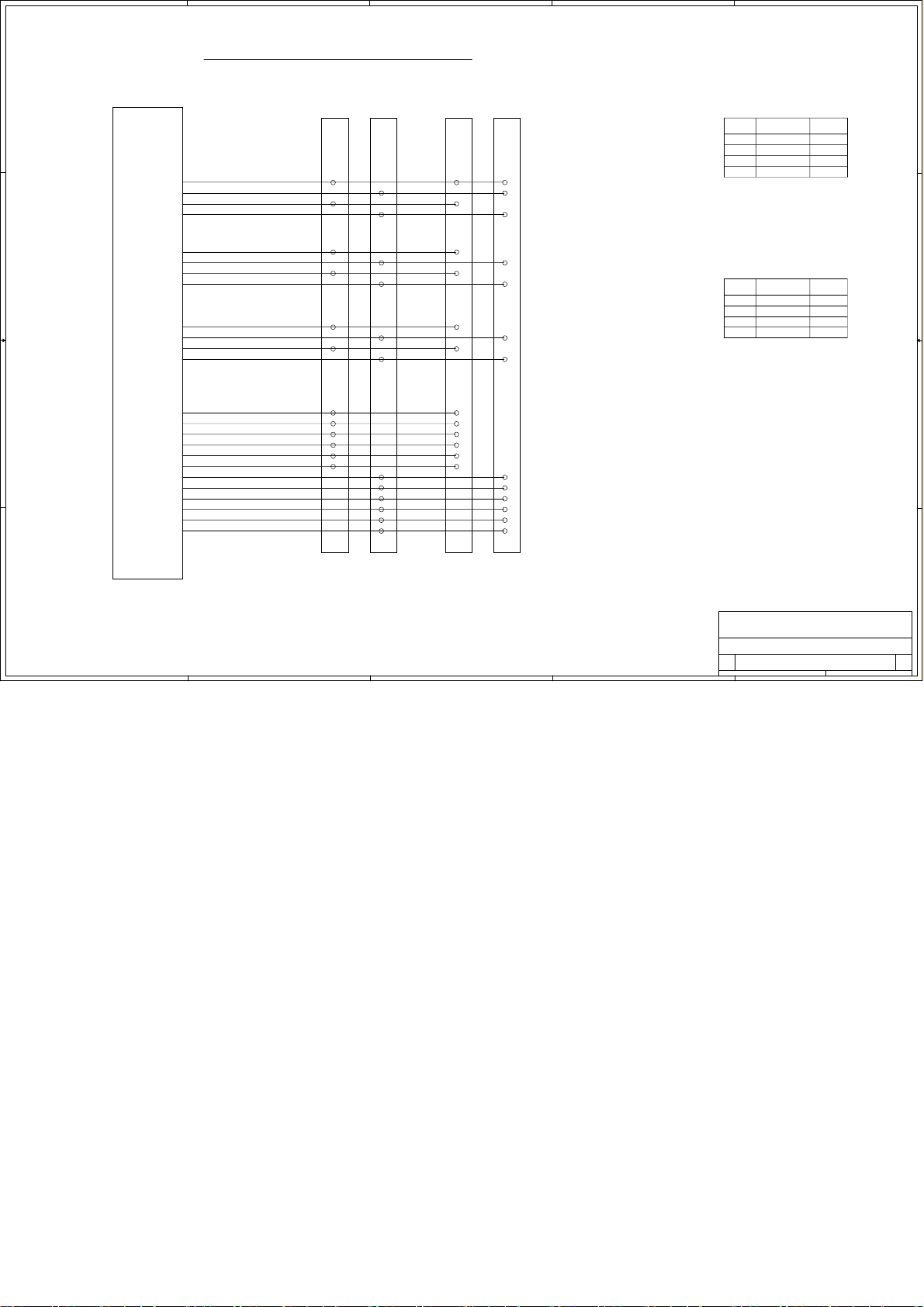

MS-9157 CLOCK BLOCK DIAGRAM

D D

DDR2A_CMDCLK_A0_P/N

DDR2A_CMDCLK_A1_P/N

MCH_BCLK_P/N ( 200MHZ)

CPU0

MCH_100MHZ _CLKP /N

CPU1

ITP_BCLK_P/N (200MHZ)

CPU0

C C

SMA

CONNECTOR

14.318MHZCrystal

B B

3V66_3

USB_48

PCI2

REF0

DOT_48

PCI3

SRC

PCIF0

PCIF1

PCI0

PCIF2

PCI2

ICH_DMI_100MHZ_CLKP/N

ICH_USB_48MHZ_CLK

ICH_33MHZ_CLK

ICH_14MHZ_CLK

SIO_48MHZ_CLK

SIO_33MHZ_CLK

SRC_100MHZ_CLK_P/N

PCI_S LOT0_33MHZ_CLK

PCI_S LOT1_33MHZ_CLK

GLAN_ 33MHZ _CLK

1394_33MHZ_CLK

FWH_33MHZ_CLK

2

2

2

PCI 32/33 ( SLOT #0/ 1 )

PCI 32/33 ( SLOT # 2/3 )

GIGA LAN

24.576MHZ

Crystal

IEEE 1394

FWH

ITP_XDP

32.768KHZ

Crystal

ICH6

SIO

DDR2B_CMDCLK_B0_P/N

MCH

DDR2B_CMDCLK_B1_P/N

SRC1

SRC1#

SRC2

SRC2#

SRC3

SRC3#

SRC4

SRC4#

SRC5

SRC5#

SRC6

SRC6#

EXP_SLOT1_100MHZ_CLK_P/N

EXP_SLOT1_100MHZ_CLK_P/N

MCH_SRC_100MHZ_CL K_P /N

ICHSATA_SRC_100MHZ _CLK_P /N

ICH_SRC_100MHZ_CLK_P/N

LAN_SRC_100MHZ_CLK_P/N

2

2

2

2

DDR II DIMM # A1

DDR II DIMM # A2

DDR II DIMM # B1

2

DDR II DIMM # B2

PCI EXPRESS X16 SLOT # 1

PCI EXPRESS X1 SLOT # 1

SATA

BCM5721

25MHZ

Crystal

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System Clock Block Diagram

Size Document Number R e v

MS-9157

5

4

3

2

Date: Sheet of

445Wednesday, June 09, 2004

1

0BCustom

Page 5

5

4

3

2

1

MS-9157 SYSTEM RESET BLOCK D IAGRAM

D D

CPU BSEL[0:2] VTT_PWRGD

BSEL c om p arator

circuit

VTT_GD

ENABLE

1.2V Reg

PWRGD

VTT_PWRGD

VTT_PWRGD VTT_PWRGD_NCK409B_PWR_GD_N

VCC3_CLK

PWROK_N

C C

ICH_PWRBTN_N

FP_RESET_N

ASR SLP_S5_N

CPU_VRD_PWR_GD

SYS_PWR_GD_3_3V

3.3V STBY

RSM_RST_N

PWRGD

RSTIN_NPCIRST_MCH_N

4.7K-ohm

ALDERWOOD

PWRBTN_N

SYS_RESET_N

VRMPWRGD

PWROK

RSMRST_N

CPURST_N

PLTRST_ICH6_N

B B

PWRDWN_N

ICH6

LAN_RST_N

RSM_RST_N

PWR_OK

CK410

INI T_N

SLP_S3_N

SLP_S4_N SLP_S4_N

SLP_S5_N

Sus_STAT_N

CPU_PWR_GD

PCIRST_N

10K

3.3V

SB_CPU_INIT_N

SLP_S3_N

SUS_STAT_N

CPU_PWR_GD

AND

LOGIC

VTTEN

RESET_N

Voltage

Translation

Logic

Prescott or Tejas

(LGA775 CPU)

INIT_N

IDE_RST_N

PCIRST_SIO_FWH_N

PCIRST_1394_N

PCIRST_SLOT_N

VIDPWRGD

PWRGOOD

PLTRST_MCH_N

VID_GD

VID_PWRGD

CPU_PWR_GD

IDE

RST_N

FWH

RST_N

1394

RST_N PCI 3 2 ( S LO T 1&2& Mi ni P CI )

RST_NPCIRS T_GLAN_N

GLAN

MCH

CPU_VRD_PWR_GD

VTT_PWRGD

CPU0 VRD

OUTEN

CPU0_VID[5:0]PWR_GD

PLTRST_EXP_SLOT_N PCI EXPRE SS (SLOT # 1)

GPIO_LAN_DIS_N LAN_ENABLE

RSMRST_N

AND

LOGIC

LAN_DIS_N

BCM5721

A A

PS_ON_N PWR_OK PWR_OKPSON_N

Power S upply

5

PS_PWR_GD

BTX_PDG_N

4

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System Reset Block Diagram

Size Document Number R e v

MS-9157

3

2

Date: Sheet of

545Wednesday, June 09, 2004

1

0BCustom

Page 6

5

4

3

2

1

D D

ICH6

INTEL

C C

82541GI

MS-9157 SMBus Block Diagram

3.3V STBY

R

ICH_SMB*

SMBus

ISOATATION

3.3V

R

DDR CHA

DIMM A1

* Slave Address = 0XA0

DIMM A2

* Slave Address = 0XA2

DDR CHB

DIMM B1

* Slave Address = 0XA4

DIMM B2

* Slave Address = 0XA6

CK410

PCI-Express X16 Slot

R

0-OHM

(EMPTY)

R

0-OHM

(EMPTY)

PCI-Express X1 Slot

HM ADT7463

SMBUS ISOLATE

R

0-OHM

(EMPTY)

R

0-OHM

(EMPTY)

VCC5

VCC5

R

5.1K

PCI 32 / 33 Slot

( SLOT # 0/1 )

R

5.1K

PCI 32 / 33 Slot

( SLOT # 2/3 )

B B

A A

Dynamic Bus Addressing fo r I/ O Sl ots

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System SMBus Block Diagram

Size Document Number R e v

MS-9157

5

4

3

2

Date: Sheet of

645Wednesday, June 09, 2004

1

0BCustom

Page 7

5

4

3

2

1

MS-9157 DDRII Routing Block Diagram

D D

DIMMA

CLKP0

CLKN0

CLKP1

CLKN1

CLKP2

CLKN2

CS0

CS2

CKE0

CKE2

ODT0

ODT2

CS1

CS3

CKE1

CKE3

ODT1

ODT3

CLKP3

CLKN3

CLKP4

CLKN4

CLKP5

CLKN5

CS0

CS1

CS2

CS3

C C

B B

ODT0

ODT1

ODT2

ODT3

CKE0

CKE1

CKE2

CKE3

CLKP0

CLKN0

CLKP1

CLKN1

CLKP2

CLKN2

CLKP3

CLKN3

CLKP4

CLKN4

CLKP5

CLKN5

CLKP0

CLKN0

CLKP1

CLKN1

CLKP2

CLKN2

DIMMB

CS0

CS2

ODT0

ODT2

CKE0

CKE2

CS1

CS3

CKE1

CKE3

ODT1

ODT3

CLKP3

CLKN3

CLKP4

CLKN4

CLKP5

CLKN5

Signal

CS0

CS1

CS2

CS3

Signal

CKE0

CKE1

CKE2

CKE3

Relative to

DIMMA1,2

DIMMB1,2

DIMMA3,4

DIMMB3,4

Relative to

DIMMA1,2

DIMMB1,2

DIMMA3,4

DIMMB3,4

DIMM PN

193,76

193,76

193,76

193,76

DIMM PN

52,171

52,171

52

52

*Separate Channel A and B

for clocks

A A

5

A1

4

A2

B1

B2

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

DDRII Routing Block Diagram

Size Document Number R e v

MS-9157

3

2

Date: Sheet of

745Wednesday, June 09, 2004

1

0BCustom

Page 8

5

4

3

2

1

D D

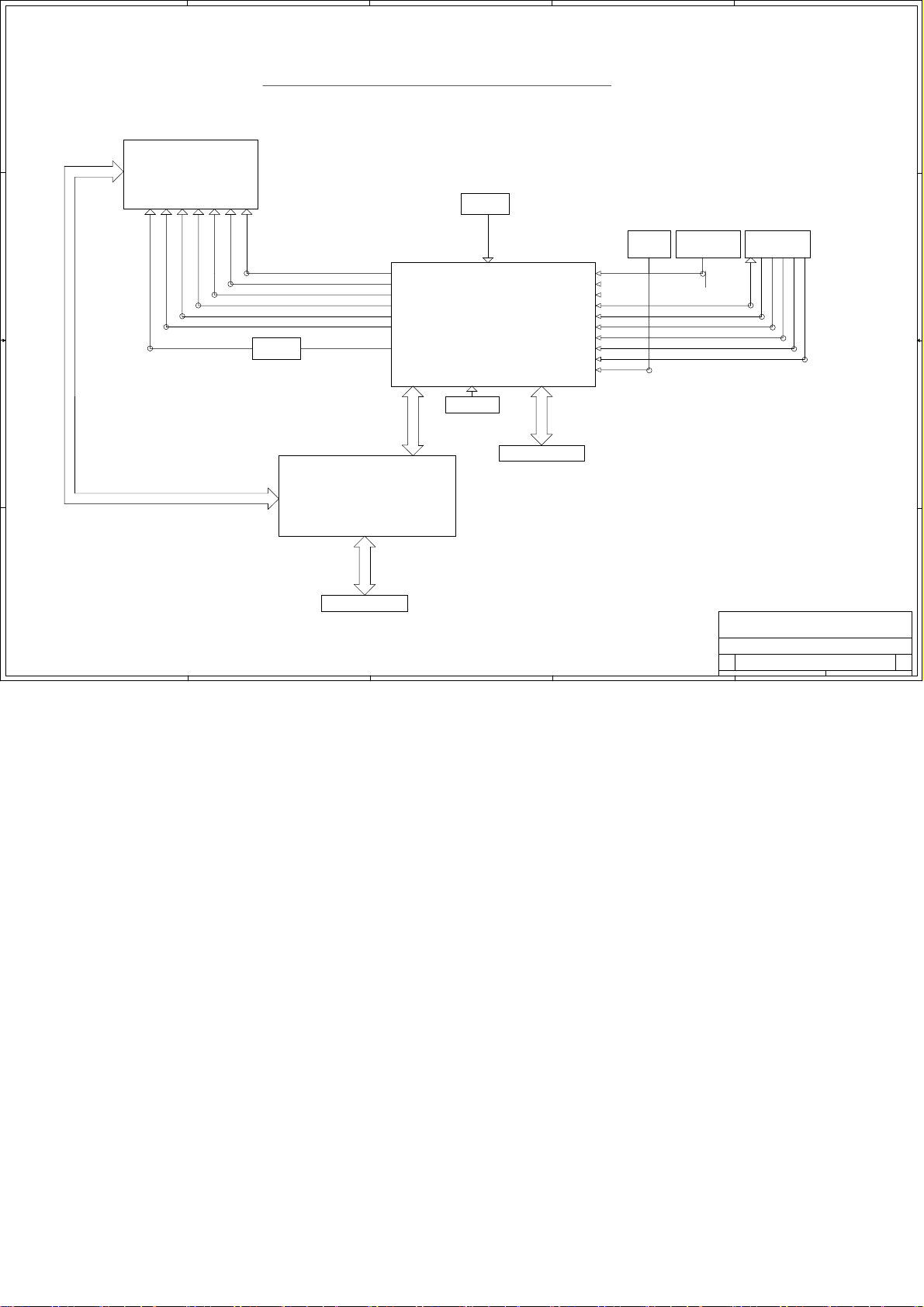

MS-9157 INTERRUPT & ERROR LOGIC DIAGRAM

Prescott

Processor

(LGA775)

INIT_N

NMI

INTR

CPU0_IERR_N

IGNNE_N

SMI_N

FERR_N

SB_CPU_FERR_N

SB_CPU_IGNNE_N

ICH_CPU_SMI_N

SB_CPU_NMI

SB_CPU_INTR

SB_CPU_INIT_N

GTL TO 3.3V

TRANSLATION

LOGIC

SB_CPU0_IERR_N

MCH

ALDERWOOD

MEMORY WRITE

( ICH6 TO

ALDERWOOD)

FERR_N

IGNNE_N

SMI_N

NMI

INTR

INIT_N

GPI7

DMI

SIO

SERIRQ

ICH6

IDE IRQ14

IDE Primary

PIRQF_N

PIRQG_N

PIRQH_N

PB_PERR_N

PB_SERR_N

PIRQA_N

PIRQB_N

PIRQC_N

PIRQD_N

PIRQE_N

PCI Express

PCI EXPRESS X 1 SLOT

IDSEL = AD22

REQ/GNT # 0

PIRQG_N

PIRQG_N

PIRQH_N

PB_PERR_N

PB_SERR_N

PIRQA_N

PIRQB_N

PIRQC_N

PIRQD_N

PIRQE_N

1394A

IDSEL = AD23

REQ/GNT # 1

82541GI

GLAN

IDSEL = AD24~27

REQ/GNT # 2~5

PCI-32 SLOT 0~3

D

B

C

A

IERR_N

C C

F

S

B

B B

MEMORY WRITE ( ALDERWOOD to PROCESSOR )

A A

5

4

PCI Express

PCI EXPRESS X 16 SLOT

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Interrupt Block Diagram

Size Document Number R e v

MS-9157

3

2

Date: Sheet of

845Wednesday, June 09, 2004

1

0BCustom

Page 9

5

4

3

2

1

MS-9157 HARDWARE MONITOR DIAGRAM

D D

ADT7463 (U25)

+3.3V +3.3V

SYSTEM_THERMAL_DIODE

C C

B B

RTD ( 1 )

10K 10K

PWM1

PWM2

PWM3

TACH1

TACH2

TACH3

+3.3V

10K

FET

AMP

FET

AMP

FET

AMP

CPU FAN

SYSTEM FAN1

SYSTEM FAN2

FAN1

FAN2

FAN3

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Hardware Monitor Block Diagram

Size Document Number R e v

MS-9157

5

4

3

2

Date: Sheet of

945Wednesday, June 09, 2004

1

0BCustom

Page 10

5

4

3

2

1

D D

FB6 80/0805-3A

VCC3

CB37

0.1u/6

FB4 80/0805-3A

C C

B B

A A

VCC3

H_FSBSEL1<11,12,16>

H_FSBSEL0<11,12,16>

H_FSBSEL2<11,12,16>

RN45

X_1K/4/8P4R

H_FSBSEL0<11,12,16>

H_FSBSEL1<11,12,16>

H_FSBSEL2<11,12,16>

CB36

0.1u/6

V_FSB_VTT

5

123456

1 2

3 4

5 6

7 8

78

X_2N3904S

10u/8

10u/8

RN42

0R

Q90

C152

C126

C171

0.1u/6

VCC3VA

SMB_CLK<18,19,33,41>

SMB_DATA<18,19,33,41>

SEL1

SEL0

SEL2

VCC3

123456

78

Q91

X_2N3904S

Clock Ge n erat or - C Y28410

42

45

21

28

34

C175

0.1u/6

29

37

38

1

2

7

6

11

13

48

51

46

47

18

16

53

CYPRESS CY28410

RN44

7 8

5 6

3 4

1 2

X_1K/4/8P4R

4

CPU_VDD

CPU_GND

SRC_VDD

SRC_VDD

SRC_VDD

SRC_GND

VDDA

VSSA

PCI_VDD

PCI_GND

PCI_VDD

PCI_GND

48_VDD

48_GND

REF_VDD

REF_GND

SCLK

SDATA

FSA

FSB/TEST_MODE

FSC/TEST_SEL

C155

0.1u/6

C176

0.1u/6

C169

0.1u/6

C137

0.1u/6

C151

0.1u/6

C124

0.1u/6

C123

0.1u/6

SEL0

SEL1

SEL2

RN43

X_10K/4/8P4R

Q92

X_2N3904S

CPU2_ITP/SRC7

CPU2_ITP#/SRC7#

SRC4_SATA

SRC4_SATA#

DOT96#

PCIF0/ITP_EN

USB_48M

VTT_PWRGD#/PD

SEL2

SEL0

SEL1

CPU0

CPU0#

CPU1

CPU1#

SRC1

SRC1#

SRC2

SRC2#

SRC3

SRC3#

SRC5

SRC5#

SRC6

SRC6#

DOT96

PCIF1

PCIF2

PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

IREF

REF

Trace l ength l ess than 0.5inchs

MCHCLK

44

43

41

40

36

35

19

20

22

23

24

25

26

27

31

30

33

32

14

15

8

9

10

54

55

56

3

4

5

12

52

50

X1

49

X2

17

39

R164 33/6

MCHCLK#

R178 33/6

R187 33/6

CPUCLK

CPUCLK#

R195 33/6

R207 33/6

ITPCLK

ITPCLK#

R212 33/6

R194 33/6

CK_PE_SRC1

CK_PE_SRC1#

R201 33/6

R211 33/6

CK_PE_SRC2

CK_PE_SRC2#

R216 33/6

CK_PE_SRC3

R223 33/6

R230 33/6

CK_PE_SRC3#

CK_PE_SRC4

R249 33/6

R256 33/6

CK_PE_SRC4#

CK_PE_SRC5

R237 33/6

CK_PE_SRC5#

R253 33/6

R224 33/6

CK_PE_SRC6

CK_PE_SRC6#

R227 33/6

PCI clock follow routing direction

PCICLK1

R152 33/6

PCICLK2

R163 33/6

R172 X_33/6

1394CLK

PCICLK3

R149 33/6

R142 33/6

ICHPCLK

FWHPCLK

R135 15/6

SIOPCLK

R147 33/6

R534 33/6

PCICLK4

PCICLK5 GLAN_33MHZ_CLK

R535 33/6

SIO48 CK_48M_ICH_SIO

R183 33/6

USB48

R181 33/6

AC9714 AC97_14

R704 33/6

R155 33/6

PLL_XI

Y2

14M-32pf-HC49S-D

PLL_XO

CLK_GD#

IREF

R202 475/6/ST

CK_H_MCH

CK_H_ MCH#

CK_H_CPU

CK_H_CPU#

CK_H_ITP

CK_H_ITP#

CK_PE_100M_16PORT

CK_PE_100M_16PORT#

CK_PE_100M_1PORT

CK_PE_100M_1PORT#

CK_PE_100M_MCH

CK_PE_100M_MCH#

CK_ICHSATA

CK_ICHSATA#

CK_PE_100M_ICH

CK_PE_100M_ICH#

CK_PE_100M_TEST

CK_PE_100M_TEST#

PCI_CLK1

PCI_CLK2

1394_33MHZ_CLK

PCI_CLK3

ICH_PCLK

FWH_PCLK

SIO_PCLK

PCI_CLK4

CK_48M_ICH_USB

CK_14M_ICH

51p/6C130

51p/6C129

FWHPCLK

Clock Generator VTT Power Down Bl ock

R184 10K/6

2N3904S

Q22

3

R232 10K /6

R754 X_10K

CK_H_MCH <14>

CK_H_MCH# <14>

CK_H_ CPU <11>

CK_H_ CPU# <11>

CK_H_ITP <40>

CK_H_ITP# <40>

CK_PE_100M_16PORT <21>

CK_PE_100M_16PORT# <21>

CK_PE_100M_1PORT <21>

CK_PE_100M_1PORT# <21>

CK_PE_100M_MCH <14>

CK_PE_100M_MCH# <14>

CK_ICHSATA <23>

CK_ICHSATA# <23>

CK_PE_100M_ICH <22>

CK_PE_100M_ICH# <22>

CK_PE_100M_TEST <22>

CK_PE_100M_TEST# <22>

PCI_CL K1 <25>

PCI_CL K2 <25>

1394_33MHZ_CLK <27>

PCI_CL K3 <26>

ICH_PCLK <22>

FWH_PCLK <30>

SIO_PCLK <32>

PCI_CL K4 <26>

GLAN_33MHZ_CLK <28>

CK_48M_ICH_SIO <32>

CK_48M_ICH_USB <23>

AC97_14 <29>

CK_14M_ICH <23>

R1708 15/6

VCC3VACLK_GD#

V_FSB_VTT

VCORE

TPM_CLK <41>

2

CK_H_CPU

CK_H_CPU#

CK_H_MCH

CK_H_ MCH#

CK_H_ITP

CK_H_ITP#

CK_PE_100M_16PORT

CK_PE_100M_16PORT#

CK_PE_100M_1PORT

CK_PE_100M_1PORT#

CK_PE_100M_MCH

CK_PE_100M_MCH#

CK_ICHSATA

CK_ICHSATA#

CK_PE_100M_ICH

CK_PE_100M_ICH#

CK_PE_100M_TEST#

CK_PE_100M_TEST

GLAN_33MHZ_CLK

PCI_CLK3

PCI_CLK4

1394_33MHZ_CLK

PCI_CLK1

PCI_CLK2

TPM_CLK

ICH_PCLK

FWH_PCLK

SIO_PCLK

CK_48M_ICH_USB

CK_48M_ICH_SIO

R188 49.9/6/ST

R196 49.9/6/STU16

R165 49.9/6/ST

R179 49.9/6/ST

R208 49.9/6/ST

R213 49.9/6/ST

R193 49.9/6/ST

R200 49.9/6/ST

R210 49.9/6/ST

R215 49.9/6/ST

R222 49.9/6/ST

R229 49.9/6/ST

R248 49.9/6/ST

R255 49.9/6/ST

R238 49.9/6/ST

R254 49.9/6/ST

R225 49.9/6/ST

R228 49.9/6/ST

X_10pC1484

X_10pC567

X_10pC568

X_10pC146

X_10pC134

X_10pC140

X_10pC132

X_10pC128

X_10pC125

X_10pC131

X_10pC150

X_10pC156

EMC HF filter capacitors, located close to PLL

VCC3

Please close to U1 as possible

C139

C143

C194

X_0.1u

Micro-Star Int'l Co., Ltd.

No.69, L i - D e S t, J ung-He City, Taipei Hsien, Taiwan. ht tp://www.m si.com.tw

Title

CK410-CY28410

Size Documen t Num ber Re v

MS-9157

Dat e: Sheet

X_0.1u

C119

X_0.1u

C190

X_0.1u

X_0.1u

1

C122

X_0.1u

10 45Wednesday, June 09, 2004

of

0BCustom

Page 11

5

D D

H_DBI#[0..3]

H_DBI#[0..3]<14>

H_ED RDY#<14>

H_IERR#<12,32>

H_FERR#<22>

H_STPCLK#<22>

H_INIT#<22>

H_DBSY#<14>

H_DRDY#<14>

H_TRDY#<14>

H_ADS#<14>

R1849 X_0/4

62/4

C303 X_0.1u

VTT_OUT_RIGHT

H_D#[0..63]<14>

H_LOCK#<14>

H_BNR#<14>

H_HIT#<14>

H_HITM#<14>

H_BPRI#<14>

H_DEFER#<14>

H_TDI<40>

H_TDO<40>

H_TMS<40>

H_TRST#<40>

H_TCK<40>

H_THRMDA<33>

H_THRMDC<33>

TRMTRIP#<22>

H_PROCHOT#<12>

H_IGNNE#<22>

ICH_H_SMI#<22>

H_A20M#<22>

R365 X_1K

LL_ID0<36>

H_FSBSEL0<10,12,16>

H_FSBSEL1<10,12,16>

H_FSBSEL2<10,12,16>

H_PWRGD<12,22>

H_CPURST#<12,14,40>

C C

H_SLP#<22>

V_FSB_VTT

R1850

B B

A A

H_D#[0..63]

5

H_A#[3..31]<14>

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

TP46

TP51

TP35

TP45

TP55

TP38

TP47

TP22

TP33

TP18

TP9

CPU_BOOT

LL_ID0

TP48

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_D#[0..63]

TP54

TP50

TP49

TP52

A8

G11

D19

C20

F2

AB2

AB3

R3

M3

AD3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

AD1

AF1

AC1

AG1

AE1

AL1

AK1

M2

AE8

AL2

N2

P2

K3

L2

AH2

N5

AE6

C9

G10

D16

A20

Y1

V2

AA2

G29

H30

G30

N1

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

H_A#[3..31]

U22A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

AJ6

AJ5

A35#

D53#

D52#

D51#

D50#

D49#

D48#

B15

A14

C14

C15

D17

D20

G22

H_D#49

H_D#48

H_D#51

H_D#52

H_D#53

H_D#47

H_D#50

4

CPU SIGNAL BLOCK

H_A#24

H_A#28

H_A#31

H_A#29

H_A#25

H_A#30

H_A#26

H_A#27

AH5

AH4

AG5

AG4

AG6

AF4

AF5

AB4

AC5

AB5

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

F21

F20

F18

F17

E22

E21

E19

E18

D22

G21

H_D#44

H_D#46

H_D#41

H_D#40

H_D#45

H_D#39

H_D#38

H_D#37

H_D#42

H_D#43

4

3

R364 X_0R

H_A#4

H_A#10

H_A#7

H_A#8

H_A#6

H_A#5

H_A#3

H_A#17

H_A#18

H_A#16

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D31#

D30#

D29#

F15

G15

G14

H_D#30

H_D#31

H_D#29

H_A#9

H_A#11

H_A#12

H_A#15

H_A#14

H_A#13

AC2

L5

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

DBR#

D28#

D27#

D26#

D25#

D24#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

F14

F12

F11

E13

D13

G13

H_D#24

H_D#23

H_D#27

H_D#26

H_D#28

H_D#25

D14#

E10

D10

D11

C12

H_D#19

H_D#14

H_D#22

H_D#20

H_D#15

H_D#17

H_D#16

H_D#21

H_D#18

H_A#19

H_A#20

H_A#21

H_A#23

H_A#22

AA5

AD6

AA4

A24#

A23#

A22#

A21#

A20#Y4A19#Y6A18#W6A17#

D37#

D36#

D35#

D34#

D33#

D32#

E16

E15

G17

G18

G16

H_D#32

H_D#35

H_D#33

H_D#36

H_D#34

FP_ RST# <23>

ITP_ CLKOUT# <40>

ITP _CLKOUT <40>

TP58

AN3

AN5

AN6

AN4

AJ3

AK3

RSVD

RSVD

ITP_CLK1

ITP_CLK0

VSS_SENSE

VCC_SENSE

D13#

D12#D8D11#

D10#

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

B12

B10

A11

A10

C11

H_D#8

H_D#10

H_D#5

H_D#4

H_D#7

H_D#13

H_D#6

H_D#9

H_D#12

H_D#11

VID[0..5]

VID4

VID3

VID2

VID1

VID0

VID5

AM5

AL4

AK4

AL6

AM3

AL5

AM2

RSVD

VID5#

VID4#

VID3#

VID2#

VID1#

VID0#

H1

GTLREF

H_BPM#5

AG3

BPM5#

H_BPM#4

AF2

BPM4#

H_BPM#3

AG2

BPM3#

H_BPM#2

AD2

BPM2#

H_BPM#1

AJ1

BPM1#

H_BPM#0

AJ2

BPM0#

H_PCREQ#

G5

PCREQ#

H_REQ#4

J6

REQ4#

H_REQ#3

K6

REQ3#

H_REQ#2

M6

REQ2#

H_REQ#1

J5

REQ1#

H_REQ#0

K4

REQ0#

H_TESTHI12

W2

TESTHI12

H_TESTHI11

P1

TESTHI11

H_TESTHI10

H5

TESTHI10

H_TESTHI9

G4

TESTHI9

H_TESTHI8

G3

TESTHI8

F24

TESTHI7

G24

TESTHI6

G26

TESTHI5

G27

TESTHI4

G25

TESTHI3

F25

TESTHI2

W3

TESTHI1

F26

TESTHI0

AK6

RSVD

G6

RSVD

G28

BCLK1#

F28

BCLK0#

H_RS#2

A3

RS2#

H_RS#1

F5

RS1#

H_RS#0

B3

RS0#

U3

AP1#

U2

AP0#

F3

BR0#

H_COMP3

R1

COMP3

H_COMP2

G2

COMP2

H_COMP1

T1

COMP1

H_COMP0

A13

COMP0

J17

DP3#

H16

DP2#

H15

DP1#

J16

DP0#

AD5

ADSTB1#

R6

ADSTB0#

C17

DSTBP3#

G19

DSTBP2#

E12

DSTBP1#

B9

DSTBP0#

A16

DSTBN3#

G20

DSTBN2#

G12

DSTBN1#

C8

DSTBN0#

L1

LINT1/NMI

K1

LINT0/INTR

TEJAS

B4

H_D#0

H_D#1

H_D#2

H_D#3

VCC_SENSE

CPU_GTLREF

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

RSVD_AK6

RSVD_G6

R377 0/4

R379 0/4

R1847 X_0/4

R1848 X_0/4

VID[0..5] <32,36>

H_BPM#[0..5]

H_P CREQ# <14>

H_R EQ#[ 0..4] <14>

R361 62/4

R358 62/4

R352 62/4

R355 62/4

R353 62/4

R276 62/4

R362 62/4

R522 X_62R

R350 X_62R

CK_ H_CP U# <10>

CK _H_C PU <10>

H_R S#[0 ..2] <14>

TP43

TP44

H_BR#0 <12,14>

R359 100ST

R349 100ST

R360 60.4RST

R305 60.4RST

TP23

TP19

TP24

TP21

H_A DSTB#1 <14>

H_A DSTB#0 <14>

H_D STBP#3 <14>

H_D STBP#2 <14>

H_D STBP#1 <14>

H_D STBP#0 <14>

H_D STBN# 3 <14>

H_D STBN# 2 <14>

H_D STBN# 1 <14>

H_D STBN# 0 <14>

H_ NMI <22>

H_ INTR <22>

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

CPU_ GTL REF <12>

V_FSB_VTT

R533 49 .9 /6 /ST

R532 49 .9 /6 /ST

R531 49 .9 /6 /ST

R530 49 .9 /6 /ST

R528 49 .9 /6 /ST

R526 49 .9 /6 /ST

PLACE BPM TERMINATION NEAR CPU

3

2

VCC_VRM_SENSE

VSS_VRM_SENSEVSS_SENSE

H_B PM#[0 ..5] <40>

VTT_O UT_LEFT

VTT_O UT_LEFT

VTT_O UT_LEFT

Place r esistor outside socket cavity if no room for

vaiable resistor, then don't do this

VTT_OUT_RIGHT <12,40>

C302

X_0.1u

VTT_OUT_RIGHT

2

VCC_ VRM _SENSE <36>

VSS_VRM_SENSE <36>

VTT_O UT_LEFT <12>

1

VTT_OUT_RIGHT

RN41

680/6/8 P4 R

VID3

1

VID1

VID2

VID4

VID0

VID5

Title

Size Doc u men t Numbe r Re v

Date: Sheet of

2

3

4

5

6

7

8

R751 680/4

R752 680/4

V_FSB_VTT

C202

R1787

10u/06

C203

100ST

G

10u/06

VCC3

GTL_DET<13,14>

Micro-Star Int'l Co ., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

VCC3

C205

C204

0.1u/6

0.1u/6

H_TESTHI0

R1788

C1567

0.1u/6

61.9ST

R1846

249ST

DS

Q136

2N7002S

H_TESTHI0

Intel LGA775 Si gn al B lo ck

MS-9157

11 45Wednesday, June 09, 2004

1

0BCustom

Page 12

5

VCORE

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

U22B

VCORE

D D

C C

VCC

VCC

AF19

VCC

AF18

VCC

AF15

VCC

AF14

VCC

AF12

VCC

AF11

VCC

AE9

VCC

AE23

VCC

AE22

VCC

AE21

VCC

AE19

VCC

AE18

VCC

AE15

VCC

AE14

VCC

AE12

VCC

AE11

VCC

AD8

VCC

AD30

VCC

AD29

VCC

AD28

VCC

AD27

VCC

AD26

VCC

AD25

VCC

AD24

VCC

AD23

VCC

AC8

VCC

AC30

VCC

AC29

VCC

AC28

VCC

AC27

VCC

AC26

VCC

AC25

VCC

AC24

VCC

AC23

VCC

AB8

VCC

AA8

VCC

VCC

VCC

Y8

Y30

VCORE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y23

Y24

Y25

Y26

Y27

Y28

Y29

W30

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

VCC

VCC

VCC

W23

W24

W25

W26

W27

W28

W29

4

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

VCC

VCC

VCC

VCC

U28

U29

U30

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCT8VCC

VCC

VCC

VCC

VCC

U23

U24

U25

U26

U27

T23

T24

T25

T26

T27

T28

T29

T30

N23

N24

N25

N26

N27

N28

N29

N30

M26

M27

M28

M29

M30

3

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

K30

M23

M24

M25

J11

J12

J13

J14

J15

J18

J19

J20

J21

AM9

AN11

AN12

AN14

AN15

AN18

VCC

VCC

VCC

VCC

VCC

VCC

RSVD/VTT_PKGSENSE

VCC

VCC

VCC

VCC

VCC

VCC

J10

AN8

AN9

AN26

AN29

AN30

AN19

AN21

VCC

VCC

VCC-IOPLL

VTTPWRGD

VCC

AN25

2

AN22

VCC

VTT_OUT

VTT_OUT

VTT_SEL

TEJAS

VCCA

VSSA

RSVD

1

H_VCCA

A23

H_VSSA

B23

D23

H_VCCIOPLL

C23

A25

VTT

A26

VTT

A27

VTT

A28

VTT

A29

VTT

A30

VTT

B25

VTT

B26

VTT

B27

VTT

B28

VTT

B29

VTT

B30

VTT

C25

VTT

C26

VTT

C27

VTT

C28

VTT

C29

VTT

C30

VTT

D25

VTT

D26

VTT

D27

VTT

D28

VTT

VCCFUSEPRG

D29

VTT

VIDFUSEPRG

D30

VTT

AM6

VTT_ OUT_RIGHT

AA1

VTT_OUT_ LEFT

J1

F27

F29

VTT_PWR

V_FSB _VTT

R269

0/4

VTT_PWR <38>

R264 X_1K

VTT_SEL

TEJ/PSC

0

1

RSVD

V_FSB _VTT

R267

0/4

VCC3

V_FSB _VTT

B B

DC voltage drop should

be less than 70mV.

A A

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

It support DC current if 100m A.

V_FSB _VTT

L11 10uH-0805-100mA

R277 X_0R

L12 10uH-0805-100mA

R291 X_0R

V_FSB _VTT

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB _VTT

R261 470/6

R260 470/6

R262 470/6

5

C223

1u/6

EC17

22u/06

H_FSBSEL0

H_FSBSEL1

H_FSBSEL2

EC18

10u/06

H_FSBSEL0 <10,11,16>

H_FSBSEL1 <10,11,16>

H_FSBSEL2 <10,11,16>

4

H_VCCIOPLL

H_VSSA

C224

X_1u

H_VCCA

49.9 OHMS OVER 100 OHMS RESISTORS

VTT_O UT_RIGHT<11,40>

VTT_ OUT_RIGHT CPU_GTLREF

VTT_OUT_ LEFT<11>

VTT_OUT_ LEFT<11>

R354

100ST

VTT_OUT_ LEFT

VTT_OUT_ LEFT

3

R356

C299

210RST/4

1u/6

Place at CPU end of routing

R270 62/4

R375 X_120R

R357 100/6

R347 62/4

R367 62/4

H_CPURST#

H_PROCHOT#

H_PWRGD

H_BR#0

C301

220p/4

H_C PURST# <11, 14,40>

H_P ROCHOT# <11>

H_PW RGD <11,22>

H_BR# 0 <11,14>

H_IE RR# <11,32>

CPU_ GTLREF <11>

GTLREF VOLTAGE SHOULD BE

0.67*VTT = 0.8V

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Intel LGA775 Power

Size Doc um ent Num ber Re v

MS-9157

2

Date: Sheet of

12 45Wednesday, June 09, 2004

1

0BCustom

Page 13

5

4

3

2

1

GTL_DET <11, 14>

D D

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

V30

V29

V28

V27

V26

V25

V24

VSS

VSSV3VSS

VSS

AH20

V23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH7

AJ10

AJ13

AH23

AH24

AC4

AE3

AE4

D14

E23

E24

F23

U22C

RSVD

RSVD

RSVD

A12

A15

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

C C

B B

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

AA3

AA6

AA7

AB1

AB7

AC3

AC6

AC7

AD4

AD7

AE2

RSVDD1RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE5

AE7

AF10

AF13

AE29

AE30

B13

RSVD

RSVD

RSVDE5RSVDE6RSVDE7RSVD

RSVDF6RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

RSVDH2RSVDJ2RSVDJ3RSVDN4RSVDP5RSVDT2RSVDV1RSVDW1RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF3

AF6

AF7

AF29

AF30

AG10

AG13

Y3

VSS

VSS

VSS

AG16

AG17

AG20

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH1

AG7

AH10

AH13

AG23

AG24

VSS

AH16

AH17

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

R30

R29

R28

R27

R26

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AJ28

AJ29

AK2

AJ30

AK10

AK13

AK16

AK17

AK5

AK7

AK20

AK23

AL10

AK24

AK27

AK28

AK29

AK30

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL13

AL16

AL17

AL20

AL23

AL24

L30

L29

L28

VSSL3VSS

VSS

VSS

VSS

VSS

VSS

AL3

AL7

AM1

AL27

AL28

K2

L27

L26

L25

L24

L23

K5

VSS

VSS

VSS

VSS

VSS

VSS

VSSK7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM10

AM13

AM16

AM17

AM20

AM23

AM24

AM27

AM28

H28

H29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

GTL_DET

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSB1VSS

AN1

AN2

AM4

AM7

AN10

AN13

AN16

AN7

AN17

AN20

AN23

AN24

AN27

AN28

H14

VSS

H13

VSS

H12

VSS

H11

VSS

H10

VSS

G1

VSS

F7

VSS

F4

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

E8

VSS

E29

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E2

VSS

E17

VSS

E14

VSS

E11

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

C7

VSS

C4

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

B8

VSS

B5

VSS

B24

VSS

B20

VSS

B17

VSS

VSS

TEJAS

B11

B14

A A

5

4

3

2

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City , Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Intel LGA775 GND

Size Document Number Re v

MS-9157

Date: Sheet

of

13 45Wednesday, June 09, 2004

1

0BCustom

Page 14

5

4

3

2

1

H_A#[3..31]<11>

H_DBI#[0..3]

H_DBI#[0..3]<11>

D D

H_REQ#[0..4]<11>

H_ADSTB#0<11>

C C

B B

H_ADSTB#1<11>

H_DSTBP#0<11>

H_DSTBN#0<11>

H_DBI#0<11>

H_DSTBP#1<11>

H_DSTBN#1<11>

H_DBI#1<11>

H_DSTBP#2<11>

H_DSTBN#2<11>

H_DBI#2<11>

H_DSTBP#3<11>

H_DSTBN#3<11>

H_DBI#3<11>

H_ADS#<11>

H_BNR#<11>

H_BPRI#<11>

H_BR#0<11,12>

H_CPURST#<11,12,40>

H_DBSY#<11>

H_DEFER#<11>

H_DRDY#<11>

H_EDRDY#<11>

H_HIT#<11>

H_HITM#<11>

H_LOCK#<11>

H_PCREQ#<11>

H_RS#[0..2]<11>

H_RS#[0..2]

H_TRDY#<11>

H_ADSTB#0

H_ADSTB#1

H_DSTBP#0

H_DSTBN#0

H_DBI#0

H_DSTBP#1

H_DSTBN#1

H_DBI#1

H_DSTBP#2

H_DSTBN#2

H_DBI#2

H_DSTBP#3

H_DSTBN#3

H_DBI#3

H_ADS#

H_BNR#

H_BPRI#

H_BR#0

H_CPURST#

H_DBSY#

H_DEFER#

H_DRDY#

H_EDRDY#

H_HIT#

H_HITM#

H_LOCK#

H_PCREQ#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H29

K29

J29

G30

G32

K30

L29

M30

L31

L28

J28

K27

K33

M28

R29

L26

N26

M26

N31

P26

N29

P28

R28

N33

T27

T31

U28

T26

T29

F33

E32

H31

G31

F31

J31

N27

E33

E35

E34

H26

F26

J26

J19

F19

K19

B29

C29

B26

M31

M35

E30

R33

G24

L35

J35

M32

P33

L34

N35

L33

E31

K34

P34

J32

N34

ALDERWOOD

U24A

REV=1.0

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

HREQ0

HREQ1

HREQ2

HREQ3

HREQ4

HADSTB0

HADSTB1

HDSTBP0

HDSTBN0

HDINV0

HDSTBP1

HDSTBN1

HDINV1

HDSTBP2

HDSTBN2

HDINV2

HDSTBP3

HDSTBN3

HDINV3

HADS

HBNR

HBPRI

HBREQ0

HCPURST

HDBSY

HDEFER

HDRDY

HEDRDY

HHIT

HHITM

HLOCK

HPCREQ

HRS0

HRS1

HRS2

HTRDY

DCL_CORE_GMCH

ALDERWOOD

CORE

H_D#0

J33

HD0

H_D#1

H33

HD1

H_D#2

J34

HD2

H_D#3

G35

HD3

H_D#4

H35

HD4

H_D#5

G34

HD5

H_D#6

F34

HD6

HSWING

HSCOMP

HRCOMP

HVREF

HCLKP

HCLKN

1 of 8

H_D#7

G33

HD7

H_D#8

D34

HD8

H_D#9

C33

HD9

H_D#10

D33

HD10

H_D#11

B34

HD11

H_D#12

C34

HD12

H_D#13

B33

HD13

H_D#14

C32

HD14

H_D#15

B32

HD15

H_D#16

E28

HD16

H_D#17

C30

HD17

H_D#18

D29

HD18

H_D#19

H28

HD19

H_D#20

G29

HD20

H_D#21

J27

HD21

H_D#22

F28

HD22

H_D#23

F27

HD23

H_D#24

E27

HD24

H_D#25

E25

HD25

H_D#26

G25

HD26

H_D#27

J25

HD27

H_D#28

K25

HD28

H_D#29

L25

HD29

H_D#30

L23

HD30

H_D#31

K23

HD31

H_D#32

J22

HD32

H_D#33

J24

HD33

H_D#34

K22

HD34

H_D#35

J21

HD35

H_D#36

M21

HD36

H_D#37

H23

HD37

H_D#38

M19

HD38

H_D#39

K21

HD39

H_D#40

H20

HD40

H_D#41

H19

HD41

H_D#42

M18

HD42

H_D#43

K18

HD43

H_D#44

K17

HD44

H_D#45

G18

HD45

H_D#46

H18

HD46

H_D#47

F17

HD47

H_D#48

A25

HD48

H_D#49

C27

HD49

H_D#50

C31

HD50

H_D#51

B30

HD51

H_D#52

B31

HD52

H_D#53

A31

HD53

H_D#54

B27

HD54

H_D#55

A29

HD55

H_D#56

C28

HD56

H_D#57

A28

HD57

H_D#58

C25

HD58

H_D#59

C26

HD59

H_D#60

D27

HD60

H_D#61

A27

HD61

H_D#62

E24

HD62

H_D#63

B25

HD63

HXSWING

A23

HXSCOMP

D24

HXRCOMP

B23

MCH_GTLREF

A24

CK_H_MCH

M23

CK_H_MCH#

M22

NB

H_D #[0..63 ] <11>

CK_H _MCH <10>

CK_H_ MCH# <10>

U24B

E11

F11

J11

H11

P10

R10

V10

U10

A11

B11

K13

J13

F9

E9

F7

E7

B3

B4

D5

E5

G6

G5

H8

H7

J6

J5

K8

K7

L6

L5

M8

M7

N6

N5

P7

P8

R6

R5

U5

U6

T9

T8

V7

V8

EXP_PXP0

EXP_RXN0

EXP_PXP1

EXP_RXN1

EXP_PXP2

EXP_RXN2

EXP_PXP3

EXP_RXN3

EXP_PXP4

EXP_RXN4

EXP_PXP5

EXP_RXN5

EXP_PXP6

EXP_RXN6

EXP_PXP7

EXP_RXN7

EXP_PXP8

EXP_RXN8

EXP_PXP9

EXP_RXN9

EXP_PXP10

EXP_RXN10

EXP_PXP11

EXP_RXN11

EXP_PXP12

EXP_RXN12

EXP_PXP13

EXP_RXN13

EXP_PXP14

EXP_RXN14

EXP_PXP15

EXP_RXN15

DMI_PXP0

DMI_PXN0

DMI_PXP1

DMI_PXN1

DMI_PXP2

DMI_PXN2

DMI_PXP3

DMI_PXN3

GCLKP

GCLKN

RSV

RSV

ALDERWOOD

REV=1.0

BOM=CORE

FIN=NB

EXP_TXP0

EXP_TXN0

EXP_TXP1

EXP_TXN1

EXP_TXP2

EXP_TXN2

EXP_TXP3

EXP_TXN3

EXP_TXP4

EXP_TXN4

EXP_TXP5

EXP_TXN5

EXP_TXP6

EXP_TXN6

EXP_TXP7

EXP_TXN7

EXP_TXP8

EXP_TXN8

EXP_TXP9

EXP_TXN9

EXP_TXP10

EXP_TXN10

EXP_TXP11

EXP_TXN11

EXP_TXP12

EXP_TXN12

EXP_TXP13

EXP_TXN13

EXP_TXP14

EXP_TXN14

EXP_TXP15

EXP_TXN15

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

EXP_COMPO

EXP_COMPI

2 of 8

C10

C9

A9

A8

C8

C7

A7

A6

C6

C5

C2

D2

E3

F3

F1

G1

G3

H3

H1

J1

J3

K3

K1

L1

L3

M3

M1

N1

N3

P3

P1

R1

R3

T3

T1

U1

U3

V3

V5

W5

Y10

W10

EXP_A_TXP_0

EXP_A_TXN_0

EXP_A_TXP_1

EXP_A_TXN_1

EXP_A_TXP_2

EXP_A_TXN_2

EXP_A_TXP_3

EXP_A_TXN_3

EXP_A_TXP_4

EXP_A_TXN_4

EXP_A_TXP_5

EXP_A_TXN_5

EXP_A_TXP_6

EXP_A_TXN_6

EXP_A_TXP_7

EXP_A_TXN_7

EXP_A_TXP_8

EXP_A_TXN_8

EXP_A_TXP_9

EXP_A_TXN_9

EXP_A_TXP_10

EXP_A_TXN_10

EXP_A_TXP_11

EXP_A_TXN_11

EXP_A_TXP_12

EXP_A_TXN_12

EXP_A_TXP_13

EXP_A_TXN_13

EXP_A_TXP_14

EXP_A_TXN_14

EXP_A_TXP_15

EXP_A_TXN_15

DMI_MTP_ IRP_0

DMI_MTN_IRN_0

DMI_MTP_ IRP_1

DMI_MTN_IRN_1

DMI_MTP_ IRP_2

DMI_MTN_IRN_2

DMI_MTP_ IRP_3

DMI_MTN_IRN_3

GRCOMP

EXP_A_TXP_0 <21>

EXP_A_TXN_0 <21>

EXP_A_TXP_1 <21>

EXP_A_TXN_1 <21>

EXP_A_TXP_2 <21>

EXP_A_TXN_2 <21>

EXP_A_TXP_3 <21>

EXP_A_TXN_3 <21>

EXP_A_TXP_4 <21>

EXP_A_TXN_4 <21>

EXP_A_TXP_5 <21>

EXP_A_TXN_5 <21>

EXP_A_TXP_6 <21>

EXP_A_TXN_6 <21>

EXP_A_TXP_7 <21>

EXP_A_TXN_7 <21>

EXP_A_TXP_8 <21>

EXP_A_TXN_8 <21>

EXP_A_TXP_9 <21>

EXP_A_TXN_9 <21>

EXP_A_TXP_10 <21>

EXP_A_TXN_10 <21>

EXP_A_TXP_11 <21>

EXP_A_TXN_11 <21>

EXP_A_TXP_12 <21>

EXP_A_TXN_12 <21>

EXP_A_TXP_13 <21>

EXP_A_TXN_13 <21>

EXP_A_TXP_14 <21>

EXP_A_TXN_14 <21>

EXP_A_TXP_15 <21>

EXP_A_TXN_15 <21>

DMI_MTP _ IRP_0 <22>

DMI_ MTN_IRN_0 <22>

DMI_MTP _ IRP_1 <22>

DMI_ MTN_IRN_1 <22>

DMI_MTP _ IRP_2 <22>

DMI_ MTN_IRN_2 <22>

DMI_MTP _ IRP_3 <22>

DMI_ MTN_IRN_3 <22>

EXP_A_RXP_0<21>

EXP_A_RXN_0<21>

EXP_A_RXP_1<21>

EXP_A_RXN_1<21>

EXP_A_RXP_2<21>

EXP_A_RXN_2<21>

EXP_A_RXP_3<21>

EXP_A_RXN_3<21>

EXP_A_RXP_4<21>

EXP_A_RXN_4<21>

EXP_A_RXP_5<21>

EXP_A_RXN_5<21>

EXP_A_RXP_6<21>

EXP_A_RXN_6<21>

EXP_A_RXP_7<21>

EXP_A_RXN_7<21>

EXP_A_RXP_8<21>

EXP_A_RXN_8<21>

EXP_A_RXP_9<21>

EXP_A_RXN_9<21>

EXP_A_RXP_10<21>

EXP_A_RXN_10<21>

EXP_A_RXP_11<21>

EXP_A_RXN_11<21>

EXP_A_RXP_12<21>

EXP_A_RXN_12<21>

EXP_A_RXP_13<21>

EXP_A_RXN_13<21>

EXP_A_RXP_14<21>

EXP_A_RXN_14<21>

EXP_A_RXP_15<21>

EXP_A_RXN_15<21>

DMI_ITP_M RP_0<22>

DMI_ITN_MRN_0<22>

DMI_ITP_M RP_1<22>

DMI_ITN_MRN_1<22>

DMI_ITP_M RP_2<22>

DMI_ITN_MRN_2<22>

DMI_ITP_M RP_3<22>

DMI_ITN_MRN_3<22>

CK_PE _100M_MCH<10>

CK_PE _100M_MCH#<10>

EXP_A_RXP_0

EXP_A_RXN_0

EXP_A_RXP_1

EXP_A_RXN_1

EXP_A_RXP_2

EXP_A_RXN_2

EXP_A_RXP_3

EXP_A_RXN_3

EXP_A_RXP_4

EXP_A_RXN_4

EXP_A_RXP_5

EXP_A_RXN_5

EXP_A_RXP_6

EXP_A_RXN_6

EXP_A_RXP_7

EXP_A_RXN_7

EXP_A_RXP_8

EXP_A_RXN_8

EXP_A_RXP_9

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXN_10

EXP_A_RXP_11

EXP_A_RXN_11

EXP_A_RXP_12

EXP_A_RXN_12

EXP_A_RXP_13

EXP_A_RXN_13

EXP_A_RXP_14

EXP_A_RXN_14

EXP_A_RXP_15

EXP_A_RXN_15

DMI_ITP_M RP_0

DMI_ITN_MRN_0

DMI_ITP_M RP_1

DMI_ITN_MRN_1

DMI_ITP_M RP_2

DMI_ITN_MRN_2

DMI_ITP_M RP_3

DMI_ITN_MRN_3

CK_PE _100M_MCH

CK_PE _100M_MCH#

V_FSB _VTT

V_FSB _VTT

HD_SWING VOLTAGE "10 MIL TRACE , 7 MIL

SPACE" HD_SWING S/B 1/4*VTT +/- 2%

PLACE DIVIDER RESISTOR NEAR VTT

R308

A A

301RST/6

R317

102/4/ST C254

HXSWING

0.01u/6

GTL_DET<11,13>

5

VCORE

+12V

R1786

10K/6

R1785

619RST

Q132

2N7002S

D S

V_FSB _VTT

G

4

R300

100ST

R301

210RST/4

MCH_GTLREF

C237

0.1u/6

C236

X_220p

3

L15 0/12

+

CT16

330u/6.3V

V_1P5 _PCIEXPRESSV_1P5_CORE

C243

C244

R320 24.9RST/6

10u/8

10u/8

R309 60.4RST

GRCOMP

2

HXSCOMP

C248

X_2.2P

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Alderwood CPU/PCI Signal

Size Doc um ent Num ber Re v

MS-9157

Date: Sheet of

R316

20ST/4

1

HXRCOMP

14 45Wednesd ay, June 0 9, 2004

0BCustom

Page 15

5

ALDERWOOD

D D

MAA_A[0..13]<18,20>

WE_A#<18,20>

CAS_A#<18,20>

RAS_A#<18,20>

SBS_A[0..2]<18,20>

SCS_A#[0..3]<18,20>

SCKE_A[0..3]<18,20>

C C

ODT_ A [0..3]<18,20>

P_DDR0_A<18>

N_DDR0_A<18>

P_DDR1_A<18>

N_DDR1_A<18>

P_DDR2_A<18>

N_DDR2_A<18>

P_DDR3_A<18>

N_DDR3_A<18>

P_DDR4_A<18>

N_DDR4_A<18>

P_DDR5_A<18>

N_DDR5_A<18>

SDQS_A<18>

SDQS_A#<18>

B B

A A

TP53

TP61

TP59

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

WE_A#

CAS_A#

RAS_A#

SBS_A0

SBS_A1

SBS_A2

SCS_A#0

SCS_A#1

SCS_A#2

SCS_A#3

SCKE_A0

SCKE_A1

SCKE_A2

SCKE_A3

ODT_A0

ODT_A1

ODT_A2

ODT_A3

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

P_DDR3_A

N_DDR3_A

P_DDR4_A

N_DDR4_A

P_DDR5_A

N_DDR5_A

SDQS_A

SDQS_A#

SCB_A0

SCB_A1

SCB_A2

SCB_A3

SCB_A4

SCB_A5

SCB_A6

SCB_A7

TP_ SA DDR1 M A1 3

TP_SA_RCVENOUT

TP_SA_RCVENIN

SM_XSLEWIN

MCH_VREF_A

5

AN26

AP25

AN25

AR24

AP23

AN22

AR23

AN21

AN23

AP22

AP26

AP21

AN20

AN30

AN28

AP29

AP27

AN27

AR27

AR20

AR29

AN31

AR28

AP31

AP19

AN19

AN18

AR19

AP30

AP32

AN29

AN32

AL29

AM30

AN2

AN3

AC34

AC35

AL28

AK28

AM3

AM2

AC33

AB34

V30

U30

V32

V31

AA31

AA30

R30

R31

Y30

AB29

AB33

AH15

AE16

AK12

AJ12

AE7

U24C

SMA_A0

SMA_A1

SMA_A2

SMA_A3

SMA_A4

SMA_A5

SMA_A6

SMA_A7

SMA_A8

SMA_A9

SMA_A10

SMA_A11

SMA_A12

SMA_A13

SWE_A

SCAS_A

SRAS_A

SBS_A0

SBS_A1

SBS_A2

SCS_A0

SCS_A1

SCS_A2

SCS_A3

SCKE_A0

SCKE_A1

SCKE_A2

SCKE_A3

SODT_A0

SODT_A1

SODT_A2

SODT_A3

SCLK_A0

SCLK_A0

SCLK_A1

SCLK_A1

SCLK_A2

SCLK_A2

SCLK_A3

SCLK_A3

SCLK_A4

SCLK_A4

SCLK_A5

SCLK_A5

SDQS_A8

SDQS_A8

SCB_A0

SCB_A1

SCB_A2

SCB_A3

SCB_A4

SCB_A5

SCB_A6

SCB_A7

RSV

RSV/TP1

RSV/TP0

SM_SLEWOUT0

SM_SLEWIN0

SVREF0

ALDERWOOD

REV=1.0

FIN=NB

BOM=CORE

3 of 8

SDQS_A0

SDQS_A0

SDM_A0

SDQ_A0

SDQ_A1

SDQ_A2

SDQ_A3

SDQ_A4

SDQ_A5

SDQ_A6

SDQ_A7

SDQS_A1

SDQS_A1

SDM_A1

SDQ_A8

SDQ_A9

SDQ_A10

SDQ_A11

SDQ_A12

SDQ_A13

SDQ_A14

SDQ_A15

SDQS_A2

SDQS_A2

SDM_A2

SDQ_A16

SDQ_A17

SDQ_A18

SDQ_A19

SDQ_A20

SDQ_A21

SDQ_A22

SDQ_A23

SA_DQS_3

SA_DQS_3

SA_DM_3

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SDQS_A4

SDQS_A4

SDM_A4

SDQ_A32

SDQ_A33

SDQ_A34

SDQ_A35

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_A39

SDQS_A5

SDQS_A5

SDM_A5

SDQ_A40

SDQ_A41

SDQ_A42

SDQ_A43

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_A47

SDQS_A6

SDQS_A6

SDM_A6

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_A54

SDQ_A55

SDQS_A7

SDQS_A7

SDM_A7

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_A62

SDQ_A63

4

DQS_A0

AG1

DQS_A#0

AG2

DQM_A0

AF2

DATA_A0

AE3

DATA_A1

AF3

DATA_A2

AH3

DATA_A3

AJ2

DATA_A4

AE2

DATA_A5

AE1

DATA_A6

AG3

DATA_A7

AH2

DQS_A1

AL3

DQS_A#1

AL2

DQM_A1

AL1

DATA_A8

AK2

DATA_A9

AK3

DATA_A10

AN4

DATA_A11

AP4

DATA_A12

AJ1

DATA_A13

AJ3

DATA_A14

AP2

DATA_A15

AP3

DQS_A2

AP7

DQS_A#2

AN7

DQM_A2

AP6

DATA_A16

AP5

DATA_A17

AK7

DATA_A18

AM9

DATA_A19

AL7

DATA_A20

AR5

DATA_A21

AN5

DATA_A22

AM7

DATA_A23

AM8

DQS_A3

AH16

DQS_A#3

AG17

DQM_A3

AF17

DATA_A24

AE17

DATA_A25

AF16

DATA_A26

AL17

DATA_A27

AH17

DATA_A28

AE15

DATA_A29

AD17

DATA_A30

AK16

DATA_A31

AJ17

DQS_A4

AK27

DQS_A#4

AJ28

DQM_A4

AJ33

DATA_A32

AK29

DATA_A33

AK31

DATA_A34

AH27

DATA_A35

AD27

DATA_A36

AL30

DATA_A37

AL31

DATA_A38

AG27

DATA_A39

AF28

DQS_A5

AG35

DQS_A#5

AG33

DQM_A5

AG34

DATA_A40

AH34

DATA_A41

AH35

DATA_A42

AF33

DATA_A43

AE33

DATA_A44

AK34

DATA_A45

AJ34

DATA_A46

AG32

DATA_A47

AF34

DQS_A6

AA34

DQS_A#6

AA35

DQM_A6

AA33

DATA_A48

AD31

DATA_A49

AD35

DATA_A50

Y33

DATA_A51

W34

DATA_A52

AE35

DATA_A53

AE34

DATA_A54

AA32

DATA_A55

Y35

DQS_A7

U34

DQS_A#7

U35

DQM_A7

U33

DATA_A56

V34

DATA_A57

V33

DATA_A58

R32

DATA_A59

R34

DATA_A60

W35

DATA_A61

W33

DATA_A62

T33

DATA_A63

T35

4

MAA_B[0..13]<19,20>

WE_B#<19,20>

CAS_B#<19,20>

RAS_B#<19,20>

SBS_B[0..2]<19,20>

SCS_B#[0..3]<19,20>

SCKE_B[0..3]<19,20>

ODT_ B [0..3]<19,20>

P_DDR0_B<19>

N_DDR0_B<19>

P_DDR1_B<19>

N_DDR1_B<19>

P_DDR2_B<19>

N_DDR2_B<19>

P_DDR3_B<19>

N_DDR3_B<19>

P_DDR4_B<19>

N_DDR4_B<19>

P_DDR5_B<19>

N_DDR5_B<19>

SDQS_B<19>

SDQS_B#<19>

TP56

TP62

TP63

MAA_B0

MAA_B1

MAA_B2

MAA_B3

MAA_B4

MAA_B5

MAA_B6

MAA_B7

MAA_B8

MAA_B9

MAA_B10

MAA_B11

MAA_B12

MAA_B13

WE_B#

CAS_B#

RAS_B#

SBS_B0

SBS_B1

SBS_B2

SCS_B#0

SCS_B#1

SCS_B#2

SCS_B#3

SCKE_B0

SCKE_B1

SCKE_B2

SCKE_B3

ODT_B0

ODT_B1

ODT_B2

ODT_B3

P_DDR0_B

N_DDR0_B

P_DDR1_B

N_DDR1_B

P_DDR2_B

N_DDR2_B

P_DDR3_B

N_DDR3_B

P_DDR4_B

N_DDR4_B

P_DDR5_B

N_DDR5_B

SDQS_B

SDQS_B#

SCB_B0

SCB_B1

SCB_B2

SCB_B3

SCB_B4

SCB_B5

SCB_B6

SCB_B7

TP_S MAA_DDR_B

TP_SB_RCVENOUT

TP_SB_RCVENIN

SM_YSLEWIN

MCH_VREF_B

SMRCOMP_P

SMRCOMP_N

SMOC DCOMP1

SMOC DCOMP0

3

AN15

AR15

AN14

AP14

AN13

AN11

AP13

AR11

AR12

AP11

AP15

AP10

AN10

AM34

AP17

AP18

AN17

AR16

AN16

AN9

AP33

AM33

AN33

AP34

AR9

AP9

AR8

AN8

AN34

AL34

AL35

AL33

AH23

AG23

AK9

AL9

AE26

AE25

AL23

AK22

AJ11

AL11

AD28

AD29

AK21

AJ21

AJ20

AJ18

AJ23

AJ24

AL20

AK18

AL21

AL22

AD32

AK15

AL15

AF9

AE10

AE8

AG8

AG4

AE5

AF5

3

U24D

SMA_B0

SMA_B1

SMA_B2

SMA_B3

SMA_B4

SMA_B5

SMA_B6

SMA_B7

SMA_B8

SMA_B9

SMA_B10

SMA_B11

SMA_B12

SMA_B13

SWE_B

SCAS_B

SRAS_B

SBS_B0

SBS_B1

SBS_B2

SCS_B0

SCS_B1

SCS_B2

SCS_B3

SCKE_B0

SCKE_B1

SCKE_B2

SCKE_B3

SODT_B0

SODT_B1

SODT_B2

SODT_B3

SCLK_B0

SCLK_B0

SCLK_B1

SCLK_B1

SCLK_B2

SCLK_B2

SCLK_B3

SCLK_B3

SCLK_B4

SCLK_B4

SCLK_B5

SCLK_B5

SDQS_B8

SDQS_B8

SCB_B0

SCB_B1

SCB_B2

SCB_B3

SCB_B4

SCB_B5

SCB_B6

SCB_B7

RSV

RSV/TP3

RSV/TP2

SM_SLEWIN1

SM_SLEWOUT1

SVREF1

SRCOMP1

SRCOMP0

SOCOMP1

SOCOMP0

ALDERWOOD

ALDERWOOD

REV=1.0

NB

CORE

4 of 8

SDQS_B0

SDQS_B0

SDM_B0

SDQ_B0

SDQ_B1

SDQ_B2

SDQ_B3

SDQ_B4

SDQ_B5

SDQ_B6

SDQ_B7

SDQS_B1

SDQS_B1

SDM_B1

SDQ_B8

SDQ_B9

SDQ_B10

SDQ_B11

SDQ_B12

SDQ_B13

SDQ_B14

SDQ_B15

SDQS_B2

SDQS_B2

SDM_B2

SDQ_B16

SDQ_B17

SDQ_B18

SDQ_B19

SDQ_B20

SDQ_B21

SDQ_B22

SDQ_B23

SDQS_B3

SDQS_B3

SDM_B3

SDQ_B24

SDQ_B25

SDQ_B26

SDQ_B27

SDQ_B28

SDQ_B29

SDQ_B30

SDQ_B31

SDQS_B4

SDQS_B4

SDM_B4

SDQ_B32

SDQ_B33

SDQ_B34

SDQ_B35

SDQ_B36

SDQ_B37

SDQ_B38

SDQ_B39

SDQS_B5

SDQS_B5

SDM_B5

SDQ_B40

SDQ_B41

SDQ_B42

SDQ_B43

SDQ_B44

SDQ_B45

SDQ_B46

SDQ_B47

SDQS_B6

SDQS_B6

SDM_B6

SDQ_B48

SDQ_B49

SDQ_B50

SDQ_B51

SDQ_B52

SDQ_B53

SDQ_B54

SDQ_B55

SDQS_B7

SDQS_B7

SDM_B7

SDQ_B56

SDQ_B57

SDQ_B58

SDQ_B59

SDQ_B60

SDQ_B61

SDQ_B62

SDQ_B63

DCL_CO RE_GMCH

2

DQS_B0

AH8

DQS_B#0

AH9

DQM_B0

AH10

DATA_B0

AG11

DATA_B1

AG10

DATA_B2

AJ7

DATA_B3

AJ6

DATA_B4

AE11

DATA_B5

AF11

DATA_B6

AJ8

DATA_B7

AH7

DQS_B1

AM5

DQS_B#1

AL5

DQM_B1

AK5

DATA_B8

AK10

DATA_B9

AL4

DATA_B10

AL8

DATA_B11

AF12

DATA_B12

AH4

DATA_B13

AJ5

DATA_B14

AL6

DATA_B15

AN6

DQS_B2

AH13

DQS_B#2

AG14

DQM_B2

AH12

DATA_B16

AF13

DATA_B17

AD14

DATA_B18

AF14

DATA_B19

AE14

DATA_B20

AD12

DATA_B21

AE13

DATA_B22

AK13

DATA_B23

AL14

DQS_B3

AG20

DQS_B#3

AF20

DQM_B3

AE20

DATA_B24

AD18

DATA_B25

AE19

DATA_B26

AL18

DATA_B27

AK19

DATA_B28

AF15

DATA_B29

AD15

DATA_B30

AH19

DATA_B31

AH21

DQS_B4

AH25

DQS_B#4

AG26

DQM_B4

AF25

DATA_B32

AF24

DATA_B33

AG24

DATA_B34

AL26

DATA_B35

AJ26

DATA_B36

AF23

DATA_B37

AD23

DATA_B38

AL25

DATA_B39

AJ25

DQS_B5

AH28

DQS_B#5

AH30

DQM_B5

AH31

DATA_B40

AK32

DATA_B41

AJ31

DATA_B42

AG31

DATA_B43

AF30

DATA_B44

AJ29

DATA_B45

AK33

DATA_B46

AG30

DATA_B47

AG28

DQS_B6

AB31

DQS_B#6

AC30

DQM_B6

AD24

DATA_B48

AF27

DATA_B49

AE27

DATA_B50

AC26

DATA_B51

AB26

DATA_B52

AE31

DATA_B53

AE29

DATA_B54

AC28

DATA_B55

AB27

DQS_B7

W27

DQS_B#7

Y28

DQM_B7

W31

DATA_B56

AA28

DATA_B57

W29

DATA_B58

V28

DATA_B59

V29

DATA_B60

Y26

DATA_B61

AA29

DATA_B62

W26

DATA_B63

U26

R344 1KST/4

VCC_DDR2

R339

1KST/4

PLACE CLOSE TO MCH

VCC_DDR2

R345

80.6RST

C297

0.1u/6

R340 80.6RST

R348 40.2/4 /ST

R351 40.2/4 /ST

DATA_A[0..63]

DAT A_A[0 ..63] <18>

DQS_A[0..7]

DQS _A[0 ..7] <18>

DQS_ A #[0..7]

DQS _A#[ 0..7] <18>

SCB_A[0..7] SCB_B[0..7]

SCB _A[0 ..7] <18> SCB _B[0 ..7] <19>

DQM_ A [0..7]

DQM _A[0. .7] <18>

Micro-Star Int'l Co ., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Alderw o o d M em o r y Signal

Size Doc u men t Numbe r Re v

MS-9157

2

Date: Sheet of

CB70

1u/6

SMRCOMP_N

SMRCOMP_P

SMOC DCOMP1

SMOC DCOMP0

1

MCH_VREF_B

C296

0.1u/6

MCH_VREF_A

C289

0.1u/6

DATA_B[0..63]

DQS_B[0..7]

DQS_ B #[0..7]

DQM_ B [0..7]

1

DAT A_B[0 ..63] <19>

DQS _B[0 ..7] <19>

DQS _B#[ 0..7] <19>

DQM _B[0. .7] <19>

15 45Wednesday, June 09, 2004

0BCustom

Page 16

5

4

3

2

1

ANALOG FILTERS

L24 10uH-0805-100mA

L20 10uH-0805-100mA

L21 10uH-0805-100mA

L23 10uH-0805-100mA

L32 OPTION 0 ohm

H_FSBSEL0<10,11,12>

H_FSBSEL1<10,11,12>

H_FSBSEL2<10,11,12>

VCCA_GPLL_R

L22 0.1uH

H_FSBSEL0

H_FSBSEL1

H_FSBSEL2

R32 5 X_1K

R303 0/6

L29 OPTION 0 ohm

C233

X_0.22u

R322 10K/6

R314 10K/6

R310 10K/6

R307 1K/6

L18 1 uH-0805/0.5A

V_2P5_MCH

U24E

ALDERWOOD

H16

E15

D17

M16

F15

C15

A16

B15

C14

K15

L10

M10

AR2

AR1

AP1

AH5

AG6

Y12

V12

U12

T12

R24

R12

P30

P24

BSEL_0

BSEL_1

BSEL_2

RSV

RSV

MTYPE

EXP_SLR

RSV

RSV

RSV

VCC

VSS

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

ALDERW OOD

REV =1.0

FIN=NB

BOM=CORE

DREFCLKN

DREFCLKP

EXTTS

RSTIN

PWROK

ICH_SYNC

5 of 8

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

RSV

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

RSV

RSV

NC

NOA_0

D D

C C

B B

TP67

TP68

TP69

TP70

TP71

V_1P5_CORE

NOA_1

NOA_2

NOA_3

NOA_4

NOA_5

NOA_6

NOA_7

NOA_8

NOA_9

AR35

AR34

AP35

AM24

AM21

AM18

AM15

AM12

AL27

AK24

AJ14

AH24

AG29

AG25

AF22

AF19

AE30

AE18

AD30

AD21

AC24

AC23

AB12

AA12

W12

AC22

AC21

AC20

AC19

AC18

AC17

AC16

AC15

AC14

AC13

AC12

E12

D12

F14

D14

H14

G14

E14

J14

L14

M15

CK_96M_DREF

M13

CK_96M_DREF#

M12

DACREFSET

A15

P23

P12

N24

N23

N22

N12

L19

L12

K12

J12

H17

H15

H12

G12

F24

F12

E16

C16

B35

B1

A34

A2

K16

TP_BMBUSY

G16

TESTIN

R35

AF7

AG7

M14

TPEV_MCH_DET

A35

R753 2/6

EXTTS

PLTRST_MCH#

PWROK

ICH_SYNC#

V_2P5_DAC_FILTERED <17>

V_1P5_CORE

R304 10K/6

TP37

TP42

PLT RST_MC H# <40>

PWR OK <23, 35, 39, 40,42>

ICH_SYNC# <23>

TP30

ICH_SYNC#

V_2P5_MCH

V_2P5_MCH

R1845

8.2K/6

V_1P5_CORE

VCCA_GPLL

C250

10u/8

VCCA_HPLL

+

CT15

470u-6.3V

VCCA_DPLLA

+

CT17

330u/6.3V

VCCA_DPLLB

+

CT14

330u/6.3V

VCCA_MPLL

+

CT12

470u-6.3V

V_2P5_DAC_FILTERED

+

CT13

100u/25V

NOA_0

NOA_1

NOA_2

NOA_5

NOA_6

R315 1K/6

C235

0.1u/6

VCCA_GPLL <17>

C238

0.1u/6

VCCA_HPLL <17>

C245

0.1u/6

VCCA_ D PLLA <17>

C239

X_0.1u

VCCA_ D PLLB <17>

C241

X_0.1u

VCCA_MPLL <17>

C234

0.1u/6

V_2P5_DAC_FILTERED <17>