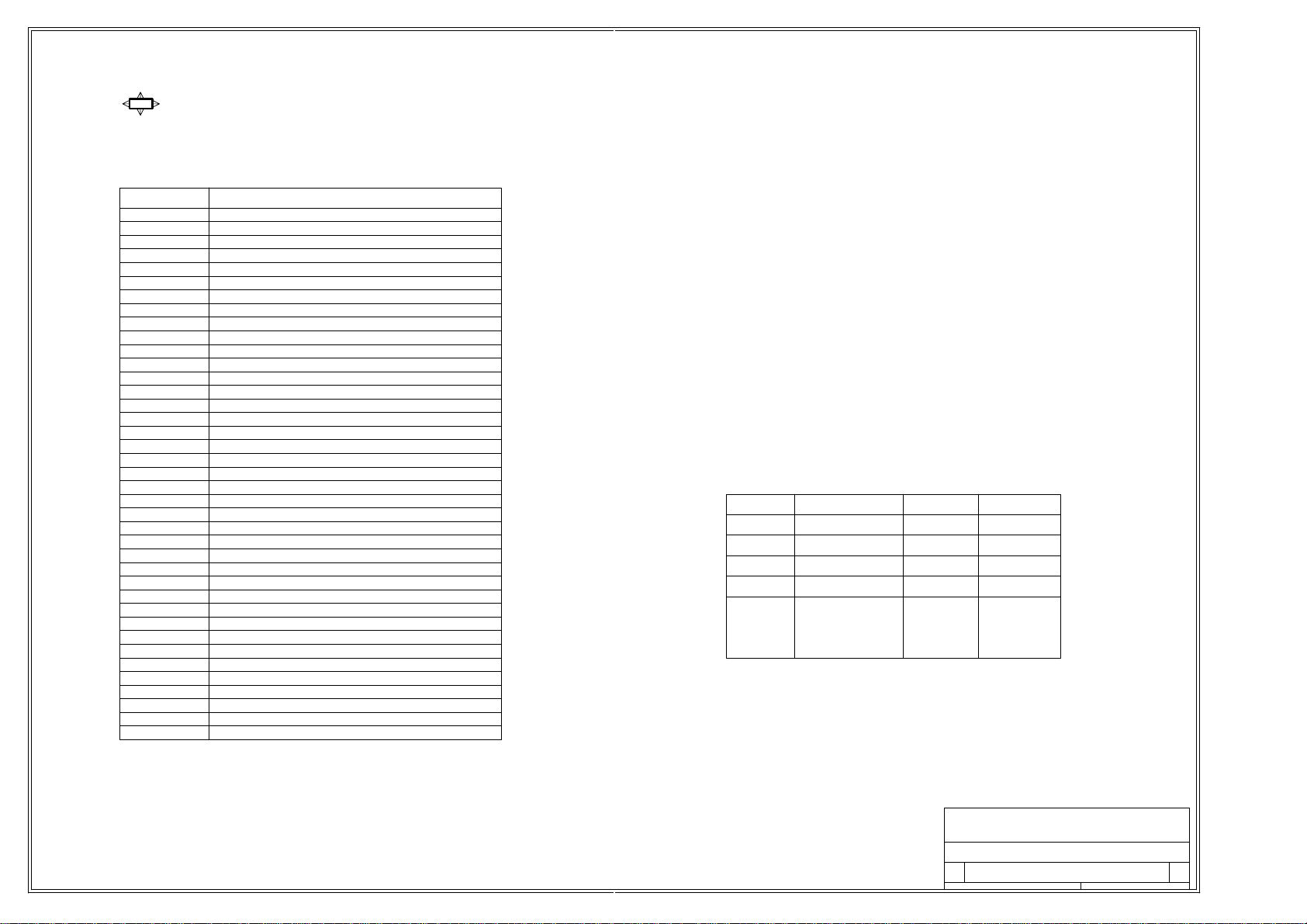

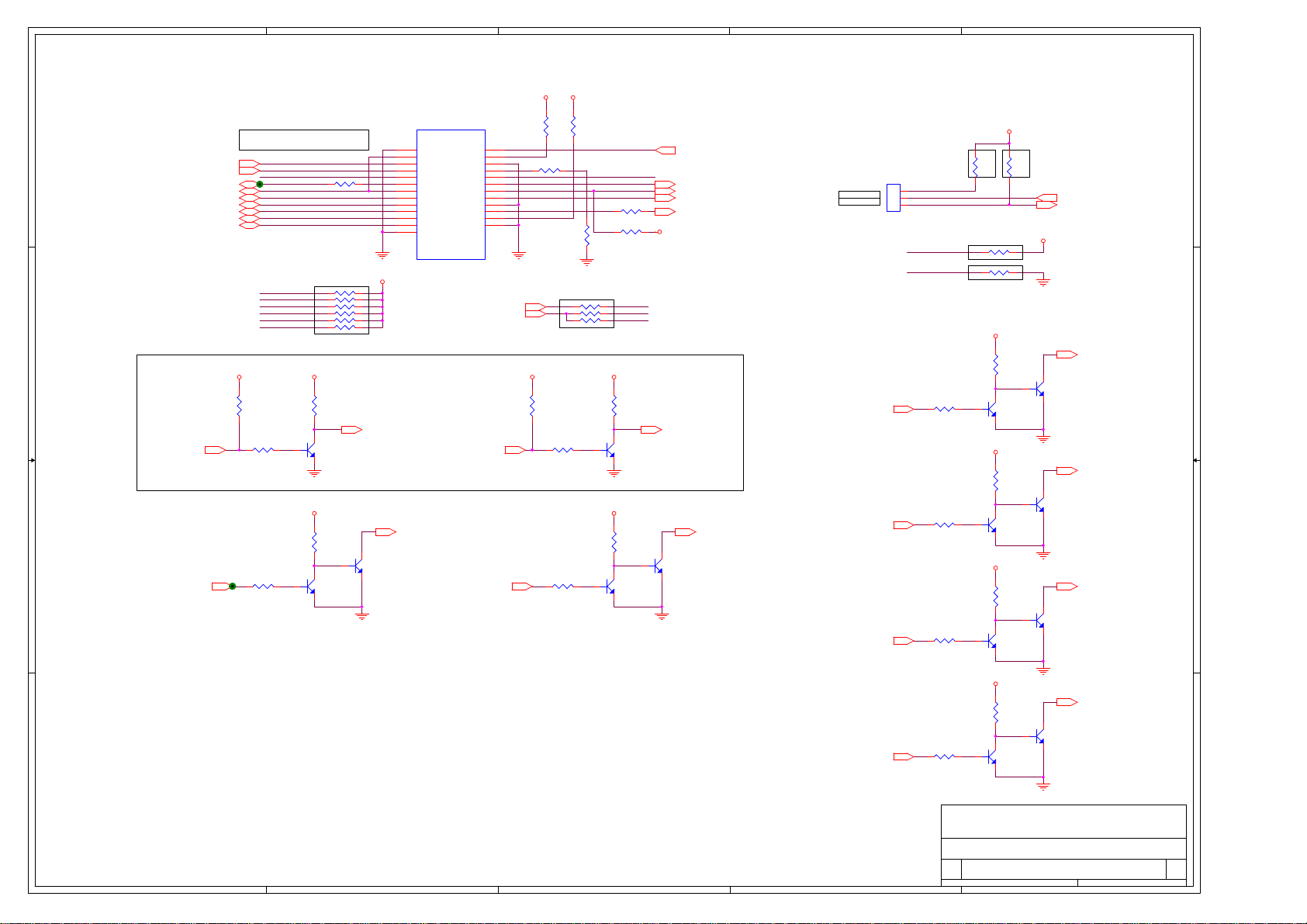

Page 1

1

MSI

MS-9151 REV 100

Tumwater + ICH5R + PXH Schematics

Table of Contents

TitlePage

01

02

03

04

05

06

07

08

09

10-11

20 PCI-E x16 Slot

30 USB / SATA / IDE Connectors

A A

31 AC'97 AD1981B CODEC

32 PCI-32 SLOTs

33 GbE BCM5721

34 IEEE 1394

35-36 VGA RADEON 7000-M

37 FWH / ASR / PERR / Improper Shutdown

38-39 PXH

41 PCI-X 100MHz Slot support ZCR (Black Color)

43-45 SCSI (AIC-7902W)

46 SIO PC87366 / LEGECY IO Ports

47 I2C Mux. circuits

48 Hardware Monitor ADT7468

49

50-51

52

Table of Contents

System Block Diagram

Power Delivery Block Diagram

System Clock Block Diagram

System Reset Block Diagram

System SMBus Block Diagram

DDRII Routing Block Diagram

Interrupt Routing Block Diagram

Hardwar Monitor Block Diagram

Processor 0

Processor 112-13

Processor Level Shift / ITP Port14

CK409B Clock Gen. / DB800 SRC Buffer15

MCH (Tumwater)16-19

DDRII 40021-27

ICH5-R28-29

PCI-X 133MHz Slot (Green Color)40

PCI-X 100MHz Slot42

Front Panel / Power Connctor

System Voltage Regulators

NMI / S3 Circuit / 5V Dual Circuit

Processor 0 VRD53

Processor 1 VRM54

Manule Part / BOM options55

Revision Change History56

Parts P/N difference between projects

Part Reference OAK/Spruce (BOM default) N3 Memo

N32-1040481-F02 N32-1030091-H06FAN1~FAN4

N59-09M0021-F02 N51-09M0021-F02COM1/COM2

N59-25F0071-F02 N51-25F0041-F02LPT1

N32-1120031-M06JFP1 N32-1080131-H06 N3 use 8 pin header

N3 use 3 pin FAN

with 2 pcs screws

with 2 pcs screws

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Table of Contents

Size Document Number Rev

MS-9151-100

1

Date: Sheet of

1 56Thursday, June 03, 2004

100Custom

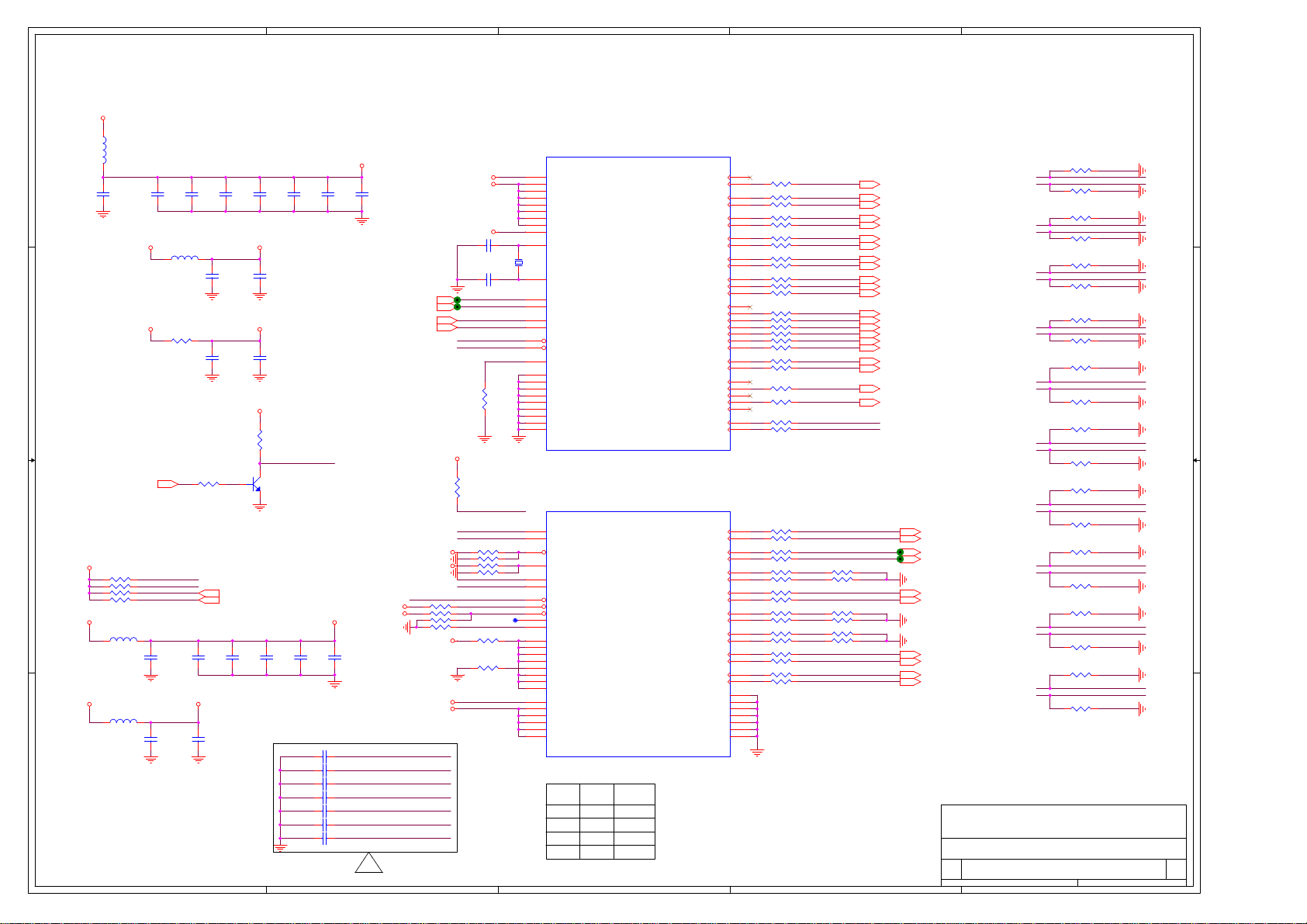

Page 2

5

4

3

2

1

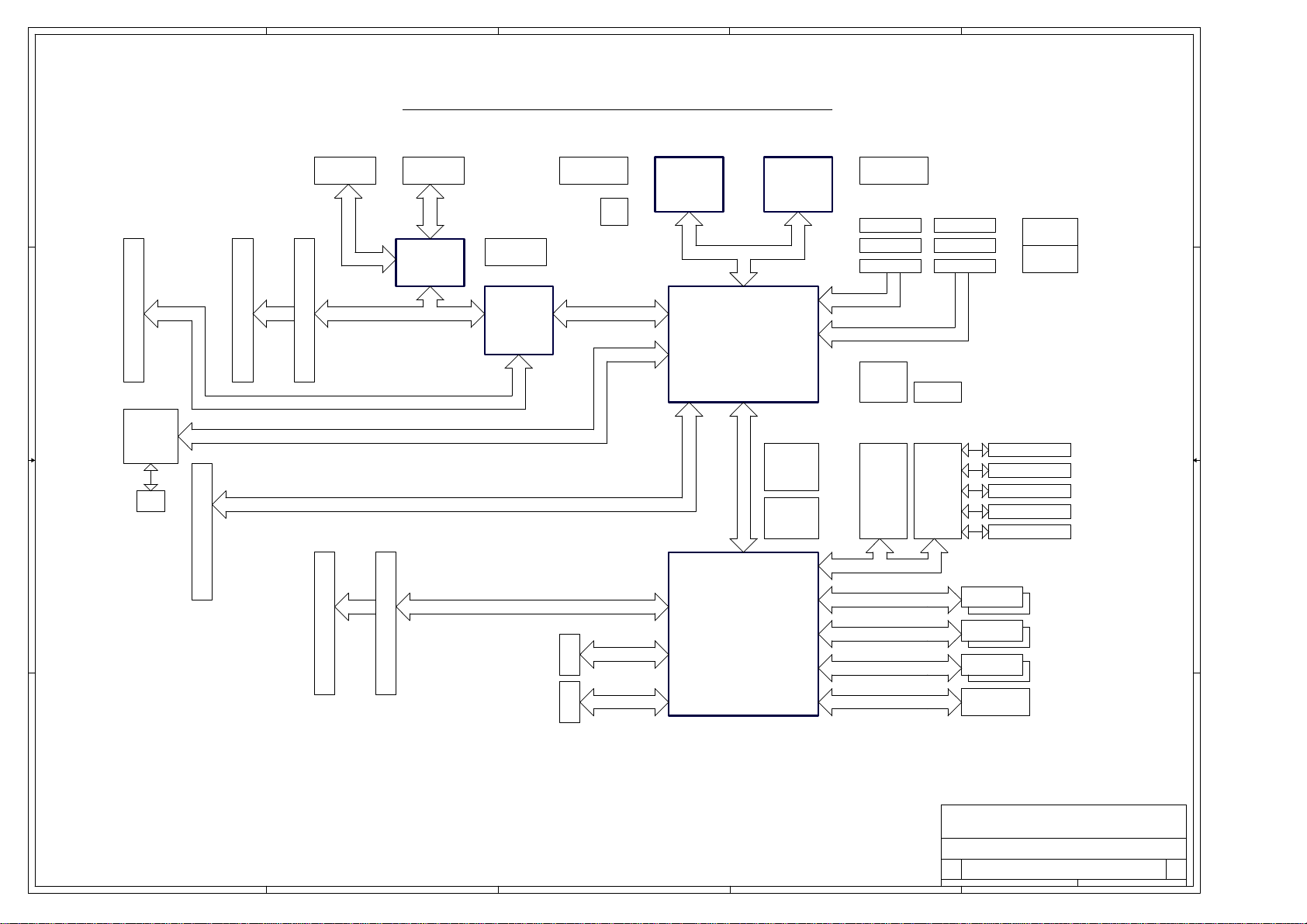

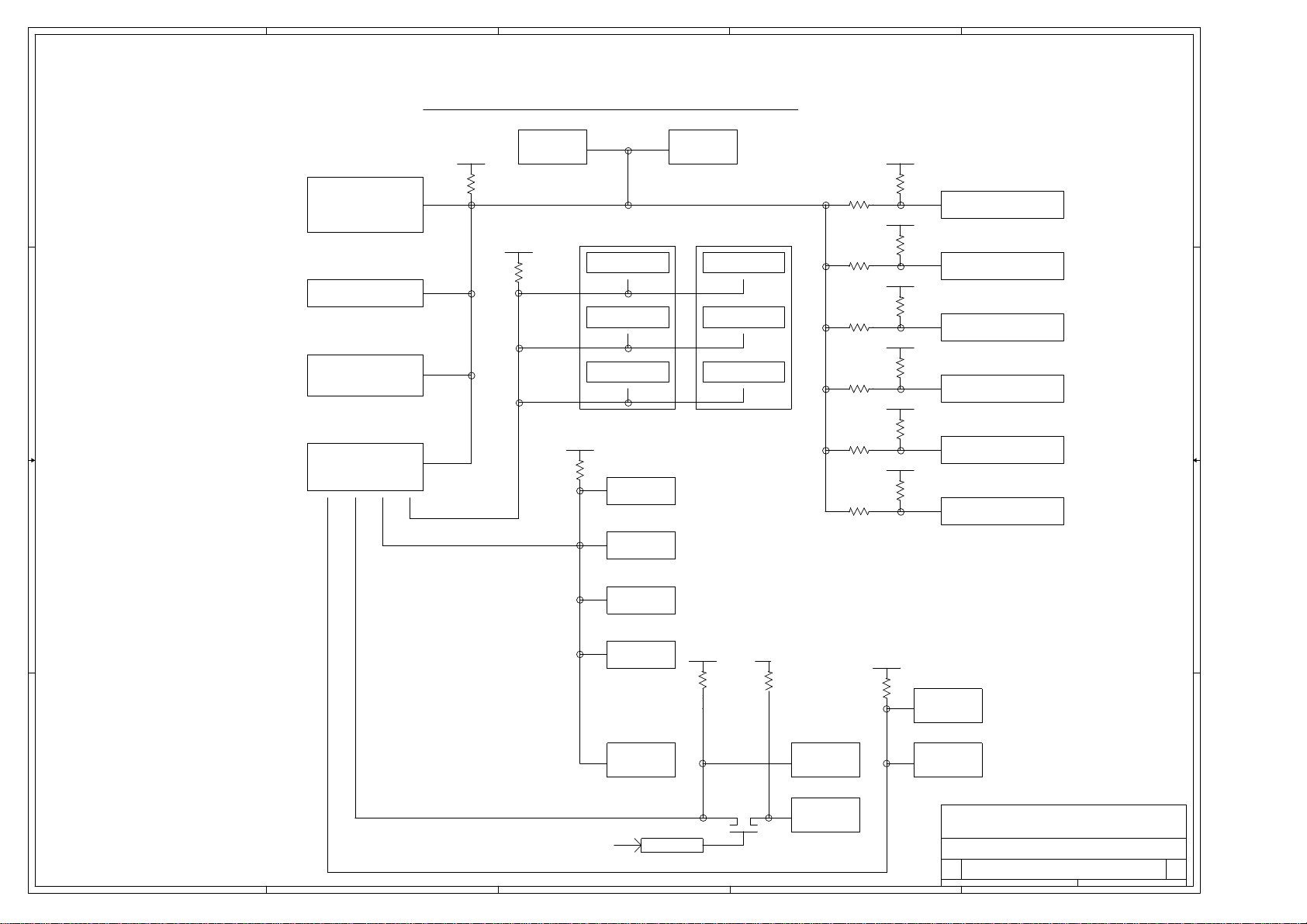

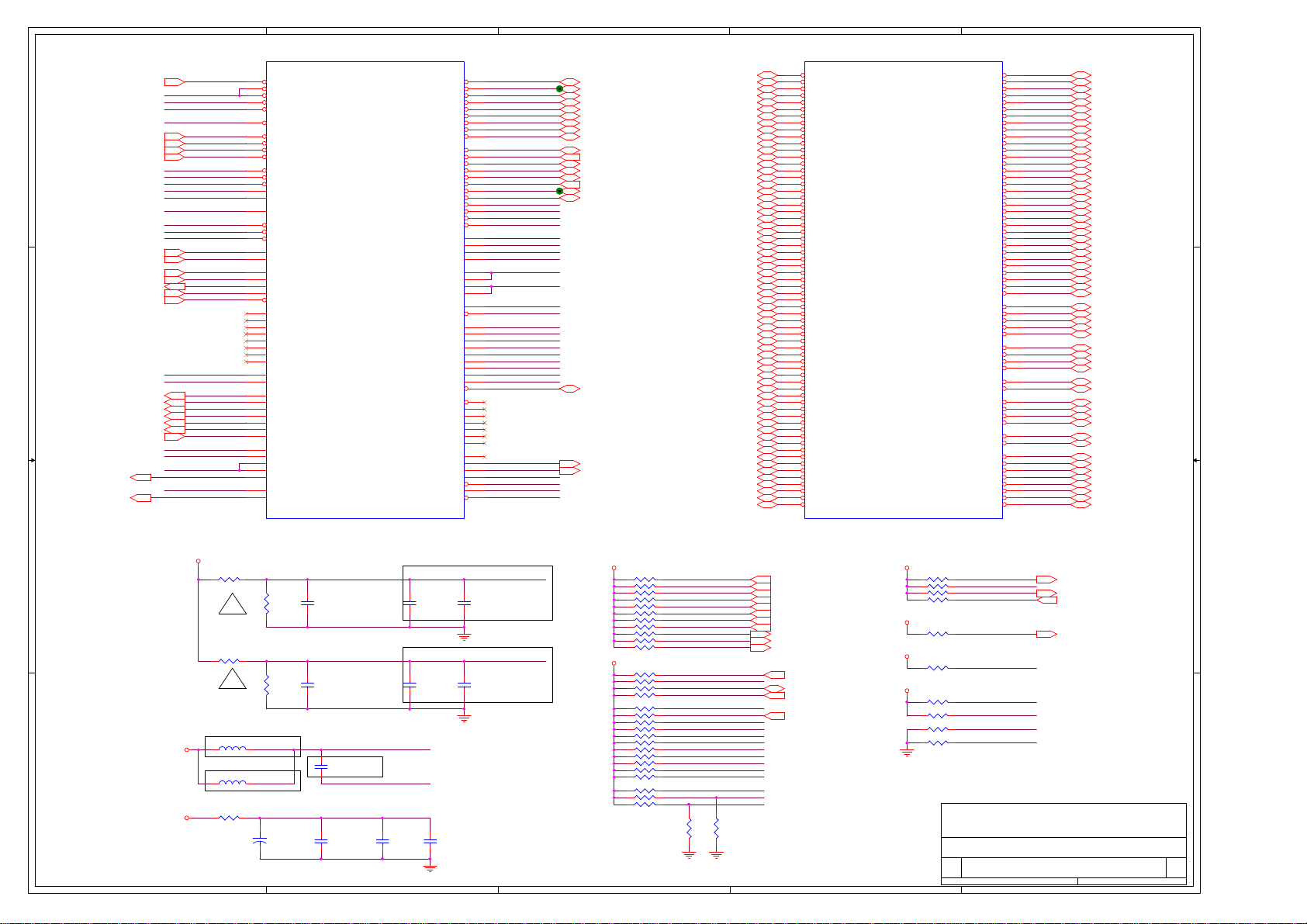

MS-9151 SYSTEM BLOCK DIAGRAM

D D

SCSI Conn

( INTERNAL )

SCSI 0

SCSI Conn

( INTERNAL )

SCSI 1

SCSI Ctrl.

AIC7902

SCSI VRegs

( 1.8V & 2.5V )

CPU0 VRD CPU1 VRM

ITP

CPU 0 CPU 1

( NOCONA /

JAYHAWK )

( 800MT/S - 6.4GB/S )

( NOCONA /

JAYHAWK )

DIMM B3

DIMM B2

DIMM B1 DIMM A1

DIMM A3

DIMM A2

1.8V VRD

( DDR II )

S3 SUPPORT

CIRCUITRY

PCI-X ( 100MT/S-800MB/S )

PCI-X 100MHZ SLOT #2

PCI-X 133MHZ SLOT

C C

B B

#3

BroadCom

BCM5721

GbE

RJ45

PCI EXPRESS X 16 SLOT # 6

PCI-X 100MHZ SLOT

#1

PCI-X ( 133MT/S-1GB/S )

PCI EXPRESS X4 ( 2GB/S )

PCI EXPRESS X16 ( 8GB/S )

(ZCR)

PXH

PCI 32-BIT 33MHZ 5V ( 133MB/S )

PCI EXPRESS X4 ( 2GB/S )

GROUP A

LINKS 4-7

GROUP A

LINKS 0

GROUP B & C

MCH

HUB INTERFACE 1.5

CK409B

CLOCK

DB800

BUFFER

ICH5-R

PCI 32/33 5V SLOT

#5

PCI 32/33 5V SLOT

#4

S-ATA

S-ATA

S-ATA

S-ATA

DDR II ( 400MT/S )

DDR II ( 400MT/S )

1.5V VRD

(MCH/PXH

/ICH5)

FWH

49LF008A

LPC

USB PORT #0 / #1

USB PORT #2 / #3

USB PORT #4 / #5

PRIMARY ATA-100

1.2V VRD

( FSB VTT )

Super I/O

PC87366

SERIAL PORT X 2

PARALLEL PORT

FLOPPY

PS/2 KEYBOARD

PS/2 MOUSE

REAR USB

REAR USB

FRONT USB

IDE

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System Block Diagram

Size Document Number Rev

MS-9151-100

5

4

3

2

Date: Sheet of

2 56Wednesday, June 02, 2004

1

100Custom

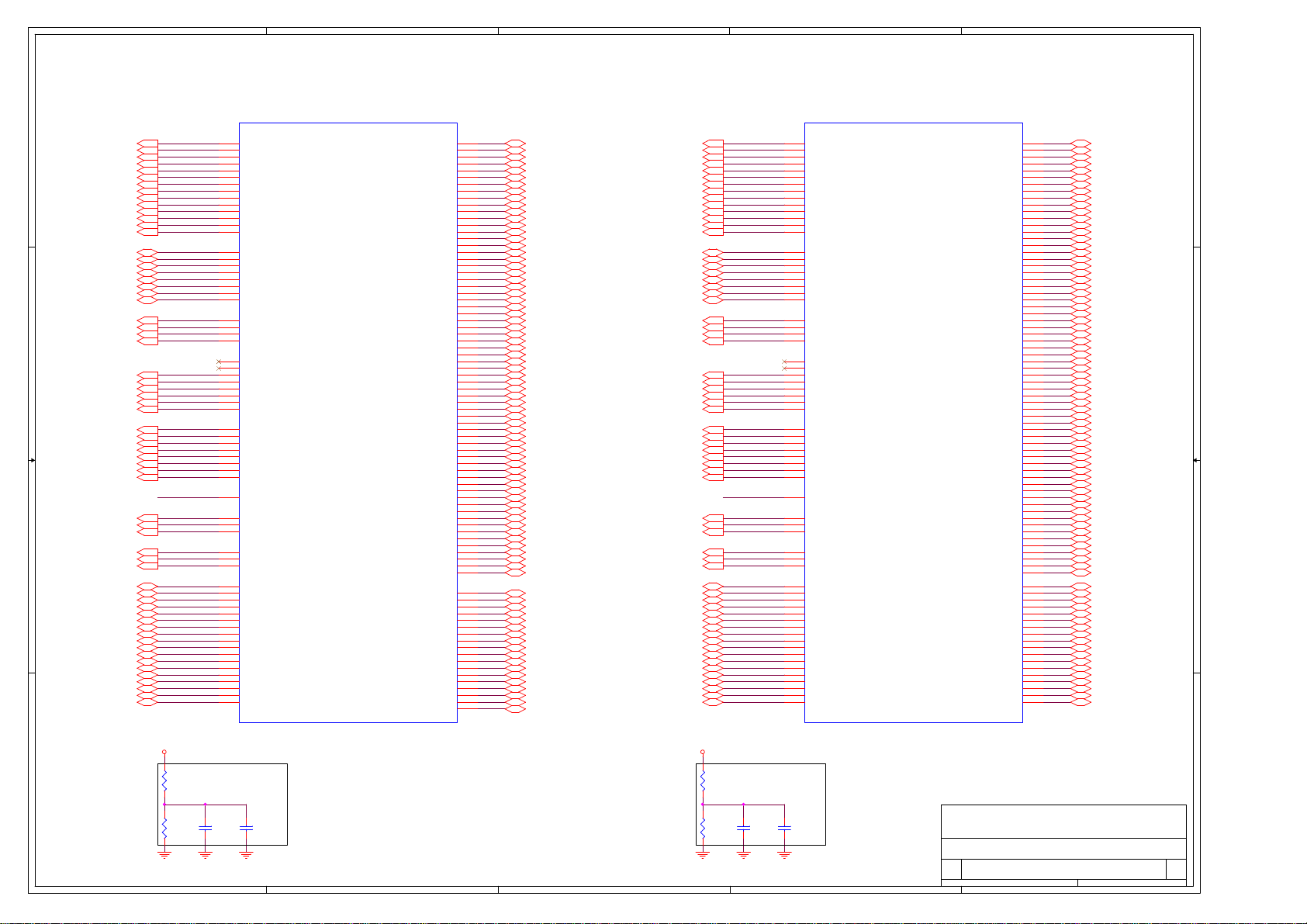

Page 3

5

4

3

2

1

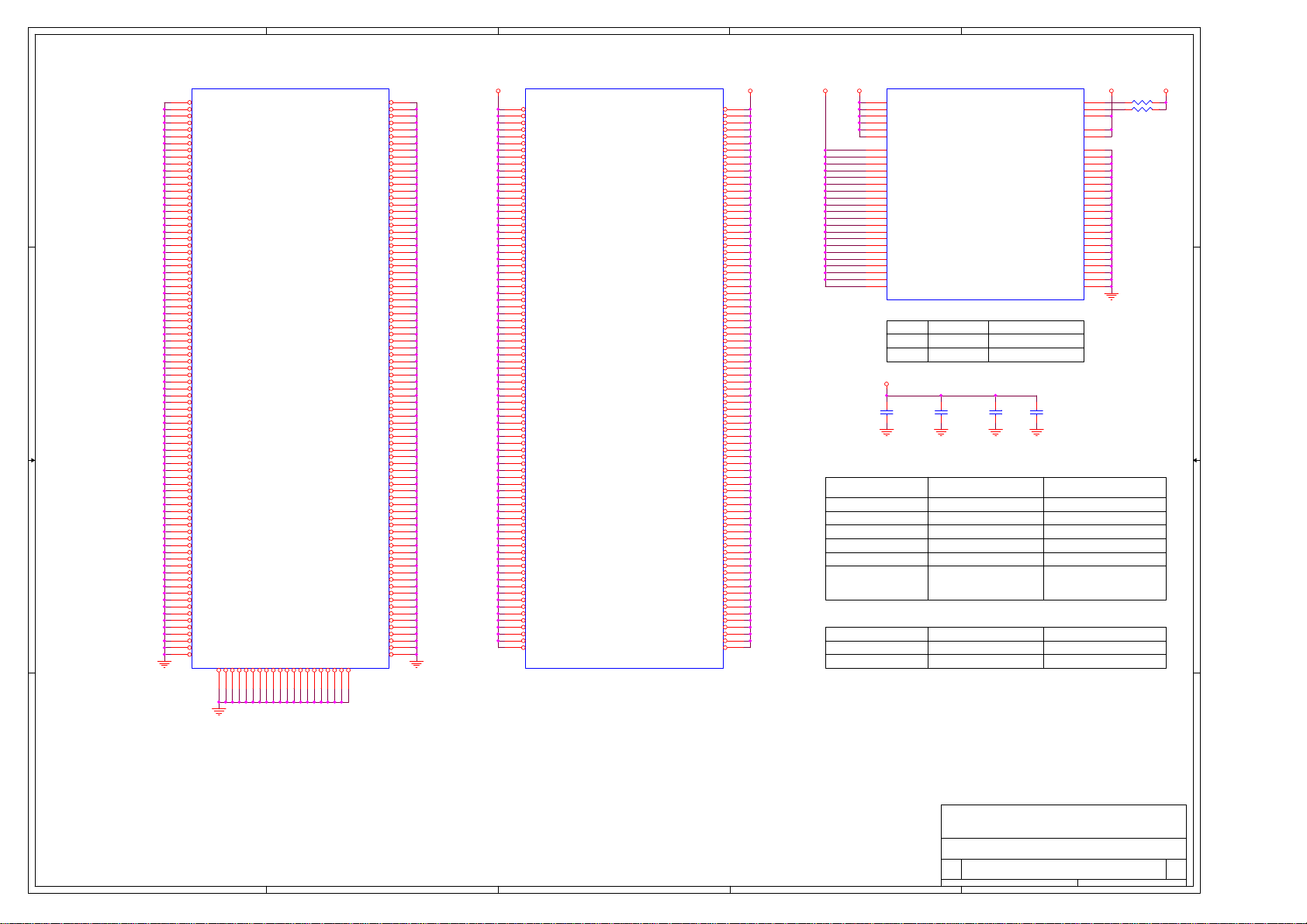

(1.275*120)/(12*0.8)=15.94

15.94A

VRD10.1

Switch Reg

D D

C C

B B

A A

31.88A

P12V_CPU

P12V

20.829A+?

P5V

38.235A+?

15.94A

VRM10.1 CPU1

Switch Reg

5.02A

P1V8

Switch Reg

(1.8*26.75)/(12*0.8)=5.02

4A

Fan*4

5.8A

PCI[1:6]

(Note 1)

P5V_AUD AD1981B

Linear RegVR7

3A

PWR1394

D2

Power Isolation

(1.5*12.47)/(5*0.7)=5.35

5.35A

P1V5 MCH

Switch Reg

85mA

Lattice

ISP2032E

?mA

PAL16V6

( U63 )

P2V5_VGA RADEON

VR6

Linear Reg

0.4A

VCC25_A

VR2

Linear Reg

0.4A

VCC25_B

VR3

Linear Reg

2A

LVTTRMPWR

_A

D39

Power Isolation

2A

LVTTRMPWR

_B

D40

Power Isolation

3A+?

P5V_USB USB*6

Switch

?mA

1394

UB TI_TSB

25A

PCI[2:6]

(Note 2)

5

120A

120A

6.00A

Q34

19.65A

1.1A

?mA9.5 mA+?

9.5mA

1.5A

1.5A

6.61A

0.86A

5.00A

?mA?mA

0.8A

2A

2A

3A

?mA

CPU0

P_VTT

Linear Reg

P1V8_AUX

Switch

DDR

Termination

SM2211

J1394CON1

1394_USB1B

ICH5

PXH

7000M

AIC-7902

SCSI_A

SCSI_B

Keyboard

& Mouse

(Reference Intel)

6.00A

1.65A

18A

4

CPU

MCH

ICH5

MCH

DIMMx6

MS-9151 POWER DELIEVERY DIAGRAM

?mA ?mA

RADEON

P3V3

Note 1: PCI & PCI-X is 0.5A , PCI Express*16 is 3.3A

Note 2: PCI & PCI-X is 5A

Note 3: 500uA for power down , 2.5mA for wake up

Note 4: 20mA for power down , 375mA for wake up

7000M

?mA

P1V8_VGA

VR1 Linear Reg

AIC-7902

0.78A

SVCC18

VR4

Linear Reg

VCC3_CLK

Power Isolation

FB1

VCC3_CLKA

Power Isolation

FB2

VCC3

_SRCLK

FB3

Power Isolation

VCC3

_SRCLK2

FB4

Power Isolation

0.48A

ICH5

0.60A

PXH

0.03A

PC87417

95.4mA

1394

150mA

NC7S08*3

( U89,91,124 )

3mA

EEPROM(U11)

AT24C02N

PCI[1:6]

?mA

JSCSI_BPI

P5V_STBY

0.78A0.36A

0.35A0.35A

CK409B

0.25A0.25A

DB800

3

1.597A+?

2

5mA+?

P5V_USB USB*6

Switch

1.592A+?

P3V3_STBY P1V8_STBY

U114 VR5Linear Reg Linear Reg

Title

Size Document Number Rev

Date: Sheet of

5mA

(Note 3)

?mA

?mA 300?mA

300mA

400mA

388mA

20mA

6mA

?mA

?mA

38uA

3mA

475mA

(Note 4)

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Power Delivery Block Diagram

MS-9151-100

Keyboard

& Mouse

P1V8_STBY

Linear Reg

P1V_STBY

Linear Reg

ICH5

PC87417

ADT7463*2

BCM5721

PCA9545

PCA9557*2

EEPROM(U43)

AT24C32N

PCI[1:6]

1

bird

300mA

400mA

3 56Wednesday, June 02, 2004

P1V8_AUX

Switch

BCM5721

BCM5721

100Custom

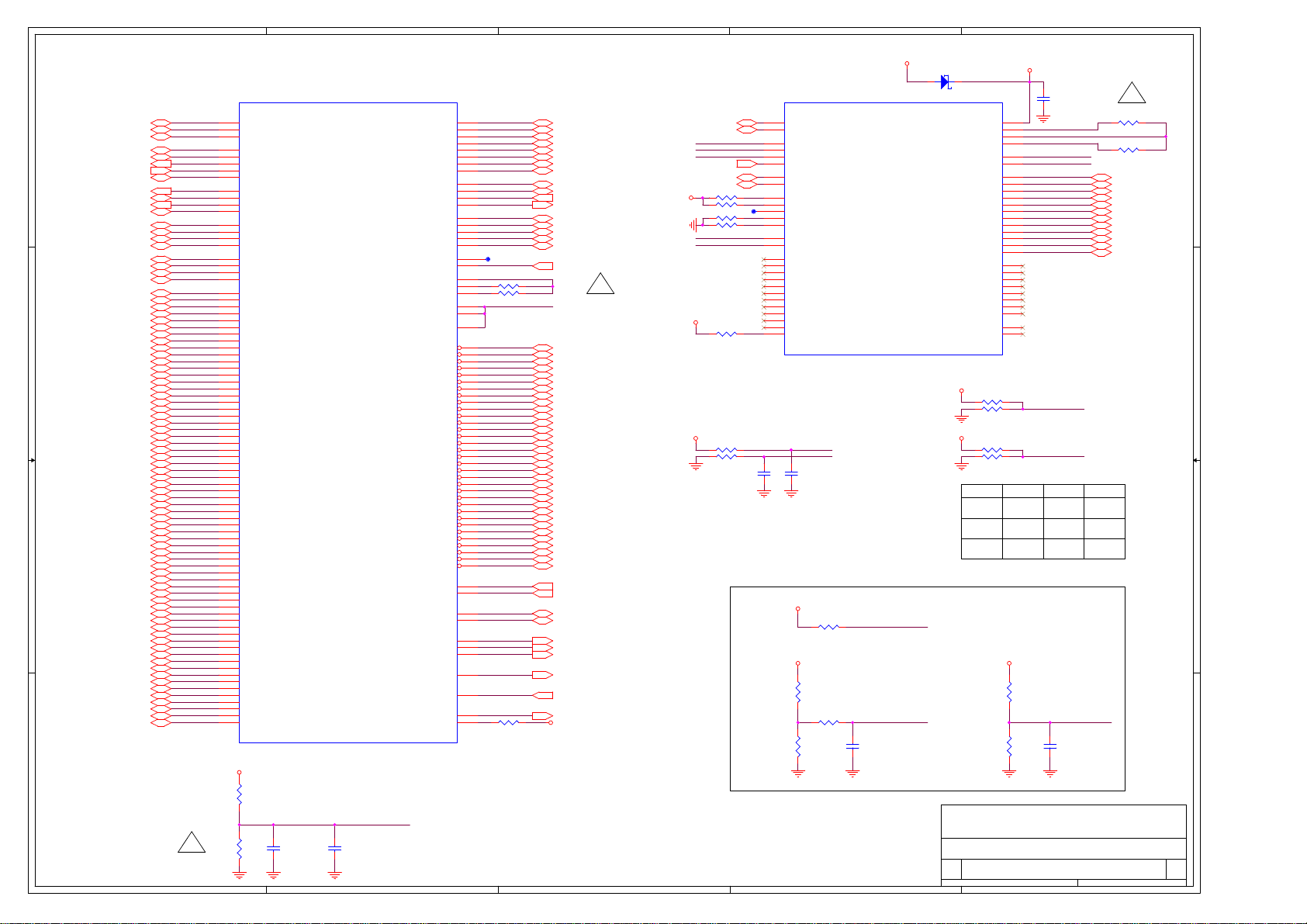

Page 4

5

4

3

2

1

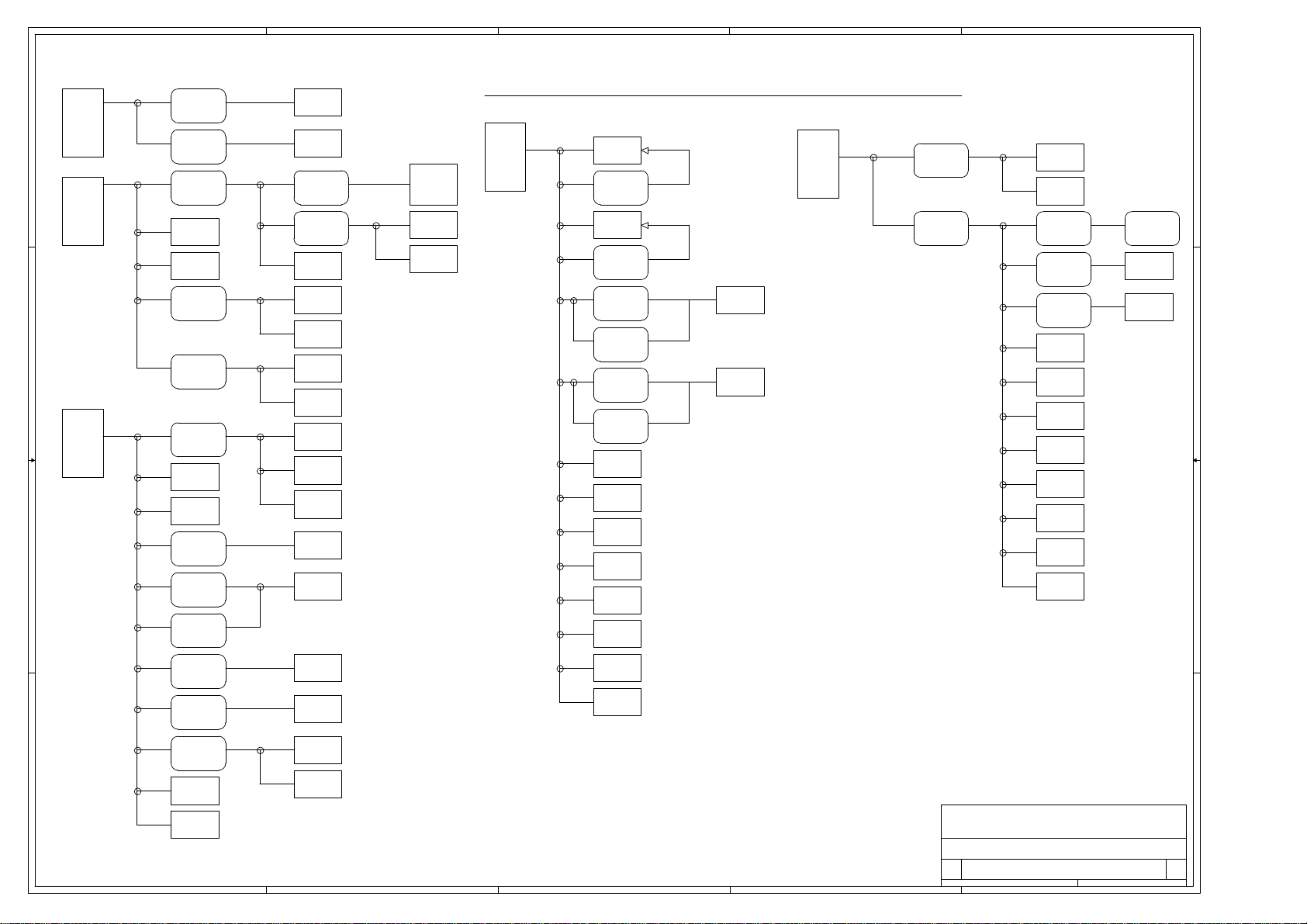

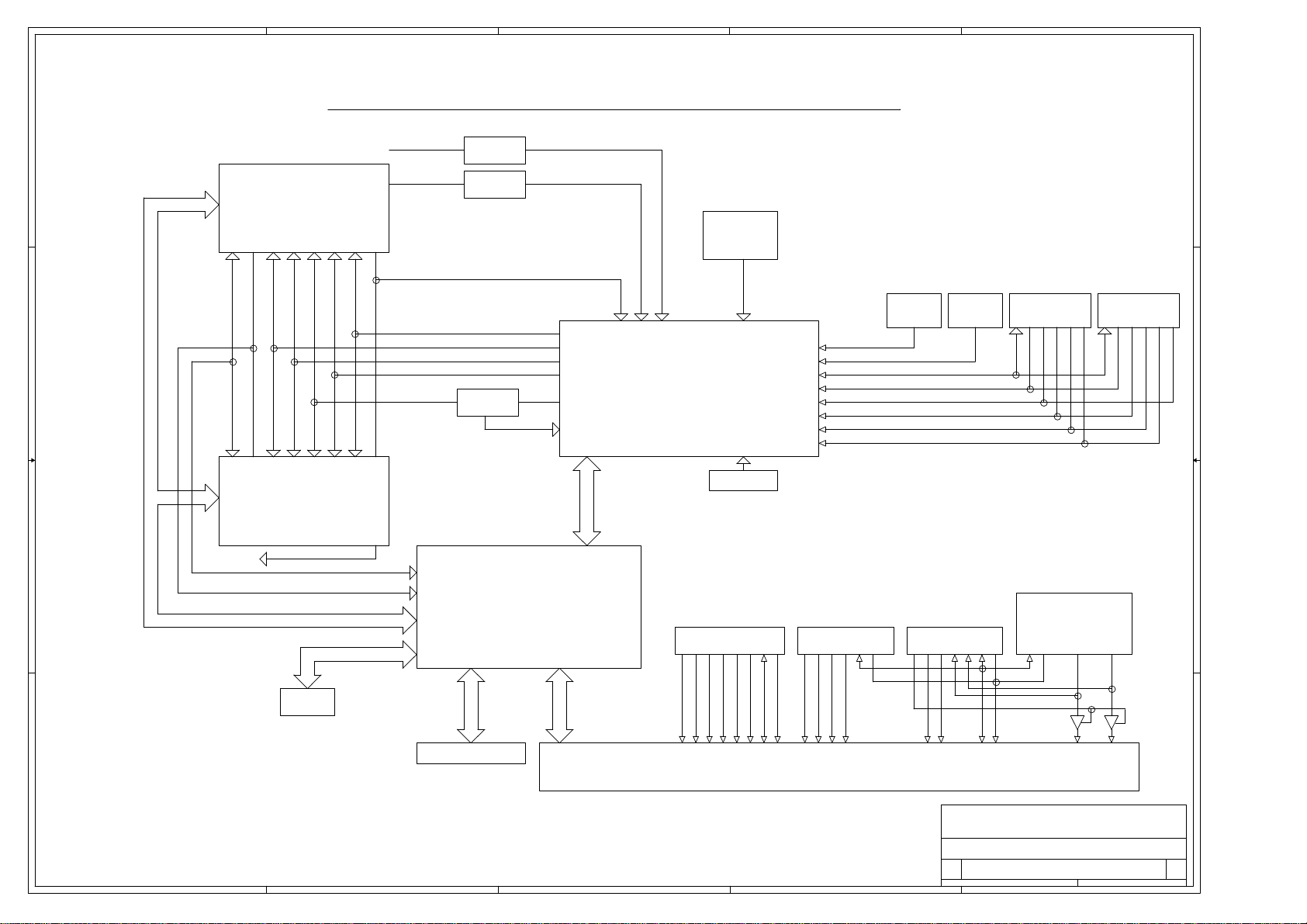

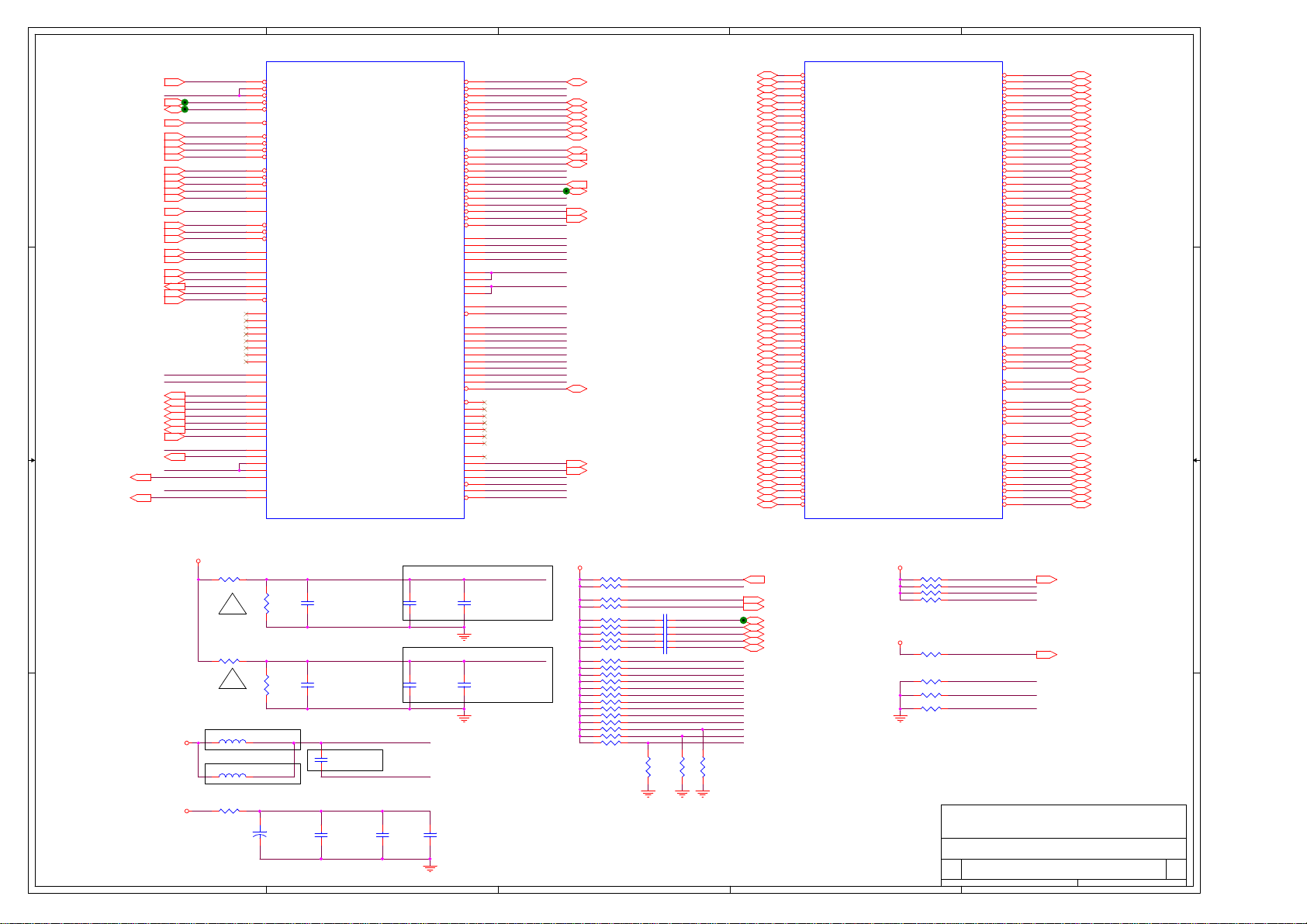

MS-9151 CLOCK BLOCK DIAGRAM

D D

CPU3

CPU2

CPU1

3V66_1

CPU0

C C

3V66_3

USB_48

PCIF0

SMA

CONNECTOR

14.318MHZCrystal

B B

A A

REF0

DOT_48

PCIF1

SRC

PCI1

PCI2

PCI3

PCI4

PCI5

PCIF2

P0_BCLK_P/N (200MHZ)

P1_BCLK_P/N (200MHZ)

MCH_BCLK_P/N (200MHZ)

MCH_66MHZ_CLK

ITP_BCLK_P/N (200MHZ)

ICH_HI_66MHZ_CLK

ICH_USB_48MHZ_CLK

ICH_33MHZ_CLK

ICH_14MHZ_CLK

SIO_48MHZ_CLK

SIO_33MHZ_CLK

SRC_100MHZ_CLK_P/N

PERR_33MHZ_CLK

PCI_SLOT2_33MHZ_CLK

PCI_SLOT3_33MHZ_CLK

PCI_SLOT3_33MHZ_CLK

1394_33MHZ_CLK

FWH_33MHZ_CLK

BCLK(P/N-1/0)

2

BCLK(P/N-1/0)

2

2

2

2

PAL16V8

PCI 32/33 ( SLOT # 2 )

PCI 32/33 ( SLOT # 3 )

27MHZ

Crystal

RADEON 7000M

24.576MHZ

Crystal

IEEE 1394

FWH

ITP_XDP

32.768KHZ

Crystal

ICH5

SIO

CPU0

CPU1

MCH

ICH_SRC_100MHZ_CLK_P/N

DDRA_CMDCLK_A0_P/N

DDRA_CMDCLK_A1_P/N

DDRA_CMDCLK_A2_P/N

DDRB_CMDCLK_B0_P/N

DDRB_CMDCLK_B1_P/N

DDRB_CMDCLK_B2_P/N

MCH_SRC_100MHZ_CLK_P/N

2 2

DIFF0 DIFF1 DIFF6

SRC

2

2

2

A1

DDR II DIMM #

2

DDR II DIMM #

25MHZ

Crystal

B1

2

A2

DDR II DIMM #

DDR II DIMM #

BCM5721

2

EXP_NW_100MHZ_CLK_P/N

DB800 ( SRC - DIFFERENTIAL BUFFER )

2

A3

DDR II DIMM #

B3

DDR II DIMM #

B2

PCI EXPRESS X16 SLOT # 1

2

EXP_SLOT1_100MHZ_CLK_P/N

DIFF7

DIFF4

PAPCLKO(6)

PAPCLKI

PBPCLKO(6)

PBPCLKI

2

PXH_SRC_100MHZ_CLK_P/N

PAPCLKO(0)

PXH

PBPCLKO(0)

PXH_PBPCLKO(0)

PAPCLKO(1)

PAPCLKO(2)

PXH_PAPCLKO(0)

PXH_PAPCLKO(1)

PXH_PAPCLKO(2)

PCI-X SLOT # 5

SUPPORTS

ZCR

PCI-X SLOT # 5

PCI-X SLOT # 6

U320 SCSI AIC7902

80MHZ

Osc

PCI-X SLOT # 4(133MHZ)

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System Clock Block Diagram

Size Document Number Rev

MS-9151-100

5

4

3

2

Date: Sheet of

4 56Wednesday, June 02, 2004

1

100Custom

Page 5

5

4

3

2

1

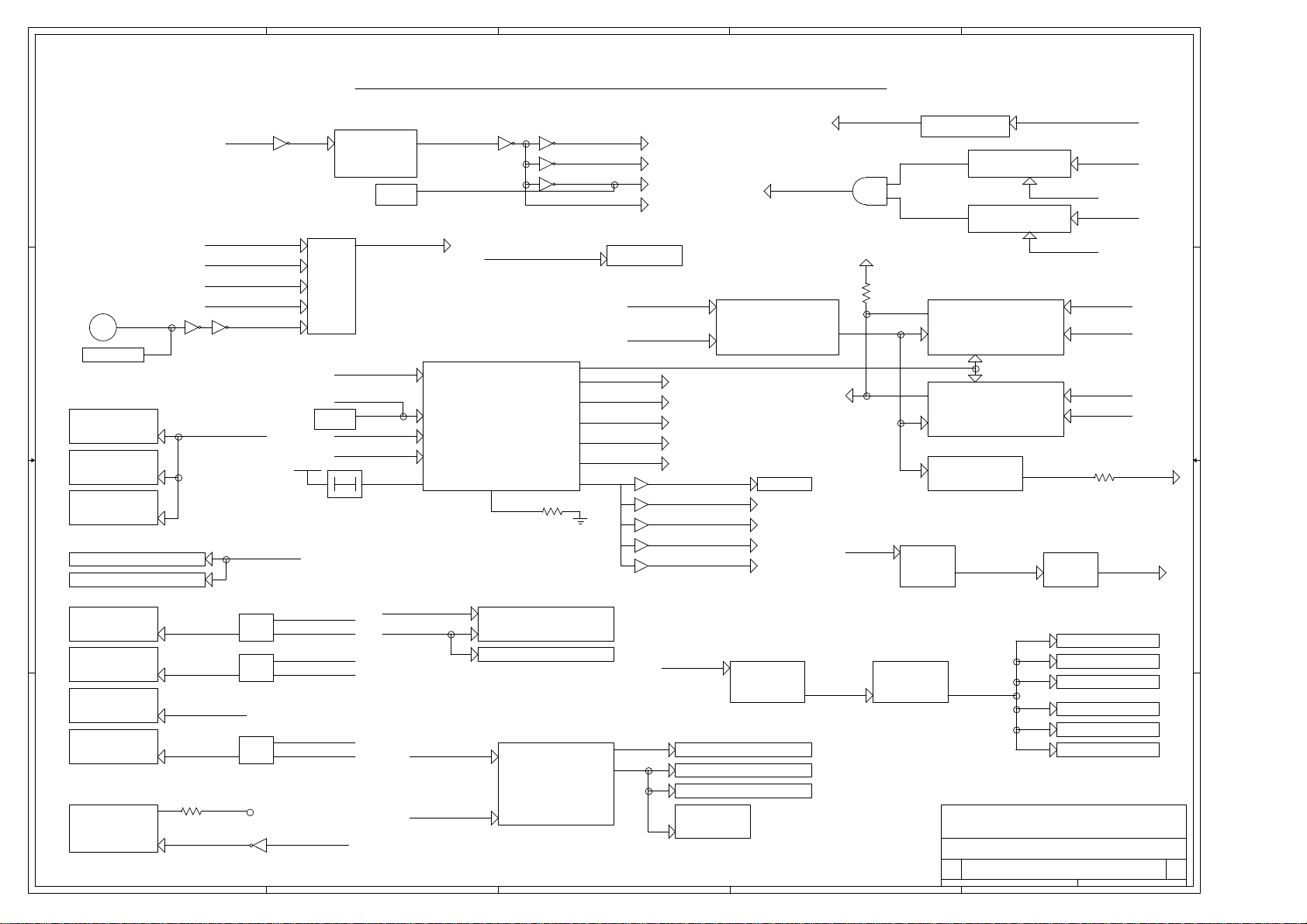

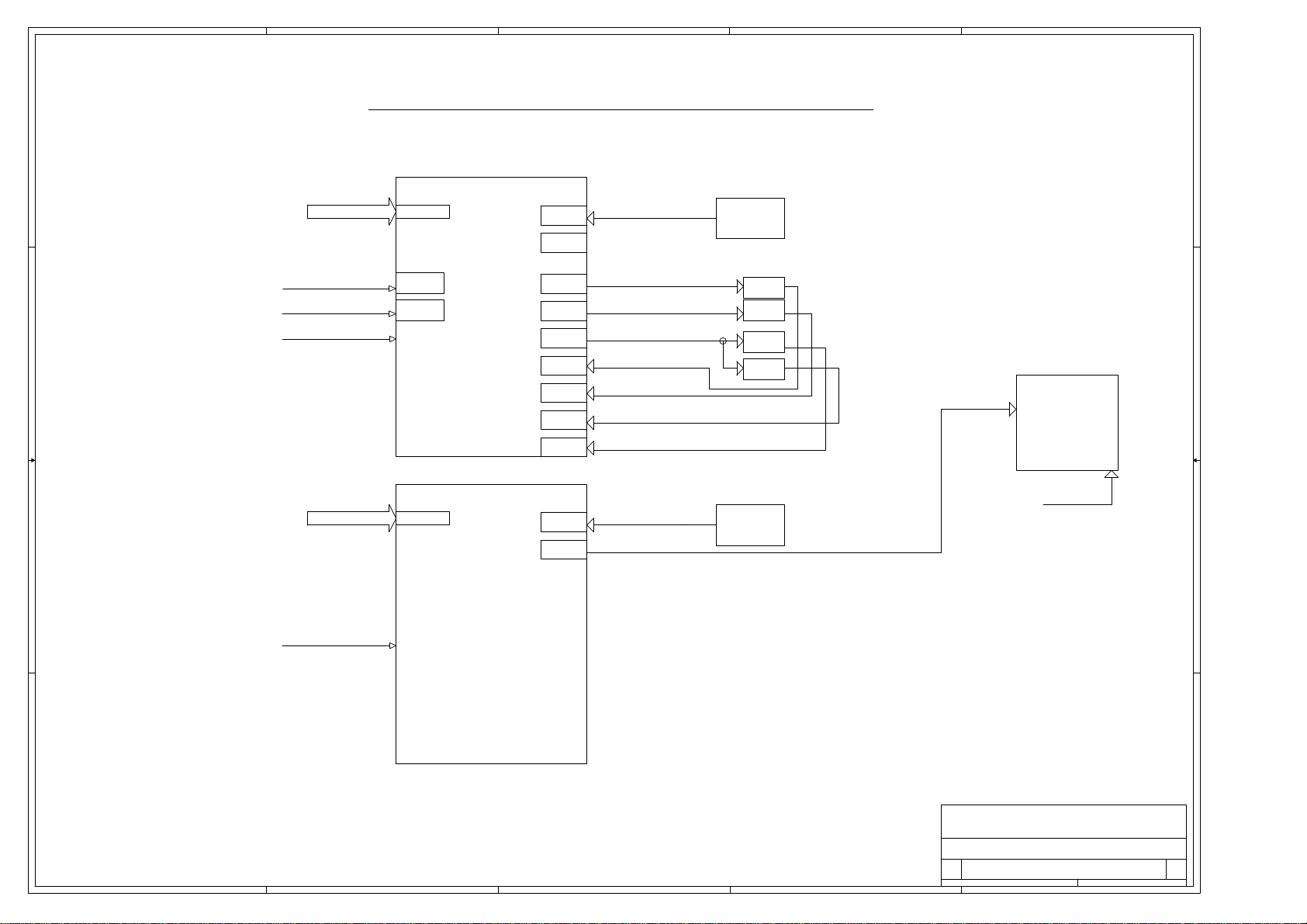

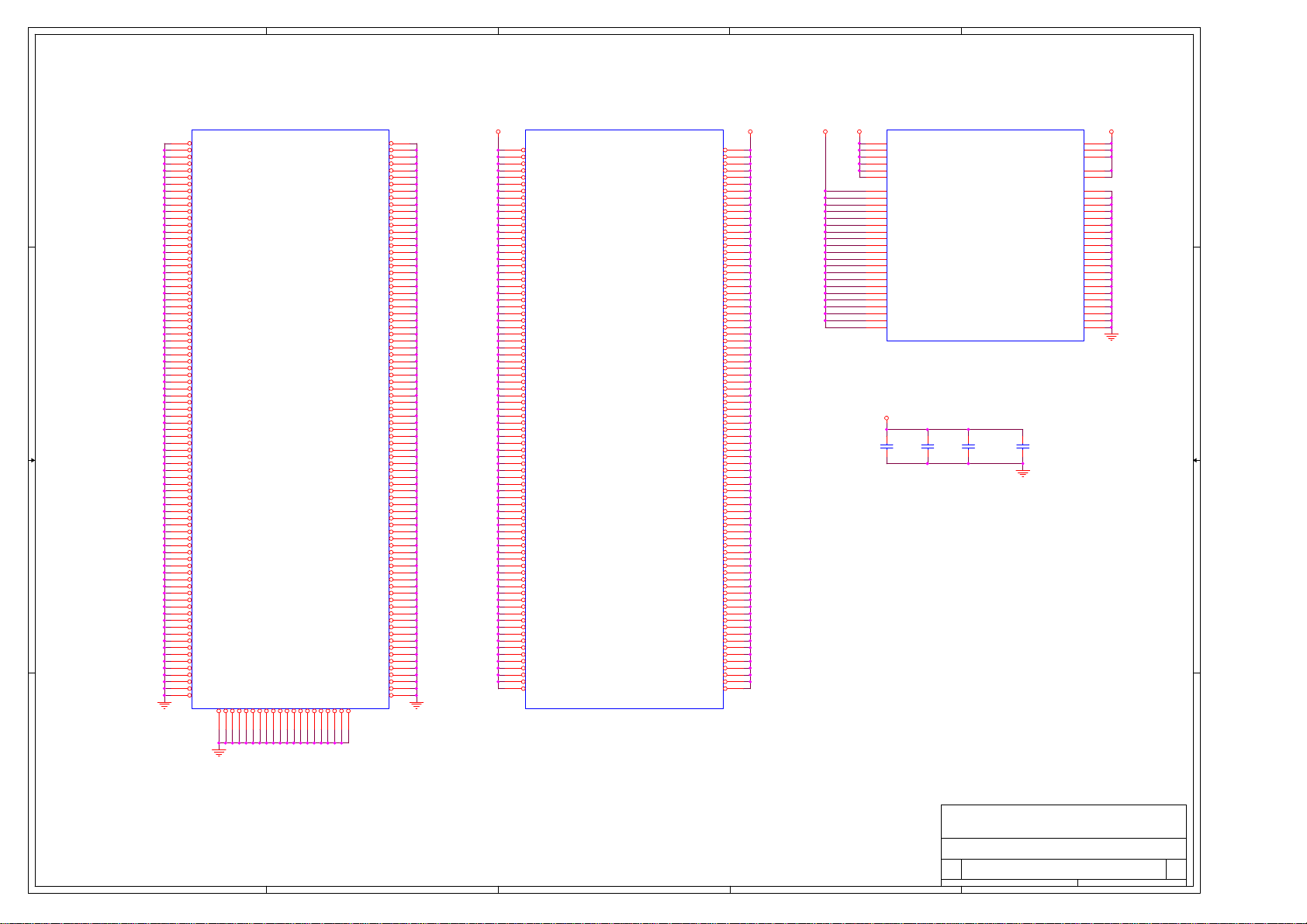

MS-9151 SYSTEM RESET BLOCK DIAGRAM

DBR_N

CPU1_SKTOCC_N, CPU BSELSSB_VTT_PWRGD BSEL comparator

CPU0 VRD

OUTEN

SB_VTT_PWRGD

CPU1 VRD

OUTEN

SB_VTT_PWRGD

VIDPWRGD

PWRGOOD

PWRGOOD

VIDPWRGD

DBR_RESET_N

Voltage

Translation

Logic

CPU0_VID[5:0]

CPU1_VID[5:0]

VID_PWRGD

CPU_PWR_GD

CPU_PWR_GD

VID_PWRGD

0-ohm

VID_PWRGD

FP_RESET_N

D D

On-board Power switch

( Debug Only )

C C

Front Panel

FWH

JSCSI_BP1

RST_N

RST_N

SLP_S3_N

WAKE_N ICH_PWRBTN_N

PME_N

SLP_S4_N

GPIO_WOL_EN_N

FP_PWRBTN_NFP_BTN_N

PCIRST_BUFF3_N

A

B

C

D

E

ASR

3.3V STBY

DAL16V6

B B

PCI 32 (SLOT # 2) RST_N

PCI 32 (SLOT # 3) RST_N

PCIRST_BUFF1_N

PWR_OKPS_ON_N PS_PWR_GDPSON_N SYS_PWR_GD_3_3V

Power Supply

JRST1

O

Note:

O=(AB+C+D)(E)

ICH_PWRBTN_N

FP_RESET_N

CPU_VRD_PWR_GD

SYS_PWR_GD_3_3V

RSM_RST_N

PWRBTN_N

SYS_RESET_N

VRMPWRGD

PWROK

RSMRST_N

PS_PWR_GD_N

ICH5

Sus_STAT_N

CPU_PWR_GD

LAN_RST_N

RSM_RST_N

SYS_PWR_GD_BUFF1

FP_RESET_N

PS_PWR_GD_N

INI T_N

SLP_S3_N

SLP_S4_N

SLP_S5_N

PCIRST_N

10K

5V Dual Source

Switch Circuit

SB_CPU_INIT_N

SLP_S3_N

SLP_S4_N

SLP_S5_N

SUS_STAT_N

CPU_PWR_GD

SYS_PWR_GD_3_3V

PCIRST_BUFF2_N

IDE_RSTDRV_N

PCIRST_BUFF1_N

PCIRST_BUFF2_N

PCIRST_BUFF3_N

PCIRST_BUFF4_N

PWRGD

RSTIN_N

CPU_VRD_PWR_GD

TUMWATER

IDE

3.3V

CPURST_N

VTT_EN

VTT_EN

circuit

CPU0_PWRGD

CPU1_PWRGD

VTTEN

RESET_N

VTTEN

RESET_N

RESET_N

ENABLE

1.2V Reg

PWRGD

PWR_GD

PWR_GD

Nocona

(CPU0)

INIT_N

INIT_N

Nocona

(CPU1)

ITP_XDP

SB_VTT_PWRGD

RADEON

7000M

1394

SIO

BCM5721

A A

RST_N

RST_N

LRESET_N

LAN_DIS_N

PWRDWN_N

1394_PCIRST_N

PCIRST_BUFF2_N

LAN_ENABLE GPIO_LAN_DIS_N

4.7K-ohm

AND

LOGIC

AND

LOGIC

AND

LOGIC

VCC3_CLK

PCIRST_BUFF1_N

GPIO_VGA_DIS_NVGA_PCIRST_N

PCIRST_BUFF1_N

GPIO_1394_DIS_N

PCIRST_BUFF2_N

CK409B

CK409B_PWR_GD_N

5

SB_VTT_PWRGDVTT_PWRGD_N

FP_PWRBTN_N

SYS_PWR_GD_BUFF1

SYS_PWR_GD_3_3V

PCIRST_BUFF4_N

4

POWER_ON_J

RESET

PWRDG

PWROK

RST IN_N

JMGT1

PCI EXPRESS (SLOT # 1)

PB_PCIRST_N

PA_PCIRST_N

PXH

RESET_N

PS_PWR_GD

RST_N PCI-X 133MHZ (SLOT # 4)

RST_N PCI-X 100MHZ (SLOT # 6)

SCSI Controller

PRST_N

3

ENABLE

1.5V D2D

PWRGD_1_5V

PWR_GD

PCI-X 100MHZ (SLOT # 5)RST_N

2

1.8V D2D

ENABLE

PWRGD_1_8V

PWR_GD

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System Reset Block Diagram

Size Document Number Rev

MS-9151-100

Date: Sheet of

RESET_N

RESET_N

RESET_N

RESET_N

DIMM # A1

DIMM # A2

DIMM # A3

DIMM # B1RESET_N

DIMM # B2

DIMM # B3

5 56Wednesday, June 02, 2004

1

100Custom

Page 6

5

4

3

2

1

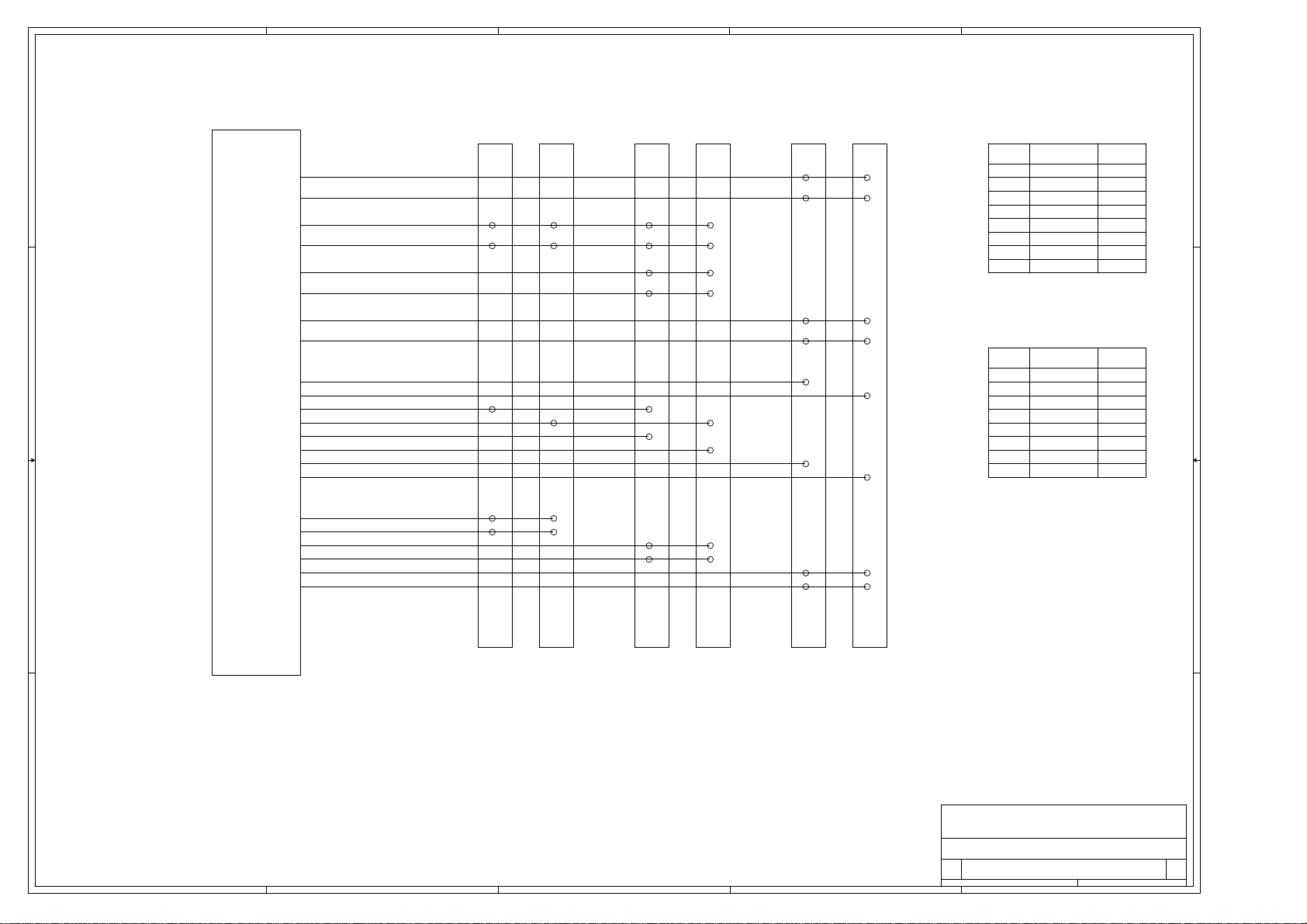

MS-9151 SMBus Block Diagram

D D

ICH5-R

* Slave Address = 0X44

3.3V STBY

R

ICH_SMB*

HM ADT7463

* Slave Address = 0X58

3.3V

DDR CHA DDR CHB

DIMM A1

R

* Slave Address = 0XA0 * Slave Address = 0XA8

JMGT1

* Slave Address = ???

C C

BCM

DIMM A2

DIMM A3

5721 GbE

* Slave Address = ???

3.3V

PCA9545

SMBus Repeater

2 0

3

* Slave Address = 0XE0

B B

1

DIMM_SMB*

MCH_SMB*

R

TUMWATER

* Slave Address = 0X60

* Slave Address = 0XC0

HM ADT7468

* Slave Address = 0X5C

PXH

* Slave Address = 0XAA* Slave Address = 0XA2

* Slave Address = 0XAC* Slave Address = 0XA4

DIMM B1

DIMM B2

DIMM B3

R

0-OHM

(EMPTY)

R

0-OHM

(EMPTY)

R

0-OHM

(EMPTY)

R

0-OHM

(EMPTY)

R

0-OHM

(EMPTY)

R

0-OHM

(EMPTY)

3.3V STBY

R

5.1K

3.3V STBY

R

5.1K

3.3V STBY

R

5.1K

3.3V STBY

R

5.1K

3.3V STBY

R

5.1K

3.3V STBY

R

5.1K

PCI-Express X16 Slot

( SLOT # 1 )

PCI 32 / 33 Slot

( SLOT # 2 )

PCI 32 / 33 Slot

( SLOT # 3 )

PCI-X 133 Slot

( SLOT # 4 )

PCI-X 100 Slot (ZCR)

( SLOT # 5 )

PCI-X 100 Slot (ZCR)

( SLOT # 6 )

Dynamic Bus Addressing for I/O Slots

CK409B

* Slave Address = 0XD2

DB800

* Slave Address = 0XDC

R

P5V3.3V

R

3.3V STBY

PCA9557PW

* Slave Address = 0X30

PWR BP

A A

IDE_RSTDRV_N

5

4

I2C_PWR

* Slave Address =

0XA0, 0XA2,

0XA6, 0X46, 0X76

Isolate Logic

3

EEPROM

* Slave Address = 0XAE

SCSI BP

I2C_DASD

* Slave Address =

0X40, 0X90, 0X9C

0XA0, 0XA4, 0XE2

2

PCA9557PW

* Slave Address = 0X32

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

System SMBus Block Diagram

Size Document Number Rev

MS-9151-100

Date: Sheet of

1

6 56Wednesday, June 02, 2004

100Custom

Page 7

5

4

3

2

1

RANK2 RANK3(/2) RANK4(/1)

D D

CS0

CS1

CS2

CS3

CS4

CS5

CS0

ODT0

CS0

ODT0

CS1

ODT1

CS0 CS0

ODT0 ODT0

CS1

ODT1

CS6

CS7

C C

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

CKE6

CKE7

CKE0

CKE0

CKE1

CKE1

CKE0

CKE0

CS1 CS1

ODT1 ODT1

CS0 CS0

ODT0 ODT0

CKE1

CKE1

CKE0

CKE0

Signal Relative to

CS0

CS1

CS2

CS3

CS4

CS5

CS6

CS7

Signal Relative to

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

CKE6

CKE7

DIMM3

DIMM3

DIMM1,2

DIMM1,2

DIMM2

DIMM2

DIMM3

DIMM3

DIMMA3

DIMMB3

DIMMA1,2

DIMMB1,2

DIMMA2

DIMMB2

DIMMA3

DIMMB3

DIMM PN

76

77

193,76

195,77

193

195

193

195

DIMM PN

171

171

52,171

52,171

52

52

52

52

CMDCLKP0

CMDCLKN0

CMDCLKP1

B B

CMDCLKN1

CMDCLKP2

p185

p186

CMDCLKN2

CMDCLKP3

p185

p186

p185p185

p186 p186

p185

p186

p185

p186

CMDCLKN3

*Separate Channel A and B

for clocks

A1 A2 A3B1 B2 B3

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

DDRII Routing Block Diagram

Size Document Number Rev

MS-9151-100

5

4

3

2

Date: Sheet of

7 56Wednesday, June 02, 2004

1

100Custom

Page 8

5

4

3

2

1

MS-9151 INTERRUPT & ERROR LOGIC DIAGRAM

D D

NOCONA

/JAYHAWK

IERR_N

SB_CPU1_IERR_N

SB_CPU0_IERR_N

( CPU0 )

MCERR_NMCERR_N

BINIT_NBINIT_N

INTRINTR

C C

F

S

B

INIT_N INIT_N

IGNNE_NIGNNE_N

NMINMI

FERR_NFERR_N

SMI_NSMI_N

SB_CPU_FERR_N

SB_CPU_IGNNE_N

SB_CPU_INIT_N

SB_CPU_INTR

ICH_CPU_SMI_N

SB_CPU_NMI

NOCONA

/JAYHAWK

( CPU1 )

SB_CPU1_IERR_N

B B

MEMORY WRITE ( MSI - TUMWATER to PROCESSOR )

SB_MCERR_N

SB_BINIT_N

MSI (UPSTREAM)

PCI Express

IERR_N

MCERR_N

BINIT_N

GTL TO 3.3V

TRANSLATION

LOGIC

GTL TO 3.3V

TRANSLATION

LOGIC

External NMI

Logic (P.52)

GPIO_NMI_N

MCH

CPU1_IERR_N

CPU0_IERR_N

IGNNE_N

INIT_N

INTR

SMI_N

GPIO40

FERR_N

MEMORY WRITE

(MSI - ICH5 TO

TUMWATER

HI 1.5

SIO

SIO_SMI_N

SIO_SMI_N

GPI2

GPI3

ICH5

GPI15

IDE IRQ14

PIRQG_N

PIRQH_N

PB_PERR_N

PB_SERR_N

PIRQA_N

PIRQB_N

PIRQC_N

PIRQD_N

PIRQG_N

PIRQH_N

PB_PERR_N

PB_SERR_N

PIRQA_N

PIRQB_N

PIRQC_N

PIRQD_N

IDE Primary

PXH PCI Bus B

Device # 1

System slot IDSEL = AD17

REQ/GNT B # 0

PXH PCI Bus A

Device # 2

System slot IDSEL = AD18

REQ/GNT B # 1

PCI-X 133 PCI-X 100 PCI-X 100 (ZCR)

A A AB B BC C CD D D

ICH5 Internal PIRQ assignment :

PIRQA-- USB1.1 Controller # 1 & 4

PIRQB-- SMBUS, AC'97, Modem, CSA

PIRQC-- USB1.1 Controller # 3, Native IDE, S-ATA

PIRQD-- USB1.1 Controller # 2

PIRQE-- LAN ( DEVICE 8 )

PIRQH-- USB2.0 Controller #1

Device # 4

IDSEL = AD20

REQ/GNT # 3

TDI

Device # 3

IDSEL = AD19

REQ/GNT # 2

VGA 1394A

PXH PCI Bus A

Device # 1

System slot IDSEL = AD17

REQ/GNT B # 0

PXH PCI Bus A

Device # 3

IDSEL = AD19 or Control logic

if MROMB card is present

REQ/GNT B # 2

Device # 1

IDSEL = AD17

REQ/GNT # 0

PCI-32 SLOT

A B C D

SCSI Controller

INTA_N INTB_N

PERR_N

SERR_N

Device # 2

IDSEL = AD18

REQ/GNT # 1

PCI-32 SLOT

A B C D

82570EI

PCI EXPRESS X 16 SLOT

A A

5

4

MSI ( UPSTREAM )

PCI

Express

MEMORY WRITE

(MSI - PXH to TUMWATER)

PCI

Express

3

PBIRQ_N (0)

PBIRQ_N (1)

PBIRQ_N (3)

PBIRQ_N (2)

PBIRQ_N (4)

PBIRQ_N (5)

PB_PERR_N

PB_SERR_N

MROMB_PRESENT_N

ENB

ENB

PXH

PB_PERR_N

PAIRQ_N (3)

PAIRQ_N (2)

PAIRQ_N (0)

PAIRQ_N (1)

2

PAIRQ_N (5)

PAIRQ_N (4)

Title

Size Document Number Rev

Date: Sheet of

PB_SERR_N

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Interrupt Routing Block Diagram

MS-9151-100

PAIRQ_N (7)

PAIRQ_N (6)

8 56Wednesday, June 02, 2004

1

100Custom

Page 9

5

4

3

2

1

MS-9151 HARDWARE MONITOR DIAGRAM

D D

ADT7468 (U39)

CPU0 VID [ 5 : 0 ]

CPU0_THERMAL_DIODE

CPU1_THERMAL_DIODE

P_VCCP0

C C

VID [ 5 : 0 ]

RTD ( 1 )

RTD ( 2 )

VCCP

THERM#

ALERT#

PWM1

PWM2

PWM3

TACH1

TACH2

TACH3

TACH4

CPU0_PROCHOT_N

CPU0

FAN4

FAN1

FAN3

FAN2

HM1_ALERT_N

GPI9

GPI10

ICH5-R

INTRUDER_N

ADT7463 (U40)

intruder switch

CPU1 VID [ 5 : 0 ]

B B

P_VCCP1

VID [ 5 : 0 ]

VCCP

THERM#

ALERT#

CPU1_PROCHOT_N

CPU1

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Hardwar Monitor Block Diagram

Size Document Number Rev

MS-9151-100

5

4

3

2

Date: Sheet of

9 56Wednesday, June 02, 2004

1

100Custom

Page 10

5

4

3

2

1

CPU1A

IN

SB_BPRI_N12,17

SB_CPU0_BREQ_23_N

SB_BREQ_N1

SB_BREQ_N0

SB_CPURST_N

IN

D D

C C

B B

SB_RS_N212,17

IN

SB_RS_N112,17

IN

SB_RS_N012,17

IN

SB_RSP_N12,17

SB_CPU_A20M_N

SB_CPU_IGNNE_N

SB_CPU_INIT_N

NMI

SB_CPU_INTR

CPU_PWR_GD

ICH_CPU_SMI_N

SB_CPU_SLP_N

SB_CPU_STPCLK_N

IN

P0_BCLK_N15

IN

P0_BCLK15

IN

ITP_TCK014

IN

ITP_TDI_P014

OUT

ITP_TDO_P014

IN

ITP_TMS12,14

IN

ITP_TRST_N12,14

CPU0_VTT_BSEL1

CPU0_VTT_BSEL0

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

PU_VCCPLL_CPU0

VTT_EN

P_VCCP_A_CPU0

AGND_CPU0

P_VTT

VID_CPU0_R548,53

VID_CPU0_R448,53

VID_CPU0_R348,53

VID_CPU0_R248,53

VID_CPU0_R148,53

VID_CPU0_R048,53

VID_PWRGD12,50

P0_VCCSENSE53

P0_VSSSENSE53

Sighting #23

D23

D10

E11

F12

D20

F21

D22

E21

C6

F27

C26

D6

G23

B24

AB7

C27

AE6

D4

W5

E24

C24

E25

A25

F24

AA28

AA29

AB28

AB29

AC29

AD28

AD29

AE30

AB3

AA3

C3

D3

AD1

AD4

AB4

B27

AA5

D26

R1 49.9R1%

0D

Y8

BPRI_N

BR3_N

BR2_N

BR1_N

BR0_N

RESET_N

RS2_N

RS1_N

RS0_N

RSP_N

A20M_N

IGNNE_N

INIT_N

LINT1_NMI

LINT0_INTR

NOCONA 1/5

PWRGOOD

SMI_N

SLP_N

STPCLK_N

BCLK1

Y4

BCLK0

TCK

TDI

TDO

TMS

TRST_N

N/C

N/C

N/C

N/C

N/C

N/C

N/C

N/C

BSEL1

BSEL0

A1

VID5

B3

VID4

VID3

VID2

E3

VID1

F3

VID0

B1

VIDPWRGD

VCCPLL

E1

VTTEN

VCCIOPLL

VCCA

VCCSENSE

VSSA

VSSSENSE

SOCKET_604

Put the VREF & VCCA in the Cavity

775 mV

R8

90.9R1%

Trace Width >= 12 mil

C1

C1U16X50805

FERR_N/PBE_N

THERMTRIP_N

PROCHOT_N

BOOT_SELECT

FORCEPR_N

OPTIMIZED_COMPAT_N

84.5R1% -->90.9R1%

R19 49.9R1%

0D

84.5R1% -->90.9R1%

Place close to pin AD4

L1 10U150m_1210

P_VTT

A A

L2 10U150m_1210

R22

90.9R1%

775 mV

Trace Width >= 12 mil

C4

C1U16X50805

Trace Width >= 12 mil

P_VCCP_A_CPU0

C7

C22U16Y1210

AGND_CPU0

Place between

pin AB4 & AA5

Place close to pin AB4

Trace Width >= 12 mil

PU_VCCPLL_CPU0

C8

X_C4.7U10Y1206

C9

X_C0.1U16X

4

Notes:

Value X_ means non-stuff

R42 X_0R

P1V5

5

12

+

EC1

X_CD470U6.3EL11

D19

ADS_N

F11

BINIT_N

F20

BNR_N

E4

BPM5_N

E8

BPM4_N

F5

BPM3_N

E7

BPM2_N

F8

BPM1_N

F6

BPM0_N

F18

DBSY_N

C23

DEFER_N

E18

DRDY_N

E22

HIT_N

A23

HITM_N

E19

TRDY_N

A17

LOCK_N

D7

MCERR_N

E5

IERR_N

E27

F26

B25

AC28

COMP3

D25

COMP2

E16

COMP1

AD16

COMP0

F9

GTLREF3

F23

GTLREF2

W9

GTLREF1

W23

GTLREF0

B5

ODTEN

A3

SKTOCC_N

W6

TESTHI0

W7

TESTHI1

W8

TESTHI2

Y6

TESTHI3

AA7

TESTHI4

AD5

TESTHI5

AE5

TESTHI6

A26

TESTHI7

Y29

TESTHI8

A16

TEST_BUS

W3

RESERVED

Y3

RESERVED

AC1

RESERVED

AE15

RESERVED

AE16

RESERVED

AE29

RESERVED

AE28

RESERVED

AE4

SMB_PRT

Y28

THERMDC

Y27

THERMDA

G7

A15

AC30

SLEW_CTRL

C1

VREF_P_VTT_CPU0_0

C2

C220P50N

VREF_P_VTT_CPU0_3

C5

C220P50N

C10

X_C0.1U16X

SB_CPU0_IERR_N

SB_CPU_FERR_N

SB_CPU_THERMTRIP_N

SB_CPU0_PROCHOT_N

PU_COMP3_CPU0

PU_COMP2_CPU0

PD_COMP1_CPU0

PD_COMP0_CPU0

VREF_P_VTT_CPU0_3

VREF_P_VTT_CPU0_0

PU_ODTEN_CPU0

CPU0_SKTOCC_N

PU_CPU0_0

PU_CPU0_1

PU_CPU0_2

PU_CPU0_3

PU_CPU0_4

PU_CPU0_5

PU_CPU0_6

PU_CPU0_7

PU_CPU0_8

PU_BOOT_SELECT_CPU0

SB_CPU0_FORCEPR_N

CPU0_SLEW_CTRL

CPU0_OPTIM_COMPAT_CTRL

C3

C220P50N

C6

C220P50N

BI

SB_ADS_N 12,17

BI

SB_BINIT_N 12,17

BI

SB_BNR_N 12,17

BI

CPU_BPM_N5 12,14

BI

CPU_BPM_N4 12,14

BI

CPU_BPM_N3 12,14

BI

CPU_BPM_N2 12,14

BI

CPU_BPM_N1 12,14

BI

CPU_BPM_N0 12,14

BI

SB_DBSY_N 12,17

IN

SB_DEFER_N 12,17

BI

SB_DRDY_N 12,17

BI

SB_HIT_N 12,17

BI

SB_HITM_N 12,17

IN

SB_TRDY_N 12,17

BI

SB_LOCK_N 12,17

BI

SB_MCERR_N 12,17

BI

SB_CPU0_CPU1_TESTBUS 12

OUT

CPU0_THERMDC 48

OUT

CPU0_THERMDA 48

P_VTT

P_VTT

3

R2 220R

R4 220R

R6 220R

R9 220R

R11 220R

R12 220R

R13 220R

R14 220R

R15 51R

R17 510R

R18 510R

R21 X_51R

R23 51R

R1198 51R

R1199 51R

R24 51R

R25 330R

R28 X_51R

R29 X_51R

R31 51R

R32 51R

R34 51R

R35 51R

R36 51R

R37 51R

R38 51R

R39 X_51R

R40 X_51R

R41 X_51R

SB_D_N6312,17

SB_D_N6212,17

SB_D_N6112,17

SB_D_N6012,17

SB_D_N5912,17

SB_D_N5812,17

SB_D_N5712,17

SB_D_N5612,17

SB_D_N5512,17

SB_D_N5412,17

SB_D_N5312,17

SB_D_N5212,17

SB_D_N5112,17

SB_D_N5012,17

SB_D_N4912,17

SB_D_N4812,17

SB_D_N4712,17

SB_D_N4612,17

SB_D_N4512,17

SB_D_N4412,17

SB_D_N4312,17

SB_D_N4212,17

SB_D_N4112,17

SB_D_N4012,17

SB_D_N3912,17

SB_D_N3812,17

SB_D_N3712,17

SB_D_N3612,17

SB_D_N3512,17

SB_D_N3412,17

SB_D_N3312,17

SB_D_N3212,17

SB_D_N3112,17

SB_D_N3012,17

SB_D_N2912,17

SB_D_N2812,17

SB_D_N2712,17

SB_D_N2612,17

SB_D_N2512,17

SB_D_N2412,17

SB_D_N2312,17

SB_D_N2212,17

SB_D_N2112,17

SB_D_N2012,17

SB_D_N1912,17

SB_D_N1812,17

SB_D_N1712,17

SB_D_N1612,17

SB_D_N1512,17

SB_D_N1412,17

SB_D_N1312,17

SB_D_N1212,17

SB_D_N1112,17

SB_D_N1012,17

SB_D_N912,17

SB_D_N812,17

SB_D_N712,17

SB_D_N612,17

SB_D_N512,17

SB_D_N412,17

SB_D_N312,17

SB_D_N212,17

SB_D_N112,17

SB_D_N012,17

SB_CPU_A20M_N

SB_CPU_SLP_N

NMI

SB_CPU_INTR

ICH_CPU_SMI_N

SB_CPU_INIT_N

SB_CPU_IGNNE_N

SB_CPU_STPCLK_N

SB_CPU_FERR_N VTT_EN

CPU0_VTT_BSEL0

CPU0_VTT_BSEL1

SB_CPU0_FORCEPR_N

SB_CPU0_BREQ_23_N

SB_BREQ_N0

SB_BREQ_N1

PU_ODTEN_CPU0

CPU_PWR_GD

PU_CPU0_8

PU_CPU0_7

PU_CPU0_6

PU_CPU0_5

PU_CPU0_4

PU_CPU0_3

PU_CPU0_2

PU_CPU0_1

PU_CPU0_0

PU_BOOT_SELECT_CPU0

CPU0_OPTIM_COMPAT_CTRL

CPU0_SLEW_CTRL

R43

X_0R

R44

X_51R

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

CPU1B

AB6

BI

D63_N

Y9

BI

D62_N

AA8

BI

D61_N

AC5

BI

D60_N

AC6

BI

D59_N

AE7

BI

D58_N

AD7

BI

D57_N

AC8

BI

D56_N

AB10

BI

D55_N

AA10

BI

D54_N

AA11

BI

D53_N

AB13

BI

D52_N

AB12

BI

D51_N

AC14

BI

D50_N

AA14

BI

D49_N

AA13

BI

D48_N

AC9

BI

D47_N

AD8

BI

D46_N

AD10

BI

D45_N

AE9

BI

D44_N

AC11

BI

D43_N

AE10

BI

D42_N

AC12

BI

D41_N

AD11

BI

D40_N

AD14

BI

D39_N

AD13

BI

D38_N

AB15

BI

D37_N

AD18

BI

D36_N

AE13

BI

D35_N

AC17

BI

D34_N

AA16

BI

D33_N

AB16

BI

D32_N

AB17

BI

D31_N

AD19

BI

D30_N

AD21

BI

D29_N

AE20

BI

D28_N

AE22

BI

D27_N

AC21

BI

D26_N

AC20

BI

D25_N

AA18

BI

D24_N

AC23

BI

D23_N

AE23

BI

D22_N

AD24

BI

D21_N

AC24

BI

D20_N

AE25

BI

D19_N

AD25

BI

D18_N

AC26

BI

D17_N

AE26

BI

D16_N

AA19

BI

D15_N

AB19

BI

D14_N

AB22

BI

D13_N

AB20

BI

D12_N

AA21

BI

D11_N

AA22

BI

D10_N

AB23

BI

D9_N

AB25

BI

D8_N

AB26

BI

D7_N

AA24

BI

D6_N

Y23

BI

D5_N

AD27

BI

D4_N

AA25

BI

D3_N

Y24

BI

D2_N

AA27

BI

D1_N

Y26

BI

D0_N

SOCKET_604

SB_CPU_A20M_N 12,28

SB_CPU_SLP_N 12,28

NMI 12,28

SB_CPU_INTR 12,28

ICH_CPU_SMI_N 12,28

SB_CPU_INIT_N 12,28,37

SB_CPU_IGNNE_N 12,28

SB_CPU_STPCLK_N 12,28

SB_CPU_FERR_N 12,28

CPU0_VTT_BSEL0 14

CPU0_VTT_BSEL1 14

IN

SB_CPU0_FORCEPR_N 14

BI

SB_BREQ_N0 12,17

IN

SB_BREQ_N1 12,17

IN

CPU_PWR_GD 12,28

NOCONA 2/5

P_VTT

P3V3

P3V3_STBY

P_VTT

2

C8

A35_N

C9

A34_N

A7

A33_N

A6

A32_N

B7

A31_N

C11

A30_N

D12

A29_N

E13

A28_N

B8

A27_N

A9

A26_N

D13

A25_N

E14

A24_N

C12

A23_N

B11

A22_N

B10

A21_N

A10

A20_N

F15

A19_N

D15

A18_N

D16

A17_N

C14

A16_N

C15

A15_N

A12

A14_N

B13

A13_N

B14

A12_N

B16

A11_N

A13

A10_N

D17

A9_N

C17

A8_N

A19

A7_N

C18

A6_N

B18

A5_N

A20

A4_N

A22

A3_N

B22

REQ4_N

C20

REQ3_N

C21

REQ2_N

B21

REQ1_N

B19

REQ0_N

AB9

DBI3_N

AE12

DBI2_N

AD22

DBI1_N

AC27

DBI0_N

D9

AP1_N

E10

AP0_N

AE17

DP3_N

AC15

DP2_N

AE19

DP1_N

AC18

DP0_N

F14

ADSTB1_N

F17

ADSTB0_N

Y11

DSTBP3_N

Y14

DSTBP2_N

Y17

DSTBP1_N

Y20

DSTBP0_N

Y12

DSTBN3_N

Y15

DSTBN2_N

Y18

DSTBN1_N

Y21

DSTBN0_N

R3 51R

R5 51R

R7 51R

R10 51R

R16 4.7KR

R20 X_4.7KR

R26 100R1%

R27 100R1%

R30 49.9R1%

R33 49.9R1%

SB_CPU0_IERR_N

SB_CPU0_PROCHOT_N

SB_CPU_THERMTRIP_N

SB_CPURST_N

CPU0_SKTOCC_N

PU_COMP2_CPU0

PU_COMP3_CPU0

PD_COMP0_CPU0

PD_COMP1_CPU0

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

P0 Processor & Termination

Size Document Number Rev

MS-9151-100

Date: Sheet of

BI

SB_A_N35 12,17

BI

SB_A_N34 12,17

BI

SB_A_N33 12,17

BI

SB_A_N32 12,17

BI

SB_A_N31 12,17

BI

SB_A_N30 12,17

BI

SB_A_N29 12,17

BI

SB_A_N28 12,17

BI

SB_A_N27 12,17

BI

SB_A_N26 12,17

BI

SB_A_N25 12,17

BI

SB_A_N24 12,17

BI

SB_A_N23 12,17

BI

SB_A_N22 12,17

BI

SB_A_N21 12,17

BI

SB_A_N20 12,17

BI

SB_A_N19 12,17

BI

SB_A_N18 12,17

BI

SB_A_N17 12,17

BI

SB_A_N16 12,17

BI

SB_A_N15 12,17

BI

SB_A_N14 12,17

BI

SB_A_N13 12,17

BI

SB_A_N12 12,17

BI

SB_A_N11 12,17

BI

SB_A_N10 12,17

BI

SB_A_N9 12,17

BI

SB_A_N8 12,17

BI

SB_A_N7 12,17

BI

SB_A_N6 12,17

BI

SB_A_N5 12,17

BI

SB_A_N4 12,17

BI

SB_A_N3 12,17

BI

SB_REQ_N4 12,17

BI

SB_REQ_N3 12,17

BI

SB_REQ_N2 12,17

BI

SB_REQ_N1 12,17

BI

SB_REQ_N0 12,17

BI

SB_DBI_N3 12,17

BI

SB_DBI_N2 12,17

BI

SB_DBI_N1 12,17

BI

SB_DBI_N0 12,17

BI

SB_AP_N1 12,17

BI

SB_AP_N0 12,17

BI

SB_DP_N3 12,17

BI

SB_DP_N2 12,17

BI

SB_DP_N1 12,17

BI

SB_DP_N0 12,17

BI

SB_ADSTB_N1 12,17

BI

SB_ADSTB_N0 12,17

BI

SB_DSTBP_N3 12,17

BI

SB_DSTBP_N2 12,17

BI

SB_DSTBP_N1 12,17

BI

SB_DSTBP_N0 12,17

BI

SB_DSTBN_N3 12,17

BI

SB_DSTBN_N2 12,17

BI

SB_DSTBN_N1 12,17

BI

SB_DSTBN_N0 12,17

OUT

SB_CPU0_IERR_N 14

OUT

SB_CPU_THERMTRIP_N 12,28

IN

SB_CPURST_N 12,14,17,37

OUT

VTT_EN 12,50

1

10 56Wednesday, June 02, 2004

100Custom

Page 11

5

4

3

2

1

CPU1C

L31

GND

L29

GND

L27

GND

L25

GND

L23

GND

L9

GND

D D

C C

B B

L7

L5

L3

L1

K30

K28

K26

K24

K8

K6

K4

K2

J31

J29

J27

J25

J23

J9

J7

J5

J3

J1

H30

H28

H26

H24

H8

H6

H4

H2

G31

G29

G27

G25

G9

G5

G3

G1

F30

F28

F25

F19

F13

F7

F2

E31

E29

E23

E17

E15

E9

D30

D28

D27

D21

D11

D5

D2

C31

C29

C25

C19

C13

C7

B30

B28

B23

B17

B15

B9

B2

A31

A29

A27

A21

A11

SOCKET_604

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

NOCONA 3/5

GND

GND

GND

GND

GND

GND

GND

GN1

GN2

GN3

GN4

GN5

GN6

GN7

GN8

GND

GN9

GND

GND

GN10

GND

GN11

GND

GN12

GND

GN13

GND

GN14

GND

GN15

GND

GN16

GND

GN17

GND

GN18

GND

GN19

GND

GN20

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

M30

M28

M26

M24

M8

M6

M4

M2

A5

P_VCCP0 P_VCCP0 P_VTT P_VTTP_VCCP0

CPU1D

L28

L26

L24

L8

L6

L4

L2

K31

K29

K27

K25

K23

K9

K7

K5

K3

K1

J30

J28

J26

J24

J8

J6

J4

J2

H31

H29

H27

H25

H23

H9

H7

H5

H3

H1

G30

G28

G26

G24

G8

G6

G4

G2

F31

F29

F22

F16

F4

F1

E30

E28

E26

E20

E6

E2

D31

D29

D24

D18

D14

D8

D1

C30

C28

C22

C16

C4

C2

B31

B29

B26

B20

B6

A30

A28

A24

A18

A14

A8

A2

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SOCKET_604

NOCONA 4/5

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

L30

AA31

AA26

AA20

AA6

AA4

AA1

Y30

Y22

Y16

Y2

W31

W29

W27

W25

W1

V30

V28

V26

V24

V8

V6

V4

V2

U31

U29

U27

U25

U23

U9

U7

U5

U3

U1

T30

T28

T26

T24

T8

T6

T4

T2

R31

R29

R27

R25

R23

R9

R7

R5

R3

R1

P30

P28

P26

P24

P8

P6

P4

P2

N31

N29

N27

N25

N23

N9

N7

N5

N3

N1

M31

M29

M27

M25

M23

M9

M7

M5

M3

M1

CPU1E

AD12

AC10

AA12

AE24

AE18

AE14

AD30

AD26

AD20

AC31

AC22

AC16

AB30

AB24

AB18

AB14

Y10

F10

E12

AE8

AE3

AD6

AD2

AC4

AC3

AB8

AB2

VTT

VTT

VTT

VTT

VTT

VTT

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SOCKET_604

NOCONA 5/5

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

C5

VTT

B4

VTT

A4

VTT

C10

VTT

B12

VTT

AE27

AE21

AE11

AE2

AD31

AD23

AD17

AD15

AD9

AD3

AC25

AC19

AC13

AC7

AC2

AB31

AB27

AB21

AB11

AB5

AB1

SIGNAL C-STEP SIGNALPin Out

CPU0_TEST1C5

CPU0_TEST0

B4 VCCFUSEPRG

P_VTT

C11

C22U16Y1210

C12

C22U16Y1210

VCCVIDPRG

C13

C0.1U16X

C14

C1U6.3X5

Nacona Processor (667 MHz) Pin Out Differences Relative to Nocana Processor (533 MHz)

Nacona Processor (667 MHz) Nocana Processor (533 MHz)Pin Out

OPTIMIZED/COMPAT#C1

E1 VSS

G7 VSS

A1 RESERVED

AD1 RESERVED

A4 VCCVID

B4, B12, C10, E12, F10,

Y10, AA12, AC10, AD12

VTTEN

VIDPWRGD

VID5

VCCPLL

VTT

VSS

VCCVIDLBC5

VCC

Jayhawk Processor (667 MHz) Pin Out Differences Relative to Nocana Processor (667 MHz)

Jayhawk Processor (667 MHz) Nacona Processor (667 MHz)Pin Out

COMP[2..3]D25, AC28

A26, Y29 RESERVED, N/C

TESTHI[7..8]

RESERVED, N/C

R45 0R

R46 0R

P_VTT

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

P0 Processor & PWR/GND/Misc.

Size Document Number Rev

MS-9151-100

5

4

3

2

Date: Sheet of

11 56Wednesday, June 02, 2004

1

100Custom

Page 12

5

4

3

2

1

CPU2A

SB_BINIT_N

SB_BNR_N

SB_HIT_N

SB_HITM_N

SB_MCERR_N

R82

0R

R83

X_51R

SB_D_N6310,17

SB_D_N6210,17

SB_D_N6110,17

SB_D_N6010,17

SB_D_N5910,17

SB_D_N5810,17

SB_D_N5710,17

SB_D_N5610,17

SB_D_N5510,17

SB_D_N5410,17

SB_D_N5310,17

SB_D_N5210,17

SB_D_N5110,17

SB_D_N5010,17

SB_D_N4910,17

SB_D_N4810,17

SB_D_N4710,17

SB_D_N4610,17

SB_D_N4510,17

SB_D_N4410,17

SB_D_N4310,17

SB_D_N4210,17

SB_D_N4110,17

SB_D_N4010,17

SB_D_N3910,17

SB_D_N3810,17

SB_D_N3710,17

SB_D_N3610,17

SB_D_N3510,17

SB_D_N3410,17

SB_D_N3310,17

SB_D_N3210,17

SB_D_N3110,17

SB_D_N3010,17

SB_D_N2910,17

SB_D_N2810,17

SB_D_N2710,17

SB_D_N2610,17

SB_D_N2510,17

SB_D_N2410,17

SB_D_N2310,17

SB_D_N2210,17

SB_D_N2110,17

SB_D_N2010,17

SB_D_N1910,17

SB_D_N1810,17

SB_D_N1710,17

SB_D_N1610,17

SB_D_N1510,17

SB_D_N1410,17

SB_D_N1310,17

SB_D_N1210,17

SB_D_N1110,17

SB_D_N1010,17

SB_D_N910,17

SB_D_N810,17

SB_D_N710,17

SB_D_N610,17

SB_D_N510,17

SB_D_N410,17

SB_D_N310,17

SB_D_N210,17

SB_D_N110,17

SB_D_N010,17

IN

OUT

OUT

BI

BI

BI

BI

BI

IN

SB_BPRI_N10,17

SB_CPU1_BREQ_23_N

SB_BREQ_N010,17

SB_BREQ_N110,17

SB_CPURST_N10,14,17,37

D D

SB_CPU_A20M_N10,28

SB_CPU_IGNNE_N10,28

SB_CPU_INIT_N10,28,37

NMI10,28

SB_CPU_INTR10,28

CPU_PWR_GD10,28

ICH_CPU_SMI_N10,28

SB_CPU_SLP_N10,28

SB_CPU_STPCLK_N10,28

C C

VID_CPU1_R548,54

VID_CPU1_R448,54

VID_CPU1_R348,54

VID_CPU1_R248,54

VID_CPU1_R148,54

VID_CPU1_R048,54

VID_PWRGD10,50

P1_VCCSENSE54

P1_VSSSENSE54

B B

IN

BI

IN

IN

SB_RS_N210,17

IN

SB_RS_N110,17

IN

SB_RS_N010,17

IN

SB_RSP_N10,17

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

P1_BCLK_N15

IN

P1_BCLK15

IN

ITP_TCK114

IN

ITP_TDI_P114

OUT

ITP_TDO_P114

IN

ITP_TMS10,14

IN

ITP_TRST_N10,14

CPU1_VTT_BSEL1

CPU1_VTT_BSEL0

OUT

OUT

OUT

OUT

OUT

OUT

IN

PU_VCCPLL_CPU1

OUT

VTT_EN10,50

P_VCCP_A_CPU1

OUT

AGND_CPU1

OUT

P_VTT

D23

D10

E11

F12

D20

F21

D22

E21

C6

F27

C26

D6

G23

B24

AB7

C27

AE6

D4

W5

E24

C24

E25

A25

F24

AA28

AA29

AB28

AB29

AC29

AD28

AD29

AE30

AB3

AA3

C3

D3

AD1

AD4

AB4

B27

AA5

D26

R47 49.9R1%

0D

Y8

BPRI_N

BR3_N

BR2_N

BR1_N

BR0_N

RESET_N

RS2_N

RS1_N

RS0_N

RSP_N

A20M_N

IGNNE_N

INIT_N

LINT1_NMI

LINT0_INTR

NOCONA 1/5

PWRGOOD

SMI_N

SLP_N

STPCLK_N

BCLK1

Y4

BCLK0

TCK

TDI

TDO

TMS

TRST_N

N/C

N/C

N/C

N/C

N/C

N/C

N/C

N/C

BSEL1

BSEL0

A1

VID5

B3

VID4

VID3

VID2

E3

VID1

F3

VID0

B1

VIDPWRGD

VCCPLL

E1

VTTEN

VCCIOPLL

VCCA

VCCSENSE

VSSA

VSSSENSE

SOCKET_604

Put the VREF & VCCA in the Cavity

754 mV

R53

84.5R1%

Trace Width >= 12 mil

C15

C1U16X50805

FERR_N/PBE_N

THERMTRIP_N

PROCHOT_N

BOOT_SELECT

FORCEPR_N

OPTIMIZED_COMPAT_N

64.9R1% -->49.9R1%

R63 49.9R1%

0D

64.9R1% -->49.9R1%

Place close to pin AD4

L3 10U150m_1210

P_VTT

P1V5

L4 10U150m_1210

Place close to pin AB4

R84 X_0R

A A

Notes:

Value X_ means non-stuff

5

R67

84.5R1%

12

+

EC2

X_CD470U6.3EL11

754 mV

Trace Width >= 12 mil

C23

C1U16X50805

Trace Width >= 12 mil

P_VCCP_A_CPU1

C26

C22U16Y1210

AGND_CPU1

Trace Width >= 12 mil

PU_VCCPLL_CPU1

C27

X_C4.7U10Y1206

4

Place between

pin AB4 & AA5

C28

X_C0.1U16X

ADS_N

BINIT_N

BNR_N

BPM5_N

BPM4_N

BPM3_N

BPM2_N

BPM1_N

BPM0_N

DBSY_N

DEFER_N

DRDY_N

HIT_N

HITM_N

TRDY_N

LOCK_N

MCERR_N

IERR_N

COMP3

COMP2

COMP1

COMP0

GTLREF3

GTLREF2

GTLREF1

GTLREF0

ODTEN

SKTOCC_N

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TEST_BUS

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

SMB_PRT

THERMDC

THERMDA

SLEW_CTRL

C16

C220P50N

C24

C220P50N

C29

X_C0.1U16X

D19

SB_BINIT_N

F11

SB_BNR_N

F20

E4

E8

F5

E7

F8

F6

F18

C23

E18

SB_HIT_N

E22

SB_HITM_N

A23

E19

A17

SB_MCERR_N

D7

SB_CPU1_IERR_N

E5

E27

F26

SB_CPU1_PROCHOT_N

B25

PU_COMP3_CPU1

AC28

PU_COMP2_CPU1

D25

PD_COMP1_CPU1

E16

PD_COMP0_CPU1

AD16

VREF_P_VTT_CPU1_3

F9

F23

VREF_P_VTT_CPU1_0

W9

W23

PD_ODTEN_CPU1

B5

CPU1_SKTOCC_N

A3

PU_CPU1_0

W6

PU_CPU1_1

W7

PU_CPU1_2

W8

PU_CPU1_3

Y6

PU_CPU1_4

AA7

PU_CPU1_5

AD5

PU_CPU1_6

AE5

PU_CPU1_7

A26

PU_CPU1_8

Y29

A16

W3

Y3

AC1

AE15

AE16

AE29

AE28

AE4

Y28

Y27

PU_BOOT_SELECT_CPU1

G7

SB_CPU1_FORCEPR_N

A15

CPU1_SLEW_CTRL

AC30

CPU1_OPTIM_COMPAT_CTRL

C1

VREF_P_VTT_CPU1_0

C17

C220P50N

VREF_P_VTT_CPU1_3

C25

C220P50N

BI

SB_ADS_N 10,17

BI

CPU_BPM_N5 10,14

BI

CPU_BPM_N4 10,14

BI

CPU_BPM_N3 10,14

BI

CPU_BPM_N2 10,14

BI

CPU_BPM_N1 10,14

BI

CPU_BPM_N0 10,14

BI

SB_DBSY_N 10,17

IN

SB_DEFER_N 10,17

BI

SB_DRDY_N 10,17

IN

SB_TRDY_N 10,17

BI

SB_LOCK_N 10,17

OUT

SB_CPU_FERR_N 10,28

OUT

SB_CPU_THERMTRIP_N 10,28

BI

SB_CPU0_CPU1_TESTBUS 10

OUT

CPU1_THERMDC 48

OUT

CPU1_THERMDA 48

P_VTT

R48 51R

R50 51R

R54 510R

R55 510R

R56 39R

R58 39R

R59 39R

R60 39R

R61 39R

R64 51R

R65 51R

R66 51R

R68 51R

R70 51R

R71 51R

R73 51R

R74 51R

R76 51R

R77 X_51R

R78 X_51R

R79 X_51R

R80 51R

3

SB_CPU1_FORCEPR_N

SB_CPU1_BREQ_23_N

CPU1_VTT_BSEL0

CPU1_VTT_BSEL1

C18 C47P50N

C19 C47P50N

C20 C47P50N

C21 C47P50N

C22 C47P50N

PU_CPU1_8

PU_CPU1_7

PU_CPU1_6

PU_CPU1_5

PU_CPU1_4

PU_CPU1_3

PU_CPU1_2

PU_CPU1_1

PU_CPU1_0

PU_BOOT_SELECT_CPU1

CPU1_OPTIM_COMPAT_CTRL

CPU1_SLEW_CTRL

SB_CPU0_CPU1_TESTBUS

R81

X_100R

CPU2B

AB6

BI

D63_N

Y9

BI

D62_N

AA8

BI

D61_N

AC5

BI

D60_N

AC6

BI

D59_N

AE7

BI

D58_N

AD7

BI

D57_N

AC8

BI

D56_N

AB10

BI

D55_N

AA10

BI

D54_N

AA11

BI

D53_N

AB13

BI

D52_N

AB12

BI

D51_N

AC14

BI

D50_N

AA14

BI

D49_N

AA13

BI

D48_N

AC9

BI

D47_N

AD8

BI

D46_N

AD10

BI

D45_N

AE9

BI

D44_N

AC11

BI

D43_N

AE10

BI

D42_N

AC12

BI

D41_N

AD11

BI

D40_N

AD14

BI

D39_N

AD13

BI

D38_N

AB15

BI

D37_N

AD18

BI

D36_N

AE13

BI

D35_N

AC17

BI

D34_N

AA16

BI

D33_N

AB16

BI

D32_N

AB17

BI

D31_N

AD19

BI

D30_N

AD21

BI

D29_N

AE20

BI

D28_N

AE22

BI

D27_N

AC21

BI

D26_N

AC20

BI

D25_N

AA18

BI

D24_N

AC23

BI

D23_N

AE23

BI

D22_N

AD24

BI

D21_N

AC24

BI

D20_N

AE25

BI

D19_N

AD25

BI

D18_N

AC26

BI

D17_N

AE26

BI

D16_N

AA19

BI

D15_N

AB19

BI

D14_N

AB22

BI

D13_N

AB20

BI

D12_N

AA21

BI

D11_N

AA22

BI

D10_N

AB23

BI

D9_N

AB25

BI

D8_N

AB26

BI

D7_N

AA24

BI

D6_N

Y23

BI

D5_N

AD27

BI

D4_N

AA25

BI

D3_N

Y24

BI

D2_N

AA27

BI

D1_N

Y26

BI

D0_N

SOCKET_604

SB_CPU1_FORCEPR_N 14

CPU1_VTT_BSEL0 14

CPU1_VTT_BSEL1 14

SB_BINIT_N 10,17

SB_BNR_N 10,17

SB_HIT_N 10,17

SB_HITM_N 10,17

SB_MCERR_N 10,17

NOCONA 2/5

P_VTT

P3V3_STBY

2

C8

A35_N

C9

A34_N

A7

A33_N

A6

A32_N

B7

A31_N

C11

A30_N

D12

A29_N

E13

A28_N

B8

A27_N

A9

A26_N

D13

A25_N

E14

A24_N

C12

A23_N

B11

A22_N

B10

A21_N

A10

A20_N

F15

A19_N

D15

A18_N

D16

A17_N

C14

A16_N

C15

A15_N

A12

A14_N

B13

A13_N

B14

A12_N

B16

A11_N

A13

A10_N

D17

A9_N

C17

A8_N

A19

A7_N

C18

A6_N

B18

A5_N

A20

A4_N

A22

A3_N

B22

REQ4_N

C20

REQ3_N

C21

REQ2_N

B21

REQ1_N

B19

REQ0_N

AB9

DBI3_N

AE12

DBI2_N

AD22

DBI1_N

AC27

DBI0_N

D9

AP1_N

E10

AP0_N

AE17

DP3_N

AC15

DP2_N

AE19

DP1_N

AC18

DP0_N

F14

ADSTB1_N

F17

ADSTB0_N

Y11

DSTBP3_N

Y14

DSTBP2_N

Y17

DSTBP1_N

Y20

DSTBP0_N

Y12

DSTBN3_N

Y15

DSTBN2_N

Y18

DSTBN1_N

Y21

DSTBN0_N

R49 51R

R51 51R

R1140 100R1%

R1141 100R1%

R62 4.7KR

R69 49.9R1%

R72 49.9R1%

R75 51R

SB_CPU1_IERR_N

SB_CPU1_PROCHOT_N

PU_COMP2_CPU1

PU_COMP3_CPU1

CPU1_SKTOCC_N

PD_COMP0_CPU1

PD_COMP1_CPU1

PD_ODTEN_CPU1

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

P1 Processor & Termination

Size Document Number Rev

MS-9151-100

Date: Sheet of

OUT

SB_CPU1_IERR_N 14

OUT

CPU1_SKTOCC_N 47,49

BI

SB_A_N35 10,17

BI

SB_A_N34 10,17

BI

SB_A_N33 10,17

BI

SB_A_N32 10,17

BI

SB_A_N31 10,17

BI

SB_A_N30 10,17

BI

SB_A_N29 10,17

BI

SB_A_N28 10,17

BI

SB_A_N27 10,17

BI

SB_A_N26 10,17

BI

SB_A_N25 10,17

BI

SB_A_N24 10,17

BI

SB_A_N23 10,17

BI

SB_A_N22 10,17

BI

SB_A_N21 10,17

BI

SB_A_N20 10,17

BI

SB_A_N19 10,17

BI

SB_A_N18 10,17

BI

SB_A_N17 10,17

BI

SB_A_N16 10,17

BI

SB_A_N15 10,17

BI

SB_A_N14 10,17

BI

SB_A_N13 10,17

BI

SB_A_N12 10,17

BI

SB_A_N11 10,17

BI

SB_A_N10 10,17

BI

SB_A_N9 10,17

BI

SB_A_N8 10,17

BI

SB_A_N7 10,17

BI

SB_A_N6 10,17

BI

SB_A_N5 10,17

BI

SB_A_N4 10,17

BI

SB_A_N3 10,17

BI

SB_REQ_N4 10,17

BI

SB_REQ_N3 10,17

BI

SB_REQ_N2 10,17

BI

SB_REQ_N1 10,17

BI

SB_REQ_N0 10,17

BI

SB_DBI_N3 10,17

BI

SB_DBI_N2 10,17

BI

SB_DBI_N1 10,17

BI

SB_DBI_N0 10,17

BI

SB_AP_N1 10,17

BI

SB_AP_N0 10,17

BI

SB_DP_N3 10,17

BI

SB_DP_N2 10,17

BI

SB_DP_N1 10,17

BI

SB_DP_N0 10,17

BI

SB_ADSTB_N1 10,17

BI

SB_ADSTB_N0 10,17

BI

SB_DSTBP_N3 10,17

BI

SB_DSTBP_N2 10,17

BI

SB_DSTBP_N1 10,17

BI

SB_DSTBP_N0 10,17

BI

SB_DSTBN_N3 10,17

BI

SB_DSTBN_N2 10,17

BI

SB_DSTBN_N1 10,17

BI

SB_DSTBN_N0 10,17

1

12 56Wednesday, June 02, 2004

100Custom

Page 13

5

CPU2C

D D

C C

B B

L31

GND

L29

GND

L27

GND

L25

GND

L23

GND

L9

GND

L7

GND

L5

GND

L3

GND

L1

GND

K30

GND

K28

GND

K26

GND

K24

GND

K8

GND

K6

GND

K4

GND

K2

GND

J31

GND

J29

GND

J27

GND

J25

GND

J23

GND

J9

GND

J7

GND

J5

GND

J3

GND

J1

GND

H30

GND

H28

GND

H26

GND

H24

GND

H8

GND

H6

GND

H4

GND

H2

GND

G31

GND

G29

GND

G27

GND

G25

GND

G9

GND

G5

GND

G3

GND

G1

GND

F30

GND

F28

GND

F25

GND

F19

GND

F13

GND

F7

GND

F2

GND

E31

GND

E29

GND

E23

GND

E17

GND

E15

GND

E9

GND

D30

GND

D28

GND

D27

GND

D21

GND

D11

GND

D5

GND

D2

GND

C31

GND

C29

GND

C25

GND

C19

GND

C13

GND

C7

GND

B30

GND

B28

GND

B23

GND

B17

GND

B15

GND

B9

GND

B2

GND

A31

GND

A29

GND

A27

GND

A21

GND

A11

GND

SOCKET_604

NOCONA 3/5

GND

GND

GND

GND

GND

GND

GND

GN1

GN2

GN3

GN4

GN5

GN6

GN7

GN8

GND

GN9

GND

GND

GN10

GND

GN11

GND

GN12

GND

GN13

GND

GN14

GND

GN15

GND

GN16

GND

GN17

GN18

GND

GND

GN19

GND

GN20

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

4

P_VCCP1 P_VCCP1 P_VTT P_VTTP_VCCP1

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

M30

M28

M26

M24

M8

M6

M4

M2

A5

L28

L26

L24

L8

L6

L4

L2

K31

K29

K27

K25

K23

K9

K7

K5

K3

K1

J30

J28

J26

J24

J8

J6

J4

J2

H31

H29

H27

H25

H23

H9

H7

H5

H3

H1

G30

G28

G26

G24

G8

G6

G4

G2

F31

F29

F22

F16

F4

F1

E30

E28

E26

E20

E6

E2

D31

D29

D24

D18

D14

D8

D1

C30

C28

C22

C16

C4

C2

B31

B29

B26

B20

B6

A30

A28

A24

A18

A14

A8

A2

CPU2D

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SOCKET_604

3

NOCONA 4/5

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

L30

AA31

AA26

AA20

AA6

AA4

AA1

Y30

Y22

Y16

Y2

W31

W29

W27

W25

W1

V30

V28

V26

V24

V8

V6

V4

V2

U31

U29

U27

U25

U23

U9

U7

U5

U3

U1

T30

T28

T26

T24

T8

T6

T4

T2

R31

R29

R27

R25

R23

R9

R7

R5

R3

R1

P30

P28

P26

P24

P8

P6

P4

P2

N31

N29

N27

N25

N23

N9

N7

N5

N3

N1

M31

M29

M27

M25

M23

M9

M7

M5

M3

M1

2

CPU2E

AD12

VTT

AC10

AA12

AE24

AE18

AE14

AD30

AD26

AD20

AC31

AC22

AC16

AB30

AB24

AB18

AB14

Y10

F10

E12

AE8

AE3

AD6

AD2

AC4

AC3

AB8

AB2

VTT

VTT

VTT

VTT

VTT

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

SOCKET_604

P_VTT

C30

C0.1U16X

NOCONA 5/5

C31

C32

C1U6.3X5

C22U16Y1210

C33

C22U16Y1210

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

1

C5

VTT

B4

VTT

A4

VTT

C10

VTT

B12

VTT

AE27

AE21

AE11

AE2

AD31

AD23

AD17

AD15

AD9

AD3

AC25

AC19

AC13

AC7

AC2

AB31

AB27

AB21

AB11

AB5

AB1

A A

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

P1 Processor & PWR/GND/Misc.

Size Document Number Rev

MS-9151-100

5

4

3

2

Date: Sheet of

13 56Wednesday, June 02, 2004

1

100Custom

Page 14

5

D D

SB_CPURST_N10,12,17,37

CPU_BPM_N510,12

CPU_BPM_N410,12

CPU_BPM_N310,12

CPU_BPM_N210,12

CPU_BPM_N110,12

CPU_BPM_N010,12

C C

SB_CPU0_IERR_N10

B B

GPIO_CPU0_FORCEPR_N28

A A

Notes:

Value X_ means non-stuff

5

Place R? at the place where the

HCPURST# singal starts to branch

IN

ITP_BCLK_N15

IN

ITP_BCLK15

IN

IN

ITP_FBO

SB_CPURST_N

BI

CPU_BPM_N5

BI

CPU_BPM_N4 ITP_TDI_P0

BI

CPU_BPM_N3

BI

CPU_BPM_N2

BI

CPU_BPM_N1

BI

CPU_BPM_N0

BI

CPU_BPM_N0

CPU_BPM_N1

CPU_BPM_N2

CPU_BPM_N3

CPU_BPM_N4

CPU_BPM_N5

R1275

51R

R1128 2.7KR

R1153 4.7KR

R91 0R

BPM1_ITP

BPM0_ITP

R96 51R

R97 51R

R98 51R

R100 51R

R101 51R R106 22R

R102 51R

P3V3

R1127

1KR

Q119

B

N-MMBT3904

E C

R1152

4.7KR

Q130

B

N-MMBT3904

E C

OUT

GPIO_CPU0_IERR 28

B

E C

4

25

23

21

19

17

15

13

11

9

7

5

3

1

P_VTT

Close to ICH5

OUT

SB_CPU0_FORCEPR_N 10

Q129

N-MMBT3904

4

GND

BPM5DR#

BCLKN

BCLKP

FBO

RESET#

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

GND

X_ITP_PORT

GPIO_CPU1_FORCEPR_N28

3

P3V3

P_VTT

R85

R86

1.5KR

X_150RJITP1

R94

X_220R

R103 22R

R105 22R

ITP_TDO_P1

ITP_TCK

ITP_TRST_N

ITP_TMS

R92 0R

R1285 39R

ITP_TCK

ITP_TCK

ITP_FBO

IN

ITP_TDO_P1 12

OUT

ITP_TRST_N 10,12

OUT

ITP_TMS 10,12

OUT

ITP_TDI_P0 10

OUT

FP_RESET_N 28,37,47,49

P_VTT

PWR

GND

TRST#

TMS

GND

DBR#

DBA#

GND

TDO

TCK

24

22

20

R90 X_0R

18

FBI

16

14

12

10

TDI

8

6

4

2

IN

ITP_TCK010

IN

ITP_TCK112

Closed to CPU

P_VTTP_VTT

R1276

51R

R1130 2.7KR

SB_CPU1_IERR_N12

IN

IN

R1150 4.7KR

P3V3

R1129

1KR

OUT

GPIO_CPU1_IERR 28

Q120

B

N-MMBT3904

E C

P3V3P3V3

OUT

E C

Q127

N-MMBT3904

SB_CPU1_FORCEPR_N 12

R1149

4.7KR

B

Q128

B

N-MMBT3904

E C

3

CPU0_VTT_BSEL010

CPU0_VTT_BSEL110

CPU1_VTT_BSEL012

CPU1_VTT_BSEL112

2

UP : 1-2

DP : 2-3

2

P_VTT

R88

closed to ITP closed to P1

JITP2

ITP_TDO_P1

1

ITP_TDO_P0

2

ITP_TDI_P1

3

D1x3-BK

ITP_TDI_P0

ITP_TRST_N

75R1%

closed to P0

R93 150R

R95 680R

closed to ITP

P3V3

R99

3.3KR

IN

IN

IN

IN

R104 100R

R108 100R

R111 100R

R126 100R

B

E C

P3V3

R107

3.3KR

B

E C

P3V3

R109

3.3KR

B

E C

P3V3

R114

3.3KR

B

E C

Micro-Star Int'l Co., Ltd.

No.69, Li-De St, Jung-He City, Taipei Hsien, Taiwan. http://www.msi.com.tw

Title

Level Shift / ITP Debug Port

Size Document Number Rev

MS-9151-100

Date: Sheet of

R89

150R

P_VTT

B

Q2

N-MMBT3904

B

Q4

N-MMBT3904

B

Q6

N-MMBT3904

B

Q8

N-MMBT3904

OUT

IN

E C

E C

E C

E C

1

ITP_TDO_P0 10

ITP_TDI_P1 12

OUT

CPU0_BSEL0 15

Q1

N-MMBT3904

OUT

CPU0_BSEL1 15

Q3

N-MMBT3904

OUT

CPU1_BSEL0 15

Q5

N-MMBT3904

OUT

CPU1_BSEL1 15

Q7

N-MMBT3904

1

14 56Wednesday, June 02, 2004

100Custom

Page 15

P3V3

5

4

3

2

1

D D

C C

B B

A A

Notes:

Value X_ means non-stuff

FB1

300L700m_250_0805

C170

C10U6.3X51206

SB_VTT_PWRGD50,53,54

P3V3

R201 1KR

R203 1KR

R205 1KR

R206 1KR

P3V3 VCC3_SRCLK

FB3 300L700m_250_0805

VCC3_CLK VCC3_SRCLK2

FB4 300L700m_250_0805

C171

C172

C0.1U16X

C173

C0.1U16X

C179

C10U6.3X51206

C182

C10U6.3X51206

VCC3_CLK

B

C0.1U16X

P3V3 VCC3_CLKA

FB2 300L700m_250_0805

VCC3_CLK VCC3_CLKB

R184 10R_0805

R1106 10KR

IN

E C

CPU0_BSEL0

CPU0_BSEL1

CPU1_BSEL0

CPU1_BSEL1

C184

C10U6.3X51206

C190

C10U6.3X51206

5

IN

CPU1_BSEL0 14

IN

CPU1_BSEL1 14

C185

C0.1U16X

C191

C0.1U16X

C186

C0.1U16X

C174

C175

C0.1U16X

C0.1U16X

C180

C0.1U16X

C183

C0.1U16X

R1105

10KR

CK409B_PWR_GD_N

Q115

N-MMBT3904

C187

C188

C0.1U16X

C0.1U16X

C1386 X_C10P50N

C1387 X_C10P50N

C1388 X_C10P50N

C1389 X_C10P50N

C1390 X_C10P50N

C1391 X_C10P50N

C1392 X_C10P50N

VCC3_CLK

C176

C0.1U16X

C189

C0.1U16X

VCC3_SRCLK

VCC3_SRCLK

C177

C0.1U16X

MCH_SMBDAT17,38,47

MCH_SMBCLK17,38,47

CPU0_BSEL014

CPU0_BSEL114

VCC3_SRCLK

VCC3_SRCLK

VCC3_SRCLK

VCC3_SRCLK2

VCC3_SRCLK

SIO_48MHZ_CLK

ICH_USB_48MHZ_CLK

1394_33MHZ_CLK

VGA_33MHZ_CLK

PCI_SLOT3_33MHZ_CLK

PCI_SLOT2_33MHZ_CLK

SIO_33MHZ_CLK

0C

4

VCC3_CLKA

VCC3_CLK

VCC3_CLKB

C178 C33P50N

Y1

14.318MHZ32P_D

C181 C33P50N

MCH_SMBDAT

IN

MCH_SMBCLK

IN

CPU0_BSEL0

IN

CPU0_BSEL1

IN