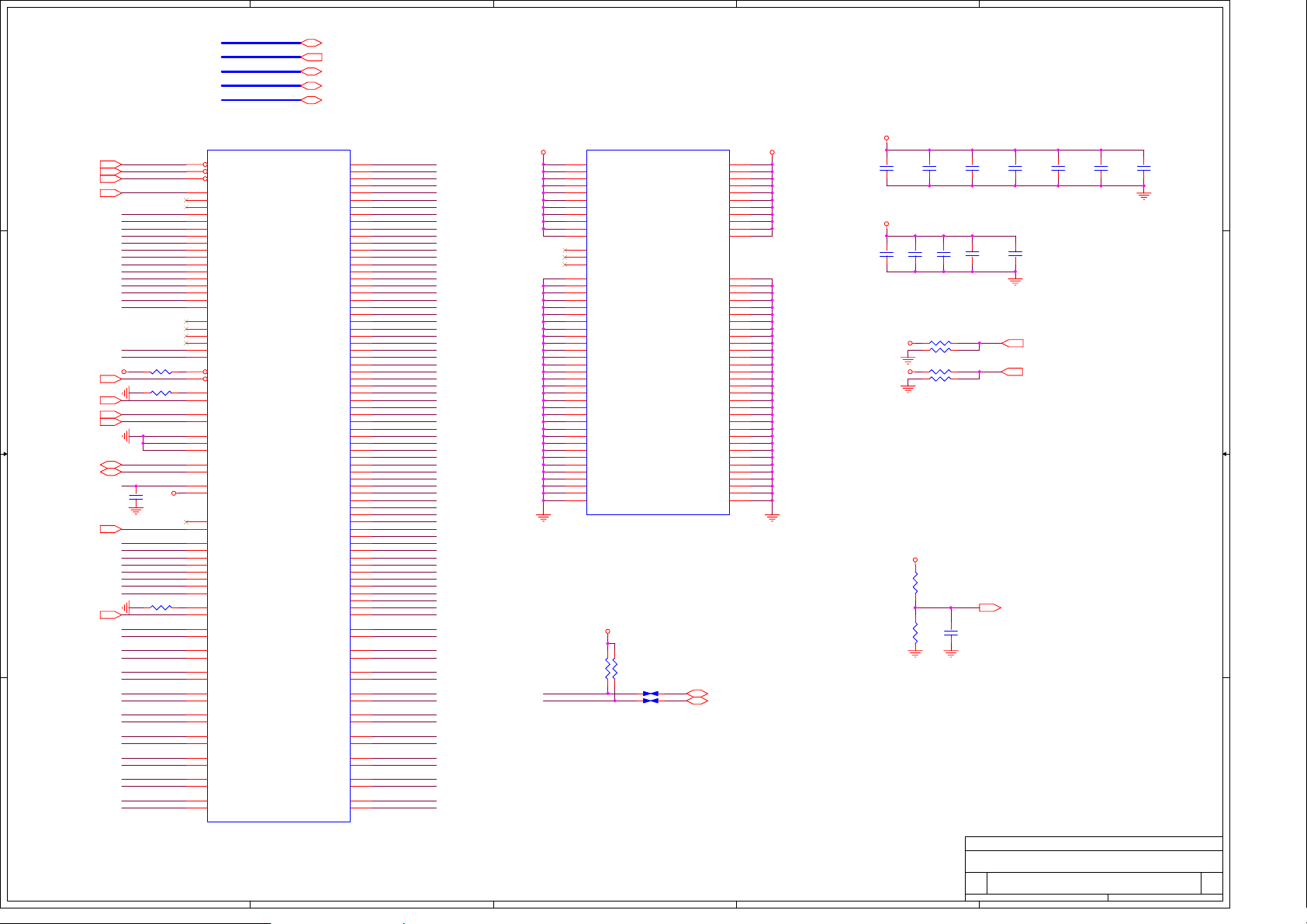

Page 1

5

4

3

2

1

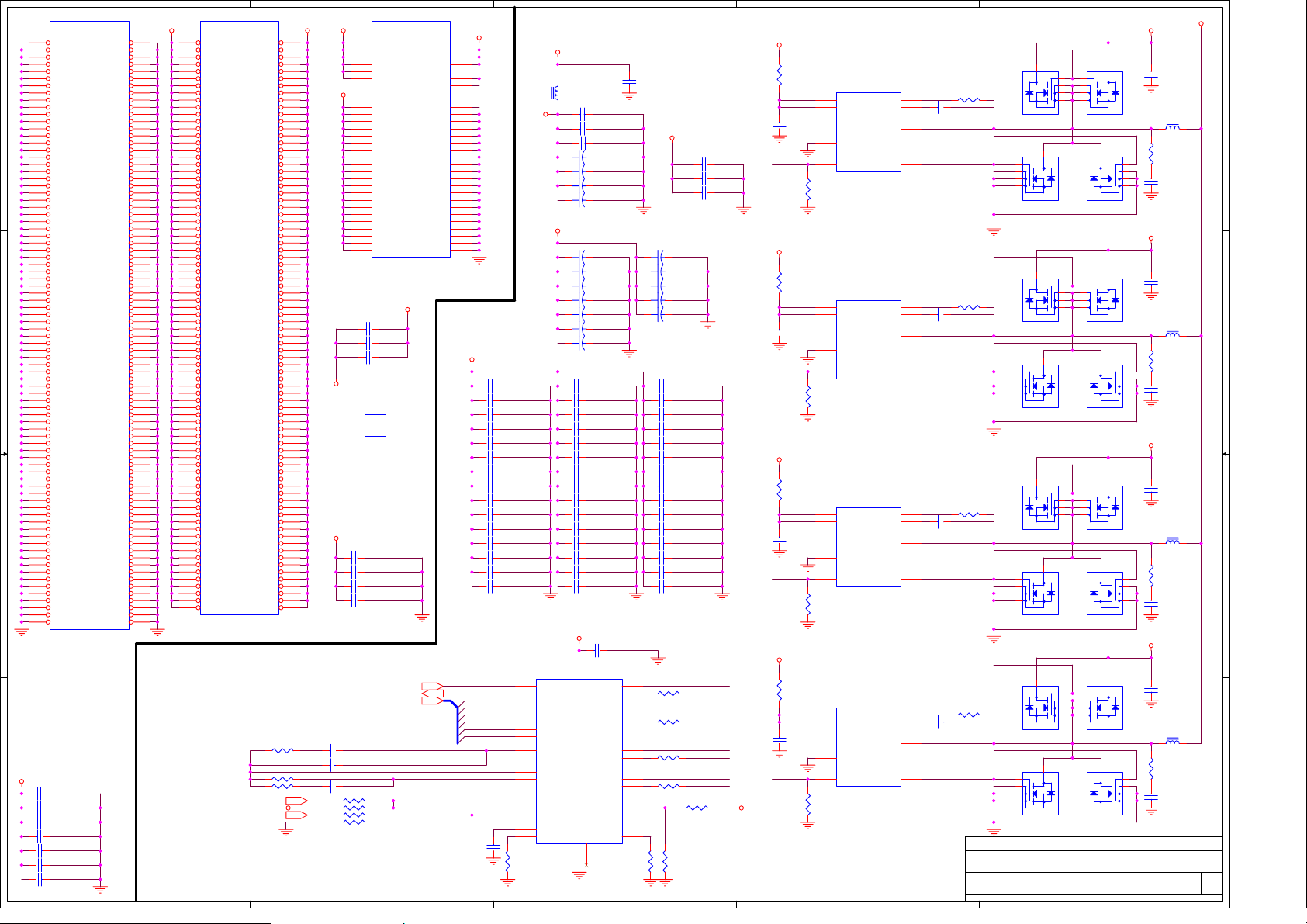

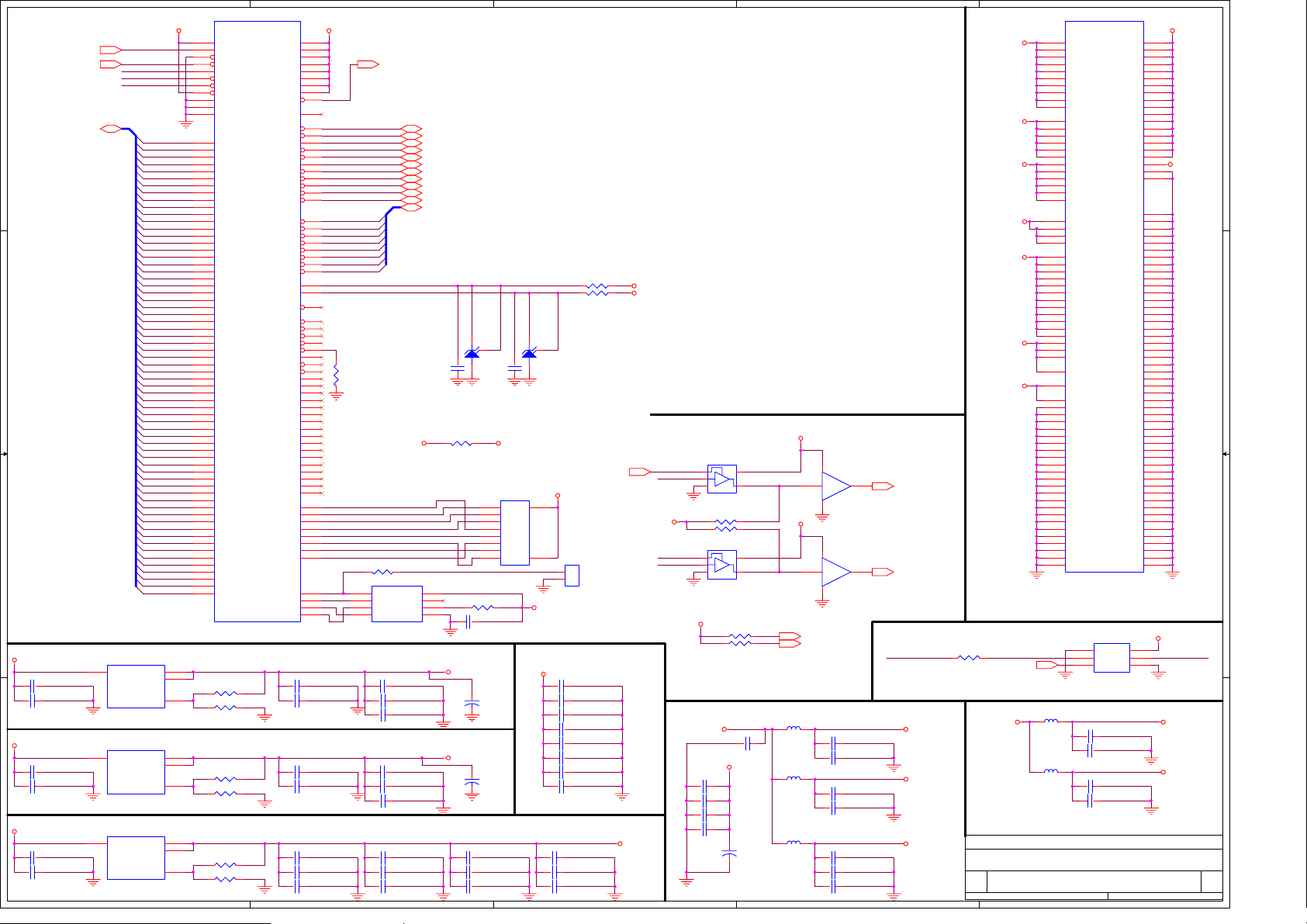

MS-9146 VER:200

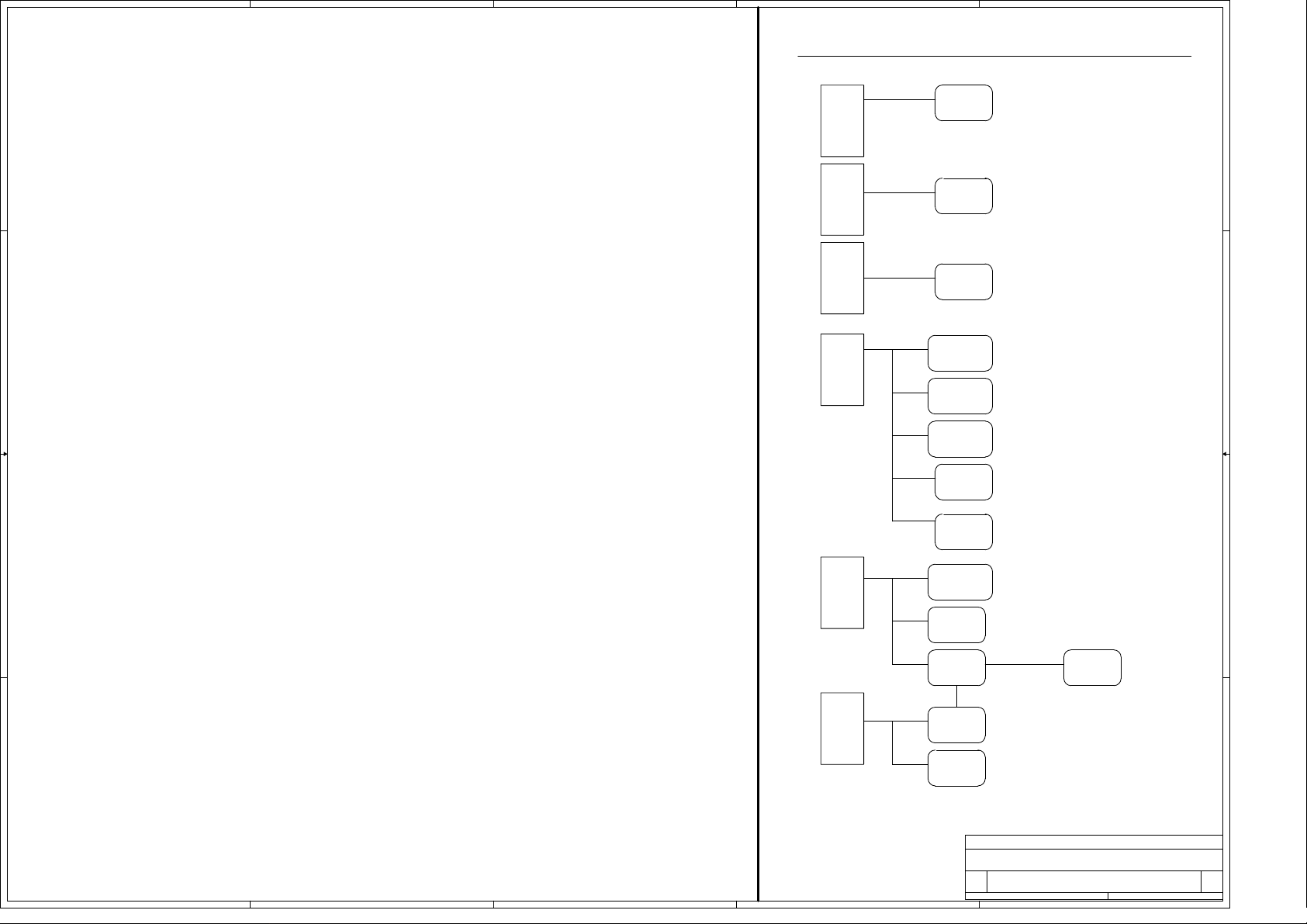

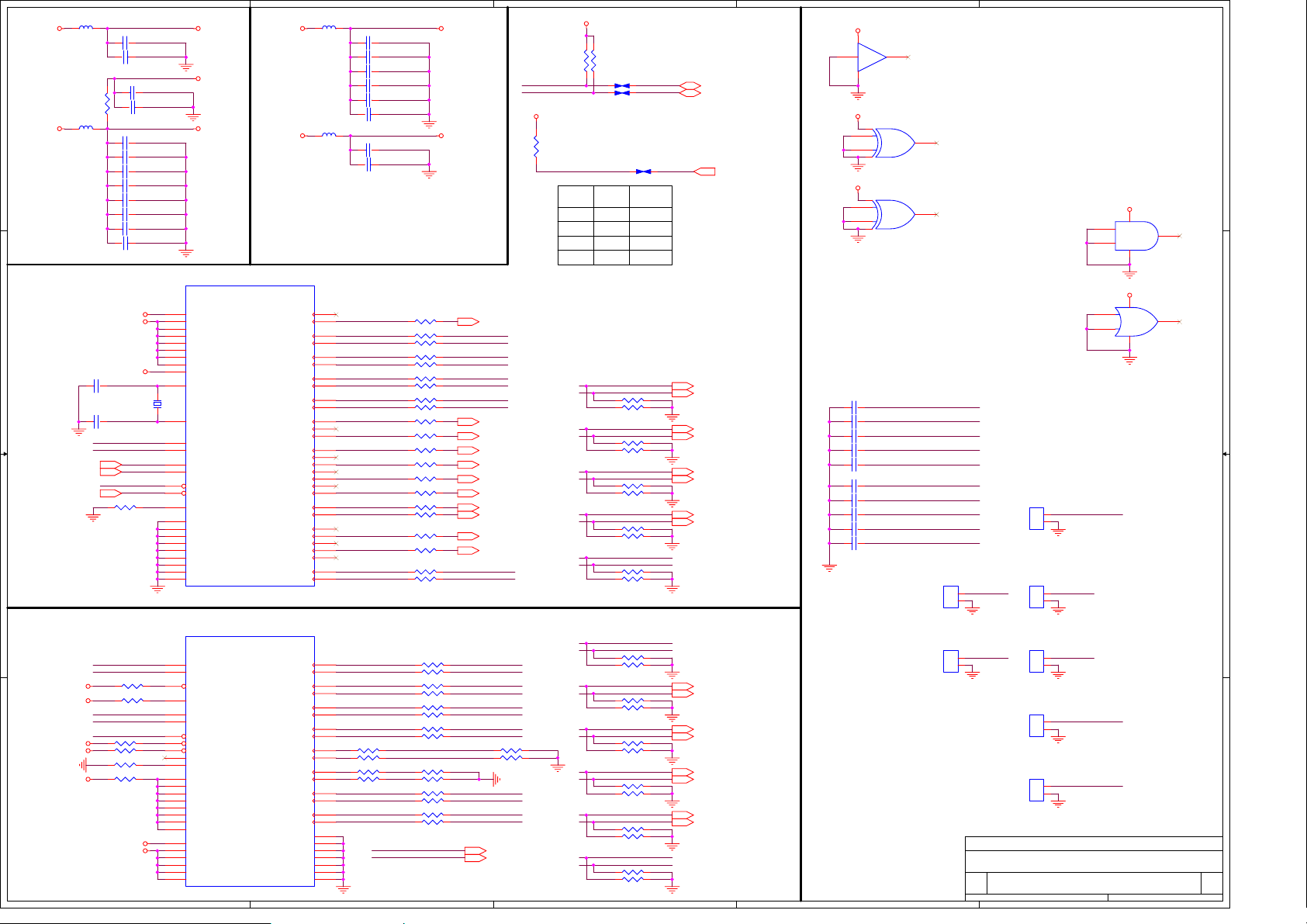

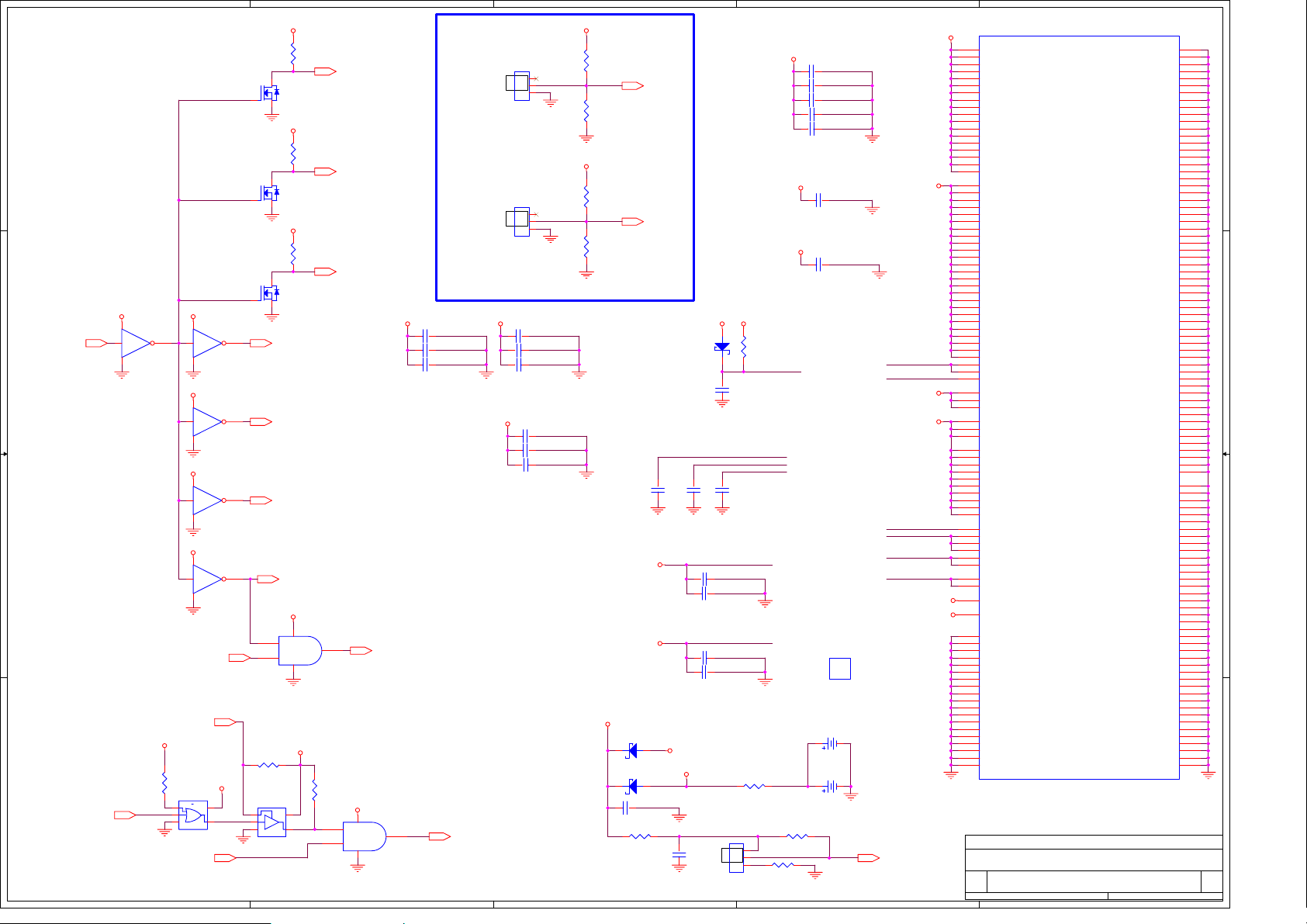

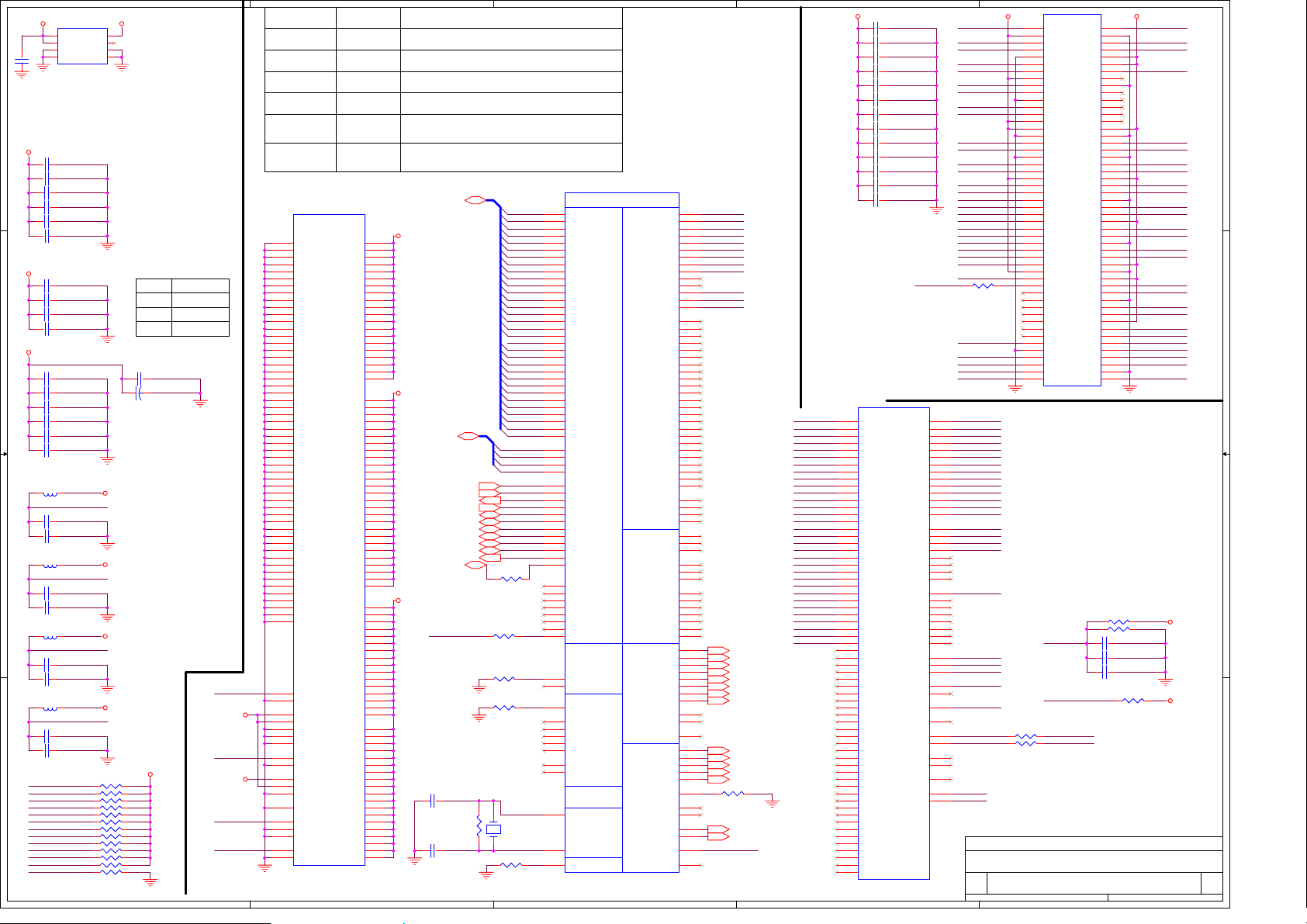

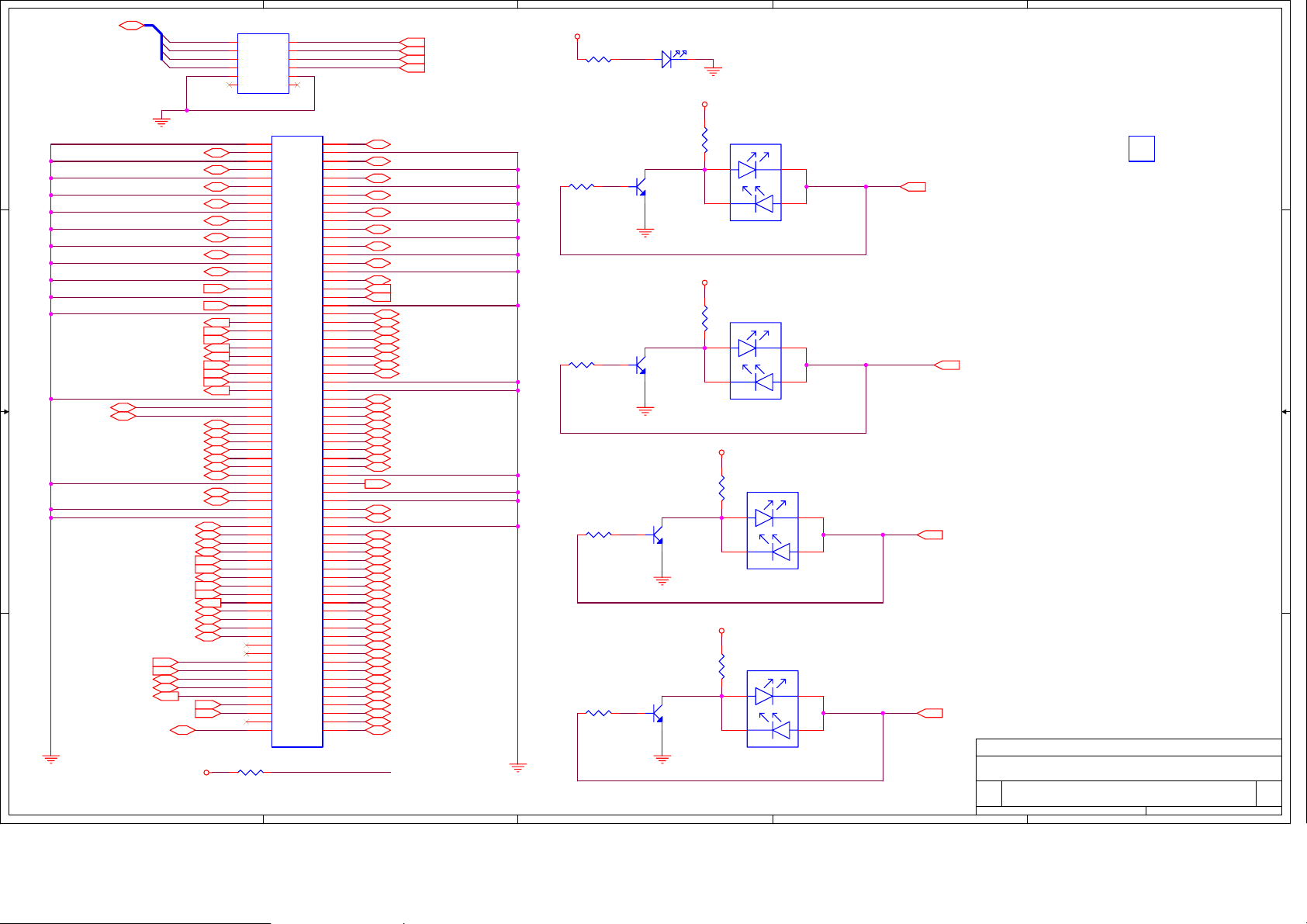

MS-9146 POWER BLOCK DIAGRAM

U109

P_VCCP0

Switch Reg

P_VCCP1

Switch Reg

P1V8

Switch Reg

U41

P2V5_SCSIA

Linear Reg

P2V5_SCSIB

Linear Reg

P2V5_VGA

Linear Reg

P1V5

Switch Reg

P_VTT

Switch Reg

P1V8_SCSI

Linear Reg

P1V8_VGA

Linear Reg

P3V3_AUX

MOS Switch

U108

U16, U5, U9, U13, U18

U33, U22, U26, U30, U35

U58

U59

U159

U47

U45

U60

U150

VCC1.5SBY

Linear Reg

Q71

01_Power Block Diagram

D D

02_System Block Diagram

03_Clock Block Diagram

04_SMbus Block Diagram

05_CLK

P12V_CPU0

06_CPU0 Signal

07_CPU0 Decap, VRM0

08_CPU1 Signal

09_CPU1 Decap, VRM1

10_MCH-DDR II 400

P12V_CPU1

11_MCH PCI-E, Hub Interface

12_MCH Decap, Light Path, ITP

13_DDR II-DIMM A1

14_DDR II-DIMM A2

15_DDR II-DIMM A3

16_DDR II-DIMM A4

17_DDR II-DIMM B1

C C

18_DDR II-DIMM B2

19_DDR II-DIMM B3

20_DDR II-DIMM B4

21_ICH5

P5V P12V

22_ICH5 Decap

23_IDE, SATA, USB, FWH, Speaker

24_PXH Express, Decap

25_PXH PCIA, PCIB

26_PCI-X BusA Slot PCI4(ZCR)

27_PCI-X BusB slot PCI1

28_PCI-E x8 Slot PCIEX1

29_Super I/O, COM1, COM2, Parallel Port, FDD

30_Hardware Monitor, Fans, FRU

31_BMC

32_SCSI PCI, Decap, ZCR Logic

B B

33_SCSI Disk, Connect, Vref Circuit

34_W83791D

35_LAN 82546GB

36_VGA

37_VGA, THERMTRIP_#

P3V3

38_System Logic

39_P_VTT, P1V5, P1V8, P3V3_AUX

40_Debug LED, BP Connect

41_History

P3V3_STB

Linear Reg

P5V_STB

A A

5

4

3

2

VCC2.5SBY

Linear Reg

U107

Q72

Title

Power Block Diagram

Size Document Number Rev

MS9146 200

Date: Sheet

1

of

141Thursday, November 11, 2004

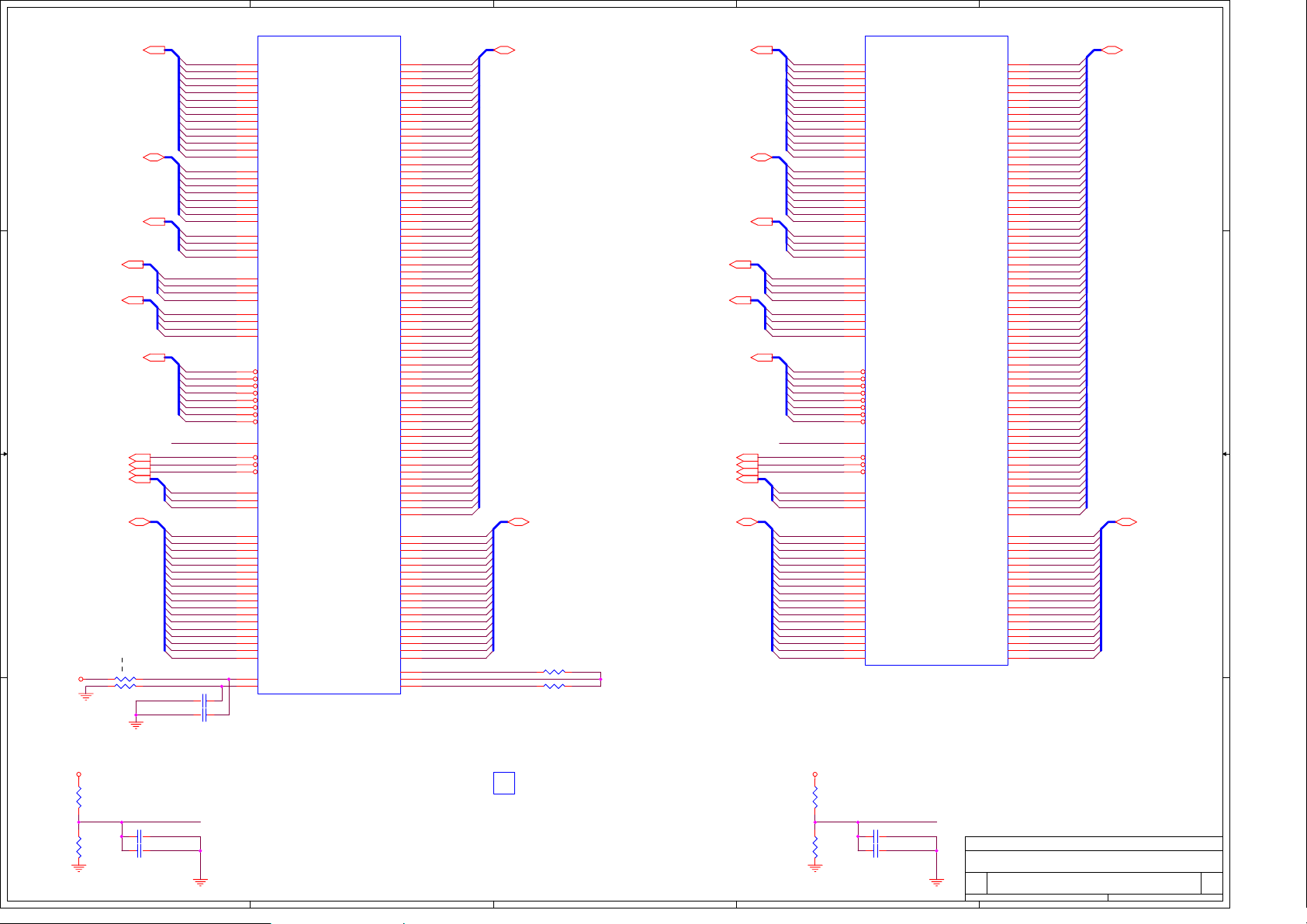

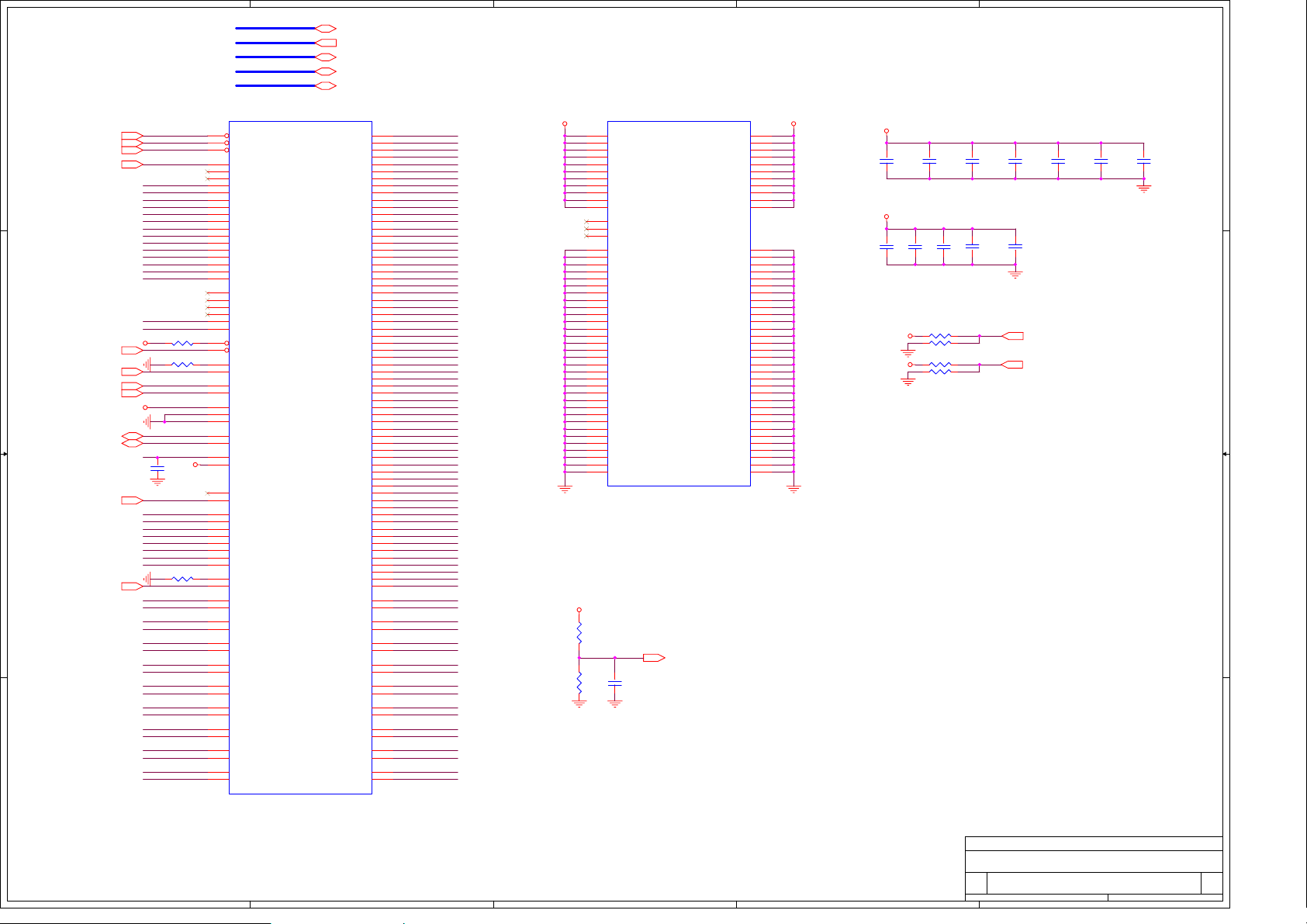

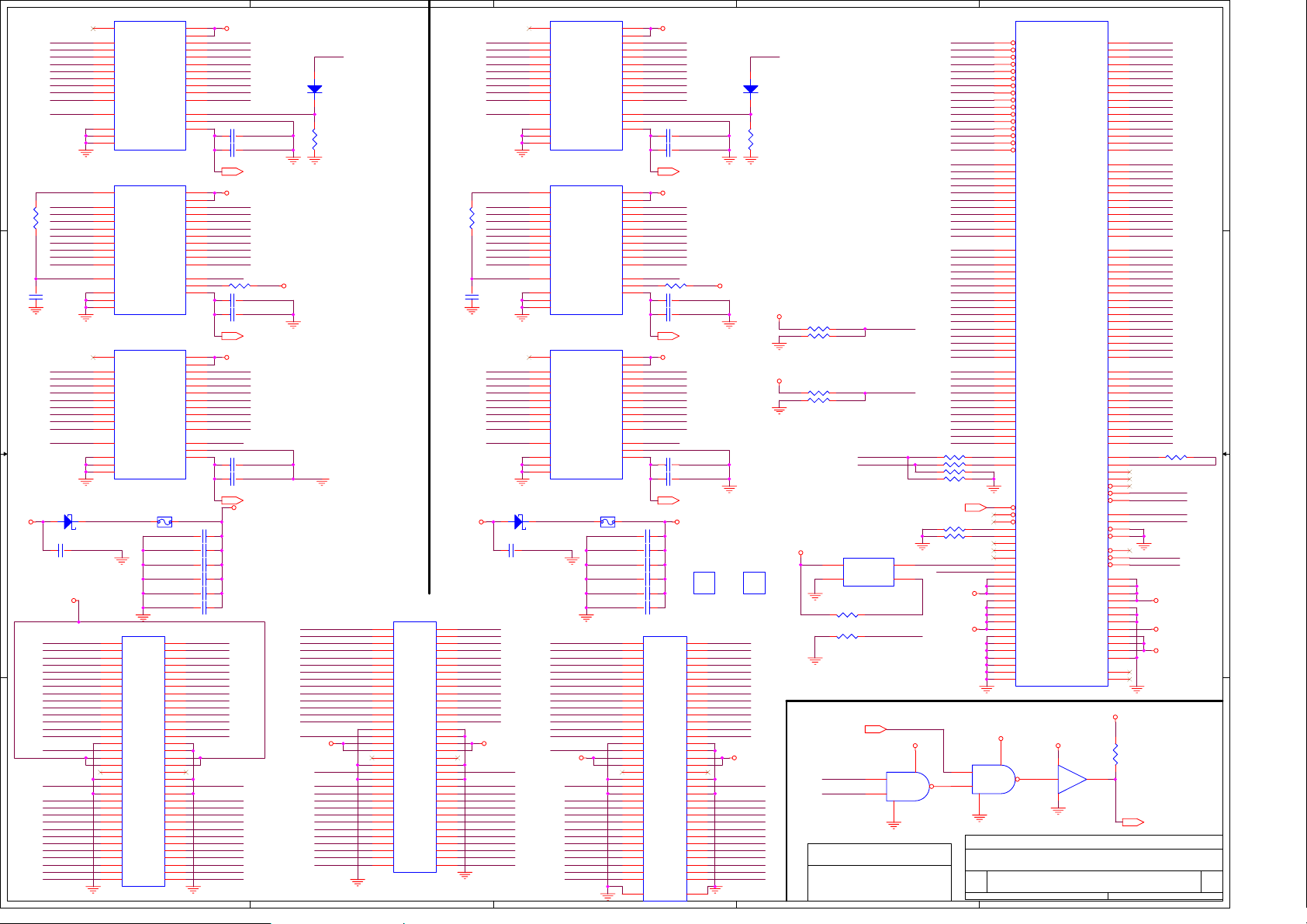

Page 2

5

4

3

2

1

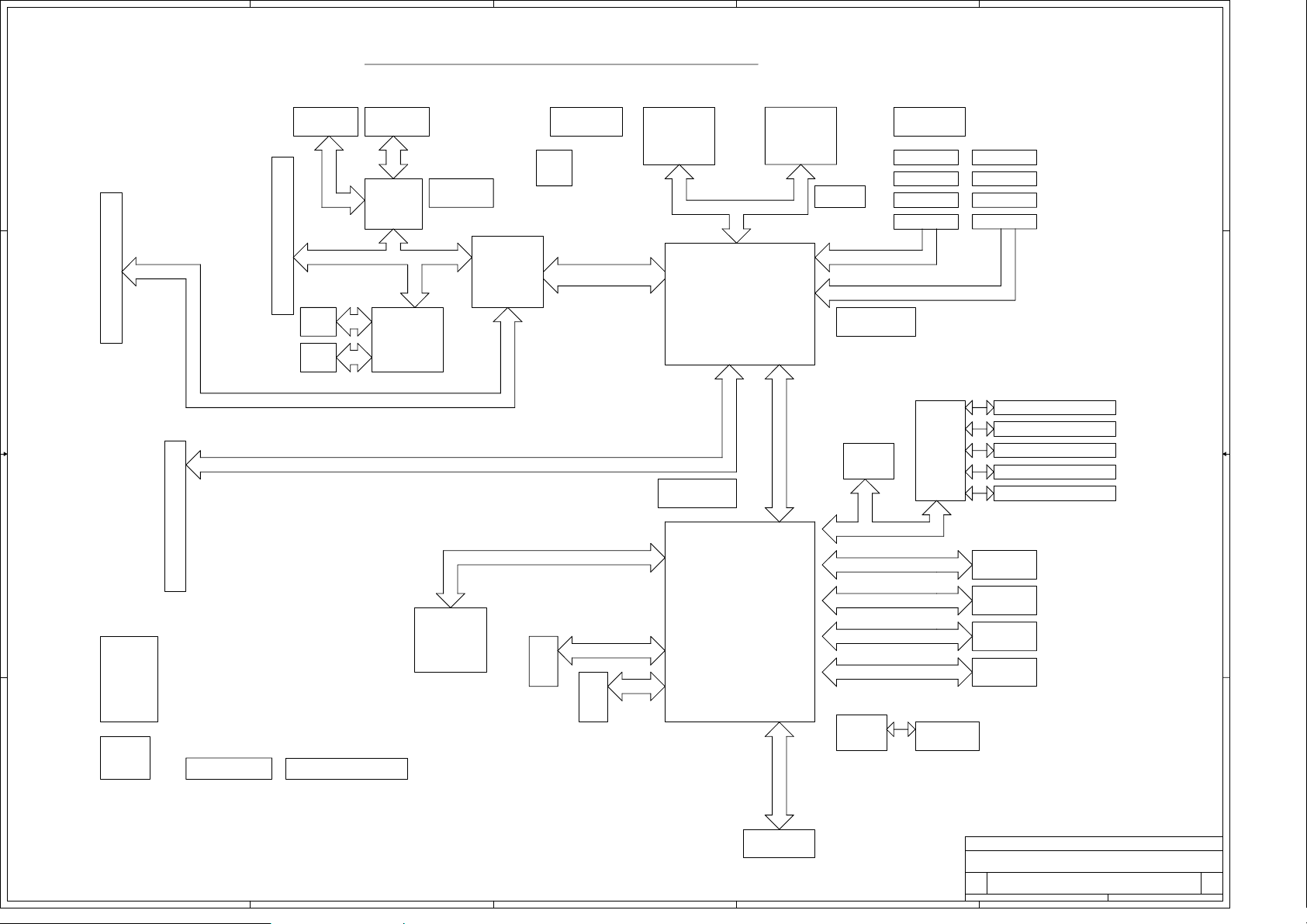

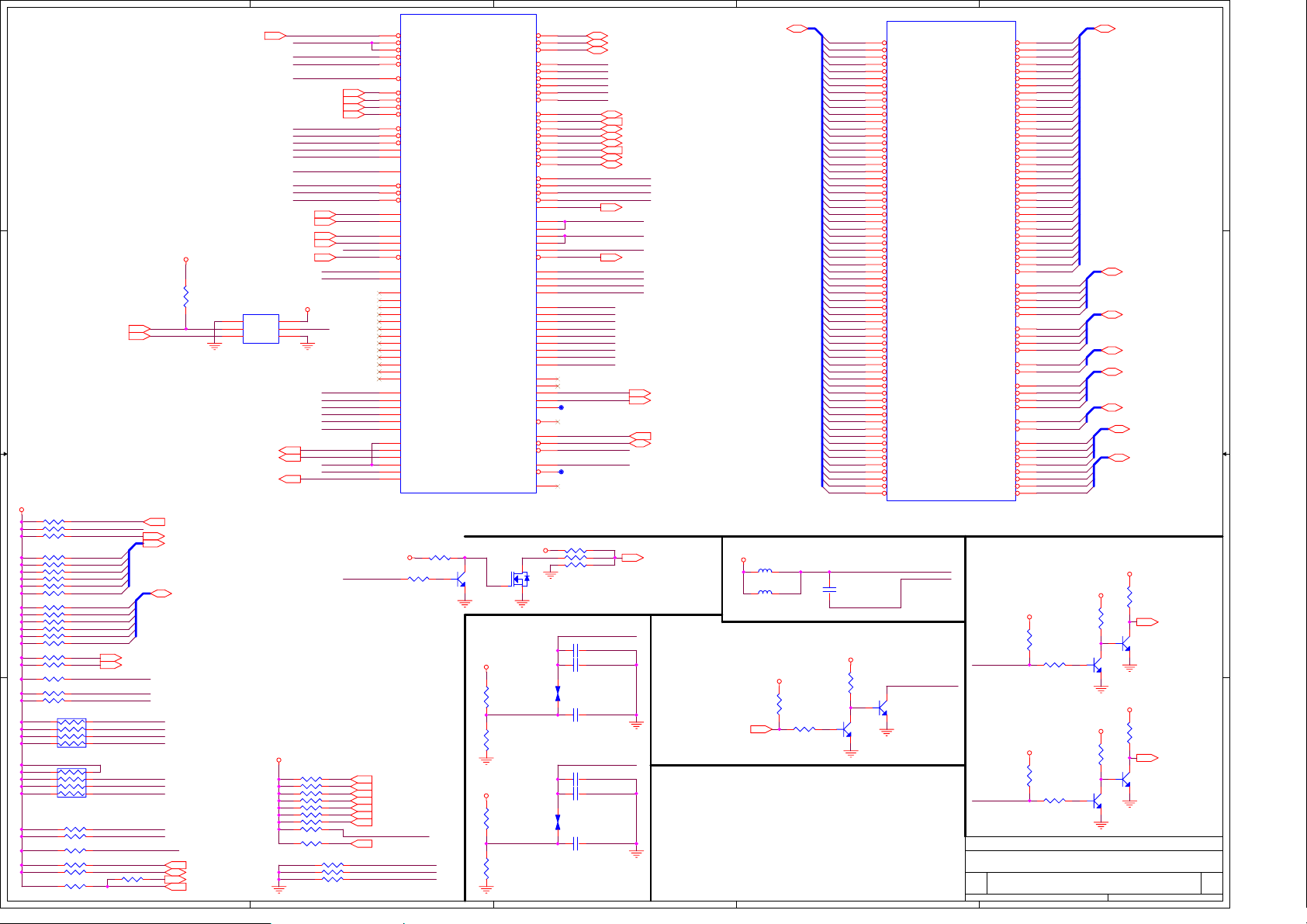

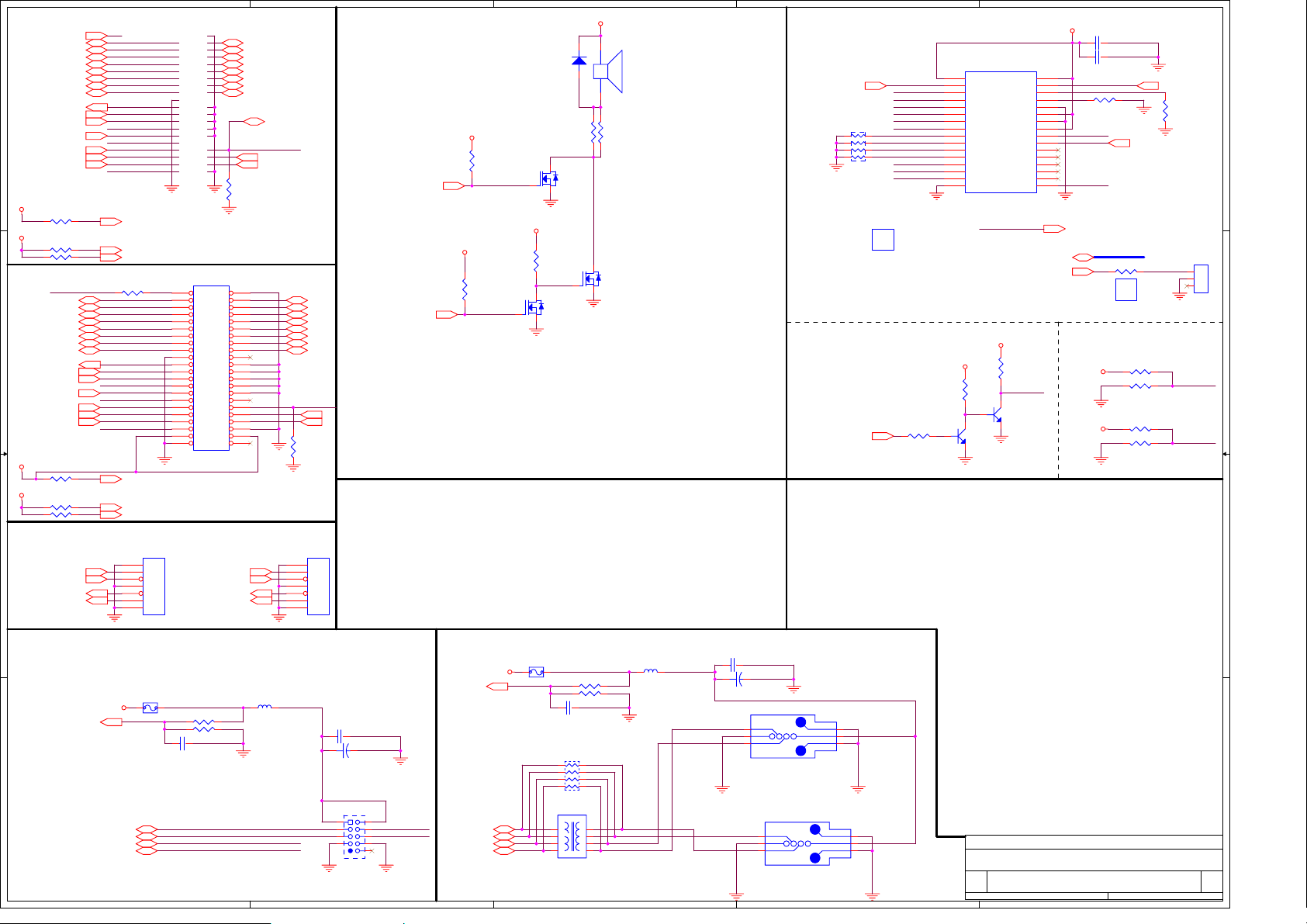

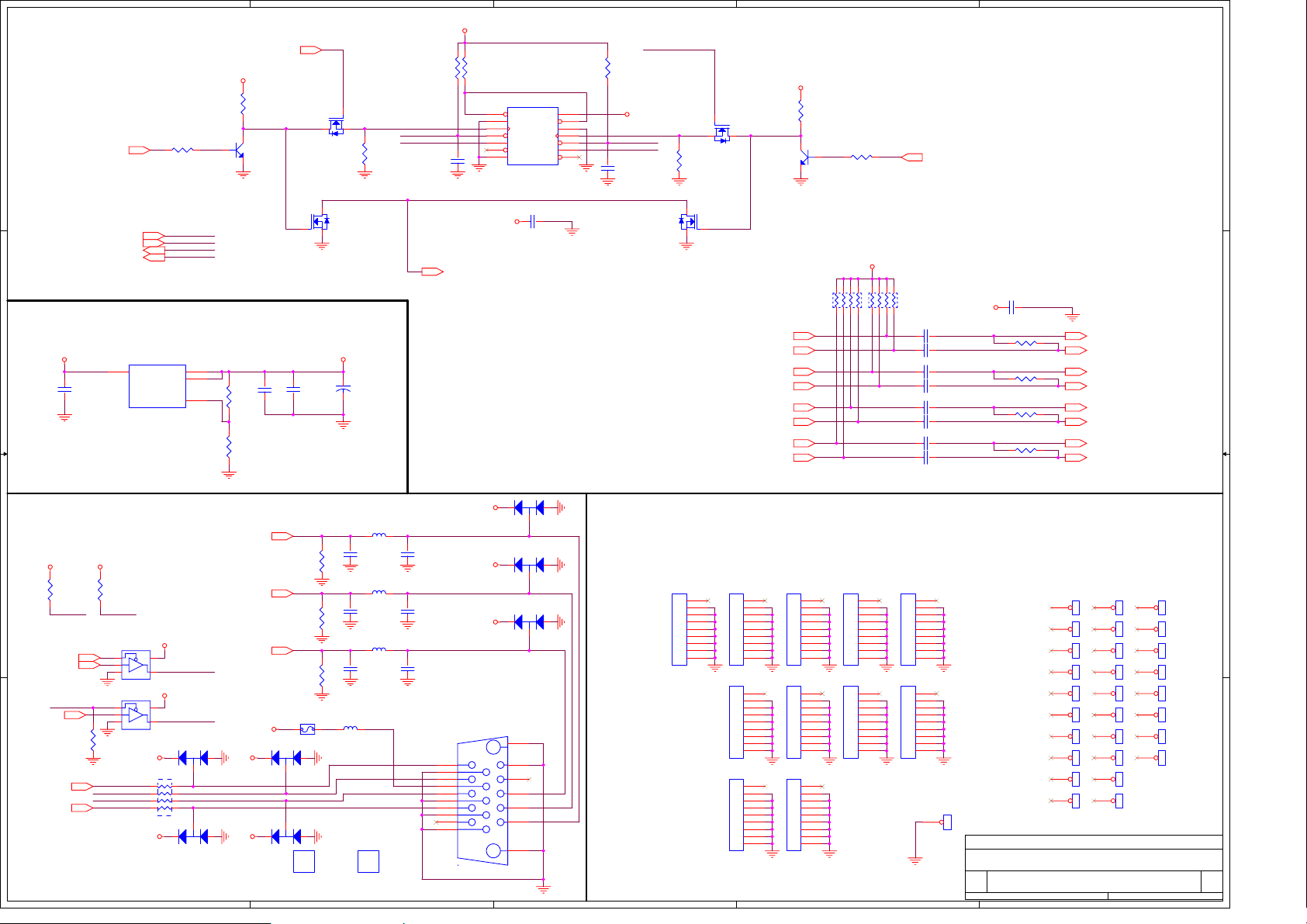

MS-9146 SYSTEM BLOCK DIAGRAM

D D

PCI-X 133MHZ ( SLOT PCI1 )

C C

PCI-X ( 133MT/S-1GB/S )

X8 CONNECTOR

B B

PCI EXPRESS ( SLOT PCIEX2 )

SCSI Conn

( INTERNAL )

PCI-X 66MHZ ( SLOT PCI4, ZCR Support )

RJ45

RJ45

SCSI Conn

( INTERNAL )

SCSI 0

PCI-X ( 66MT/S-500MB/S )

or

SCSI 1

Dual U320

SCSI Ctlr

( AIC7902 )

PCI-X (100MT/S-800B/S ) * 3 Riser Slot

SCSI VRegs

( 1.8V & 2.5V )

82546GB

PCI EXPRESS X8 ( 4GB/S Duplex )

CPU0 VRD

ITP

NOTE: ALL COYOTE VARIANTS WILL

SUPPORT NOCONA PROCESSORS

( EARLY JAYHAWK PROCESSORS )

SPLIT PLANE CONFIGURATION ONLY

PXH-D

or

PXH

PCI 32-BIT 33MHZ 5V ( 133MB/S )

PCI EXPRESS X8

( 4GB/S Duplex )

CPU 0

( NOCONA/

JAYHAWK )

SB ( 800MT/S - 6.4GB/S )

GROUP A

LINKS 0-7

GROUP B

LINKS 0-3

GROUP B

LINKS 4-7

1.5V VRD

(

MCH/PXH/ ICH5 )

MCH

GROUP C

LINKS 0-7

CPU 1

( NOCONA/

JAYHAWK )

HUB INTERFACE 1.5

1.2V VRD

( FSB VTT )

DDR II( 400MT/S - 3.2GB/S )

DDR II( 400MT/S - 3.2GB/S )

1.8V VRD

( DDR II 400 )

FWH

LPC

USB PORT# 0

CPU1 VRD

DIMM B3

DIMM B2

DIMM B1

SIO

( PC87366 )

DIMM A4DIMM B4

DIMM A3

DIMM A2

DIMM A1

SERIAL PORT ( BACK PANEL )

SERIAL PORT ( INTERNAL )

FLOPPY

PS/2 KEYBOARD

PS/2 MOUSE

REAR USB

USB PORT# 1

REAR USB

ICH5

VGA

CK409B

( CLOCK

SYNTH/

DRVR )

DB800

FRONT PANEL HDR

A A

BMC SODIMM CONNECTOR

ATI7000M

S-ATA

S-ATA

S-ATA

S-ATA

SECONDARY ATA-100

IDE

5

4

3

USB PORT# 2

USB PORT# 3

Fan Speed

Control

Circuitry

2

FRONT USB

FRONT USB

Hard Monitor

ADT7463

Title

System Block Diagram

Size Document Number Rev

MS9146 200

Date: Sheet

1

241Thursday, November 11, 2004

of

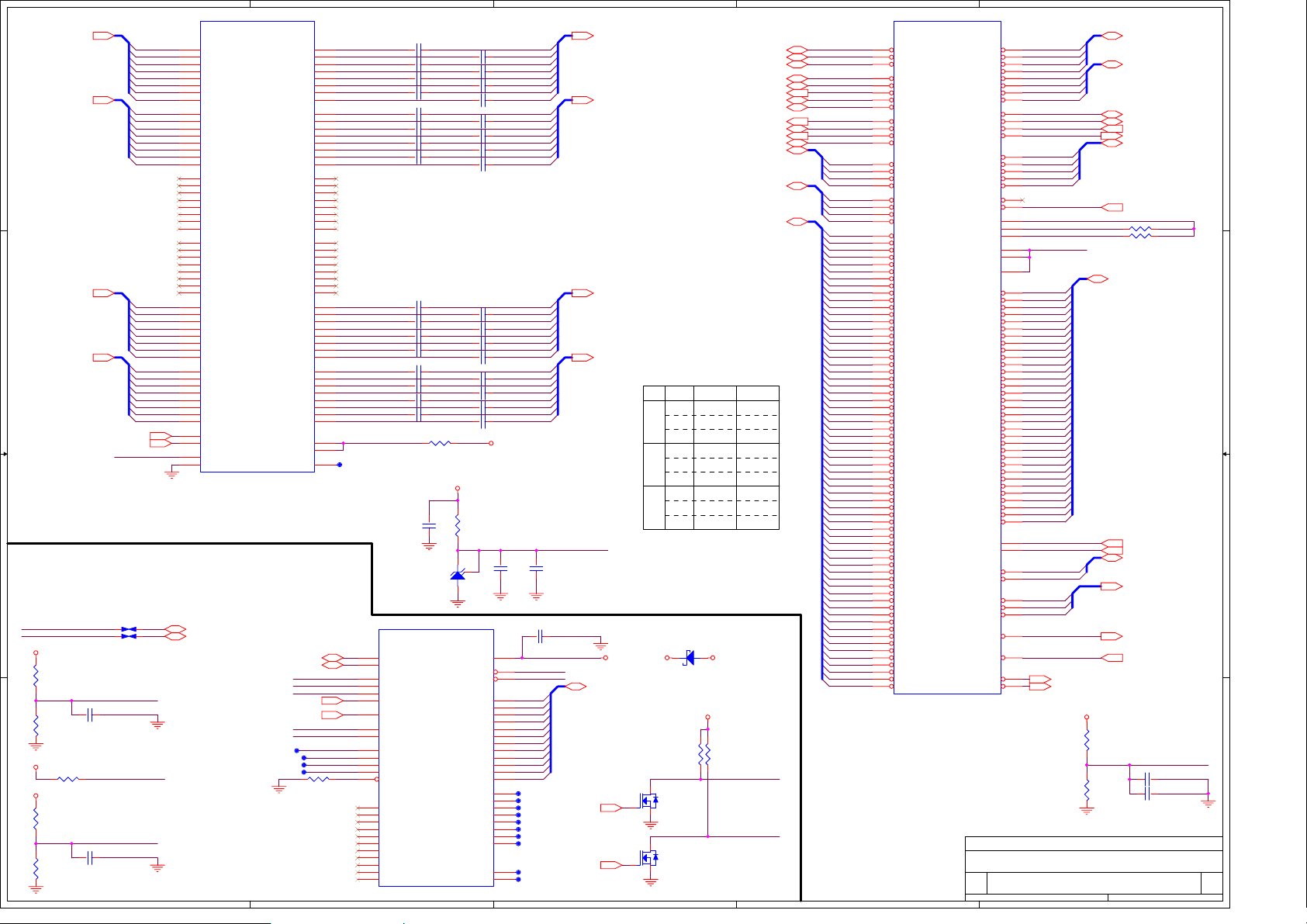

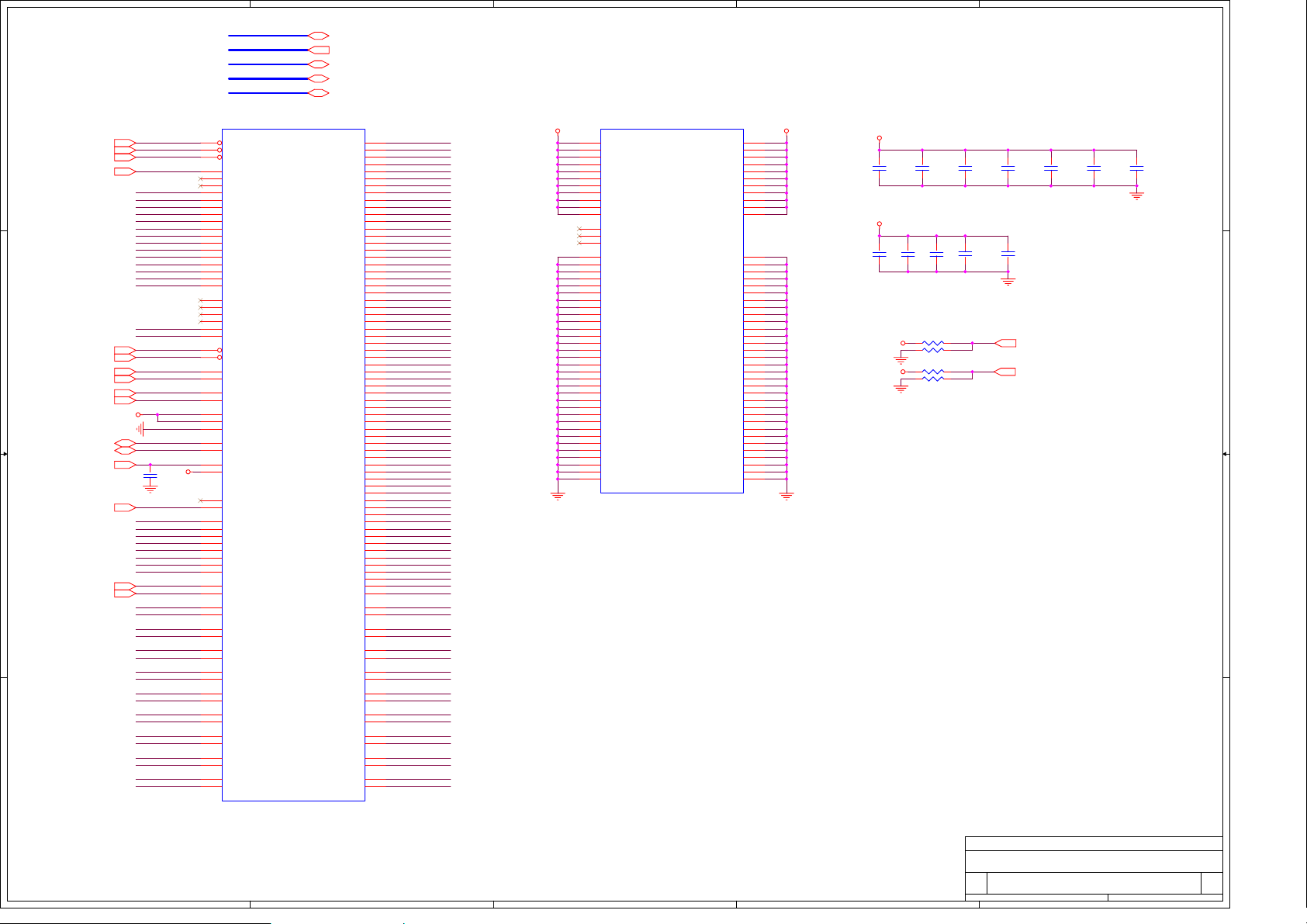

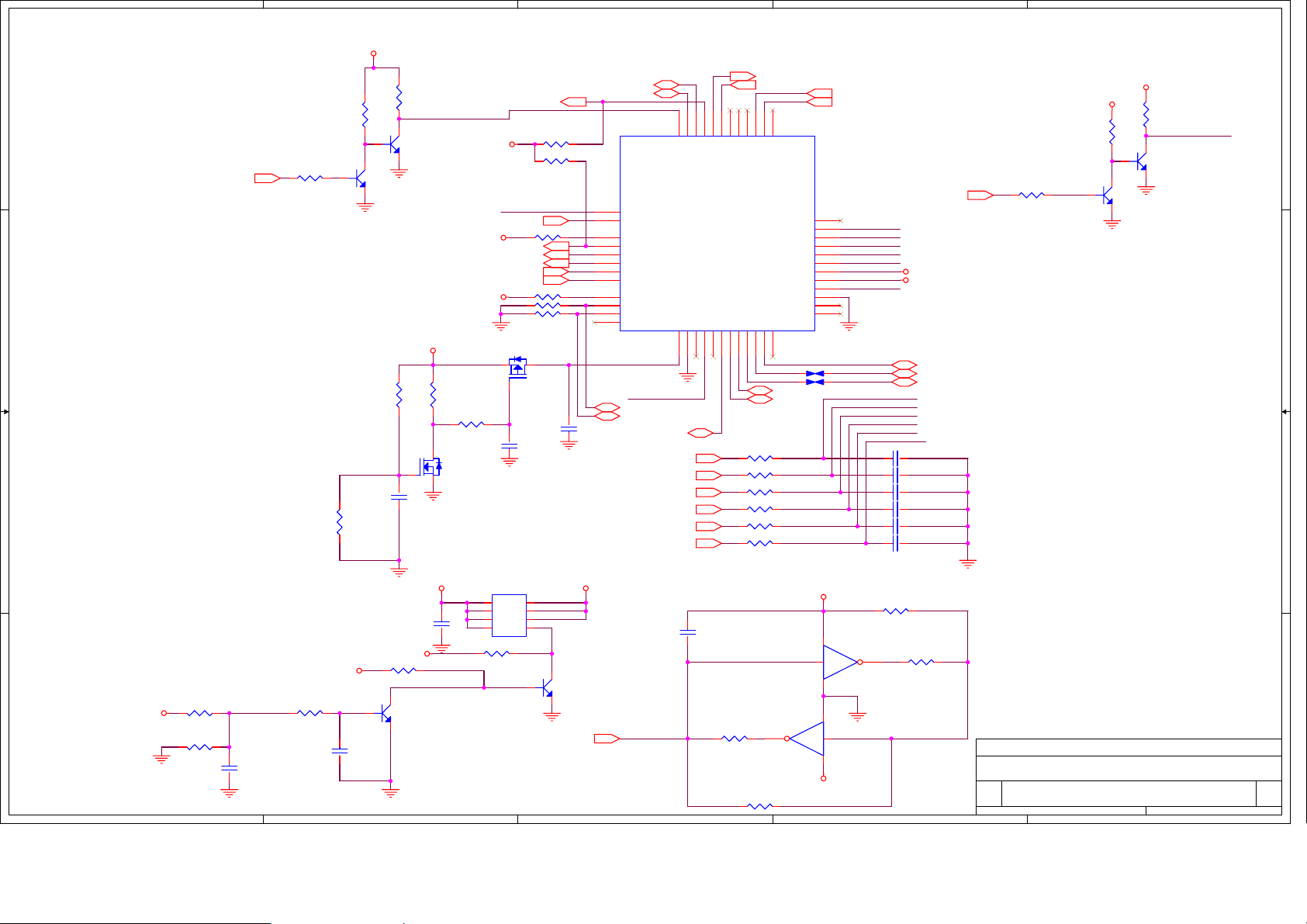

Page 3

5

4

3

2

1

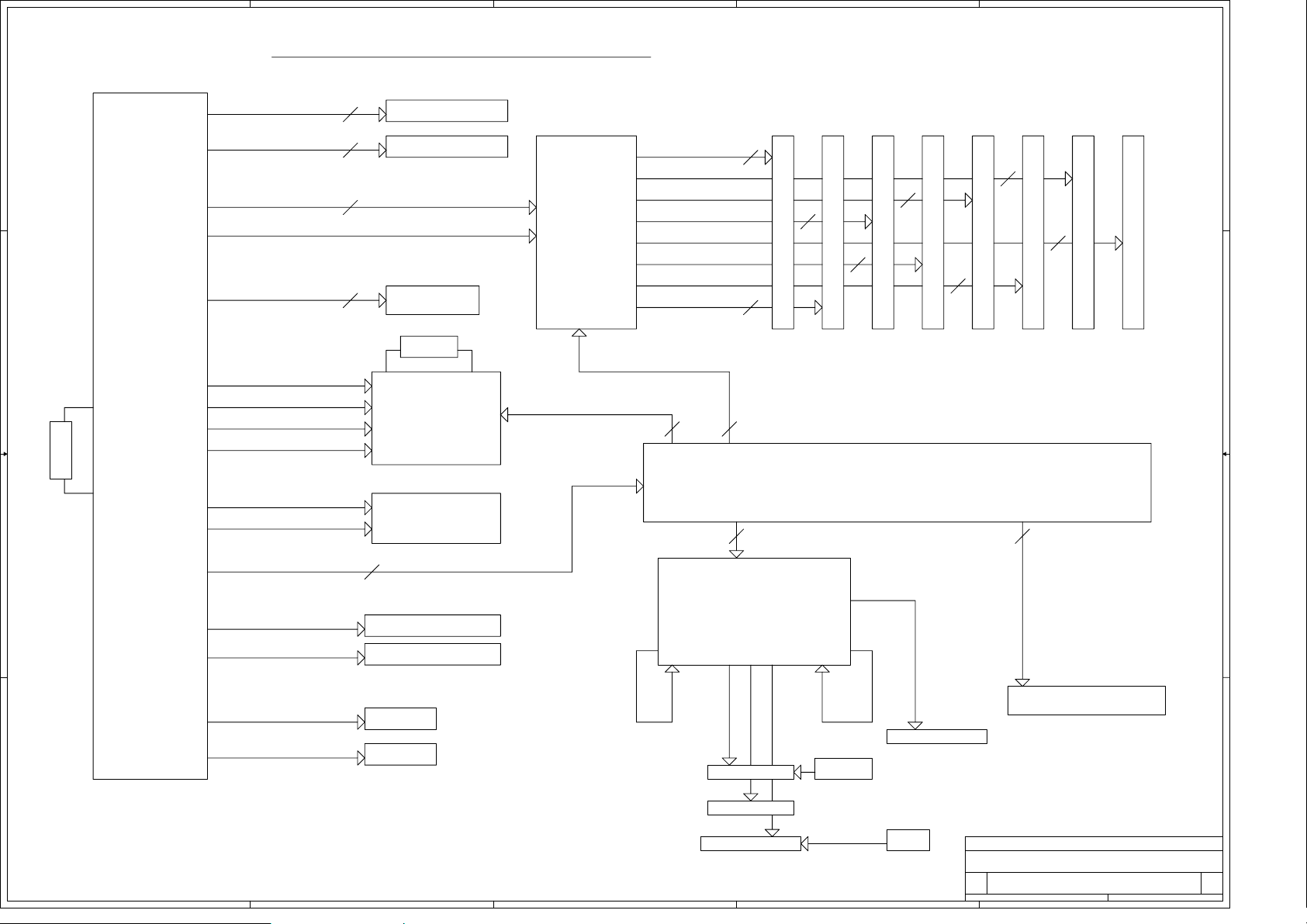

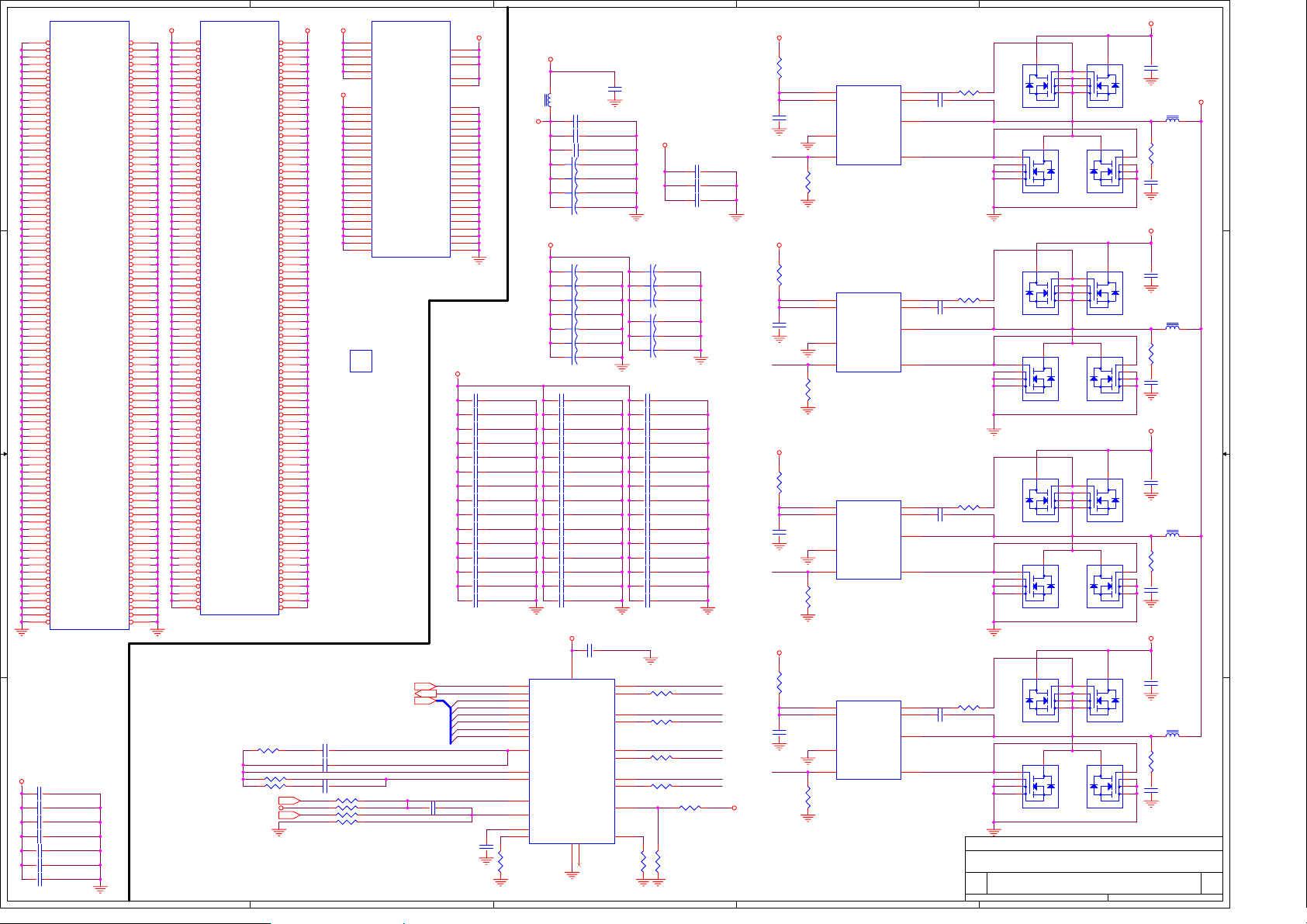

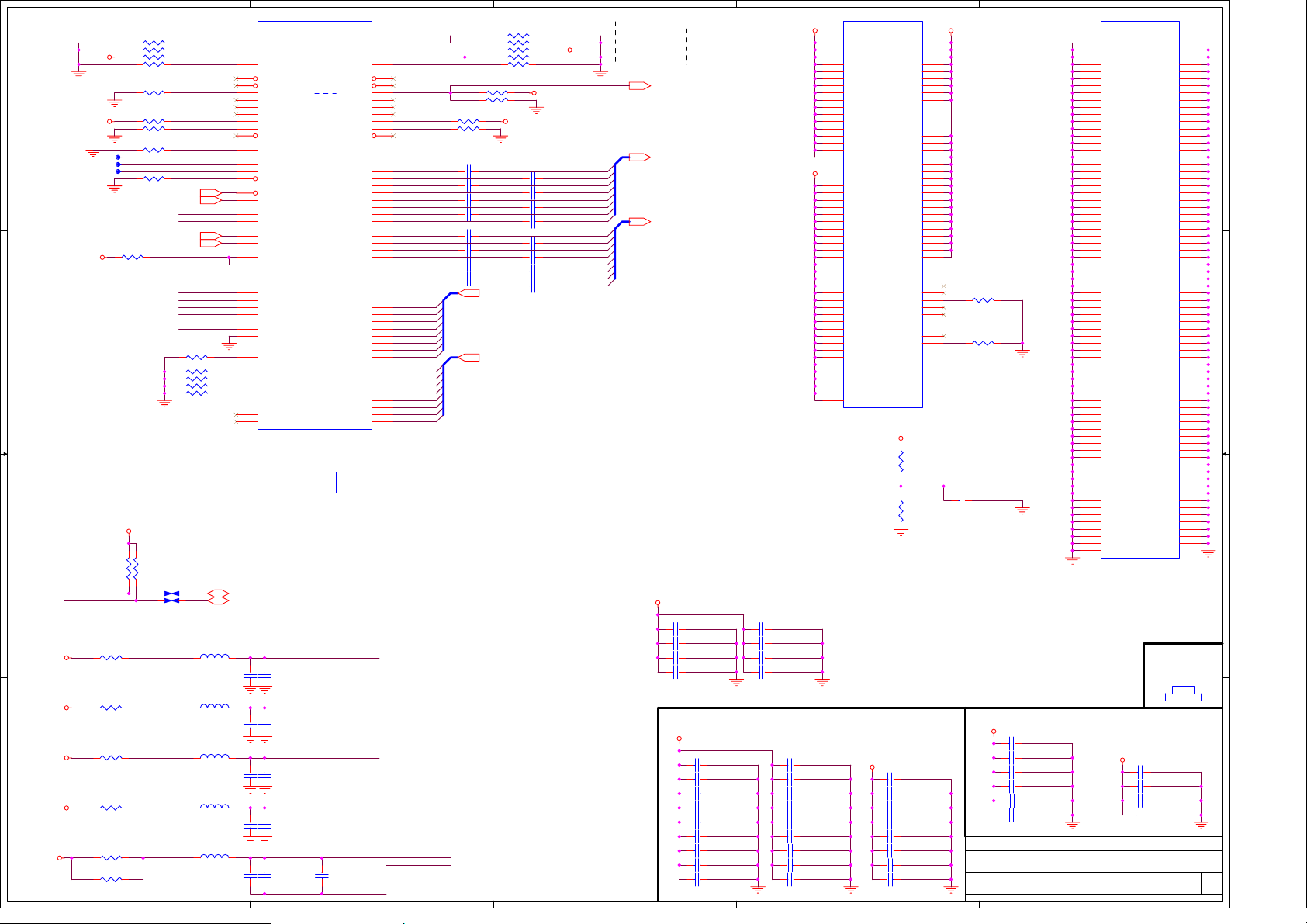

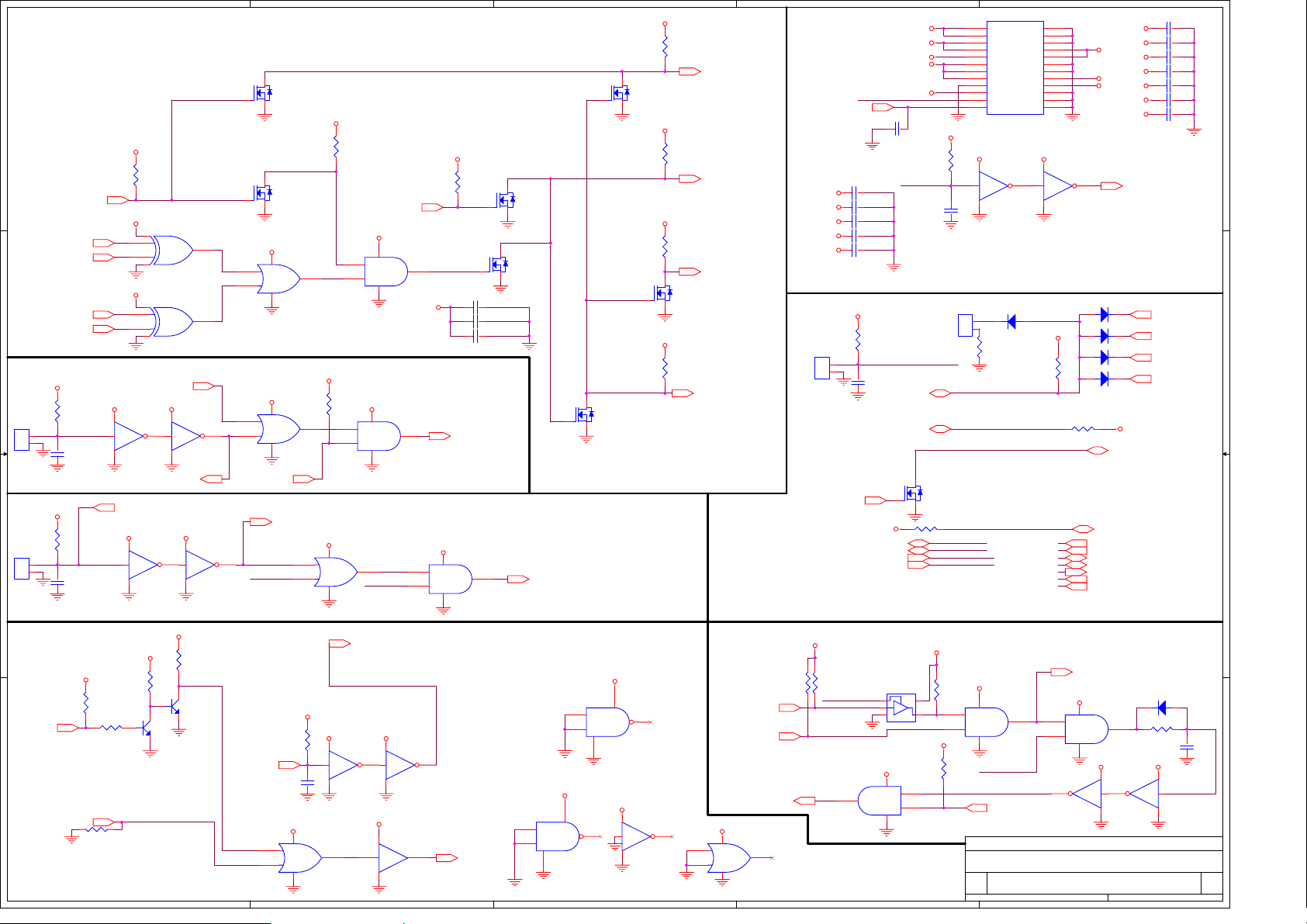

MS-9146 CLOCK BLOCK DIAGRAM

D D

C C

14.318MHZ

Crystal

B B

CPU3

CPU2

CPU1

3V66_1

CPU0

3V66_3

USB_48

PCIF0

REF0

DOY_48

PCIF2

SRC

3V66_3

PCI0

PCI2

P0_BCLK_P/N (200MHZ)

P1_BCLK_P/N (200MHZ)

MCH_BCLK_P/N (200MHZ)

MCH_66CLK

ITP_BCLK_P/N (200MHZ)

ICH_66CLK

ICH_48CLK

ICH_33CLK

ICH_14CLK

SIO_48CLK

SIO_33CLK

SRC_100CLK_P/N

BMC_33CLK

PCI_SLOT_33CLK

BCLK(P/N-1/0)

2

BCLK(P/N-1/0)

2

2

2

ITP_XDP

32.768KHZ

Crystal

2

BMC Connector

Debug Port Connect (J2)

ICH5

SIO

CPU0

CPU1

MCH

ICH_100CLK_P/N

DDRA_CMDCLK_P/N0

DDRA_CMDCLK_P/N1

DDRA_CMDCLK_P/N2

DDRA_CMDCLK_P/N3

DDRB_CMDCLK_P/N0

DDRB_CMDCLK_P/N1

DDRB_CMDCLK_P/N2

DDRB_CMDCLK_P/N3

MCH_100CLK_P/N

SRC

2

2

2

DDR II 400 DIMM # A1

2

22

2

DDR II 400 DIMM # B1

DDR II 400 DIMM # A2

DDR II 400 DIMM # B2

2

DIFF0 DIFF1 DIFF2 DIFF3

DB800 ( SRC - DIFFERENTIAL BUFFER )

DIFF4 DIFF6 DIFF5

PXH_100CLK_P/N2

PAPCLK0(2)

PBPCLK0(2)

PBPCLK0(1)

PBPCLK0(0)

PB_PCLKI

PBPCLK0(5)

PXH

PAPCLK0(6)

PAPCLKI

PAPCLK0(1)

PAPCLK0(0)

2

DDR II 400 DIMM # A3

SLOT0_100CLK_P/N

DDR II 400 DIMM # B3

2

2

DDR II 400 DIMM # A4

DDR II 400 DIMM # B4

REF1

PCI6

PCI_VGA_33CLK

PACLK6

ATI7000M

PBCLK6

PXH_PBPCLK_SLOT

PCI EXPRESS X8 SLOT PCIEX1

PCI-X SLOT PCI1

FWH_33CLK

PCI4

A A

FWH

PXH_PAPCLK_LAN

82546GB

PXH_PAPCLK_SLOT1

PXH_PAPCLK_SCSI

25MHZ

Crystal

SUPPORTS 1U/2U RISER

PCI-X SLOT PCI4

SUPPORTS 1U/2U RISER

U320 SCSI AIC7902

5

4

3

AIC_CLKINP

80MHZ

Osc

2

Title

Clock Bolck Diagram

Size Document Number Rev

MS9146 200

Date: Sheet

341Thursday, November 11, 2004

1

of

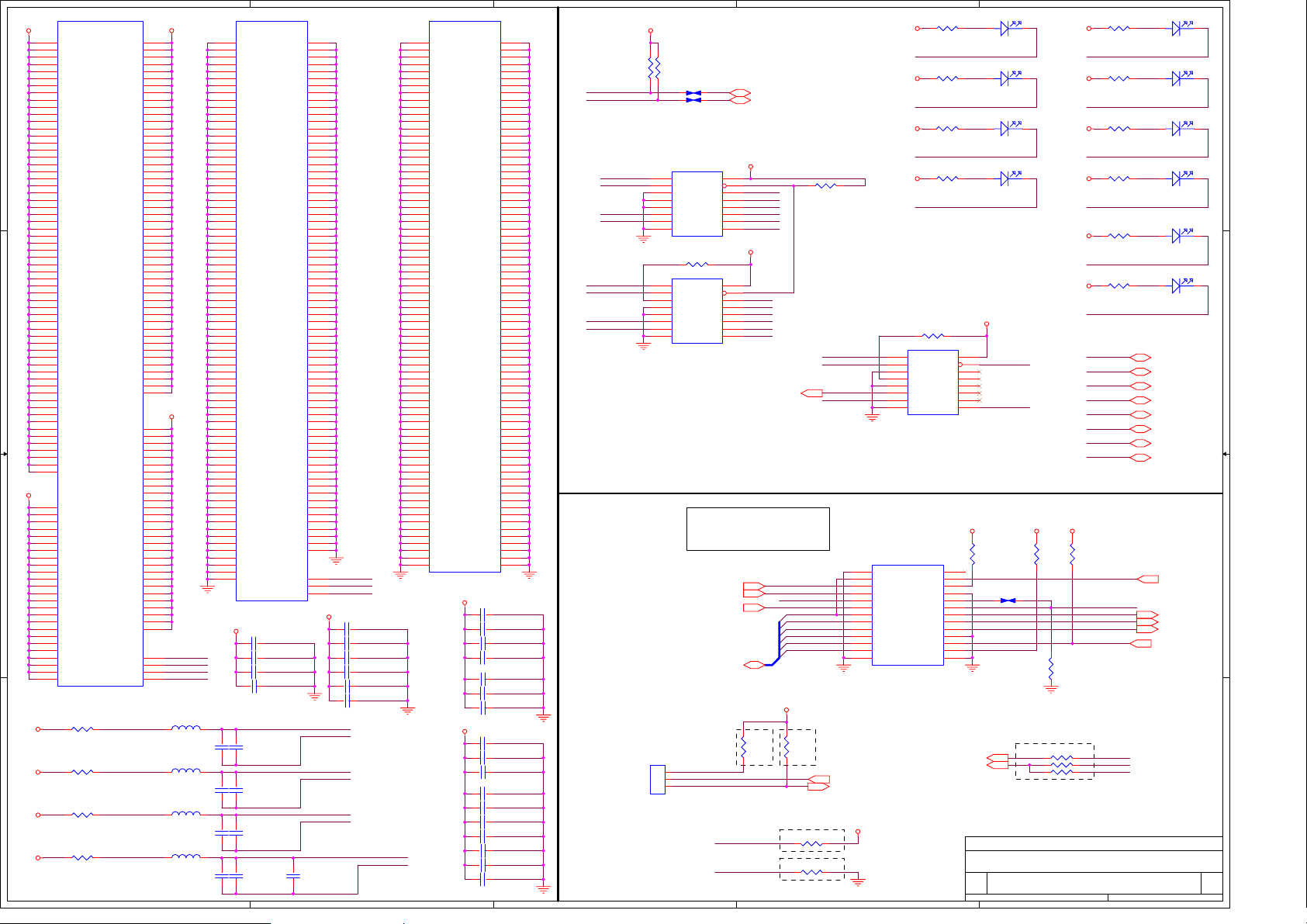

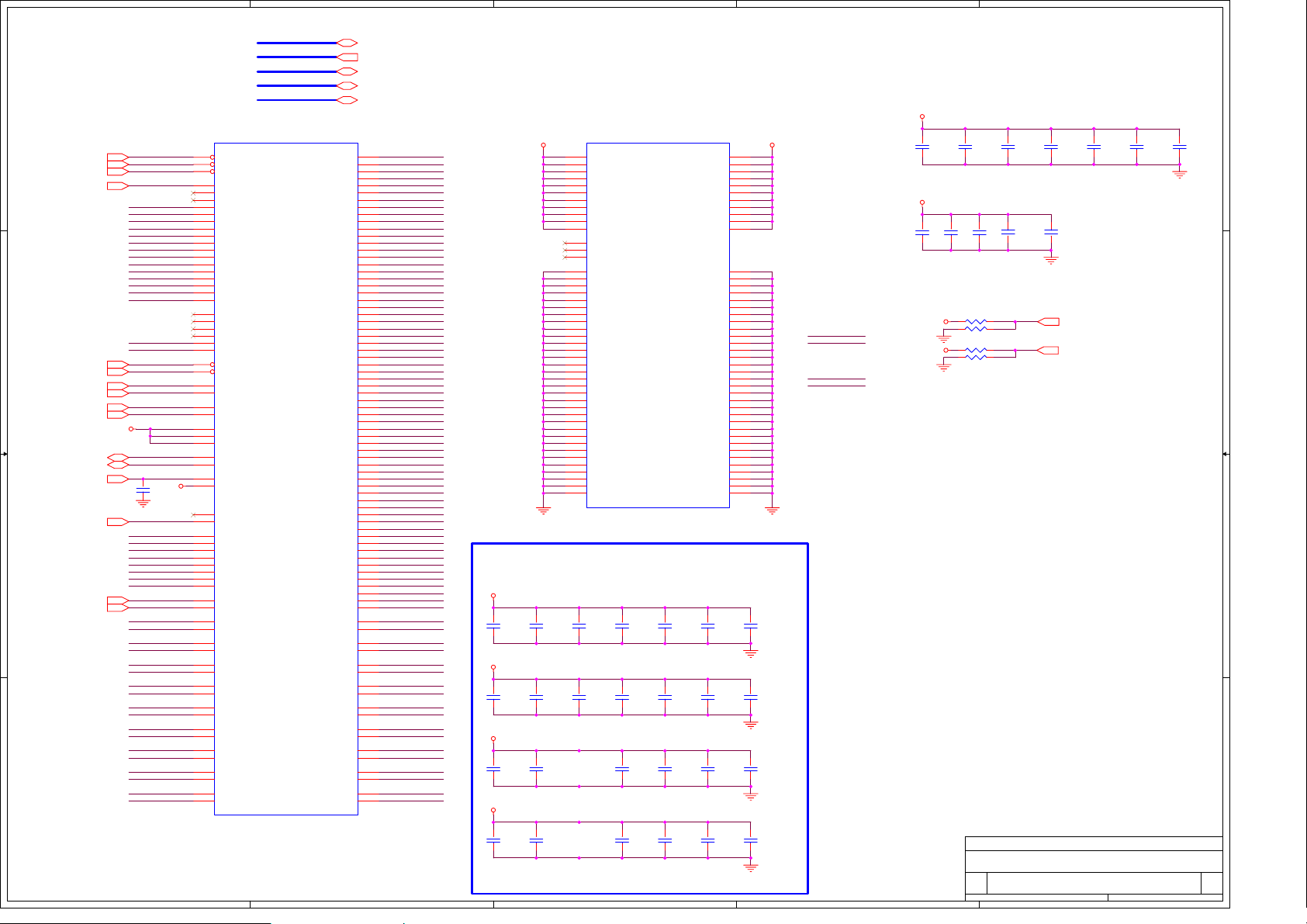

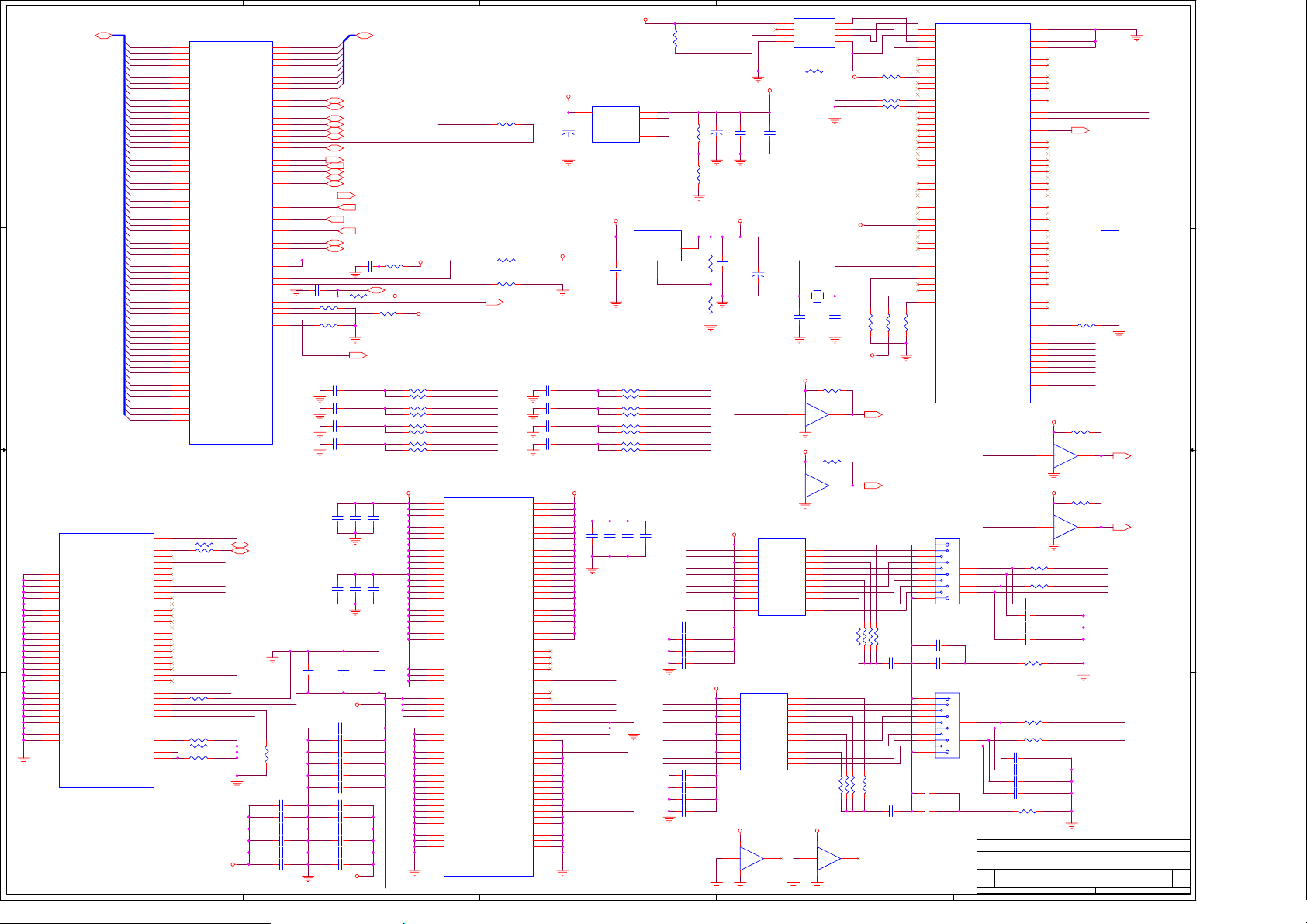

Page 4

5

4

3

2

1

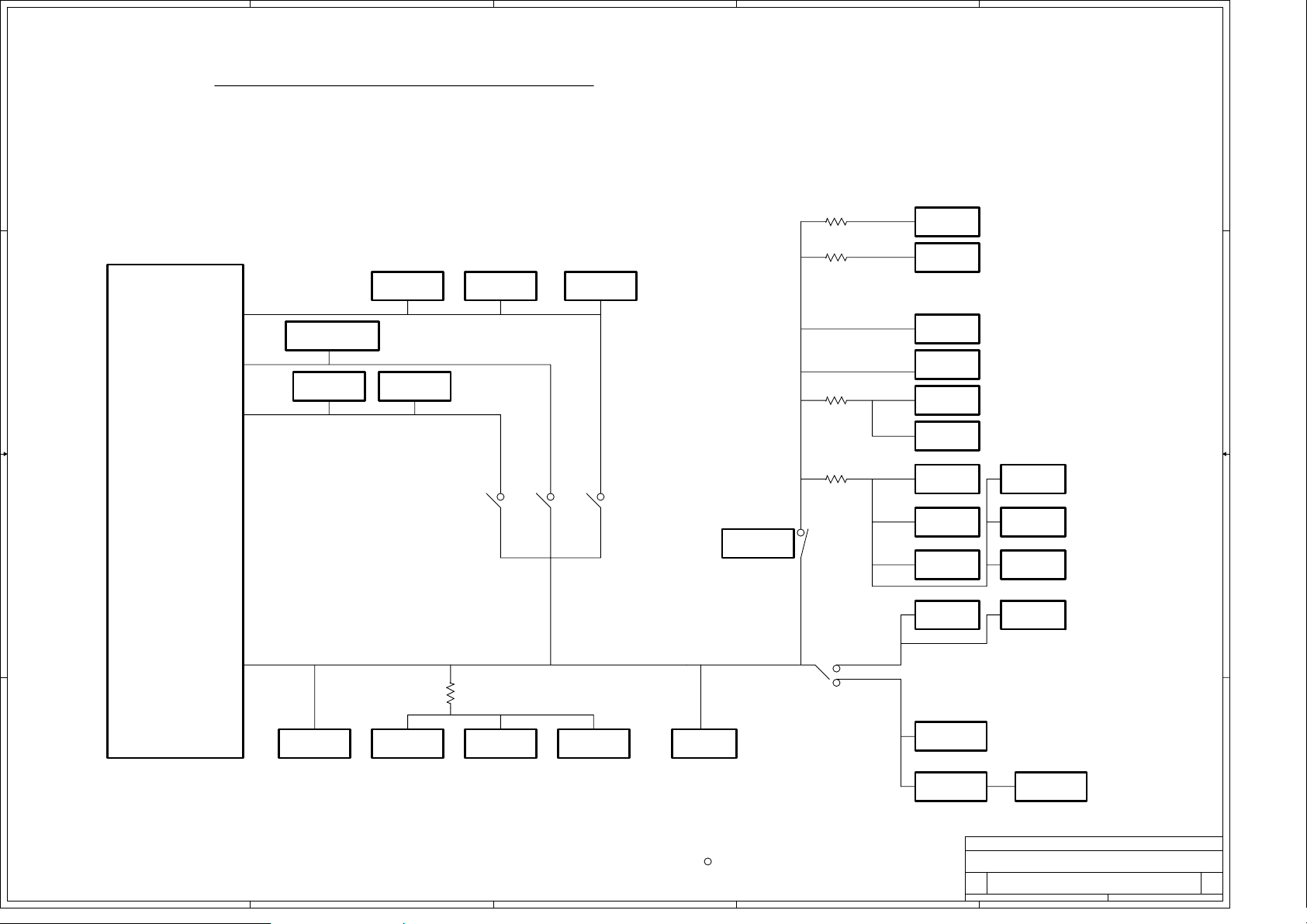

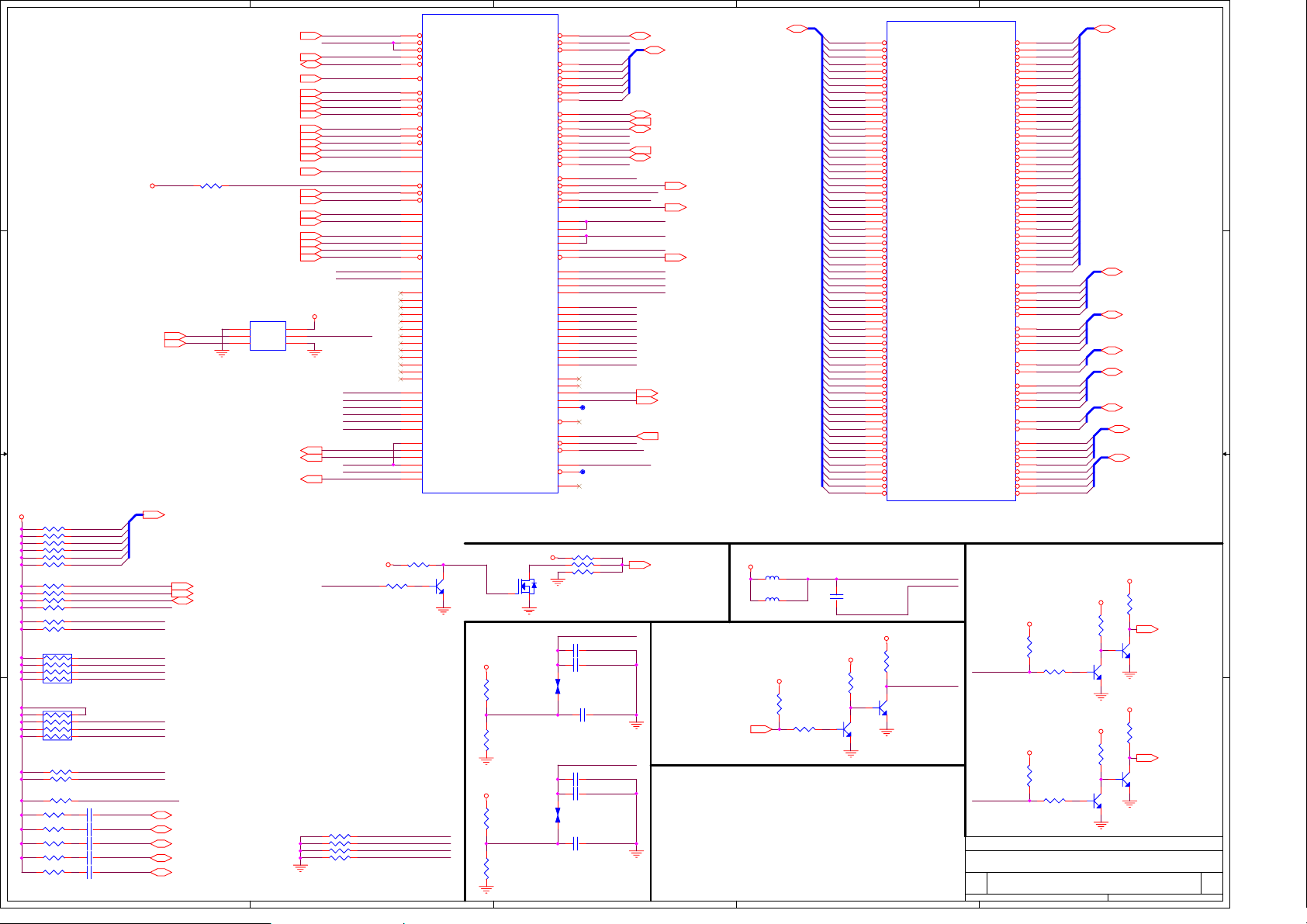

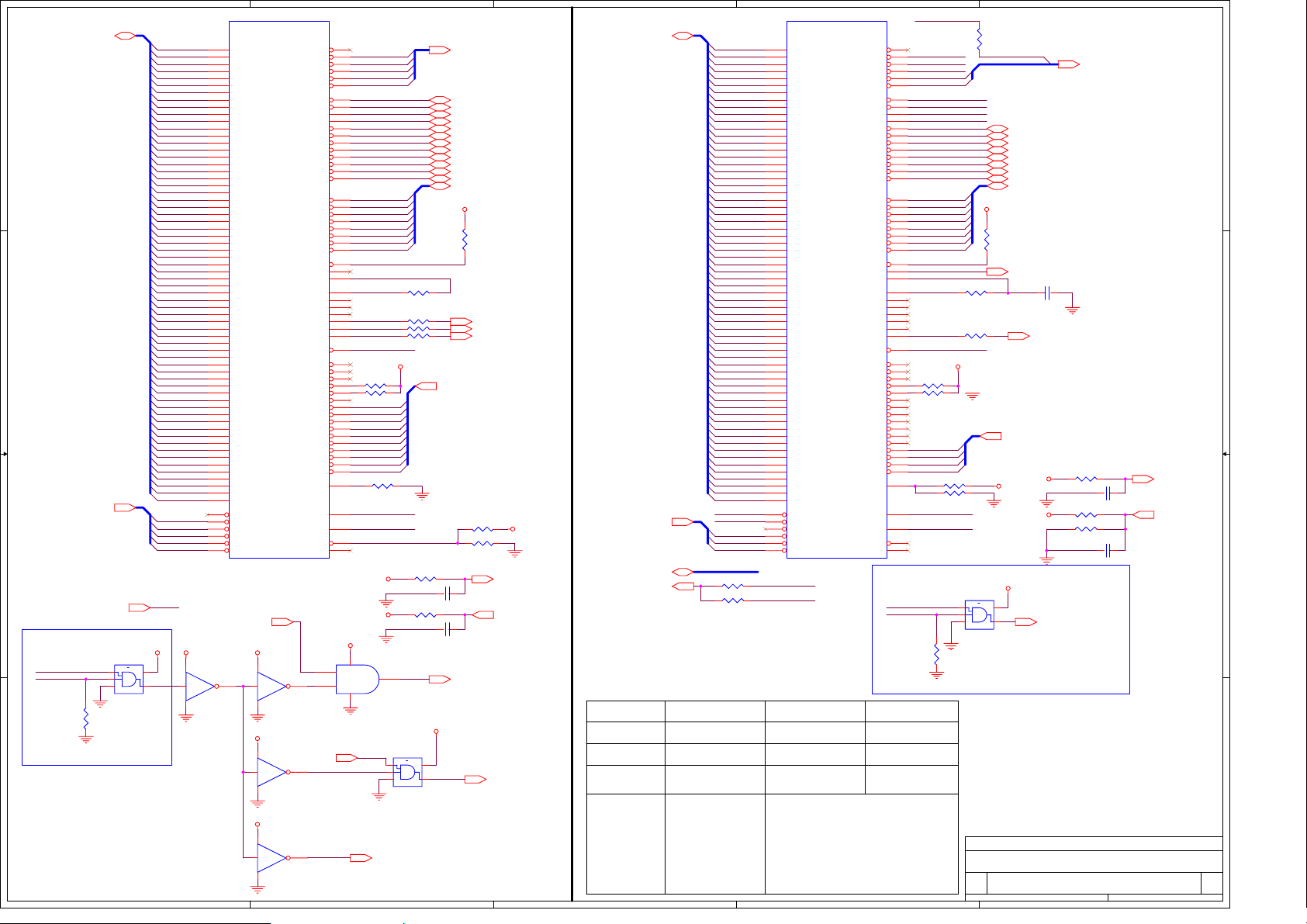

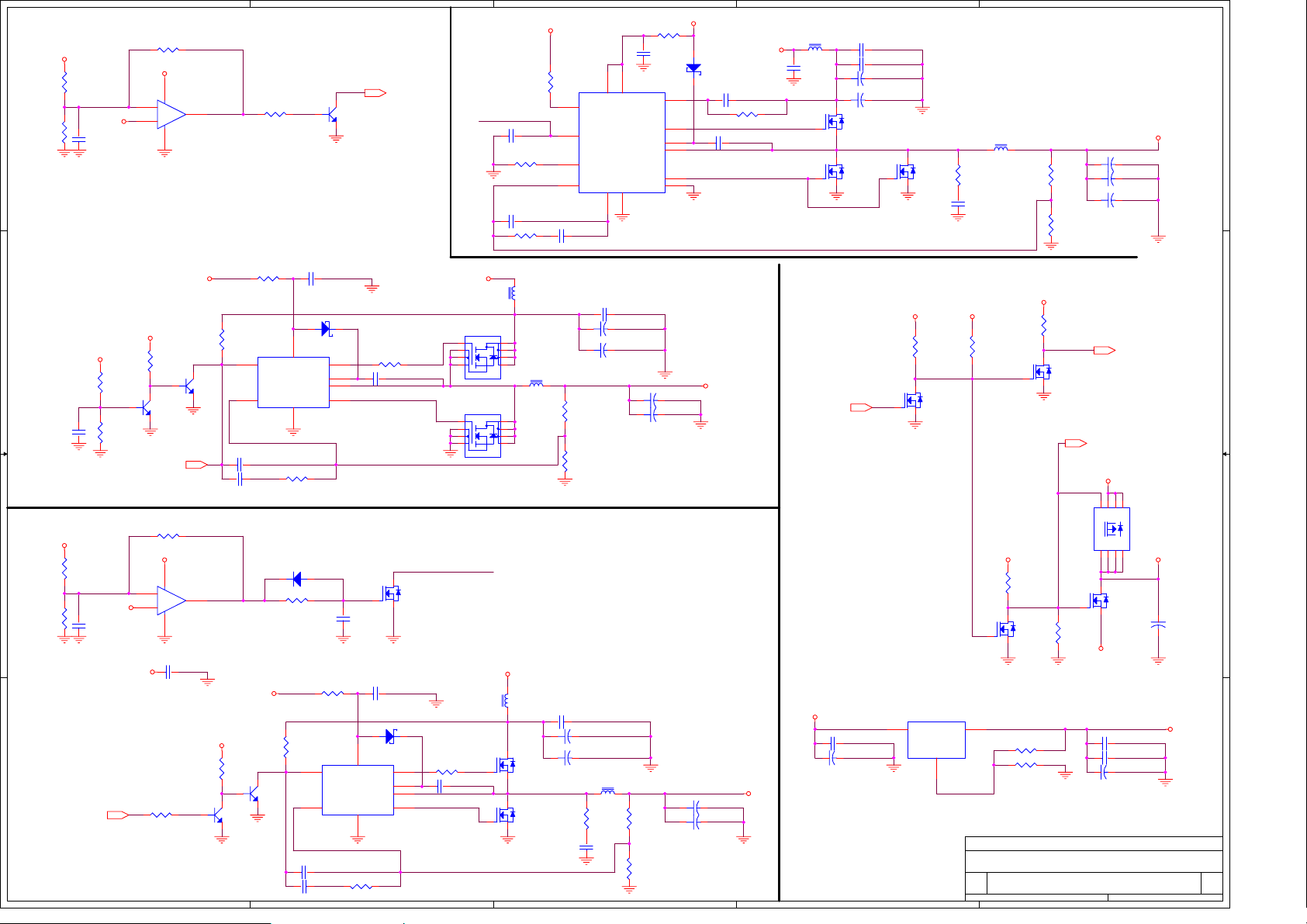

MS-9146 SMBus BLOCK DIAGRAM

D D

R13

SMB_MCH

0-OHM

R13

SMB_PXH

0-OHM

PCI_I2C

SMB_PCI

PCI 1

Add:0x??

PCI 4

Add:0x??

PCIEX 1

Add:0x??

82546

C C

LAN_I2C

IPMB_I2C

I2C1_3V

B B

I2C3_5VSB

SMB_LAN

SMB_IPMB

NC

NC

Add:0x??

IPMI_5P

Add:0x??

CN14 CN28

IPMI_4P

Add:0x??

PRESENCE1=0

** BMC not install**

VRM_PWRGD=1

**SYS_PWRGD**

PCA9515

Repeater

SMB_MAIN

R13

SMB_CLK

0-OHM

(EMPTY)

R13

SMB_DIMM

0-OHM

(EMPTY)

MCH

Add:0x60

PXH

Add:0xC0

AD7643_1

Add:0x5A

AD7643_2

Add:0x5C

CK409B

Add:0xD2

DB800

Add:0xDC

DIMMA1

Add:0xA0

DIMMA2

Add:0xA2

DIMMA3

Add:0xA4

U101

U104

DIMMB1

Add:0xA8

DIMMB2

Add:0xAA

DIMMB3

Add:0xAC

Add:0xA6

I2C2_3VSB

BMC Connector

A A

5

SMB_ICH

ICH5

Add:0x44

PCA9557_1

Add:0x30

U1 U99 U158 U54U43

4

SMB_ICH

R

SMB_HMLIGHT

PCA9557_2

Add:0x32

PCA9557_2

Add:0x34

W83791

Add:0x58

3

SMB_DIMMA4_B4

SMB_FRU

For Level Shift

2

U31

FRU

Add:0xAE

U26 CN4

PCA9515

Repeater

Add:0xAE

PWR_SP

Add:0xA6

Title

SMBUS Block Diagram

Size Document Number Rev

MS9146 200

Date: Sheet

441Thursday, November 11, 2004

1

of

DIMMB4DIMMA4

Page 5

5

P3V3

B15

300_0805

D D

P3V3

B14

300_0805

Power => CK409B Power => DB800

R324

10

C234

104P

C238

10u_0805

C190

104P

C182

10u_0805

C750

104P

C748

104P

C749

104P

C751

104P

C747

104P

C752

104P

C746

104P

C236

10u_0805

VCC3_CLKA

VCC3_CLKB

VCC3_CLK

P3V3

P3V3

B13

300_0805

B12

300_0805

4

C771

104P

C845

104P

C827

104P

C820

104P

C842

104P

C231

10u_0805

C237

104P

C233

10u_0805

VCC3_SRCLK

VCC3_SRCLK2

SMBDATA_CLK

SMBCLK_CLK

VCC3_CLK

R360

x_4.7K

CK409B_PWRDWN_#

R328

5.1K

P3V3

F_SEL1

0

0

1

1

3

R334

5.1K

CP9

x_COPPER

CP10 x_COPPER

CP11 x_COPPER

F_SEL0

FREQ.

0

100 Mhz

133 Mhz

1

200 Mhz

0

166 Mhz

1

BI SMBDATA_MAIN 11,13,24,30,31

BI SMBCLK_MAIN 11,13,24,30,31

IN VRM_PWRGD 21,31,38

2

P3V3

147

13 12

UC1F

74LVC07

P3V3

UG1C

14

9

10

7

74LVC86

P3V3

UG1D

14

12

13

7

74LVC86

1

8

11

12

13

P3V3_AUX

147

11

UL1D

74HC08

U70

CK409B

VCC3_CLKA

VCC3_CLK

C C

VCC3_CLKB

C230

33p

C223

33p

SMBDATA_CLK

SMBCLK_CLK

INCPU0_BSEL06,38

INCPU0_BSEL16,38

CK409B_PWRDWN_#

INCLK_VTT_PWRGD_#38

R419 475RST

B B

SRC_100CLK_P

SRC_100CLK_N

VCC3_SRCLK

VCC3_SRCLK

VCC3_SRCLK

VCC3_SRCLK

VCC3_SRCLK

A A

R430 10K

R521 10K

SMBCLK_CLK

SMBDATA_CLK

CK409B_PWRDWN_#

R512 10K

R513 10K

R429 475RST

R473 1K

VCC3_SRCLK2

VCC3_SRCLK

55

VDD_A

24

VDD_3V66

48

VDD_CPU

42

VDD_CPU

16

VDD_PCI

10

VDD_PCI

36

VDD_SRC

3

VDD_REF

34

VDD_48

4

XTAL_IN

Y114.318MHZ32P_D

5

XTAL_OUT

30

SDAT

28

SCLK

51

FS_A

56

FS_B

21

PWRDWN_N

35

VTT_PWRGD_N

52

IREF

54

VSS_A

25

VSS_3V66

45

VSS_CPU

17

VSS_PCI

11

VSS_PCI

39

VSS_SRC

33

VSS_48

53

VSS_IREF

6

VSS_REF

CK409B

U79

DB800

DB800

4

SRC_IN_P

5

SRC_IN_N

1

SRC_DIV2_N

22

PLL

23

SCL

24

SDA

26

PWRDWN_N

27

SRC_STOP_N

28

HIGH_BW_N

45

LOCK

46

IREF

44

OE_7

36

OE_6

35

OE_5

43

OE_4

7

OE_3

15

OE_2

14

OE_1

6

OE_0

48

VDD_A

39

VDD4

31

VDD3

19

VDD2

11

VDD1

2

VDD0

5

VCH/3V66_4

REF1

REF0

CPU_3_P

CPU_3_N

CPU_2_P

CPU_2_N

CPU_1_P

CPU_1_N

CPU_0_P

CPU_0_N

PCIF2

PCIF1

PCIF0

PCI6

PCI5

PCI4

PCI3

PCI2

PCI1

PCI0

DOT_48

USB_48

3V66_3

3V66_2

3V66_1

3V66_0

SRC_P

SRC_N

DIF_7_P

DIF_7_N

DIF_6_P

DIF_6_N

DIF_5_P

DIF_5_N

DIF_4_P

DIF_4_N

DIF_3_P

DIF_3_N

DIF_2_P

DIF_2_N

DIF_1_P

DIF_1_N

DIF_0_P

DIF_0_N

VSS_A

VSS5

VSS4

VSS3

VSS2

VSS1

VSS0

2

ICH_14CLK_R

1

MCH_BCLK_P_R

50

MCH_BCLK_N_R

49

ITP_BCLK_P_R

47

ITP_BCLK_N_R

46

P1_BCLK_P_R

44

P1_BCLK_N_R

43

P0_BCLK_P_R

41

P0_BCLK_N_R

40

SIO_33CLK_R

9

8

ICH_33CLK_R

7

PCI_VGACLK_R

20

19

FWH_CLK_R

18

15

PCI_SLOTCLK_R

14

13

BMC_CLK_R

12

SIO_48CLK_R

32

ICH_48CLK_R

31

29

ICH_66CLK_R

27

26

MCH_66CLK_R

23

22

SRC_100CLK_P_R

38

SRC_100CLK_N_R

37

LAN_100CLK_P_R

42

LAN_100CLK_N_R

41

SLOT0_100CLK_P_R

38

SLOT0_100CLK_N_R

37

SLOT1_100CLK_P_R SLOT1_100CLK_P

34

SLOT1_100CLK_N_R

33

PXH_100CLK_P_R

30

PXH_100CLK_N_R

29

R508 X_33

20

R514 X_33

21

R493 x_33

16

R498 x_33

17

MCH_100CLK_P_R

12

MCH_100CLK_N_R

13

ICH_100CLK_P_R

8

ICH_100CLK_N_R

9

47

40

32

25

18

10

3

R412 33

R411 33

R407 33

R400 33

R392 33

R384 33

R378 33

R371 33

R363 33

R385 33

R393 33

R368 33

R369 33

R376 33

R379 33

R339 33

R340 33

R341 33

R352 33

R354 33

R344 33

R492 x_49.9RST

R497 x_49.9RST

SLOT2_100CLK_P

SLOT2_100CLK_N

4

R433 33

R440 33

R450 33

R464 33

R480 X_33

R489 X_33

R495 33

R503 33

SLOT2_100CLK_P

SLOT2_100CLK_N

R467 33

R477 33

R437 33

R444 33

OUT ICH_14CLK 21

MCH_BCLK_P

MCH_BCLK_N

ITP_BCLK_P

ITP_BCLK_N

P1_BCLK_P

P1_BCLK_N

P0_BCLK_P

P0_BCLK_N

OUT SIO_33CLK 29

OUT ICH_33CLK 21

OUT PCI_VGA_33CLK 36

OUT FWH_33CLK 23

OUT PCI_SLOT_33CLK 40

OUT BMC_33CLK 31

OUT SIO_48CLK 29

OUT ICH_48CLK 21

OUT ICH_66CLK 21

OUT MCH_66CLK 11

SRC_100CLK_P

SRC_100CLK_N

LAN_100CLK_P

LAN_100CLK_N

SLOT0_100CLK_P

SLOT0_100CLK_N

SLOT1_100CLK_N

PXH_100CLK_P

PXH_100CLK_N

MCH_100CLK_P

MCH_100CLK_N

ICH_100CLK_P

ICH_100CLK_N

OUT SLOT2_100CLK_P 28

OUT SLOT2_100CLK_N 28

R507 X_49.9RST

R515 X_49.9RST

P0_BCLK_P

P0_BCLK_N

R362 49.9RST

R370 49.9RST

P1_BCLK_P

P1_BCLK_N

R377 49.9RST

R383 49.9RST

MCH_BCLK_P

MCH_BCLK_N

R406 49.9RST

R413 49.9RST

ITP_BCLK_P

ITP_BCLK_N

R391 49.9RST

R399 49.9RST

SRC_100CLK_P

SRC_100CLK_N

R343 49.9RST

R353 49.9RST

LAN_100CLK_P

LAN_100CLK_N

R441 49.9RST

R434 49.9RST

SLOT0_100CLK_P

SLOT0_100CLK_N

R465 49.9RST

R451 49.9RST

PXH_100CLK_P

PXH_100CLK_N

R504 49.9RST

R496 49.9RST

MCH_100CLK_P

MCH_100CLK_N

R476 49.9RST

R466 49.9RST

ICH_100CLK_P

ICH_100CLK_N

R443 49.9RST

R436 49.9RST

SLOT1_100CLK_P

SLOT1_100CLK_N

R490 X_49.9RST

R481 X_49.9RST

3

OUT P0_BCLK_P 6

OUT P0_BCLK_N 6

OUT P1_BCLK_P 8

OUT P1_BCLK_N 8

OUT MCH_BCLK_P 11

OUT MCH_BCLK_N 11

OUT ITP_BCLK_P 12

OUT ITP_BCLK_N 12

OUT SLOT0_100CLK_P 28

OUT SLOT0_100CLK_N 28

OUT PXH_100CLK_P 24

OUT PXH_100CLK_N 24

OUT MCH_100CLK_P 11

OUT MCH_100CLK_N 11

OUT ICH_100CLK_P 21

OUT ICH_100CLK_N 21

C222

x_22p

C220

x_22p

C217

x_22p

C216

x_22p

C199

x_22p

C194

x_22p

C187

x_22p

C193

x_22p

C235

x_22p

C214

x_22p

2

ICH_33CLK

SIO_33CLK

BMC_33CLK

FWH_33CLK

MCH_66CLK

ICH_66CLK

ICH_48CLK

SIO_48CLK

ICH_14CLK

PCI_VGA_33CLK

CN10

2

1

x_1X2

Layer 1, Width=6mil

50ohm

CN14

110ohm_N

2

1

x_1X2

Layer 8, Differential Pair,

Width=4mil, Space=6mil 110ohm

CN15

85ohm_N

2

1

x_1X2

Layer 6, Differential Pair,

Width=4mil, Space=5mil 85ohm

Title

Size Document Number Rev

Date: Sheet

CN9

110ohm_P

2

1

x_1X2

CN13

85ohm_P

2

1

x_1X2

CN12

2

1

x_1X2

Layer 8, Width=6mil

50ohm

CN11

2

1

x_1X2

Layer 3, Width=4mil

50ohm

Clock

MS9146 200

P3V3

147

13

12

1

UM1D

74LVC32

541Friday, January 21, 2005

11

of

Page 6

5

INSB_BPRI_#8,11

SB_CPU0_BREQ_23_#

SB_BREQ_#1

SB_BREQ_#0

SB_CPURST_#

D D

P_VTT

R27

270

U24

6

INICH_CPU_SMI_#8,21,31

C C

P_VTT

B B

A A

CPU0_DISABLE_#34

R39 51

R133 51

R40 51

R108 510

R102 510

R116 510

R208 510

R127 510

R149 510

R139 51

R46 51

R836 51

R45 51

R47 51

R43 51

R131 51

R155 51

R42 51

R787 100RST

R800 100RST

51-8P4R

7 8

5 6

3 4

1 2

RN78

1 2

3 4

5 6

7 8

RN79

51-8P4R

R41 x_51

R792 x_51

R786 51

R785 51

R790 51

R797 51

SB_CPU0_IERR_#

CPU0_VID5

CPU0_VID4

CPU0_VID3

CPU0_VID2

CPU0_VID1

CPU0_VID0

CPU_BPM_#5

CPU_BPM_#4

CPU_BPM_#3

CPU_BPM_#2

CPU_BPM_#1

CPU_BPM_#0

PU_ODTEN_CPU0

PU_COMP3_CPU0

PU_COMP2_CPU0

IN

IN ITP_TMS 8,12

OUT SB_CPU0_PROCHOT_# 34

OUT CPU0_VID[0..5] 7,30

BI CPU_BPM_#[0..5] 8,12

OUT SB_CPU_FERR_# 8,21

OUT SB_CPU0_THERMTRIP_# 37

PU_CPU0_5

PU_CPU0_7

PU_CPU0_1

PU_CPU0_3

PU_CPU0_2

PU_CPU0_6

PU_CPU0_4

OUT SB_CPURST_#_R 12

5

Pull up when ODT disable

Pull up when ODT disable

IN SB_BREQ_#1 8,11

BI SB_BREQ_#0 8,11

IN SB_CPURST_# 8,11

PU_CPU0_0

PU_CPU0_8

SB_CPU0_BREQ_23_#

R798 1K

4 5

1

PI5C3303

BE = 1

B---C

Also Pullup in ICH5

VCC

A

BC

BE

GND

P_VTT

SB_CPU_A20M_#

SB_CPU_IGNNE_#

SB_CPU_INIT_#

SB_CPU_NMI

SB_CPU_INTR

CPU_PWR_GD

CPU0_SMI_#

SB_CPU_SLP_#

SB_CPU_STPCLK_#

INP0_BCLK_N5

INP0_BCLK_P5

INITP_TCK012

INITP_TDI_P012

INITP_TRST_#8,12

SB_CPU0_BSEL1

SB_CPU0_BSEL0

P5V

2

CPU0_SMI_#

3

CPU0_VID5

CPU0_VID4

CPU0_VID3

CPU0_VID2

CPU0_VID1

CPU0_VID0

OUTCPU0_VCC_SEN7

OUTVTT_EN8,39

CPU0_VCCA

CPU0_VSSA

OUTCPU0_VSS_SEN7

R137 220

R119 220

R44 220

R37 220

R273 220

R122 220

R788 220

R144 1.8K

R267 300

R791 49.9RST

R801 49.9RST

R799 X_0

4

CPU1A

D23

BPRI_N

D10

BR3_N

E11

BR2_N

F12

BR1_N

D20

BR0_N

Y8

RESET_N

F21

INSB_RS_#28,11

INSB_RS_#18,11

INSB_RS_#08,11

INSB_RSP_#8,11

ITP_TMS

SB_CPU0_IERR_#

RS2_N

D22

RS1_N

E21

RS0_N

C6

RSP_N

F27

A20M_N

C26

IGNNE_N

D6

INIT_N

G23

LINT1_NMI

B24

LINT0_INTR

AB7

PWRGOOD

C27

SMI_N

AE6

SLP_N

D4

STPCLK_N

W5

BCLK1

Y4

BCLK0

E24

TCK

C24

TDI

A25

TMS

F24

TRST_N

AB3

BSEL1

AA3

BSEL0

AE29

RESERVED16

AE28

RESERVED

Y3

RSVD_15

AD29

RSVD_14

AD28

RSVD_13

AC29

RSVD_12

AB29

RSVD_10

AB28

RSVD_9

AA29

RSVD_8

AA28

RSVD_7

AE15

RSVD_3

AC1

RSVD_2

AE16

RSVD_1

A1

VID5

B3

VID4

C3

VID3

D3

VID2

E3

VID1

F3

VID0

AD4

VCCIOPLL

B27

VCCSENSE

E1

VTTEN

AB4

VCCA

AA5

VSSA

D26

VSSSENSE

E9G022-001

P3V3

4.7K

R135

IN SB_CPU_A20M_# 8,21

IN SB_CPU_IGNNE_# 8,21

IN SB_CPU_INIT_# 8,21,23

IN SB_CPU_INTR 8,21

IN SB_CPU_SLP_# 8,21

IN

SB_CPU_STPCLK_# 8,21

IN SB_CPU_NMI 8,38

CPU0_SMI_#

IN CPU_PWR_GD 8,21

PD_COMP1_CPU0

PD_COMP0_CPU0

CPU0_SLEW_CTRL

4

NOCONA 1/5

BreakPoint

Monitor

Machine

CheckError

(RSVD_11)COMP2

(RSVD_6)TESTHI8

(RSVD_4)TESTHI7

(RESERVED17)TEST_BUS

OPTPMPZED_COMPAT_N

R156

4.7K

B

Q17

E C

MMBT3904

P_VTT

P_VTT

ADS_N

BINIT_N

BNR_N

BPM5_N

BPM4_N

BPM3_N

BPM2_N

BPM1_N

BPM0_N

DBSY_N

DEFER_N

DRDY_N

HIT_N

HITM_N

TRDY_N

LOCK_N

MCERR_N

IERR_N

FERR_N_PBE_N

THERMTRIP_N

PROCHOT_N

GTLREF3

GTLREF2

GTLREF1

GTLREF0

ODTEN

SKTOCC_N

(RSVD_5)COMP3

COMP1

COMP0

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

SMB_PRT

VCCPLL

THERMDC

THERMDA

BOOT_SELECT

RSVD

VIDPWRGD

FORCEPR_N

SLEW_CTRL

G

R183

49.9RST

CPU0_VREF0

R198

90.9RST

R176

49.9RST

CPU0_VREF3

R171

90.9RST

TDO

NC

P3V3

DS

Q12

2N7002

SOT23SGD

D19

F11

F20

E4

E8

F5

E7

F8

F6

F18

C23

E18

E22

A23

E19

A17

D7

E5

E27

F26

B25

E25

F9

F23

W9

W23

B5

A3

D25

AC28

E16

AD16

Y29

A26

AE5

AD5

AA7

Y6

W8

W7

W6

AE4

AD1

Y28

Y27

G7

W3

B1

A16

A15

AC30

C1

AE30

R104 10K

R105 1K

R106 10K

3

BI SB_ADS_# 8,11

BI SB_BINIT_# 8,11

BI SB_BNR_# 8,11

CPU_BPM_#5

CPU_BPM_#4

CPU_BPM_#3

CPU_BPM_#2

CPU_BPM_#1

CPU_BPM_#0

BI SB_DBSY_# 8,11

IN SB_DEFER_# 8,11

BI SB_DRDY_# 8,11

BI SB_HIT_# 8,11

BI SB_HITM_# 8,11

IN SB_TRDY_# 8,11

BI SB_LOCK_# 8,11

SB_CPU0_IERR_#

SB_CPU_FERR_#

SB_CPU0_THERMTRIP_#

SB_CPU0_PROCHOT_#

BI SB_MCERR_# 8,11

OUT ITP_TDO_P0 12

VREF_P_VTT_CPU0_3

VREF_P_VTT_CPU0_0

PU_ODTEN_CPU0

OUT CPU0_SKTOCC_# 34,38

PU_COMP3_CPU0

PU_COMP2_CPU0

PD_COMP1_CPU0

PD_COMP0_CPU0

PU_CPU0_8

PU_CPU0_0

PU_CPU0_5

PU_CPU0_6

PU_CPU0_1

PU_CPU0_7

PU_CPU0_3

PU_CPU0_2

PU_CPU0_4

OUT CPU0_THERMDC 30

TP14

CPU0_FORCEPR_#

CPU0_SLEW_CTRL

TP1

These two TP have on-die

pull up resistor

VREF_P_VTT_CPU0_0

C113

220p

C114

220p

CP6

x_COPPER

C90

1u

VREF_P_VTT_CPU0_3

C58

220p

C59

220p

CP5

x_COPPER

C68

1u

OUT CPU0_THERMDA 30

OUT SB_CPU0_IERR 34

3

IN VID_PWRGD 8,38

BI SB_TEST_BUS 8

CPU0

FORCEPR_#

P_VTT

L2

10u165MA1210

L1

10u165MA1210

P3V3

INSB_CPU0_FORCEPR_#29

R29

2.7K

BISB_D_#[0..63]8,11

4.7K

R28

SB_D_#63

SB_D_#62

SB_D_#61

SB_D_#60

SB_D_#59

SB_D_#58

SB_D_#57

SB_D_#56

SB_D_#55

SB_D_#54

SB_D_#53

SB_D_#52

SB_D_#51

SB_D_#50

SB_D_#49

SB_D_#48

SB_D_#47

SB_D_#46

SB_D_#45

SB_D_#44

SB_D_#43

SB_D_#42

SB_D_#41

SB_D_#40

SB_D_#39

SB_D_#38

SB_D_#37

SB_D_#36

SB_D_#35

SB_D_#34

SB_D_#33

SB_D_#32

SB_D_#31

SB_D_#30

SB_D_#29

SB_D_#28

SB_D_#27

SB_D_#26

SB_D_#25

SB_D_#24

SB_D_#23

SB_D_#22

SB_D_#21

SB_D_#20

SB_D_#19

SB_D_#18

SB_D_#17

SB_D_#16

SB_D_#15

SB_D_#14

SB_D_#13

SB_D_#12

SB_D_#11

SB_D_#10

SB_D_#9

SB_D_#8

SB_D_#7

SB_D_#6

SB_D_#5

SB_D_#4

SB_D_#3

SB_D_#2

SB_D_#1

SB_D_#0

R32

4.7K

B

C191

22u_1210

P3V3

E C

2

AB6

Y9

AA8

AC5

AC6

AE7

AD7

AC8

AB10

AA10

AA11

AB13

AB12

AC14

AA14

AA13

AC9

AD8

AD10

AE9

AC11

AE10

AC12

AD11

AD14

AD13

AB15

AD18

AE13

AC17

AA16

AB16

AB17

AD19

AD21

AE20

AE22

AC21

AC20

AA18

AC23

AE23

AD24

AC24

AE25

AD25

AC26

AE26

AA19

AB19

AB22

AB20

AA21

AA22

AB23

AB25

AB26

AA24

Y23

AD27

AA25

Y24

AA27

Y26

B

Q2

MMBT3904

2

CPU1B

NOCONA 2/5

D63_N

D62_N

D61_N

D60_N

D59_N

D58_N

D57_N

D56_N

D55_N

D54_N

D53_N

D52_N

D51_N

D50_N

D49_N

D48_N

D47_N

D46_N

D45_N

D44_N

D43_N

D42_N

D41_N

D40_N

D39_N

D38_N

D37_N

D36_N

D35_N

D34_N

D33_N

D32_N

D31_N

D30_N

D29_N

D28_N

D27_N

D26_N

D25_N

D24_N

D23_N

D22_N

D21_N

D20_N

D19_N

D18_N

D17_N

D16_N

D15_N

D14_N

D13_N

D12_N

D11_N

D10_N

D9_N

D8_N

D7_N

D6_N

D5_N

D4_N

D3_N

D2_N

D1_N

D0_N

E9G022-001

CPU0_VCCA

CPU0_VSSA

CPU0_FORCEPR_#

Q3

E C

MMBT3904

1

SB_A_#35

C8

A35_N

SB_A_#34

C9

A34_N

SB_A_#33

A7

A33_N

SB_A_#32

A6

A32_N

SB_A_#31

B7

A31_N

SB_A_#30

C11

A30_N

SB_A_#29

D12

A29_N

SB_A_#28

E13

A28_N

SB_A_#27

B8

A27_N

SB_A_#26

A9

A26_N

SB_A_#25

D13

A25_N

SB_A_#24

E14

A24_N

SB_A_#23

C12

A23_N

SB_A_#22

B11

A22_N

SB_A_#21

B10

A21_N

SB_A_#20

A10

A20_N

SB_A_#19

F15

A19_N

SB_A_#18

D15

A18_N

SB_A_#17

D16

A17_N

SB_A_#16

C14

A16_N

SB_A_#15

C15

A15_N

SB_A_#14

A12

A14_N

SB_A_#13

B13

A13_N

SB_A_#12

B14

A12_N

SB_A_#11

B16

A11_N

SB_A_#10

A13

A10_N

SB_A_#9

D17

A9_N

SB_A_#8

C17

A8_N

SB_A_#7

A19

A7_N

SB_A_#6

C18

A6_N

SB_A_#5

B18

A5_N

SB_A_#4

A20

A4_N

SB_A_#3

A22

A3_N

SB_REQ_#4

B22

REQ4_N

REQ3_N

REQ2_N

REQ1_N

REQ0_N

Indicate the

polarity of the

SB_D_#[0..63]

Address Parity

DBI3_N

DBI2_N

DBI1_N

DBI0_N

Data Parity

ADSTB1_N

ADSTB0_N

DSTBP3_N

DSTBP2_N

DSTBP1_N

DSTBP0_N

DSTBN3_N

DSTBN2_N

DSTBN1_N

DSTBN0_N

Frequency

Select

SB_CPU0_BSEL1

SB_CPU0_BSEL0

Title

Size Document Number Rev

Date: Sheet

SB_REQ_#3

C20

SB_REQ_#2

C21

SB_REQ_#1

B21

SB_REQ_#0

B19

SB_DBI_#3

AB9

SB_DBI_#2

AE12

SB_DBI_#1

AD22

SB_DBI_#0

AC27

SB_AP_#1

D9

AP1_N

SB_AP_#0

E10

AP0_N

DP3_N

DP2_N

DP1_N

DP0_N

CPU0 Signal

MS9146 200

AE17

AC15

AE19

AC18

F14

F17

Y11

Y14

Y17

Y20

Y12

Y15

Y18

Y21

P_VTT

P_VTT

SB_DP_#3

SB_DP_#2

SB_DP_#1

SB_DP_#0

SB_ADSTB_#1

SB_ADSTB_#0

SB_DSTBP_#3

SB_DSTBP_#2

SB_DSTBP_#1

SB_DSTBP_#0

SB_DSTBN_#3

SB_DSTBN_#2

SB_DSTBN_#1

SB_DSTBN_#0

R226

510

R219

4.7K

R375

510

R374

4.7K

BI SB_A_#[3..35] 8,11

BI SB_REQ_#[0..4] 8,11

BI SB_DBI_#[0..3] 8,11

BI SB_AP_#[0..1] 8,11

BI SB_DP_#[0..3] 8,11

BI SB_ADSTB_#[0..1] 8,11

P3V3

R187

4.7K

B

B

Q30

E C

MMBT3904

P3V3

R367

4.7K

B

B

Q47

E C

MMBT3904

1

BI SB_DSTBP_#[0..3] 8,11

BI SB_DSTBN_#[0..3] 8,11

P3V3

R160

4.7K

OUT CPU0_BSEL1 5,38

Q26

E C

MMBT3904

P3V3

R417

4.7K

OUT CPU0_BSEL0 5,38

Q48

E C

MMBT3904

641Friday, January 21, 2005

of

Page 7

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

5

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

M30

M28

M26

M24

M8

M6

M4

M2

5

CPU1D

P_VCCP0 P_VTTP_VCCP0

NOCONA 4/5

L28

VCC

L26

VCC

L24

VCC

L8

VCC

L6

VCC

L4

VCC

L2

VCC

K31

VCC

K29

VCC

K27

VCC

K25

VCC

K23

VCC

K9

VCC

K7

VCC

K5

VCC

K3

VCC

K1

VCC

J30

VCC

J28

VCC

J26

VCC

J24

VCC

J8

VCC

J6

VCC

J4

VCC

J2

VCC

H31

VCC

H29

VCC

H27

VCC

H25

VCC

H23

VCC

H9

VCC

H7

VCC

H5

VCC

H3

VCC

H1

VCC

G30

VCC

G28

VCC

G26

VCC

G24

VCC

G8

VCC

G6

VCC

G4

VCC

G2

VCC

F31

VCC

F29

VCC

F22

VCC

F16

VCC

F4

VCC

F1

VCC

E30

VCC

E28

VCC

E26

VCC

E20

VCC

E6

VCC

E2

VCC

D31

VCC

D29

VCC

D24

VCC

D18

VCC

D14

VCC

D8

VCC

D1

VCC

C30

VCC

C28

VCC

C22

VCC

C16

VCC

C4

VCC

C2

VCC

B31

VCC

B29

VCC

B26

VCC

B20

VCC

B6

VCC

A30

VCC

A28

VCC

A24

VCC

A18

VCC

A14

VCC

A8

VCC

A2

VCC

E9G022-001

R272 20KST

R275 3KST

R276 20KST

P_VCCP0

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

L30

AA31

AA26

AA20

AA6

AA4

AA1

Y30

Y22

Y16

Y2

W31

W29

W27

W25

W1

V30

V28

V26

V24

V8

V6

V4

V2

U31

U29

U27

U25

U23

U9

U7

U5

U3

U1

T30

T28

T26

T24

T8

T6

T4

T2

R31

R29

R27

R25

R23

R9

R7

R5

R3

R1

P30

P28

P26

P24

P8

P6

P4

P2

N31

N29

N27

N25

N23

N9

N7

N5

N3

N1

M31

M29

M27

M25

M23

M9

M7

M5

M3

M1

INCPU0_VCC_SEN6

INCPU0_VSS_SEN6

C136 x_C

R796 X_0

R795 0

R794 X_0

R793 0

CPU1C

NOCONA 3/5

L31

GND

L29

GND

L27

GND

L25

GND

L23

GND

L9

GND

L7

GND

L5

GND

L3

GND

L1

GND

K30

GND

K28

D D

C C

B B

A A

GND

K26

GND

K24

GND

K8

GND

K6

GND

K4

GND

K2

GND

J31

GND

J29

GND

J27

GND

J25

GND

J23

GND

J9

GND

J7

GND

J5

GND

J3

GND

J1

GND

H30

GND

H28

GND

H26

GND

H24

GND

H8

GND

H6

GND

H4

GND

H2

GND

G31

GND

G29

GND

G27

GND

G25

GND

G9

GND

G5

GND

G3

GND

G1

GND

F30

GND

F28

GND

F25

GND

F19

GND

F13

GND

F7

GND

F2

GND

E31

GND

E29

GND

E23

GND

E17

GND

E15

GND

E9

GND

D30

GND

D28

GND

D27

GND

D21

GND

D11

GND

D5

GND

D2

GND

C31

GND

C29

GND

C25

GND

C19

GND

C13

GND

C7

GND

B30

GND

B28

GND

B23

GND

B17

GND

B15

GND

B9

GND

B2

GND

A31

GND

A29

GND

A27

GND

A21

GND

A11 A5

GND GND

E9G022-001

P_VTT

C330

104P

C286

104P

C300

104P

C852

104P

C287

10u_0805

C878

10u_0805

C780

10u_0805

4

CPU1E

NOCONA 5/5

AD12

VTT

AC10

VTT

AA12

VTT

Y10

VTT

F10

VTT

E12 C10

VTT VTT

P_VCCP0

AE24

VCC

AE18

VCC

AE14

VCC

AE8

VCC

AE3

VCC

AD30

VCC

AD26

VCC

AD20

VCC

AD6

VCC

AD2

VCC

AC31

VCC

AC22

VCC

AC16

VCC

AC4

VCC

AC3

VCC

AB30

VCC

AB24

VCC

AB18

VCC

AB14

VCC

AB8

VCC

AB2

VCC

E9G022-001

CPU1-S

CpuSupporter

C140

3300p

C150

3300p

4

INVR0_EN38,39

OUTVRM0_PWRGD38

INCPU0_VID[0..5]6,30

VTT

VTT

VTT

VTT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

P_VCCP0

C725

10u_0805

B4

C5

A4

B12

AE27

AE21

AE11

AE2

AD31

AD23

AD17

AD15

AD9

AD3

AC25

AC19

AC13

AC7

AC2

AB31

AB27

AB21

AB11

AB5

AB1

CPU0_VID4

CPU0_VID3

CPU0_VID2

CPU0_VID1

CPU0_VID0

CPU0_VID5

C132

223P

P_VTT

0.8V~1.55V / 90A

P12V_CPU0

CHOCK1

CH-1.1U25A

VIN0

+

1 2

+

1 2

+

1 2

+

1 2

P_VCCP0

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

C709

10u_0805

C677

10u_0805

C694

10u_0805

C702

10u_0805

C693

10u_0805

C695

10u_0805

C723

10u_0805

C736

10u_0805

C740

10u_0805

C681

10u_0805

C684

10u_0805

C722

10u_0805

C89

10u_0805

C62

10u_0805

C80

10u_0805

27

13

12

14

15

16

11

28

R170

100KST

Fs = 245 KHz

2

3

4

5

6

7

8

U51

EN

PGOOD

VID4

VID3

VID2

VID1

VID0

VID12.5

COMP

FB

VDIFF

VSEN

RGND

REF

FS

ISL6556B

C739

10u_0805

C680

10u_0805

C726

10u_0805

C706

10u_0805

C705

10u_0805

C735

10u_0805

C727

10u_0805

C738

10u_0805

C682

10u_0805

C699

10u_0805

C714

10u_0805

C724

10u_0805

C700

10u_0805

C69

10u_0805

C61

10u_0805

P5V

26

VCC

GND

17

C21

x_47p

C22

104P

C20

1u_0805

TC2

x_330u/16V

TC4

330u/16V

TC5

330u/16V

TC3

330u/16V

TC13

820u/2.5V

TC15

820u/2.5V

TC10

820u/2.5V

TC12

820u/2.5V

TC7

820u/2.5V

TC8

820u/2.5V

TC9

820u/2.5V

C73

4.7u_0805

PWM1

ISEN1

PWM2

ISEN2

PWM3

ISEN3

PWM4

ISEN4

OFS

TCOMP

OVP

1

3

C19

x_47p

21

20

22

23

18

19

25

24

9

10

R237

2KST

3

P_VCCP0

+

TC14

1 2

820u/2.5V

+

TC6

1 2

820u/2.5V

+

TC11

1 2

820u/2.5V

+

TC16

1 2

820u/2.5V

+

TC52

1 2

220u2VSp

+

TC53

1 2

220u2VSp

C720

10u_0805

C679

10u_0805

C688

10u_0805

C712

10u_0805

C678

10u_0805

C707

10u_0805

C734

10u_0805

C737

10u_0805

C675

10u_0805

C692

10u_0805

C718

10u_0805

C687

10u_0805

C711

10u_0805

C98

10u_0805

C97

10u_0805

R246 2KST

R243 2KST

R252 2KST

R235 2KST

R224 470KST

R230

x_3KST

C385

104P

C374

104P

C373

104P

PWM01

ISEN01

PWM02

ISEN02

PWM03

ISEN03

PWM04

ISEN04

2

P5V

5

BSC059N03S

U16

1

2

3

4

BSC032N03S

BSC059N03S

U10

1

2

3

4

BSC032N03S

BSC059N03S

U20

1

2

3

4

BSC032N03S

BSC059N03S

U22

1

2

3

4

BSC032N03S

U17

5

5

U11

5

5

U21

5

5

U15

5

R779

2.2_0805

C662

10u_0805

PWM01

P5V

R778

2.2_0805

C663

10u_0805

PWM02

P5V

R777

2.2_0805

C665

10u_0805

PWM03

P5V

R780

2.2_0805

C664

10u_0805

PWM04

P5V

R775

499KST

R773

499KST

R774

499KST

R776

499KST

6

7

4

3

6

7

4

3

6

7

4

3

6

7

4

3

U4

VCC

PVCC

GND

PWM

HIP6605

U6

VCC

PVCC

GND

PWM

HIP6605

U5

VCC

PVCC

GND

PWM

HIP6605

U7

VCC

PVCC

GND

PWM

HIP6605

1

U_G

2

BOOT

8

PHASE

5

L_G

1

U_G

2

BOOT

8

PHASE

5

L_G

1

U_G

2

BOOT

8

PHASE

5

L_G

1

U_G

2

BOOT

8

PHASE

5

L_G

2

R23

2.2_0805

C23

0.22u

ISEN01

R25

2.2_0805

C24

0.22u

ISEN02

R24

2.2_0805

C25

0.22u

ISEN03

R26

2.2_0805

C26

0.22u

ISEN04

Title

CPU0 DeCAP, VRM0

Size Document Number Rev

MS9146 200

Date: Sheet

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

U9

1

2

3

4

BSC059N03S

5

BSC032N03S

U19

1

2

3

4

BSC059N03S

5

BSC032N03S

U13

1

2

3

4

BSC059N03S

5

BSC032N03S

U23

1

2

3

4

BSC059N03S

5

BSC032N03S

1

VIN0

5

U8

5

U18

5

U12

5

U14

C669

10u_1206

P_VCCP0

CHOCK2

CH-0.68U49A

R781

1

2.2_0805

2

3

4

C670

102p

VIN0

C666

10u_1206

CHOCK3

CH-0.68U49A

R783

2.2_0805

1

2

3

4

C672

102p

VIN0

C668

10u_1206

CHOCK4

CH-0.68U49A

R782

2.2_0805

1

2

3

4

C671

102p

VIN0

C667

10u_1206

CHOCK5

CH-0.68U49A

R784

2.2_0805

1

2

3

4

C673

102p

741Friday, January 21, 2005

of

Page 8

5

INSB_BPRI_#6,11

SB_CPU1_BREQ_23_#

INSB_BREQ_#06,11

BISB_BREQ_#16,11

INSB_CPURST_#6,11

INSB_RS_#26,11

INSB_RS_#16,11

INSB_RS_#06,11

VCC

GND

INSB_RSP_#6,11

INSB_CPU_A20M_#6,21

INSB_CPU_IGNNE_#6,21

INSB_CPU_INIT_#6,21,23

INSB_CPU_NMI6,38

INSB_CPU_INTR6,21

INCPU_PWR_GD6,21

INSB_CPU_SLP_#6,21

IN

INP1_BCLK_N5

INP1_BCLK_P5

INITP_TCK112

INITP_TDI_P112

INITP_TMS6,12

INITP_TRST_#6,12

P5V

2

3

OUTCPU1_VCC_SEN9

OUTVTT_EN6,39

OUTCPU1_VSS_SEN9

R348 51

R805 49.9RST

R825 49.9RST

R822 0

SB_CPU1_IERR_#

D D

P_VTT

INICH_CPU_SMI_#6,21,31

C C

P_VTT

R517 510

R516 510

R526 510

R524 510

R523 510

R527 510

B B

R342 51

R811 51

R789 51

R486 51

R807 100RST

R824 100RST

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R810 51

R823 51

A A

R814 51

R813 39

R809 39

R808 39

R806 39

R812 39

RN18

51-8P4R

RN17

51-8P4R

CPU1_VID5

CPU1_VID4

CPU1_VID3

CPU1_VID2

CPU1_VID1

CPU1_VID0

SB_CPU1_IERR_#

PU_COMP3_CPU1

PU_COMP2_CPU1

PU_CPU1_5

PU_CPU1_3

PU_CPU1_7

PU_CPU1_1

PU_CPU1_4

PU_CPU1_2

PU_CPU1_6

PU_CPU1_0

PU_CPU1_8

SB_CPU1_BREQ_23_#

C783

47p

C778

47p

C777

47p

C776

47p

C784

47p

INCPU1_DISABLE_#34

OUT CPU1_VID[0..5] 9,30

OUT SB_CPU1_THERMTRIP_# 37

OUT SB_CPU1_PROCHOT_# 34

BI SB_TEST_BUS 6

Pull up when ODT disable

Pull up when ODT disable

BI SB_BINIT_# 6,11

BI SB_BNR_# 6,11

BI SB_HIT_# 6,11

BI SB_HITM_# 6,11

BI SB_MCERR_# 6,11

5

R8031.8K

SB_CPU_STPCLK_#6,21

U25

6

A

4 5

BC

1

BE

PI5C3303

BE = 1

B---C

BackSide

BackSide

BackSide

BackSide

BackSide

CPU1_SMI_#

SB_CPU1_BSEL1

SB_CPU1_BSEL0

CPU1_SMI_#

CPU1_VID4

CPU1_VID3

CPU1_VID2

CPU1_VID1

CPU1_VID0

CPU1_VCCA

CPU1_VSSA

4

D23

D10

E11

F12

D20

F21

D22

E21

F27

C26

G23

B24

AB7

C27

AE6

E24

C24

A25

F24

AB3

AA3

AE29

AE28

AD29

AD28

AC29

AB29

AB28

AA29

AA28

AE15

AC1

AE16

AD4

B27

AB4

AA5

D26

P3V3

4.7K

R487

PD_ODTEN_CPU1

PD_COMP1_CPU1

PD_COMP0_CPU1

CPU1_SLEW_CTRL

4

Y8

C6

D6

D4

W5

Y4

Y3

A1

B3

C3

D3

E3

F3

E1

R505

4.7K

B

CPU2A

BPRI_N

BR3_N

BR2_N

BR1_N

BR0_N

RESET_N

RS2_N

RS1_N

RS0_N

RSP_N

A20M_N

IGNNE_N

INIT_N

LINT1_NMI

LINT0_INTR

PWRGOOD

SMI_N

SLP_N

STPCLK_N

BCLK1

BCLK0

TCK

TDI

TMS

TRST_N

BSEL1

BSEL0

RESERVED16

RESERVED

RSVD_15

RSVD_14

RSVD_13

RSVD_12

RSVD_10

RSVD_9

RSVD_8

RSVD_7

RSVD_3

RSVD_2

RSVD_1

VID5

VID4

VID3

VID2

VID1

VID0

VCCIOPLL

VCCSENSE

VTTEN

VCCA

VSSA

VSSSENSE

E9G022-001

E C

NOCONA 1/5

BreakPoint

Monitor

Machine

CheckError

(RSVD_11)COMP2

(RSVD_6)TESTHI8

(RSVD_4)TESTHI7

(RESERVED17)TEST_BUS

OPTPMPZED_COMPAT_N

Q63

MMBT3904

P_VTT

R535

49.9RST

R542

84.5RST

P_VTT

R533

49.9RST

R522

84.5RST

ADS_N

BINIT_N

BNR_N

BPM5_N

BPM4_N

BPM3_N

BPM2_N

BPM1_N

BPM0_N

DBSY_N

DEFER_N

DRDY_N

HIT_N

HITM_N

TRDY_N

LOCK_N

MCERR_N

IERR_N

FERR_N_PBE_N

THERMTRIP_N

PROCHOT_N

GTLREF3

GTLREF2

GTLREF1

GTLREF0

ODTEN

SKTOCC_N

(RSVD_5)COMP3

COMP1

COMP0

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

SMB_PRT

VCCPLL

THERMDC

THERMDA

BOOT_SELECT

RSVD

VIDPWRGD

FORCEPR_N

SLEW_CTRL

P3V3

DS

G

Q62

2N7002

SOT23SGD

CPU1_VREF0

CPU1_VREF3

D19

F11

F20

E4

E8

F5

E7

F8

F6

F18

C23

E18

E22

A23

E19

A17

D7

E5

E27

F26

B25

E25

TDO

F9

F23

W9

W23

B5

A3

D25

AC28

E16

AD16

Y29

A26

AE5

AD5

AA7

Y6

W8

W7

W6

AE4

AD1

Y28

Y27

G7

W3

B1

A16

A15

AC30

C1

AE30

NC

R511 10K

R502 1K

R491 10K

VREF_P_VTT_CPU1_0

CP15

x_COPPER

VREF_P_VTT_CPU1_3

CP14

x_COPPER

3

SB_BINIT_#

SB_BNR_#

CPU_BPM_#5

CPU_BPM_#4

CPU_BPM_#3

CPU_BPM_#2

CPU_BPM_#1

CPU_BPM_#0

SB_HIT_#

SB_HITM_#

SB_MCERR_#

SB_CPU1_IERR_#

SB_CPU1_THERMTRIP_#

SB_CPU1_PROCHOT_#

TP17

SB_TEST_BUS

CPU1_FORCEPR_#

CPU1_SLEW_CTRL

TP16

These two TP have on-die

pull up resistor

C299

220p

C298

220p

C294

1u

C276

220p

C277

220p

C283

1u

BI SB_ADS_# 6,11

BI SB_DBSY_# 6,11

IN SB_DEFER_# 6,11

BI SB_DRDY_# 6,11

IN SB_TRDY_# 6,11

BI SB_LOCK_# 6,11

VREF_P_VTT_CPU1_3

VREF_P_VTT_CPU1_0

PD_ODTEN_CPU1

PU_COMP3_CPU1

PU_COMP2_CPU1

PD_COMP1_CPU1

PD_COMP0_CPU1

PU_CPU1_8

PU_CPU1_0

PU_CPU1_5

PU_CPU1_6

PU_CPU1_1

PU_CPU1_7

PU_CPU1_2

PU_CPU1_4

OUT CPU1_THERMDC 30

OUT CPU1_THERMDA 30

IN VID_PWRGD 6,38

OUT SB_CPU1_IERR 34

3

BI CPU_BPM_#[0..5] 6,12

OUT SB_CPU_FERR_# 6,21

OUT ITP_TDO_P1 12

OUT CPU1_SKTOCC_# 34,38

CPU1

FORCEPR_#

P_VTT

L9

10u165MA1210

L10

10u165MA1210

P3V3

R332

2.7K

INSB_CPU1_FORCEPR_#29

2

C332

22u_1210

Q42

E C

MMBT3904

2

AB10

AA10

AA11

AB13

AB12

AC14

AA14

AA13

AD10

AC11

AE10

AC12

AD11

AD14

AD13

AB15

AD18

AE13

AC17

AA16

AB16

AB17

AD19

AD21

AE20

AE22

AC21

AC20

AA18

AC23

AE23

AD24

AC24

AE25

AD25

AC26

AE26

AA19

AB19

AB22

AB20

AA21

AA22

AB23

AB25

AB26

AA24

AD27

AA25

AA27

B

AB6

AA8

AC5

AC6

AE7

AD7

AC8

AC9

AD8

AE9

Y23

Y24

Y26

Y9

P_VTT

CPU2B

NOCONA 2/5

D63_N

D62_N

D61_N

D60_N

D59_N

D58_N

D57_N

D56_N

D55_N

D54_N

D53_N

D52_N

D51_N

D50_N

D49_N

D48_N

D47_N

D46_N

D45_N

D44_N

D43_N

D42_N

D41_N

D40_N

D39_N

D38_N

D37_N

D36_N

D35_N

D34_N

D33_N

D32_N

D31_N

D30_N

D29_N

D28_N

D27_N

D26_N

D25_N

D24_N

D23_N

D22_N

D21_N

D20_N

D19_N

D18_N

D17_N

D16_N

D15_N

D14_N

D13_N

D12_N

D11_N

D10_N

D9_N

D8_N

D7_N

D6_N

D5_N

D4_N

D3_N

D2_N

D1_N

D0_N

E9G022-001

CPU1_VCCA

CPU1_VSSA

R335

51

CPU1_FORCEPR_#

Q44

E C

MMBT3904

Indicate the

polarity of the

SB_D_#[0..63]

Address Parity

Data Parity

ADSTB1_N

ADSTB0_N

DSTBP3_N

DSTBP2_N

DSTBP1_N

DSTBP0_N

DSTBN3_N

DSTBN2_N

DSTBN1_N

DSTBN0_N

Frequency

Select

SB_CPU1_BSEL1

SB_CPU1_BSEL0

Title

Size Document Number Rev

Date: Sheet

BISB_D_#[0..63]6,11

SB_D_#63

SB_D_#62

SB_D_#61

SB_D_#60

SB_D_#59

SB_D_#58

SB_D_#57

SB_D_#56

SB_D_#55 SB_A_#27

SB_D_#54

SB_D_#53

SB_D_#52

SB_D_#51

SB_D_#50

SB_D_#49

SB_D_#48

SB_D_#47

SB_D_#46

SB_D_#45

SB_D_#44

SB_D_#43

SB_D_#42

SB_D_#41

SB_D_#40

SB_D_#39

SB_D_#38

SB_D_#37

SB_D_#36

SB_D_#35

SB_D_#34

SB_D_#33

SB_D_#32

SB_D_#31

SB_D_#30

SB_D_#29

SB_D_#28

SB_D_#27

SB_D_#26

SB_D_#25

SB_D_#24

SB_D_#23

SB_D_#22

SB_D_#21

SB_D_#20PU_CPU1_3

SB_D_#19

SB_D_#18

SB_D_#17

SB_D_#16

SB_D_#15

SB_D_#14

SB_D_#13

SB_D_#12

SB_D_#11

SB_D_#10

SB_D_#9

SB_D_#8

SB_D_#7

SB_D_#6

SB_D_#5

SB_D_#4

SB_D_#3

SB_D_#2

SB_D_#1

SB_D_#0

P3V3

R321

4.7K

B

4.7K

R333

1

SB_A_#35

C8

A35_N

SB_A_#34

C9

A34_N

SB_A_#33

A7

A33_N

SB_A_#32

A6

A32_N

SB_A_#31

B7

A31_N

SB_A_#30

C11

A30_N

SB_A_#29

D12

A29_N

SB_A_#28

E13

A28_N

B8

A27_N

SB_A_#26

A9

A26_N

SB_A_#25

D13

A25_N

SB_A_#24

E14

A24_N

SB_A_#23

C12

A23_N

SB_A_#22

B11

A22_N

SB_A_#21

B10

A21_N

SB_A_#20

A10

A20_N

SB_A_#19

F15

A19_N

SB_A_#18

D15

A18_N

SB_A_#17

D16

A17_N

SB_A_#16

C14

A16_N

SB_A_#15

C15

A15_N

SB_A_#14

A12

A14_N

SB_A_#13

B13

A13_N

SB_A_#12

B14

A12_N

SB_A_#11

B16

A11_N

SB_A_#10

A13

A10_N

SB_A_#9

D17

A9_N

SB_A_#8

C17

A8_N

SB_A_#7

A19

A7_N

SB_A_#6

C18

A6_N

SB_A_#5

B18

A5_N

SB_A_#4

A20

A4_N

SB_A_#3

A22

A3_N

SB_REQ_#4

B22

REQ4_N

REQ3_N

REQ2_N

REQ1_N

REQ0_N

DBI3_N

DBI2_N

DBI1_N

DBI0_N

SB_REQ_#3

C20

SB_REQ_#2

C21

SB_REQ_#1

B21

SB_REQ_#0

B19

SB_DBI_#3

AB9

SB_DBI_#2

AE12

SB_DBI_#1

AD22

SB_DBI_#0

AC27

SB_AP_#1

D9

AP1_N

SB_AP_#0

E10

AP0_N

DP3_N

DP2_N

DP1_N

DP0_N

CPU1 Signal

MS9146 200

AE17

AC15

AE19

AC18

F14

F17

Y11

Y14

Y17

Y20

Y12

Y15

Y18

Y21

P_VTT

P_VTT

SB_DP_#3

SB_DP_#2CPU1_VID5

SB_DP_#1

SB_DP_#0

SB_ADSTB_#1

SB_ADSTB_#0

SB_DSTBP_#3

SB_DSTBP_#2

SB_DSTBP_#1

SB_DSTBP_#0

SB_DSTBN_#3

SB_DSTBN_#2

SB_DSTBN_#1

SB_DSTBN_#0

R545

510

4.7K

R544

R546

510

4.7K

R547

BI SB_A_#[3..35] 6,11

BI SB_REQ_#[0..4] 6,11

BI SB_DBI_#[0..3] 6,11

BI SB_AP_#[0..1] 6,11

BI SB_DP_#[0..3] 6,11

BI SB_ADSTB_#[0..1] 6,11

P3V3

R536

4.7K

B

B

Q66

E C

MMBT3904

P3V3

R555

4.7K

B

B

Q68

E C

MMBT3904

1

BI SB_DSTBP_#[0..3] 6,11

BI SB_DSTBN_#[0..3] 6,11

P3V3

R525

4.7K

OUT CPU1_BSEL1 38

Q64

E C

MMBT3904

P3V3

R556

4.7K

OUT CPU1_BSEL0 38

Q69

E C

MMBT3904

841Friday, January 21, 2005

of

Page 9

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

5

AA30

AA23

AA17

AA15

AA9

AA2

Y31

Y25

Y19

Y13

Y7

Y5

Y1

W30

W28

W26

W24

W4

W2

V31

V29

V27

V25

V23

V9

V7

V5

V3

V1

U30

U28

U26

U24

U8

U6

U4

U2

T31

T29

T27

T25

T23

T9

T7

T5

T3

T1

R30

R28

R26

R24

R8

R6

R4

R2

P31

P29

P27

P25

P23

P9

P7

P5

P3

P1

N30

N28

N26

N24

N8

N6

N4

N2

M30

M28

M26

M24

M8

M6

M4

M2

5

CPU2C

NOCONA 3/5

L31

GND

L29

GND

L27

GND

L25

GND

L23

GND

L9

GND

L7

GND

L5

GND

L3

GND

L1

GND

K30

GND

K28

D D

C C

B B

A A

GND

K26

GND

K24

GND

K8

GND

K6

GND

K4

GND

K2

GND

J31

GND

J29

GND

J27

GND

J25

GND

J23

GND

J9

GND

J7

GND

J5

GND

J3

GND

J1

GND

H30

GND

H28

GND

H26

GND

H24

GND

H8

GND

H6

GND

H4

GND

H2

GND

G31

GND

G29

GND

G27

GND

G25

GND

G9

GND

G5

GND

G3

GND

G1

GND

F30

GND

F28

GND

F25

GND

F19

GND

F13

GND

F7

GND

F2

GND

E31

GND

E29

GND

E23

GND

E17

GND

E15

GND

E9

GND

D30

GND

D28

GND

D27

GND

D21

GND

D11

GND

D5

GND

D2

GND

C31

GND

C29

GND

C25

GND

C19

GND

C13

GND

C7

GND

B30

GND

B28

GND

B23

GND

B17

GND

B15

GND

B9

GND

B2

GND

A31

GND

A29

GND

A27

GND

A21

GND

A11 A5

GND GND

E9G022-001

P_VTT

C198

104P

C698

104P

C218

104P

C57

104P

C683

10u_0805

C719

10u_0805

C676

10u_0805

CPU2D

P_VCCP1 P_VCCP1

NOCONA 4/5

L28

VCC

L26

VCC

L24

VCC

L8

VCC

L6

VCC

L4

VCC

L2

VCC

K31

VCC

K29

VCC

K27

VCC

K25

VCC

K23

VCC

K9

VCC

K7

VCC

K5

VCC

K3

VCC

K1

VCC

J30

VCC

J28

VCC

J26

VCC

J24

VCC

J8

VCC

J6

VCC

J4

VCC

J2

VCC

H31

VCC

H29

VCC

H27

VCC

H25

VCC

H23

VCC

H9

VCC

H7

VCC

H5

VCC

H3

VCC

H1

VCC

G30

VCC

G28

VCC

G26

VCC

G24

VCC

G8

VCC

G6

VCC

G4

VCC

G2

VCC

F31

VCC

F29

VCC

F22

VCC

F16

VCC

F4

VCC

F1

VCC

E30

VCC

E28

VCC

E26

VCC

E20

VCC

E6

VCC

E2

VCC

D31

VCC

D29

VCC

D24

VCC

D18

VCC

D14

VCC

D8

VCC

D1

VCC

C30

VCC

C28

VCC

C22

VCC

C16

VCC

C4

VCC

C2

VCC

B31

VCC

B29

VCC

B26

VCC

B20

VCC

B6

VCC

A30

VCC

A28

VCC

A24

VCC

A18

VCC

A14

VCC

A8

VCC

A2

VCC

E9G022-001

L30

VCC

AA31

VCC

AA26

VCC

AA20

VCC

AA6

VCC

AA4

VCC

AA1

VCC

Y30

VCC

Y22

VCC

Y16

VCC

Y2

VCC

W31

VCC

W29

VCC

W27

VCC

W25

VCC

W1

VCC

V30

VCC

V28

VCC

V26

VCC

V24

VCC

V8

VCC

V6

VCC

V4

VCC

V2

VCC

U31

VCC

U29

VCC

U27

VCC

U25

VCC

U23

VCC

U9

VCC

U7

VCC

U5

VCC

U3

VCC

U1

VCC

T30

VCC

T28

VCC

T26

VCC

T24

VCC

T8

VCC

T6

VCC

T4

VCC

T2

VCC

R31

VCC

R29

VCC

R27

VCC

R25

VCC

R23

VCC

R9

VCC

R7

VCC

R5

VCC

R3

VCC

R1

VCC

P30

VCC

P28

VCC

P26

VCC

P24

VCC

P8

VCC

P6

VCC

P4

VCC

P2

VCC

N31

VCC

N29

VCC

N27

VCC

N25

VCC

N23

VCC

N9

VCC

N7

VCC

N5

VCC

N3

VCC

N1

VCC

M31

VCC

M29

VCC

M27

VCC

M25

VCC

M23

VCC

M9

VCC

M7

VCC

M5

VCC

M3

VCC

M1

VCC

R566 20KST

R565 3KST

R564 20KST

P_VCCP1

INCPU1_VCC_SEN8

INCPU1_VSS_SEN8

P_VCCP1

P_VCCP1

C336 x_C

R592 X_0

R589 0

R598 X_0

R597 0

4

CPU2E

P_VTT

NOCONA 5/5

AD12

VTT

AC10

VTT

AA12

VTT

Y10

VTT

F10

VTT

E12 C10

VTT VTT

P_VCCP1

AE24

VCC

AE18

VCC

AE14

VCC

AE8

VCC

AE3

VCC

AD30

VCC

AD26

VCC

AD20

VCC

AD6

VCC

AD2

VCC

AC31

VCC

AC22

VCC

AC16

VCC

AC4

VCC

AC3

VCC

AB30

VCC

AB24

VCC

AB18

VCC

AB14

VCC

AB8

VCC

AB2

VCC

E9G022-001

P_VCCP0

C313

104P

C397

104P

C268

104P

CPU2-S

CpuSupporter

C289

47u_1210

C377

47u_1210

C378

47u_1210

C379

47u_1210

C335

3300p

C334

3300p

4

INVR1_EN38

OUTVRM1_PWRGD38

INCPU1_VID[0..5]8,30

C386

10u_0805

3

P_VTT

B4

VTT

C5

VTT

A4

VTT

B12

VTT

AE27

GND

AE21

GND

AE11

GND

AE2

GND

AD31

GND

AD23

GND

AD17

GND

AD15

GND

AD9

GND

AD3

GND

AC25

GND

AC19

GND

AC13

GND

AC7

GND

AC2

GND

AB31

GND

AB27

GND

AB21

GND

AB11

GND

AB5

GND

AB1

GND

P_VCCP1

CPU1_VID4

CPU1_VID3

CPU1_VID2 PWM12

CPU1_VID1

CPU1_VID0

CPU1_VID5

C333

223P

0.8V~1.55V / 90A

P12V_CPU1

CHOCK10

CH-1.1U25A

P_VCCP1

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

+

1 2

C899

10u_0805

C833

10u_0805

C911

10u_0805

C907

10u_0805

C875

10u_0805

C790

10u_0805

C855

10u_0805

C838

10u_0805

C898

10u_0805

C881

10u_0805

C864

10u_0805

C812

10u_0805

C861

10u_0805

C297

10u_0805

C281

10u_0805

P5V

26

17

C425

x_47p

C424

104P

C421

1u_0805

TC44

330u/16V

TC40

x_330u/16V

TC49

330u/16V

TC48

330u/16V

TC37

820u/2.5V

TC39

820u/2.5V

TC26

820u/2.5V

TC31

820u/2.5V

TC25

820u/2.5V

TC27

820u/2.5V

TC29

820u/2.5V

C387

4.7u_0805

PWM1

ISEN1

VCC

PWM2

ISEN2

PWM3

ISEN3

PWM4

ISEN4

TCOMP

OVP

GND

1

C897

10u_0805

C826

10u_0805

C909

10u_0805

C906

10u_0805

C879

10u_0805

C849

10u_0805

C847

10u_0805

C828

10u_0805

C869

10u_0805

C903

10u_0805

C770

10u_0805

C873

10u_0805

C291

10u_0805

C284

10u_0805

C288

10u_0805

VIN1

U86

27

EN

2

PGOOD

3

VID4

4

VID3

5

VID2

6

VID1

7

VID0

8

VID12.5

13

COMP

12

FB

14

VDIFF

15

VSEN

16

RGND

11

REF

28

FS

ISL6556B

R590

100KST

Fs = 245 KHz

OFS

3

C398

x_47p

1 2

1 2

1 2

1 2

1 2

21

R596 2KST

20

22

R594 2KST

23

18

R593 2KST

19

25

R595 2KST

24

9

10

R567

2KST

P_VCCP1

+

TC38

820u/2.5V

+

TC30

820u/2.5V

+

TC28

820u/2.5V

+

TC36

x_820u/2.5V

+

TC54

220u2VSp

C840

10u_0805

C910

10u_0805

C908

10u_0805

C882

10u_0805

C853

10u_0805

C905

10u_0805

C813

10u_0805

C876

10u_0805

C865

10u_0805

C775

10u_0805

C868

10u_0805

C774

10u_0805

C785

10u_0805

C296

10u_0805

C280

10u_0805

R568 470KST

R569

x_3KST

C28

104P

C27

104P

C29

104P

PWM11

ISEN11

ISEN12

PWM13

ISEN13

PWM14

ISEN14

2

P5V

5

BSC059N03S

U87

1

2

3

4

BSC032N03S

BSC059N03S

U98

1

2

3

4

BSC032N03S

BSC059N03S

U105

1

2

3

4

BSC032N03S

BSC059N03S

U103

1

2

3

4

BSC032N03S

U90

5

5

U106

5

5

U104

5

5

U102

5

R832

2.2_0805

PWM11

P5V

R863

2.2_0805

10u_0805

PWM12

P5V

R865

2.2_0805

PWM13

P5V

R872

2.2_0805

PWM14

P5V

C920

10u_0805

C945

C944

10u_0805

C946

10u_0805

R830

499KST

R864

499KST

R866

499KST

R867

499KST

6

7

4

3

6

7

4

3

6

7

4

3

6

7

4

3

U89

VCC

PVCC

GND

PWM

HIP6605

U125

VCC

PVCC

GND

PWM

HIP6605

U124

VCC

PVCC

GND

PWM

HIP6605

U123

VCC

PVCC

GND

PWM

HIP6605

1

U_G

2

BOOT

8

PHASE

5

L_G

1

U_G

2

BOOT

8

PHASE

5

L_G

1

U_G

2

BOOT

8

PHASE

5

L_G

1

U_G

2

BOOT

8

PHASE

5

L_G

2

R610

2.2_0805

C439

0.22u

ISEN11

R763

2.2_0805

C622

0.22u

ISEN12

R764

2.2_0805

C621

0.22u

ISEN13

R762

2.2_0805

C623

0.22u

ISEN14

Title

CPU1 DeCAP, VRM1

Size Document Number Rev

MS9146 200

Date: Sheet

1

2

3

4

1

2

3

4

1

2

3

4

1

2

3

4

1

U91

1

2

3

4

BSC059N03S

5

BSC032N03S

U116

1

2

3

4

BSC059N03S

5

BSC032N03S

U114

1

2

3

4

BSC059N03S

5

BSC032N03S

U112

1

2

3

4

BSC059N03S

5

BSC032N03S

1

5

U88

5

U100

5

U115

5

U113

P_VCCP1

VIN1

C921

10u_1206

CHOCK11

CH-0.68U49A

R629

2.2_0805

1

2

3

4

C443

102p

VIN1

C941

10u_1206

CHOCK14

CH-0.68U49A

R841

2.2_0805

1

2

3

4

C923

102p

VIN1

C942

10u_1206

CHOCK13

CH-0.68U49A

R844

1

2.2_0805

2

3

4

C926

102p

VIN1

C943

10u_1206

CHOCK12

CH-0.68U49A

R842

2.2_0805

1

2

3

4

C927

102p

941Friday, January 21, 2005

of

Page 10

5

4

3

2

1

U84A

DDRA_A13

DDRA_A12

DDRA_A11

DDRA_A10

DDRA_A9

DDRA_A8

DDRA_A7

DDRA_A6

D D

OUTDDRA_CMDCLK_P[0..3]13,14,15,16

OUTDDRA_CMDCLK_N[0..3]13,14,15,16

Intel ERATA 10.17

DDRA_CMDCLK_N(P)1,2

C C

exchange

OUTDDRA_CAS_#13,14,15,16

OUTDDRA_RAS_#13,14,15,16

OUTDDRA_WE_#13,14,15,16

OUTDDRA_BA[0..2]13,14,15,16

BIDDRA_DQS_P[0..17]13,14,15,16

B B

SPEC Request 0.5%

R570 40.2RST

P1V8

R571 40.2RST

DDRA_A5

DDRA_A4

DDRA_A3

DDRA_A2

DDRA_A1

DDRA_A0

BIDDRA_CB[0..7]13,14,15,16

DDRA_CB7

DDRA_CB6

DDRA_CB5

DDRA_CB4

DDRA_CB3

DDRA_CB2

DDRA_CB1

DDRA_CB0

OUTMEM_CKE[0..3]13,14,15,16,17,18,19,20

MEM_CKE3

MEM_CKE2

MEM_CKE1

MEM_CKE0

DDRA_CMDCLK_P3

DDRA_CMDCLK_P2

DDRA_CMDCLK_P1

DDRA_CMDCLK_P0

DDRA_CMDCLK_N3

DDRA_CMDCLK_N2

DDRA_CMDCLK_N1

DDRA_CMDCLK_N0

OUTDDRA_CS_#[0..7]13,14,15,16

DDRA_CS_#7

DDRA_CS_#6

DDRA_CS_#5

DDRA_CS_#4

DDRA_CS_#3

DDRA_CS_#2

DDRA_CS_#1

DDRA_CS_#0

DDRA_MCH_VREF

DDRA_BA0

DDRA_BA1

DDRA_BA2 DDRB_BA2

DDRA_DQS_P17

DDRA_DQS_P16

DDRA_DQS_P15

DDRA_DQS_P14

DDRA_DQS_P13

DDRA_DQS_P12

DDRA_DQS_P11

DDRA_DQS_P10

DDRA_DQS_P9

DDRA_DQS_P8

DDRA_DQS_P7

DDRA_DQS_P6

DDRA_DQS_P5

DDRA_DQS_P4

DDRA_DQS_P3

DDRA_DQS_P2

DDRA_DQS_P1

DDRA_DQS_P0

DDRRES2

DDRRES1

C339

104P

C338

104P

AG23

AF22

AE4

AJ22

AK20

AN20

AF18

AH17

AJ16

AK15

AL14

AD14

AH5

AE10

AF10

AH10

AJ10

AD11

AE11

AG11

AK26

AL26

AN26

AE26

AC10

AH13

AH11

AF13

AD9

AG12

AJ12

AF12

AM3

AA6

Y10

AB5

AF6

AE25

AH8

P10

AD8

AH14

AE20

AF25

AL32

AF9

AC6

AG14

AH19

AJ24

AJ30

AE1

AE2

U6

AJ9

L4

M3

M5

N5