Page 1

A B C

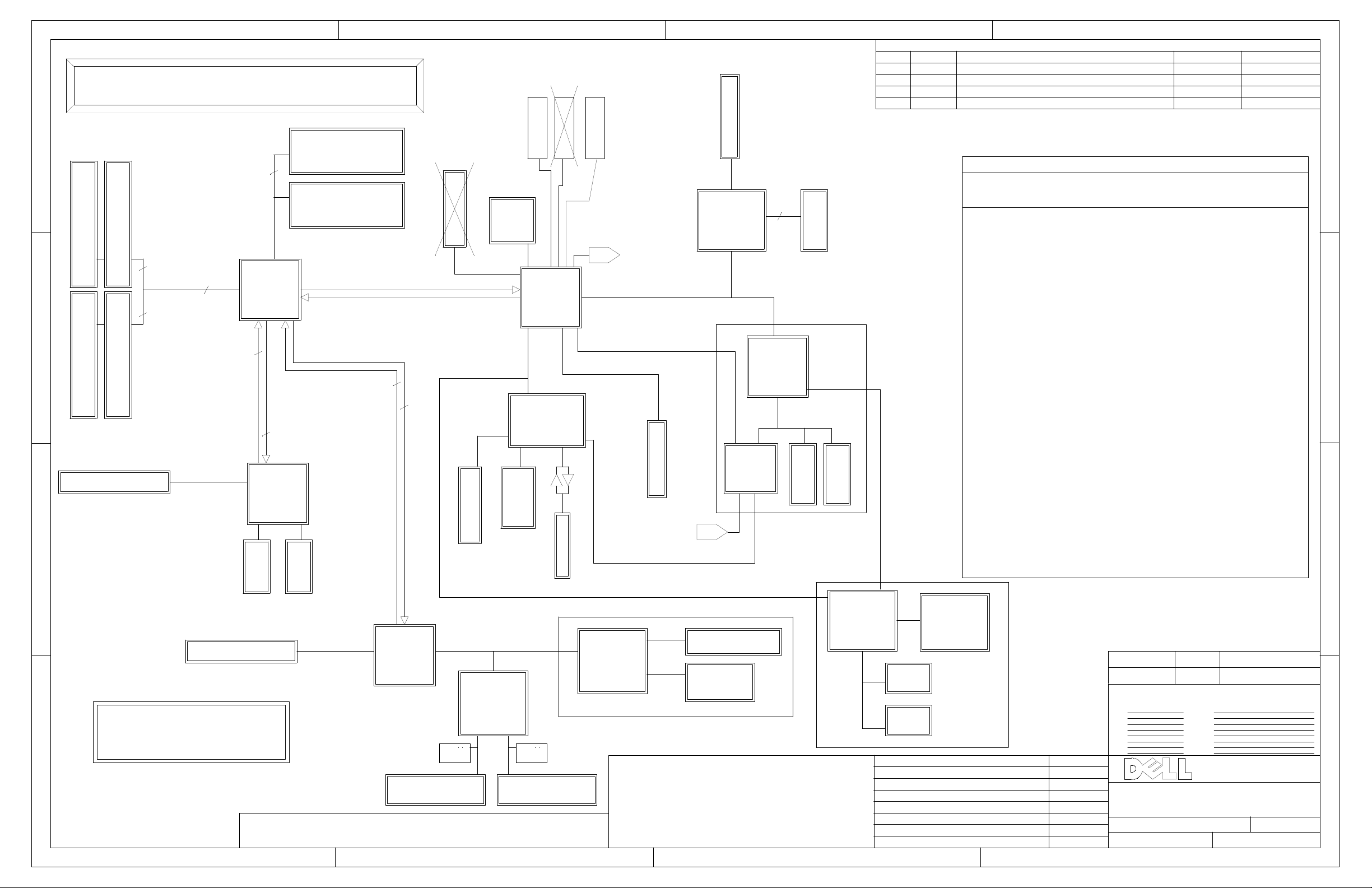

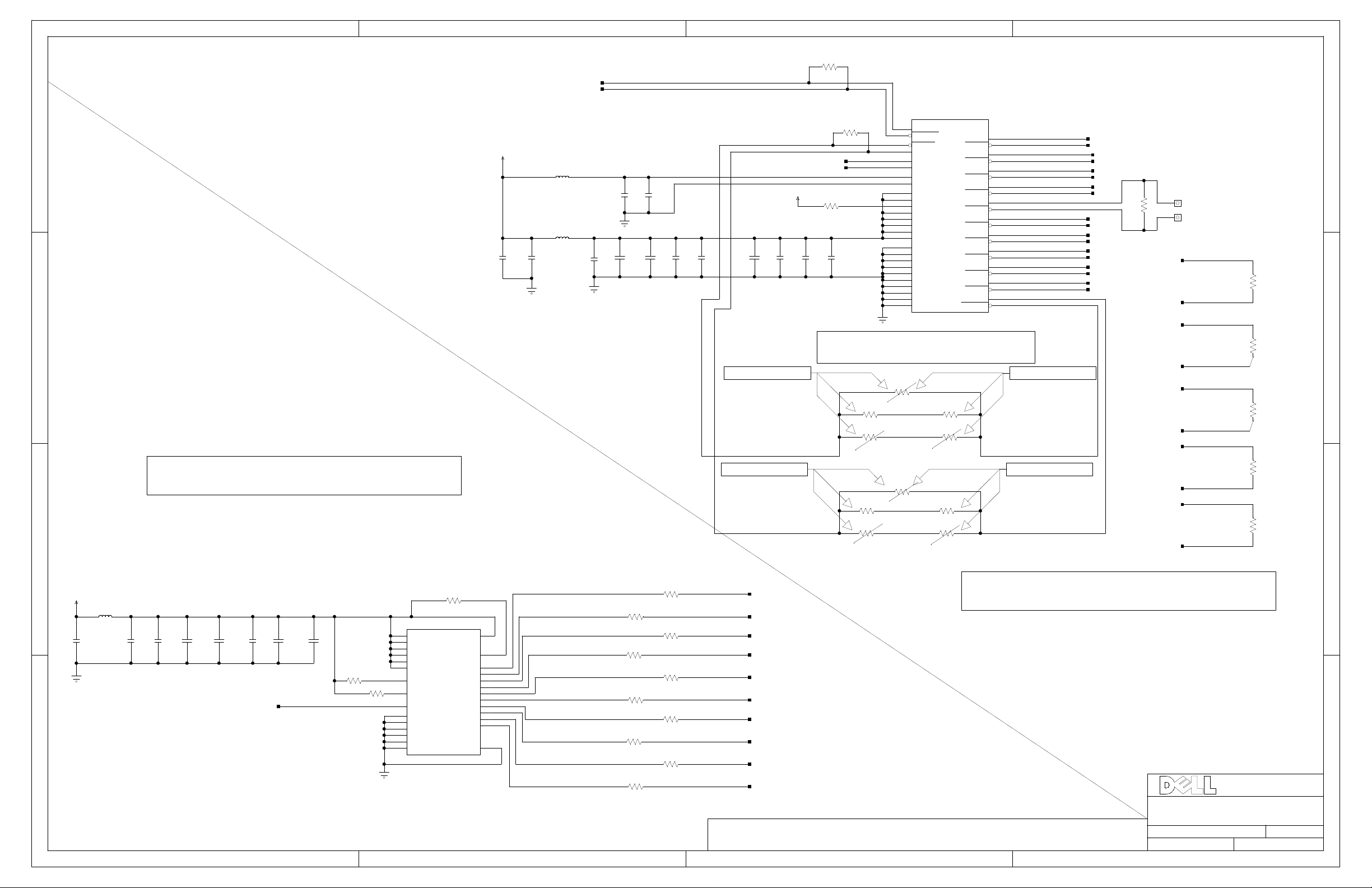

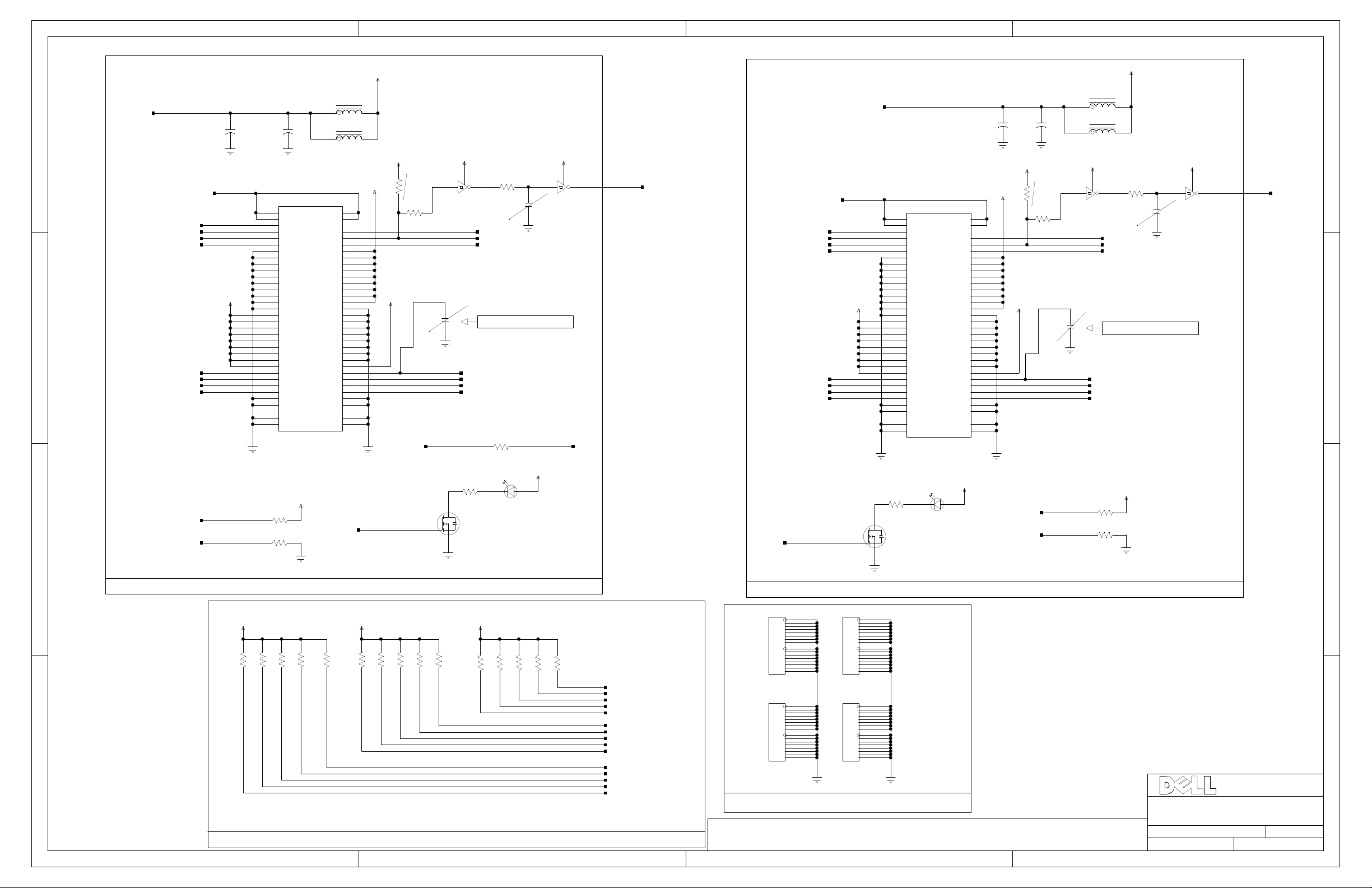

EVERGLADES MOTHERBOARD

Dell Controlled Print

D

REVISIONS

REV

X00-00 22 MAY 2003

A00-00

146313

FIRST PROTOTYPES

A00 PRODUCTION RELEASE

DESCRIPTIONECO DATE

06 JUNE 2003 SCOTT RAMSEY

APPROVED

1

1U DDR DIMM (PC2100)

1U DDR DIMM (PC2100)

Registered ECC SDRAMRegistered ECC SDRAM

2

1U DDR DIMM (PC2100)

1U DDR DIMM (PC2100)

PCI-X 133 SLOT

3

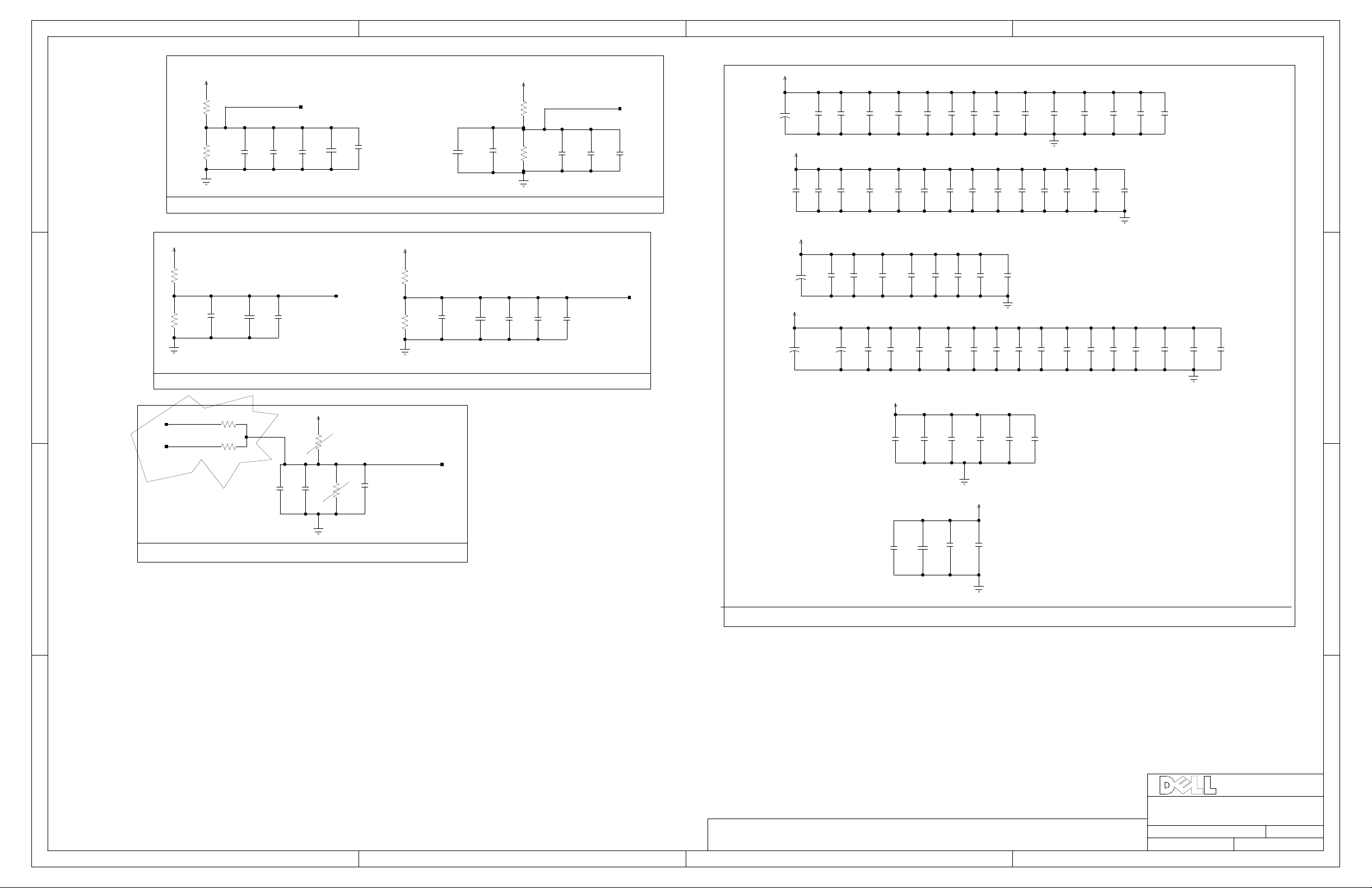

BLOCK DIAGRAM

4

64 bits data

DATA QUAD PUMPED

(4266 MB/S)

64

Registered ECC SDRAM

SEPARATE INBOUND & OUTBOUND

Registered ECC SDRAM

MEMORY BUS

128 bits data

64

DATA DOUBLE PUMPED

133MHz

(4266 MB/S)

IMB BUS

16 bits

DATA DOUBLE PUMPED

64 BIT PCI-X BUS

400 MHz

(1600 MB/S

EACH WAY)

PCI-X 133

(1067 MB/S)

16

DATA

PCI-X 133 SLOT

MAIN

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

PRESTONIA

PROCESSOR 1

64

DATA

P6 Bus

133MHz

PRESTONIA

PROCESSOR 2

RCC

GCLE

CMIC

SEPARATE INBOUND & OUTBOUND

SEPARATE INBOUND & OUTBOUND

16

DATA

AB

EACH IS 4 bits

DOUBLE PUMPED

(200 MB/S EACH WAY)

DATA DOUBLE PUMPED

(1600 MB/S

RCC

CIOB-E

PCI Bridge

RJ-45

Connector

GB ETHERNET

RJ-45

Connector

GB ETHERNET

64 BIT PCI-X BUS

PCI-X 133

(1067 MB/S)

THIN IMB BUS

200MHz

16

DATA

IMB BUS

16 bits

400 MHz

EACH WAY)

CIOB-X2

PCI Bridge

32Mb (4MB)

FLASH

(BIOS)

X BUS

LPC BUS

16

DATA

HARD DRIVES

ATA-100

IDE

FLOPPY

ON BACKPLANE

PCI-X 100

(800 MB/S)

RCC

ON BACKPLANE

64 BIT PCI-X BUS

LSI

53C1030

Dual

Channel

Ultra 320

SCSI

SCSI

Term

EXTERNAL BACKPLANE

Connector

Ultra320 SCSI

USB 1

USB 2

Connector

RCC

CSB5

South

Bridge

NATIONAL

PC87414

Super

I/O Chip

PS/2

Connectors

KB & MOUSE

SCSI

Term

Connector

USB 3

Connector

Connector

ON CTRL PANEL

USB4

32 BIT PCI BUS

33 MHz

(133 MB/S)

PRIMARY IDE

SECONDARY IDE

SERIAL PORT B

SERIAL A

INTEL

i80321

"Verde"

ROMB

Processor

ROMB CARD

THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER

CORP., EXCEPT AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN

ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE

REPRODUCED IN WHOLE OR IN PART AND MUST BE RETURNED TO DELL

COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION

OF THE PURPOSE OF THE LOAN. NEITHER THIS ITEM NOR THE

INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS

NOT HAVING A NEED FOR SUCH USE OR DISCLOSURE CONSISTENT WITH

THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF

DELL COMPUTER CORPORATION.

Header

CD-ROM

ON BACKPLANE

ON BACKPLANE

OPTIONAL

OPTIONAL

PROPRIETARY NOTE

TABLE OF CONTENTS

VGA

ATI

RAGE XL

Video

ESM4

Agilent

SP2

Processor

ESM4

FPGA

OPTIONAL

USB4

LPC BUS

RAID Memory

128MB DDR200

16Mb (2MB)

FLASH

(RAID)

32

DATA

8 MB

SDRAM

(2Mx32)

OPTIONAL

ESM4

CARD

SDRAM

FLASH

QLOGIC

ZIRCON

ESM3

BMC

Processor

I2C

SRAM

128KB

FLASH

32Mb

DRAWN

DESIGNED

CHECKED

APPROVED

APPROVED

APPROVED

APPROVED

RELEASED

TABLE OF CONTENTS

PAGE

XILINX

XC9572XL

ESM3

Support

CPLD

ESM3

EVERGLADES TEAM

SHANE CHIASSON

WILL SMITH

STUART HAYES

DESCRIPTION

...

1

TABLE OF CONTENTS and BLOCK DIAGRAM

...

2

CLOCK DIAGRAM

...

3

...

4

CLOCKS

...

5

MEMORY & PCI CLOCKS

...

6

PROCESSORS

PROCESSORS

...

7

...

8

PROCESSORS

...

9

VRMS

...

10

ITP & LEVEL TRANSLATION

...

11

CMIC-LE (MEMORY INTERFACE)

...

12

CMIC-LE

...

13

CMIC-LE DECOUPLING & SUPPORT

...

14

DDR DIMMS

...

15

DDR DIMMS

16...

DDR TERMINATION

...

17

SPARE GATES

...

18

CSB5

...

19

IRQ SERIALIZATION & X-BUS ADDRESS LATCHES

...

20

USB, REAR CYCLOPS

21

...

SYSTEM BIOS FLASH, CSB5 I2C MUX

...

22

SIO

...

23

PS/2 AND SERIAL

...

24

ATI VIDEO

25...

VIDEO MEMORY & CONNECTOR

...

26

CIOB-X2

...

27

CIOB-X2 POWER

28...

CIOB-E -- PCI-X AND PHYSICAL LAYER INTERFACE

...

29

CIOB-E -- IMB BUS AND STRAPPING

...

30

CIOB-E -- POWER

...

31

SECONDARY PCI-X BUS SERIES TERMINATORS

32

...

PHYSICAL LAYER NIC CONNECTORS

...

33

PCI-X BUS -- PULL-UPS AND CONNECTORS

...

34

-12V INVERTER

ESM3 -- ZIRCON BMP and SUPPORT CPLD

...

35

...

36

ESM3 -- SRAM and FLASH

ESM3 -- I2C

...

37

ESM3 -- FANS

38...

39

...

ESM3 -- ESM4 and INTRUSION DETECTION

...

40

ESM3 -- VOLTAGE MONITORING

...

41

DC/DC CONVERTERS: 5V, 3.3V, 2.5V, 1.8V, 1.5V, 1.25V

...

42

BACKPLANE CONNECTOR

...

43

LSI SCSI CONTROLLER--PCI-X/SCSI DIFFERENTIAL PAIRS

44...

LSI SCSI CONTROLLER--POWER/MISC

...

45

SCSI TERMINATION AND EXTERNAL SCSI CONNECTOR

...

46

FRONT PANEL CONNECTOR & IMPEDANCE TEST COUPONS

...

47

POWERGOOD CPLD

48...

POWER SUPPLY CONNECTOR

...

49

ESM4 NIC CONNECTOR

50...

RESET BLOCK DIAGRAM

...

51

ROMB (CONNECTOR, BATTERY, CHARGER, SUPPORT CIRCUITRY)

PWA P/N

02/14/03

02/14/03

02/14/03

02/14/03

MSI

Celestica

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO

TITLE

EVERGLADES MB

DWG NO.

DATE

P1348

H1631

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

SCHEM,PLNR,PE1750,533MSI

X1004

6/6/2003

DCBA

Build 1

Build 2

COMPUTER

CORPORATION

AUSTIN,TEXAS

REV.

SHEET

1 OF 51

1

6-9-2003_13:45EVERGLADES

1

2

3

4

A00-00

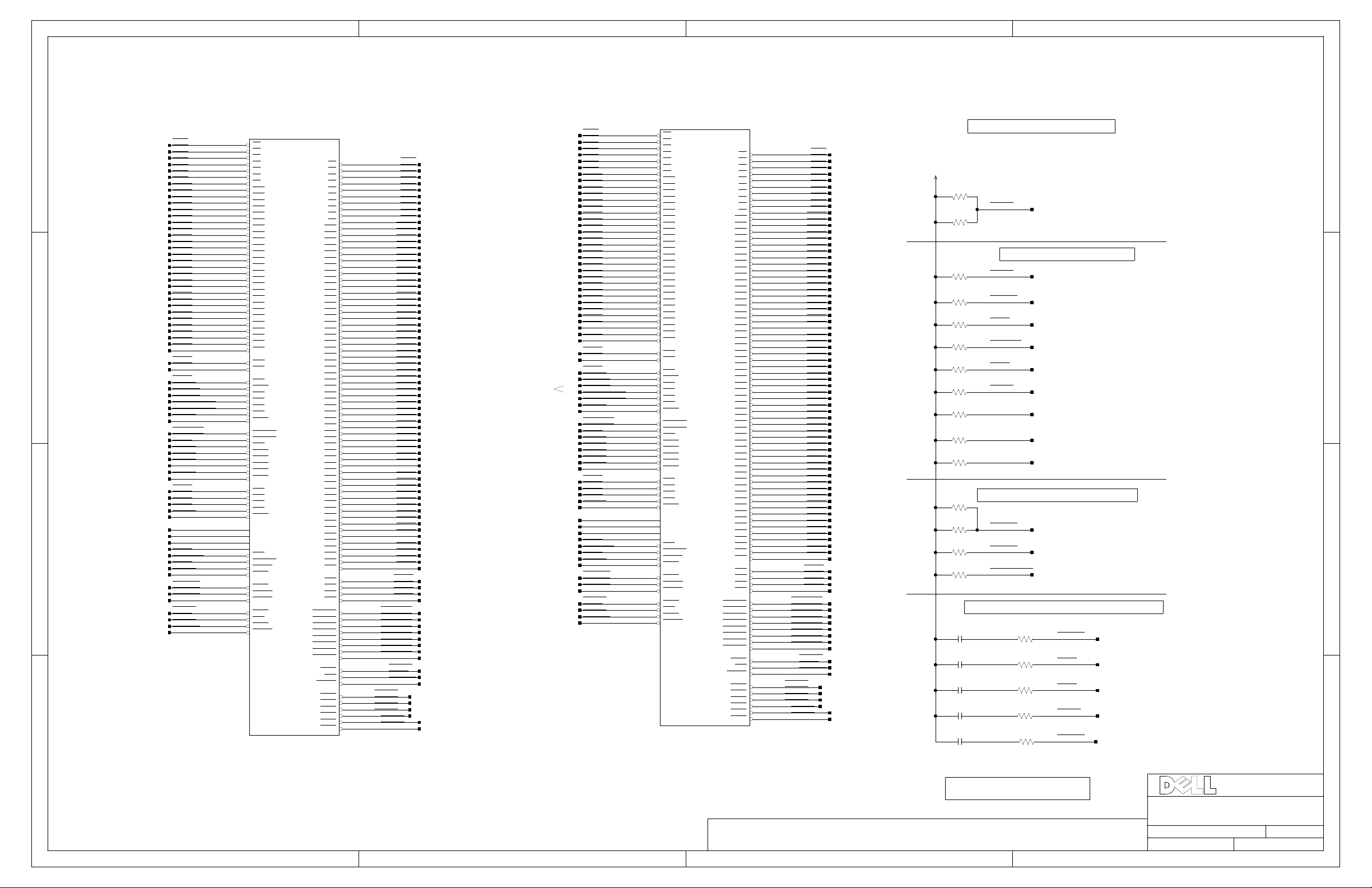

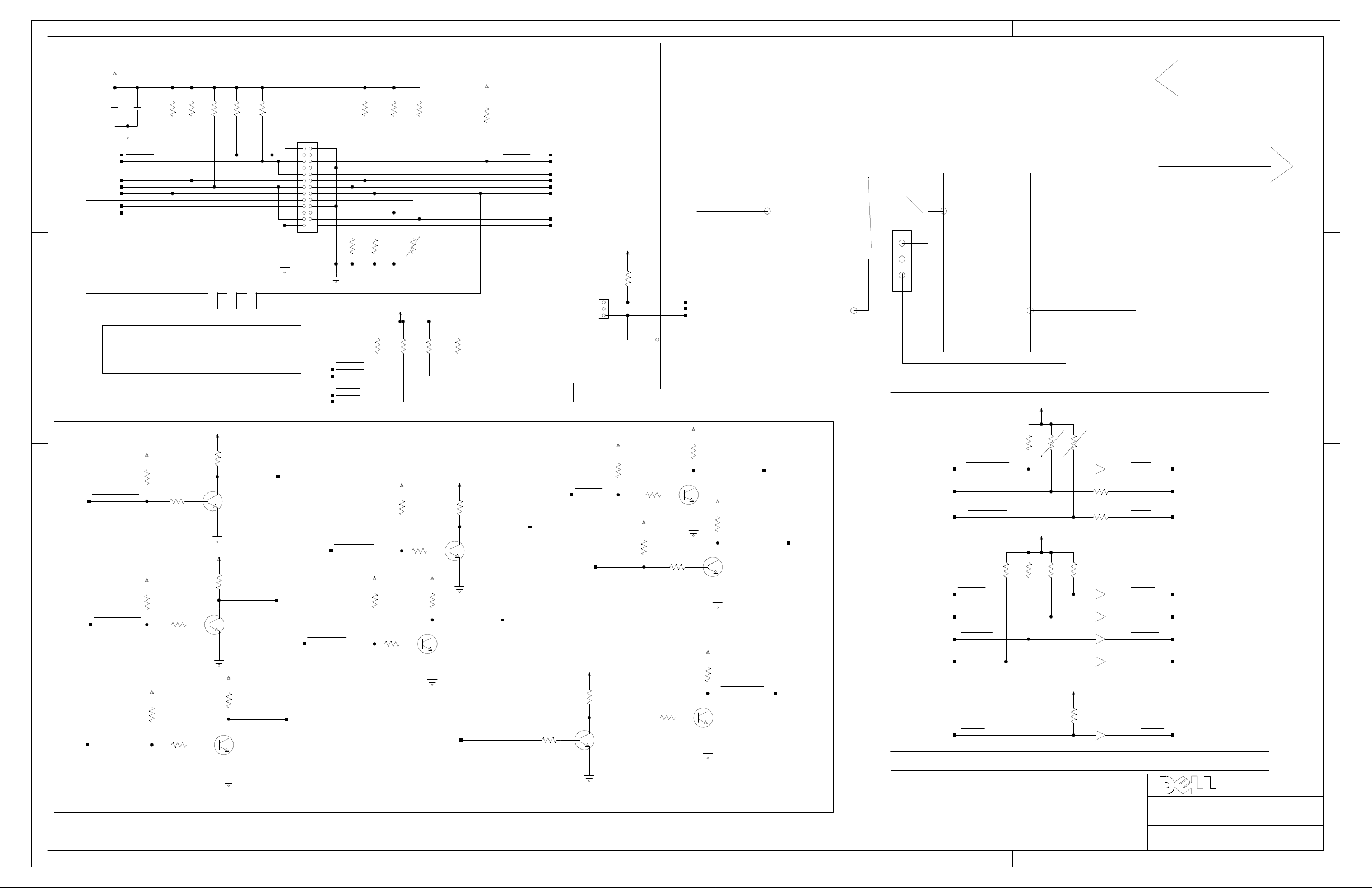

Page 2

B D

CA

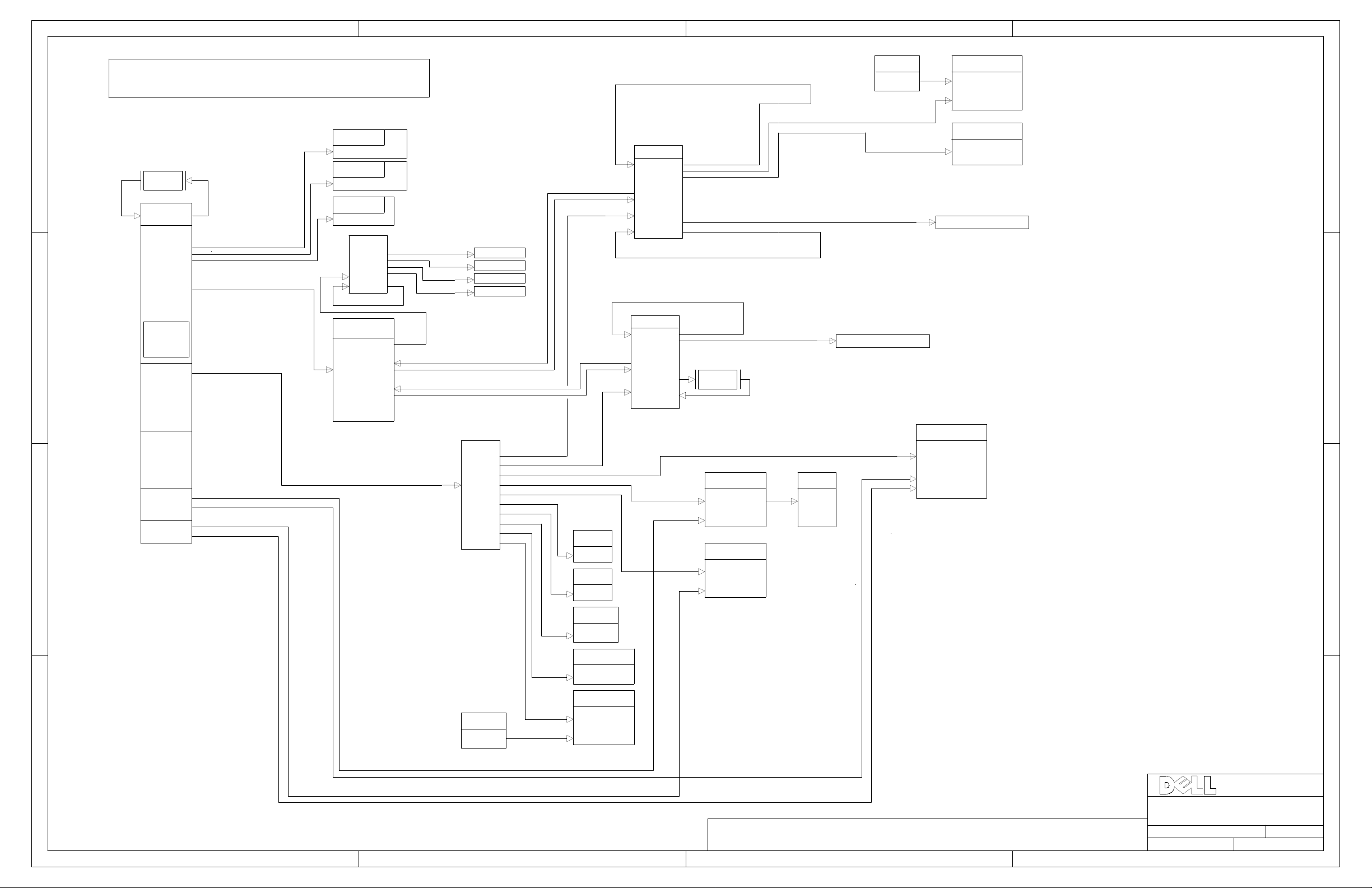

80MHz

OSC

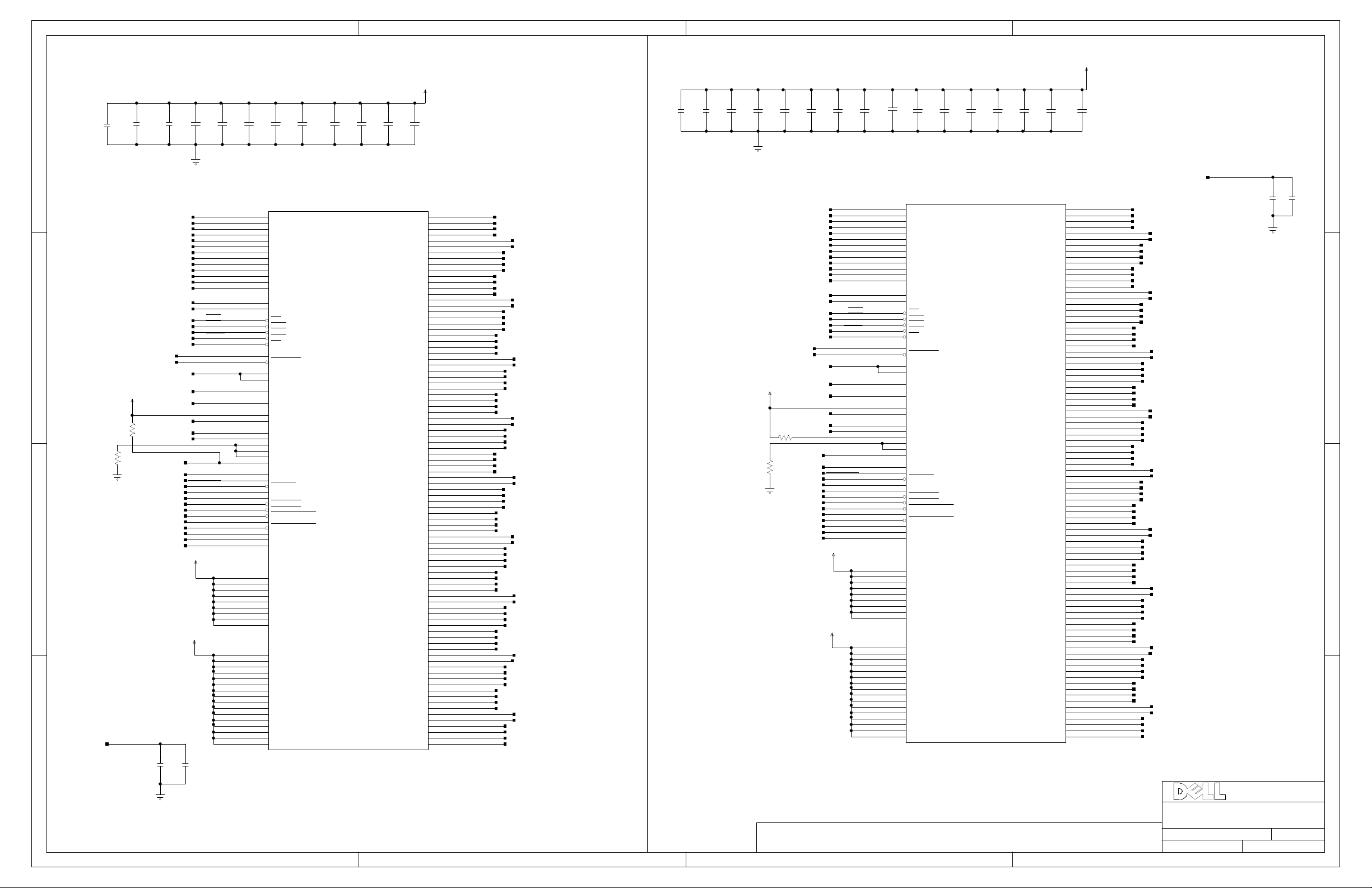

CLOCK DISTRIBUTION DIAGRAM

100MHz

1

14.3MHz

XTAL

XTALOUTXTALIN

133MHz

133MHz

133M

CDC950

2

CLOCK

GENERATOR

33M

REF

48M

133MHz

133MHz

33MHz

14.3MHz

14.3MHz

48MHz

48MHz

3

PRESTONIA

PROCESSOR

HOST

PRESTONIA

PROCESSOR

HOST

ITP

(DEBUG)

HOST

1-to-9

ZERO

DELAY

Buffer

IN

FB

CMIC-LE

NORTH BRIDGE

MCLK

IMB_CLK_A_R

BCLK

IMB_CLK_A_T

IMB_CLK_B_R

IMB_CLK_B_T

IMB_CLK_T

133MHz

133MHz

33MHz

200MHz

200MHz

200MHz

200MHz

DIMM

DIMM

DIMM

DIMM

1-to-10

BUFFER

10MHz

OSC

CLKOUT

33MHz

33MHz

33MHz

33MHz

33MHz

33MHz

33MHz

33MHz

33MHz

33MHz

200MHz

200MHz

200MHz

200MHz

PIRQ

SHIFTER

CLK

PIRQ

SHIFTER

CLK

ESM4

CONNECTOR

PCICLK

ESM3

CPLD

LPCCLK

ESM3

PROCESSOR

LPCCLK

CLKIN

CIOB-X2

PFBCLK

PCLK0

FSCLK_T

FSCLK_R

33M

SFBCLK SCLK0

CIOB-E

PFBCLK

PCLK0

PCLK0

PCLK0

FSCLK_T

FSCLK_R

33M

14.3MHz

33/66/133MHz

33/66/133MHz

25 MHz

XTAL

PCICLK

XTALIN XTALOUT

LPCCLK

48MHz

CLKIN

ATI

VIDEO

MEM_CLK CLK

SUPER I/O

87414

100MHz

100MHz

33/66/133MHz

33/66/133MHz

PROG

VIDEO

MEMORY

64 BIT PCI-X SLOT

14.3MHz

48MHz

80MHz

CLKOUT

SOUTH BRIDGE

PCICLK

REFCLK

USBCLK

64 BIT PCI-X SLOT

CSB5

LSI

1030

SCSICLK

PCICLK

ROMB SOCKET

PCICLK_IN

1

2

3

4

A B

14.3MHz

14.3MHz

48MHz

48MHz

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

COMPUTER

CORPORATION

TITLE

EVERGLADES MB

SCHEM,PLNR,PE1750,533MSI

DWG NO.

X1004

DATE

6/6/2003

EVERGLADES 2 6-9-2003_13:55

DC

AUSTIN,TEXAS

REV.

SHEET

2 OF 51

A00-00

4

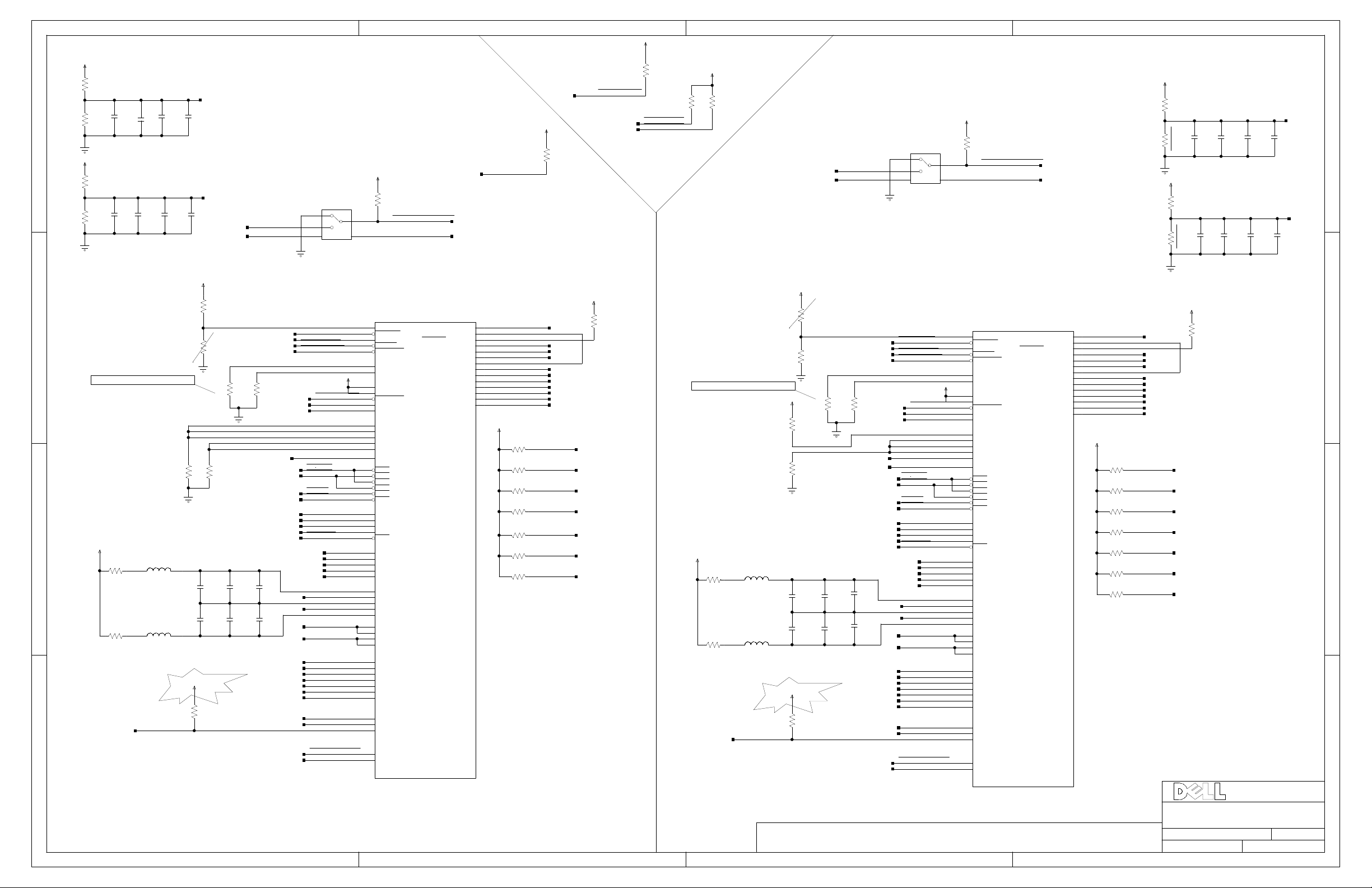

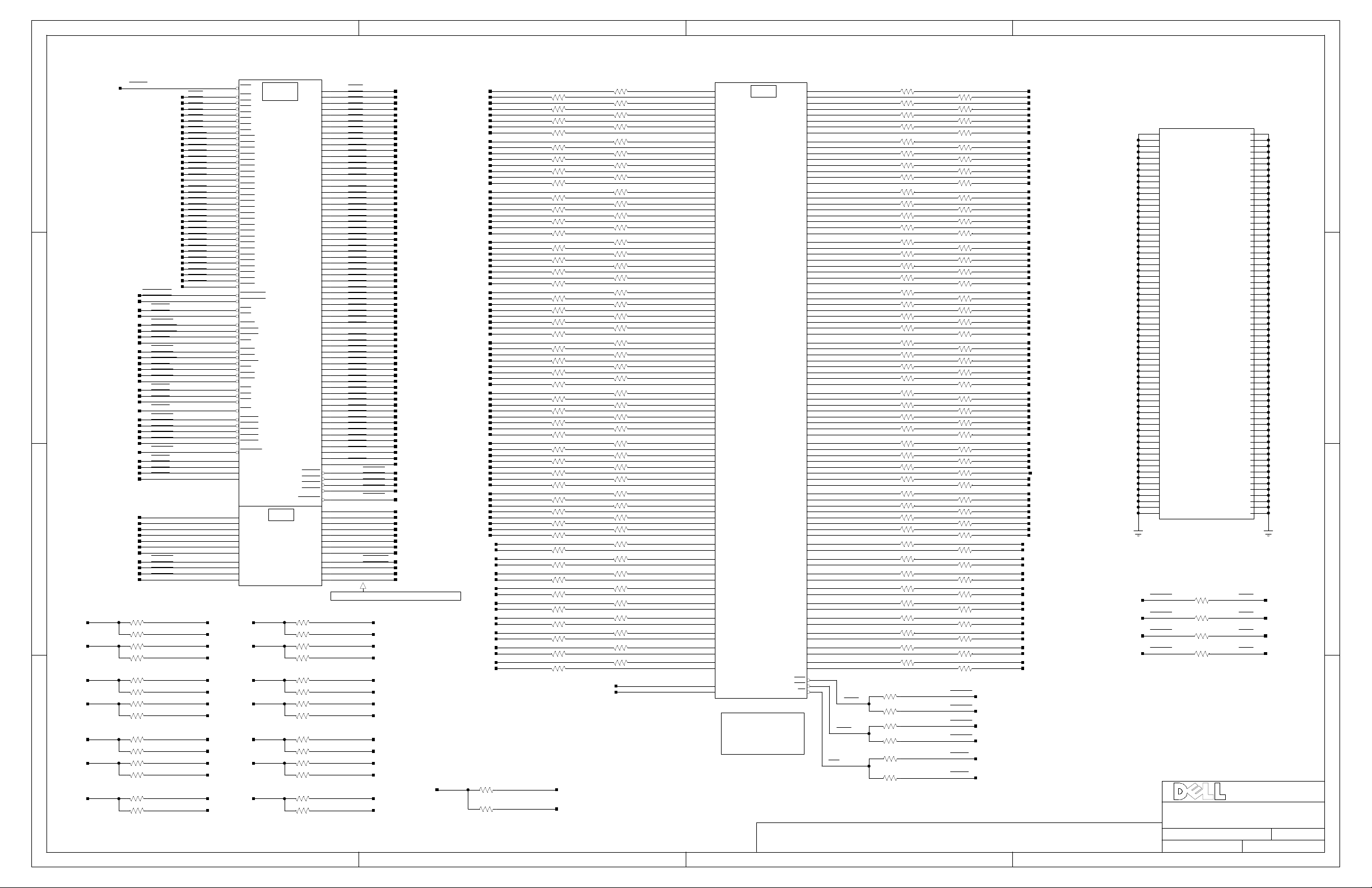

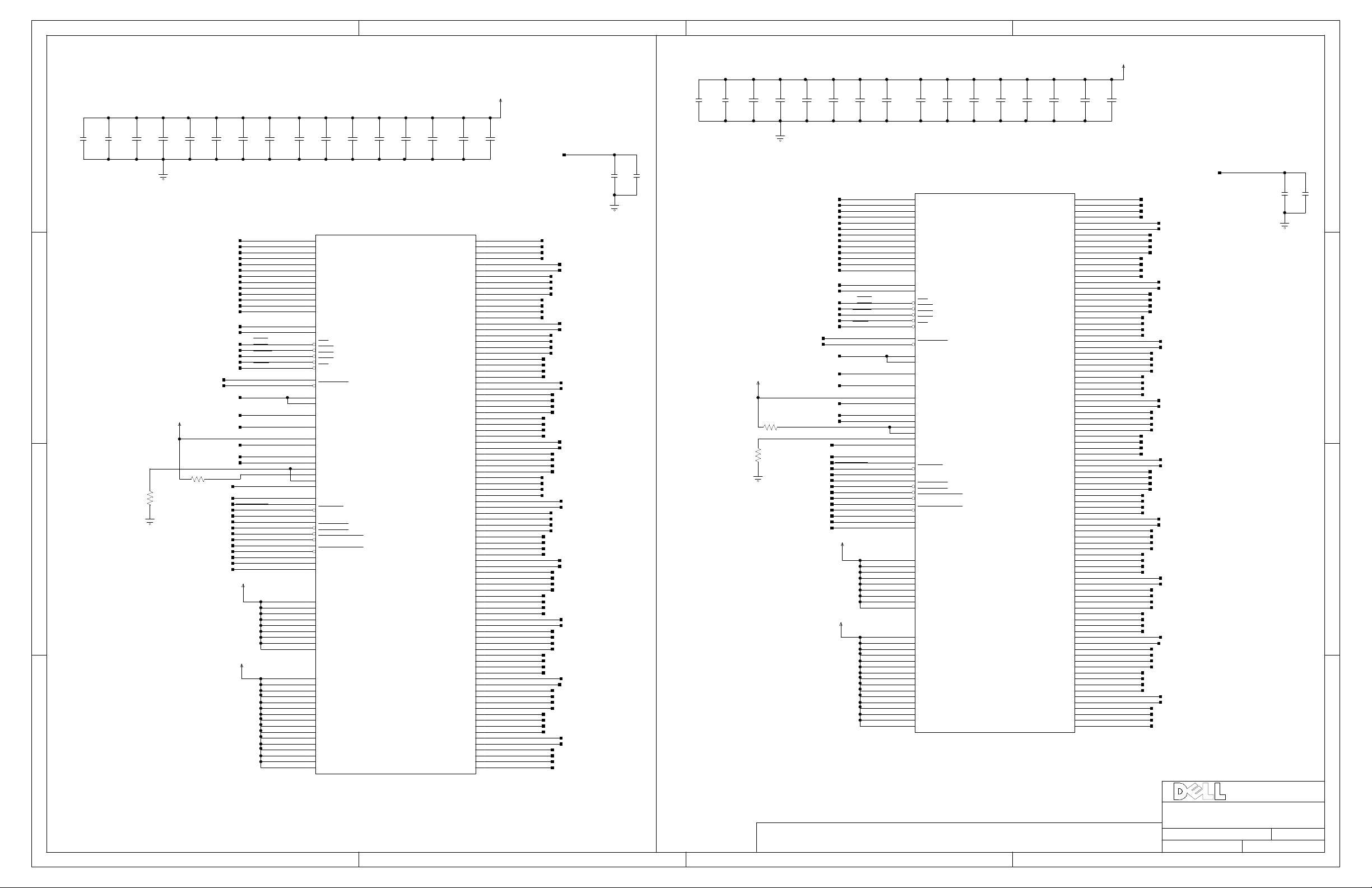

Page 3

B D

CA

1

2

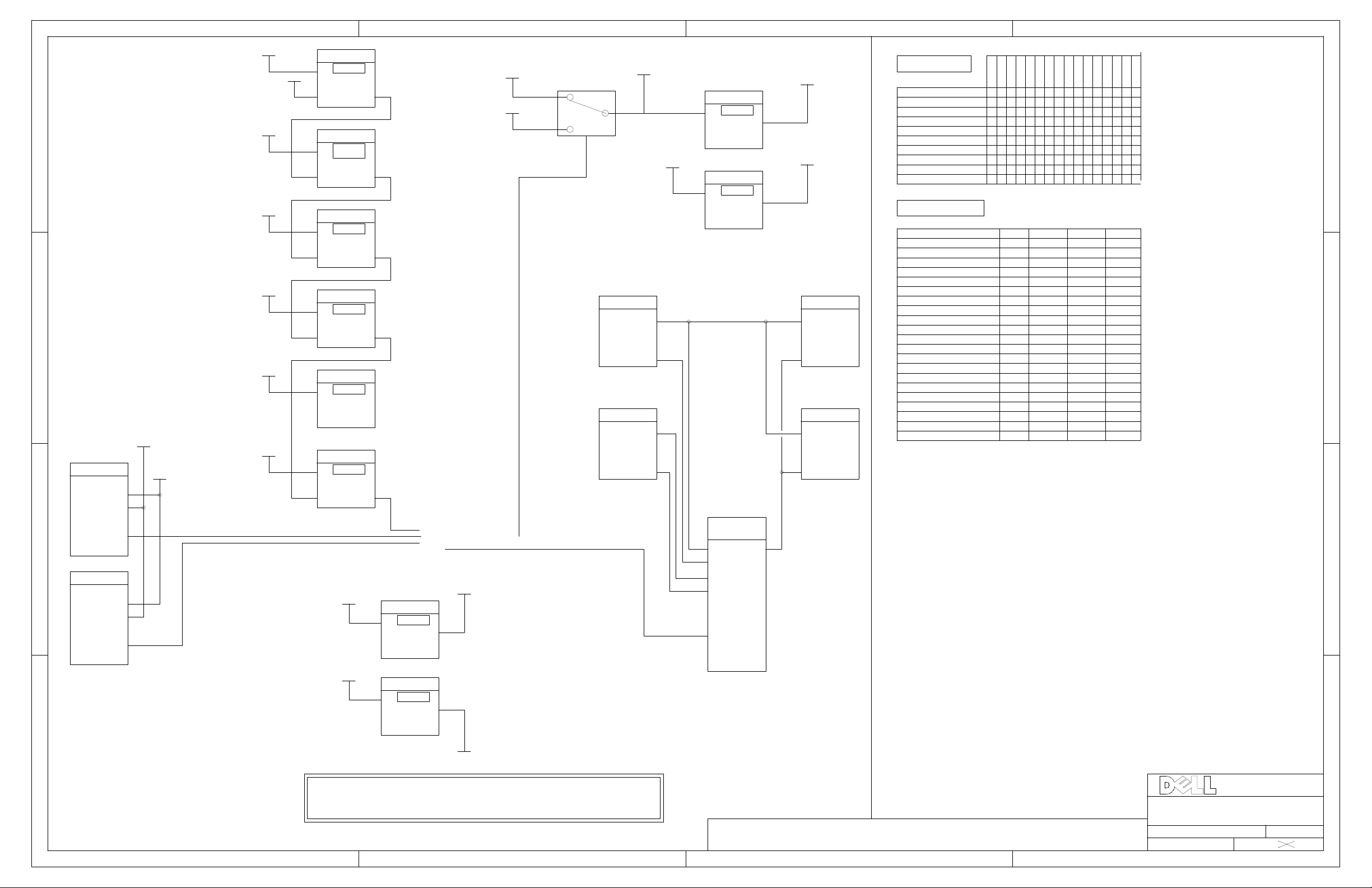

GREY BOX 1

3

GREY BOX 2

$8.35 for 100W SIP

+3.3V_AUX

+12V

+12V

+3.3V_FP

PWRGOOD

AC_OKPS_ON

+12V

+3.3V_FP

PWRGOOD

AC_OKPS_ON

PAGE 48

+12V

+12V

+12V

+12V

+2.5V

+12V

+12V

+5V

8-9A

IN

ENABLE

+5V

PWRGOOD

+1.8V

1.7A

IN

+1.8V

PWRGOODENABLE

+3.3V

11A

IN

+3.3V

PWRGOODENABLE

+2.5V

18A

IN

+2.5V

PWRGOODENABLE

+1.5V

2.7A

IN

+1.5V

DDR_TERM

5-6A

IN

+1.25V

PWRGOODENABLE

+3.3V_AUX

+5V

40W SIP=8A MAX

...OR 1x40W + 1x15W

PAGE 41

15W SIP

PAGE 41

40W SIP=10A MAX

...OR 1x40W + SMALL LINEAR?

PAGE 41

100W SIP=25A MAX

PAGE 41

LINEAR FROM 2.5V

PAGE 41

15W SIP

PAGE 41

+3.3V_AUX

+3.3V

INCOMPLETE!

+5V_AUX

5V_AUX

100mA

IN

+2.5V

PAGE 37

-12V

IN

100mA

PAGE 34

+2.5V

+3.3V_NIC

+2.5V_AUX

0.5A

IN

+2.5V

+3.3V_NIC or +2.5V_NIC ???

PAGE 30

+1.2V_AUX

1.9A

IN

+5V

PAGE 30

PROC 1

VID

PWRGOOD

THERMTRIP

PROC 2

V_CORE V_CORE

PWRGOOD

VID

THERMTRIP

+2.5V_NIC

LINEAR

+1.2V_NIC

LINEAR

CORE VRM 1

V_CORE

VIDV_CORE

ENABLEPWRGOOD

PAGE 9

CORE VRM 2

VID

ENABLE

PWRGOOD

PAGE 9

POWERGOOD

CPLD

VRM_ENVID1

THERMTRIP1

VID2

THERMTRIP2

PIRQ CONNECTIONS

PIRQ0

PIRQ1

PIRQ2

PIRQ3

PIRQ4

PIRQ5

DEVICE

CIOB-E

LSI 1030 SCSI

VERDE ROMB

PCI-X SLOT 1

PCI-X SLOT 2

ESM4

ESM3

PCI DEVICE NUMBERS

DEVICE BUS AD LINE DEVICE

CMIC

CIOB-E

CIOB-X2

ATI VIDEO

CSB5 -- MAIN

CSB5 -- IDE

CSB5 -- LPC BUS

CSB5 -- XIOAPIC (UNUSED)

ESM4

PCI-X SLOT 1 1

LSI 1030 SCSI

PCI-X SLOT 2

GIGABIT NIC A

GIGABIT NIC B

B

A

A

A

USES GPIOE16 ON THE SUPER I/O CHIP -- MUST BE SOFTWARE CONFIGURED TO GENERATE IRQ

0

0

0

0

0

0

0

0 AD31 0xF 3

0

0

2VERDE ROMB

2

3

4

PIRQ6

B

B

A B C D

AD16

AD30 0xE

AD31 0xF 0

AD31 0xF

AD31 0xF

AD31

AD24

AD22

AD19

AD21

AD20

TO USE ITP CONNECTOR,

POPULATE THE FOLLOWING COMPONENTS:

R106/R107 ON PAGE 4 WITH 22 OHM (133MHz CLOCK TO ITP)

J15 and P11 WITH APPROPRIATE CONNECTORS

PIRQ7

PIRQ8

PIRQ9

A B C D

0xF

PIRQ10

PIRQ11

PIRQ12

FUNCTION

0

8

6

3

5

4

1

14

PIRQ13

PIRQ14

0

1

2CSB5 -- USB

4-6

0

1

PIRQ15

1

DCBA

2

3

4

VOLTAGE CONVERTER BLOCK DIAGRAM

A B

-12V

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

COMPUTER

CORPORATION

TITLE

EVERGLADES MB

SCHEM,PLNR,PE1750,533MSI

DWG NO.

X1004

DATE

6/6/2003

EVERGLADES 3 6-9-2003_13:55

DC

AUSTIN,TEXAS

REV.

SHEET

3 OF 51

A00-00

4

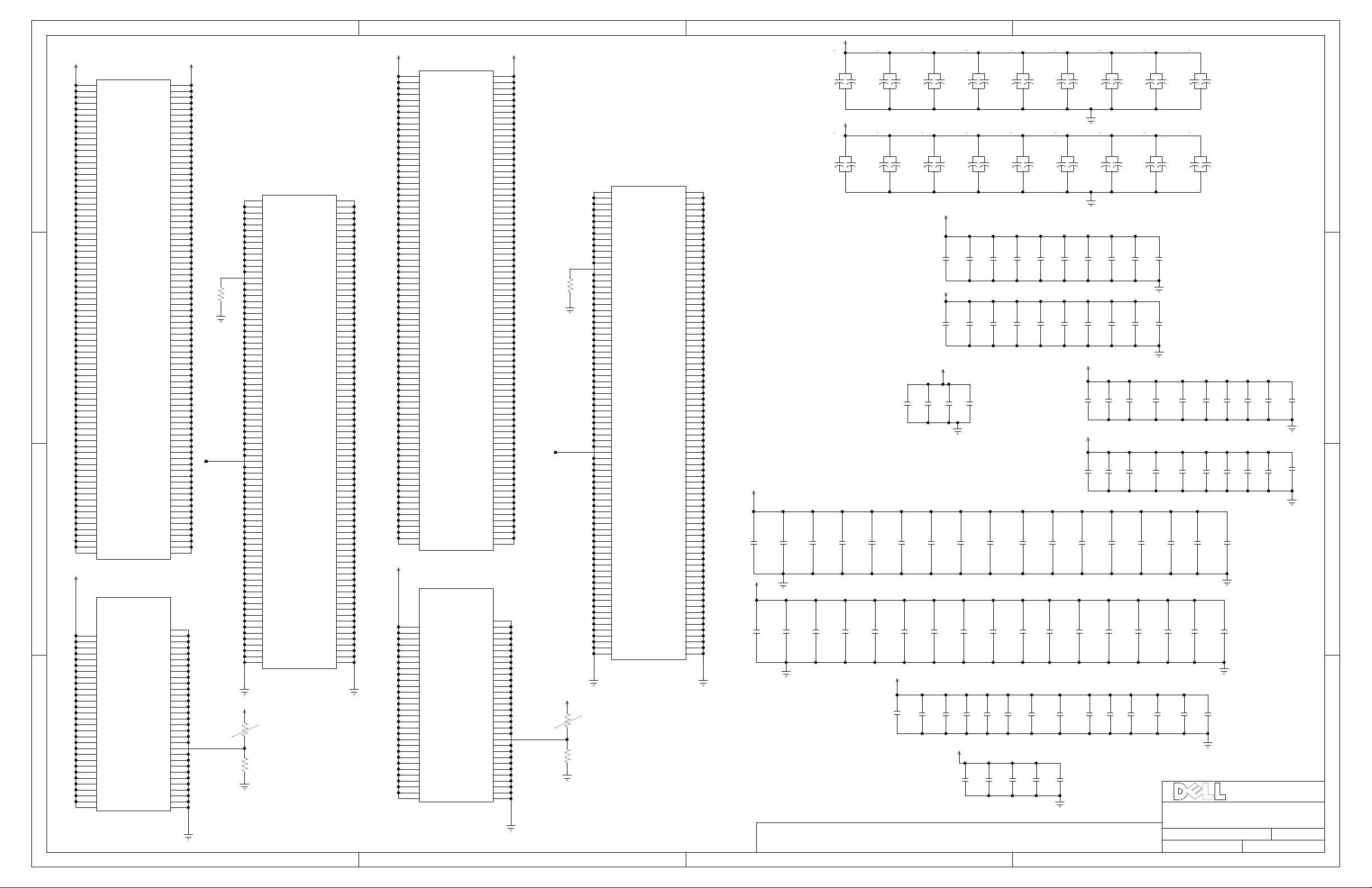

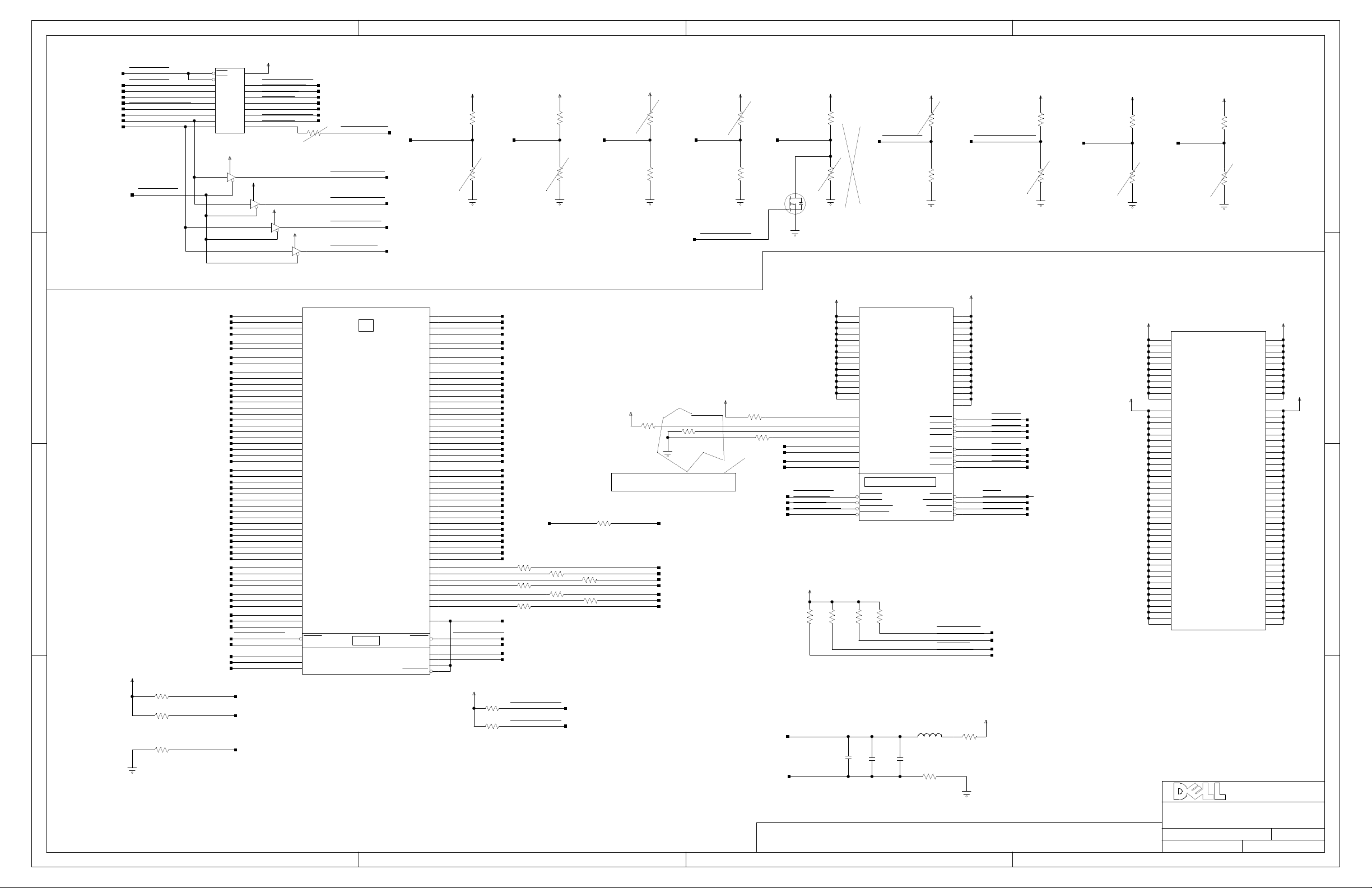

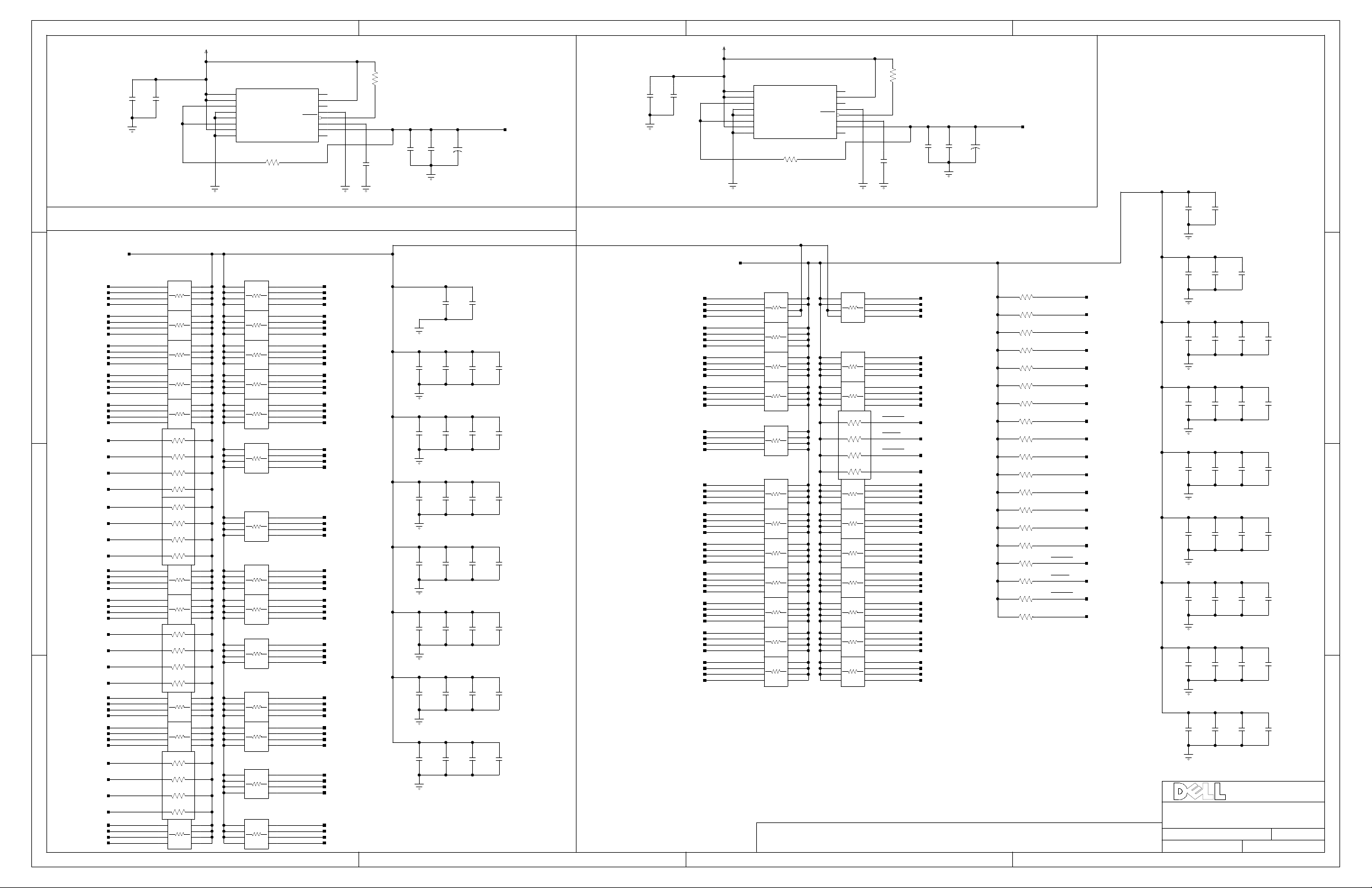

Page 4

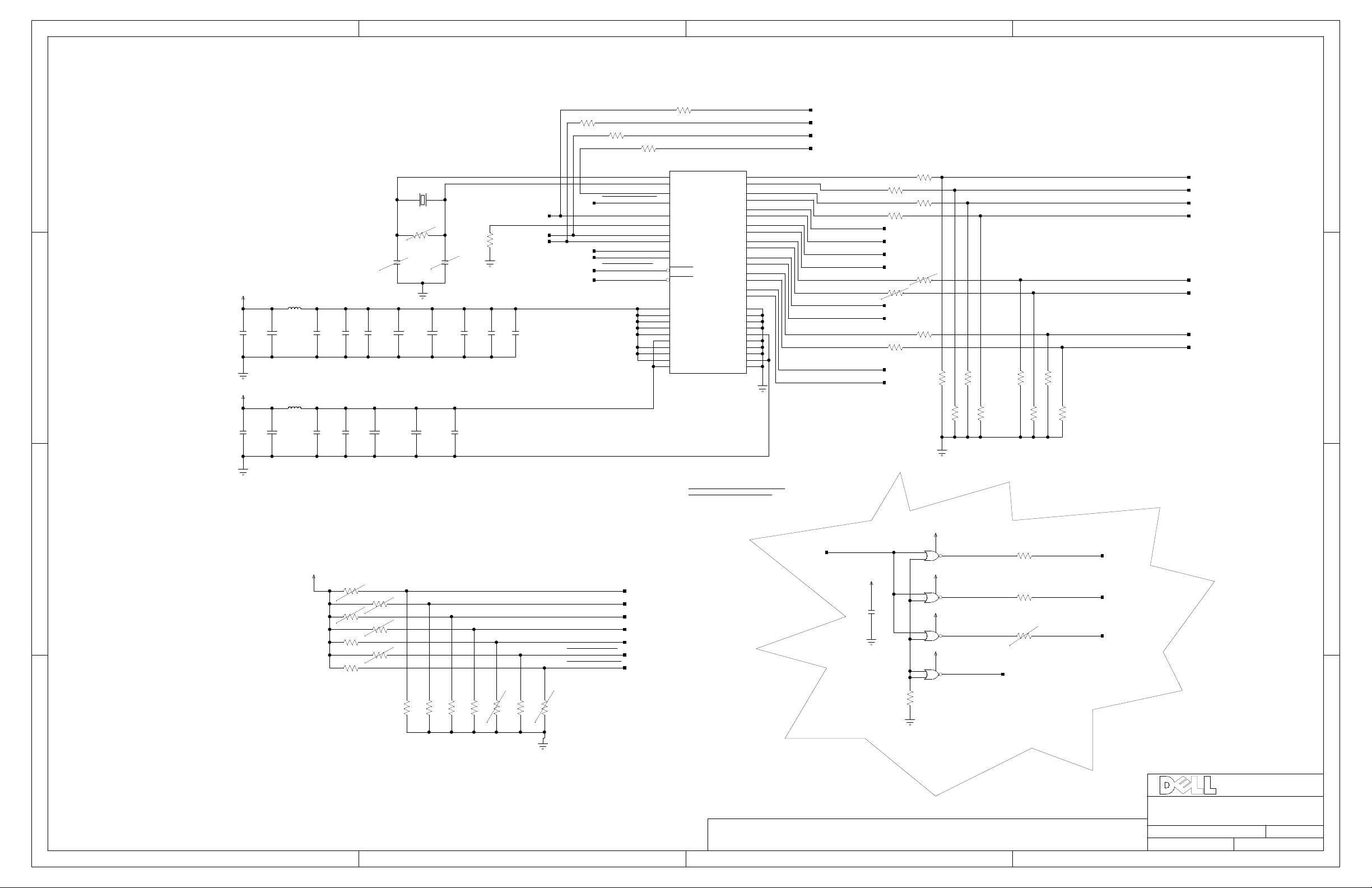

ROOM=MAINCLK

B D

CA

R199

R185

21

1

CK_SYN_XIN1

10pF

50V-5%

21

CB191

1 2

0.1uF 16V

CK_SYN_XIN2

R176

475-1%

1 2

21

CB17021CB189

0.1uF 16V

0.1uF 16V

0.1uF 16V

4

4

4

4,7,12,22

V_3P3_SYN1

V_3P3_SYN2

X3

21

14.31818MHz

R179

12

1M-5%

NP*

21

10pF

1 2

C235

NP*

+3.3V

21

2

C248

+3.3V

21

C230

4.7uF

4.7uF

C247

1 2

6.3V-10%

C231

1 2

6.3V-10%

L41

600mA

.01UF

50V-20%

L39

1 2

600mA

.01UF

50V-20%

21

21

CB193

21

CB172

4.7uF

CB190

6.3V-10%

4.7uF

CB178

6.3V-10%

1 2

0.1uF 16V0.1uF 16V

21

1 2

CB169

CB167

CB192

0.1uF 16V

.01UF

1 2

50V-20%

1 2

50V-5%

.01UF

50V-20%

1 2

CB179

1 2

CB168

.01UF

50V-20%

C242

.01UF

NP*

50V-20%

CB171

22-5%

47

4

4

4

R184

1 2

22-5%

R_CK_33M_PCI

GPI_SYN_SEL100

R_CK_14M_CSB

SYN_IREF_26

R_CK_48M_USB

R_CK_48M_SIO

SYN_MULTSEL0

SYN_MULTSEL1

GPI_SPREAD_EN

SYNTH_EN

R183

1 2

22-5%

21

22-5%

22 7

XIN HCLK0

23

XOUT

1

CLK33

48

SEL100/133

19

REF

26

IREF

3

3V48/SELA

4

3V48B/SELB

30

MULTISEL0

29

MULTISEL1

20

SPREAD

44

PWRDWN

2

VDD0

6

VDD1

12

VDD2

18

VDD3

24

VDD4

25

VDD5

31

VDD6

37

VDD7

43

VDD8

46

VDD9

U24

HCLKB0

HCLKB1

HCLKB2

HCLKB3

HCLKB4

HCLKB5

HCLKB6

HCLKB7

CDC950/9248

TSSOP48

SUB*_4C853

HCLK1

HCLK2

HCLK3

HCLK4

HCLK5

HCLK6

HCLK7

GND0

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

GND9

8

10

11

13

14

16

17

42

41

39

38

36

35

33

32

5

9

15

21

27

28

34

40

45

47

CK_14M_TO_BUFFER

CK_48M_SIO

CK_48M_USB

CK_33M_PBUF2

4

22

18

5

R_CK_100M_CPU0_P

R_CK_100M_CPU0_N

R_CK_100M_CPU1_P

R_CK_100M_CPU1_N

NC_CK_100M_MEM_P

NC_CK_100M_MEM_N

NC_CK_100M_SYN_16

NC_CK_100M_SYN17

R_CK_100M_ITP_P

R_CK_100M_ITP_N

NC_CK_100M_SP2_P

NC_CK_100M_SP2_N

R_CK_100M_CMIC_P

R_CK_100M_CMIC_N

NC_CK_100M_SYN33_P

NC_CK_100M_SYN32_N

1 2

NP0

1 2

R195

22-5%

R197

22-5%

R171

22-5%

R173

22-5%

1 2

21

1 2

NP0

21

1 2

R194

22-5%

R196

22-5%

R170

22-5%

R172

22-5%

21

21

R208

R210

49.9-1%

21

R209

49.9-1%

21

49.9-1%

R211

21

49.9-1%

21

R152

R154

49.9-1%

21

R153

49.9-1%

21

49.9-1%

R155

21

49.9-1%

CK_100M_CPU0_P

CK_100M_CPU0_N

CK_100M_CPU1_P

CK_100M_CPU1_N

CK_100M_ITP_P

CK_100M_ITP_N

CK_100M_CMIC_P

CK_100M_CMIC_N

1

6

6

6

6

10

10

12

12

2

4C853 RCC_SYN (TSSOP48) IS:

TI CDC950DGG

ICS ICS9248AG-150

PHILIPS PCK2022RDGG

PERICOM PI6C210A

+3.3V

14 U65

R470

1 2

2

1

3

74VHC02

5

6

74VHC02

8

9

74VHC02

11

12

74VHC02

220

CK_14M_XLSYN_R

SUB*_907XP

+3.3V

SUB TO LCX FOR EDGE RATE

14 U65

4

CK_14M_CSB_R

SUB*_907XP

+3.3V

SUB TO LCX FOR EDGE RATE

14 U65

10

CK_14M_RNDM_R

SUB*_907XP

+3.3V

SUB TO LCX FOR EDGE RATE

14 U65

13

NC_14MBUF_X2

SUB*_907XP

SUB TO LCX FOR EDGE RATE

X01 -- BUFFERED 14MHz CLOCK TO IMPROVE EDGE RATES

3

+3.3V

R214

21

NP

10K-5%

R193

1 2

NP

10K-5%

R192

21

NP

10K-5%

R174

1 2

NP

10K-5%

R175

21

10K-5%

R198

21

NP

10K-5%

R169

1 2

10K-5%

21

R212

1 2

SPREAD LOW = SPREAD ENABLED

4

SPREAD HIGH = SPREAD DISABLED

SEL100 LOW = 100MHZ

SEL100 HIGH = 133MHZ

MULTSEL0 & MULTSEL1 SELECTION

0 0 60ohm, 0.71V

0 1 50ohm, 0.71V

SELA & SELB SELECTION

0 0 H=NORMAL MODE

R207

1K-5%

R205

1K-5%

1 2

R156

1K-5%

NP

21

21

220

R157

220

R213

1 2

220

21

R151

NP

220

R_CK_14M_CSB

R_CK_48M_SIO

R_CK_48M_USB

SYN_MULTSEL0

SYN_MULTSEL1

GPI_SPREAD_EN

GPI_SYN_SEL100

4

4

4

4

4

4

4,7,12,22

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

CK_14M_TO_BUFFER

4

+3.3V

21

CB509

0.1uF 16V

A B

R472

33-5%

R471

33-5%

R494

33-5%

21

CK_14M_XLSYN

21

CK_14M_CSB

21

CK_14M_RNDM

NP*

24

18

47

3

4

COMPUTER

CORPORATION

TITLE

EVERGLADES MB

SCHEM,PLNR,PE1750,533MSI

DWG NO.

DATE

X1004

6/6/2003

EVERGLADES 4 6-9-2003_13:55

DC

AUSTIN,TEXAS

REV.

SHEET

4 OF 51

A00-00

Page 5

B D

CK_133M_MCLK_P

11

CK_133M_MCLK_N

11

1

CK_MEM_FB_133M_N

+2.5V

C345

1 2

1 2

CB271

0.1uF 16V

L46

600mA

L45

600mA

0.1uF 16V

21

21

6.3V-10%

4.7uF

CB272

1

2

C328

1 2

CB284

1 2

CB283

3300pF

50V-10%

.01UF

CB282

50V-20%

1 2

0.1uF 16V

.01UF

1 2

1 2

CB281

50V-20%

1 2

CB273

0.1uF 16V

0.1uF 16V

CK_MEM_FB_133M_P

+2.5V

C335

1 2

.01UF

1 2

CB285

50V-20%

0.1uF 16V

1 2

CB274

2

OVERLAP THESE THREE PINS

IF POSSIBLE

CA

R294

1 2

100-1%

ROOM=DDRCLK

U33

0-5%0-5%

RB137

RB133

1 2

0-5%

CLK0_P

CLK0_N

CLK1_P

CLK1_N

CLK2_P

CLK2_N

CLK3_P

CLK3_N

CLK4_P

CLK4_N

CLK5_P

CLK5_N

CLK6_P

CLK6_N

CLK7_P

CLK7_N

CLK8_P

CLK8_N

CLK9_P

CLK9_N

FBOUT_P

FBOUT_N

12

NP*

3

2

5

6

10

9

20

19

22

23

46

47

44

43

39

40

29

30

27

26

32

33

1 2

100-1%

14,15,21

14,15,21

R295

1 2

0-5%

C332

1 2

0.1uF 16V

0.1uF 16V

R276

ASDATA_2P5V

ASCLK_2P5V

13

CLKIN_P

14

CLKIN_N

35

FBIN_N

36

FBIN_P

37

SDA

12

SCK

16

AVCC

17

AGND

4

VDDQ0

11

VDDQ1

15

I2CVDD

21

VDDQ3

28

VDDQ4

34

VDDQ5

38

VDDQ6

45

VDDQ7

1

GND0

7

GND1

8

GND2

18

GND3

24

GND4

25

GND5

31

GND6

41

GND7

42

GND8

48

GND9

2.5V PLL CLOCK DRIVER

FBIN_N AND FBIN_P ARE SWAPPED ON DIFFERENT VENDORS

BUT FBOUT_P AND FBOUT_N ARE ALSO SWAPPED

NOTE

SO IT IS NOT A PROBLEM

0-5%

12

RB134

NP*

FBOUT_LOOP1_N

12

RB141

RB139

1 2

FBOUT_LOOP2_N

0-5%

NP*

59PRT IS:

TI CDCV850DGG

ICS ICS93701BG

PHILIPS PCK2057DGG

CK_SP5_133M_P

CK_SP5_133M_N

CK_SP1_133M_P

CK_SP1_133M_N

CK_SP2_133M_P

CK_SP2_133M_N

CK_SP3_133M_P

CK_SP3_133M_N

CK_DBG_133M_P

CK_DBG_133M_N

CK_SP4_133M_P

CK_SP4_133M_N

CK_133M_DDR3_P

CK_133M_DDR3_N

CK_133M_DDR2_P

CK_133M_DDR2_N

CK_133M_DDR1_P

CK_133M_DDR1_N

CK_133M_DDR0_P

CK_133M_DDR0_N

CK_MEM_FB_OUT_133M_P

CK_MEM_FB_OUT_133M_N

OVERLAP THESE THREE PINS

IF POSSIBLE

5

5

5

5

5

5

5

5

5

5

15

15

15

15

14

14

14

14

HEADER FOR LOGIC ANALYZER CLOCK

J4

1

NP*

100-1%

J3

1

NP*

5

5

5

CK_SP1_133M_P

CK_SP1_133M_N

CK_SP2_133M_P

R292

1 2

100-1%

R297

1 2

2

R293

100-1%

1

CK_SP2_133M_N

5

CK_SP3_133M_P

5

CK_SP3_133M_N

5

CK_SP4_133M_P

5

1 2

R296

1 2

100-1%100-1%

OVERLAP THESE THREE PINS

33 MHz PCI CLOCK GENERATION

3

+3.3V

1 2

0.1uF 16V

C426

21

L50

600mA

21

CB427

4.7uF

21

CB413

6.3V-10%

V_3P3_PBUF2

C418

1 2

0.1uF 16V

.01UF

50V-20%

C397

1 2

.01UF

50V-20%

1 2

C405

C398

1 2

0.1uF 16V

CK_33M_PBUF2

4

.01UF

50V-20%

1 2

CB415

.01UF

50V-20%

RB267

10K-5%

21

4

2204T CKBUF_M (SSOP28) IS:

ROOM=PCICLK

10K-5%

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

SDATA

SCLOCK

BUF_IN

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

W40S11_02

SUB*_2204T

U37

R371

10K-5%

1

5

10

19

24

28

14

21

15

9

4

8

12

17

21

25

R345

21

VDDIIC

SDRAM0

SDRAM1

SDRAM2

SDRAM3

SDRAM4

SDRAM5

SDRAM6

SDRAM7

SDRAM8

SDRAM9

VSSIIC

PBUF2_OE

13

20

OE

2

3

6

7

22

23

26

27

11

18

16

R_CK_33M_LPC

R_CK_33M_CIOB

R_CK_33M_VIDEO

R_CK_33M_SIO

R_CK_33M_PIRQ0

R_CK_33M_RISER

R_CK_33M_ESM4

R_CK_33M_CPLD1

R_CK_33M_CSB5

R_CK_33M_PIRQ1

RB242

22-5%

RB246

22-5%

R344

22-5%

R336

1 2

22-5%

R347

22-5%

R343

21

22-5%

21

RB245

21

22-5%

21

RB244

21

22-5%

21

RB241

21

22-5%

RB265

21

22-5%

21

IF POSSIBLE

CK_33M_LPC

CK_33M_CIOB

CK_33M_VIDEO

CK_33M_SIO

CK_33M_PIRQ0

CK_33M_CIOBE

CK_33M_ESM4

CLK_PCI32_ZIRCON

CK_33M_CSB5

CK_33M_PIRQ1

0-5%

NP*

12

RB136

0-5% 0-5%

FBOUT_LOOP1_P

12

RB142

RB140

1 2

FBOUT_LOOP2_P

0-5% 0-5%

NP*

19

27

24

22

19

28

39

35

18

19

12

RB138

RB135

1 2

NP*

MEMORY CLOCK GENERATION

CYPRESS W40S11-02

PERICOM PI6C182AH

ICS ICS9279AF-03

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

A B

OVERLAP THESE THREE PINS

IF POSSIBLE

R275

CK_SP4_133M_N

5

CK_SP5_133M_P

5

CK_SP5_133M_N

5

TITLE

EVERGLADES MB

SCHEM,PLNR,PE1750,533MSI

DWG NO.

DATE

X1004

6/6/2003

EVERGLADES 5 6-9-2003_13:55

DC

1 2

R300

100-1%

1 2

COMPUTER

CORPORATION

AUSTIN,TEXAS

REV.

SHEET

5 OF 51

A00-00

3

4

Page 6

B D

CA

1

H_A3

6,11

H_A4

6,11

H_A5

6,11

H_A6

6,11

H_A7

6,11

H_A8

6,11

H_A9

6,11

H_A10

6,11

H_A11

6,11

H_A12

6,11

H_A13

6,11

H_A14

6,11

H_A15

6,11

H_A16

6,11

H_A17

6,11

H_A18

6,11

H_A19

6,11

H_A20

6,11

H_A21

6,11

H_A22

6,11

H_A23

6,11

H_A24

6,11

H_A25

6,11

H_A26

6,11

H_A27

6,11

H_A28

6,11

H_A29

6,11

H_A30

6,11

H_A31

6,11

H_A32

6,11

H_A33

2

3

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,10

6,10

6,10

6,10

6,10,12

6,10

6,10

6,11

6,10

6,10

6,10

6,10

H_A34

H_A35

H_AP0

H_AP1

H_BNR

H_BPRI

H_BREQ0

H_BREQ1

6

H_BREQ23_PU

6

H_BREQ23_PU

6

H_LOCK

H_ADSTB0

H_ADSTB1

H_ADS

H_REQ0

H_REQ1

H_REQ2

H_REQ3

H_REQ4

H_RS0

H_RS1

H_RS2

H_RSP

H_TRDY

CK_100M_CPU0_P

4

CK_100M_CPU0_N

4

H_INTR

H_NMI

H_SLP

H_STPCLK

H_RST

H_INIT

H0_IERR

10

H_MCERR

H_BINIT

H_A20M

H_SMI

H_FERR

H_IGNNE

A22

A20

B18

C18

A19

C17

D17

A13

B16

B14

B13

A12

C15

C14

D16

D15

F15

A10

B10

B11

C12

E14

D13

A9

B8

E13

D12

C11

B7

A6

A7

C9

C8

E10

D9

F20

D23

D20

F12

E11

D10

A17

F17

F14

D19

B19

B21

C21

C20

B22

E21

D22

F21

C6

E19

Y4

W5

B24

G23

AE6

D4

Y8

D6

E5

D7

F11

F27

C27

E27

C26

PRESTONIA/NOCONA 604 PROCESSOR

4

PROC_0

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

AP0

AP1

BNR

BPRI

BR0

BR1

BR2

BR3

LOCK

ADSTB0

ADSTB1

ADS

REQ0

REQ1

REQ2

REQ3

REQ4

RS0

RS1

RS2

RSP

TRDY

BCLK0

BCLK1

LINT0

LINT1

SLP

STPCLK

RESET

INIT

IERR

MCERR

BINIT

A20M

SMI

FERR

IGNNE

REV. 1.5-EMTS, ZIF SKT

HETERO 1 OF 5

ADD1=ADD*_Y0363_SCREW

ADD2=ADD*_Y0363_SCREW

ADD3=ADD*_Y0363_SCREW

ADD4=ADD*_Y0363_SCREW

ADD5=ADD*_Y0363_SCREW

ADD6=ADD*_Y0363_SCREW

ADD7=ADD*_Y0363_SCREW

ADD8=ADD*_Y0363_SCREW

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

DP0

DP1

DP2

DP3

DSTBN0

DSTBN1

DSTBN2

DSTBN3

DSTBP0

DSTBP1

DSTBP2

DSTBP3

HITM

HIT

DEFER

DBI0

DBI1

DBI2

DBI3

DBSY

DRDY

H_A3

6,11

H_A4

6,11

H_A5

6,11

H_A6

6,11

Y26

D0

AA27

D1

Y24

D2

AA25

D3

AD27

D4

Y23

D5

AA24

D6

AB26

D7

AB25

D8

AB23

D9

AA22

AA21

AB20

AB22

AB19

AA19

AE26

AC26

AD25

AE25

AC24

AD24

AE23

AC23

AA18

AC20

AC21

AE22

AE20

AD21

AD19

AB17

AB16

AA16

AC17

AE13

AD18

AB15

AD13

AD14

AD11

AC12

AE10

AC11

AE9

AD10

AD8

AC9

AA13

AA14

AC14

AB12

AB13

AA11

AA10

AB10

AC8

AD7

AE7

AC6

AC5

AA8

Y9

AB6

AC18

AE19

AC15

AE17

Y21

Y18

Y15

Y12

Y20

Y17

Y14

Y11

A23

E22

C23

AC27

AD22

AE12

AB9

F18

E18

H_DSTBN0

H_DSTBN1

H_DSTBN2

H_DSTBN3

H_DSTBP0

H_DSTBP1

H_DSTBP2

H_DSTBP3

H_HITM

H_HIT

H_DEFER

H_DBI0

H_DBI1

H_DBI2

H_DBI3

H_DBSY

H_DRDY

H_D0

H_D1

H_D2

H_D3

H_D4

H_D5

H_D6

H_D7

H_D8

H_D9

H_D10

H_D11

H_D12

H_D13

H_D14

H_D15

H_D16

H_D17

H_D18

H_D19

H_D20

H_D21

H_D22

H_D23

H_D24

H_D25

H_D26

H_D27

H_D28

H_D29

H_D30

H_D31

H_D32

H_D33

H_D34

H_D35

H_D36

H_D37

H_D38

H_D39

H_D40

H_D41

H_D42

H_D43

H_D44

H_D45

H_D46

H_D47

H_D48

H_D49

H_D50

H_D51

H_D52

H_D53

H_D54

H_D55

H_D56

H_D57

H_D58

H_D59

H_D60

H_D61

H_D62

H_D63

H_DP0

H_DP1

H_DP2

H_DP3

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,12

6,12

6,12

6,12

6,12

6,12

6,12

6,12

6,11

6,11

6,11

6,11

6,11

Swizzled.

ADD1=ADD*_89JJP_SCREW2

ADD2=ADD*_89JJP_SCREW2

ADD3=ADD*_89JJP_SCREW2

ADD4=ADD*_89JJP_SCREW2

ADD5=ADD*_89JJP_SCREW2

ADD6=ADD*_89JJP_SCREW2

ADD7=ADD*_89JJP_SCREW2

ADD8=ADD*_89JJP_SCREW2

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,10

6,10

6,10

6,10

6,10,12

6,10

6,10

6,11

6,10

6,10

6,10

6,10

H_A7

H_A8

H_A9

H_A10

H_A11

H_A12

H_A13

H_A14

H_A15

H_A16

H_A17

H_A18

H_A19

H_A20

H_A21

H_A22

H_A23

H_A24

H_A25

H_A26

H_A27

H_A28

H_A29

H_A30

H_A31

H_A32

H_A33

H_A34

H_A35

H_AP0

H_AP1

H_BNR

H_BPRI

H_BREQ1

6

H_BREQ0

H_BREQ23_PU

6

H_BREQ23_PU

6

H_LOCK

H_ADSTB0

H_ADSTB1

H_ADS

H_REQ0

H_REQ1

H_REQ2

H_REQ3

H_REQ4

H_RS0

H_RS1

H_RS2

H_RSP

H_TRDY

CK_100M_CPU1_P

4

CK_100M_CPU1_N

4

H_INTR

H_NMI

H_SLP

H_STPCLK

H_RST

H_INIT

H1_IERR

10

H_MCERR

H_BINIT

H_A20M

H_SMI

H_FERR

H_IGNNE

A22

A20

B18

C18

A19

C17

D17

A13

B16

B14

B13

A12

C15

C14

D16

D15

F15

A10

B10

B11

C12

E14

D13

A9

B8

E13

D12

C11

B7

A6

A7

C9

C8

E10

D9

F20

D23

D20

F12

E11

D10

A17

F17

F14

D19

B19

B21

C21

C20

B22

E21

D22

F21

C6

E19

Y4

W5

B24

G23

AE6

D4

Y8

D6

E5

D7

F11

F27

C27

E27

C26

PRESTONIA/NOCONA 604 PROCESSOR

SOURCE SYNC GROUP 1 - BUS_NAME=GTL1

SOURCE SYNC GROUP 2 - BUS_NAME=GTL2

SOURCE SYNC GROUP 3 - BUS_NAME=GTL3

SOURCE SYNC GROUP 4 - BUS_NAME=GTL4

SOURCE SYNC GROUP 5 - BUS_NAME=GTL5

SOURCE SYNC GROUP 6 - BUS_NAME=GTL6

GTL "WIRE-OR" SIGNALS - BUS_NAME=GTL_WIREOR

GTL COMMON CLOCK INPUT SIGNALS - BUS_NAME=GTL_INPUT

GTL COMMON CLOCK I/O SIGNALS - BUS_NAME=GTL_IO

PROC_1

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

AP0

AP1

BNR

BPRI

BR0

BR1

BR2

BR3

LOCK

ADSTB0

ADSTB1

ADS

REQ0

REQ1

REQ2

REQ3

REQ4

RS0

RS1

RS2

RSP

TRDY

BCLK0

BCLK1

LINT0

LINT1

SLP

STPCLK

RESET

INIT

IERR

MCERR

BINIT

A20M

SMI

FERR

IGNNE

REV. 1.5-EMTS, ZIF SKT

HETERO 1 OF 5

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

DP0

DP1

DP2

DP3

DSTBN0

DSTBN1

DSTBN2

DSTBN3

DSTBP0

DSTBP1

DSTBP2

DSTBP3

HITM

HIT

DEFER

DBI0

DBI1

DBI2

DBI3

DBSY

DRDY

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

Y26

AA27

Y24

AA25

AD27

Y23

AA24

AB26

AB25

AB23

AA22

AA21

AB20

AB22

AB19

AA19

AE26

AC26

AD25

AE25

AC24

AD24

AE23

AC23

AA18

AC20

AC21

AE22

AE20

AD21

AD19

AB17

AB16

AA16

AC17

AE13

AD18

AB15

AD13

AD14

AD11

AC12

AE10

AC11

AE9

AD10

AD8

AC9

AA13

AA14

AC14

AB12

AB13

AA11

AA10

AB10

AC8

AD7

AE7

AC6

AC5

AA8

Y9

AB6

AC18

AE19

AC15

AE17

Y21

Y18

Y15

Y12

Y20

Y17

Y14

Y11

A23

E22

C23

AC27

AD22

AE12

AB9

F18

E18

H_DSTBN0

H_DSTBN1

H_DSTBN2

H_DSTBN3

H_DSTBP0

H_DSTBP1

H_DSTBP2

H_DSTBP3

H_HITM

H_HIT

H_DEFER

H_DBI0

H_DBI1

H_DBI2

H_DBI3

H_DBSY

H_DRDY

H_D0

H_D1

H_D2

H_D3

H_D4

H_D5

H_D6

H_D7

H_D8

H_D9

H_D10

H_D11

H_D12

H_D13

H_D14

H_D15

H_D16

H_D17

H_D18

H_D19

H_D20

H_D21

H_D22

H_D23

H_D24

H_D25

H_D26

H_D27

H_D28

H_D29

H_D30

H_D31

H_D32

H_D33

H_D34

H_D35

H_D36

H_D37

H_D38

H_D39

H_D40

H_D41

H_D42

H_D43

H_D44

H_D45

H_D46

H_D47

H_D48

H_D49

H_D50

H_D51

H_D52

H_D53

H_D54

H_D55

H_D56

H_D57

H_D58

H_D59

H_D60

H_D61

H_D62

H_D63

H_DP0

H_DP1

H_DP2

H_DP3

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

ROOM=LEVEL_TRANSLATION

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,11

6,12

6,12

6,12

6,12

6,12

6,12

6,12

6,12

6,11

6,11

6,11

6,11

6,11

ROOM=PROC_0

ROOM=PROC_0

ROOM=PROC_0

ROOM=PROC_0

ROOM=PROC_0

ROOM=PROC_0

ROOM=PROC_0

ROOM=PROC_0

ROOM=PROC_0

ROOM=PROC_0

ROOM=PROC_1

ROOM=PROC_0

ROOM=PROC_0

ROOM=PROC_0

NACONA GUIDELINES RECOMMEND 47pF HERE

INSTEAD OF 27pF LIKE BOXSTER

A B

ASYNC LINES DRIVEN BY PROCESSORS

THERMTRIP--TERMINATE AT RECEIVER ONLY

FERR--TERMINATE BOTH ENDS OF LINE

VCORE

RB167

56.2-1%

RB185

12

12

IERR--TERMINATED AT RECEIVER ONLY

H_FERR

Put RB424 close to PROC_0

6,10

Put RB411 close to LEVEL TRANSLATION

56.2-1%

ASYNC LINES DRIVEN BY CHIPSET

RB168

1 2

H_A20M

301-1%

RB183

1 2

301-1%

RB189

1 2

301-1%

RB173

1 2

301-1%

RB233

1 2

301-1%

RB156

1 2

301-1%

RB170

1 2

H_IGNNE

H_SMI

SUB*_143MM

H_STPCLK

H_SLP

H_INIT

H_INTR

SUB TO 130 OHM

301-1%

RB191

1 2

301-1%

RB219

1 2

H_NMI

H_PWRGOOD

301-1%

BREQ SIGNALS (NO ON-DIE TERMINATION)

RB164

1 2

49.9-1%

RB192

1 2

49.9-1%

RB153

1 2

49.9-1%

RB155

1 2

H_BREQ1

H_BREQ0

H_BREQ23_PU

49.9-1%

PLACEMENT NOT CRITICAL

6,10

6,10

6,10

6,10

6,10

6,10

6,10

6,10

7,47

BREQ1--TERMINATE AT EITHER END (DOESN'T GO TO CHIPSET)

6

BREQ0--TERMINATE AT END FARTHER FROM CHIPSET

6,11

BREQ23--LOCATION ISN'T CRITICAL

6

WIRED-OR SIGNALS AC TERM AT MIDDLE PROCESSOR

ROOM=PROC_1

CB294

47pF

50V-5%

CB293

47pF

50V-5%

CB292

47pF

50V-5%

CB297

47pF

50V-5%

CB289

47pF

50V-5%

21

21

21

21

21

RB145

1 2

40.2-1%

RB144

1 2

40.2-1%

RB143

1 2

40.2-1%

RB162

1 2

40.2-1%

RB146

1 2

40.2-1%

H_BINIT

H_BNR

H_HIT

H_HITM

H_MCERR

6,11

6,11

6,11

6,11

6,10

TERMINATION

PROCESSORS 1 & 2

COMPUTER

CORPORATION

TITLE

EVERGLADES MB

SCHEM,PLNR,PE1750,533MSI

DWG NO.

DATE

X1004

6/6/2003

AUSTIN,TEXAS

DC

SHEET

REV.

6 OF 51

6-9-2003_13:556EVERGLADES

1

2

3

4

A00-00

Page 7

1

VCORE

21

R322

49.9-1%

R321

100-1%100-1%

SUB TO 84.5 OHM

FOR NOCONA

SUB*_97604

1 2

VCORE

21

R314

49.9-1%

R315

1 2

SUB TO 84.5 OHM

FOR NOCONA

SUB*_97604

1 2

CB371

1 2

CB321

1uF

10V-10%

1uF

CB322

10V-10%

H0_GTLREF01

CB363

2 1

CB35921CB370

0.1uF 16V

H0_GTLREF23

2 1

0.1uF 16V

21

21

CB320

0.1uF 16V

21

CB323

0.1uF 16V

7

0.1uF 16V

7

0.1uF 16V

NC_PROC0HS_3

NC_PROC0HS_4

B D

CHANGED FOR NOCONA SUPPORT:

PIN A4 CONNECTED TO PIN C5

ADDED 50OHM PULL-UP TO PIN A15

CHANGED PIN C1 FROM GND TO 50OHM PULL-DOWN

CHANGED PIN G7 FROM GND TO NO CONNECT

CHANGED PIN AC30 FROM GND TO PU/PD OPTION

CHANGED CAPS ON WIRED-OR AC TERM FROM 27pF TO 47pF

--S HAYES 4/30/02

ITP_TDI_H0

7,10

PLACE THIS RESISTOR NEAR PROC_0

22,35,47

PROC0_HS

P1

1

P2

P3

3

4 5

MP1 MP2

SW PUSHBUTTON

SPDT

NP*

+3.3V_AUX

2

R319

1 2

8.2K-5%

GPI_PROC0_HS_PRES

NC_PROC0HS_5

+3.3V

8.2K-5%

1 2

PERHAPS 3.3V WOULD BE BETTER HERE?

VCORE

RB193

1 2

150-1%

7

CPU_SMBALERT

7,22,35,47

7,22,35,47

RB215

H1_CPU_PRES

H0_CPU_PRES

+3.3V_AUX

RB166

1 2

RB174

1 2

8.2K-5%

8.2K-5%

ROOM=PROC_0 ROOM=PROC_1

CA

+3.3V_AUX

PROC1_HS

P1

1

P3

NC_PROC1HS_3

NC_PROC1HS_4 NC_PROC1HS_5

3

4 5

MP1 MP2

SW PUSHBUTTON

SPDT

NP*

R320

1 2

P2

8.2K-5%

2

GPI_PROC1_HS_PRES

22,35,47

VCORE

21

R324

49.9-1%100-1%

R323

1 2

SUB*_97604

SUB TO 84.5 OHM

FOR NOCONA

VCORE

21

R316

49.9-1%

R317

100-1%

1 2

SUB TO 84.5 OHM

FOR NOCONA

SUB*_97604

1 2

CB367

CB315

1uF

1 2

CB366

2 1

10V-10%

1uF

CB316

10V-10%

H1_GTLREF01

CB351

0.1uF 16V

H1_GTLREF23

2 1

CB318

0.1uF 16V

21

0.1uF 16V

21

0.1uF 16V

21

CB355

CB317

7

0.1uF 16V

21

0.1uF 16V

1

7

VCORE

21

1K-1%

RB172

On DIE term

enabled

2

SUB COMP TO 43.2 PER SERVERWORKS

X01 -- CHANGING BACK TO 49.9 TO IMPROVE MARGIN -swh10/18

Tsensor = 30h/31h

PI-ROM = A0h/A1h

3

VCORE

RB225

1 2

0-5%

SUB TO 0 OHM

RB224

1 2

0-5%

2 1

4.7uH 30mA

SUB*_7H671

4.7uH 30mA

SUB*_7H671

H0_CPU_TYPE

18

LB7

LB4

21

220

RB158

NP

RB218

1 2

49.9-1%

1K-1%

1K-1%

RB217

RB210

1 2

1 2

+80%-20%

22uF 10V

CB408

1 2

1 2

CB401

22uF 10V

1 2

8.2K-5%

22uF 10V

SUB*_3X016

1 2

1 2

CB407

+80%-20%

SUB*_3X016

CB402

+80%-20%

22uF 10V

+80%-20%

SUB*_3X016

12

SUB 22uF CAPS ON BOTTOM

OF BOARD UNDER PROCESSORS

TO LOW-PROFILE VERSION

+3.3V_AUX

RB220

7,22,35,47

21

RB154

49.9-1%

CB386

2 1

0.1uF 16V

0.1uF 16V

2 1

SUB*_3X016

4 4

6,7,47

7,21,37,46

7,21,37,46

CB385

4,7,12,22

H0_ODTEN

H0_PROCHOT

10

H_PWRGOOD

H0_CPU_PRES

H0_THERMTRIP

10

H0_COMP0

H0_COMP1

7

H0_SM_EP_A012

H0_SM_TS_A01

GPO_SMB_WP

7

H_BPM02

7,10

H_BPM13

7,10

H_BPM4

7,10

H_BPM5

7,10

ITP_TCK

7,10

ITP_TDI_H0

7,10

ITP_TDO_H0

10

ITP_TMS

7,10

ITP_TRST

7,10

9,47

9,47

9,47

9,47

9,47

7

7

7

7

7

7

7

7

7

H0_THERM_D+

37

H0_THERM_D-

37

GPI_SYN_SEL100

CPU_SMBALERT

ENV_SEG0_SCL

ENV_SEG0_SDA

H0_VID0

H0_VID1

H0_VID2

H0_VID3

H0_VID4

V_VID_H0_VCCA

NC_H0_VCCSENSE

H0_VSSA

NC_H0_VSSSENSE

V_VID_H0_VPLL

H0_GTLREF01

H0_GTLREF23

H0_TESTHI0

H0_TESTHI1

H0_TESTHI2

H0_TESTHI3

H0_TESTHI4

H0_TESTHI5

H0_TESTHI6

NC_H0_RSVD77

B5

B25

AB7

A3

F26

AD16

E16

+3.3V

AE29

AE28

AD28

AC28

AC29

AA29

AB29

AB28

AA28

Y29

AD29

F6

F8

E7

F5

E8

E4

E24

C24

E25

A25

F24

F3

E3

D3

C3

B3

AB4

B27

AA5

D26

AD4

W23

W9

F23

F9

W6

W7

W8

Y6

AA7

AD5

AE5

Y27

Y28

AE4

AA3

AB3

PRESTONIA/NOCONA 604 PROCESSOR

PROC_0

ODTEN

PROCHOT

PWRGOOD

SKTOCC

THRMTRIP

COMP0

COMP1

SM_VCC_AE29

SM_VCC_AE28

SM_ALERT

SM_CLK

SM_DAT

SM_EP_A0

SM_EP_A1

SM_EP_A2

SM_TS1_A0

SM_TS1_A1

SM_WP

BPM0

BPM1

BPM2

BPM3

BPM4

BPM5

TCK

TDI

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

VCCA

VCCSENSE

VSSA

VSSSENSE

VCCIOPLL

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

THRM_ANODE

THRM_CATH

SMB_PRT

BSEL0

BSEL1

REV. 1.5-EMTS, ZIF SKT

VCCVID/RSVD_A4

FORCEPR/RSVD_A15

VCCVIDLB/RSVD_C5

HETERO 2 OF 5

RSVD_A1

RSVD_A16

RSVD_A26

RSVD_B1

RSVD_D25

RSVD_W3

RSVD_Y3

RSVD_AC1

RSVD_AD1

RSVD_AE15

RSVD_AE16

A1

A4

A15

A16

A26

B1

C5

D25

W3

Y3

AC1

AD1

AE15

AE16

VCORE

NC_H0_RSVD1

H0_VCCVIDLOOP

H0_FORCEPR

NC_H0_RSVD4

NC_H0_RSVD5

NC_H0_RSVD8

NC_H0_RSVD17

NC_H0_RSVD89

NC_H0_RSVD66

NC_H0_RSVD80

NC_H0_RSVD83

NC_H0_RSVD87

NC_H0_RSVD88

RB200

12

SUB*_6610C

1K-1%

RB197

12

SUB*_6610C

1K-1%

RB194

12

SUB*_6610C

1K-1%

RB205

12

SUB*_6610C

1K-1%

RB206

12

SUB*_6610C

1K-1%

RB231

12

SUB*_6610C

1K-1%

RB232

12

SUB*_6610C

1K-1%

H0_TESTHI0

H0_TESTHI1

H0_TESTHI2

H0_TESTHI3

H0_TESTHI4

H0_TESTHI5

H0_TESTHI6

7

7

7

7

7

7

7

VCORE

21

RB147

49.9-1%

X01 -- CHANGING BACK TO 49.9 TO IMPROVE MARGIN -swh10/18

SUB COMP TO 43.2 PER SERVERWORKS

Tsensor = 32h/33h

PI-ROM = A2h/A3h

VCORE

2 1

4.7uH 30mA

SUB*_7H671

4.7uH 30mA

SUB*_7H671

H1_CPU_TYPE

18

LB5

LB6

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

RB222

1 2

0-5%

RB223

1 2

0-5%

A B

VCORE

21

NP

RB165

On DIE term disabled

1K-1% 1K-1%

RB175

1 2

RB208

12

RB207

12

CB405

1 2

+80%-20%

22uF 10V

8.2K-5%

21

RB221

+80%-20%

22uF 10V

SUB*_3X016

CB393

1 2

1 2

CB406

22uF 10V

SUB*_3X016

49.9-1%

+80%-20%

SUB*_3X016

+3.3V

100-1% 1K-1%

+80%-20%

22uF 10V

SUB*_3X016

1 2

CB394

12

SUB 22uF CAPS ON BOTTOM

OF BOARD UNDER PROCESSORS

TO LOW-PROFILE VERSION

+3.3V_AUX

RB230

1 2

7,22,35,47

R318

1 2

49.9-1%

CB381

2 1

0.1uF 16V

0.1uF 16V

2 1

CB382

4,7,12,22

10

6,7,47

10

7,21,37,46

7,21,37,46

H1_SM_PR_A1

H1_SM_PR_A2

H1_SM_TS_A0

7

7,10

7,10

7,10

7,10

7,10

10

10

7,10

7,10

7

7

7

7

7

7

7

7

7

37

37

H1_ODTEN

H1_PROCHOT

H_PWRGOOD

H1_CPU_PRES

H1_THERMTRIP

H1_COMP0

H1_COMP1

7

NC_H1_SM_TS_A1

H_BPM02

H_BPM13

H_BPM4

H_BPM5

ITP_TCK

ITP_TDI_H1

ITP_TDO_H1

ITP_TMS

ITP_TRST

GPI_SYN_SEL100

NC_H1_RSVD77

+3.3V

CPU_SMBALERT

ENV_SEG0_SCL

ENV_SEG0_SDA

H1_SM_EP_A0

GPO_SMB_WP

H1_VID0

9,47

H1_VID1

9,47

H1_VID2

9,47

H1_VID3

9,47

H1_VID4

9,47

V_VID_H1_VCCA

NC_H1_VCCSENSE

H1_VSSA

NC_H1_VSSSENSE

V_VID_H1_VPLL

H1_GTLREF01

H1_GTLREF23

H1_TESTHI0

H1_TESTHI1

H1_TESTHI2

H1_TESTHI3

H1_TESTHI4

H1_TESTHI5

H1_TESTHI6

H1_THERM_D+

H1_THERM_D-

B5

B25

AB7

A3

F26

AD16

E16

AE29

AE28

AD28

AC28

AC29

AA29

AB29

AB28

AA28

Y29

AD29

F6

F8

E7

F5

E8

E4

E24

C24

E25

A25

F24

F3

E3

D3

C3

B3

AB4

B27

AA5

D26

AD4

W23

W9

F23

F9

W6

W7

W8

Y6

AA7

AD5

AE5

Y27

Y28

AE4

AA3

AB3

PRESTONIA/NOCONA 604 PROCESSOR

PROC_1

ODTEN

PROCHOT

PWRGOOD

SKTOCC

THRMTRIP

COMP0

COMP1

SM_VCC_AE29

SM_VCC_AE28

SM_ALERT

SM_CLK

SM_DAT

SM_EP_A0

SM_EP_A1

SM_EP_A2

SM_TS1_A0

SM_TS1_A1

SM_WP

BPM0

BPM1

BPM2

BPM3

BPM4

BPM5

TCK

TDI

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

VCCA

VCCSENSE

VSSA

VSSSENSE

VCCIOPLL

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

THRM_ANODE

THRM_CATH

SMB_PRT

BSEL0

BSEL1

REV. 1.5-EMTS, ZIF SKT

VCCVID/RSVD_A4

FORCEPR/RSVD_A15

VCCVIDLB/RSVD_C5

HETERO 2 OF 5

RSVD_AE15

RSVD_AE16

RSVD_A1

RSVD_A16

RSVD_A26

RSVD_B1

RSVD_D25

RSVD_W3

RSVD_Y3

RSVD_AC1

RSVD_AD1

A1

A4

A15

A16

A26

B1

C5

D25

W3

Y3

AC1

AD1

AE15

AE16

VCORE

NC_H1_RSVD1

H1_VCCVIDLOOP

H1_FORCEPR

NC_H1_RSVD4

NC_H1_RSVD5

NC_H1_RSVD8

NC_H1_RSVD17

NC_H1_RSVD89

NC_H1_RSVD66

NC_H1_RSVD80

NC_H1_RSVD83

NC_H1_RSVD87

NC_H1_RSVD88

RB198

12

H1_TESTHI0

SUB*_6610C

1K-1%

RB196

12

H1_TESTHI1

SUB*_6610C

1K-1%

RB195

12

H1_TESTHI2

SUB*_6610C

1K-1%

RB203

12

H1_TESTHI3

SUB*_6610C

1K-1%

RB209

12

H1_TESTHI4

SUB*_6610C

1K-1%

RB216

12

H1_TESTHI5

SUB*_6610C

1K-1%

RB213

12

H1_TESTHI6

SUB*_6610C

1K-1%

VCORE

21

RB163

49.9-1%

7

7

7

7

7

7

7

PROCESSORS 1 & 2

CPU-- Misc. & RSVD

COMPUTER

CORPORATION

TITLE

EVERGLADES MB

AUSTIN,TEXAS

SCHEM,PLNR,PE1750,533MSI

DWG NO.

DATE

DC

X1004

6/6/2003

SHEET

7 OF 51

REV.

6-9-2003_13:557EVERGLADES

A00-00

2

3

Page 8

B D

ROOM=PROC_0

ROOM=PROC_1

L6

L8

L24

L26

L28

L30

M1

M3

M5

M7

M9

M23

M25

M27

M29

M31

N1

N3

N5

N7

N9

N23

N25

N27

N29

N31

P2

P4

P6

P8

P24

P26

P28

P30

R1

R3

R5

R7

R9

R23

R25

R27

R29

R31

T2

T4

T6

T8

T24

T26

T28

T30

U1

U3

U5

U7

U9

U23

U25

U27

U29

U31

V2

V4

V6

V8

V24

V26

V28

V30

W1

W25

W27

W29

W31

Y2

Y10

Y16

Y22

Y30

Y19

Y25

Y31

AA2

AA9

AA15

AA17

AA23

AA30

AB1

AB5

AB11

AB21

AB27

AB31

AC2

AC7

AC13

AC19

AC25

AC30

AD3

AD9

AD15

AD17

AD23

AD31

AE2

AE11

AE21

AE27

VCOREVCORE

PROC_1

VSS_A5

VSS_A11

VSS_A21

VSS_A27

VSS_A29

VSS_A31

VSS_B2

VSS_B9

VSS_B15

VSS_B17

VSS_B23

VSS_B28

VSS_B30

VSS/TESTLOW

VSS_C7

VSS_C13

VSS_C19

VSS_C25

VSS_C29

VSS_C31

VSS_D2

VSS_D5

VSS_D11

VSS_D21

VSS_D27

VSS_D28

VSS_D30

VSS_E1

VSS_E9

VSS_E15

VSS_E17

VSS_E23

VSS_E29

VSS_E31

VSS_F2

VSS_F7

VSS_F13

VSS_F19

VSS_F25

VSS_F28

VSS_F30

VSS_G1

VSS_G3

VSS_G5

VSS/BOOTSEL

VSS_G9

VSS_G25

VSS_G27

VSS_G29

VSS_G31

VSS_H2

VSS_H4

VSS_H6

VSS_H8

VSS_H24

VSS_H26

VSS_H28

VSS_H30

VSS_J1

VSS_J3

VSS_J5

VSS_J7

VSS_J9

VSS_J23

VSS_J25

VSS_J27

VSS_J29

VSS_J31

VSS_K2

VSS_K4

VSS_K6

VSS_K8

VSS_K24

VSS_K26

VSS_K28

VSS_K30

VSS_L1

VSS_L3

VSS_L5

REV. 1.5-EMTS, ZIF SKT

HETERO 4 OF 5

VSS_L7

VSS_L9

VSS_L23

VSS_L25

VSS_L27

VSS_L29

VSS_L31

VSS_M2

VSS_M4

VSS_M6

VSS_M8

VSS_M24

VSS_M26

VSS_M28

VSS_M30

VSS_N2

VSS_N4

VSS_N6

VSS_N8

VSS_N24

VSS_N26

VSS_N28

VSS_N30

VSS_P1

VSS_P3

VSS_P5

VSS_P7

VSS_P9

VSS_P23

VSS_P25

VSS_P27

VSS_P29

VSS_P31

VSS_R2

VSS_R4

VSS_R6

VSS_R8

VSS_R24

VSS_R26

VSS_R28

VSS_R30

VSS_T1

VSS_T3

VSS_T5

VSS_T7

VSS_T9

VSS_T23

VSS_T25

VSS_T27

VSS_T29

VSS_T31

VSS_U2

VSS_U4

VSS_U6

VSS_U8

VSS_U24

VSS_U26

VSS_U28

VSS_U30

VSS_V1

VSS_V3

VSS_V5

VSS_V7

VSS_V9

VSS_V23

VSS_V25

VSS_V27

VSS_V29

VSS_V31

VSS_W2

VSS_W4

VSS_W24

VSS_W26

VSS_W28

VSS_W30

VSS_Y1

VSS_Y5

VSS_Y7

VSS_Y13

L7

L9

L23

L25

L27

L29

L31

M2

M4

M6

M8

M24

M26

M28

M30

N2

N4

N6

N8

N24

N26

N28

N30

P1

P3

P5

P7

P9

P23

P25

P27

P29

P31

R2

R4

R6

R8

R24

R26

R28

R30

T1

T3

T5

T7

T9

T23

T25

T27

T29

T31

U2

U4

U6

U8

U24

U26

U28

U30

V1

V3

V5

V7

V9

V23

V25

V27

V29

V31

W2

W4

W24

W26

W28

W30

Y1

Y5

Y7

Y13

VCORE

+80%-20%

22uF 10V

+80%-20%

22uF 10V

CB291

1 2

SUB*_3X016

VCORE

+80%-20%

22uF 10V

CB365

1 2

SUB*_3X016

SUB 22uF CAPS ON BOTTOM

OF BOARD UNDER PROCESSORS

TO LOW-PROFILE VERSION 3X016

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL COMPUTER CORP. AUSTIN, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL COMPUTER CORP. EXCEPT

AS AUTHORIZED BY DELL COMPUTER CORP., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL COMPUTER CORP. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL COMPUTER CORPORATION.

1 2

C373

+80%-20%

22uF 10V

CB348

1 2

SUB*_3X016

+80%-20%

22uF 10V

SUB*_3X016

+80%-20%

22uF 10V

SUB*_3X016

NC_H1_BS

VCORE

RB226

H1_SLEWCTL

RB227

A5

A11

A21

A27

A29

A31

B2

B9

B15

B17

B23

B28

B30

C1

H1_C1

21

RB176

21

1 2

C7

C13

C19

C25

C29

49.9-1%

C31

D2

D5

D11

D21

D27

D28

D30

E1

E9

E15

E17

E23

E29

E31

F2

F7

F13

F19

F25

F28

F30

G1

G3

G5

G7

G9

G25

G27

G29

G31

H2

H4

H6

H8

H24

H26

H28

H30

J1

J3

J5

J7

J9

J23

J25

J27

J29

J31

K2

K4

K6

K8

K24

K26

K28

K30

L1

L3

L5

PRESTONIA/NOCONA 604 PROCESSOR

49.9-1%0-5%

NP*

VCOREVCORE

PROC_0

A2

VCC_A2

A8

VCC_A8

A14

VCC_A14

A18

VCC_A18

A24

VCC_A24

A28

VCC_A28

A30

VCC_A30

1

2

3

B4

VCC_B4

B6

VCC_B6

B12

VCC_B12

B20

VCC_B20

B26

VCC_B26

B29

VCC_B29

B31

VCC_B31

C2

VCC_C2

C4

VCC_C4

C10

VCC_C10

C16

VCC_C16

C22

VCC_C22

C28

VCC_C28

C30

VCC_C30

D1

VCC_D1

D8

VCC_D8

D14

VCC_D14

D18

VCC_D18

D24

VCC_D24

D29

VCC_D29

D31

VCC_D31

E2

VCC_E2

E6

VCC_E6

E12

VCC_E12

E20

VCC_E20

E26

VCC_E26

E28

VCC_E28

E30

VCC_E30

F1

VCC_F1

F4

VCC_F4

F10

VCC_F10

F16

VCC_F16

F22

VCC_F22

F29

VCC_F29

F31

VCC_F31

G2

VCC_G2

G4

VCC_G4

G6

VCC_G6

G8

VCC_G8

G24

VCC_G24

G26

VCC_G26

G28

VCC_G28

G30

VCC_G30

H1

VCC_H1

H3

VCC_H3

H5

VCC_H5

H7

VCC_H7

H9

VCC_H9

H23

VCC_H23

H25

VCC_H25

H27

VCC_H27

H29

VCC_H29

H31

VCC_H31

J2

VCC_J2

J4

VCC_J4

J6

VCC_J6

J8

VCC_J8

J24

VCC_J24

J26

VCC_J26

J28

VCC_J28

J30

VCC_J30

K1

VCC_K1

K3

VCC_K3

K5

VCC_K5

K7

VCC_K7

K9

VCC_K9

K23

VCC_K23

K25

VCC_K25

K27

VCC_K27

K29

VCC_K29

K31

VCC_K31

L2

VCC_L2

L4

VCC_L4

PRESTONIA/NOCONA 604 PROCESSOR

REV. 1.5-EMTS, ZIF SKT

VCORE

HETERO 3 OF 5

PROC_0

AA1

VCC_AA1

AA4

VCC_AA4

AA6

VCC_AA6

AA12

VCC_AA12

AA20

VCC_AA20

AA26

VCC_AA26

AA31

VCC_AA31

AB2

VCC_AB2

AB8

VCC_AB8

AB14

VCC_AB14

AB18

VCC_AB18

AB24

VCC_AB24

AB30

VCC_AB30

SCHEM,PLNR,PE1750,533MSI

AC3

VCC_AC3

AC4

VCC_AC4

AC10

VCC_AC10

AC16

VCC_AC16

AC22

VCC_AC22

AC31

VCC_AC31

AD2

VCC_AD2

AD6

4 4

AD12

AD20

AD26

AD30

AE3

AE8

AE14

AE18

AE24

PRESTONIA/NOCONA 604 PROCESSOR

SLEWCTRL/VSS

VCC_AD6

VCC_AD12

VCC_AD20

VCC_AD26

VCC_AD30

VCC_AE3

VCC_AE8

VCC_AE14

VCC_AE18

VCC_AE24

REV. 1.5-EMTS, ZIF SKT

HETERO 5 OF 5

ROOM=PROC_0

VCC_L6

VCC_L8

VCC_L24

VCC_L26

VCC_L28

VCC_L30

VCC_M1

VCC_M3

VCC_M5

VCC_M7

VCC_M9

VCC_M23

VCC_M25

VCC_M27

VCC_M29

VCC_M31

VCC_N1

VCC_N3

VCC_N5

VCC_N7

VCC_N9

VCC_N23

VCC_N25

VCC_N27

VCC_N29

VCC_N31

VCC_P2

VCC_P4

VCC_P6

VCC_P8

VCC_P24

VCC_P26

VCC_P28

VCC_P30

VCC_R1

VCC_R3

VCC_R5

VCC_R7

VCC_R9

VCC_R23

VCC_R25

VCC_R27

VCC_R29

VCC_R31

VCC_T2

VCC_T4

VCC_T6

VCC_T8

VCC_T24

VCC_T26

VCC_T28

VCC_T30

VCC_U1

VCC_U3

VCC_U5

VCC_U7

VCC_U9

VCC_U23

VCC_U25

VCC_U27

VCC_U29

VCC_U31

VCC_V2

VCC_V4

VCC_V6

VCC_V8

VCC_V24

VCC_V26

VCC_V28

VCC_V30

VCC_W1

VCC_W25

VCC_W27

VCC_W29

VCC_W31

VCC_Y2

VCC_Y10

VCC_Y16

VCC_Y22

VCC_Y30

VSS_Y19

VSS_Y25

VSS_Y31

VSS_AA2

VSS_AA9

VSS_AA15

VSS_AA17

VSS_AA23

VSS_AA30

VSS_AB1

VSS_AB5

VSS_AB11

VSS_AB21

VSS_AB27

VSS_AB31

VSS_AC2

VSS_AC7

VSS_AC13

VSS_AC19

VSS_AC25

VSS_AD3

VSS_AD9

VSS_AD15

VSS_AD17

VSS_AD23

VSS_AD31

VSS_AE2

VSS_AE11

VSS_AE21

VSS_AE27

L6

L8

L24

L26

L28

L30

M1

M3

M5

M7

M9

M23

M25

M27

M29

M31

N1

N3

N5

N7

N9

N23

N25

N27

N29

N31

P2

P4

P6

P8

P24

P26

P28

P30

R1

R3

R5

R7

R9

R23

R25

R27

R29

R31

T2

T4

T6

T8

T24

T26

T28

T30

U1

U3

U5

U7

U9

U23

U25

U27

U29

U31

V2

V4

V6

V8

V24

V26

V28

V30

W1

W25

W27

W29

W31

Y2

Y10

Y16

Y22

Y30

Y19

Y25

Y31

AA2

AA9

AA15

AA17

AA23

AA30

AB1

AB5

AB11

AB21

AB27

AB31

AC2

AC7

AC13

AC19

AC25

AC30

AD3

AD9

AD15

AD17

AD23

AD31

AE2

AE11

AE21

AE27

A5

VSS_A5

A11

VSS_A11

A21

VSS_A21

A27

VSS_A27

A29

VSS_A29

A31

VSS_A31

B2

VSS_B2

B9

VSS_B9

B15

VSS_B15

B17

VSS_B17

B23

VSS_B23

B28

VSS_B28

B30

VSS_B30

C1

H0_C1

21

RB184

49.9-1%

NC_H0_BS

H0_SLEWCTL

VSS/TESTLOW

C7

VSS_C7

C13

VSS_C13

C19

VSS_C19

C25

VSS_C25

C29

VSS_C29

C31

VSS_C31

D2

VSS_D2

D5

VSS_D5

D11

VSS_D11

D21

VSS_D21

D27

VSS_D27

D28

VSS_D28

D30

VSS_D30

E1

VSS_E1

E9

VSS_E9

E15

VSS_E15

E17

VSS_E17

E23

VSS_E23

E29

VSS_E29

E31

VSS_E31

F2

VSS_F2

F7

VSS_F7

F13

VSS_F13

F19

VSS_F19

F25

VSS_F25

F28

VSS_F28

F30

VSS_F30

G1

VSS_G1

G3

VSS_G3

G5

VSS_G5

G7

VSS/BOOTSEL

G9

VSS_G9

G25

VSS_G25

G27

VSS_G27

G29

VSS_G29

G31

VSS_G31

H2

VSS_H2

H4

VSS_H4

H6

VSS_H6

H8

VSS_H8

H24

VSS_H24

H26

VSS_H26

H28

VSS_H28

H30

VSS_H30

J1

VSS_J1

J3

VSS_J3

J5

VSS_J5

J7

VSS_J7

J9

VSS_J9

J23

VSS_J23

J25

VSS_J25

J27

VSS_J27

J29

VSS_J29

J31

VSS_J31

K2

VSS_K2

K4

VSS_K4

K6

VSS_K6

K8

VSS_K8

K24

VSS_K24

K26

VSS_K26

K28

VSS_K28

K30

VSS_K30

L1

VSS_L1

L3

VSS_L3

L5

VSS_L5

PRESTONIA/NOCONA 604 PROCESSOR

REV. 1.5-EMTS, ZIF SKT

HETERO 4 OF 5

VCORE

21

RB229

49.9-1%0-5%

NP*

RB228

1 2

PROC_0

VSS_L7

VSS_L9

VSS_L23

VSS_L25

VSS_L27

VSS_L29

VSS_L31

VSS_M2

VSS_M4

VSS_M6

VSS_M8

VSS_M24

VSS_M26

VSS_M28

VSS_M30

VSS_N2

VSS_N4

VSS_N6

VSS_N8

VSS_N24

VSS_N26

VSS_N28

VSS_N30

VSS_P1

VSS_P3

VSS_P5

VSS_P7

VSS_P9

VSS_P23

VSS_P25

VSS_P27

VSS_P29

VSS_P31

VSS_R2

VSS_R4

VSS_R6

VSS_R8

VSS_R24

VSS_R26

VSS_R28

VSS_R30

VSS_T1

VSS_T3

VSS_T5

VSS_T7

VSS_T9

VSS_T23

VSS_T25

VSS_T27

VSS_T29

VSS_T31

VSS_U2