MSI MS-7928 Schematics rev1.0

1

smd.db-x7.ru

Cover Sheet

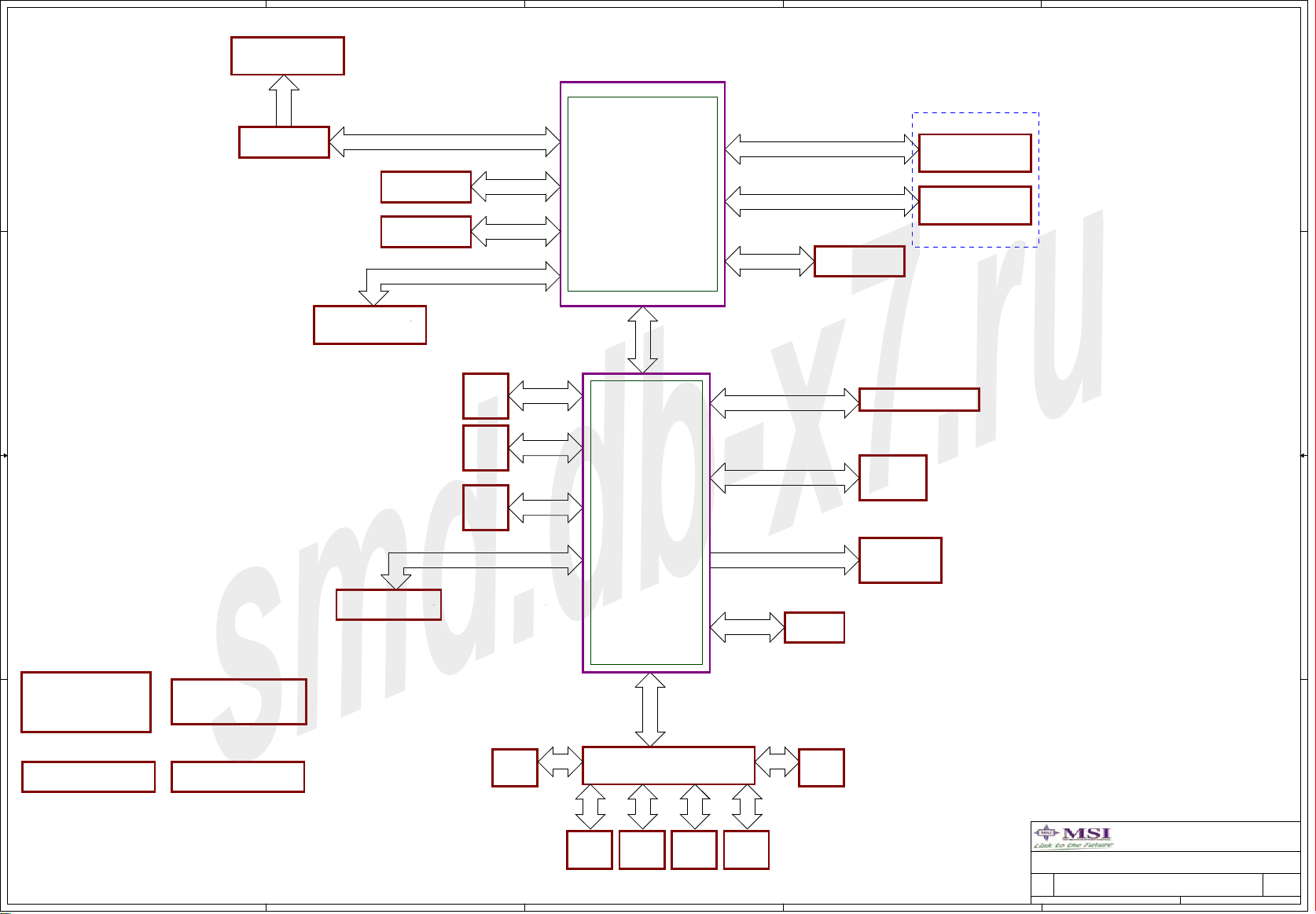

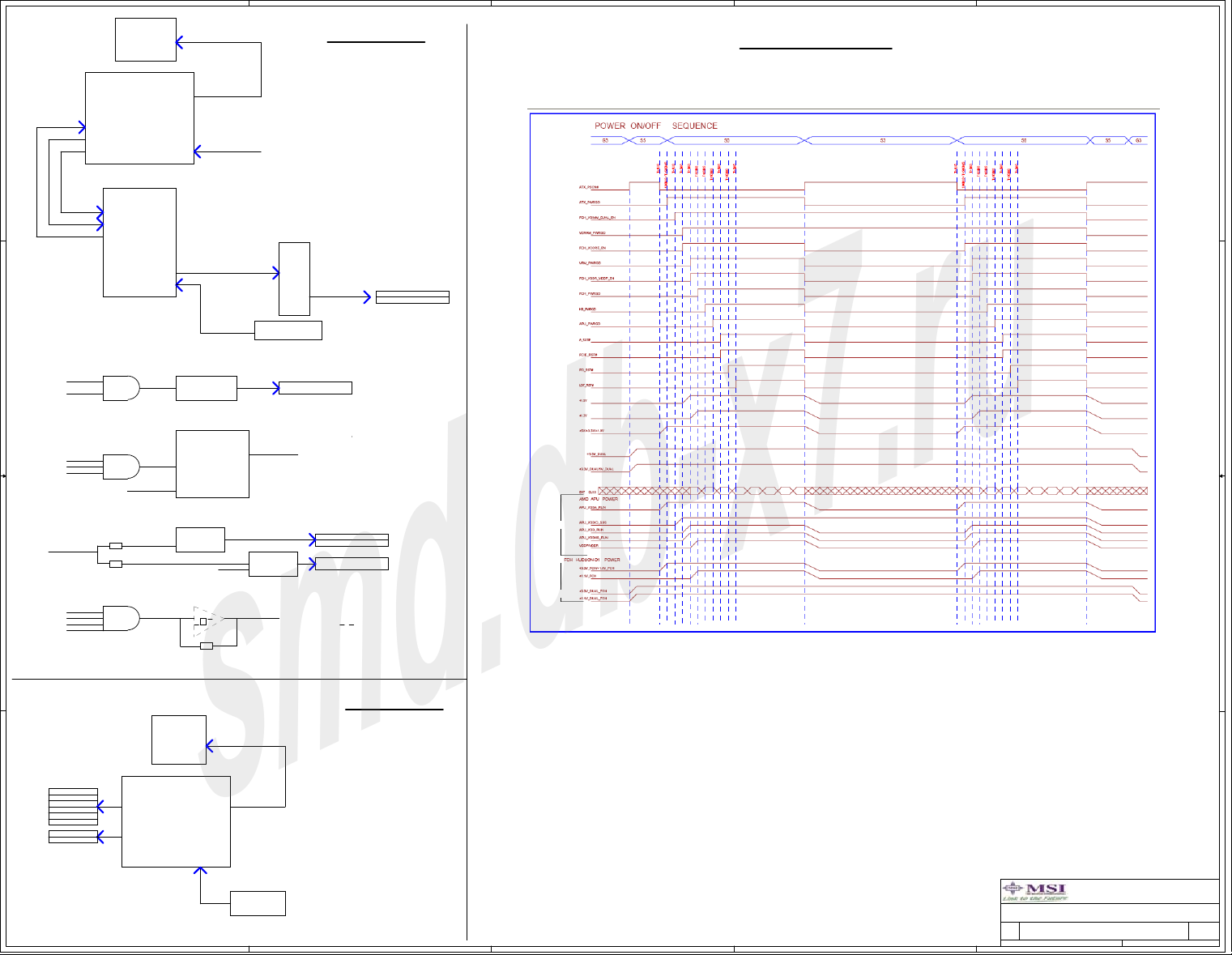

BLOCK DIAGRAM

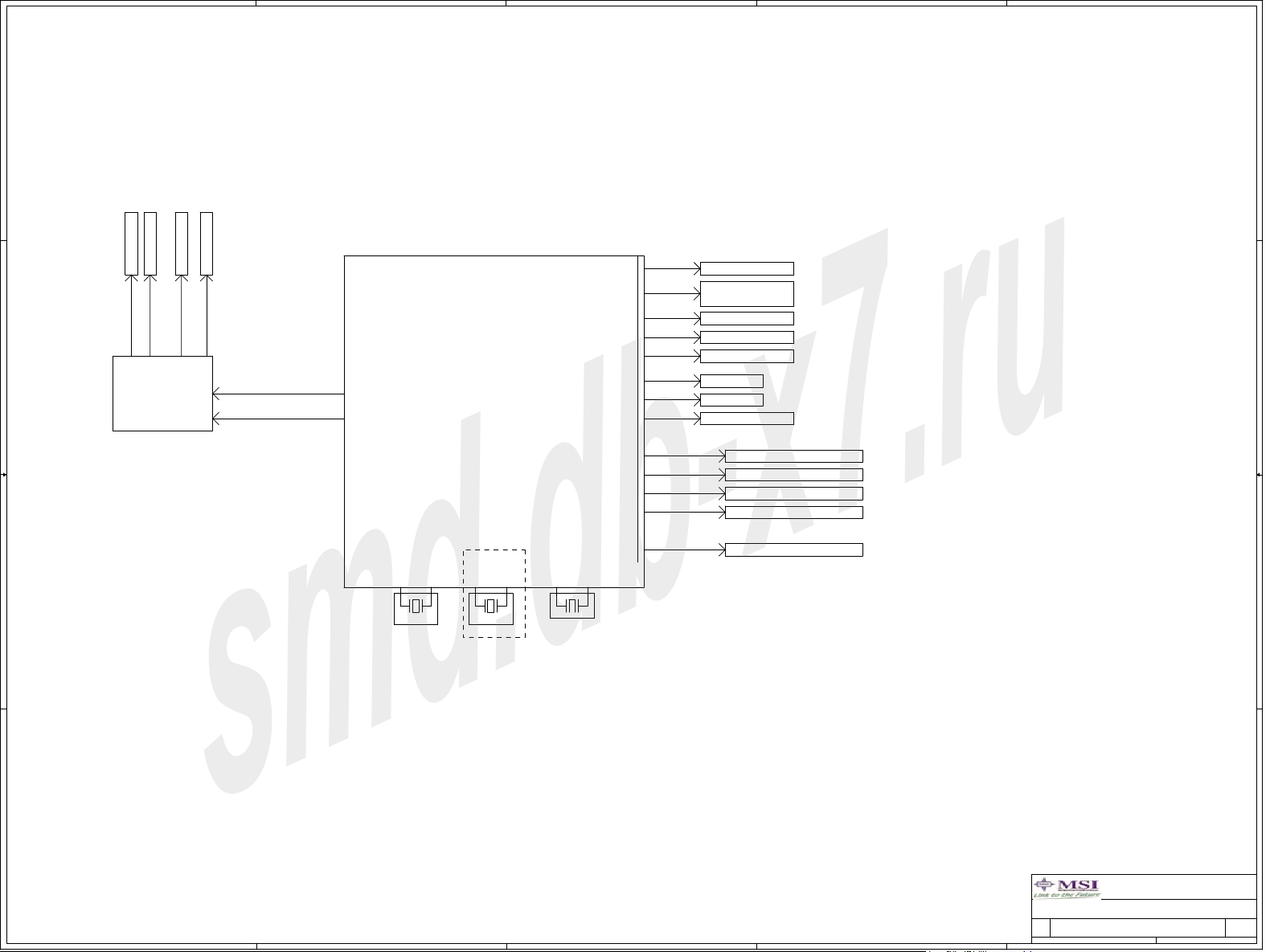

Clock Distribution

PWRGD&RESET Map

GPIO/MSIC TABLE

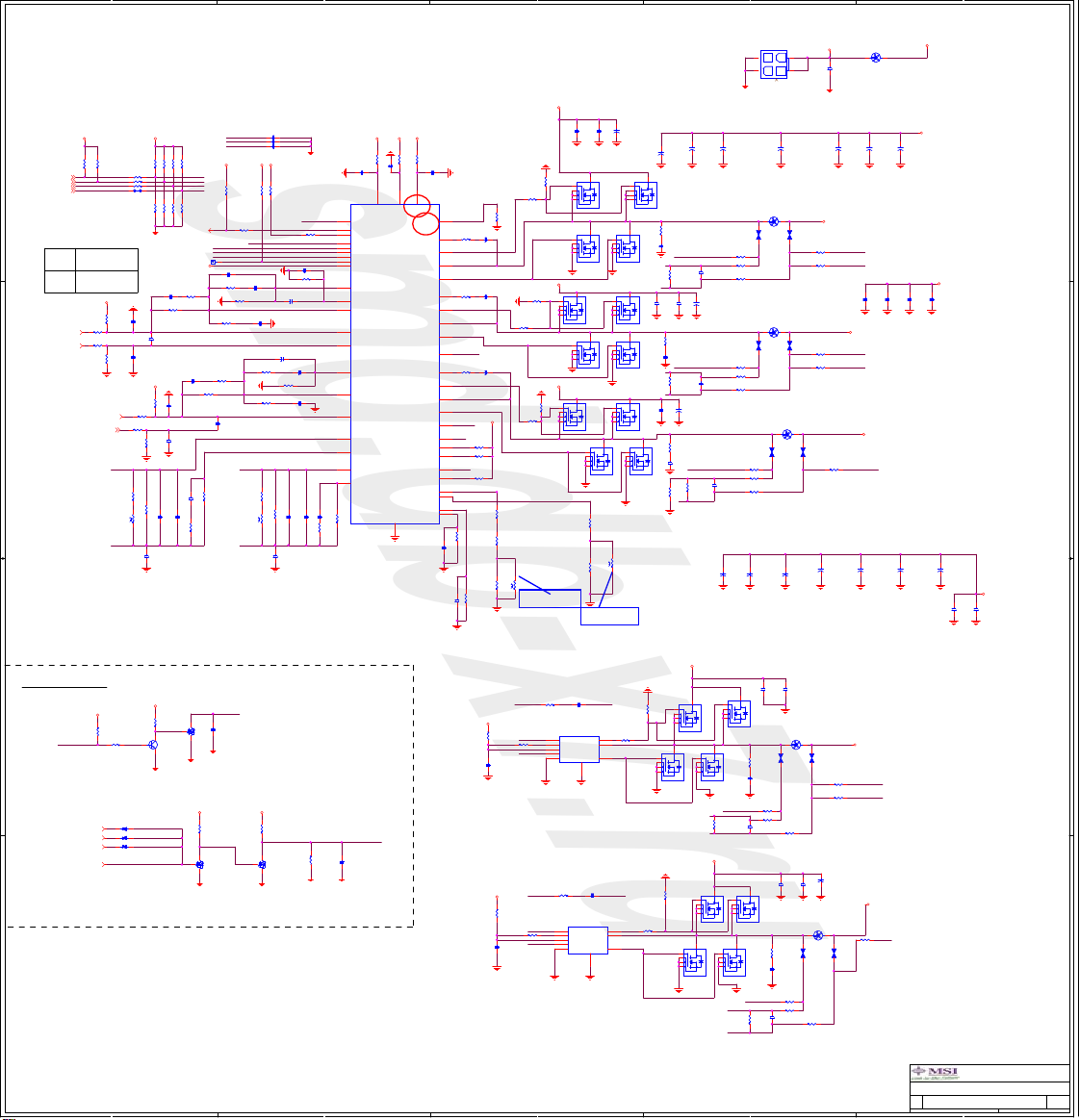

VRM Intersil 6277/6377 3+1 PHASE

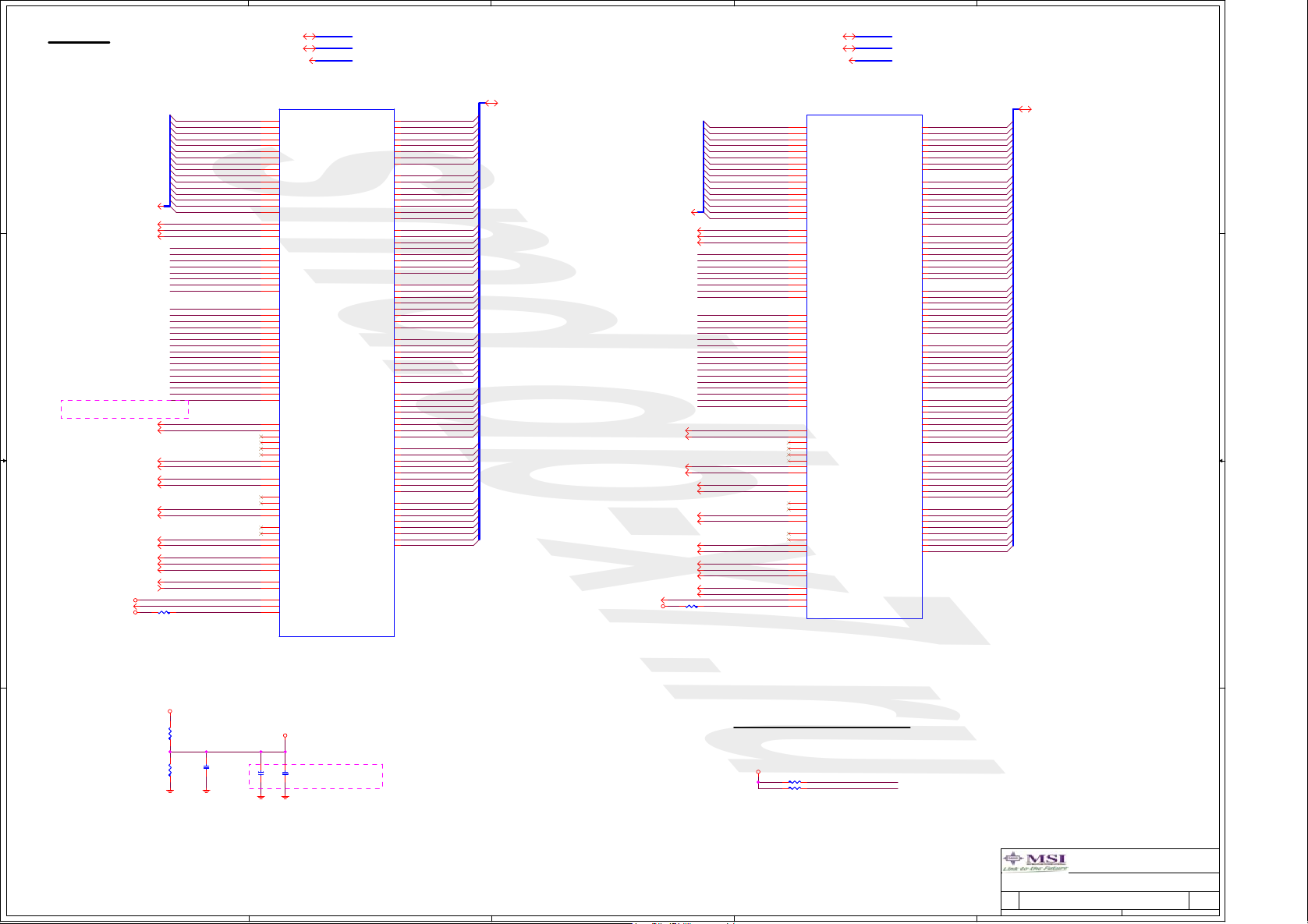

AMD FM2

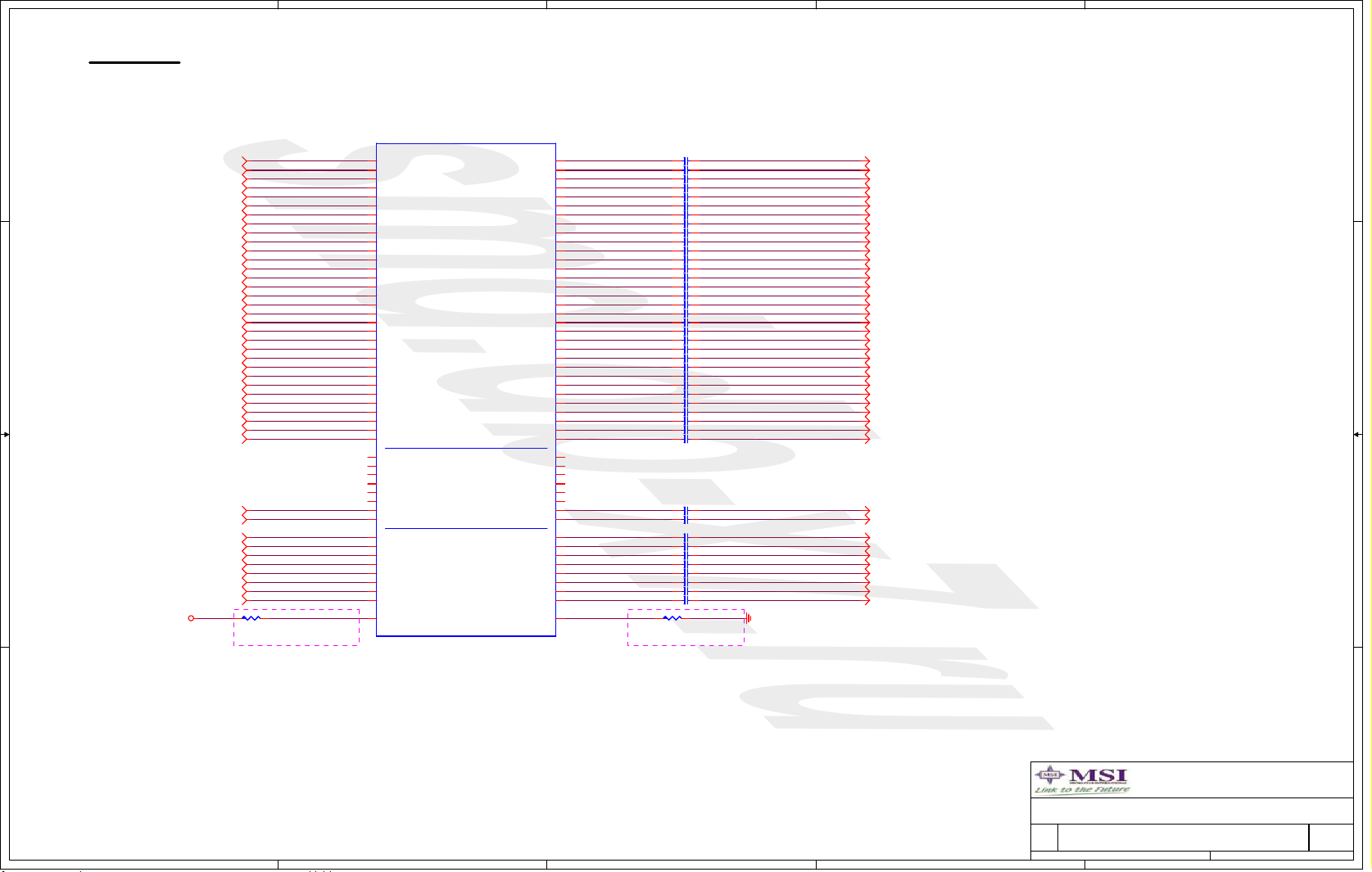

DDR3 DIMM

DDR REF POWER AND CAPS

AMD BOLTON D3

Display CONN

DVI_D CONN

VGA CONN.

PCIE X16 SLOT

PCIE X1 SLOTs

A A

PCI SLOT

LAN-RTL8111E

Azalia CODEC ALC662

USB 2.0 CONN.

USB 3.0 CONN.

USB POWER/DISCHARGE

SATA/ FAN

SUPER I/O IT8728F

ACPI UPI & SYS POWER

FCH CORE & DDR POWER

ATX/F_Panel/EMI/LED

Auto BOM manual

History

1

2

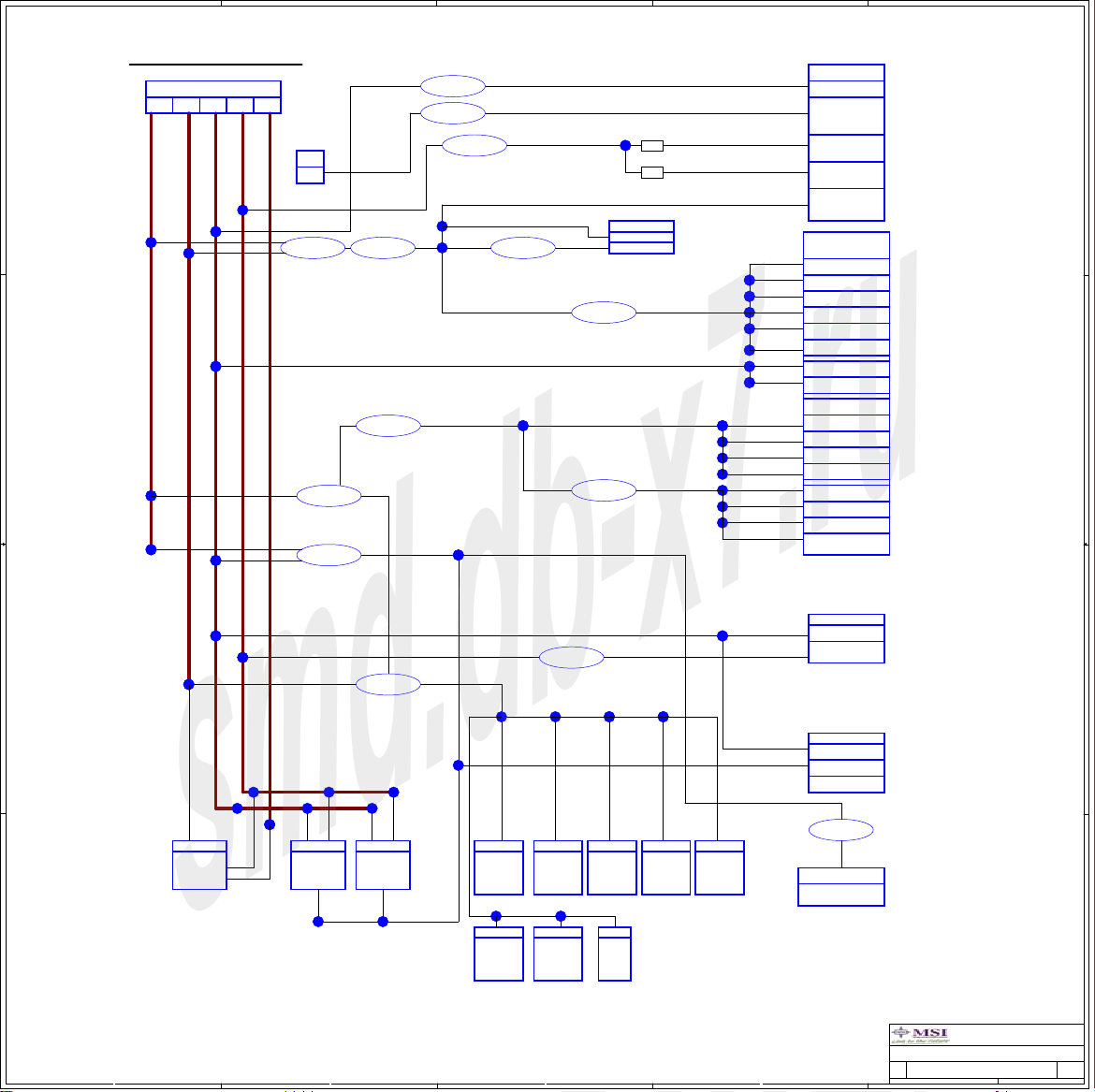

3 Power Deliver Chart

4

5

6

7

8 ~ 11

12

13

14~18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

(MS-7928 Ver:1.0)

CPU:

AMD FM2+ colay FM2(Trinity/Richland/Kaveri (auto detect))

System Chipset:

AMD - BOLTON D3

On Board Chipset:

CLOCK GEN --FCH internal clock gen

LPC Super I/O --IT8728F

LAN-Realtek 8111E

Azalia CODEC - Realtek ALC662

Main Memory:

DDR III * 2 (max 16G)

Expansion Slots:

PCI Express X16 Slot * 1

PCI Express X1 Slot * 2

PCI Slot *1

VRM

Controller - Intersil 62773+6208/4+2 Phase

mATX: 244mm * 244mm

Kaveri

Title

Title

Title

COVER SHEET

COVER SHEET

COVER SHEET

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

1

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Kaveri 1.0

Kaveri 1.0

Kaveri 1.0

136Saturday, January 18, 2014

136Saturday, January 18, 2014

136Saturday, January 18, 2014

of

of

5

smd.db-x7.ru

4

3

2

1

VGA CONNECTOR

D D

Bolton D3

C C

VGA

21

16

RTL8111E-VC

VGA MAIN LINK

DVI-D CON

DP CON

PCIE INTERFACE

25

Kaveri BLOCK DIAGRAM

DP 0

DP1

20

DP2

19

USB

2.0

Rear

USB

3.0

Front

USB

3.0

USB 2.0

27

USB 3.0

28

USB 3.0

28

FM2+

8~11

UMI

Bolton D3

DDRIII 1333~1866

DDRIII 1333~1866

PCIE x16

AZALIA

SERIAL ATA 3.0

CHA

CHB

PCIE GFX x16

ALC662

i-SATA 4

22

UNBUFFERED

DDRIII DIMM1

UNBUFFERED

DDRIII DIMM2

30

12

12

26

B B

PCIE x1 SLOT1,2

ACPI CONTROLLER

32

DDR3 DRAM POWER

FCH CORE POWER

A A

5

33

CPU CORE POWER

NB CORE POWER

Intersil ISL62773

Intersil ISL6208

ATX CON

7

34

PCIE INTERFACE

23

FAN

30

PS2

31

4

14~18

SUPER I/O ITE8728F

SERIAL

PORT1

SERIAL

PORT2

31

3

31

SPI ROM 32Mb

2

16

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

Kaveri 1.0

Kaveri 1.0

Kaveri 1.0

236Saturday, January 18, 2014

236Saturday, January 18, 2014

236Saturday, January 18, 2014

of

of

1

of

SPI Bus

31

GPIO

31

LPC

31

TPM

LPT

31

5

smd.db-x7.ru

4

3

2

1

Power Deliver Chart

ATX P/S WITH 1A STBY CURRENT

5VSB

+/-5%5V+/-5%

D D

C C

3.3V

+/-5%

12V

+/-5%

-12V

+/-5%

CPU

PW

12V

+/-5%

5VDIMM Linear

REGULATOR

VCC5_SB FET

REGULATOR

VCC3_WAKE Linear

REGULATOR

1.5V VDD SW

REGULATOR

VCC3_SB SW

REGULATOR

VCC5_SB

2.5V Shunt

Regulator

VRM SW

REGUALTOR

1.2V VDDR

REGULATOR

CPU_VDD (S0, S1)

0.75V VTT_DDR

REGULATOR

DDRIII DIMM X2

VDD MEM

VTT_DDR

1.1V VCCP SW

REGULATOR

VCC3 (S0, S1)

VCC3_SB (S0, S1, S3, S5)

1.1V_SB Linear

REGULATOR

VDDA25 (S0, S1)

VCCP (S0, S1) / VCC_NB (S0, S1)

CPU_VDDR (S0, S1)

0R

CPU_VDDP (S0, S1)

0R

VCC_DDR (S0, S1, S3)

15 A

1 A

NB_VCC1P1 (S0, S1)

+1.1VDUAL(S0,S1,S3,S5)

AMD FM2 CPU

VDDA

FM2+:1.8V ;FM2:2.5V

VDDCORE

0.8-2V

VDDNBCORE

1.2V

CPU_VDDR

FM2+:1.05V;FM2:1.2A

CPU_VDDP

FM2+:1.05V;FM2:1.2A

DDR3 MEM I/F 1.5V

VCC_DDR

1.5V-5A;

0.8~2.3V

1.35-4.9A;

BOLTON D3

VDDPL_11_DAC

VDDAN_11_ML

100 mA

VDDCR_11

500 mA

VDDAN_11_SATA

700 mA

VDDAN_11_CLK

400 mA

VDDAN_11_PCIE

900 mA

VDDIO_33_PCIGP 3.3V

300 mA

(S0, S1)

VDDPL_33_*_RUN

320 mA

VDDPL_33_*_ALW

34 mA

VDDIO_33_GBE_S

1 mA

VDDAN_33_USB_S

130 mA

VDDXL_33_S

6 mA

VDDIO_33_S

30 mA

VDDCR/AN_11_SUSB_S

500 mA

VDDCR/AN_11_USB_S

52 mA

VDDCR_11_GBE_S

100 mA

VDDCR_11_S

100 mA

0.9A

120A

60A

5A

5A

20 mA

VCC3 (S0, S1)

+5VA Linear

B B

COM Port

VCC5

+12V

-12V

0.1A

X1 PCIE per

3.3V

12V

3.3Vaux

A A

5

SVCC Linear

SVCC(S0,S3)

REGULATOR

X16 PCIE per USB 2.0 X2 FR

3.0A

0.5A

0.1A

4

3.3V

12V

3.3VDual

3.0A

5.5A

0.3A

VCC3_WAKE (S0, S1, S3, S5)

USB 3.0 X2 FR

VDD

5VDual

VDD

5VDual

1.8A 1.8A

REGULATOR

USB 2.0 X2 FR

VDD

5VDual

1.0A1.0A

USB 3.0 X2 RL

VDD

5VDual

3

USB 2.0 X2 FR

VDD

5VDual

1.0A

2XPS/2

5VDual

0.5A

USB 2.0 X2 RL

VDD

5VDual

1.0A

+5VA (S0, S1)

VCC3 (S0, S1)

VCC3_WAKE (S0, S1, S3, S5)

USB 2.0 X2 RL

VDD

5VDual

1.0A

2

AUDIO CODEC

3.3V CORE

5V ANALOG

SUPER I/O

+3.3V (S0, S1)

+3.3VDUAL (S3)

VBAT

+LAN_3VSB

REGULATOR

+LAN_3VSB

ENTHERNET

3.3V 1.05V

70mA

0.1A

0.1A

0.01A

0.01A

300mA

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

Power Deliver Chart

Power Deliver Chart

Power Deliver Chart

Custom

Custom

Custom

Kaveri 1.0

Kaveri 1.0

Kaveri 1.0

1

of

of

of

336Saturday, January 18, 2014

336Saturday, January 18, 2014

336Saturday, January 18, 2014

5

smd.db-x7.ru

4

3

2

1

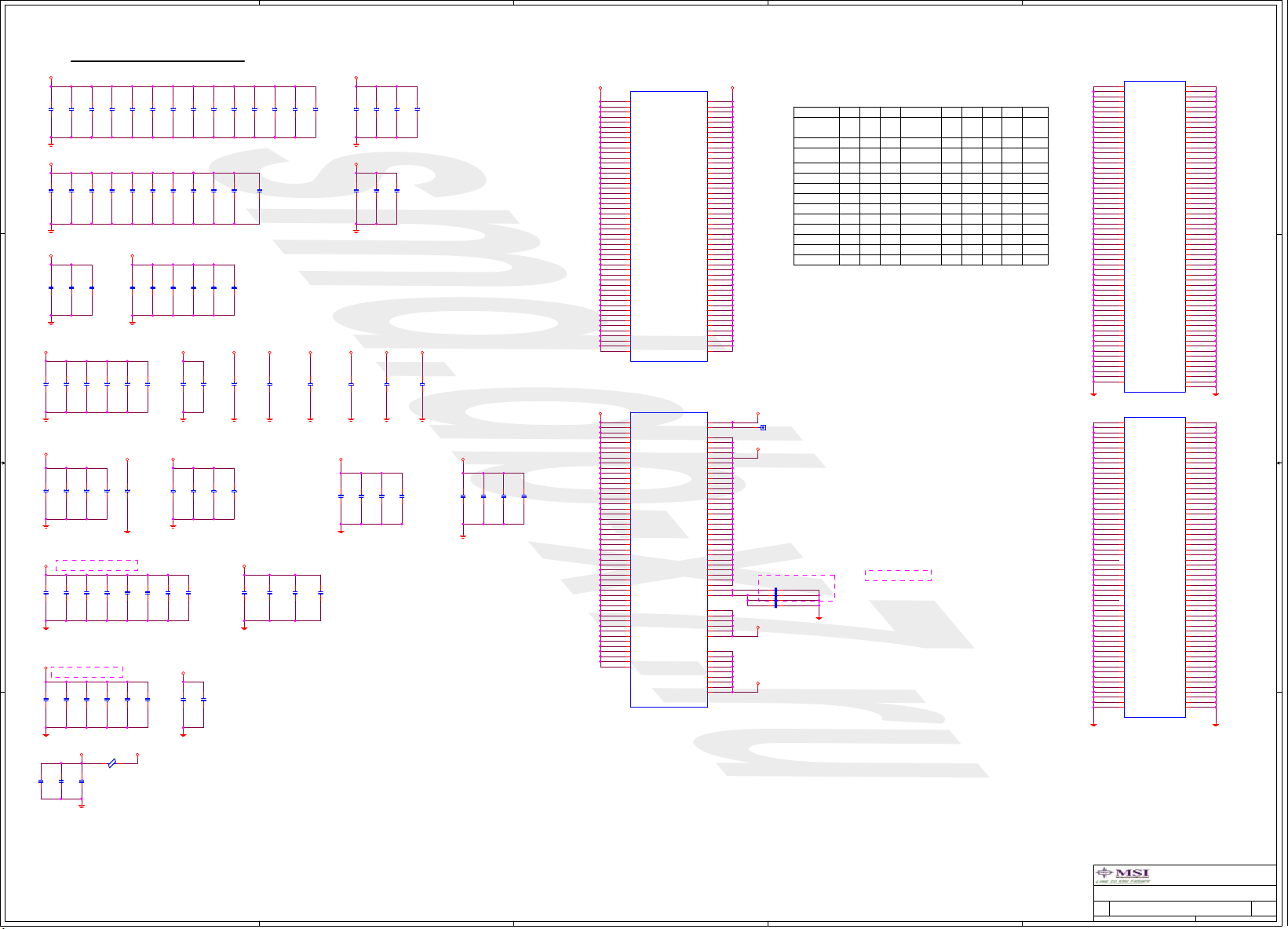

INTERNAL CLOCK MODE

D D

CH A CH B

DIMM1

DIMM2

DIMM3

DIMM4

AMD

HudsonD3

FCH_GFX_CLKP/N

FCH_GPP_CLK0P/N

FCH_GPP_CLK1P/N

FCH_GPP_CLK2P/N

FCH_GPP_CLK3P/N

FCH_GPP_CLK4P/N

32K_X1

32K_X2

RTC CLOCK

32.768K Hz

LPCCLK0

LPCCLK1

AZ_BITCLK

MEM_MA_CLK_H0/L0

MEM_MA_CLK_H3/L3

MEM_MA_CLK_H2/L2

C C

MEM_MA_CLK_H1/L1

AMD

FM2+ APU

B B

MEM_MB_CLK_H0/L0

MEM_MB_CLK_H3/L3

MEM_MB_CLK_H1/L1

MEM_MB_CLK_H2/L2

APU_CLKP/N

DISP_CLKP/N

FCH_APU_CLKP

FCH_DISP_CLKP

100MHZ (NO SPREAD)

USBCLK

14M_25M_48M_OSC

25M_X2

25MHZ

SATA_X1

FOR SATA DNI

25M Hz

SATA_X2

25M_X1

PCICLK0

PCICLK1

PCICLK3

PCICLK2

PCICLK4

RTCCLK

SPI_CLK

PCICLK0

33MHZ

PCI_CLK3PCI_CLK1

33MHZ

PCICLK2

33MHZ

PCICLK4

33MHZ

LPC_CLK0

LPCCLK1

33MHZ

AZ_BIT_CLK

24MHZ

SPI_CLK

xxHZ

PE16_GXF_CLK/PE16_GXF_CLK#

100MHZ

PE1_GPP_CLK0/PE1_GPP_CLK0#

100MHZ

PE1_GPP_CLK1/PE1_GPP_CLK1#

100MHZ

PE_MINI_CLK/PE_MINI_CLK#

100MHZ

PE_LAN_CLK/PE_LAN_CLK#

100MHZ

SIO ITE8733F

STRAPS SETTING,

UNUSED CLOCKS

LPC header

PCI SLOT

STRAPS SETTING,

RESERVE TP

HD AUDIO

SPI ROM & HEADER

PCIE GFX SLOT (FM2+, 16 LANES)

PCIE GPP SLOT1 (BoltonD3, 1 LANE)

PCIE GPP SLOT2 (BoltonD3, 1 LANE)

PCIE GPP SLOT3 (BoltonD3, 1 LANE)

PCIE LAN (FM2+, 1 LANE)

reserve LAN_CLKREQ#

PCIEX16 SLOT

PCIE X1 SLOT

PCIE X1 SLOT

Mini PCIE X1 SLOT

PCIE LAN

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Clock Distribution

Clock Distribution

Clock Distribution

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Kaveri 1.0

Kaveri 1.0

Kaveri 1.0

1

436Saturday, January 18, 2014

436Saturday, January 18, 2014

436Saturday, January 18, 2014

of

of

5

smd.db-x7.ru

FM2+

PWROK(Pin AF14)

BoltonD3,

HUDSON D3/D2

APU_PG(Pin E26)

D D

PWR_BTN#(Pin J4)

SLP_S3#(Pin T3)

SLP_S5#(Pin W2)

APU_PWRGD

FCH_PWRGDPWR_GD(Pin N7)

4

PWRGD MAP

3

2

1

POWER ON SEQUENCE

ITE 8728F

SLP_S5#(Pin 38)SLP_S5#

SUSB#(Pin 31)SLP_S3#

PSOUT# (Pin 28)PSOUT#

ATX_POWER

PSON# (Pin 30)

PSIN# (Pin 29)

C C

ATX_PWROK

SLP_S5#

ATX_PWROK

APU_FM2R1

VCC_DDR

DDR_EN

VCORE_EN

VRM_PWROK

U13

UP1566

VRM U1

ISL62773

VDDPWRGD(Pin 23)

EN(Pin 9)

PWROK(Pin 10)

PS_ON#

VRM_PWRGD

Pin13

ATX_PWROK U29 (UP7501) 5VDIMM

Pin12

F_PANEL1PSIN#

VCC_DDR

U35 (uP0105) VDDA_25

FCH_PWRGD_R

U46

TPS51211

*

D80

VRM_PWRGD

B B

ATX_PWROK

NB_VCC1P1

FP_RST#

SLP_S3#

CPU_VDDP_VDDR_EN

NBCORE_EN

D81

CPU_VDD

U37

VCC3

APL5611

U41

FCH_PWRGD

CPU_VDDP

CPU_VDDR

NB_VCC1P1

MEANS OPTION

*

RESET MAP

FM2+

RESET_L(Pin AF10)

PCIE 16X slot

PCIE 1X slot 1

PCIE 1X slot 2

PCIE LAN

Mini PCIE

TPM

A A

LPC debug

Reserve TP

Reserve TP

BoltonD3,

HUDSON D3/D2

PCIE_RST#(Pin AE2)

A_RST#(Pin AD5)Super IO

PCIE_RST2#(Pin AB6)

PCIRST#(Pin AB5)

5

SYS_RESET#(Pin U4)

APU_RST#(Pin F26)

FP_RST#

APU_RST#

F_PANEL

RESET#(Pin 12)

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

PWRGD&RESET MAP

PWRGD&RESET MAP

PWRGD&RESET MAP

Kaveri 1.0

Kaveri 1.0

Kaveri 1.0

1

536Saturday, January 18, 2014

536Saturday, January 18, 2014

536Saturday, January 18, 2014

of

of

of

5

smd.db-x7.ru

4

3

2

1

DDR DIMM Config.

DEVICE

DIMM 1

10100000B

CH-A

D D

10100010B A4H

CH-A MEM_MA_CLK_H3/L3

DIMM 3

10100001B

CH-B

DIMM 4

10100011B A6H

CH-B

CLOCKADDRESS

MEM_MA_CLK_H1/L1

A0H

MEM_MA_CLK_H2/L2

MEM_MA_CLK_H0/L0DIMM 2

MEM_MB_CLK_H1/L1

A2H

MEM_MB_CLK_H2/L2

MEM_MB_CLK_H0/L0

MEM_MB_CLK_H3/L3

SMBus TABLE

SOURCE

DP0_AUXP_C

/DP0_AUXN_C

APU

DP1_AUXP_C

C C

/DP1_AUXN_C

SCLK0/SDATA0

FCH

SCLK1/SDATA1 LAN,PCIE SLOTs,MINI_PCIE

SCLK3/SDATA3 TP

LINKED DEVICESINGLE NAME

HDMI

Bolton D3

DP to VGA translator

DIMMs,CLOCK GEN

,SIO

RESET TABLE

SOURCE

PCIE_RST# PCIe 16X,1X,LAN,MINI_PCIE

FCH

B B

FRONT

PANEL

A_RST# SIO,LPC debug

PCIE_RST2# RESERVE TP

LDT_RST# APU

AZ_RST# AZALIA CODEC

DDR3_RST# NC

FC_RST# DEBUG BUS

ROM_RST# NC

FP_RST# FCH,CLOCK GEN

LINKED DEVICESINGLE NAME

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

GPIO/MSIC/ TABLE

GPIO/MSIC/ TABLE

GPIO/MSIC/ TABLE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Kaveri 1.0

Kaveri 1.0

Kaveri 1.0

1

636Saturday, January 18, 2014

636Saturday, January 18, 2014

636Saturday, January 18, 2014

of

of

5

smd.db-x7.ru

VID Override Circuit

D D

C C

APU_SVC10

APU_SVD10

APU_SVT10

APU_PWRGD10,14

SVC SVD

00

0

COREFB+10

COREFB-10

R1

X_1KR0402R1X_1KR0402

Pre_PWROK

Metal VID

1.1

1

1.0

0.9

01

0.8

11

R42

R42

R46 0R0402R46 0R0402

NB_SENSE+10

NB_SENSE-10

VCC_DDRVCC_DDR

R5

R4

R2

X_1KR0402R2X_1KR0402

R10 0R0402R10 0R0402

R11 0R0402R11 0R0402

R12 33R0402R12 33R0402

SP1SP1

X_1KR0402R5X_1KR0402

X_1KR0402R4X_1KR0402

R19

R19

R18

R18

X_220R

X_220R

X_220R

X_220R

BOOT VOLTAGE

C15

VCCP

10R0402

10R0402

0R0402

0R0402

R41

R41

R47

R47

C15

C1000p50X0402

C1000p50X0402

R40

R40

3.83KR1%0402

3.83KR1%0402

C330p16N0402-RH-1

C330p16N0402-RH-1

C24

C24

C26

C26

C330p16N0402-RH-1

C330p16N0402-RH-1

C27

C27

10R0402

10R0402

C1000p50X0402

C1000p50X0402

CPU_VDDNB

R60

R60

C36

C36

10R0402

10R0402

R62

R62

0R0402

0R0402

R65

R65

0R0402

0R0402

R66

R66

C1000p50X0402

C1000p50X0402

10R0402

10R0402

VSUM+ NB_VSUM+

2.61KR1%0402

2.61KR1%0402

R74

R74

C42

C42

C0.33u6.3X50402-RH

C0.33u6.3X50402-RH

R81

R81

C0.22u50X_0805

C0.22u50X_0805

11KR0.5%0402-RH

11KR0.5%0402-RH

RT1

RT1

10KRT1%

10KRT1%

CLOSE to CHOKE1

C48

C48

C0.1u16X0402

C0.1u16X0402

R16

R16

R6

X_1KR0402

X_1KR0402

X_1KR0402R6X_1KR0402

SVC

SVD

SVT

VRM_PWROK

R21

R21

R20

R20

X_220R

X_220R

X_220R

X_220R

VRM_PWRGD33

VCC_DDR

R36 301R1%0402R36 301R1%0402

C32

C32

C470p50X0402

C470p50X0402

C330p16N0402-RH-1

C330p16N0402-RH-1

C38

C38

C43

C43

R84

R84

X_100R0402

X_100R0402

TP1TP1

R59

R59

C41 C0.33u6.3X50402-RHC41 C0.33u6.3X50402-RH

R55

R55

5.6KR1%0402

5.6KR1%0402

R75

R75

649R1%0402

649R1%0402

R13

R13

SVC

SVD

SVT

C12 C100p50N0402C12 C100p50N0402

R31

R31

137KR1%0402

137KR1%0402

R43

R43

499R1%0402

499R1%0402

VRM_PWRGD_R

VRM_PWROK

VCORE_EN

VCC5

VCC5 VCC5

R14

R14

1KR1%0805

1KR1%0805

X_1KR1%0805

X_1KR1%0805

R23 0R0402R23 0R0402

C13

C13

C330p50N0402

C330p50N0402

R38 41.2KR1%0402R38 41.2KR1%0402

C25 C1000p50X0402C25 C1000p50X0402

3.83KR1%0402

3.83KR1%0402

R52

R52

143KR1%0402

143KR1%0402

R61

R61

C37

C37

C330p16N0402-RH-1

C330p16N0402-RH-1

2.61KR1%0402

2.61KR1%0402

RT2

RT2

10KRT1%

10KRT1%

NB_VSUM-VSUM-

CLOSE to CHOKE3

C1 X_C0.1u16X50402-2C1 X_C0.1u16X50402-2

C2 X_C0.1u16X50402-2C2 X_C0.1u16X50402-2

C3 C2.2u6.3X50402C3 C2.2u6.3X50402

R15

R15

5.62KR1%0402

5.62KR1%0402

R76

R76

X_1KR1%0805

X_1KR1%0805

PG_NB

VRM_PWROK

C17 C10p25N0402-RH-2C17 C10p25N0402-RH-2

C28 C100p50N0402C28 C100p50N0402

C30

C30

R57

R57

34KR1%0402

34KR1%0402

C44

C44

11KR0.5%0402-RH

11KR0.5%0402-RH

R82

R82

C0.1u50X0805

C0.1u50X0805

C49

C49

C0.1u16X0402

C0.1u16X0402

VCORE_EN

VRM_PWRGD_R

R24 X_0R0402R24 X_0R0402

C11

C11

X_C0.1u16X0402

X_C0.1u16X0402

R30

R30

X_24.9KR1%0402

X_24.9KR1%0402

C470p50X0402

C470p50X0402

C34 C1500p50X0402C34 C1500p50X0402

C45

C45

C0.33u25X0805

C0.33u25X0805

4

VCC5 VCC5

+12VIN

R8

R7

2.2R0805R72.2R0805

C6

C1u6.3X70603-HFC6C1u6.3X70603-HF

9

ENABLE

23

PGOOD

42

PGOOD_NB

10

PWROK

4

SVC

6

SVD

8

SVT

5

VR_HOT_L

7

VDDIO

22

COMP

20

FB2

21

FB

18

VSEN

19

RTN

43

COMP_NB

44

FB_NB

45

VSEN_NB

16

ISUMP

17

ISUMN

47

ISUMP_NB

46

ISUMN_NB

C46 C0.33u6.3X50402-RHC46 C0.33u6.3X50402-RH

R83 422R1%0402R83 422R1%0402

R86 X_100R0402R86 X_100R0402

ISL62773HRZ_QFN48-HFISL62773HRZ_QFN48-HF

C4

C1u6.3X70603-HFC4C1u6.3X70603-HF

29

VDD

1R0805R81R0805

30

VDDP

PAD GND

49

R9

0R0805R90R0805

C5 C0.22u16XC5 C0.22u16X

35

xinhai@schmatic update(2011/10/07)

VIN

41

FCCM_NB

24

BOOT1

25

UGATE1

26

PHASE1

27

LGATE1

34

BOOT2

33

UGATE2

32

PHASE2

31

LGATE2

28

PWM_Y

36

BOOTX

37

UGATEX

38

PHASEX

39

LGATEX

40

PWM2_NB

15

ISNE1

14

ISNE2

13

ISEN3

48

ISNE1_NB

1

ISEN2_NB

12

NTC

2

NTC_NB

11

IMON

3

IMON_NB

C47

C47

C1000p50X0402

C1000p50X0402

R26

R26

0R0805

0R0805

R37

R37

0R0805

0R0805

PWMY

R53

R53

0R0805

0R0805

UG1_NB

PH1_NB

LG1_NB

PWM2_NB

ISEN1

ISEN2

R67

R67

X_0R0402

X_0R0402

ISEN3

R69

R69

X_0R0402

X_0R0402

NB_ISEN1

NB_ISEN2

R72 X_0R0402R72 X_0R0402

R89

R89

118KR1%0402

118KR1%0402

C50

C50

R94

R94

C1000p50X0402

C1000p50X0402

118KR1%0402

118KR1%0402

C9

C0.22u16XC9C0.22u16X

C16

C16

C0.22u16X

C0.22u16X

C31

C31

C0.22u16X

C0.22u16X

VCC5

X_27.4KR1%0402-RH

X_27.4KR1%0402-RH

R22

R22

X_41.2KR1%

X_41.2KR1%

UG1

PH1

LG1

UG2

PH2

LG2

R85

R85

0R0402

0R0402

R90

R90

18.2KR1%0402-RH

18.2KR1%0402-RH

100KRT1%0402

100KRT1%0402

R92

R92

3

R17 0R0805R17 0R0805

10KR0402

10KR0402

R39

R39

R44 0R0805R44 0R0805

N-PK516BA_PDFN8-HF

N-PK516BA_PDFN8-HF

R63

R63

10KR0402

10KR0402

R64 0R0805R64 0R0805

N-PK516BA_PDFN8-HF

N-PK516BA_PDFN8-HF

RT4

RT4

ERT-J0EV474J

CLOSE Q1 or Q13

VIN

C1u16X5-RHC7C1u16X5-RH

R3210KR0402 R3210KR0402

4

3

2

1

N-PK516BA_PDFN8-HF

N-PK516BA_PDFN8-HF

4

3

2

1

N-PK510BA_PDFN8-HF

N-PK510BA_PDFN8-HF

VIN

4

3

2

1

4

3

2

1

N-PK510BA_PDFN8-HF

N-PK510BA_PDFN8-HF

VIN

4

3

2

1

N-PK510BA_PDFN8-HF

N-PK510BA_PDFN8-HF

X_C10u16X50805-HFC8X_C10u16X50805-HF

C7

5

Q2

Q2

5

Q3

Q3

N-PK510BA_PDFN8-HF

N-PK510BA_PDFN8-HF

5

Q5

Q5

N-PK516BA_PDFN8-HF

N-PK516BA_PDFN8-HF

5

Q8

Q8

5

Q9

Q9

N-PK516BA_PDFN8-HF

N-PK516BA_PDFN8-HF

4

3

2

1

R88

R88

18.2KR1%0402-RH

18.2KR1%0402-RH

R91

X_27.4KR1%0402-RH

R91

X_27.4KR1%0402-RH

ERT-J0EV474J

CLOSE Q7 or Q8

+

+

12

C8

EC10

EC10

CD270u16SO-HF-1

CD270u16SO-HF-1

4

3

2

1

N-PK516BA_PDFN8-HF

N-PK516BA_PDFN8-HF

5

Q4

Q4

4

3

2

1

5

4

3

2

1

5

Q7

Q7

4

3

2

1

N-PK510BA_PDFN8-HF

N-PK510BA_PDFN8-HF

5

4

3

2

1

5

Q12

Q12

4

3

2

1

N-PK510BA_PDFN8-HF

N-PK510BA_PDFN8-HF

RT3

100KRT1%0402

RT3

100KRT1%0402

2

ATX_12V

ATX_12V

123

+

+

12

+

+

12

EC1

EC1

EC2

EC9

EC9

C470u2.5SO-HF

C470u2.5SO-HF

R25

R25

2.2R1206

2.2R1206

C10

C10

C1000p50N

C1000p50N

C29

C29

C1000p50N

C1000p50N

C35

C35

EC2

C560u6.3SO-RH

C560u6.3SO-RH

C560u6.3SO-RH

C560u6.3SO-RH

CHOKE1

CHOKE1

CH-0.3u50A0.6m-HF

CH-0.3u50A0.6m-HF

1 2

12

CP1CP1

R28 3.65KR1%0402R283.65KR1%0402

VSUM+

ISEN1

R29 10KR0402R29 10KR0402

C14

C14

R108

R108

C0.22u16X0402-HF

C0.22u16X0402-HF

R34 1R1%0402R34 1R1%0402

X_10KR0402

X_10KR0402

VSUM-

+

+

12

C20

C20

EC11

EC11

CD270u16SO-HF-1

CD270u16SO-HF-1

X_C10u16X50805-HF

X_C10u16X50805-HF

R45

R45

2.2R1206

2.2R1206

VSUM+ ISEN3

ISEN2

C33

C33

R114

R114

C0.22u16X0402-HF

C0.22u16X0402-HF

X_10KR0402

X_10KR0402

VSUM-

12

+

+

EC12

EC12

CD270u16SO-HF-1

CD270u16SO-HF-1

R68

R68

2.2R1206

2.2R1206

C39

C39

C1000p50N

C1000p50N

NB_VSUM+

NB_ISEN1

R116

R116

X_10KR0402

X_10KR0402

NB_VSUM-

EC17

EC17

X_C470u2.5SO-HF

X_C470u2.5SO-HF

R50 3.65KR1%0402R503.65KR1%0402

R54 10KR0402R54 10KR0402

R58 1R1%0402R58 1R1%0402

R70 3.65KR1%0402R703.65KR1%0402

R73 10KR0402R73 10KR0402

C40

C40

C0.22u16X0402-HF

C0.22u16X0402-HF

R80 1R1%0402R80 1R1%0402

+

+

12

CP3CP3

+

+

12

CHOKE2

CHOKE2

CH-0.3u50A0.6m-HF

CH-0.3u50A0.6m-HF

1 2

12

CP6CP6

EC18

EC18

X_C470u2.5SO-HF

X_C470u2.5SO-HF

Q6

Q6

Q10

Q10

5

X_10KR0402

X_10KR0402

+

+

12

5

Q1

Q1

C1u16X5-RH

C1u16X5-RH

C19

C19

C1u16X5-RH

C1u16X5-RH

Q11

Q11

R79

R79

12V

12V

12V

12V

GND GND

GND GND

PWRCONN4P_WHITE-RH-3

PWRCONN4P_WHITE-RH-3

5

+

+

12

EC4

EC4

C560u6.3SO-RH

C560u6.3SO-RH

12

CP2CP2

12

CP4CP4

CHOKE3

CHOKE3

CH-0.3u50A0.6m-HF

CH-0.3u50A0.6m-HF

1 2

12

CP5CP5

+

+

12

EC19

EC19

X_C470u2.5SO-HF

X_C470u2.5SO-HF

4

R27 X_10KR0402R27 X_10KR0402

R33 X_10KR0402R33 X_10KR0402

R48 X_10KR0402R48 X_10KR0402

R51 X_10KR0402R51 X_10KR0402

12

+12VIN

C60

C60

+

+

12

VCCP

R71 X_10KR0402R71 X_10KR0402

+

+

12

EC13

EC13

C560u6.3SO-RH

C560u6.3SO-RH

C0.1u16X50402-2

C0.1u16X50402-2

EC6

EC6

C560u6.3SO-RH

C560u6.3SO-RH

ISEN2

ISEN3

ISEN1

1 2

C22u6.3X50805-RH

C22u6.3X50805-RH

VCCP

NB_ISEN2

+

+

12

CHOKE5

CHOKE5

CH-1.2u15A1.7m-RH-2

CH-1.2u15A1.7m-RH-2

+

+

12

EC7

EC7

C560u6.3SO-RH

C560u6.3SO-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C18

C18

CPU_VDDNB

EC14

EC14

C560u6.3SO-RH

C560u6.3SO-RH

1

VIN

VCCP

+

+

12

EC8

EC8

C560u6.3SO-RH

C560u6.3SO-RH

VCCP

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22

C22

C21

C21

C23

C23

+

+

12

+

+

12

EC15

EC15

EC16

EC16

C560u6.3SO-RH

C560u6.3SO-RH

C560u6.3SO-RH

C560u6.3SO-RH

CPU_VDDNB

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C52

C52

C53

C53

VIN

C1u16X5-RH

4

3

2

1

N-PK516BA_PDFN8-HF

N-PK516BA_PDFN8-HF

5

Q19

Q19

VSUM+

R117

R117

X_10KR0402

X_10KR0402

VIN

5

Q21

Q21

4

3

2

1

N-PK516BA_PDFN8-HF

N-PK516BA_PDFN8-HF

4

3

2

1

N-PK510BA_PDFN8-HF

N-PK510BA_PDFN8-HF

NB_ISEN2

NB_VSUM-

ISEN3

VSUM-

5

Q27

Q27

C1u16X5-RH

5

Q16

Q16

R105

R105

2.2R1206

2.2R1206

C59

C59

C1000p50X0402

C1000p50X0402

R1093.65KR1%0402R1093.65KR1%0402

R110 10KR0402R110 10KR0402

C61

C61

C0.22u16X0402-HF

C0.22u16X0402-HF

5

Q22

Q22

NB_VSUM+

R120

R120

X_10KR0402

X_10KR0402

2

C54

C54

X_C10u16X50805-HF

X_C10u16X50805-HF

1 2

12

CP8CP8

R1111R1%0402R1111R1%0402

C1u16X5-RH

C1u16X5-RH

C62

C62

R122

R122

2.2R1206

2.2R1206

C70

C70

C1000p50X0402

C1000p50X0402

R127 3.65KR1%0402R127 3.65KR1%0402

R129 10KR0402R129 10KR0402

C72

C72

C0.22u16X0402-HF

C0.22u16X0402-HF

C55

C55

CHOKE4

CHOKE4

CH-0.3u50A0.6m-HF

CH-0.3u50A0.6m-HF

CP7CP7

C66

C66

X_C10u16X50805-HF

X_C10u16X50805-HF

1 2

12

CP9CP9

R1321R1%0402R1321R1%0402

12

R49 X_10KR0402R49 X_10KR0402

R56 X_10KR0402R56 X_10KR0402

+

+

12

EC20

EC20

CD270u16SO-HF-1

CD270u16SO-HF-1

CHOKE6

CHOKE6

CH-0.3u50A0.6m-HF

CH-0.3u50A0.6m-HF

CP10CP10

12

VCCP

ISEN1

ISEN2

CPU_VDDNB

R124 X_10KR0402R124 X_10KR0402

NB_ISEN1

Title

Title

Title

ISL62773+6208

ISL62773+6208

ISL62773+6208

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Kaveri 1.0

Kaveri 1.0

Kaveri 1.0

1

of

of

of

736Saturday, January 18, 2014

736Saturday, January 18, 2014

736Saturday, January 18, 2014

Sequence

B B

A A

VRM_PWRGD_R

VDDA_25_PWROK32

ATX_PWROK31,32,33,34

APU_FM2R110,33

VCORE_EN_R31,33

VCCP

R95

R95

X_1KR0402

X_1KR0402

R96 X_10KR0402R96 X_10KR0402

D6 S-RB751V-40_SOD323-RHD6 S-RB751V-40_SOD323-RH

D1 S-RB751V-40_SOD323-RHD1 S-RB751V-40_SOD323-RH

D2 S-RB751V-40_SOD323-RHD2 S-RB751V-40_SOD323-RH

VCORE_EN_R

5

VCC5

Q14

Q14

C

C

B

B

E

E

X_N-SST3904_SOT23

X_N-SST3904_SOT23

R93

R93

X_10KR0402

X_10KR0402

G

G

VRM_PWRGD

DS

C51

C51

Q13

Q13

X_C0.1u16X50402-2

X_C0.1u16X50402-2

X_N-2N7002P_SOT23-3-HF

X_N-2N7002P_SOT23-3-HF

VCC5 +12VIN

R98

R98

10KR0402

10KR0402

DS

Q17

Q17

N-2N7002P_SOT23-3-HF

N-2N7002P_SOT23-3-HF

G

Make sure +12VIN

connector plug in

R99

R99

10.7KR1%0402

10.7KR1%0402

DS

Q18

Q18

N-2N7002P_SOT23-3-HF

N-2N7002P_SOT23-3-HF

R102

R102

3.3KR0402

3.3KR0402

BOOT3 PH3

R97

R97

C56

C56

0R0805

0R0805

C0.22u16X

C0.22u16X

10KR0402

VCC5

R101

R101

0R0805

0R0805

C58

C58

C1u6.3X50402-HF

C1u6.3X50402-HF

VCORE_EN

C57

C57

C2.2u6.3X5

C2.2u6.3X5

VCC5

R115

R115

0R0805

0R0805

C68

C68

C1u6.3X50402-HF

C1u6.3X50402-HF

4

U2

U2

BOOT3

2

BOOT

R104 0R0805R104 0R0805

7

FCCM

6

VCC

PWMY

3

PWM

4

BOOT2_NB PH2_NB

R112

R112

0R0805

0R0805

BOOT2_NB

2

R119 0R0805R119 0R0805

7

6

PWM2_NB

3

4

3

ISL6208BCRZ_QFN8-HF

ISL6208BCRZ_QFN8-HF

UGATE

PHASE

LGATE5GND

GND_P

9

C65

C65

C0.22u16X

C0.22u16X

ISL6208BCRZ_QFN8-HF

ISL6208BCRZ_QFN8-HF

U3

U3

BOOT

UGATE

FCCM

PHASE

VCC

PWM

LGATE5GND

GND_P

9

10KR0402

R103 0R0805R103 0R0805

1

PH3

8

LG3

N-PK510BA_PDFN8-HF

N-PK510BA_PDFN8-HF

UG2_NB

1

PH2_NB

8

LG2_NB

R100

R100

UG3

10KR0402

10KR0402

R118 0R0805R118 0R0805

4

3

2

1

N-PK516BA_PDFN8-HF

N-PK516BA_PDFN8-HF

5

Q20

Q20

4

3

2

1

R113

R113

N-PK510BA_PDFN8-HF

N-PK510BA_PDFN8-HF

5

Q15

Q15

4

3

2

1

N-PK510BA_PDFN8-HF

N-PK510BA_PDFN8-HF

4

3

2

1

N-PK516BA_PDFN8-HF

N-PK516BA_PDFN8-HF

5

Q26

Q26

4

3

2

1

5

smd.db-x7.ru

4

3

2

1

FM1 PCIE I/F

D D

CPU1A

CPU1A

GFX_RX0P22

GFX_RX0N22

GFX_RX1P22

GFX_RX1N22

GFX_RX2P22

GFX_RX2N22

GFX_RX3P22

GFX_RX3N22

GFX_RX4P22

GFX_RX4N22

GFX_RX5P22

GFX_RX5N22

GFX_RX6P22

GFX_RX6N22

GFX_RX7P22

GFX_RX7N22

GFX_RX8P22

GFX_RX8N22

C C

B B

CPU_VDDP

GFX_RX9P22

GFX_RX9N22

GFX_RX10P22

GFX_RX10N22

GFX_RX11P22

GFX_RX11N22

GFX_RX12P22

GFX_RX12N22

GFX_RX13P22

GFX_RX13N22

GFX_RX14P22

GFX_RX14N22

GFX_RX15P22

GFX_RX15N22

LAN_RXP25

LAN_RXN25

UMI_RX0P14

UMI_RX0N14

UMI_RX1P14

UMI_RX1N14

UMI_RX2P14

UMI_RX2N14

UMI_RX3P14

UMI_RX3N14

R134 196R1%R134 196R1% R135 196R1%R135 196R1%

LAN_RXP

LAN_RXN

APU_P_ZVDDP

Layout:

Place within 1.5'' of APU

AD8

P_GFX_RXP0

AD9

P_GFX_RXN0

AC7

P_GFX_RXP1

AC8

P_GFX_RXN1

AB5

P_GFX_RXP2

AB6

P_GFX_RXN2

AB8

P_GFX_RXP3

AB9

P_GFX_RXN3

AA7

P_GFX_RXP4

AA8

P_GFX_RXN4

Y5

P_GFX_RXP5

Y6

P_GFX_RXN5

Y8

P_GFX_RXP6

Y9

P_GFX_RXN6

W7

P_GFX_RXP7

W8

P_GFX_RXN7

V5

P_GFX_RXP8

V6

P_GFX_RXN8

V8

P_GFX_RXP9

V9

P_GFX_RXN9

U7

P_GFX_RXP10

U8

P_GFX_RXN10

T5

P_GFX_RXP11

T6

P_GFX_RXN11

T8

P_GFX_RXP12

T9

P_GFX_RXN12

R7

P_GFX_RXP13

R8

P_GFX_RXN13

P5

P_GFX_RXP14

P6

P_GFX_RXN14

P8

P_GFX_RXP15

P9

P_GFX_RXN15

AF5

P_GPP_RXP0

AF6

P_GPP_RXN0

AF8

P_GPP_RXP1

AF9

P_GPP_RXN1

AE7

P_GPP_RXP2

AE8

P_GPP_RXN2

AD5

P_GPP_RXP3

AD6

P_GPP_RXN3

AJ8

P_UMI_RXP0

AJ7

P_UMI_RXN0

AH6

P_UMI_RXP1

AH5

P_UMI_RXN1

AH9

P_UMI_RXP2

AH8

P_UMI_RXN2

AG8

P_UMI_RXP3

AG7

P_UMI_RXN3

AJ2

P_ZVDDP

ZIF-SOCKET906-HF

ZIF-SOCKET906-HF

PCI EXPRESS

PCI EXPRESS

UMI GPP GRAPHICS

UMI GPP GRAPHICS

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

P_GFX_TXP4

P_GFX_TXN4

P_GFX_TXP5

P_GFX_TXN5

P_GFX_TXP6

P_GFX_TXN6

P_GFX_TXP7

P_GFX_TXN7

P_GFX_TXP8

P_GFX_TXN8

P_GFX_TXP9

P_GFX_TXN9

P_GFX_TXP10

P_GFX_TXN10

P_GFX_TXP11

P_GFX_TXN11

P_GFX_TXP12

P_GFX_TXN12

P_GFX_TXP13

P_GFX_TXN13

P_GFX_TXP14

P_GFX_TXN14

P_GFX_TXP15

P_GFX_TXN15

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_UMI_TXP0

P_UMI_TXN0

P_UMI_TXP1

P_UMI_TXN1

P_UMI_TXP2

P_UMI_TXN2

P_UMI_TXP3

P_UMI_TXN3

P_ZVSS

AC2

AC1

AC4

AC5

AB2

AB3

AA2

AA1

AA4

AA5

Y2

Y3

W2

W1

W4

W5

V2

V3

U2

U1

U4

U5

T2

T3

R2

R1

R4

R5

P2

P3

N2

N1

AF2

AF3

AE2

AE1

AE4

AE5

AD2

AD3

UMI_TX0P_APU

AJ5

UMI_TX0N_APU

AJ4

UMI_TX1P_APU

AH3

UMI_TX1N_APU

AH2

UMI_TX2P_APU

AG1

UMI_TX2N_APU

AG2

UMI_TX3P_APU

AG5

UMI_TX3N_APU

AG4

APU_P_ZVSS

AJ1

GFX_TXP0

GFX_TXN0

GFX_TXP1

GFX_TXN1

GFX_TXP2

GFX_TXN2

GFX_TXP3

GFX_TXN3

GFX_TXP4

GFX_TXN4

GFX_TXP5

GFX_TXN5

GFX_TXP6

GFX_TXN6

GFX_TXP7

GFX_TXN7

GFX_TXP8

GFX_TXN8

GFX_TXP9

GFX_TXN9

GFX_TXP10

GFX_TXN10

GFX_TXP11

GFX_TXN11

GFX_TXP12

GFX_TXN12

GFX_TXP13

GFX_TXN13

GFX_TXP14

GFX_TXN14

GFX_TXP15

GFX_TXN15

LAN_TXP

LAN_TXN

C106 C0.1u10X0402C106 C0.1u10X0402

C107 C0.1u10X0402C107 C0.1u10X0402

C108 C0.1u10X0402C108 C0.1u10X0402

C109 C0.1u10X0402C109 C0.1u10X0402

C110 C0.1u10X0402C110 C0.1u10X0402

C111 C0.1u10X0402C111 C0.1u10X0402

C112 C0.1u10X0402C112 C0.1u10X0402

C113 C0.1u10X0402C113 C0.1u10X0402

C114 C0.1u10X0402C114 C0.1u10X0402

C115 C0.1u10X0402C115 C0.1u10X0402

Layout:

Place within 1.5'' of APU

C74 C0.22u6.3X70402C74 C0.22u6.3X70402

C75 C0.22u6.3X70402C75 C0.22u6.3X70402

C76 C0.22u6.3X70402C76 C0.22u6.3X70402

C77 C0.22u6.3X70402C77 C0.22u6.3X70402

C78 C0.22u6.3X70402C78 C0.22u6.3X70402

C79 C0.22u6.3X70402C79 C0.22u6.3X70402

C80 C0.22u6.3X70402C80 C0.22u6.3X70402

C81 C0.22u6.3X70402C81 C0.22u6.3X70402

C82 C0.22u6.3X70402C82 C0.22u6.3X70402

C83 C0.22u6.3X70402C83 C0.22u6.3X70402

C84 C0.22u6.3X70402C84 C0.22u6.3X70402

C85 C0.22u6.3X70402C85 C0.22u6.3X70402

C86 C0.22u6.3X70402C86 C0.22u6.3X70402

C87 C0.22u6.3X70402C87 C0.22u6.3X70402

C88 C0.22u6.3X70402C88 C0.22u6.3X70402

C89 C0.22u6.3X70402C89 C0.22u6.3X70402

C90 C0.22u6.3X70402C90 C0.22u6.3X70402

C91 C0.22u6.3X70402C91 C0.22u6.3X70402

C92 C0.22u6.3X70402C92 C0.22u6.3X70402

C93 C0.22u6.3X70402C93 C0.22u6.3X70402

C94 C0.22u6.3X70402C94 C0.22u6.3X70402

C95 C0.22u6.3X70402C95 C0.22u6.3X70402

C96 C0.22u6.3X70402C96 C0.22u6.3X70402

C97 C0.22u6.3X70402C97 C0.22u6.3X70402

C98 C0.22u6.3X70402C98 C0.22u6.3X70402

C99 C0.22u6.3X70402C99 C0.22u6.3X70402

C100 C0.22u6.3X70402C100 C0.22u6.3X70402

C101 C0.22u6.3X70402C101 C0.22u6.3X70402

C102 C0.22u6.3X70402C102 C0.22u6.3X70402

C103 C0.22u6.3X70402C103 C0.22u6.3X70402

C104 C0.22u6.3X70402C104 C0.22u6.3X70402

C105 C0.22u6.3X70402C105 C0.22u6.3X70402

GFX_TXC_0P 22

GFX_TXC_0N 22

GFX_TXC_1P 22

GFX_TXC_1N 22

GFX_TXC_2P 22

GFX_TXC_2N 22

GFX_TXC_3P 22

GFX_TXC_3N 22

GFX_TXC_4P 22

GFX_TXC_4N 22

GFX_TXC_5P 22

GFX_TXC_5N 22

GFX_TXC_6P 22

GFX_TXC_6N 22

GFX_TXC_7P 22

GFX_TXC_7N 22

GFX_TXC_8P 22

GFX_TXC_8N 22

GFX_TXC_9P 22

GFX_TXC_9N 22

GFX_TXC_10P 22

GFX_TXC_10N 22

GFX_TXC_11P 22

GFX_TXC_11N 22

GFX_TXC_12P 22

GFX_TXC_12N 22

GFX_TXC_13P 22

GFX_TXC_13N 22

GFX_TXC_14P 22

GFX_TXC_14N 22

GFX_TXC_15P 22

GFX_TXC_15N 22

LAN_TXC_P 25

LAN_TXC_N 25

UMI_TX0P 14

UMI_TX0N 14

UMI_TX1P 14

UMI_TX1N 14

UMI_TX2P 14

UMI_TX2N 14

UMI_TX3P 14

UMI_TX3N 14

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

FM2 PCIE I/F

FM2 PCIE I/F

FM2 PCIE I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

Kaveri 1.0

Kaveri 1.0

Kaveri 1.0

1

of

of

of

836Saturday, January 18, 2014

836Saturday, January 18, 2014

836Saturday, January 18, 2014

5

smd.db-x7.ru

4

3

2

1

FM1DDR3 I/F

D D

MEM_MA_ADD[15..0]12

MEM_MA_BANK012

MEM_MA_BANK112

MEM_MA_BANK212

C C

mach@CLOCK assignment can be changed

MEM_MA_CLK_H012

MEM_MA_CLK_L012

MEM_MA_CLK_H312

MEM_MA_CLK_L312

MEM_MA_CKE012

MEM_MA_CKE112

MEM_MA1_ODT012

MEM_MA1_ODT112

MEM_MA1_CS_L012

MEM_MA1_CS_L112

MEM_MA_RAS_L12

MEM_MA_CAS_L12

APU_MA_VREFDQ13

MEM_MA_WE_L12

MEM_MA_RESET#12

MEM_MA_HOT#12

APU_M_VREF

VCC_DDR

B B

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_CLK_H0

MEM_MA_CLK_L0

MEM_MA_CLK_H3

MEM_MA_CLK_L3

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MA1_ODT0

MEM_MA1_ODT1

MEM_MA1_CS_L0

MEM_MA1_CS_L1

MEM_MA_RAS_L

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RESET#

MEM_MA_HOT#

APU_MA_VREFDQ

R137 39.2R1%0402R137 39.2R1%0402

MEM_MA_DQS_L[7..0]12

MEM_MA_DQS_H[7..0]12

MEM_MA_DM[7..0]12

CPU1B

CPU1B

V27

MA_ADD0

P27

MA_ADD1

R25

MA_ADD2

P26

MA_ADD3

R24

MA_ADD4

P24

MA_ADD5

P23

MA_ADD6

N26

MA_ADD7

N23

MA_ADD8

M25

MA_ADD9

V24

MA_ADD10

N25

MA_ADD11

M24

MA_ADD12

Y23

MA_ADD13

L27

MA_ADD14

L24

MA_ADD15

W26

MA_BANK0

V25

MA_BANK1

L26

MA_BANK2

E17

MA_DM0

H21

MA_DM1

F25

MA_DM2

G29

MA_ZVDDIO

MA_DM3

AF29

MA_DM4

AE25

MA_DM5

AG21

MA_DM6

AF17

MA_DM7

H17

MA_DQS_H0

G17

MA_DQS_L0

F21

MA_DQS_H1

E21

MA_DQS_L1

G26

MA_DQS_H2

G25

MA_DQS_L2

F30

MA_DQS_H3

E30

MA_DQS_L3

AE28

MA_DQS_H4

AE29

MA_DQS_L4

AG24

MA_DQS_H5

AG25

MA_DQS_L5

AF20

MA_DQS_H6

AF21

MA_DQS_L6

AE16

MA_DQS_H7

AD16

MA_DQS_L7

U27

MA_CLK_H0

U26

MA_CLK_L0

T23

MA_CLK_H1

U23

MA_CLK_L1

T25

MA_CLK_H2

T26

MA_CLK_L2

R27

MA_CLK_H3

R28

MA_CLK_L3

L23

MA_CKE0

K26

MA_CKE1

AA24

MA0_ODT0

AC27

MA0_ODT1

AA25

MA1_ODT0

AC26

MA1_ODT1

Y27

MA0_CS_L0

AB26

MA0_CS_L1

W23

MA1_CS_L0

AB25

MA1_CS_L1

W25

MA_RAS_L

Y24

MA_CAS_L

Y26

MA_WE_L

J25

MA_RESET_L

U24

MA_EVENT_L

K22

M_VREF

E15

MA_VREFDQ(FM2:VSS)

J24

MA_ZVDDIO(FM2:M_ZVDDIO)

ZIF-SOCKET906-HF

ZIF-SOCKET906-HF

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MEM_MA_DATA0

F16

MEM_MA_DATA1

G16

MEM_MA_DATA2

H18

MEM_MA_DATA3

F19

MEM_MA_DATA4

F15

MEM_MA_DATA5

H15

MEM_MA_DATA6

E18

MEM_MA_DATA7

F18

MEM_MA_DATA8

G20

MEM_MA_DATA9

H20

MEM_MA_DATA10

E23

MEM_MA_DATA11

G23

MEM_MA_DATA12

G19

MEM_MA_DATA13

E20

MEM_MA_DATA14

F22

MEM_MA_DATA15

G22

MEM_MA_DATA16

F24

MEM_MA_DATA17

H24

MEM_MA_DATA18

E27

MEM_MA_DATA19

F27

MEM_MA_DATA20

H23

MEM_MA_DATA21

E24

MEM_MA_DATA22

E26

MEM_MA_DATA23

H26

MEM_MA_DATA24

G28

MEM_MA_DATA25

E29

MEM_MA_DATA26

H29

MEM_MA_DATA27

H30

MEM_MA_DATA28

H27

MEM_MA_DATA29

F28

MEM_MA_DATA30

F31

MEM_MA_DATA31

G31

MEM_MA_DATA32

AD30

MEM_MA_DATA33

AF30

MEM_MA_DATA34

AG27

MEM_MA_DATA35

AF27

MEM_MA_DATA36

AD31

MEM_MA_DATA37

AE31

MEM_MA_DATA38

AG28

MEM_MA_DATA39

AD28

MEM_MA_DATA40

AF26

MEM_MA_DATA41

AD25

MEM_MA_DATA42

AF23

MEM_MA_DATA43

AE23

MEM_MA_DATA44

AD27

MEM_MA_DATA45

AE26

MEM_MA_DATA46

AF24

MEM_MA_DATA47

AD24

MEM_MA_DATA48

AG22

MEM_MA_DATA49

AD21

MEM_MA_DATA50

AE19

MEM_MA_DATA51

AG19

MEM_MA_DATA52

AD22

MEM_MA_DATA53

AE22

MEM_MA_DATA54

AE20

MEM_MA_DATA55

AD19

MEM_MA_DATA56

AG18

MEM_MA_DATA57

AE17

MEM_MA_DATA58

AF15

MEM_MA_DATA59

AG15

MEM_MA_DATA60

AD18

MEM_MA_DATA61

AF18

MEM_MA_DATA62

AG16

MEM_MA_DATA63

AD15

MEM_MA_DATA[63..0] 12

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD[15..0]12

MEM_MB_BANK012

MEM_MB_BANK112

MEM_MB_BANK212

MEM_MB_CLK_H012

MEM_MB_CLK_L012

MEM_MB_CLK_H312

MEM_MB_CLK_L312

MEM_MB_CKE012

MEM_MB_CKE112

MEM_MB1_ODT012

MEM_MB1_ODT112

MEM_MB1_CS_L012

MEM_MB1_CS_L112

MEM_MB_RAS_L12

MEM_MB_CAS_L12

MEM_MB_WE_L12

MEM_MB_RESET#12

MEM_MB_HOT#12

APU_MB_VREFDQ13

VCC_DDR

R136 39.2R1%0402R136 39.2R1%0402

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_CLK_H0

MEM_MB_CLK_L0

MEM_MB_CLK_H3

MEM_MB_CLK_L3

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MB1_ODT0

MEM_MB1_ODT1

MEM_MB1_CS_L0

MEM_MB1_CS_L1

MEM_MB_RAS_L

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RESET#

MEM_MB_HOT#

APU_MB_VREFDQ

MB_ZVDDIO

MEM_MB_DQS_L[7..0]12

MEM_MB_DQS_H[7..0]12

V31

N28

P29

N29

N31

M30

M31

M28

M27

L30

W31

L29

K28

AB28

K31

W29

V30

K29

D16

B20

A25

D29

AL29

AH25

AK21

AJ17

A17

B17

B21

C21

D25

C25

B29

A29

AJ29

AH29

AK25

AL25

AJ20

AJ21

AL16

AL17

U30

U29

T29

T28

R31

T31

P30

R30

AA30

AC30

AA31

AC29

Y29

AB29

Y30

AB31

W28

AA27

AA28

V28

D14

K25

MEM_MB_DM[7..0]12

CPU1C

CPU1C

J31

J30

J28

J27

ZIF-SOCKET906-HF

ZIF-SOCKET906-HF

MEMORY CHANNEL B

MEMORY CHANNEL B

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

MB_CLK_H0

MB_CLK_L0

MB_CLK_H1

MB_CLK_L1

MB_CLK_H2

MB_CLK_L2

MB_CLK_H3

MB_CLK_L3

MB_CKE0

MB_CKE1

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB1_ODT1

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB1_CS_L1

MB_RAS_L

MB_CAS_L

MB_WE_L

MB_RESET_L

MB_EVENT_L

MB_VREFDQ(FM2:VSS)

MB_ZVDDIO(FM2:RSVD5)

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MEM_MB_DATA0

A16

MEM_MB_DATA1

C16

MEM_MB_DATA2

B18

MEM_MB_DATA3

A19

MEM_MB_DATA4

C15

MEM_MB_DATA5

B15

MEM_MB_DATA6

D17

MEM_MB_DATA7

C18

MEM_MB_DATA8

D20

MEM_MB_DATA9

A20

MEM_MB_DATA10

D22

MEM_MB_DATA11

D23

MEM_MB_DATA12

C19

MEM_MB_DATA13

D19

MEM_MB_DATA14

A22

MEM_MB_DATA15

C22

MEM_MB_DATA16

C24

MEM_MB_DATA17

B24

MEM_MB_DATA18

B26

MEM_MB_DATA19

C27

MEM_MB_DATA20

A23

MEM_MB_DATA21

B23

MEM_MB_DATA22

D26

MEM_MB_DATA23

A26

MEM_MB_DATA24

C28

MEM_MB_DATA25

D28

MEM_MB_DATA26

C31

MEM_MB_DATA27

D31

MEM_MB_DATA28

B27

MEM_MB_DATA29

A28

MEM_MB_DATA30

B30

MEM_MB_DATA31

C30

MEM_MB_DATA32

AJ30

MEM_MB_DATA33

AK30

MEM_MB_DATA34

AH28

MEM_MB_DATA35

AJ27

MEM_MB_DATA36

AG30

MEM_MB_DATA37

AH31

MEM_MB_DATA38

AK28

MEM_MB_DATA39

AL28

MEM_MB_DATA40

AJ26

MEM_MB_DATA41

AH26

MEM_MB_DATA42

AH23

MEM_MB_DATA43

AJ23

MEM_MB_DATA44

AK27

MEM_MB_DATA45

AL26

MEM_MB_DATA46

AJ24

MEM_MB_DATA47

AK24

MEM_MB_DATA48

AK22

MEM_MB_DATA49

AH22

MEM_MB_DATA50

AL19

MEM_MB_DATA51

AK19

MEM_MB_DATA52

AL23

MEM_MB_DATA53

AL22

MEM_MB_DATA54

AH20

MEM_MB_DATA55

AL20

MEM_MB_DATA56

AJ18

MEM_MB_DATA57

AH17

MEM_MB_DATA58

AJ15

MEM_MB_DATA59

AK15

MEM_MB_DATA60

AH19

MEM_MB_DATA61

AK18

MEM_MB_DATA62

AK16

MEM_MB_DATA63

AH16

MEM_MB_DATA[63..0] 12

Layout:

Place within 1.0'' of APU

VCC_DDR

R138

R138

1KR1%

1KR1%

C116

C116

R139

R139

1KR1%

1KR1%

A A

5

C1000p50X0402

C1000p50X0402

APU_M_VREF

C117

C117

C0.1u10X0402

C0.1u10X0402

C118

C118

Layout:

Place within 1.0'' of APU

C1000p50X0402

C1000p50X0402

4

3

Pull up resistor

VCC_DDR

R153 1KR0402R153 1KR0402

R141 1KR0402R141 1KR0402

MEM_MA_HOT#

MEM_MB_HOT#

2

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

FM2 DDR3 I/F

FM2 DDR3 I/F

FM2 DDR3 I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Kaveri 1.0

Kaveri 1.0

Kaveri 1.0

1

936Monday, January 20, 2014

936Monday, January 20, 2014

936Monday, January 20, 2014

of

of

5

smd.db-x7.ru

FM1 DISPLAY I/F

Note: Several vias on the DP0 interface violate the minimum distance rules

for via to via spacing between diff pairs. These violations have been reviewed and approved

on an individual basis, and pose no significant singal integrity issues for this implementation since

the route lengths are under the maximum allowed spec, and the via distance violations are not severe.

DP0_TX0P16

APU_SIC

C122

C122

X_C10p50N0402

D D

APU_RST#

APU_PWRGD

APU_THERMTRIP#

C C

APU_ALERT#

B B

X_C10p50N0402

Layout: Place within 1.5'' of APU

C136

C136

C180p50N0402

C180p50N0402

VCC_DDR

R152

R152

2

10KR0402

10KR0402

61

Q30A

Q30A

NN-CMKT3904_SOT363-6-RH

NN-CMKT3904_SOT363-6-RH

R162

R162

5

10KR0402

10KR0402

34

Q30B

Q30B

NN-CMKT3904_SOT363-6-RH

NN-CMKT3904_SOT363-6-RH

C137

C137

FCH

DVI-D

C180p50N0402

C180p50N0402

VCC3_SBVCC_DDR

R163

R163

10KR0402

10KR0402

DP0_TX0N16

DP0_TX1P16

DP0_TX1N16

DP0_TX2P16

DP0_TX2N16

DP0_TX3P16

DP0_TX3N16

DP1_TX0P20

DP1_TX0N20

DP1_TX1P20

DP1_TX1N20

DP1_TX2P20

DP1_TX2N20

DP1_TX3P20

DP1_TX3N20

Display Port

FCH_THERMTRIP# 15

FCH_TALERT# 16

C119 C0.1u10X0402C119 C0.1u10X0402

C120 C0.1u10X0402C120 C0.1u10X0402

C121 C0.1u10X0402C121 C0.1u10X0402

C123 C0.1u10X0402C123 C0.1u10X0402

C124 C0.1u10X0402C124 C0.1u10X0402

C125 C0.1u10X0402C125 C0.1u10X0402

C126 C0.1u10X0402C126 C0.1u10X0402

C127 C0.1u10X0402C127 C0.1u10X0402

C128 C0.1u10X0402C128 C0.1u10X0402

C129 C0.1u10X0402C129 C0.1u10X0402

C130 C0.1u10X0402C130 C0.1u10X0402

C131 C0.1u10X0402C131 C0.1u10X0402

C132 C0.1u10X0402C132 C0.1u10X0402

C133 C0.1u10X0402C133 C0.1u10X0402

C134 C0.1u10X0402C134 C0.1u10X0402

C135 C0.1u10X0402C135 C0.1u10X0402

DP2_TX0P_APU19

DP2_TX0N_APU19

DP2_TX1P_APU19

DP2_TX1N_APU19

DP2_TX2P_APU19

DP2_TX2N_APU19

DP2_TX3P_APU19

DP2_TX3N_APU19

APU_CLK14

APU_CLK#14

DISP_CLK14

DISP_CLK#14

APU_SVC7

APU_SVD7

APU_SVT7

APU_SIC34

APU_SID

APU_SID34

APU_RST#

APU_RST#15

APU_PWRGD7,14

APU_PROCHOT#14

APU_PWRGD

PULL UP

VCC_DDR

R176 1KR0402R176 1KR0402

R177 1KR0402R177 1KR0402

R180 300R0402R180 300R0402

R181 300R0402R181 300R0402

R182 1KR0402R182 1KR0402

R183 1KR0402R183 1KR0402

R184 1KR0402R184 1KR0402

R185 1KR0402R185 1KR0402

R186 1KR0402R186 1KR0402

VCC3_ALW

A A

R187 10KR0402R187 10KR0402

TEST2, TEST3, TEST6, TEST10, TEST23, TEST28_H TEST28_L, and any RSVD pins have no connections.

TEST4, TEST5, TEST[17:14], TEST25_H/L,TEST30_H/L, and TEST32_H/L have onboard test points.

APU_SIC_R

APU_SID

APU_RST#

APU_PWRGD

APU_PROCHOT#

APU_ALERT#

APU_THERMTRIP#

FCH_DMA_ACTIVE#

LDTSTOP_L

APU_FM2R1

5

CORETYPE0 CORETYPE1

TN/RD

KV

TBD

TBD

11

0

1

R166 10R0402R166 10R0402

APU_PROCHOT#

APU_THERMTRIP#

APU_ALERT#

1

0

00

4

DP0_TX0P_APU

DP0_TX0N_APU

DP0_TX1P_APU

DP0_TX1N_APU

DP0_TX2P_APU

DP0_TX2N_APU

DP0_TX3P_APU

DP0_TX3N_APU

DP1_TX0P_APU

DP1_TX0N_APU

DP1_TX1P_APU

DP1_TX1N_APU

DP1_TX2P_APU

DP1_TX2N_APU

DP1_TX3P_APU

DP1_TX3N_APU

DP2_TX0P_APU

DP2_TX0N_APU

DP2_TX1P_APU

DP2_TX1N_APU

DP2_TX2P_APU

DP2_TX2N_APU

DP2_TX3P_APU

DP2_TX3N_APU

APU_SVC

APU_SVD

APU_SVT

APU_SIC_RAPU_SIC

CPU_TDI

CPU_TDO

CPU_TCK

CPU_TMS

CPU_TRST_L

CPU_DBRDY

CPU_DBREQ_L

4

ROUTE PCIE AS 85OHM +/-10%

PLACE CAPS WITH APU < 1 INCH

Trace length within 10"

CPU1D

CPU1D

ANALOG/DISPLAY/MISC

ANALOG/DISPLAY/MISC

N4

DP0_TXP0

N5

DP0_TXN0

M2

DP0_TXP1

M3

DP0_TXN1

L2

DP0_TXP2

L1

DP0_TXN2

L4

DP0_TXP3

L5

DP0_TXN3

K2

DP1_TXP0

K3

J2

J1

J4

J5

H2

H3

L7

L8

K5

K6

K8

K9

J7

J8

N7

N8

M5

M6

M8

M9

AL12

AK12

AG12

AF12

C1

C2

D1

AK14

AL14

AF10

AF14

AE10

AH14

AJ14

G11

E10

E11

F11

F10

G10

E9

ZIF-SOCKET906-HF

ZIF-SOCKET906-HF

DP1_TXN0

DP1_TXP1

DP1_TXN1

DP1_TXP2

DP1_TXN2

DP1_TXP3

DP1_TXN3

DP2_TXP0

DP2_TXN0

DP2_TXP1

DP2_TXN1

DP2_TXP2

DP2_TXN2

DP2_TXP3

DP2_TXN3

DP2_TXP4

DP2_TXN4

DP2_TXP5

DP2_TXN5

DP2_TXP6

DP2_TXN6

CLKIN_H

CLKIN_L

DISP_CLKIN_H

DISP_CLKIN_L

SVC

SVD

SVT

SIC

SID

RESET_L

PWROK

PROCHOT_L

THERMTRIP_L

ALERT_L

TDI

TDO

TCK

TMS

TRST_L

DBRDY

DBREQ_L

DISPLAY PORT 0

DISPLAY PORT 0

DISPLAY PORT 2 DISPLAY PORT 1

DISPLAY PORT 2 DISPLAY PORT 1

SER. CLK

SER. CLK

CORETYPE0(FM2:RSVD1)

CORETYPE1(FM2:RSVD2)

JTAG CTRL

JTAG CTRL

For FM2+ colay

DP0_AUXN_C

R178

R178

1.8KR0402

1.8KR0402

Q32

Q32

D

N-2N7002

N-2N7002

D

G

G

S

S

VCC3

R194 0R0402R194 0R0402

R195 0R0402R195 0R0402

VOLT_SELECT VOLT_SELECT

CORETYPE0

CORETYPE1

DP_AUX_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

DP0_AUXP

DP0_AUXN

DP1_AUXP

DP1_AUXN

DP2_AUXP

DP2_AUXN

DP3_AUXP

DP3_AUXN

DISPLAY PORT MISC.

DISPLAY PORT MISC.

DP4_AUXP

DP4_AUXN

DP5_AUXP

DP5_AUXN

DP0_HPD

DP1_HPD

DP2_HPD

DP3_HPD

DP4_HPD

DP5_HPD

TEST4

TEST5

TEST6

TEST9

TEST10

TEST14

TEST15

TEST16

TEST17

TEST18

TEST

TEST

TEST19

TEST20

TEST24

TEST25_H

TEST25_L

TEST28_H

TEST28_L

TEST30_H

TEST30_L

TEST31

TEST32_H

TEST32_L

TEST35

FM2R2(FM2:FM2R1)

DMAACTIVE_L

LDTSTOP_L

MISC

MISC

BP5/IDLEEXIT_L

RSVD1(FM2:CORETYPE)

RSVD3

RSVD4

RSVD6

RSVD7

RSVD8

VDDP_SENSE

VDDNB_SENSE

VDDIO_SENSE

VDD_SENSE

SENSE RSVD

SENSE RSVD

VDDR_SENSE

VSS_SENSE

Q33

Q33

D

D

G

G

S

S

N-2N7002

N-2N7002

R188 20KR0402-2R188 20KR0402-2

3

DP_AUX_ZVSS

G9

APU_BLON

F8

APU_DIGON

G8

APU_BLPWM

E8

E1

E2

F1

F2

G1

G2

E5

E6

F5

F6

G5

G6

E3

F3

G3

DP3_HPD

E7

DP4_HPD

F7

DP5_HPD

G7

APU_TEST4

T21

APU_TEST5

U21

APU_TEST6

AD14

APU_TEST9

P21

APU_TEST10

R21

APU_TEST14

F12

APU_TEST15

E12

APU_TEST16

F13

APU_TEST17

E13

APU_TEST18

G13

APU_TEST19

G14

APU_TEST20

F14

APU_TEST24

E14

APU_TEST25_H

AJ11

APU_TEST25_L

AH11

APU_TEST28_H

H10

APU_TEST28_L

J10

APU_TEST30_H

T22

APU_TEST30_L

U22

APU_TEST31

AG31

APU_TEST32_H

V22

APU_TEST32L

R22

APU_TEST35

AE14

APU_FM2R1

AC10

FCH_DMA_ACTIVE#

AG14

AD10

G12

CORETYPE0

AJ13

CORETYPE1

AH13

F9

AD12

K23

AB23

AC24

AG10

VDDP_SENSE

C3

A3

A4

B3

VDDR_SENSE

C4

R174 0R0402R174 0R0402

B4

R175 0R0402R175 0R0402

DP0_AUXP_C

R179

R179

1.8KR0402

1.8KR0402

CORE TYPE LOGIC

R189 10KR0402R189 10KR0402

5

2

Q34

Q34

NN-CMKT3904_SOT363-6-RH

NN-CMKT3904_SOT363-6-RH

4

6

1

3

3

2

HDT+ Connector

R143 0R0402R143 0R0402

R144 10KR0402R144 10KR0402

R145 10KR0402R145 10KR0402

R146 10KR0402R146 10KR0402

Q29A

Q29A

NN-CMKT3904_SOT363-6-RH

NN-CMKT3904_SOT363-6-RH

VCC_DDR

R167

R167

1KR0402

1KR0402

B

Q31

Q31

X_N-SST3904_SOT23

X_N-SST3904_SOT23

VCC_DDR

J1

J1

1

CPU_VDDIO

3

GND

5

GND

7

GND

CPU_TRST_L9CPU_PWROK_BUF

CPU_DBRDY311CPU_RST_L_BUF

CPU_DBRDY213CPU_DBRDY0

CPU_DBRDY115CPU_DBREQ_L

17

GND

CPU_VDDIO19CPU_PLLTEST1

H2X10SM-1.27PITCH_BLUE-RH

H2X10SM-1.27PITCH_BLUE-RH

VCC3 VCC3

R150

R150

2

10KR0402

10KR0402

APU_PWROK_BUFAPU_PWRGD APU_LDT_RST_BUF

61

R168

R168

X_10KR0402

X_10KR0402

CE

SCAN Conn,

APU_TEST18

APU_TEST19

APU_TEST24

APU_TEST20

Layout: Place within 1.5'' of APU

R142 150R1%0402R142 150R1%0402

FCH

DVI-D

CPU_TRST_L

FCH

FM_IDLEEXIT_L

DP0_AUXP_C 16

DP0_AUXN_C 16

DP1_AUXP_C 20

DP1_AUXN_C 20

DP2_AUXP_C 19

DP2_AUXN_C 19

R147 100KR0402R147 100KR0402

R148 100KR0402R148 100KR0402

R149 100KR0402R149 100KR0402

TP2TP2

TP3TP3

TP4TP4

TP5TP5

TP6TP6

R701 X_1KR0402R701 X_1KR0402

TP8TP8

R776 X_1KR0402R776 X_1KR0402

R662 X_1KR0402R662 X_1KR0402

R154 1KR0402R154 1KR0402 R155

R156 1KR0402R156 1KR0402

R157 1KR0402R157 1KR0402

R158 1KR0402R158 1KR0402

R159 511R1%0402R159 511R1%0402

R160 511R1%0402R160 511R1%0402

TP11TP11

TP12TP12

TP13TP13

TP14TP14

R161 39.2R1%0402R161 39.2R1%0402

TP15TP15

TP16TP16

R164 X_300R0402R164 X_300R0402

R165 300R0402R165 300R0402

LDTSTOP_L

FM_IDLEEXIT_L

NB_SENSE+ 7

VDDIOFB+ 33

COREFB+ 7

COREFB- 7

NB_SENSE- 7

FCH

DVI-D

Display Port

APU_FM2R1 7,33

FCH_DMA_ACTIVE# 14

LDTSTOP_L 14

TP17TP17

TP18TP18

DP0_HPD_VGA_C 16

DP1_HPD_DVI_C 20

DP2_HPD_DP_C 19

CPU_VDDP

VCC_DDR

H:HDMI ENABLE

Display Port

WARM RESET

APU_RST#

GPU DEBUG

TP28TP28

TP29TP29

TP55TP55

VCC3

R193

R193

10KR0402

10KR0402

VOLT_SELECT

VOLT_SELECT 13,19,32,33

2

1

CPU_TCK

2

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TDO

CPU_PLLTEST0

APU_RST#

R155

0R0402

0R0402

VCC_DDR

FCH_IDLEEXIT_L 16

APU_BLON

APU_DIGON

APU_BLPWM

DP0_HPD_VGA_C

VDDIOFB+

COREFB+

NB_SENSE+

Title

Title

Title

FM2 DISPLAY/MSIC

FM2 DISPLAY/MSIC

FM2 DISPLAY/MSIC

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Kaveri 1.0

Kaveri 1.0

Kaveri 1.0

Date: Sheet

Date: Sheet

Date: Sheet

CPU_TMS

4

CPU_TDI

6

CPU_TDO

8

APU_PWROK_BUF

10

APU_LDT_RST_BUF

12

CPU_DBRDY

14

CPU_DBREQ_L

16

APU_TEST19

18

APU_TEST18

20

R151

R151

5

10KR0402

10KR0402

34

Q29B

Q29B

NN-CMKT3904_SOT363-6-RH

NN-CMKT3904_SOT363-6-RH

Layout: Place close to HDT header

R169 1KR0402R169 1KR0402

R170 1KR0402R170 1KR0402

R171 1KR0402R171 1KR0402

R172 1KR0402R172 1KR0402

R173 1KR0402R173 1KR0402

TP19TP19

TP20TP20

TP21TP21

TP22TP22

TP23TP23

TP24TP24

TP25TP25

TP26TP26

TP27TP27

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

1

CPU_TDI

CPU_TCK

CPU_TMS

CPU_TRST_L

CPU_DBREQ_L

10 36Saturday, January 18, 2014

10 36Saturday, January 18, 2014

10 36Saturday, January 18, 2014

of

of

of

5

smd.db-x7.ru

4

3

2

1

BOTTOM SIDE DECOUPLING

VCCP

C697,C700,C705,C710 change to ASM-5010

C148

C144

C144

C145

C138

C138

D D

C22u6.3X50805-RH

C22u6.3X50805-RH

VCCP

C160

C160

C10u6.3X50805

C10u6.3X50805

VCCP

C619

C619

C180p50N0402

C180p50N0402

CPU_VDDNB

C C

C174

C174

C22u6.3X50805-RH

C22u6.3X50805-RH

VCC_DDR

C192

C192

C22u6.3X50805-RH

C22u6.3X50805-RH

CPU_VDDP

Layout: Place close to Pins

B B

AH10,AJ10,AK10,AL10

C194

C194

C22u6.3X5-HF

C22u6.3X5-HF

CPU_VDDR

Layout: Place close to Pins

AH11,AJ11,AK11,AL11

C210

C210

C22u6.3X50805-RH

C22u6.3X50805-RH

C187

C187

C186

C186

C145

C139

C139

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C162

C162

C163

C163

C161

C161

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

VCCP

C615

C615

C688

C688

C180p50N0402

C180p50N0402

C180p50N0402

C180p50N0402

C175

C175

C143

C143

C176

C176

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

VCC_DDR

C199

C199

C200

C200

C207

C207

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C196

C196

C197

C197

C195

C195

C10u6.3X5-HF

C10u6.3X5-HF

C10u6.3X5-HF

C10u6.3X5-HF

C22u6.3X5-HF

C22u6.3X5-HF

C213

C213

C211

C211

C212

C212

C0.22u16X

C0.22u16X

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

VDDA_25VDDA25

FB1

FB1

30L3A-30_0603-HF

30L3A-30_0603-HF

C188

C188

C148

C146

C146

C147

C147

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C164

C164

C165

C165

C166

C166

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C620

C620

C673

C673

C676

C676

C180p50N0402

C180p50N0402

C180p50N0402

C180p50N0402

C180p50N0402

C180p50N0402

CPU_VDDNB CPU_VDDNB CPU_VDDNB CPU_VDDNB CPU_VDDNB CPU_VDDNB CPU_VDDNB

C185

C185

C184

C184

C22u6.3X50805-RH

C22u6.3X50805-RH

C201

C201

C10u6.3X50805

C10u6.3X50805

C171

C171

C0.22u16X

C0.22u16X

C214

C214

C0.22u16X

C0.22u16X

C216

C216

C22u6.3X50805-RH

C22u6.3X50805-RH

C190

C190

C4.7u6.3X50805

C4.7u6.3X50805

C191

C191

C172

C172

C0.22u16X

C0.22u16X

C1000p50X0402

C1000p50X0402

CPU_VDDR

C222

C222

C215

C215

C0.22u16X

C0.22u16X

C151

C151

C149

C149

C150

C150

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C453

C453

C443

C443

C447

C447

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C154

C154

C152

C152

C153

C153

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C457

C457

C10u6.3X50805

C10u6.3X50805

C618

C618

C685

C685

C686

C686

C180p50N0402

C180p50N0402

C180p50N0402

C180p50N0402

C180p50N0402

C180p50N0402

C178

C178

C179

C10u6.3X50805

C10u6.3X50805

C786

C786

C4.7u6.3X50805

C4.7u6.3X50805

CPU_VDDP

C218

C218

C179

C4.7u6.3X50805

C4.7u6.3X50805

C219

C219

C220

C220

C180p50N0402

C180p50N0402

C180p50N0402

C180p50N0402

C177

C177

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C10u6.3X50805

C193

C193

C796

C796

C4.7u6.3X50805

C4.7u6.3X50805

C4.7u6.3X50805

C4.7u6.3X50805

C206

C206

C1000p50X0402

C1000p50X0402

C223

C223

C180p50N0402

C180p50N0402

C180p50N0402

C180p50N0402

VCCP

C155

C155

C156

C156

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

VCCP

C458

C458

C181

C181

C180

C180

C0.22u16X

C0.22u16X

C0.22u16X

C0.22u16X

Place across each VDDIO-GND plane seam

VCC_DDR VCC_DDRVCC_DDR

C167

C167

C0.22u16X

C0.22u16X

C221

C221

C180p50N0402

C180p50N0402

C180p50N0402

C180p50N0402

CPU1H

VCCP VCCP

CPU1E

CPU1E

VDD

VDD

AA11

AA13

AA21

AB10

AB14

AB16

AB18

AC11

AC13

AC19

AC21

AC17

AB22

AB24

AB27

AB30

AC23

AC25

AC28

AC31

AA26

AA23

AA29

MEC1

MEC2

MEC3

MEC4

AB7

Y20

M10

P10

T20

W11

AA3

AA6

AB1

AB4

AD1

AE3

AF4

AF7

AG6

AH7

H12

H14

H8

J11

J13

J15

J17

J19

J21

J9

K10

K12

K14

U13

K16

Y18

K18

K20

K4

L3

L11

L15

K27

J29

U25

T30

V29

L28

L31

M22

M23

M26

N24

N27

N30

P22

U31

W24

V23

V26

U28

P25

P28

P31

R23

R26

R29

T24

W27

L25

W30

Y22

Y25

Y28

K24

K30

Y31

J26

M29

T27

VDD-1

VDD-2

VDD-3

VDD-4

VDD-5

VDD-6

VDD-7

VDD-8

VDD-9

VDD-10

VDD-11

VDD-12

VDD-13

VDD-14

VDD-15

VDD-16

VDD-17

VDD-18

VDD-19

VDD-20

VDD-21

VDD-22

VDD-23

VDD-24

VDD-25

VDD-26

VDD-27

VDD-28

VDD-29

VDD-30

VDD-31

VDD-32

VDD-33

VDD-34

VDD-35

VDD-36

VDD-37

VDD-38

VDD-39

VDD-40

VDD-41

VDD-42

VDD-43

VDD-44

VDD-45

VDD-46

VDD-47

VDD-48

VDD-49

VDD-50

ZIF-SOCKET906-HF

ZIF-SOCKET906-HF

CPU1F

CPU1F

VDDIO-1

VDDIO-2

VDDIO-3

VDDIO-4

VDDIO-5

VDDIO-6

VDDIO-7

VDDIO-8

VDDIO-9

VDDIO-10

VDDIO-11

VDDIO-12

VDDIO-13

VDDIO-14

VDDIO-15

VDDIO-16

VDDIO-17

VDDIO-18

VDDIO-19

VDDIO-20

VDDIO-21

VDDIO-22

VDDIO-23

VDDIO-24

VDDIO-25

VDDIO-26

VDDIO-27

VDDIO-28

VDDIO-29

VDDIO-30

VDDIO-31

VDDIO-32

VDDIO-33

VDDIO-34

VDDIO-35

VDDIO-36

VDDIO-37

VDDIO-38

VDDIO-39

VDDIO-40

VDDIO-41

VDDIO-42

VDDIO-43

VDDIO-44

VDDIO-45

VDDIO-46

VDDIO-47

VDDIO-48