Page 1

5

4

3

2

1

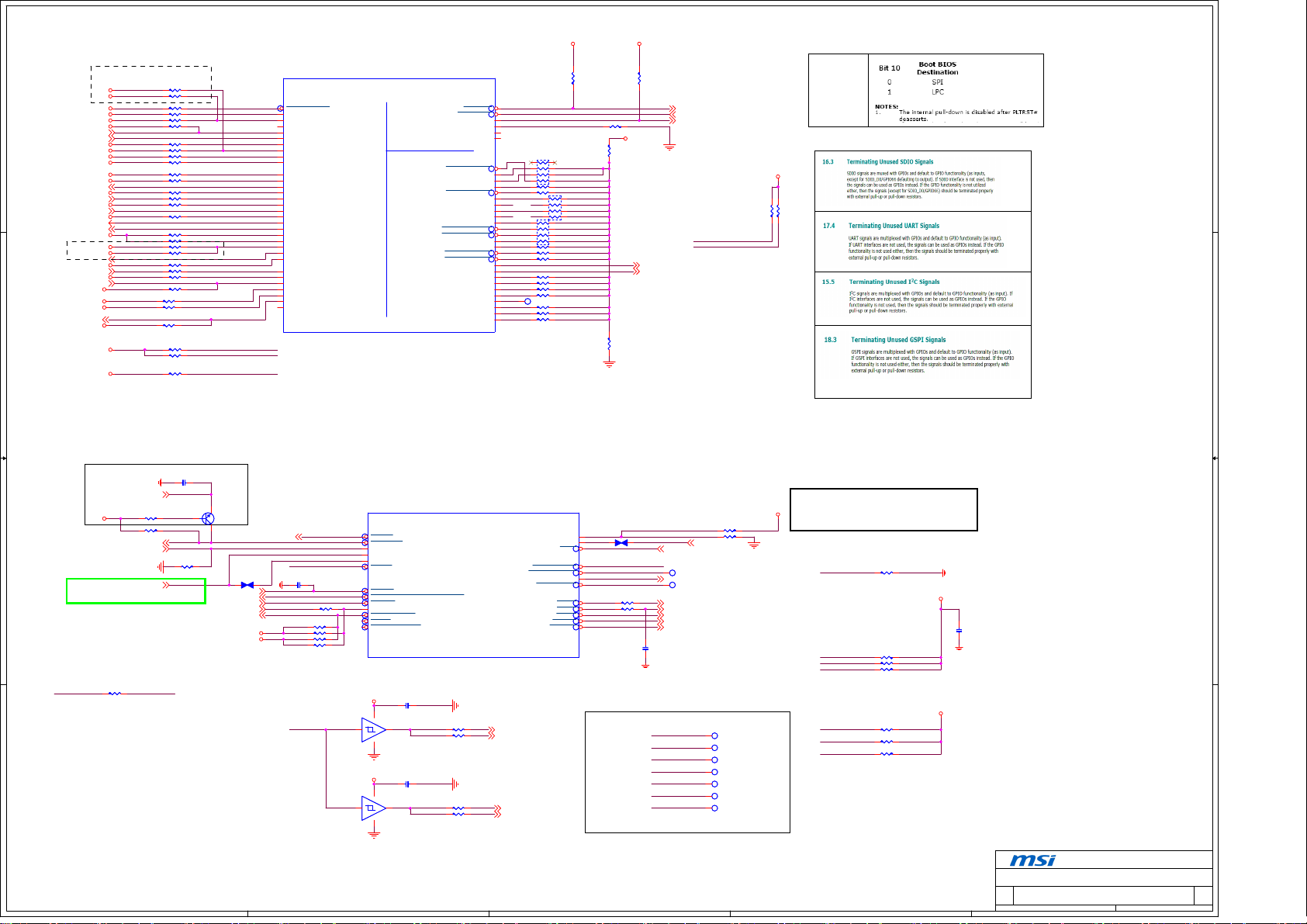

PageTitle

Cover Sheet 1

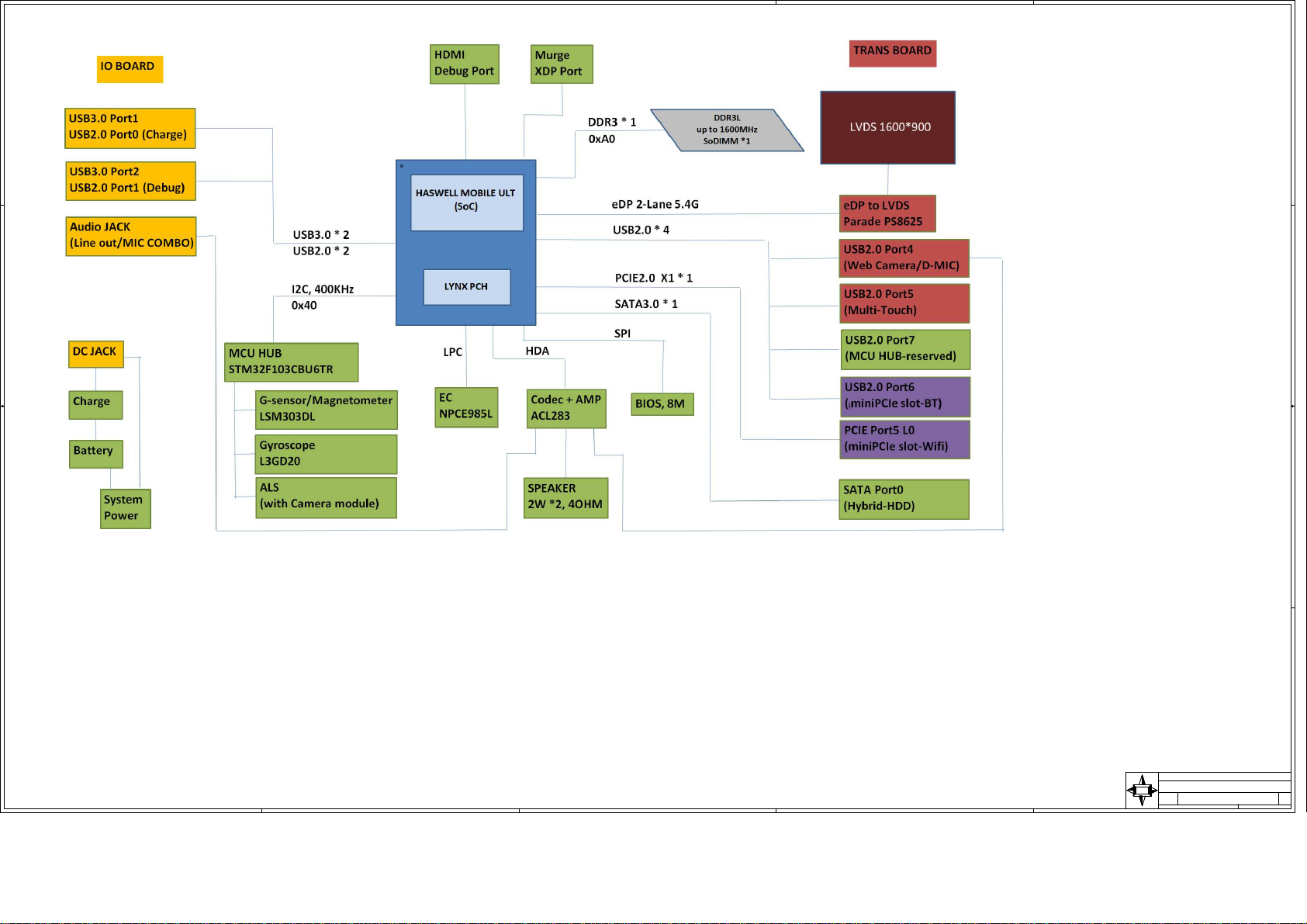

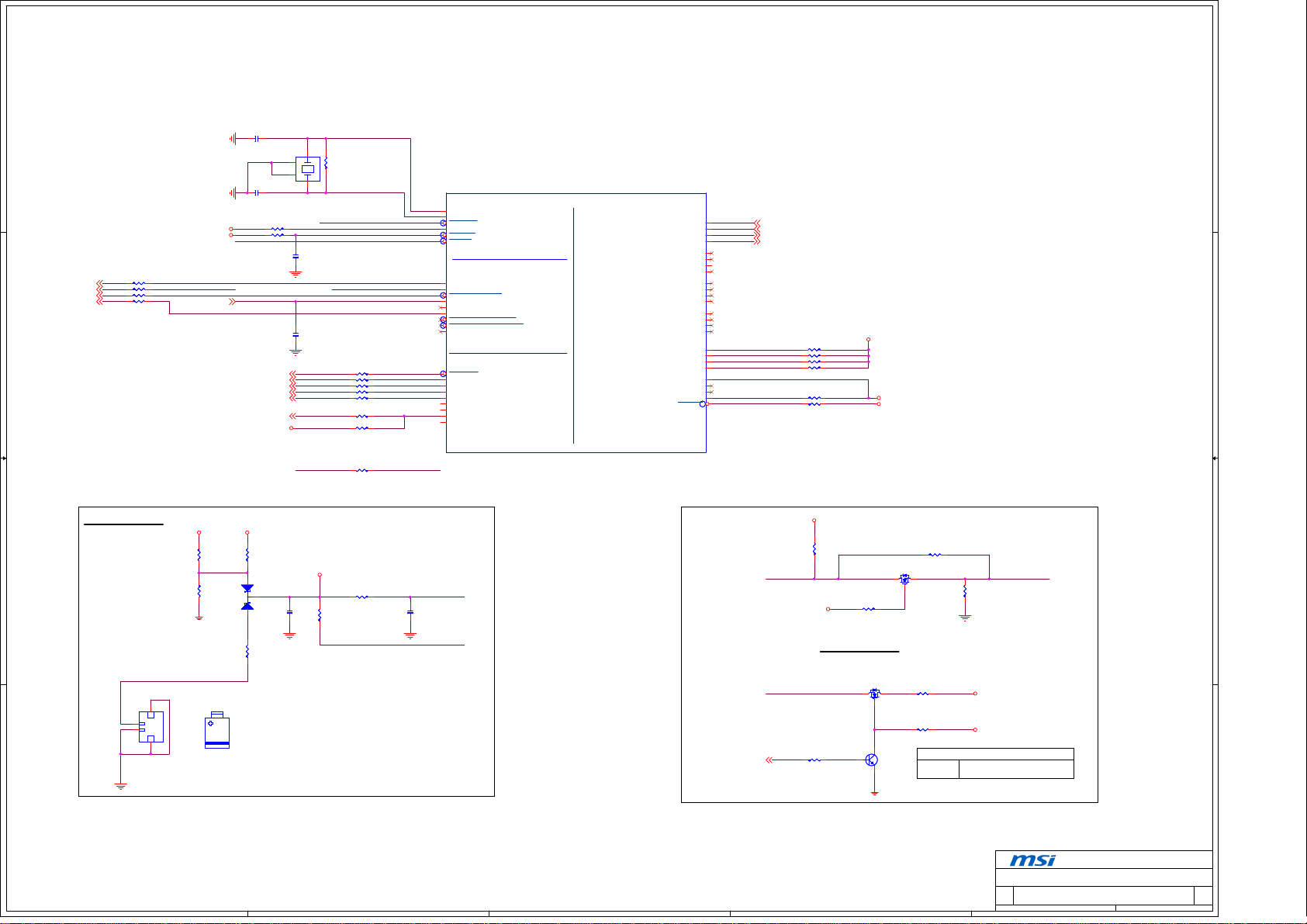

Block Diagram 2

INTEL-HASWELL and LYNX POINT (SoC)

DDR III DIMM

D D

Audio Codec-ALC283

EC NPCE985LCE

USB 3.0

USB2.0

SIDE IO BOARD

TRANSFORM BOARD

mini PCI-E/SATA

MCU and Sensor

CHARGE/Battery select

C C

POWER MAP

System Power

DDR Power

ACPI

+VCC_CORE ISL95813

+VTT_CORE ISL95870

FAN Control

MSIC

GPIO Table

B B

SMBUS Table

POWER Sequence and RESET Map

HISTORY

3 - 14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

Beta

MS-7859

CPU:

INTEL Haswell ULT (BGA 1068)

System Chipset:

NA

OnBoard Chipset:

Audio Codec and AMPLIFIER REALTEK/ALC283

SIO - NUVOTON/NPCE985LCE

eDP to LVDS converter: Parade PS8625

Flash ROM: 64 Mb SPI (CHIP)

Main Memory:

DDR3L * 1 (Single Channel)

Expansion Slots:

Mini PCI-e (X1) * 1

SATA * 1

PWM:

Controller: Intersil /ISL95813 1+1 phase

Other:

USB3.0 *2 (IO board)

USB2.0 (Pin header for Web cam, Touch)

eDP*1

Ver: 1.0

A A

MICRO-STAR INT'L CO., LTD.

MICRO-STAR INT'L CO., LTD.

MICRO-STAR INT'L CO., LTD.

MS-7859

MS-7859

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

C

C

C

Wednesday, July 03, 2013

Wednesday, July 03, 2013

5

4

3

2

Wednesday, July 03, 2013

Cover Sheet

Cover Sheet

Cover Sheet

MS-7859

1

0.2

0.2

1 36

1 36

1 36

0.2

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

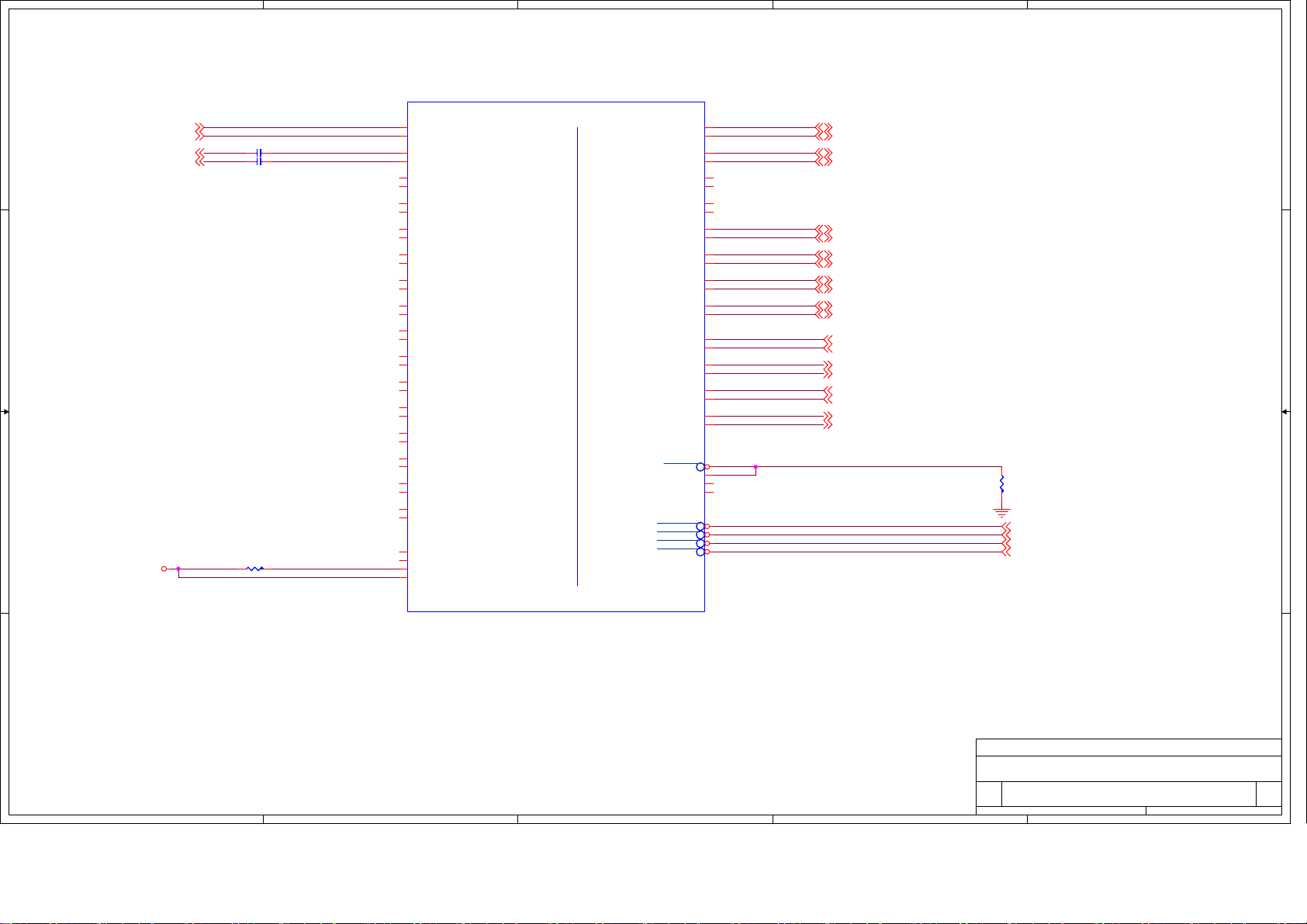

Page 2

5

D D

C C

4

3

2

1

B B

A A

MICRO-STAR INT'L CO., LTD.

MICRO-STAR INT'L CO., LTD.

MICRO-STAR INT'L CO., LTD.

MS-7859ci20313

MS-7859

Wednes day, July 03, 20 13

Wednes day, July 03, 20 13

Wednes day, July 03, 20 13

1

Block Diagram

Block Diagram

Block Diagram

MS-7859

Sheet ofDate:

2 36

Sheet ofDate:

2 36

Sheet ofDate:

2 36

MSI

MSI

MSI

Size Document D escription Rev

Size Document D escription Rev

Size Document D escription Rev

D

D

5

4

3

2

D

0.2

0.2

0.2

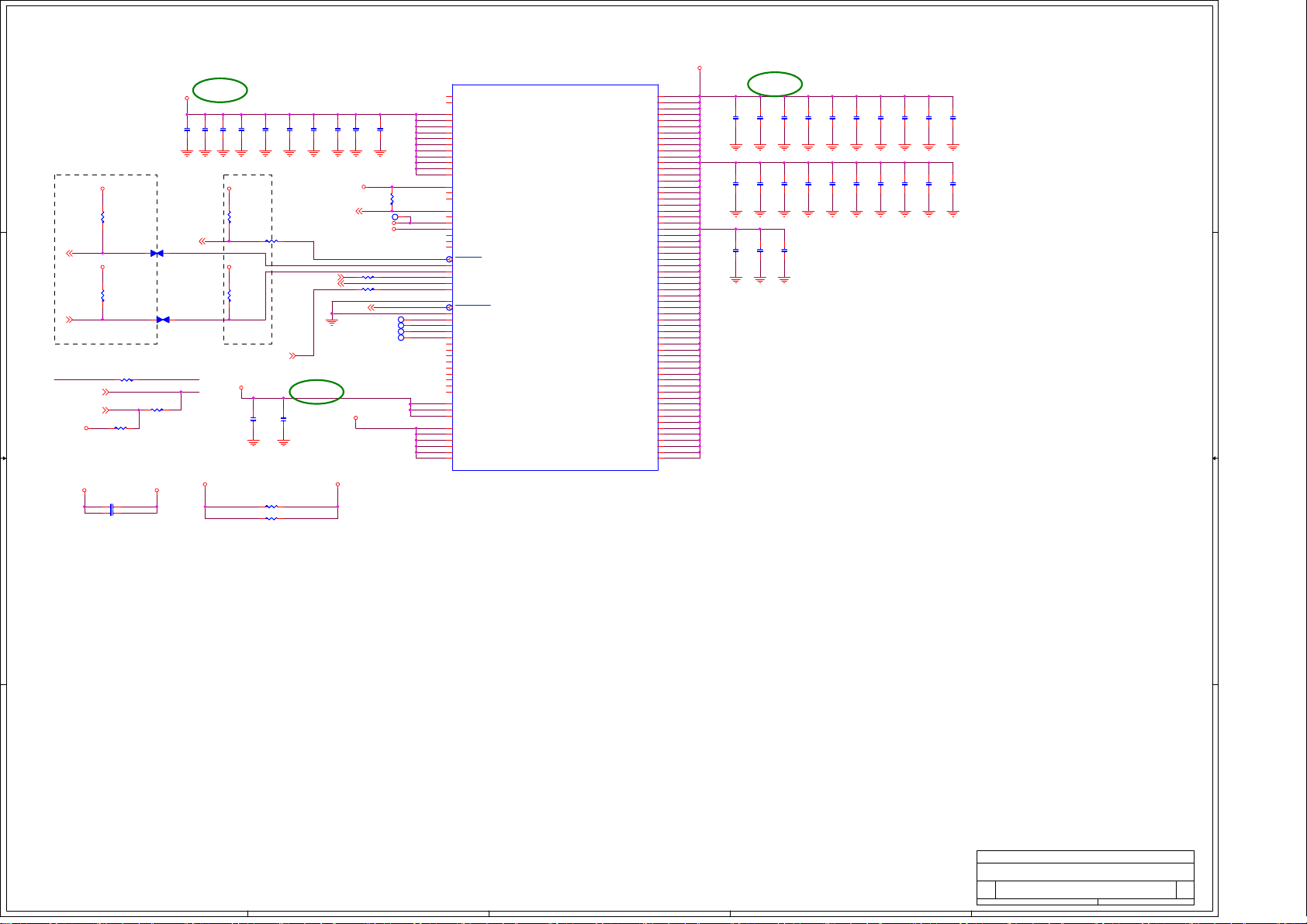

Page 3

A

HSW_ULT_DDR3L

U2A

U2A

HSW_ULT_DDR3L

B

C

D

E

DP1_TX0N_HDMI

DP1_TX0P_HDMI

DP1_TX1N_HDMI

DP1_TX1P_HDMI

DP1_TX2N_HDMI

DP1_TX2P_HDMI

DP1_TXCN_HDMI

4 4

DP1_TXCP_HDMI

3 3

2 2

C24 C0.1u10X0402C24 C0.1u10X0402

C19 C0.1u10X0402C19 C0.1u10X0402

C30 C0.1u10X0402C30 C0.1u10X0402

C31 C0.1u10X0402C31 C0.1u10X0402

C28 C0.1u10X0402C28 C0.1u10X0402

C29 C0.1u10X0402C29 C0.1u10X0402

C26 C0.1u10X0402C26 C0.1u10X0402

C27 C0.1u10X0402C27 C0.1u10X0402

+VCC3

DP1_TX0N_HDMI_R

DP1_TX0P_HDMI_R

DP1_TX1N_HDMI_R

DP1_TX1P_HDMI_R

DP1_TX2N_HDMI_R

DP1_TX2P_HDMI_R

DP1_TXCN_HDMI_R

DP1_TXCP_HDMI_R

EDP_BKLCTL21

EDP_BKLEN21

EDP_VDDEN21

RN7 8P4R-10KR0402RN7 8P4R-10KR0402

1

2

3

4

5

6

7

8

RN6 8P4R-10KR0402RN6 8P4R-10KR0402

1

2

3

4

5

6

7

8

R401 10KR0402R401 10KR0402

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

B8

A9

C6

U6

P4

N4

N2

AD4

U7

L1

L3

R5

L4

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

U2I

U2I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

eDP SIDEBAND

eDP SIDEBAND

PCIE

PCIE

HSW_ULT_DDR3L

HSW_ULT_DDR3L

1 OF 19

1 OF 19

9 OF 19

9 OF 19

EDPDDI

EDPDDI

DISPLAY

DISPLAY

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

B9

C9

D9

D11

C5

B6

B5

A6

C8

A8

D6

EDP_TXN0 21

EDP_TXP0 21

EDP_TXN1 21

EDP_TXP1 21

EDP_AUXN 21

EDP_COMP

EDP_DISP_UTIL

EDP_AUXP 21

R325 24.9R1%0402R325 24.9R1%0402 C23

TPJNC13TPJNC13

+VCCIOA_OUT

for Debug

+VCC5

L2 30L1.7A-50_0402-RHL2 30L1.7A-50_0402-RH

Cost reduce level shift

DP1_HPD

EDP_HPD

HDMI_DDC_CLK

HDMI_DDC_DATA

EDP_HPD 21

+VCC5

change from 604R to 499R, pericom recommanded

R24 680R1%0402R24 680R1%0402

R22 680R1%0402R22 680R1%0402

R20 680R1%0402R20 680R1%0402

R21 680R1%0402R21 680R1%0402

R18 680R1%0402R18 680R1%0402

R19 680R1%0402R19 680R1%0402

R16 680R1%0402R16 680R1%0402

R17 680R1%0402R17 680R1%0402

DS

Q6

Q6

G

N-2N7002_SOT23

C32

C32

C0.1u16Y0402

C0.1u16Y0402

N-2N7002_SOT23

R169

R169

2.2KR0402

2.2KR0402

HDMI_DDC_DATA

HDMI_DDC_CLK

DP1_HPD HDMI_HPD

+VCC3

R181

R181

2.2KR0402

2.2KR0402

1MR0402

1MR0402

DP1_TX0N_HDMI

DP1_TX0P_HDMI

DP1_TX1N_HDMI

DP1_TX1P_HDMI

DP1_TX2N_HDMI

DP1_TX2P_HDMI

DP1_TXCN_HDMI

DP1_TXCP_HDMI

R38

R38

G

G

+VCC3

G

HDMI_CTRLDATA

DS

Q30

Q30

N-2N7002_SOT23

N-2N7002_SOT23

HDMI_CTRLCLK

DS

Q31

Q31

N-2N7002_SOT23

N-2N7002_SOT23

DS

Q5

Q5

N-2N7002_SOT23

N-2N7002_SOT23

VDD_5V0_HDMI_F

C18

C18

C0.1u16X0402

C0.1u16X0402

GNDGND

2013.05.15

remove HDMI connector

+VCC5+VCC3

R160

R160

2.2KR0402

2.2KR0402

R30

R30

20KR0402

20KR0402

5MM

0.1A

C23

C1u10X50402-HF

C1u10X50402-HF

R159

R159

2.2KR0402

2.2KR0402

HDMI_HPD

HDMI_CTRLDATA

HDMI_CTRLCLK

DP1_TXCN_HDMI

DP1_TXCP_HDMI

DP1_TX2N_HDMI

DP1_TX2P_HDMI

DP1_TX1N_HDMI

DP1_TX1P_HDMI

DP1_TX0N_HDMI

DP1_TX0P_HDMI

GND

1 1

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

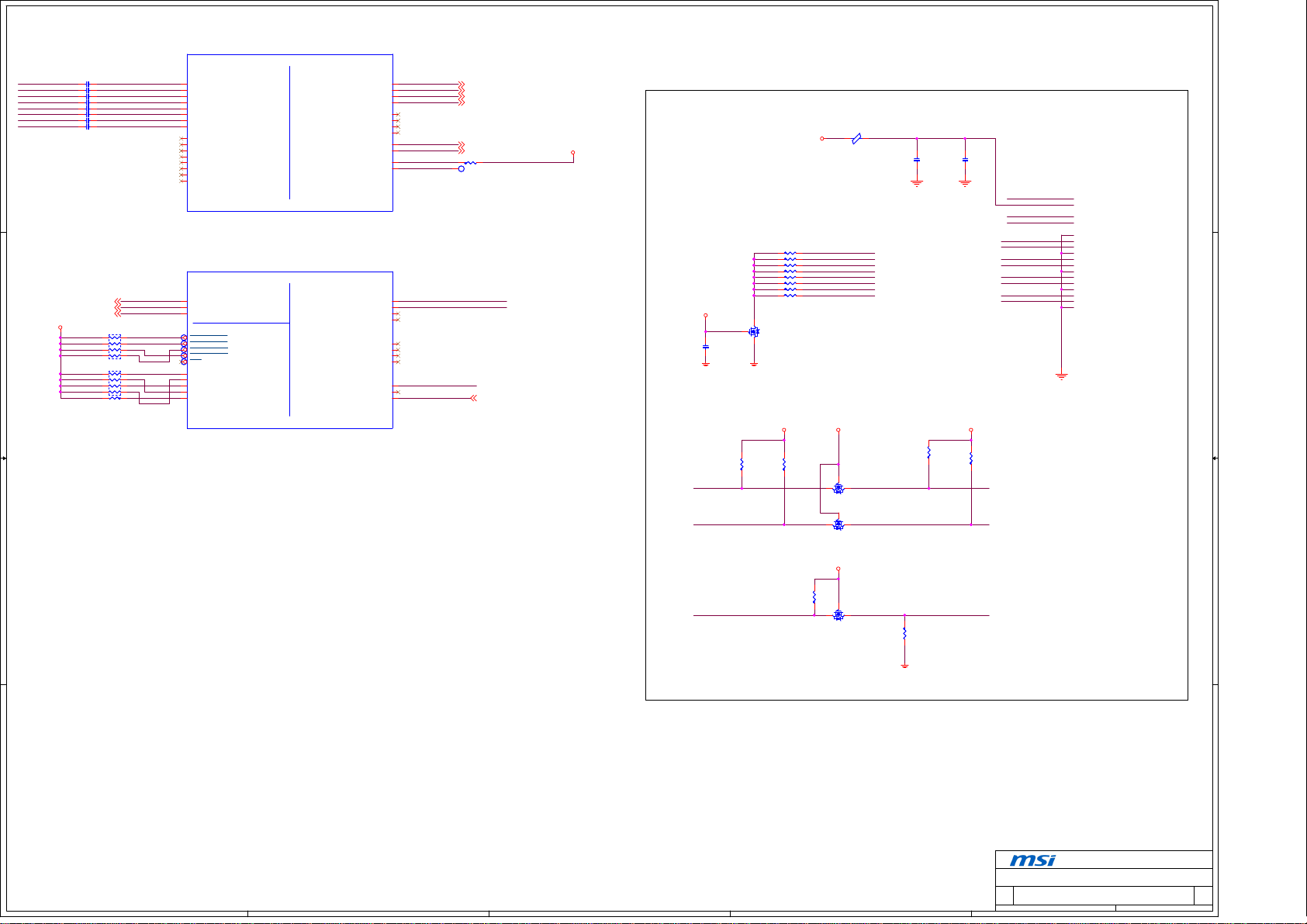

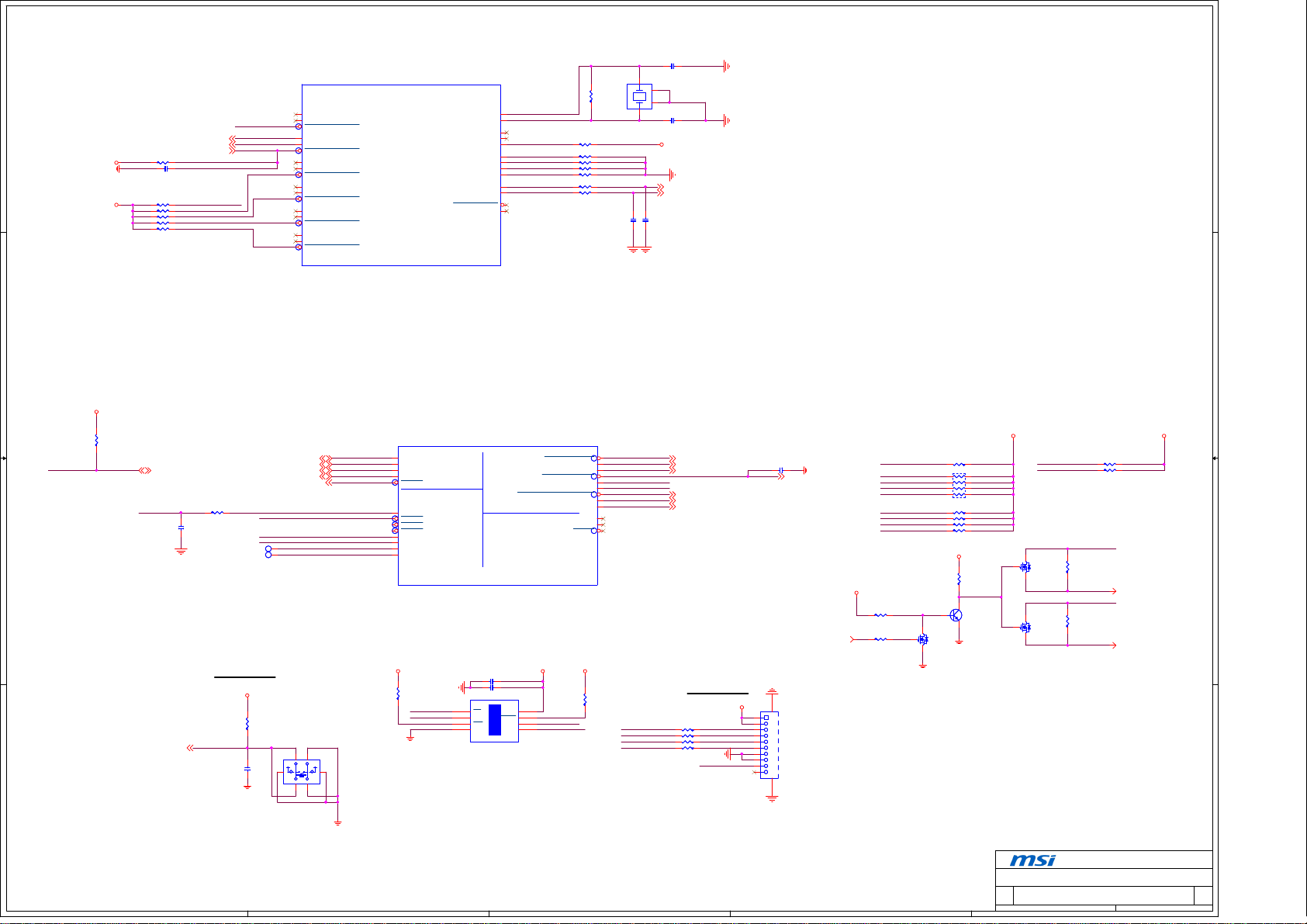

HASWELL ULT (EDP & HDMI)

HASWELL ULT (EDP & HDMI)

HASWELL ULT (EDP & HDMI)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

C

C

C

MS-7859

MS-7859

MS-7859

Date: Sheet of

Date: Sheet of

A

B

C

D

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

3 36Wednesday, July 03, 2013

3 36Wednesday, July 03, 2013

E

3 36Wednesday, July 03, 2013

0.2

0.2

0.2

Page 4

A

U2C

M_A_DQ[63:0]15

4 4

3 3

2 2

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

U2C

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

B

HSW_ULT_DDR3L

HSW_ULT_DDR3L

DDR CHANNEL A

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

C

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_CLK_DDR#0 15

M_A_CLK_DDR0 15

M_A_CLK_DDR#1 15

M_A_CLK_DDR1 15

M_A_CKE0 15

M_A_CKE1 15

M_A_CS#0 15

M_A_CS#1 15

M_A_RAS# 15

M_A_WE# 15

M_A_CAS# 15

M_A_BS0 15

M_A_BS1 15

M_A_BS2 15

M_A_A[15:0] 15

M_A_DQS#[7:0] 15

M_A_DQS[7:0] 15

C214

C214

C0.022u10X0402-HF

C0.022u10X0402-HF

M_VREF_CA_DIMMA 15

M_VREF_DQ_DIMMA 15

C213

C213

C0.022u10X0402-HF

C0.022u10X0402-HF

D

E

R227

R235

R235

24.9R1%0402

1 1

A

3 OF 19

3 OF 19

B

C

24.9R1%0402

R227

24.9R1%0402

24.9R1%0402

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

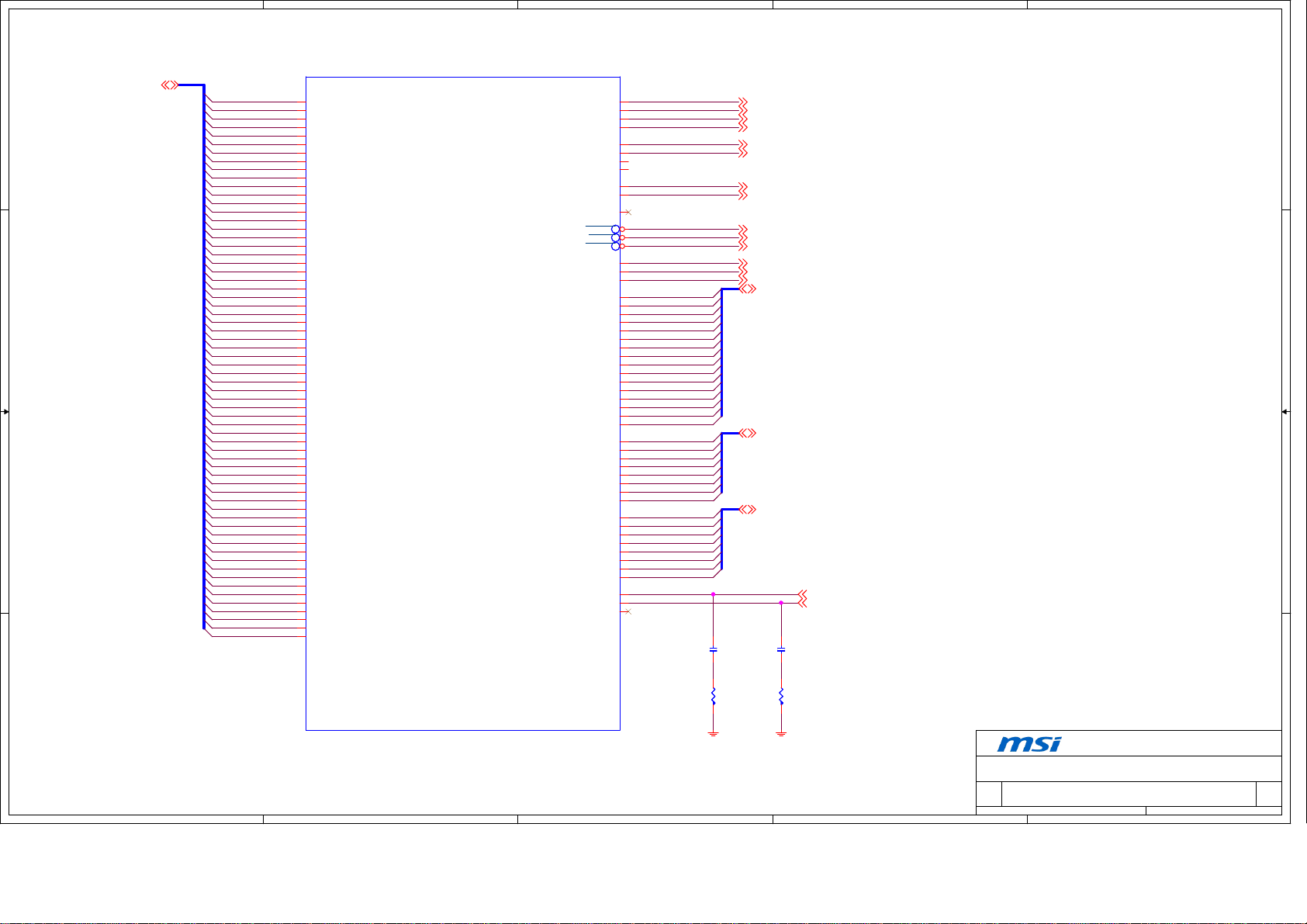

HASWELL ULT (DDR3L)CHA

HASWELL ULT (DDR3L)CHA

HASWELL ULT (DDR3L)CHA

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

MS-7859

MS-7859

MS-7859

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

4 36Wednesday, July 03, 2013

4 36Wednesday, July 03, 2013

4 36Wednesday, July 03, 2013

E

0.2

0.2

0.2

Page 5

A

U2D

U2D

B

HSW_ULT_DDR3L

HSW_ULT_DDR3L

C

D

E

AY31

SB_DQ0

AW31

4 4

3 3

2 2

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

DDR CHANNEL B

DDR CHANNEL B

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

1 1

A

4 OF 19

4 OF 19

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

HASWELL ULT (DDR3L)CHB

HASWELL ULT (DDR3L)CHB

HASWELL ULT (DDR3L)CHB

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

MS-7859

MS-7859

MS-7859

Date: Sheet of

Date: Sheet of

B

C

D

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

5 36Wednesday, July 03, 2013

5 36Wednesday, July 03, 2013

5 36Wednesday, July 03, 2013

E

0.2

0.2

0.2

Page 6

A

B

C

D

E

4 4

2013.03.28

Intel MOW change to 50K OHM crystal

RTCVCC

RTCVCC

AZ_BITCLK16

AZ_SYNC16

AZ_RST#16

3 3

2 2

1 1

R59 33R0402R59 33R0402

R328 33R0402R328 33R0402

R61 33R0402R61 33R0402

R55 33R0402R55 33R0402

RTC Circuit

2

1

HDA_SYNC_PCH_R

AZ_SDIN016AZ_SDOUT16

+ATX_5VSB +FATX_3VSB

R594

R594

X_1KR1%0402

X_1KR1%0402

SD_53261_0210_2P

SD_53261_0210_2P

N32-1020730-A81

N32-1020730-A81

BH1X2#S-1.25PITCH_WHITE-RH-3

BH1X2#S-1.25PITCH_WHITE-RH-3

BAT_X1

BAT_X1

65

R595

R595

X_2KR1%0402

X_2KR1%0402

C96

C96

C15p50N

C15p50N

Y2

32.768KHzY232.768KHz

C97

C97

C15p50N

C15p50N

R64 330KR0402R64 330KR0402

R359 20KR0402-2R359 20KR0402-2

XDP_TRST#8

XDP_TCLK18

XDP_TDI8

XDP_TDO8

XDP_TMS8

XDP_TCLK8

+VTT_CORE

R596

R596

0R0402

0R0402

D20

D20

S-BAT54C_SOT23

S-BAT54C_SOT23

Y

Z

X

RTC_P2

R152

R152

1KR0402

1KR0402

RTC_P3

BAT1

BAT1

BAT-BT-CR2032-RH

BAT-BT-CR2032-RH

RTCX1JNC

R73

R73

3

10MR1%0402

10MR1%0402

2

1 4

RTCX2JNC

SM_INTRUDER#

PCH_INTVRMEN

SRTCRST#

RTCRST#

C315

C315

C1u16Y0603

C1u16Y0603

HDA_BIT_CLK_PCH_R

HDA_SYNC_PCH

HDA_RST#_PCH_R

AZ_SDIN0

HDA_SDOUT_PCH_R

C79

C79

X_C10p50N0402

X_C10p50N0402

R190 X_0R0402R190 X_0R0402

R34 X_0R0402R34 X_0R0402

R45 X_0R0402R45 X_0R0402

R209 X_0R0402R209 X_0R0402

R195 X_0R0402R195 X_0R0402

R35 X_0R0402R35 X_0R0402

R40

R40

XDP_TDI PCH_TDO

R41 X_0R0402R41 X_0R0402

RTCVCC

R487 20KR0402R487 20KR0402

C417

C417

R486

R486

1MR0402

1MR0402

C1u16X0603

C1u16X0603

X_1KR1%0402

X_1KR1%0402

PCH_TRST#

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

AW5

AY5

AU6

AV7

AV6

AU7

AW8

AV11

AU8

AY10

AU12

AU11

AW10

AV10

AY8

AU62

AE62

AD61

AE61

AD62

AL11

AC4

AE63

AV2

RTCRST#

C366

C366

C1u16X0603

C1u16X0603

SM_INTRUDER#

U2E

U2E

RTCX1

RTCX2

INTRUDER

INTVRMEN

SRTCRST

RTCRST

HDA_BCLK/I2S0_SCLK

HDA_SYNC/I2S0_SFRM

HDA_RST/I2S_MCLK

HDA_SDI0/I2S0_RXD

HDA_SDI1/I2S1_RXD

HDA_SDO/I2S0_TXD

HDA_DOCK_EN/I2S1_TXD

HDA_DOCK_RST/I2S1_SFRM

I2S1_SCLK

PCH_TRST

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

RSVD

RSVD

JTAGX

RSVD

HSW_ULT_DDR3L

HSW_ULT_DDR3L

RTC

RTC

AUDIO SATA

AUDIO SATA

JTAG

JTAG

5 OF 19

5 OF 19

SATA_RN0/PERN6_L3

SATA_RP0/PERP6_L3

SATA_TN0/PETN6_L3

SATA_TP0/PETP6_L3

SATA_RN1/PERN6_L2

SATA_RP1/PERP6_L2

SATA_TN1/PETN6_L2

SATA_TP1/PETP6_L2

SATA_RN2/PERN6_L1

SATA_RP2/PERP6_L1

SATA_TN2/PETN6_L1

SATA_TP2/PETP6_L1

SATA_RN3/PERN6_L0

SATA_RP3/PERP6_L0

SATA_TN3/PETN6_L0

SATA_TP3/PETP6_L0

SATA0GP/GPIO34

SATA1GP/GPIO35

SATA2GP/GPIO36

SATA3GP/GPIO37

SATA_IREF

RSVD

RSVD

SATA_RCOMP

SATALED

J5

H5

B15

A15

J8

H8

A17

B17

J6

H6

B14

C15

F5

E5

C17

D17

V1

U1

V6

AC1

A12

L11

K10

C12

U3

SATA0RXN 22

SATA0RXP 22

SATA0TXN 22

SATA0TXP 22

R329

R329

1KR0402

1KR0402

+VCC3

+VTT_ASATA3PLL

+VCC3

D S

R319 10KR0402R319 10KR0402

Q47

Q47

N-2N7002LT1G_SOT23-RH

N-2N7002LT1G_SOT23-RH

R342X_0R0402 R342X_0R0402

G

R339

R339

1MR0402

1MR0402

R77 10KR0402R77 10KR0402

R76 10KR0402R76 10KR0402

R363 10KR0402R363 10KR0402

R107 10KR0402R107 10KR0402

SATA_RCOMP

R373 3KR1%0402R373 3KR1%0402

SATA_LED_SB#

R94 10KR0402R94 10KR0402

+3VSB

HDA_SYNC_PCH HDA_SYNC_PCH_R

+VCC5

ME Disable SW

Q43

Q43

G

CE

B

Q44

Q44

N-SST3904_SOT23

N-SST3904_SOT23

R324 1KR0402R324 1KR0402

DS

R303 10KR0402R303 10KR0402

+VCC3

+VCC5

Flash Descriptor Security Protect

HDA_SDO

Low = Enable

High = Disable(Overridden)

ME_3V17

N-2N7002LT1G_SOT23-RH

N-2N7002LT1G_SOT23-RH

HDA_SDOUT_PCH_R

R323 1KR0402R323 1KR0402

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

HASWELL ULT (RTC, SATA, AUDIO)

HASWELL ULT (RTC, SATA, AUDIO)

HASWELL ULT (RTC, SATA, AUDIO)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

C

C

C

MS-7859

MS-7859

MS-7859

Date: Sheet of

Date: Sheet of

A

B

C

D

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

6 36Wednesday, July 03, 2013

6 36Wednesday, July 03, 2013

E

6 36Wednesday, July 03, 2013

0.2

0.2

0.2

Page 7

A

U2F

U2F

C43

CLKOUT_PCIE_N0

1 1

CLK_MINI_PCIE_N22

CLK_MINI_PCIE_P22

PCIECLKRQ1#22

+VCC3

+VCC3

2 2

R419 10KR0402R419 10KR0402

C320 X_C10p50N0402C320 X_C10p50N0402

R105 10KR0402R105 10KR0402

R79 10KR0402R79 10KR0402

R89 10KR0402R89 10KR0402

R348 10KR0402R348 10KR0402

R100 10KR0402R100 10KR0402

PCIECLKRQ0#

PCIECLKRQ2#

PCIECLKRQ3#

PCIECLKRQ4#

PCIECLKRQ5#

PCIECLKRQ0#

PCIECLKRQ1#

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

B

HSW_ULT_DDR3L

HSW_ULT_DDR3L

CLOCK

CLOCK

SIGNALS

SIGNALS

6 OF 19

6 OF 19

XTAL24_IN

XTAL24_OUT

RSVD

RSVD

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

A25

B25

K21

M21

C26

C35

C34

AK8

AL8

AN15

AP15

B35

A35

XTAL24_IN

XTAL24_OUT

R63

R63

1MR0402

1MR0402

R54 3KR1%0402R54 3KR1%0402

R276 10KR0402R276 10KR0402

R288 10KR0402R288 10KR0402

R345 10KR0402R345 10KR0402

R350 10KR0402R350 10KR0402

R333 22R0402R333 22R0402

R332 22R0402R332 22R0402

C

C85

C85

C15p50N0402

C15p50N0402

Y1

Y1

4

24MHZ12p_S-HF-1

24MHZ12p_S-HF-1

2

C86

C86

1 3

C15p50N0402

C15p50N0402

D

E

+VTT_CORE

CLK_PCI_KBC 17

CLK_PCIF_PORT80 17

C284X_C0.1u16X0402 C284X_C0.1u16X0402

C289X_C0.1u16X0402 C289X_C0.1u16X0402

+VCC3

+VCC3

SMBCLK 8,15,17,21

SMBDATA 8,15,17,21

2

4

6

8

R530

R530

1KR0402

1KR0402

Q64

Q64

C

C

E

E

N-SST3904_SOT23

N-SST3904_SOT23

+3VSB

G

G

SMBCLK

SMBDATA

DS

Q65

Q65

N-2N7002LT1G_SOT23-RH

N-2N7002LT1G_SOT23-RH

DS

Q67

Q67

N-2N7002LT1G_SOT23-RH

N-2N7002LT1G_SOT23-RH

R459 2.2KR0402R459 2.2KR0402

R468 2.2KR0402R468 2.2KR0402

SMBCLK_PCH

R460

R460

X_0R0402

X_0R0402

SMBDATA_PCH

R466

R466

X_0R0402

X_0R0402

R449

R449

LPC_AD017

SPI_CS0#

SPI_MOSI

SPI_MISO

LPC_AD117

LPC_AD217

LPC_AD317

LPC_FRAME#17

LPC_DRQ#0

3 3

X_10KR0402

X_10KR0402

LPC_DRQ#0 17

SPI_CLK SPI_CLKR

C326

C326

X_C10p50N0402

X_C10p50N0402

R4130R0402 R4130R0402

TPJNC19TPJNC19

TPJNC27TPJNC27

AU14

AW12

AY12

AW11

AV12

U2G

U2G

LAD0

LAD1

LAD2

LAD3

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

HSW_ULT_DDR3L

HSW_ULT_DDR3L

LPC

LPC

SMBUS

SMBUS

SML1ALERT/PCHHOT/GPIO73

C-LINKSPI

C-LINKSPI

SMBALERT/GPIO11

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML0DATA

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_DATA

7 OF 19

7 OF 19

SMBCLK

CL_CLK

CL_RST

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

ILIM_SEL

SMBCLK_PCH

SMBDATA_PCH

SML0_CLK

SML0_DATA

CTL1

CTL3

CTL2

ILIM_SEL 18

SMBCLK_PCH 22

SMBDATA_PCH 22

SMLINK0 for PHY

CTL1 18

CTL3 18

CTL2 18

C99X_C10p50N0402 C99X_C10p50N0402

DRAMRST_CNTRL_PCH 8

DRAMRST_CNTRL_PCH

SMBDATA_PCH

SML0_DATA

SML0_CLK

SMBCLK_PCH

ILIM_SEL

CTL1

CTL2

CTL3

R95 1KR5%0402R95 1KR5%0402

RN2

RN2

1

3

5

7

8P4R-2.2K0402

8P4R-2.2K0402

R90 10KR0402R90 10KR0402

R375 10KR0402R375 10KR0402

R103 10KR0402R103 10KR0402

R72 10KR0402R72 10KR0402

+VCC5

+VCC3

R516 10KR0402R516 10KR0402

CHIP_PWGD9,28

CLR_CMOS

+VCC3

R149

R149

10KR0402

10KR0402

CLR_CMOS

CLR_CMOS9,17

EMI

C182

C182

X_C0.1u16X0402

X_C0.1u16X0402

4 4

D

D

B

B

CD

C

C

EAF

EAF

AB

CLR_CMOS1

CLR_CMOS1

SW-TACTB1S-HF

SW-TACTB1S-HF

EF

R71

R71

2.2KR0402

2.2KR0402

SPI_CS0#

C110 C0.1u16Y0402C110 C0.1u16Y0402

1

CS

2

DO

3

WP

GND4DI

U3

U3

W25Q64FVSSIG-HF

W25Q64FVSSIG-HF

M31-25Q6433-W03

M31-25Q6433-W03

SIC8_SST_S2A

SIC8_SST_S2A

2013.07.02

remove SPI socket

+VCC3 +VCC3+VCC3

C10u10X0805C101 C10u10X0805C101

R62

R62

2.2KR0402

2.2KR0402

SPI_MISO

SPI_MOSI

SPI_CS0#

SPI_CLK

HLOD

8

VCC

SPI_HOLD#_BSPI_MISO

7

SPI_CLK

6

CLK

SPI_MOSI

5

SPI FLASH

R91 0R0402R91 0R0402

R69 0R0402R69 0R0402

R67 0R0402R67 0R0402

R68 0R0402R68 0R0402

SPI_MISO_R

SPI_MOSI_R

SPI_CS0#_R

SPI_CLK_R

SPI_HOLD#_B

+VCC3

1112

1

2

3

4

5

6

7

8

9

10

SPI_DEBUG1

SPI_DEBUG1

BH1X10HS-1.25PITCH_WHITE-RH

BH1X10HS-1.25PITCH_WHITE-RH

N32-1100470-H06

N32-1100470-H06

FPC_CONN_12P

FPC_CONN_12P

R510 0R0402R510 0R0402

DS

Q63

Q63

G

N-2N7002LT1G_SOT23-RH

N-2N7002LT1G_SOT23-RH

B

B

Co-lay socket

Title

Title

Title

HASWELL ULT (CLOCK, SPI, LPC)

HASWELL ULT (CLOCK, SPI, LPC)

HASWELL ULT (CLOCK, SPI, LPC)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

C

C

C

MS-7859

MS-7859

MS-7859

Date: Sheet of

Date: Sheet of

A

B

C

D

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

7 36Wednesday, July 03, 2013

7 36Wednesday, July 03, 2013

E

7 36Wednesday, July 03, 2013

0.2

0.2

0.2

Page 8

A

B

C

D

E

+VTT_CORE+VCC3

2013.03.26

PROCHOT# add pull high R (62OHM to +VTT_CORE)

C196

C196

X_C0.1u10X0402

74LVC1G07:

pin 1 is NC

U10

U10

X_SN74LVC1G07

X_SN74LVC1G07

H_PROCHOT#17

4 4

If CPU PROCHOT# not used

Unstuff R1, R2. stuff R3

53

VCC

VCC

1

A Y

A Y

2

GND

GND

R1

R188 0R0402R188 0R0402

X_C0.1u10X0402

4

R3

R193

R193

62R0402

62R0402

R191 56R0402R191 56R0402

IMVP_PROCHOT#29

SM_PG_CNTL115

SM_RCOMP[0] Width:15mil Spacing:20mil/25mil

SM_RCOMP[1] Width:15mil Spacing:20mil/25mil

SM_RCOMP[2] Width:15mil Spacing:20mil/25mil

SM_RCOMP[1][2][3] Length max: 500mil

+VTT_CORE

R2

R194 X_51R1%0402R194 X_51R1%0402

H_PECI17

C193 C680p50N0402-HFC193 C680p50N0402-HF

H_PROCHOT#_R

R189 0R0402R189 0R0402

R210 10KR0402R210 10KR0402

CPUDRAMRST#

SM_PG_CNTL1

H_CATERR#

PROCPWRGD CPUDRAMRST#

SM_RCOMP0JNC

R213200R1%0402 R213200R1%0402

SM_RCOMP1JNC

R20475R1%0402 R20475R1%0402

SM_RCOMP2JNC

R205100R1%0402 R205100R1%0402

AU60

AV60

AU61

AV15

AV61

D61

K61

N62

K63

C61

U2B

U2B

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

THERMAL

THERMAL

DDR3L

DDR3L

MISC

MISC

PWR

PWR

HSW_ULT_DDR3L

HSW_ULT_DDR3L

JTAG

JTAG

2 OF 19

2 OF 19

PRDY

PREQ

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

XDP_PRDY#

J62

XDP_PREQ#

K62

PROC_TCK

E60

PROC_TMS

E61

PROC_TRST#

E59

PROC_TDI

F63

PROC_TDO

F62

XDP_CPU_BPM_N0

J60

XDP_CPU_BPM_N1

H60

H61

H62

K59

H63

K60

J61

R256 X_0R0402R256 X_0R0402

R243 X_0R0402R243 X_0R0402

R230 X_0R0402R230 X_0R0402

R239 X_0R0402R239 X_0R0402

R221 X_0R0402R221 X_0R0402

XDP_TCLK

XDP_TMS

XDP_TRST#

XDP_TDI

XDP_TDO

+VCC_DDR

R285

R285

X_1KR5%0402

X_1KR5%0402

DDR3_DRAMRST#15

DRAMRST_CNTRL_PCH7

R280 0R0402R280 0R0402

C261 X_C10p50N0402C261 X_C10p50N0402

DDR3_DRAMRST#_D

R619 X_0R0402R619 X_0R0402

2013.03.19

Add pull high to +VCC_DDR

2013.05.09

change to 10K for glitch, C72 stuff 1nF

+VCC_DDR

R614

R618 0R0402R618 0R0402

Q39

Q39

X_N-BSS138LT1G_SOT23-3-RH

X_N-BSS138LT1G_SOT23-3-RH

D S

G

C1000p50X0402

C1000p50X0402

C249

C249

C0.047u10X0402

C0.047u10X0402

R614

10KR0402

10KR0402

C72

C72

R48

R48

X_4.99KR1%0402

X_4.99KR1%0402

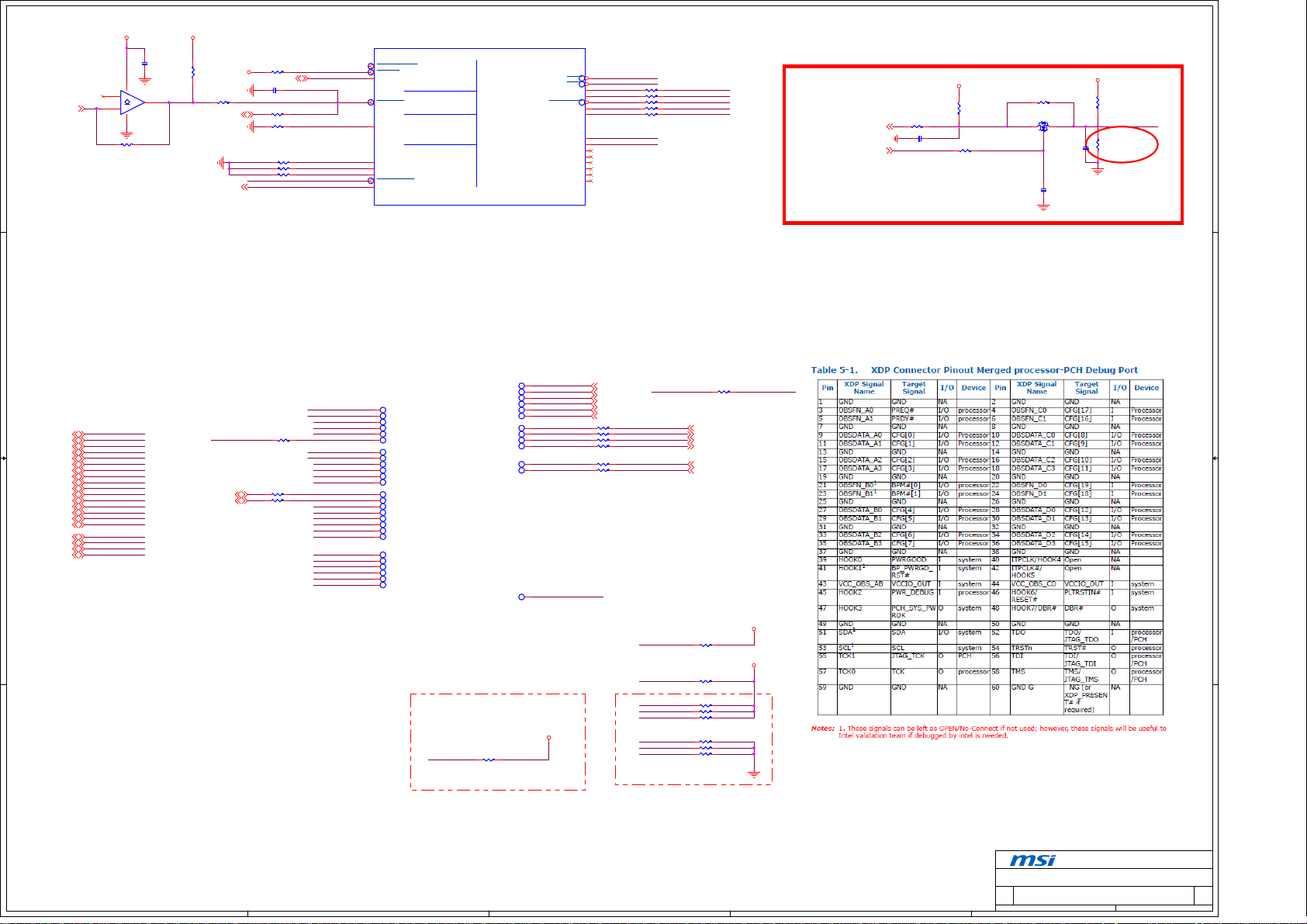

XDP (Reserved)

2013.03.25

3 3

XDP_PREQ#

XDP_PRDY#

CFG0

CFG1

CFG0

CFG014

CFG1

CFG114

CFG2

CFG214

CFG3

CFG314

CFG4

CFG414

CFG5

CFG514

CFG6

CFG614

CFG7

CFG714

CFG8

CFG814

CFG9

CFG914

CFG10

CFG1014

CFG11

CFG1114

CFG12

CFG1214

CFG13

CFG1314

CFG14

CFG1414

CFG15

CFG1514

CFG16

CFG1614

CFG18

CFG1814

CFG17

CFG1714

CFG19

CFG1914

2 2

XDP_PRESENT#

SMBDATA7,15,17,21

SMBCLK7,15,17,21

R242 1KR0402R242 1KR0402

R237 X_0R0402R237 X_0R0402

R241 X_0R0402R241 X_0R0402

CFG2

CFG3

XDP_CPU_BPM_N0

XDP_CPU_BPM_N1

CFG4

CFG5

CFG6

CFG7

SMB_DATA_R

SMB_CLK_R

CFG17

CFG16

CFG8

CFG9

CFG10

CFG11

CFG19

CFG18

CFG12

CFG13

CFG14

CFG15

TPJNC35TPJNC35

TPJNC36TPJNC36

TPJNC37TPJNC37

TPJNC38TPJNC38

TPJNC39TPJNC39

TPJNC40TPJNC40

TPJNC41TPJNC41

TPJNC42TPJNC42

TPJNC43TPJNC43

TPJNC44TPJNC44

TPJNC45TPJNC45

TPJNC46TPJNC46

TPJNC47TPJNC47

TPJNC48TPJNC48

TPJNC49TPJNC49

TPJNC50TPJNC50

TPJNC51TPJNC51

TPJNC52TPJNC52

TPJNC53TPJNC53

TPJNC54TPJNC54

TPJNC55TPJNC55

TPJNC56TPJNC56

TPJNC57TPJNC57

TPJNC58TPJNC58

TPJNC59TPJNC59

TPJNC60TPJNC60

Remove XDP port

TPJNC61TPJNC61

TPJNC62TPJNC62

TPJNC63TPJNC63

TPJNC64TPJNC64

TPJNC65TPJNC65

TPJNC66TPJNC66

TPJNC67TPJNC67

TPJNC68TPJNC68

TPJNC69TPJNC69

TPJNC70TPJNC70

TPJNC71TPJNC71

TPJNC72TPJNC72

TPJNC73TPJNC73

XDP_TCLK1

XDP_TCLK

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TMS

XDP_PWRGD

XDP_HOOK1

XDP_PWROK

XPD_RESET#

XDP_HOOK7

XDP_PRESENT#

XDP_TCLK1 6

XDP_TCLK 6

XDP_TDO 6

XDP_TRST# 6

XDP_TDI 6

XDP_TMS 6

R202 1KR1%0402R202 1KR1%0402

R212 0R0402R212 0R0402

R218 0R0402R218 0R0402

R228 0R0402R228 0R0402

R249 1KR1%0402R249 1KR1%0402

R216 1KR1%0402R216 1KR1%0402

XDP_TCLK XDP_TCLK1

R252 X_0R0402R252 X_0R0402

VCCST_PWRGD 11,28,29

PWR_DBGPOWER_DEBUG

PWRBTN# 9,17

PWR_DBG 11

SYS_PWROK 9,28

XDP_RST# 9

PM_SYSRST# 9

+VTT_CORE

PWR_DBG

Close CPU

XDP_TDI

XDP_TMS

XDP_TDO

XDP_PREQ#

+3VSB

X_1KR1%0402

XDP_PWROK

1 1

A

B

X_1KR1%0402

R223

R223

Close XDP

C

XDP_TRST#

XDP_TCLK

XDP_TCLK1

R208150R1%0402 R208150R1%0402

+VTT_CORE

R42 51R1%0402R42 51R1%0402

R238 51R1%0402R238 51R1%0402

R220 51R1%0402R220 51R1%0402

R184 X_51R1%0402R184 X_51R1%0402

R229 X_51R1%0402R229 X_51R1%0402

R248 51R1%0402R248 51R1%0402

R244 X_51R1%0402R244 X_51R1%0402

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

HASWELL ULT (MSIC)

HASWELL ULT (MSIC)

HASWELL ULT (MSIC)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

C

C

C

MS-7859

MS-7859

MS-7859

Date: Sheet of

Date: Sheet of

D

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

8 36Wednesday, July 03, 2013

8 36Wednesday, July 03, 2013

E

8 36Wednesday, July 03, 2013

0.2

0.2

0.2

Page 9

A

2013.05.15

pull up to +3VSB for leakage voltage

+3VSB

+3VSB

+VCC3

+3VSB

1 1

core power

core power

sus power

DSW power

sus power

sus power

sus power

sus power

core power

core power

core power

sus power

core power

2 2

GPIO[8, 9, 10, 13, 14, 24, 25, 26, 28, 33, 38, 39, 46, 47, 49, 56, 59, 70, 76]

defaults to GPI and can't be left floating

+FATX_3VSB

+VCC3

HID_ASSERT23

MCU_RST23

+3VSB

+FATX_3VSB

+3VSB

+3VSB

+3VSB

+3VSB

WIRELESS_EN22

+3VSB

SBS_SCI17

+3VSB

CLR_CMOS7,17

+VCC3

MULTI_TOUCH_DET19

MPY_PWREN30

+3VSB

+FATX_3VSB

+3VSB

SCI_WAKE_UP#17

+3VSB

SBS_SCI17

+3VSB

SMI#17

+VCC3

+VCC3

+VCC3

MCU_WAKE_UP#23

+VCC3

+3VSB

+VCC3

R632 10KR0402R632 10KR0402

R357 10KR0402R357 10KR0402

R98 10KR0402R98 10KR0402

R393 10KR0402R393 10KR0402

R343 X_10KR0402R343 X_10KR0402

R380 1KR5%0402R380 1KR5%0402

MCU_RST

R78 10KR0402R78 10KR0402

R371 X_10KR0402R371 X_10KR0402

R347 10KR0402R347 10KR0402

R74 10KR0402R74 10KR0402

R396 10KR0402R396 10KR0402

R82 10KR0402R82 10KR0402

WIRELESS_EN

R349 10KR0402R349 10KR0402

SBS_SCI

R615 0R0402R615 0R0402

R360 10KR0402R360 10KR0402

CLR_CMOS

R399 10KR0402R399 10KR0402

MULTI_TOUCH_DET

MPY_PWREN

R83 10KR0402R83 10KR0402

R80 10KR0402R80 10KR0402

R370 X_10KR0402R370 X_10KR0402

R633 10KR0402R633 10KR0402

SCI_WAKE_UP#

R101 10KR0402R101 10KR0402

R96 X_0R0402R96 X_0R0402

R97 10KR0402R97 10KR0402

SMI#

R75 10KR0402R75 10KR0402

R382 10KR0402R382 10KR0402

R420 10KR0402R420 10KR0402

R372 10KR0402R372 10KR0402

R106 10KR0402R106 10KR0402

R346 10KR0402R346 10KR0402

R99 X_10KR0402R99 X_10KR0402

HID_ASSERT

DSW_Wake

SCI_WAKE_UP#

MULTI_TOUCH_DET

SBS_SCI

P1

AU2

AM7

AD6

Y1

T3

AD5

AN5

AD7

AN3

AG6

AP1

AL4

AT5

AK4

AB6

U4

Y3

P3

Y2

AT3

AH4

AM4

AG5

AG3

AM3

AM2

P2

C4

L2

N5

V2

U2J

U2J

BMBUSY/GPIO76

GPIO8

LAN_PHY_PWR_CTRL/GPIO12

GPIO15

GPIO16

GPIO17

GPIO24

GPIO27

GPIO28

GPIO26

GPIO56

GPIO57

GPIO58

GPIO59

GPIO44

GPIO47

GPIO48

GPIO49

GPIO50

HSIOPC/GPIO71

GPIO13

GPIO14

GPIO25

GPIO45

GPIO46

GPIO9

GPIO10

DEVSLP0/GPIO33

SDIO_POWER_EN/GPIO70

DEVSLP1/GPIO38

DEVSLP2/GPIO39

SPKR/GPIO81

2013.03.19

change to GPIO9 for OS SCI

B

HSW_ULT_DDR3L

HSW_ULT_DDR3L

GPIO

GPIO

10 OF 19

10 OF 19

CPU/

CPU/

MISC

MISC

SERIAL IO

SERIAL IO

THRMTRIP

RCIN/GPIO82

SERIRQ

PCH_OPI_RCOMP

RSVD

RSVD

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

+VTT_CORE +VCC3

D60

KBRST#

V4

SERIRQ

T4

PCH_OPIRCOMP

AW15

AF20

AB21

RN3 8P4R-10KR0402RN3 8P4R-10KR0402

1

2

3

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4

F2

F3

G4

F1

E3

F4

D3

E4

C3

E2

4

5

6

7

8

R351 X_10KR0402R351 X_10KR0402

R369 10KR0402R369 10KR0402

RN5 8P4R-10KR0402RN5 8P4R-10KR0402

1

U1.N7

U1.J1

3

5

U1.J1

U1.N7

7

RN4 8P4R-10KR0402RN4 8P4R-10KR0402

7

8

5

6

3

4

1

2

R87 10KR0402R87 10KR0402

R93 10KR0402R93 10KR0402

R88 10KR0402R88 10KR0402

R383 10KR0402R383 10KR0402

R86 10KR0402R86 10KR0402

R374 10KR0402R374 10KR0402

R364 10KR0402R364 10KR0402

TPJNC24TPJNC24

R362 10KR0402R362 10KR0402

R397 10KR0402R397 10KR0402

R84 10KR0402R84 10KR0402

2

4

6

8

I2C0_SDA

I2C0_SCL

R199

R199

1KR0402

1KR0402

R51 49.9R1%0402R51 49.9R1%0402

R410

R410

0R0402

0R0402

R411

R411

X_0R0402

X_0R0402

C

SWAP layout

SWAP layout

R400

R400

8.2KR0402

8.2KR0402

+VCC3

I2C0_SDA 23

I2C0_SCL 23

H_THRMTRIP# 17

KBRST# 17

SERIRQ 17

Pull up 1K for I2C 400KHz

I2C0_SDA

I2C0_SCL

+VCC3

D

E

GPIO86

R851KR5%0402 R851KR5%0402

R3871KR5%0402 R3871KR5%0402

C358 X_C10p50N0402C358 X_C10p50N0402

FP_RST#17

E

E

Q53

R454 10KR0402R454 10KR0402

2013.06.25

SYS_RESET# reserved direct pull high to +VCC3

3 3

4 4

+VCC3

R642 X_10KR0402R642 X_10KR0402

PM_SYSRST#8

CHIP_PWGD7,28

EC delay 99ms

APWROK

not supporting Intel AMT

it can be connected to PWROK

SUS_WARN# SUS_ACK#

R81 X_0R0402R81 X_0R0402

A

R102 X_10KR0402R102 X_10KR0402

Q53

B

B

C

C

N-SST3904_SOT23

N-SST3904_SOT23

AC_PRESENT17

SUS_ACK#17

JNC3 X_0402JNC3 X_0402

12

RSMRST#17

SUS_WARN#17

PWRBTN#8,17

PM_BATLOW#17

+FATX_3VSB

+3VSB

2013.05.06

change ACPRESENT to EC control

Reserved +3VSB power rail

PM_SYSRST#

PLTRST#

C93 X_C10p50N0402C93 X_C10p50N0402

SUS_WARN#

PWRBTN#

AC_PRESENT

R421 0R0402R421 0R0402

PM_BATLOW#

PLTRST#

T39-02G1700-T07_SC70-6-RH

T39-02G1700-T07_SC70-6-RH

R377X_8.2KR1% R377X_8.2KR1%

R416X_10KR0402 R416X_10KR0402

R634X_8.2KR1% R634X_8.2KR1%

R635X_10KR0402 R635X_10KR0402

U2H

U2H

AK2

SUSACK

AC3

SYS_RESET

AG2

SYS_PWROK

AY7

PCH_PWROK

AB5

APWROK

AG7

PLTRST

AW6

RSMRST

AV4

SUSWARN/SUSPWRDNACK/GPIO30

AL7

PWRBTN

AJ8

ACPRESENT/GPIO31

AN4

BATLOW/GPIO72

AF3

SLP_S0

AM5

SLP_WLAN/GPIO29

+3VSB

C322 C0.1u10X0402C322 C0.1u10X0402

U22AU22A

1

6

2 5

+3VSB

C367 C0.1u10X0402C367 C0.1u10X0402

U22B

U22B

3

4

2 5

B

HSW_ULT_DDR3L

HSW_ULT_DDR3L

SYSTEM POWER MANAGEMENT

SYSTEM POWER MANAGEMENT

8 OF 19

8 OF 19

R436 33R0402R436 33R0402

R435 33R0402R435 33R0402

R438 33R0402R438 33R0402

R405 33R0402R405 33R0402

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

MINIPCIE_RST# 17,22

BUF_PLT_RST# 21

SIO_RST# 17

XDP_RST# 8

DSWVRMEN

DPWROK

WAKE

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

AW7

AV5

JNC4 X_0402JNC4 X_0402

AJ5

V5

AG4

AE6

AP5

R361 39R0402R361 39R0402

AJ6

R352 39R0402R352 39R0402

AT4

AL5

AP4

AJ7

C181

C181

C1000p50X0402

C1000p50X0402

for INTEL debug test

C

DSWVRMEN

12

CLKRUN#

RSMRST#

SLP_S4#

SLP_S3#

PCH_SLP_A#

SLP_SUS#

SLP_LAN#

PWRBTN#

PM_SYSRST#

R65 330KR0402-1R65 330KR0402-1

R60 X_330KR0402R60 X_330KR0402

RSMRST# 17

WAKE# 22SYS_PWROK8,28

TPJNC32TPJNC32

PCH_SUSCLK 17

TPJNC21TPJNC21

SLP_S4# 17,18,19,27,28

SLP_S3# 17,18,19,28

PCH_SLP_A# 22

SLP_SUS# 17

SLP_LAN# 22

TPJNC30TPJNC30

TPJNC22TPJNC22

TPJNC29TPJNC29

TPJNC31TPJNC31

TPJNC34TPJNC34

TPJNC26TPJNC26

TPJNC33TPJNC33

DSWODVREN - On Die DSW VR Enable

RTCVCC

High --- Enable internal 1.05V regulator

Low --- Disable

DPWROK

Without deep s4/s5 support tied together with RSMRST#

RSMRST#

R66 100KR0402R66 100KR0402

CLKRUN#

FP_RST#

PM_SYSRST#

WAKE#

SLP_LAN#

SUS_WARN#

CRB 100K to GND

R365 8.2KR0402R365 8.2KR0402

R469 X_10KR0402R469 X_10KR0402

R452 10KR0402R452 10KR0402

R394 X_1KR0402R394 X_1KR0402

R412 X_10KR0402R412 X_10KR0402

R70 X_10KR0402R70 X_10KR0402

D

+3VSB

+VCC3

C343

C343

X_C0.1u16X0402

X_C0.1u16X0402

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

HASWELL ULT (GPIO, SYS, POWER)

HASWELL ULT (GPIO, SYS, POWER)

HASWELL ULT (GPIO, SYS, POWER)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

C

C

C

MS-7859

MS-7859

MS-7859

Date: Sheet of

Date: Sheet of

Date: Sheet of

MICRO-STAR INT'L CO.,LTD.

9 36Wednesday, July 03, 2013

9 36Wednesday, July 03, 2013

E

9 36Wednesday, July 03, 2013

0.2

0.2

0.2

Page 10

5

D D

PCIE_MINI_RXN22

PCIE_MINI_RXP22

PCIE_MINI_TXN22

PCIE_MINI_TXP22

C C

B B

+VTT_AUSB3PLL

C82 C0.1u10X0402C82 C0.1u10X0402

C83 C0.1u10X0402C83 C0.1u10X0402

2013/01/28

change to port5 Lane0

R493KR1%0402 R493KR1%0402

PCIE_RCOMP

PETN1_JNC

PETP1_JNC

4

F10

PERN5_L0

E10

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PETN5_L1

A23

PETP5_L1

H10

PERN5_L2

G10

PERP5_L2

B21

PETN5_L2

C21

PETP5_L2

E6

PERN5_L3

F6

PERP5_L3

B22

PETN5_L3

A21

PETP5_L3

G11

PERN3

F11

PERP3

C29

PETN3

B30

PETP3

F13

PERN4

G13

PERP4

B29

PETN4

A29

PETP4

G17

PERN1/USB3RN3

F17

PERP1/USB3RP3

C30

PETN1/USB3TN3

C31

PETP1/USB3TP3

F15

PERN2/USB3RN4

G15

PERP2/USB3RP4

B31

PETN2/USB3TN4

A31

PETP2/USB3TP4

E15

RSVD

E13

RSVD

A27

PCIE_RCOMP

B27

PCIE_IREF

U2K

U2K

HSW_ULT_DDR3L

HSW_ULT_DDR3L

PCIE USB

PCIE USB

3

USB2N0

USB2P0

USB2N1

USB2P1

USB2N2

USB2P2

USB2N3

USB2P3

USB2N4

USB2P4

USB2N5

USB2P5

USB2N6

USB2P6

USB2N7

USB2P7

USB3RN1

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

RSVD

RSVD

AN8

AM8

AR7

AT7

AR8

AP8

AR10

AT10

AM15

AL15

AM13

AN13

AP11

AN11

AR13

AP13

G20

H20

C33

B34

E18

F18

B33

A33

AJ10

AJ11

AN10

AM10

AL3

AT1

AH2

AV3

USB3_RX1_N

USB3_RX1_P

USB3_TX1_N

USB3_TX1_P

USB3_RX2_N

USB3_RX2_P

USB3_TX2_N

USB3_TX2_P

USB_BIAS

USB_OCP#0

USB_OCP#1

USB_OCP#2

USB_OCP#3

USB_PN0 18

USB_PP0 18

USB_PN1 18

USB_PP1 18

USB_PN4 19

USB_PP4 19

USB_PN5 19

USB_PP5 19

USB_PN6 22

USB_PP6 22

USB_PN7 23

USB_PP7 23

USB3_RX1_N 20

USB3_RX1_P 20

USB3_TX1_N 20

USB3_TX1_P 20

USB3_RX2_N 20

USB3_RX2_P 20

USB3_TX2_N 20

USB3_TX2_P 20

2

USB3.0

USB3.0

WEBCAM

TOUCH PANEL

BT

MCU HUB

charge port

debug port

R341

R341

22.6R1%0402

22.6R1%0402

USB_OCP#0 18

USB_OCP#1 18

USB_OCP#2 19

USB_OCP#3 19

1

11 OF 19

11 OF 19

A A

Title

Title

Title

HASWELL ULT (PCIE, USB)

HASWELL ULT (PCIE, USB)

HASWELL ULT (PCIE, USB)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

MS-7859 0.2

B

MS-7859 0.2

B

MS-7859 0.2

B

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

10 36Wednesday, July 03, 2013

10 36Wednesday, July 03, 2013

10 36Wednesday, July 03, 2013

1

Page 11

5

1.4A

+VDDQ_CPU

D D

2013.03.20

Stuff at VRM

+VTT_CORE

R36

R36

X_54.9R1%0402

X_54.9R1%0402

VR_SVID_ALERT#29

VCCST_PWRGD

R620 X_0R0402R620 X_0R0402

+VDDQ_CPU+VCC_DDR

12

JNC2X_0402 JNC2X_0402

12

JNC1X_0402 JNC1X_0402

VR_READYH_VR_EN

VR_SVID_CLK29

R29

R29

X_130R1%0402

X_130R1%0402

VR_SVID_DATA29

Close to IMVP7

C C

VCCST_PWRGD8,28,29

VCCST_PWRGD_EC17

+VTT_CORE

2013.03.20

modify power sequence

VR_EN connected to VR_ready by 10K (CRB)

VCCST_PWRGD delay circuit, and reserved from EC (OD, 1.05V level)

R608 10KR0402R608 10KR0402

R622 10KR0402R622 10KR0402

C43 C0.1u25X50402C43 C0.1u25X50402

C44 C0.1u25X50402C44 C0.1u25X50402

C62

C62

C2.2u6.3X50402

C2.2u6.3X50402

75R0402

75R0402

130R1%0402

130R1%0402

+VCC_DDR

C71

C71

C2.2u6.3X50402

C2.2u6.3X50402

+VTT_CORE

R32

R32

+VTT_CORE+VTT_CORE

R39

R39

Close to

CPU

DELAY_IMVP_PWRGD28,29

C53

C53

C51

C51

C2.2u6.3X50402

C2.2u6.3X50402

C2.2u6.3X50402

C2.2u6.3X50402

+VTT_CORE

R47 0R0805R47 0R0805

R46 0R0805R46 0R0805

C49

C49

C60

C65

C65

C60

C10u6.3X5

C10u6.3X5

C10u6.3X5

C10u6.3X5

VCCSENSE29

R3143R5%0402 R3143R5%0402

EC_ALLSYSPG28

H_VR_EN29

2.6A

C267

C267

C268

C268

C22u6.3X

C22u6.3X

C10u6.3X5

C10u6.3X5

+VDDQ_CPU

C10u6.3X5

C10u6.3X5

+VCC_CORE

PWR_DBG8

+VCC_CORE

4

C45

C45

C64

C64

C10u6.3X5

C10u6.3X5

C10u6.3X5

C10u6.3X5

TPJNC11TPJNC11

+VCCIO_OUT

+VCCIOA_OUT

R219 X_0R0402R219 X_0R0402

H_VR_EN

R200 X_0R0402R200 X_0R0402

TPJNC6TPJNC6

TPJNC4TPJNC4

TPJNC10TPJNC10

TPJNC8TPJNC8

150K PULL HIGH

C59

C59

PWR_DBG

C10u6.3X5

C10u6.3X5

R43

R43

100R1%0402

100R1%0402

VCCST_PWRGD

VR_READY

ULT_RSV69

ULT_RSV70

ULT_RSV71

ULT_RSV72

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

AC58

AB23

AD23

AA23

AE59

AD60

AD59

AA59

AE60

AC59

AG58

AC22

AE22

AE23

AB57

AD57

AG57

L59

J58

F59

N58

E63

A59

E20

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

U59

V59

C24

C28

C32

U2L

U2L

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

VCCIOA_OUT

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

HSW_ULT_DDR3L

HSW_ULT_DDR3L

HSW ULT POWER

HSW ULT POWER

12 OF 19

12 OF 19

3

+VCC_CORE

C36

VCC

C40

VCC

C44

VCC

C48

VCC

C52

VCC

C56

VCC

E23

VCC

E25

VCC

E27

VCC

E29

VCC

E31

VCC

E33

VCC

E35

VCC

E37

VCC

E39

VCC

E41

VCC

E43

VCC

E45

VCC

E47

VCC

E49

VCC

E51

VCC

E53

VCC

E55

VCC

E57

VCC

F24

VCC

F28

VCC

F32

VCC

F36

VCC

F40

VCC

F44

VCC

F48

VCC

F52

VCC

F56

VCC

G23

VCC

G25

VCC

G27

VCC

G29

VCC

G31

VCC

G33

VCC

G35

VCC

G37

VCC

G39

VCC

G41

VCC

G43

VCC

G45

VCC

G47

VCC

G49

VCC

G51

VCC

G53

VCC

G55

VCC

G57

VCC

H23

VCC

J23

VCC

K23

VCC

K57

VCC

L22

VCC

M23

VCC

M57

VCC

P57

VCC

U57

VCC

W57

VCC

32A

C232

C232

C220

C220

C227

C227

C230

C230

C56

C56

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C242

C242

C50

C50

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C209

C209

C57

C57

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

2

C241

C241

C218

C226

C226

C67

C67

C68

C68

C262

C54

C54

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C66

C219

C219

C66

C207

C207

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C262

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C229

C229

C269

C269

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C218

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

C210

C210

C211

C211

C22u6.3X

C22u6.3X

C22u6.3X

C22u6.3X

1

B B

A A

Title

Title

Title

HASWELL ULT (POWER1)

HASWELL ULT (POWER1)

HASWELL ULT (POWER1)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

MS-7859 0.2

C

MS-7859 0.2

C

MS-7859 0.2

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

11 36Wednesday, July 03, 2013

11 36Wednesday, July 03, 2013

11 36Wednesday, July 03, 2013

1

Page 12

A

B

C

D

E

+VTT_CORE_IDEL

+VTT_CORE

1 1

+VTT_CORE_IDEL +VTT_AUSB3PLL

41mA

L16

L16

2.2u1A-HF

2.2u1A-HF

L17

L17

2.2u1A-HF

2.2u1A-HF

2 2

3 3

4 4

+VTT_CORE

+3VSB

+VTT_CORE

R306

R306

0R0603

0R0603

L8

L8

L7

L7

2.2u1A-HF

2.2u1A-HF

2.2u1A-HF

2.2u1A-HF

C299

C299

C22u6.3X

C22u6.3X

C294

C294

C22u6.3X

C22u6.3X

C312

C312

C22u6.3X

C22u6.3X

C100u6.3X51206-HF

C100u6.3X51206-HF

C100u6.3X51206-HF

C100u6.3X51206-HF

C288

C288

C314

C314

C22u6.3X

C22u6.3X

C297

C297

C22u6.3X

C22u6.3X

200mA

C311

C311

C1u16X0402

C1u16X0402

C1u16X0402

C1u16X0402

C307

C307

C1u16X0402

C1u16X0402

C272

C272

C1u16X0402

C1u16X0402

+VCC3

C92

C92

C95

C95

C306

C306

C1u16X0402

C1u16X0402

+VTT_ASATA3PLL

C300

C300

C22u6.3X

C22u6.3X

0.31A

C274

C274

C1u16X0402

C1u16X0402

C285

C285

C1u16X0402

C1u16X0402

C287

C287

C1u16X0402

C1u16X0402

0.042A

C293

C293

C1u16X0402

C1u16X0402

C106

C106

C1u16X0402

C1u16X0402

C317

C317

C1u16X0402

C1u16X0402

+3VSB

1.838A

C298

C298

C1u16X0402

C1u16X0402

0.041A

0.057A

0.011A

0.114A

0.20A

0.063A

0.041A

0.2A

0.063A

TP15TP15

TP14TP14

AA21

W21

AH14

AH13

AC9

AA9

AH10

K19

A20

R21

M20

AE20

AE21

L10

B18

B11

Y20

J13

J18

J17

T21

K18

V21

K9

M9

N8

P9

V8

W9

U2M

U2M

VCCHSIO

VCCHSIO

VCCHSIO

VCC1_05

VCC1_05

VCCUSB3PLL

VCCSATA3PLL

RSVD

VCCAPLL

VCCAPLL

DCPSUS3

VCCHDA

DCPSUS2

VCCSUS3_3

VCCSUS3_3

VCCDSW3_3

VCC3_3

VCC3_3

VCCCLK

VCCCLK

VCCACLKPLL

VCCCLK

VCCCLK

VCCCLK

RSVD

RSVD

RSVD

VCCSUS3_3

VCCSUS3_3

HSIO

HSIO

OPI

OPI

USB3

USB3

HDA

HDA

VRM

VRM

GPIO/LPC

GPIO/LPC

LPT LP POWER

LPT LP POWER

HSW_ULT_DDR3L

HSW_ULT_DDR3L

13 OF 19

13 OF 19

RTC

RTC

SPI

SPI

CORE

CORE

THERMAL SENSOR

THERMAL SENSOR

SERIAL IO

SERIAL IO

SUS OSCILLATOR

SUS OSCILLATOR

USB2

USB2

VCCSUS3_3

VCCRTC

DCPRTC

VCCSPI

VCCASW

VCCASW

VCC1_05

VCC1_05

VCC1_05

VCC1_05

VCC1_05

DCPSUSBYP

DCPSUSBYP

VCCASW

VCCASW

VCCASW

DCPSUS1

DCPSUS1

VCCTS1_5

VCC3_3

VCC3_3

VCCSDIO

VCCSDIO

DCPSUS4

RSVD

VCC1_05

VCC1_05

AH11

AG10

AE7

Y8

AG14

AG13

J11

H11

H15

AE8

AF22

AG19

AG20

AE9

AF9

AG8

AD10

AD8

J15

K14

K16

U8

T9

AB8

AC20

AG16

AG17

TP17TP17

+VCCRTCEXT

0.018A

0.658A

TP16TP16

0.003A

0.017A

C266

C266

C1u16X0402

C1u16X0402

0.062A

C304

C304

C1u16X0402

C1u16X0402

6uA

C316 C0.1u25X50402C316 C0.1u25X50402

1.741A

C273

C273

C1u16X0402

C1u16X0402

0.658A

0.041A

+VTT_CORE

C309

C309

C1u16X0402

C1u16X0402

+VTT_CORE

C270

C270

C1u16X0402

C1u16X0402

C308

C308

C1u16X0402

C1u16X0402

C286 C1u16X0402C286 C1u16X0402

C302

C302

C1u16X0402

C1u16X0402

+3VSB

C310

C310

C0.1u25X50402

C0.1u25X50402

C55

C55

C0.1u25X50402

C0.1u25X50402

C295

C295

C10u6.3X5

C10u6.3X5

C296

C296

C0.1u25X50402

C0.1u25X50402

C291

C291

C0.1u25X50402

C0.1u25X50402

C105

C105

C1u16X0402

C1u16X0402

C290

C290

C22u6.3X

C22u6.3X

C301

C301

C0.1u25X50402

C0.1u25X50402

+VCC3

+VTT_CORE

+VTT_CORE

+1_5VRUN

RTCVCC

+VCC3

Title

Title

Title

HASWELL ULT (POWER2)

HASWELL ULT (POWER2)

HASWELL ULT (POWER2)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

MS-7859

MS-7859

MS-7859

Date: Sheet of

Date: Sheet of

A

B

C

D

Date: Sheet of

12 36Wednesday, July 03, 2013

12 36Wednesday, July 03, 2013

12 36Wednesday, July 03, 2013

E

0.2

0.2

0.2

Page 13

A

HSW_ULT_DDR3L

HSW_ULT_DDR3L

U2N

U2N

A11

VSS

A14

VSS

A18

VSS

A24

VSS

A28

1 1

2 2

3 3

A32

A36

A40

A44

A48

A52

A56

AA1

AA58

AB10

AB20

AB22

AB7

AC61

AD21

AD3

AD63

AE10

AE5

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG1

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

14 OF 19

14 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN51

AN52

AN60

AN63

AN7

AP10

AP17

AP20

B

HSW_ULT_DDR3L

HSW_ULT_DDR3L

U2O

U2O

AP22

AP23

AP26

AP29

AP3

AP31

AP38

AP39

AP48

AP52

AP54

AP57

AR11

AR15

AR17

AR23

AR31

AR33

AR39

AR43

AR49

AR5

AR52

AT13

AT35

AT37

AT40

AT42

AT43

AT46

AT49

AT61

AT62

AT63

AU1

AU16

AU18

AU20

AU22

AU24

AU26

AU28

AU30

AU33

AU51

AU53

AU55

AU57

AU59

AV14

AV16

AV20

AV24

AV28

AV33

AV34

AV36

AV39

AV41

AV43

AV46

AV49

AV51

AV55

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

15 OF 19

15 OF 19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AV59

AV8

AW16

AW24

AW33

AW35

AW37

AW4

AW40

AW42

AW44

AW47

AW50

AW51

AW59

AW60

AY11

AY16

AY18

AY22

AY24

AY26

AY30

AY33

AY4

AY51

AY53

AY57

AY59

AY6

B20

B24

B26

B28

B32

B36

B4

B40

B44

B48

B52

B56

B60

C11

C14

C18

C20

C25

C27

C38

C39

C57

D12

D14

D18

D2

D21

D23

D25

D26

D27

D29

D30

D31

C

HSW_ULT_DDR3L

HSW_ULT_DDR3L

U2P

U2P

D33

VSS

D34

VSS

D35

VSS

D37

VSS

D38

VSS

D39

VSS

D41

VSS

D42

VSS

D43

VSS

D45

VSS

D46

VSS

D47

VSS

D49

VSS

D5

VSS

D50

VSS

D51

VSS

D53

VSS

D54

VSS

D55

VSS

D57

VSS

D59

VSS

D62

VSS

D8

VSS

E11

VSS

E17

VSS

F20

VSS

F26

VSS

F30

VSS

F34

VSS

F38

VSS

F42

VSS

F46

VSS

F50

VSS

F54

VSS

F58

VSS

F61

VSS

G18

VSS

G22

VSS

G3

VSS

G5

VSS

G6

VSS

G8

VSS

H13

VSS

16 OF 19

16 OF 19

VSS_SENSE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

D

VSSSENSE 29

E

4 4

Title

Title

Title

HASWELL ULT (GND1)

HASWELL ULT (GND1)

HASWELL ULT (GND1)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

B

B

B

MS-7859

MS-7859

MS-7859

Date: Sheet of

Date: Sheet of

A

B

C

D

Date: Sheet of

13 36Wednesday, July 03, 2013

13 36Wednesday, July 03, 2013

13 36Wednesday, July 03, 2013

E

0.2

0.2

0.2

Page 14

A

U2Q

U2Q

DAISY_CHAIN_NCTF_AW2_AY2

DAISY_CHAIN_NCTF_AW3_AY3

TPJNC5TPJNC5

1 1

TPJNC25TPJNC25 TPJNC3TPJNC3

2 2

3 3

DAISY_CHAIN_NCTF_AY60

DAISY_CHAIN_NCTF_AW61_AY61

DAISY_CHAIN_NCTF_AW62_AY62

DAISY_CHAIN_NCTF_B2

DAISY_CHAIN_NCTF_B3_A3

DAISY_CHAIN_NCTF_A61_B61

DAISY_CHAIN_NCTF_B62_B63

DAISY_CHAIN_NCTF_C1_C2

CFG08

CFG18

CFG28

CFG38

CFG48

CFG58

CFG68

CFG78

CFG88

CFG98

CFG108

CFG118

CFG128

CFG138

CFG148

CFG158

CFG168

CFG188

CFG178

CFG198

CFG_RCOMP

R203

R203

49.9R1%0402

49.9R1%0402

R340

R340

8.2KR1%0402

8.2KR1%0402

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

TD_IREF

AY2

DAISY_CHAIN_NCTF_AY2

AY3

DAISY_CHAIN_NCTF_AY3

AY60

DAISY_CHAIN_NCTF_AY60

AY61

DAISY_CHAIN_NCTF_AY61

AY62

DAISY_CHAIN_NCTF_AY62

B2

DAISY_CHAIN_NCTF_B2

B3

DAISY_CHAIN_NCTF_B3

B61

DAISY_CHAIN_NCTF_B61

B62

DAISY_CHAIN_NCTF_B62

B63

DAISY_CHAIN_NCTF_B63

C1

DAISY_CHAIN_NCTF_C1

C2

DAISY_CHAIN_NCTF_C2

U2S

U2S

AC60

CFG0

AC62

CFG1

AC63

CFG2

AA63

CFG3

AA60

CFG4

Y62

CFG5

Y61

CFG6

Y60

CFG7

V62

CFG8

V61

CFG9

V60

CFG10

U60

CFG11

T63

CFG12

T62

CFG13

T61

CFG14

T60

CFG15

AA62

CFG16

U63

CFG18

AA61

CFG17

U62

CFG19

V63

CFG_RCOMP

A5

RSVD

E1

RSVD

D1

RSVD

J20

RSVD

H18

RSVD

B12

TD_IREF

B

HSW_ULT_DDR3L

HSW_ULT_DDR3L

17 OF 19

17 OF 19

HSW_ULT_DDR3L

HSW_ULT_DDR3L

RESERVED

RESERVED

19 OF 19

19 OF 19

DAISY_CHAIN_NCTF_A3

DAISY_CHAIN_NCTF_A4

DAISY_CHAIN_NCTF_A60

DAISY_CHAIN_NCTF_A61

DAISY_CHAIN_NCTF_A62

DAISY_CHAIN_NCTF_AV1

DAISY_CHAIN_NCTF_AW1

DAISY_CHAIN_NCTF_AW2

DAISY_CHAIN_NCTF_AW3

DAISY_CHAIN_NCTF_AW61

DAISY_CHAIN_NCTF_AW62

DAISY_CHAIN_NCTF_AW63

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

PROC_OPI_RCOMP

RSVD

RSVD

RSVD

VSS

VSS

RSVD

RSVD

DAISY_CHAIN_NCTF_B3_A3

A3

DAISY_CHAIN_NCTF_A4

A4

DAISY_CHAIN_NCTF_A60

A60

DAISY_CHAIN_NCTF_A61_B61

A61

DAISY_CHAIN_NCTF_A62

A62

DAISY_CHAIN_NCTF_AV1

AV1

DAISY_CHAIN_NCTF_AW1

AW1

DAISY_CHAIN_NCTF_AW2_AY2

AW2

DAISY_CHAIN_NCTF_AW3_AY3

AW3

DAISY_CHAIN_NCTF_AW61_AY61

AW61

DAISY_CHAIN_NCTF_AW62_AY62

AW62

DAISY_CHAIN_NCTF_AW63

AW63

AV63

AU63

C63

C62

B43

A51

B51

L60

N60

W23

Y22

AY15

AV62

D58

P22

N21

P20

R20

OPIO_COMP

R52 49.9R1%0402R52 49.9R1%0402

C

TPJNC20TPJNC20

TPJNC7TPJNC7

TPJNC28TPJNC28

TPJNC23TPJNC23

TPJNC2TPJNC2

U2R

U2R

AT2

RSVD

AU44

RSVD

AV44

RSVD

D15

RSVD

F22

RSVD

H22

RSVD

J21

RSVD

D

HSW_ULT_DDR3L

HSW_ULT_DDR3L

18 OF 19

18 OF 19

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

N23

R23

T23

U10

AL1

AM11

AP7

AU10

AU15

AW14

AY14

E

R215 1KR0402R215 1KR0402

CFG4 DISPLAY PORT PRESENCE STRAP

4 4

0: ENABLED

EMBEDDED DISPLAY PORT

1: DISABLED;

NO PHYSICAL DISPLAY PORT ATTACHED TO EMBEDDED DISPLAY PORT

A

CFG4

Title

Title

Title

HASWELL ULT (GND2)

HASWELL ULT (GND2)

HASWELL ULT (GND2)

ize Document Number Rev

Size Document Number Rev

Size Document Number Rev

S

B

B

B

MS-7859

MS-7859

MS-7859

Date: Sheet of