Page 1

1

2

3

4

5

6

7

8

Lenovo Mississippi_uATX Schematic

Rev:0.4

SHEET# DESCRIPTIONSHEET# DESCRIPTION

A A

PAGE1

PAGE2

PAGE3

PAGE4

PAGE5

B B

PAGE6

PAGE7

PAGE8

PAGE9

PAGE10

PAGE11

PAGE12

C C

PAGE13

PAGE14

PAGE15

PAGE16

PAGE17

PAGE18

D D

PAGE19

PAGE20

PAGE21

PAGE22

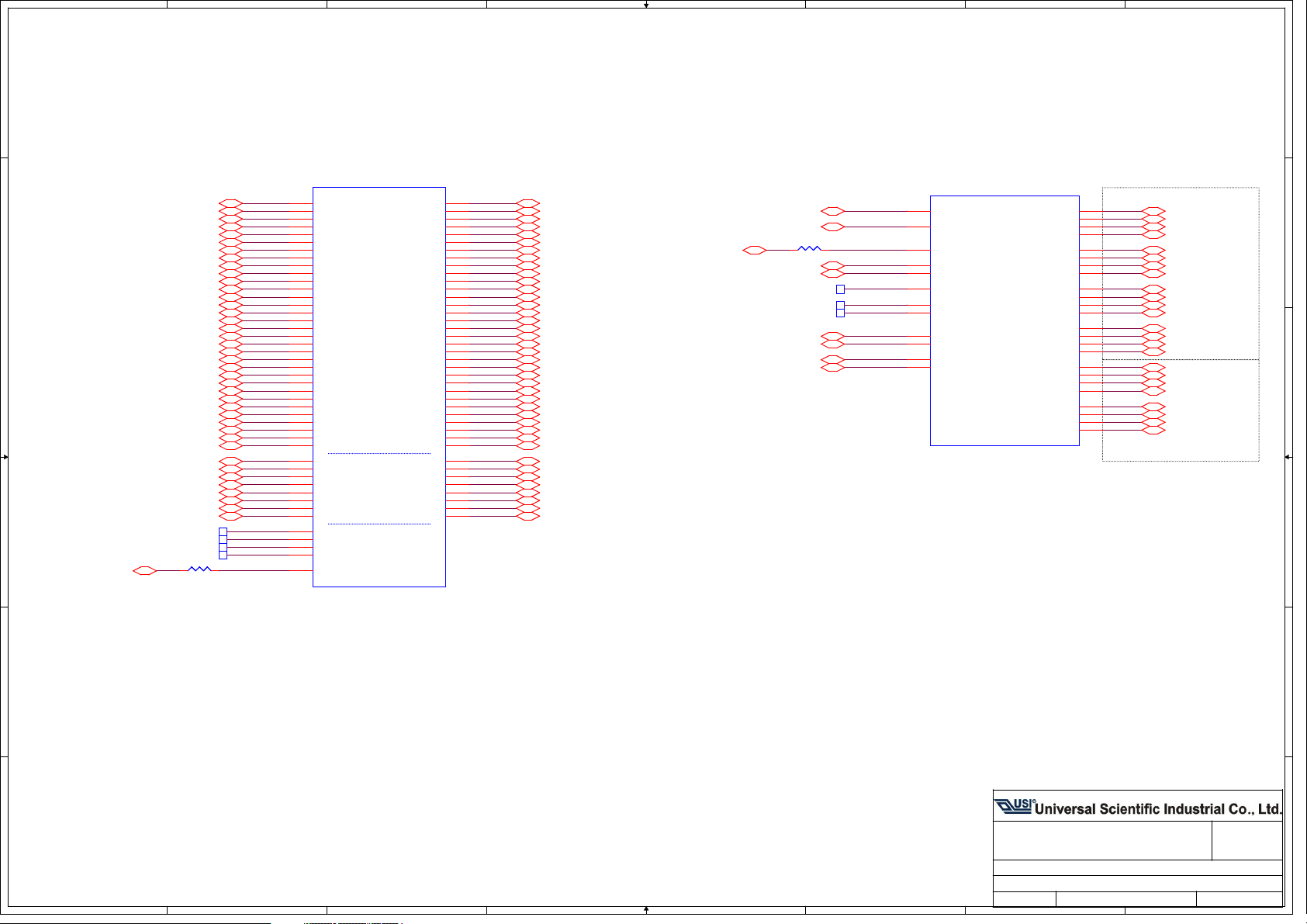

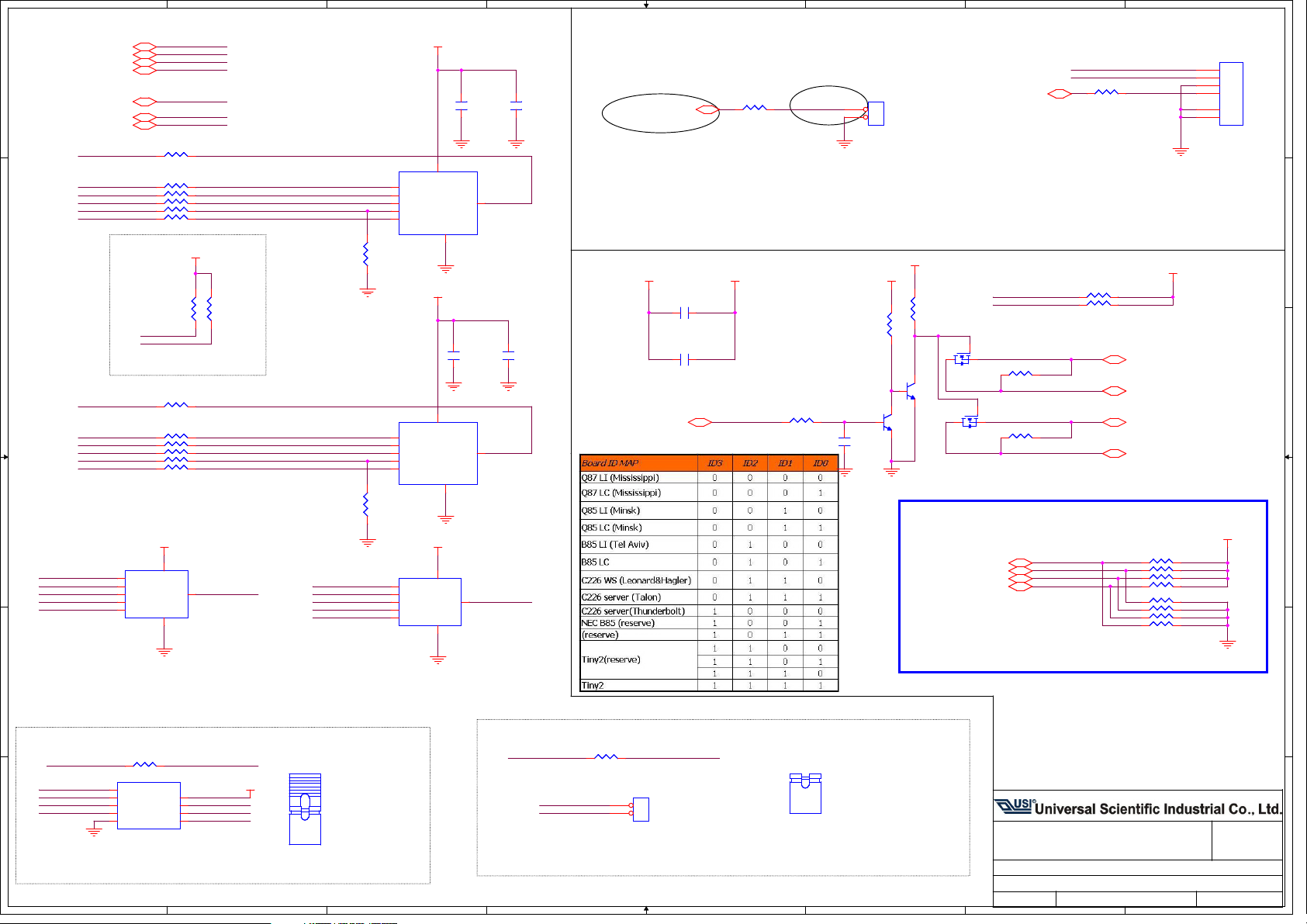

INDEX

BLOCK DIAGRAM

XDP DEBUG PORT

HASWELL SOCKET(MISC)

HASWELL SOCKET(PEGDMIFDI)

HASWELL SOCKET(MEMORY)

HASWELL SOCKET(POWER)

HASWELL SOCKET(GND)

HASWELL SOCKET(DECOUPLING)

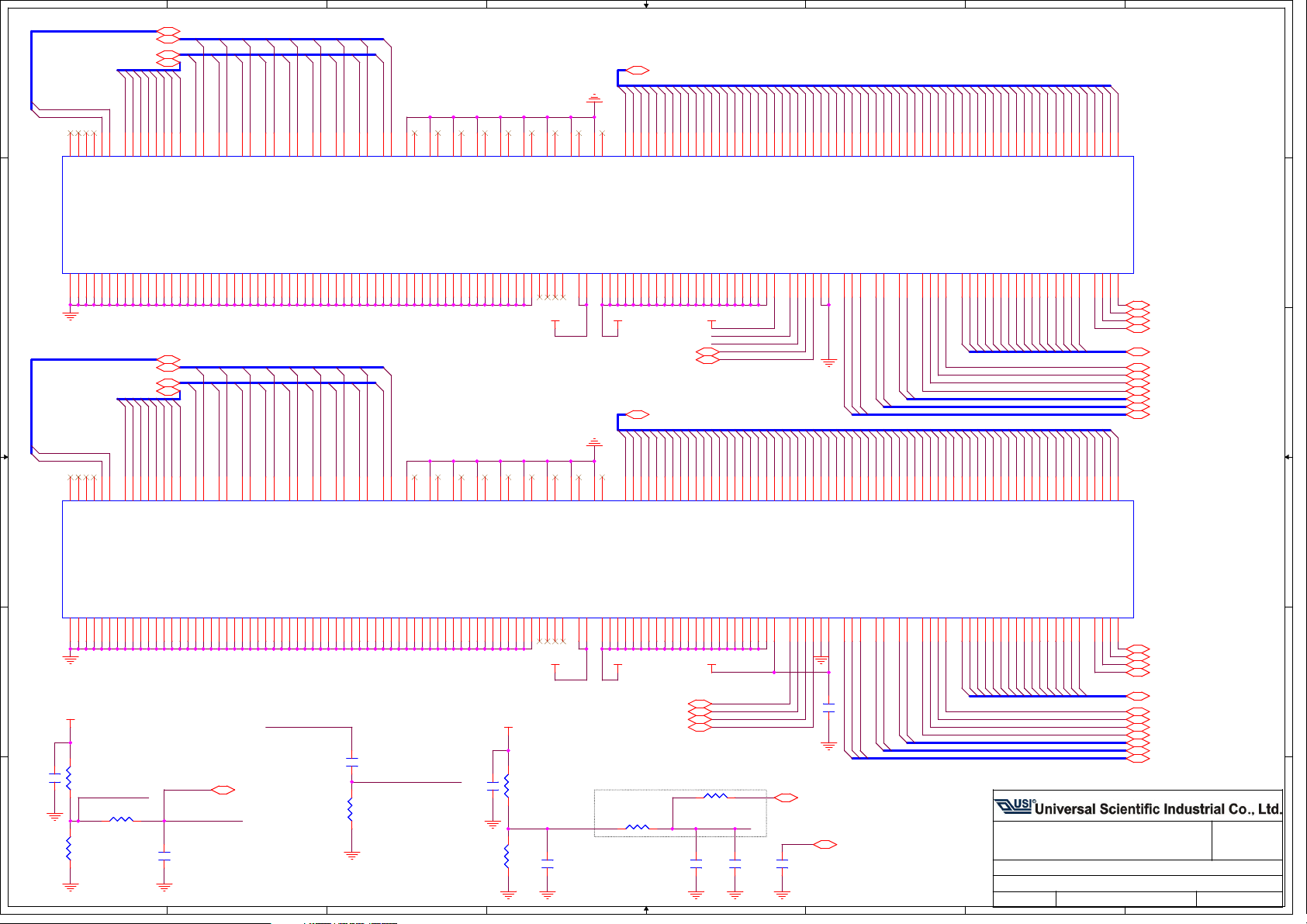

DDR3 UDIMM CHANNEL A

DDR3 UDIMM CHANNEL B

DECOUPLING

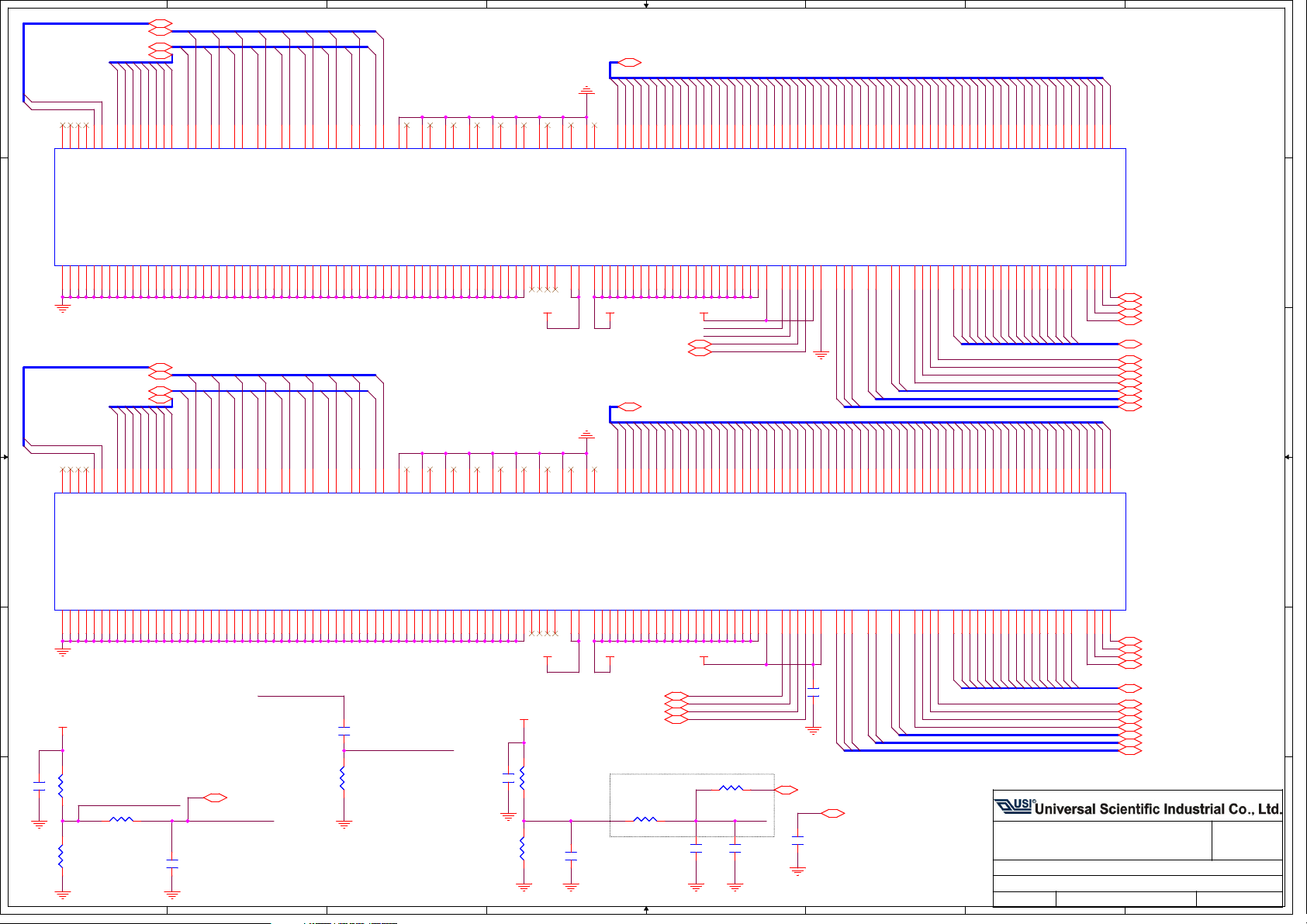

PCH (FDI_DMI_PCIE_USB)

PCH (CLOCK GEN)

PCH (SATA_QST)

PCH (LPC_HDA_SPI_SMB)

PCH (SPI_BOARD ID_iBUTTON)

PCH (DISPLAY)

PCH (POWER)

PCH (GND)

PCH (DECOUPLING)

PCI EXPRESS X16 SLOT

PAGE23 PCI EXPRESS X1& X16 (X4) SLOT

PAGE24 INTERNAL HDMI PORTD

PAGE25 REAR DP PORTC

E E

PAGE26 VGA_DP PORTB

PAGE27 F_USB3.0

PAGE28

PAGE29

PAGE30

PAGE31

F F

PAGE32

PAGE33

BLANK

F_USB2.0

REAR USB2.0 PORT_USB POWER ON

REAR USB3.0 PORT

SATA CONN

BLANK

CM

1

2

3

4

PAGE34

PAGE35

PAGE36

PAGE37

PAGE38

PAGE39

PAGE40

PAGE41

PAGE42

PAGE43

PAGE44

PAGE45

PAGE46

PAGE47

PAGE48

PAGE49

PAGE50

PAGE51

PAGE52

PAGE53

PAGE55

PAGE56

PAGE58

PAGE59

PAGE60

PAGE61

PAGE62

PAGE63

5

AUDIO CODEC ALC662VD

AUDIO JACK

LAN

TPM_ASSET ID

RSMRST LOGIC

SIO IT8733

LPT_THERMAL SENSOR

FAN CONNECTOR

COM_KBMS

PCIe TO PCI BRIDGE

PCI SLOT

ATX POWER_FPANEL CONN

VRD12 CONTROL

VRD12 OUTPUT DRIVE

SM VR

3.3VAUX VR&VCC1.5V_PCH

1.05V_PCH&ME VR

5V DUAL VR

VCC3 & VCC5

FLEXIBLE IO ASSIGN

HOLE_HEATSINKPAGE54

RESET MAP

SMBUS MAP

DSW SEQUENCEPAGE57

POWER SEQUENCE

POWER DISTRIBUTION

CLOCK DISTRIBUTION

GPIO TABLE

H/W STRAP

PCB STACK

DescriptionReference

TITLE:

TITLE:

TITLE:

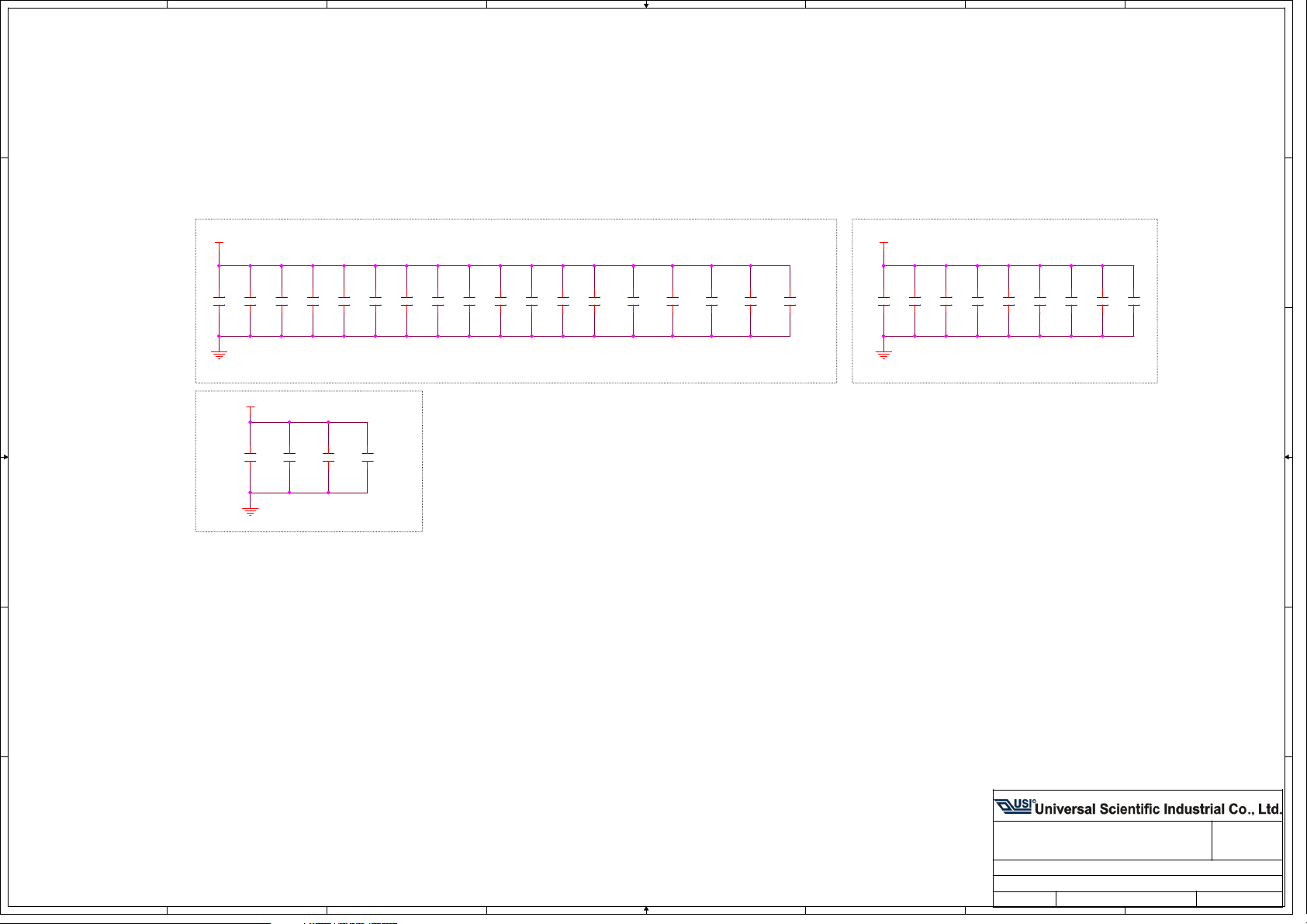

0.1UF_0402CB

Document N umber :

Document N umber :

0.01UF_0402CP

1UF_0603

6

Document N umber :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

Mississippi_uATX

Mississippi_uATX

Mississippi_uATX

INDEX

INDEX

INDEX

<Doc>

<Doc>

<Doc>

Kerry Huang

Kerry Huang

Kerry Huang

Date: PAGE:

Date: PAGE:

Date: PAGE:

A3

A3

A3

7

Friday, November 30, 2012

Friday, November 30, 2012

Friday, November 30, 2012

8

REV:

REV:

REV:

V0.4

V0.4

V0.4

1 63

1 63

1 63

of

of

of

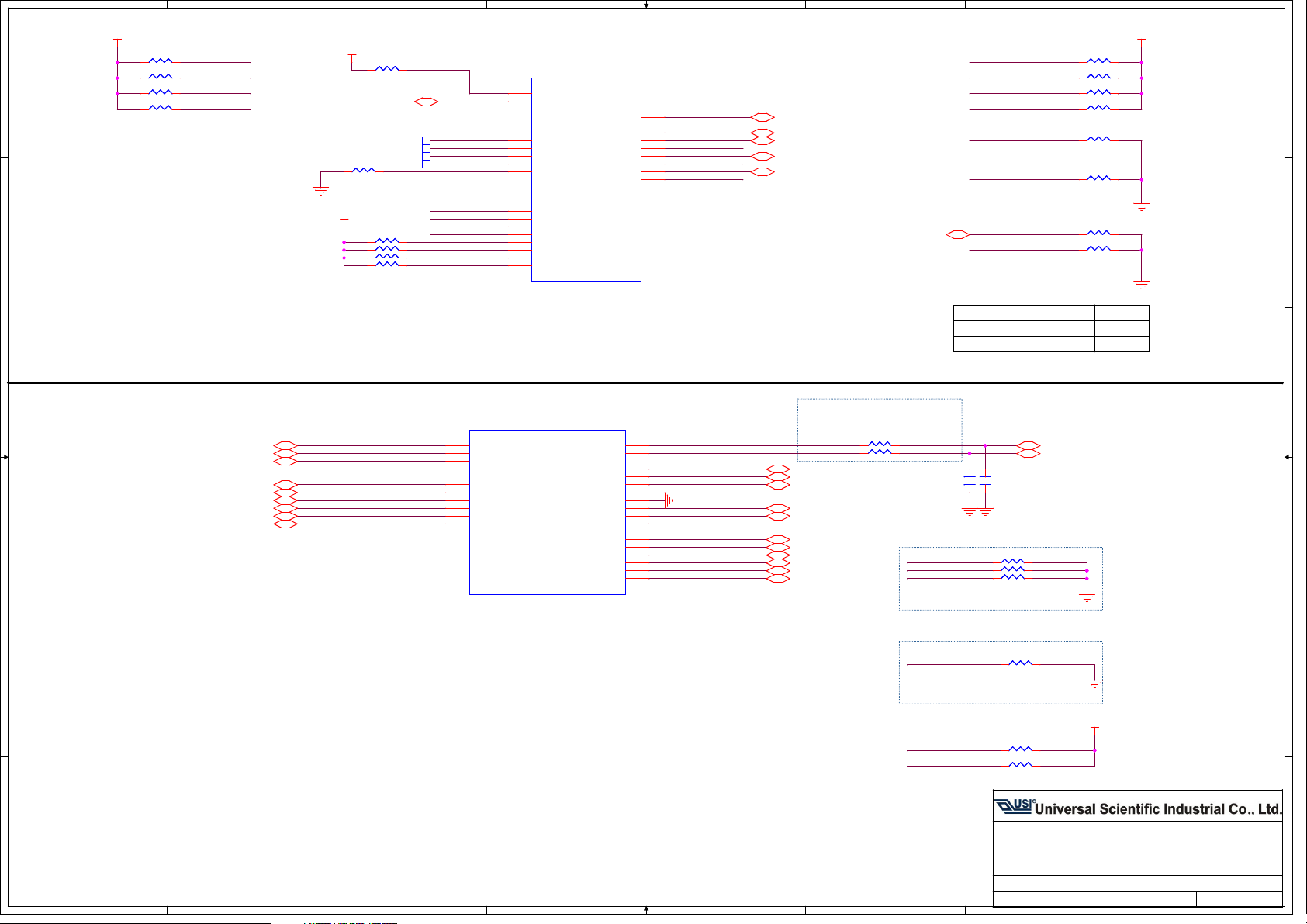

Page 2

1

2

3

4

5

6

7

8

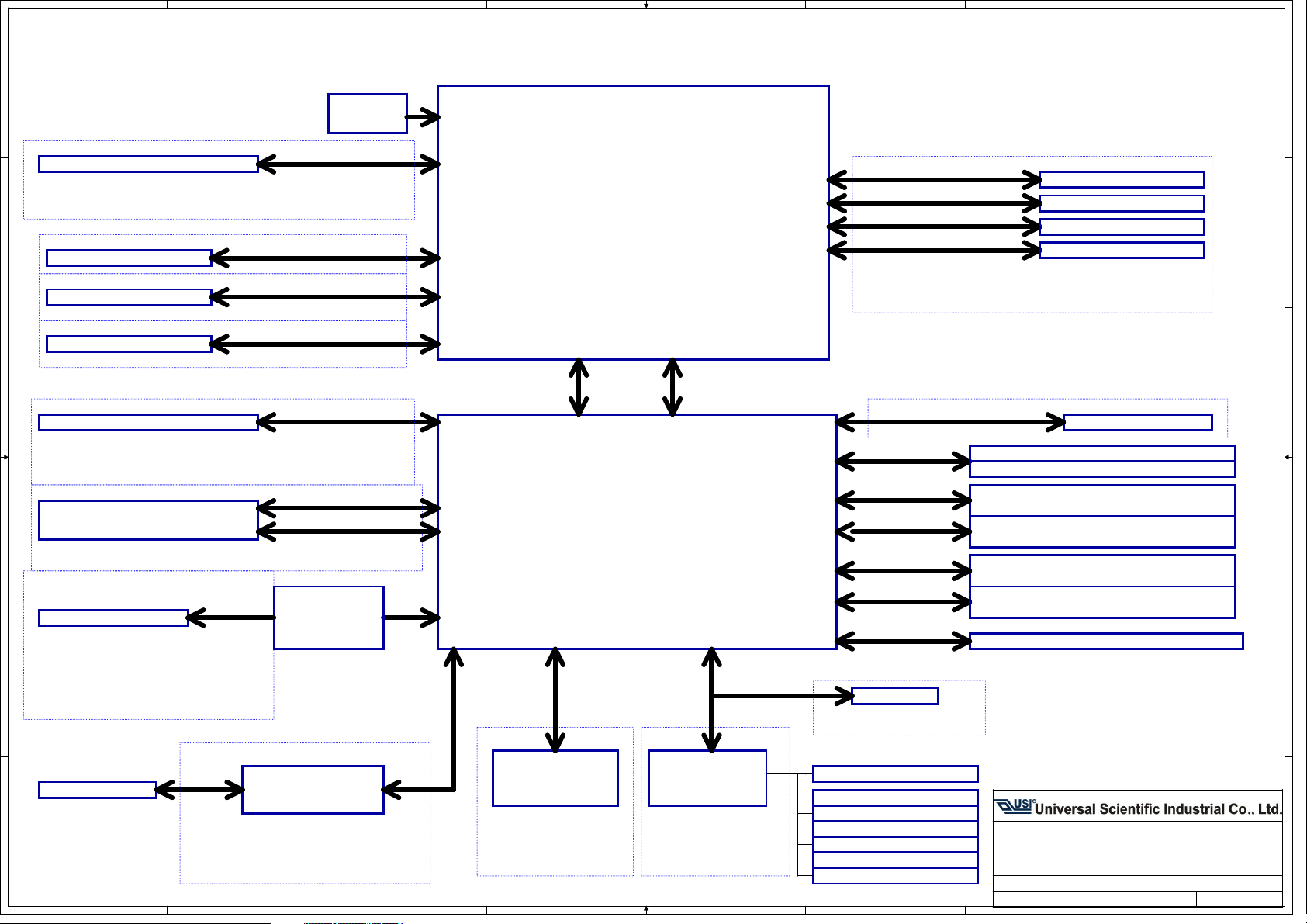

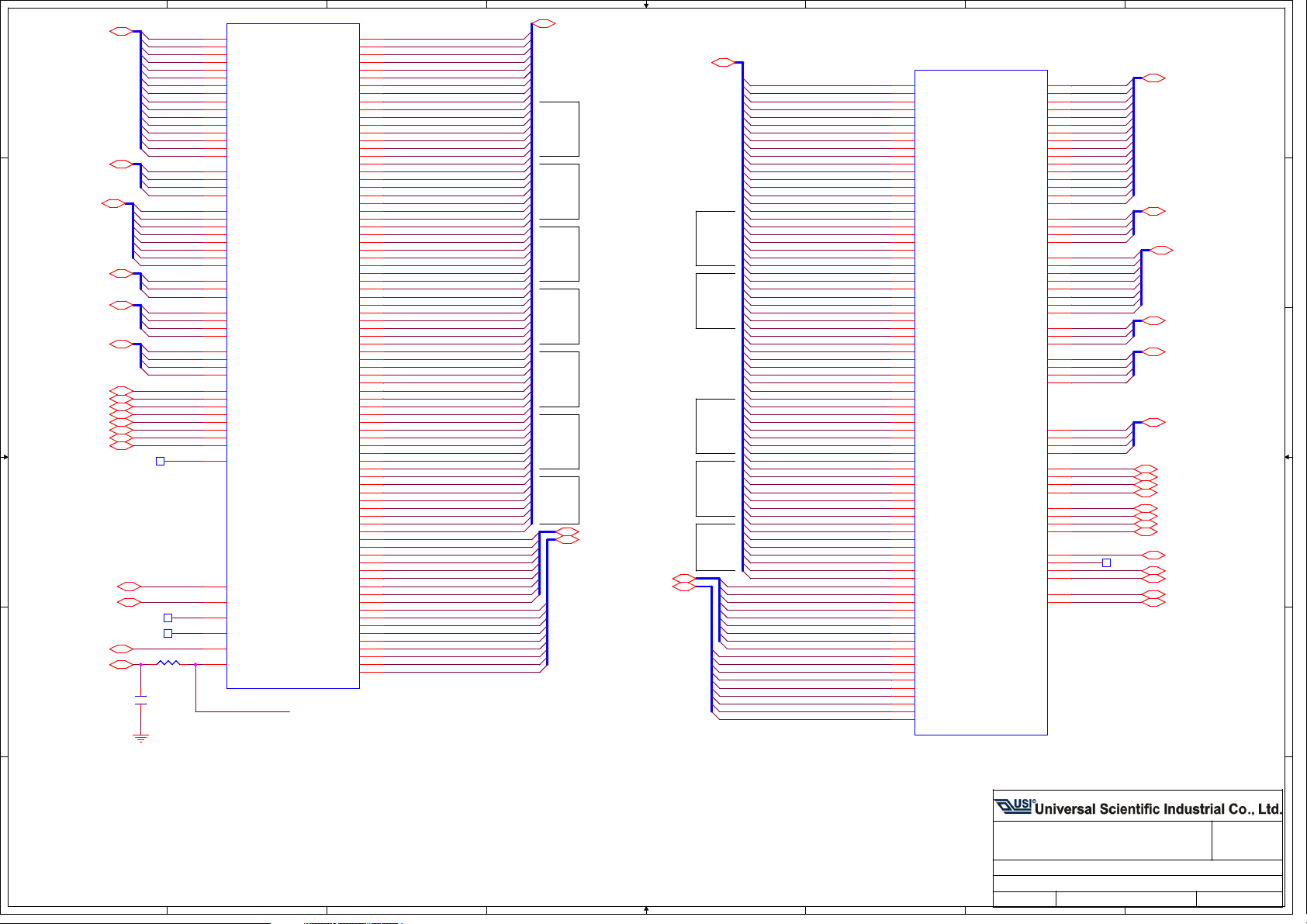

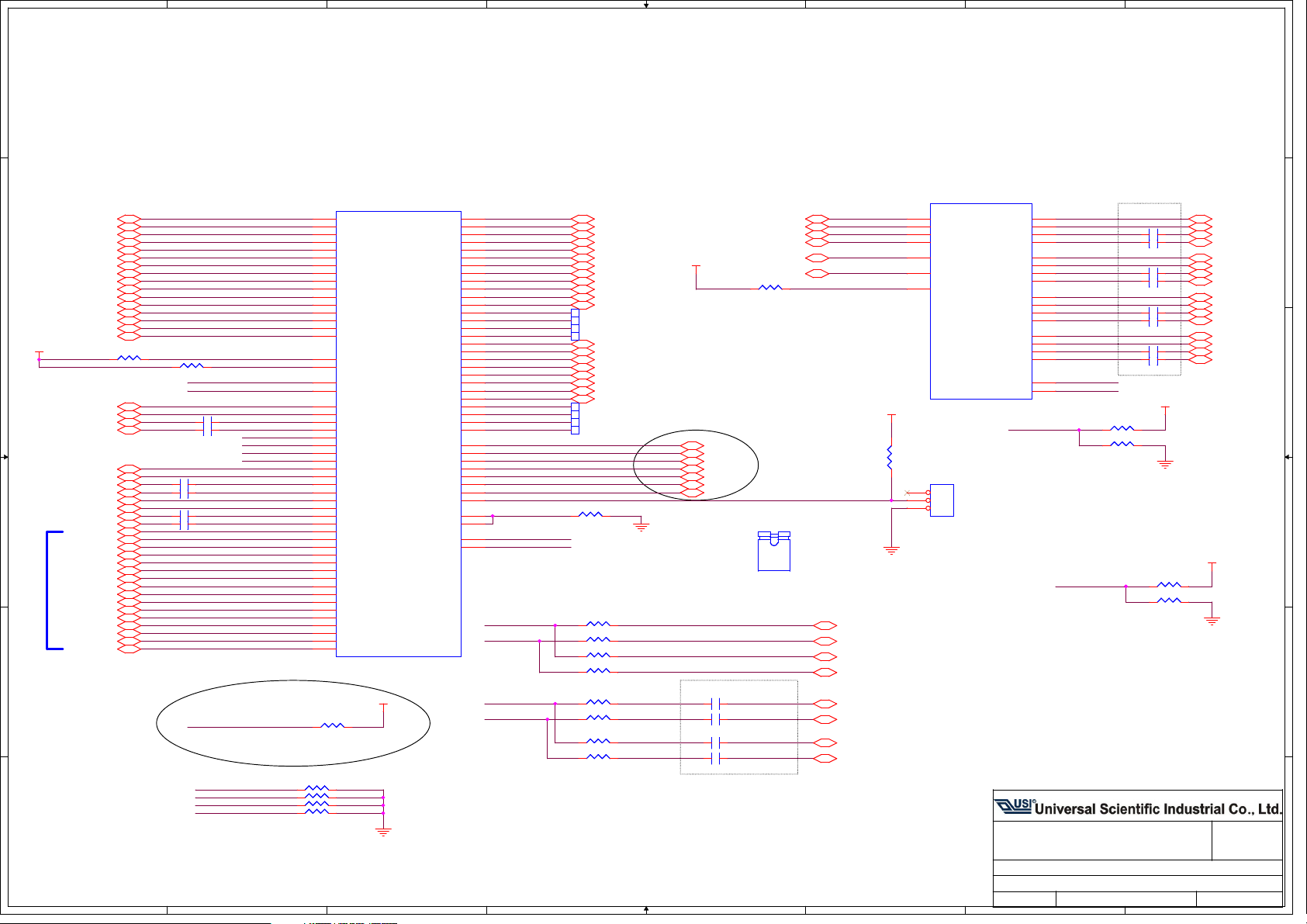

Block Diagram - Mississippi_uATX

A A

VRD 12.5

4 Phase

PCI-e x16 (X16)

PCI Express 3.0

x16

Haswell Processor

Voltage: 12V, 3.3V, 3.3VAUX

Clock: 100MHz

B B

REAR DP CONN

DDIB

CPU core: 0.5V~2.3V

Intel

DDR3 1066/1333/1600

DDR3 1066/1333/1600

DDR3 1066/1333/1600

DDR3 1066/1333/1600

CHA DIMM0

CHA DIMM1

CHB DIMM0

CHB DIMM1

REAR DP CONN

INTERNAL HDMI CONN

C C

PCI-e x16 Slot*1

Voltage: 12V, 3.3V, 3.3VAUX

Clock: 100MHz

PCI-e x1 Slot*1

D D

Voltage: 12V, 3.3V, 3.3VAUX

Clock: 100MHz

DDIC

DDID

PCI Express 2.0

PCI Express 2.0

CLINK

x4

x1

FDI X2 DMI X4(Gen 2)

Lynxpoint

PCH

(4.1W)

Voltage: 1.5V,1.05V,3.3VSB,

3.3V

DISPLAY I/O

SATA3

USB2.0

USB3.0/2.0

USB2.0

Clock: 32.768K/14/33/48/96/100MHz

PCIE to PCI

Bridge

x1

PCI-32/33 Slot*1

PCI 2.3

IT8893E

Voltage: 3.3V,5V,12V,

-12 V,3.3VAUX

E E

Clock: 33MHz

PCI Express 2.0

HDA

LPC

USB3.0/2.0

SPI

TPM

Voltage:3.3VAUX

Voltage: 0.75V, 1.5V

VGA CONN

SATA3 Box*4

eSATA Box*1

Front USB Header*2Ports

Front USB Header*2Ports

Rear USB CONN*2Ports

Rear USB CONN*4Ports

SPI Flash ROM(8MB+4MB)

Clock: 33MHz

Audio Codec

GLAN CONN *1

F F

Voltage:3.3VAUX, 1.2VAUX,

1.8VAUX

Intel CLARKVILLE

Clock: 25MHz/100MHz

1

2

3

ALC662VD

Voltage:3.3V,5V

Clock: 24MHz

4

Voltage:3.3V,

3.3VAUX

Clock: 48/33MHz

SIO

IT8733

PS/2 KB/MS HDR

COM CONN*1(Rear)

COM Header*1

Thermal monitor x2

FAN Header*4

SPI(1MB)*1

LPT Header*1

5

6

TITLE:

TITLE:

TITLE:

Mississippi_uATX

Mississippi_uATX

Mississippi_uATX

BLOCK DIAGR AM

BLOCK DIAGR AM

BLOCK DIAGR AM

Document N umber :

Document N umber :

Document N umber :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

A3

<Doc>

<Doc>

<Doc>

Kerry Huang

Kerry Huang

Kerry Huang

Date: PAGE:

Date: PAGE:

Date: PAGE:

Friday, November 30, 2012

Friday, November 30, 2012

Friday, November 30, 2012

7

8

REV:

REV:

REV:

V0.4

V0.4

V0.4

2 63

2 63

2 63

of

of

of

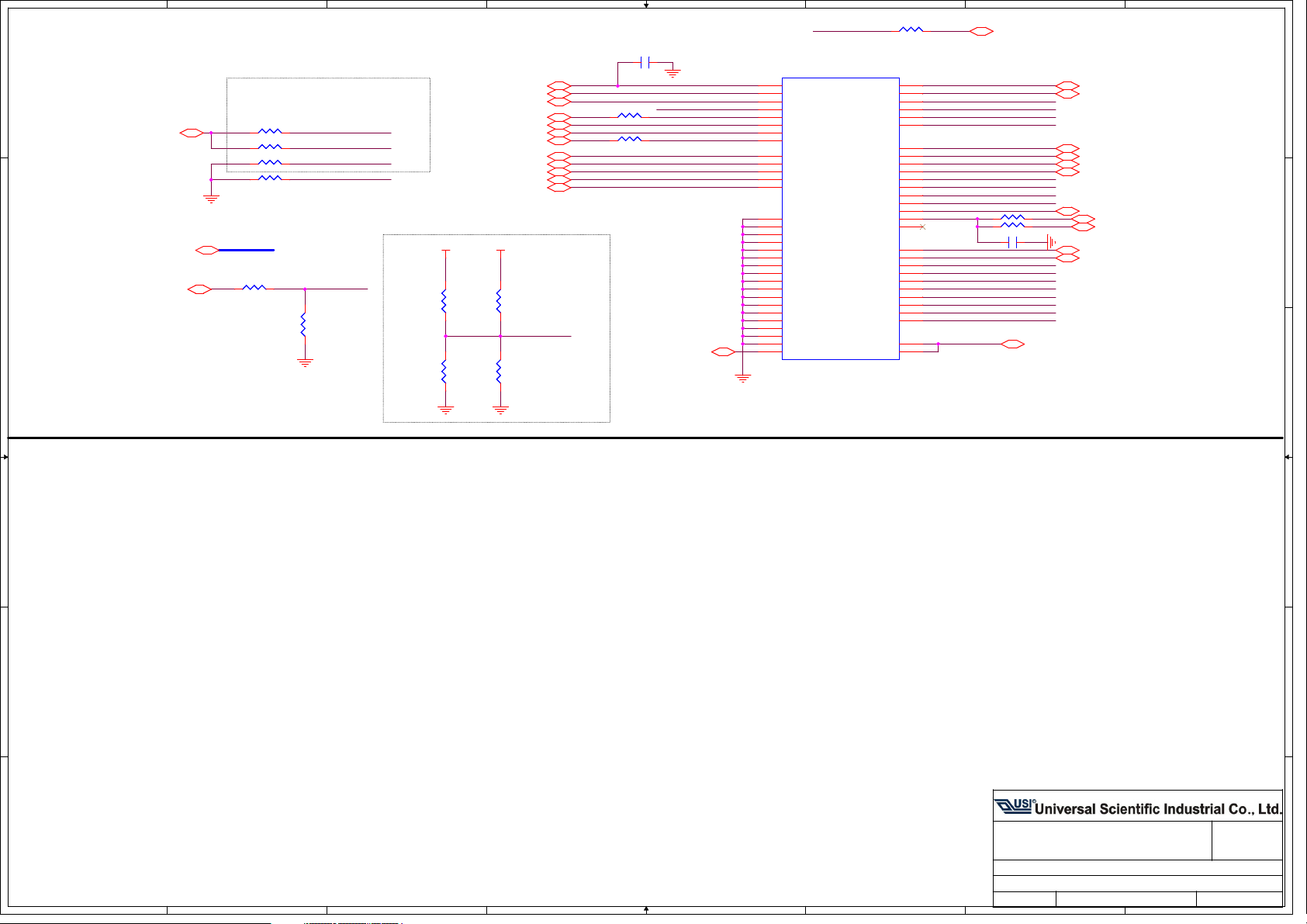

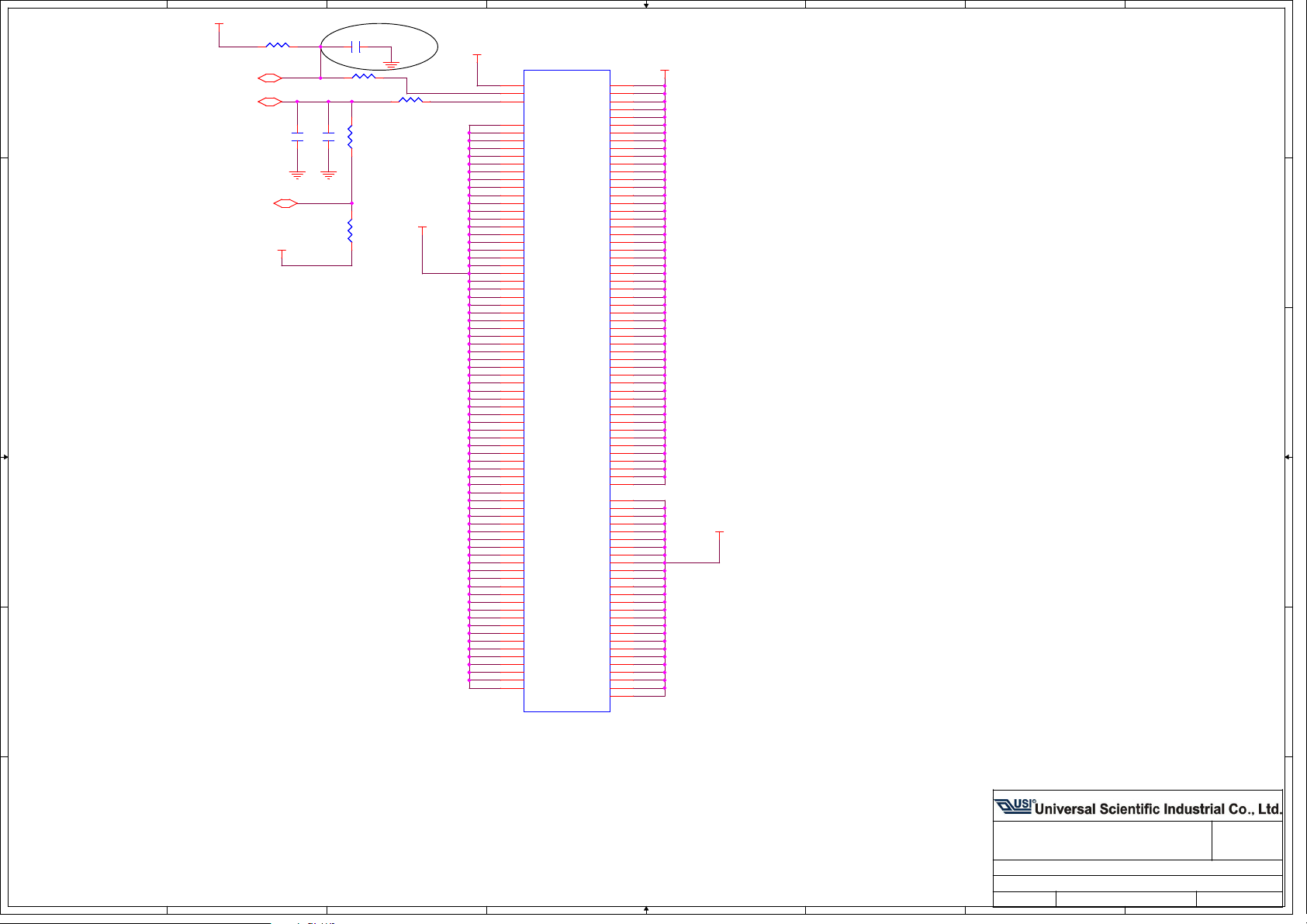

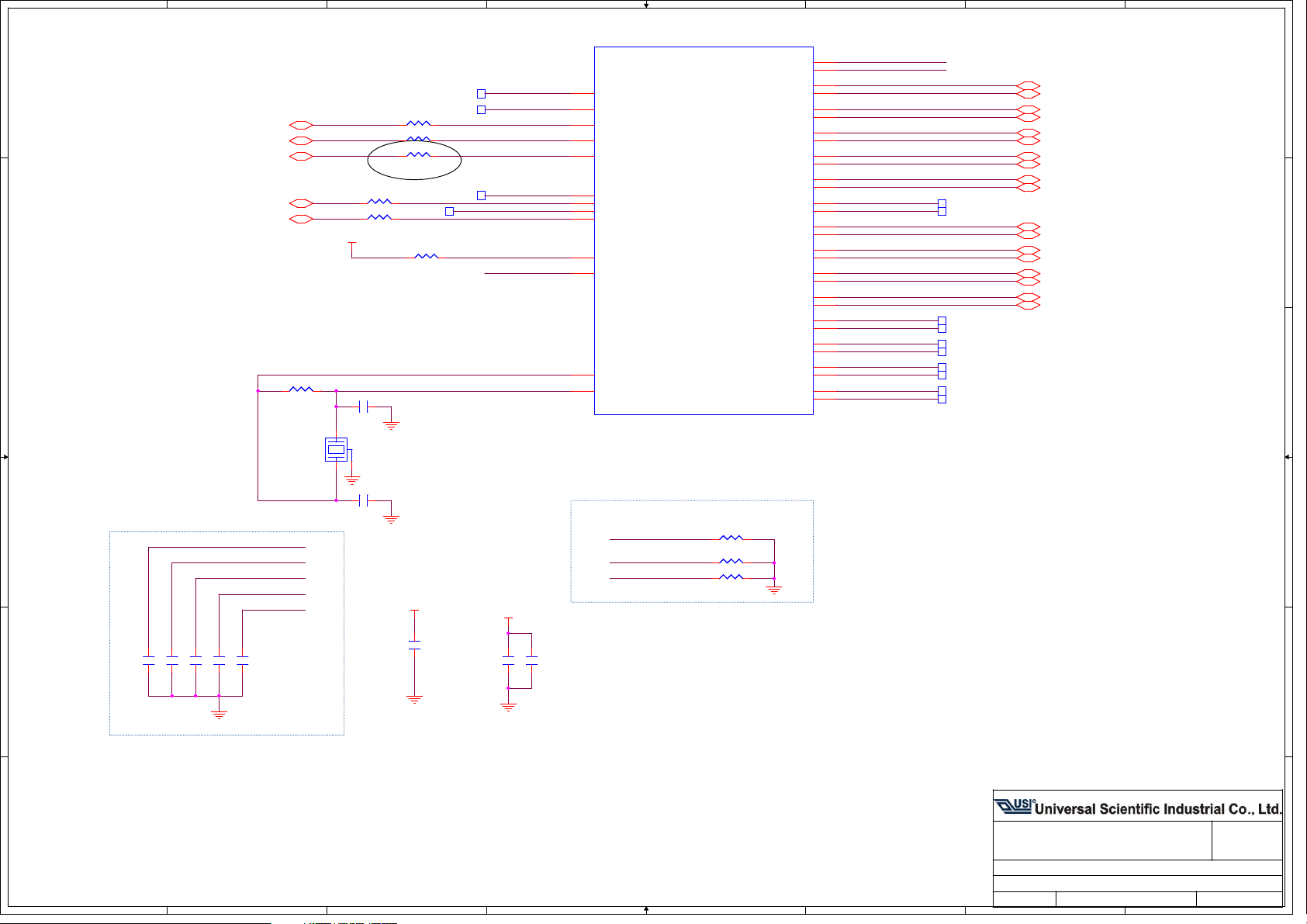

Page 3

1

CPU DEBUG CONN

A A

V_CPU_V CCIO_RIGHT3,4,46,7

B B

TPEV_PC UDEBUG[0..15]4

H_PW RGD16,4,46

C C

2

PLACE NEAR CPU

H_TCK TERMINATIOM PLACE NEAR CPU WITHIN 1.1 INCH

0402

0402

R332

R332

X_1K

X_1K

H_TDI

H_TMS

H_TCK

H_TRST_ N

XDP_PW RGD

R52 X_51R

R52 X_51R

R58 X_51R

R58 X_51R

R59 51R

R59 51R

R60 51R

R60 51R

R61 1K

R61 1K

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

3

VCC1.05V _PCH VCC3

0402

R56

R56

51R

51R

R68

R68

X_825R_ 1%

X_825R_ 1%

0402

0402

0402

4

CB48CB48

DBRESET _N16,4,45

CK_100M _CPU_XDP_DN14

CK_100M _CPU_XDP_DP14

PLTRST_ CPU_N15,4

SMB_CLK10,11,17,3 7

SMB_DAT A10,11,17,3 7

SW_ ON_N16,23,39,4 2,45

H_TDO4

H_TDI4

H_TMS4

H_TCK4

H_TRST_ N4

0402

0402

R70

R70

X_249R_ 1%

X_249R_ 1%

H_TDO

0402

0402

R78

R78

X_249R_ 1%

X_249R_ 1%

R55 1K

R55 1K

R54 1K

R54 1K

0402

0402

0402

0402

PRIVACY_MSR_ EN_N4

H_CPURS T_XDP_R_N

DBRESET _N

XDP_PW RGD

SMB_CLK

SMB_DAT A

XDP_SW _ON_N

5

XDP_PW R_DEBUG

J1

J1

48

HOOK7/DBR-

42

ITPCLK-/HOOK5

40

ITPCLK/HOOK4

39

HOOK0

46

HOOK6/RESET-

53

SCL

51

SDA

41

HOOK1

52

TDO

56

TDI

58

TMS

57

TCK0

54

TRSTn

1

GND1

2

GND2

7

GND3

8

GND4

13

GND5

14

GND6

19

GND7

20

GND8

25

GND9

26

GND10

31

GND11

32

GND12

37

GND13

38

GND14

49

GND15

50

GND16

59

GND17

60

GND18

HAVENDA LE_XDP_CONN

HAVENDA LE_XDP_CONN

OBSFN_A0

OBSFN_A1

OBSDATA_A0

OBSDATA_A1

OBSDATA_A2

OBSDATA_A3

OBSFN_B0

OBSFN_D0

OBSFN_B1

OBSFN_D1

OBSDATA_B0

OBSDATA_B1

OBSDATA_B2

OBSDATA_B3

HOOK2

HOOK3

TCK1

OBSFN_C0

OBSFN_C1

OBSDATA_C0

OBSDATA_C1

OBSDATA_C2

OBSDATA_C3

OBSDATA_D0

OBSDATA_D1

OBSDATA_D2

OBSDATA_D3

VCC_OBS_AB

VCC_OBS_CD

6

R82 0R

R82 0R

0402

0402

3

5

9

TPEV_PC UDEBUG0

11

TPEV_PC UDEBUG1

15

TPEV_PC UDEBUG2

17

TPEV_PC UDEBUG3

21

22

23

24

27

TPEV_PC UDEBUG4

29

TPEV_PC UDEBUG5

33

TPEV_PC UDEBUG6

35

TPEV_PC UDEBUG7

45

XDP_PW R_DEBUG

47

CPU_HOO K3

55

4

6

10

TPEV_PC UDEBUG8

12

TPEV_PC UDEBUG9

16

TPEV_PC UDEBUG10

18

TPEV_PC UDEBUG11

28

TPEV_PC UDEBUG12

30

TPEV_PC UDEBUG13

34

TPEV_PC UDEBUG14

36

TPEV_PC UDEBUG15

43

44

7

PWR_ DEBUG 4

R81 X_0R

R81 X_0R

0402

0402

R91 0R

R91 0R

0402

0402

CB50CB50

V_CPU_V CCIO_RIGHT 3,4,46,7

H_PREQ_ N 4

H_PRDY_N 4

CPU_BPM _0 4

HSW_ PCUSTB_1_DP 4

CPU_BPM _1 4

HSW_ PCUSTB_1_DN 4

XDP_PW R_DEBUG 4

VRMPW RGD 16,4,46

PCH_SYSPW ROK 16,39

HSW_ PCUSTB_0_DP 4

HSW_ PCUSTB_0_DN 4

8

PLACE NEAR XDP

D D

E E

TITLE:

TITLE:

TITLE:

Mississippi_uATX

Mississippi_uATX

F F

1

2

3

4

5

6

Mississippi_uATX

XDP DEBU G PORT

XDP DEBU G PORT

XDP DEBU G PORT

Document N umber :

Document N umber :

Document N umber :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

A3

<Doc>

<Doc>

<Doc>

Kerry Huang

Kerry Huang

Kerry Huang

Date: PAGE:

Date: PAGE:

Date: PAGE:

Friday, November 30, 2012

Friday, November 30, 2012

Friday, November 30, 2012

7

8

REV:

REV:

REV:

V0.4

V0.4

V0.4

3 63

3 63

3 63

of

of

of

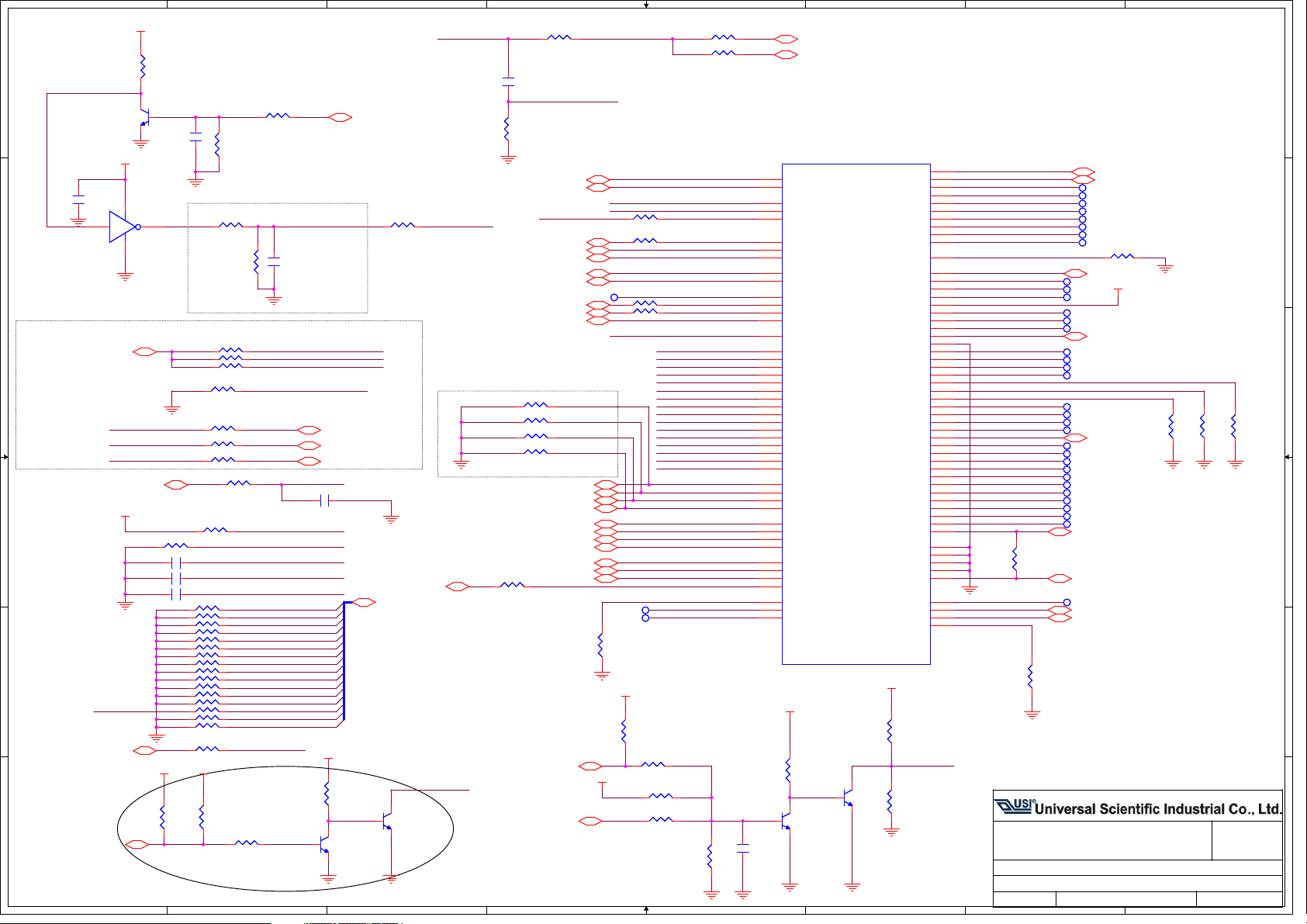

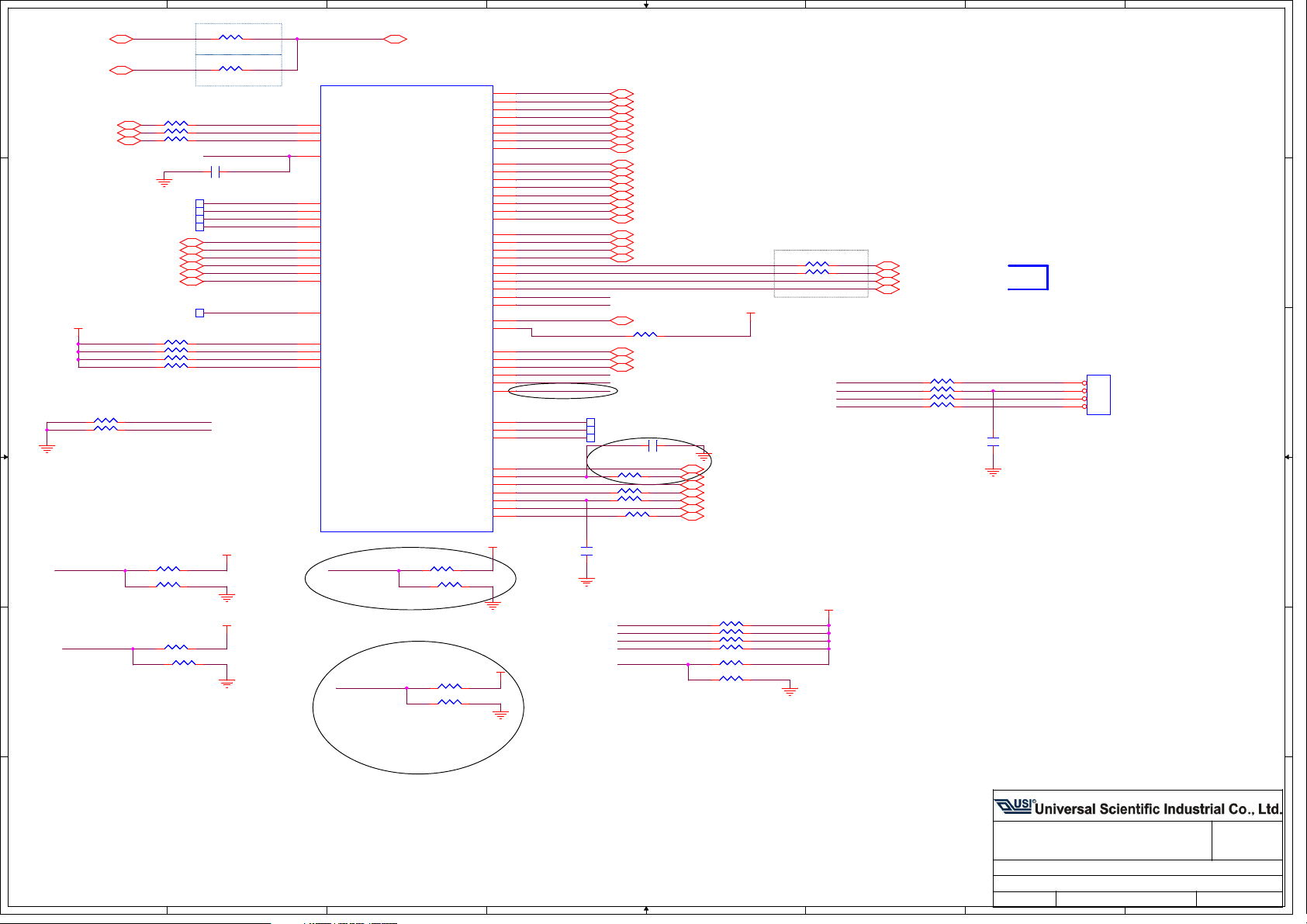

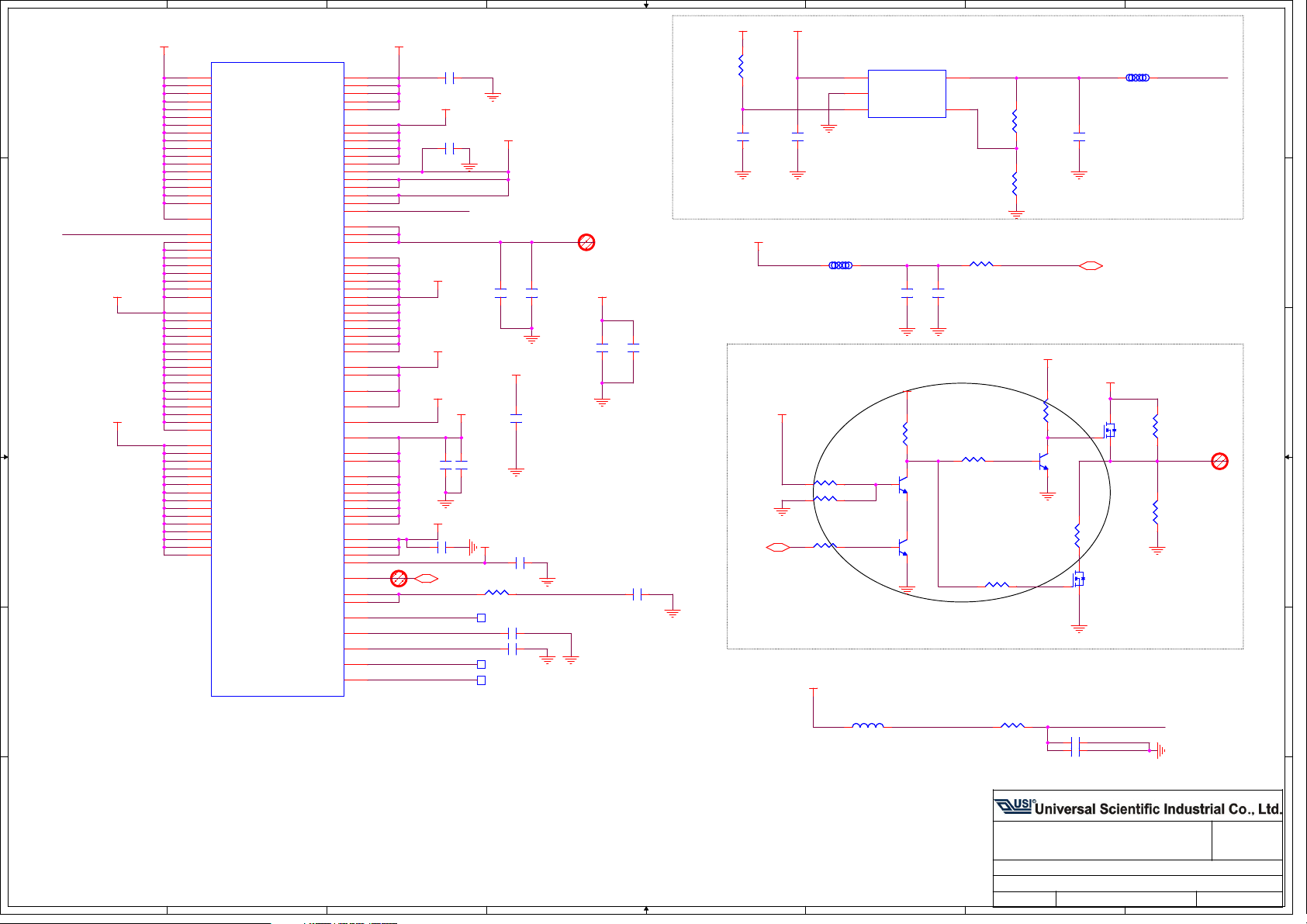

Page 4

1

SB3V_DS W

0402

0402

R336

R336

X_1K

X_1K

A A

B B

U93_1

CB46

CB46

X_0.1UF_ 0402

X_0.1UF_ 0402

U93A

U93A

1

Q130

Q130

SB3V_DS W

52

YA

YA

C

C

B

B

1

Q130_B

E

E

2 3

C664

C664

X_3904_SOT23

X_3904_SOT23

X_1UF_6.3V_X5R

X_1UF_6.3V_X5R

VCC

VCC

6

U93_6

X_SN74L VC2G14DCKR

X_SN74L VC2G14DCKR

GND

GND

SVID

R1279

V_CPU_V CCIO_RIGHT3,4,46,7

C C

H_VIDSCK

H_VIDSOUT

H_VIDALER T_N

V_CPU_V CCIO_RIGHT3,4,46,7

VCC1.05V _PCH

D D

E E

PRIVACY_MSR_ EN_N3

F F

PCH_GP816

1

HSW_ STRAP_13

R761 10K

R761 10K

C656 100PF_5 0V_NPOC656 100PF_5 0V_NPO

C663 X_10PF_ 50V_NPOC663 X_10PF_ 50V_NPO

C666 100PF_5 0V_NPOC666 100PF_5 0V_NPO

R1279

R95

R95

R1280

R1280

R325

R325

R596 0R

R596 0R

R598 0R

R598 0R

R690 0R

R690 0R

R1287

R1287

0402

0402

R752 X_1K

R752 X_1K

R753 X_1K

R753 X_1K

R754 X_1K

R754 X_1K

R435 X_1K

R435 X_1K

R743 X_1K

R743 X_1K

R559 X_1K

R559 X_1K

R744 X_1K

R744 X_1K

R739 X_1K

R739 X_1K

R745 X_1K

R745 X_1K

R740 X_1K

R740 X_1K

R746 X_1K

R746 X_1K

R741 X_1K

R741 X_1K

R747 X_1K

R747 X_1K

R742 X_1K

R742 X_1K

R748 X_1K

R748 X_1K

R749 X_1K

R749 X_1K

R343 1K

R343 1K

VCC3

SB3V

0402

0402

R984

R984

X_1K

X_1K

2

R282 X_10K

R282 X_10K

0402

0402

R285

R285

X_5K1

X_5K1

0402

0402

R65

R65

X_178R_ 1%

X_178R_ 1%

0402

0402

0402

0402

R66

R66

X_84R5_ 1%

X_84R5_ 1%

X_90R9_ 1%

X_90R9_ 1%

0402

0402

110R_1%

110R_1%

0402

0402

75R_1%

75R_1%

0402

0402

X_100R

X_100R

0402

0402

PLACE NEAR CPU

0402

0402

0402

0402

0402

0402

51R

0402

0402

1K

1K

0402

0402

CPU_DRA M_PWR_OK

TPEV_PC UDEBUG0

TPEV_PC UDEBUG1

TPEV_PC UDEBUG2

TPEV_PC UDEBUG3

TPEV_PC UDEBUG4

TPEV_PC UDEBUG5

TPEV_PC UDEBUG6

TPEV_PC UDEBUG7

TPEV_PC UDEBUG8

TPEV_PC UDEBUG9

TPEV_PC UDEBUG10

TPEV_PC UDEBUG11

TPEV_PC UDEBUG12

TPEV_PC UDEBUG13

TPEV_PC UDEBUG14

TPEV_PC UDEBUG15

TPEV_PC UDEBUG3

51R

H_THERM TRIP_N

PLTRST_ CPU_N

R1283

R1283

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

0402

to fix VCC3 lea kage

0402

0402

R961

R961

X_1K

X_1K

R966

R966

X_10K

X_10K

Q246_2

0402

0402

2

PLTRST_ N 18,22,36,3 9,54

PLTRST_ CPU_U93_N

C16

C16

X_10PF_ 50V_NPO

X_10PF_ 50V_NPO

CLOSE TO U93

H_VIDSCK

H_VIDSOUT

H_VIDALER T_N

H_VIDALER T_N_R

H_VIDSCK_ VR 46

H_VIDSOUT _VR 46

H_VIDALER T_VR_N 46

H_PROCH OT_N

C682 0.022UF_ 16V_X7RC682 0.022UF_ 16V_X7R

H_PW RGD

H_PW RGD

SB3V

0402

0402

R962

R962

X_10K

X_10K

Q246_6

C

C

B

B

2

E

E

Q246A

Q246A

1 6

X_MBT3904DW1T1G

X_MBT3904DW1T1G

3

DIMM_CA_C PU_VREF_A DIMM_CA_C PU_VREF_A_R

PLTRST_ CPU_N

X_0R

X_0R

R79

R79

0402

0402

CLOSE TO CPU

DBRESET _N16,3,45

TPEV_PC UDEBUG[0..15] 3

HSW_ STRAP_13

C

C

B

B

5

E

E

4 3

Q246B

Q246B

X_MBT3904DW1T1G

X_MBT3904DW1T1G

3

C658

C658

0.022UF_ 16V_X7R

0.022UF_ 16V_X7R

DIMM_CA_C PU_VREF_A_RC

0402

0402

R1289

R1289

24R9_1%

24R9_1%

CK_PE_1 00M_DMI_DN14

CK_PE_1 00M_DMI_DP14

H_DRAMP WRGD16

H_PW RGD16,3,46

PLTRST_ CPU_N15,3

H_PROCH OT_N46

PCH_THE RMTRIP_N15

R969 X_1K

R969 X_1K

R970 X_1K

R970 X_1K

R978 X_1K

R978 X_1K

R980 X_1K

R980 X_1K

CLOSE TO CPU

HSW_ PCUSTB_0_DP3

HSW_ PCUSTB_0_DN3

HSW_ PCUSTB_1_DP3

HSW_ PCUSTB_1_DN3

R308 0R

R308 0R

0402

0402

XDP_PW R_DEBUG3

4

2R_1%

2R_1%

R411

R411

0402

0402

H_VIDALER T_N H_VIDALER T_N_R

H_PM_SYNC _015

H_PECI15,39

H_SKTOC C_N16,45

0402

0402

0402

0402

0402

0402

0402

0402

H_TRST_ N3

H_PRDY_N3

H_PREQ_ N3

VRMPW RGD16,3,46

4

H_TCK3

H_TDI3

H_TDO3

H_TMS3

R1278 44R2_1 %

R1278 44R2_1 %

R69

R69

T60T60

R1284

R1284

R80

R80

T51T51

T50T50

0402

0402

R309

R309

49R9_1%

49R9_1%

VCC3

VCORE

R955 X_10K

R955 X_10K

R951 X_10K

R951 X_10K

H_PECI

TP_CPU_ M36

DIMM_CA_C PU_VREF_A

0402

0402

R982

R982

X_10K

X_10K

R370

R370

R371

R371

H_VIDSCK

H_VIDSOUT

0402

0402

CPU_DRA M_PWR_OK

0R

0R

0402

0402

H_PW RGD

PLTRST_ CPU_N

H_PROCH OT_CPU_N

56R

56R

0402

0402

H_THERM TRIP_N

0R

0R

0402

0402

TPEV_PC UDEBUG0

TPEV_PC UDEBUG1

TPEV_PC UDEBUG2

TPEV_PC UDEBUG3

TPEV_PC UDEBUG4

TPEV_PC UDEBUG5

TPEV_PC UDEBUG6

TPEV_PC UDEBUG7

TPEV_PC UDEBUG8

TPEV_PC UDEBUG9

TPEV_PC UDEBUG10

TPEV_PC UDEBUG11

TPEV_PC UDEBUG12

TPEV_PC UDEBUG13

TPEV_PC UDEBUG14

TPEV_PC UDEBUG15

HSW_ PCUSTB_0_DP

HSW_ PCUSTB_0_DN

HSW_ PCUSTB_1_DP

HSW_ PCUSTB_1_DN

XDP_DBR ESET_N

TESTLOW _2

TP_PROC ESSOR_K8

TP_PROC ESSOR_J10

R981

R981

X_10K

X_10K

0402

0402

0402

0402

0402

0402

Q236_2

0402

0402

R953

R953

X_10K

X_10K

5

0R

0R

0402

0402

0R

0R

0402

0402

DIMM_CA_V REF_A 10

DIMM_CA_V REF_B 11

6

7

8

CPU MISC

J3E

J3E

V4

BCLKN

V5

BCLKP

C38

VIDSCLK

C37

VIDSOUT

B37

VIDALERT-

AK21

SM_DRAMPWROK

AB35

PWRGOOD

M39

RESET-

P36

PM_SYNC

N37

PECI

M36

CATERR-

K38

PROCHOT-

F37

THERMTRIP-

D38

SKTOCC-

AB38

SM_VREF

AA37

CFG0

Y38

CFG1

AA36

CFG2

W38

CFG3

V39

CFG4

U39

CFG5

U40

CFG6

V38

CFG7

T40

CFG8

Y35

CFG9

AA34

CFG10

V37

CFG11

Y34

CFG12

U38

CFG13

W34

CFG14

V35

CFG15

Y36

CFG17

Y37

CFG16

V36

CFG19

W36

CFG18

D39

TCK

F38

TDI

F39

TDO

E39

TMS

E37

TRST-

L39

PRDY-

L37

PREQ-

G40

DBR-

N5

TESTLO

K8

RSVD_K8

J10

RSVD_J10

HASW ELL

HASW ELL

VCC3

Q236_6

Q236A

Q236A

C

C

B

B

2

E

E

1 6

C510

C510

X_0.1UF_16V_Y5V

X_0.1UF_16V_Y5V

5

0402

0402

R952

R952

X_10K

X_10K

5of10

5of10

PWR_DEBUG

RSVD_TP_1

RSVD_TP_J8

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

RSVD_AB36

RSVD_TP_AW2

RSVD_TP_AV1

VCOMP_OUT

RSVD_AB33

VCC_SENSE

VSS_SENSE

DPLL_REF_CLKN

DPLL_REF_CLKP

CFG_RCOMP

VCC1.05V _PCH

R243

R243

150R_1%

150R_1%

C

C

B

B

5

E

E

4 3

Q236B

Q236B

X_MBT3904DW1T1G

X_MBT3904DW1T1G

X_MBT3904DW1T1G

X_MBT3904DW1T1G

6

BPM0BPM1BPM2BPM3BPM4BPM5BPM6BPM7-

RSVD_T35

RSVD_M38

TESTLOW

RSVD_K9

RSVD_H15

RSVD_J9

RSVD_H14

VCC_1

RSVD_AV2

RSVD_J16

RSVD_H16

VSS_1

RSVD_V7

RSVD_AB6

RSVD_AC8

RSVD_U8

VSS_2

RSVD_Y8

RSVD_M10

RSVD_L10

RSVD_M11

RSVD_L12

RSVD_W8

RSVD_R33

RSVD_P33

VSS_3

VSS_4

VSS_5

VSS_6

RSVD_N35

0402

0402

PWR_ DEBUG

0402

0402

R301

R301

X_10K

X_10K

G39

J39

G38

H37

H38

J38

K39

K37

T35

M38

P6

K9

H15

J9

H14

M8

AV2

J16

H16

N40

N39

V7

AB6

K13

J8

R1

P1

R2

AB36

AW2

AV1

AC8

P4

U8

AB33

T8

Y8

M10

L10

M11

L12

W8

R33

P33

E40

N33

J11

M9

J7

F40

N35

W6

W5

H40

TPEV_CF G_RCOMP

CPU_BPM _0

CPU_BPM _1

TP_PROC ESSOR_G38

TP_PROC ESSOR_H37

TP_PROC ESSOR_H38

TP_PROC ESSOR_J38

TP_PROC ESSOR_K39

TP_PROC ESSOR_K37

TP_PROC ESSOR_T35

TP_PROC ESSOR_M38

TESTLOW _1

TP_PROC ESSOR_H15

TP_PROC ESSOR_J9

TP_PROC ESSOR_H14

TP_PROC ESSOR_AV2

TP_PROC ESSOR_J16

TP_PROC ESSOR_H16

PWR_ DEBUG

TP_PROC ESSOR_V7

TP_PROC ESSOR_AB6

TP_PROC ESSOR_K13

TP_PROC ESSOR_J8

DDR_RCO MP_0

DDR_RCO MP_1

DDR_RCO MP_2

TP_PROC ESSOR_AB36

TP_PROC ESSOR_AW2

TP_PROC ESSOR_AV1

TP_PROC ESSOR_AC8

TP_PROC ESSOR_U8

TP_PROC ESSOR_AB33

TP_PROC ESSOR_T8

TP_PROC ESSOR_Y8

TP_PROC ESSOR_M10

TP_PROC ESSOR_L10

TP_PROC ESSOR_M11

TP_PROC ESSOR_L12

TP_PROC ESSOR_W8

TP_PROC ESSOR_R33

TP_PROC ESSOR_P33

0402

0402

R94

R94

X_49R9_ 1%

X_49R9_ 1%

TP_PROC ESSOR_N35

TITLE:

TITLE:

TITLE:

Mississippi_uATX

Mississippi_uATX

Mississippi_uATX

HASW ELL SOCKET

HASW ELL SOCKET

HASW ELL SOCKET

Document N umber :

Document N umber :

Document N umber :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

A3

CPU_BPM _0 3

CPU_BPM _1 3

T64T64

T63T63

T66T66

T65T65

T67T67

T68T68

T31T31

R303

R303

T32T32

49R9_1%

49R9_1%

0402

0402

VCCST 7

T55T55

VCORE

T57T57

T58T58

T59T59

T61T61

T62T62

PWR_ DEBUG 3

T52T52

T49T49

T54T54

T53T53

T42T42

T43T43

T44T44

T45T45

V_VCCIOA_ LOAD 5

T47T47

T48T48

T46T46

T34T34

T35T35

T36T36

T37T37

T38T38

T39T39

T40T40

T41T41

VCC_SEN SE 46

VSS_SEN SE 46

T56T56

CK_DPNS _DN 1 4

CK_DPNS _DP 14

0402

0402

R93

R93

49R9_1%

49R9_1%

<Doc>

<Doc>

<Doc>

Kerry Huang

Kerry Huang

Kerry Huang

Date: PAGE:

Date: PAGE:

Date: PAGE:

Monday, December 0 3, 2012

Monday, December 0 3, 2012

Monday, December 0 3, 2012

7

0402

0402

0402

R291

R291

8

REV:

REV:

REV:

75R_1%

75R_1%

0402

100R_1%

100R_1%

R223

R223

V0.4

V0.4

V0.4

4 63

4 63

4 63

of

of

of

0402

0402

100R_1%

100R_1%

R292

R292

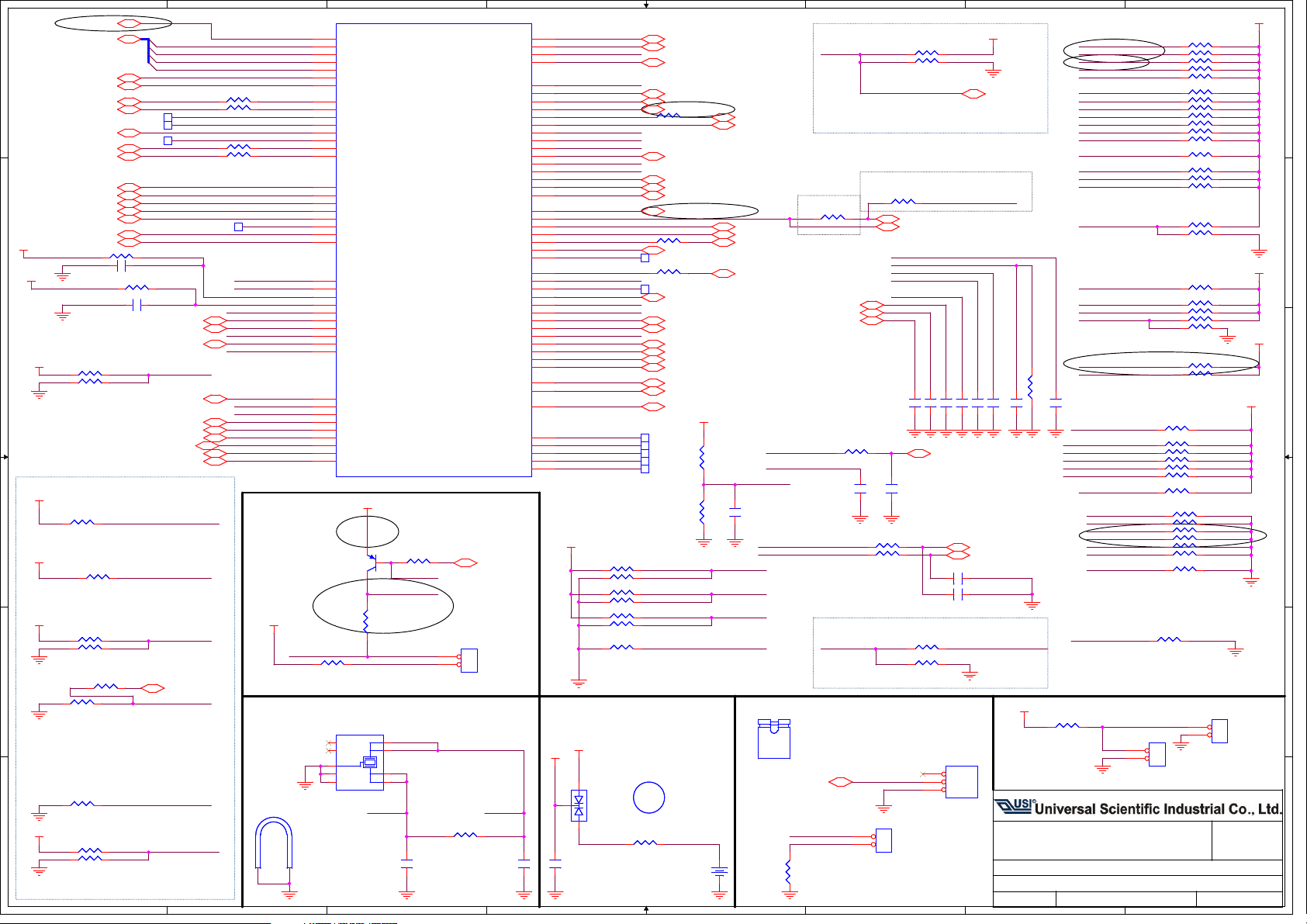

Page 5

1

A A

2

3

4

5

6

7

8

CPU PEG / DMI / GEN

CPU FDI_LINK

J3C

J3C

DP11

DP12

DP13

DP21

PEG_RCO MP

E15

F15

D14

E14

E13

F13

D12

E12

E11

F11

F10

G10

E9

F9

F8

G8

D3

D4

E4

E5

F5

F6

G4

G5

H5

H6

J4

J5

K5

K6

L4

L5

U3

T3

U1

V1

W2

V2

Y3

W3

D1

C2

B3

A4

P3

PEG_RXP0

PEG_RXN0

PEG_RXP1

PEG_RXN1

PEG_RXP2

PEG_RXN2

PEG_RXP3

PEG_RXN3

PEG_RXP4

PEG_RXN4

PEG_RXP5

PEG_RXN5

PEG_RXP6

PEG_RXN6

PEG_RXP7

PEG_RXN7

PEG_RXP8

PEG_RXN8

PEG_RXP9

PEG_RXN9

PEG_RXP10

PEG_RXN10

PEG_RXP11

PEG_RXN11

PEG_RXP12

PEG_RXN12

PEG_RXP13

PEG_RXN13

PEG_RXP14

PEG_RXN14

PEG_RXP15

PEG_RXN15

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

RSVD_TP_D1

RSVD_TP_C2

RSVD_TP_B3

RSVD_TP_A4

PEG_RCOMP

HASW ELL

HASW ELL

EXP_A_R X_0_DP22

EXP_A_R X_0_DN22

EXP_A_R X_1_DP22

EXP_A_R X_1_DN22

B B

C C

D D

V_VCCIOA_ LOAD4,5

EXP_A_R X_2_DP22

EXP_A_R X_2_DN22

EXP_A_R X_3_DP22

EXP_A_R X_3_DN22

EXP_A_R X_4_DP22

EXP_A_R X_4_DN22

EXP_A_R X_5_DP22

EXP_A_R X_5_DN22

EXP_A_R X_6_DP22

EXP_A_R X_6_DN22

EXP_A_R X_7_DP22

EXP_A_R X_7_DN22

EXP_A_R X_8_DP22

EXP_A_R X_8_DN22

EXP_A_R X_9_DP22

EXP_A_R X_9_DN22

EXP_A_R X_10_DP22

EXP_A_R X_10_DN22

EXP_A_R X_11_DP22

EXP_A_R X_11_DN22

EXP_A_R X_12_DP22

EXP_A_R X_12_DN22

EXP_A_R X_13_DP22

EXP_A_R X_13_DN22

EXP_A_R X_14_DP22

EXP_A_R X_14_DN22

EXP_A_R X_15_DP22

EXP_A_R X_15_DN22

DMI_IT_MR_0_ DP13

DMI_IT_MR_0_ DN13

DMI_IT_MR_1_ DP13

DMI_IT_MR_1_ DN13

DMI_IT_MR_2_ DP13

DMI_IT_MR_2_ DN13

DMI_IT_MR_3_ DP13

DMI_IT_MR_3_ DN13

DP11DP11

DP12DP12

DP13DP13

DP21DP21

R1281 24R9_1 %

R1281 24R9_1 %

0402

0402

3of10

3of10

PEGDMI

PEGDMI

PEG_TXP0

PEG_TXN0

PEG_TXP1

PEG_TXN1

PEG_TXP2

PEG_TXN2

PEG_TXP3

PEG_TXN3

PEG_TXP4

PEG_TXN4

PEG_TXP5

PEG_TXN5

PEG_TXP6

PEG_TXN6

PEG_TXP7

PEG_TXN7

PEG_TXP8

PEG_TXN8

PEG_TXP9

PEG_TXN9

PEG_TXP10

PEG_TXN10

PEG_TXP11

PEG_TXN11

PEG_TXP12

PEG_TXN12

PEG_TXP13

PEG_TXN13

PEG_TXP14

PEG_TXN14

PEG_TXP15

PEG_TXN15

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

A12

B12

B11

C11

C10

D10

B9

C9

C8

D8

B7

C7

A6

B6

B5

C5

E1

E2

F2

F3

G1

G2

H2

H3

J1

J2

K2

K3

M2

M3

L1

L2

AA4

AA5

AB3

AB4

AC5

AC4

AC1

AC2

EXP_A_T X_0_DP 22

EXP_A_T X_0_DN 22

EXP_A_T X_1_DP 22

EXP_A_T X_1_DN 22

EXP_A_T X_2_DP 22

EXP_A_T X_2_DN 22

EXP_A_T X_3_DP 22

EXP_A_T X_3_DN 22

EXP_A_T X_4_DP 22

EXP_A_T X_4_DN 22

EXP_A_T X_5_DP 22

EXP_A_T X_5_DN 22

EXP_A_T X_6_DP 22

EXP_A_T X_6_DN 22

EXP_A_T X_7_DP 22

EXP_A_T X_7_DN 22

EXP_A_T X_8_DP 22

EXP_A_T X_8_DN 22

EXP_A_T X_9_DP 22

EXP_A_T X_9_DN 22

EXP_A_T X_10_DP 22

EXP_A_T X_10_DN 22

EXP_A_T X_11_DP 22

EXP_A_T X_11_DN 22

EXP_A_T X_12_DP 22

EXP_A_T X_12_DN 22

EXP_A_T X_13_DP 22

EXP_A_T X_13_DN 22

EXP_A_T X_14_DP 22

EXP_A_T X_14_DN 22

EXP_A_T X_15_DP 22

EXP_A_T X_15_DN 22

DMI_MT_IR_0_ DP 13

DMI_MT_IR_0_ DN 13

DMI_MT_IR_1_ DP 13

DMI_MT_IR_1_ DN 13

DMI_MT_IR_2_ DP 13

DMI_MT_IR_2_ DN 13

DMI_MT_IR_3_ DP 13

DMI_MT_IR_3_ DN 13

FDI_CSYNC13

FDI_INT13

0402

0402

DP_RCOM P

DP32

DP30

DP31

R1282 24R9_1 %

V_VCCIOA_ LOAD4,5

R1282 24R9_1 %

CK_DP_1 35M_DN14

CK_DP_1 35M_DP14

FDI_TX_0_ DN13

FDI_TX_0_ DP13

FDI_TX_1_ DN13

FDI_TX_1_ DP13

DP32DP32

DP30DP30

DP31DP31

J3D

J3D

D16

FDI_CSYNC

D18

DISP_INT

R4

DP_RCOMP

U5

SSC_DPLL_REF_CLKN

U6

SSC_DPLL_REF_CLKP

E16

EDP_DISP_UTIL

K11

RSVD_TP_K11

J12

RSVD_TP_J12

B14

FDI_TX0N0

A14

FDI_TX0P0

C13

FDI_TX0N1

B13

FDI_TX0P1

HASW ELL

HASW ELL

4of10

4of10

DDIB_TXP0

DDIB_TXN0

DDIB_TXP1

DDIB_TXN1

DDIB_TXP2

DDIB_TXN2

DDIB_TXP3

DDIB_TXN3

DDIC_TXP0

DDIC_TXN0

DDIC_TXP1

DDIC_TXN1

DDIC_TXP2

DDIC_TXN2

DDIC_TXP3

DDIC_TXN3

DDID_TXP0

DDID_TXN0

DDID_TXP1

DDID_TXN1

DDID_TXP2

DDID_TXN2

DDID_TXP3

DDID_TXN3

E17

F17

F18

G18

G19

H19

F20

G20

D19

E19

C20

D20

D21

E21

C22

D22

B15

C15

A16

B16

B17

C17

A18

B18

DP PORT

HDMI PORT

DDPB_TX _0_DP 26

DDPB_TX _0_DN 26

DDPB_TX _1_DP 26

DDPB_TX _1_DN 26

DDPB_TX _2_DP 26

DDPB_TX _2_DN 26

DDPB_TX _3_DP 26

DDPB_TX _3_DN 26

DDPC_TX _0_DP 25

DDPC_TX _0_DN 25

DDPC_TX _1_DP 25

DDPC_TX _1_DN 25

DDPC_TX _2_DP 25

DDPC_TX _2_DN 25

DDPC_TX _3_DP 25

DDPC_TX _3_DN 25

DDPD_TX _0_DP 24

DDPD_TX _0_DN 24

DDPD_TX _1_DP 24

DDPD_TX _1_DN 24

DDPD_TX _2_DP 24

DDPD_TX _2_DN 24

DDPD_TX _3_DP 24

DDPD_TX _3_DN 24

E E

TITLE:

TITLE:

TITLE:

Mississippi_uATX

Mississippi_uATX

F F

1

2

3

4

5

6

Mississippi_uATX

HASW ELL SOCKET

HASW ELL SOCKET

HASW ELL SOCKET

Document N umber :

Document N umber :

Document N umber :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

A3

<Doc>

<Doc>

<Doc>

Kerry Huang

Kerry Huang

Kerry Huang

Date: PAGE:

Date: PAGE:

Date: PAGE:

Friday, November 30, 2012

Friday, November 30, 2012

Friday, November 30, 2012

7

8

REV:

REV:

REV:

V0.4

V0.4

V0.4

5 63

5 63

5 63

of

of

of

Page 6

1

M_MAA_A [0..15]10

A A

M_ODT_A [0..3]10

M_DATA_ A_CB[0..7]10

B B

M_SBS_A [0..2]10

M_SCKE_ A[0..3]10

M_SCS_A _N[0..3]10

C C

CLK_M_D DR0_A_DP10

CLK_M_D DR0_A_DN10

CLK_M_D DR1_A_DP10

CLK_M_D DR1_A_DN10

CLK_M_D DR2_A_DP10

CLK_M_D DR2_A_DN10

CLK_M_D DR3_A_DP10

CLK_M_D DR3_A_DN10

D D

M_RAS_A _N10

M_WE _A_N10

M_CAS_A _N10

DDR3_DR AMRST_N10,11

E E

C19

C19

X_10PF_ 50V_NPO

X_10PF_ 50V_NPO

M_MAA_A 0

M_MAA_A 1

M_MAA_A 2

M_MAA_A 3

M_MAA_A 4

M_MAA_A 5

M_MAA_A 6

M_MAA_A 7

M_MAA_A 8

M_MAA_A 9

M_MAA_A 10

M_MAA_A 11

M_MAA_A 12

M_MAA_A 13

M_MAA_A 14

M_MAA_A 15

M_ODT_A 0

M_ODT_A 1

M_ODT_A 2

M_ODT_A 3

M_DATA_ A_CB0

M_DATA_ A_CB1

M_DATA_ A_CB2

M_DATA_ A_CB3

M_DATA_ A_CB4

M_DATA_ A_CB5

M_DATA_ A_CB6

M_DATA_ A_CB7

M_SBS_A 0

M_SBS_A 1

M_SBS_A 2

M_SCKE_ A0

M_SCKE_ A1

M_SCKE_ A2

M_SCKE_ A3

M_SCS_A _N0

M_SCS_A _N1

M_SCS_A _N2

M_SCS_A _N3

DP42DP42

DP40DP40

DP41DP41

R77

R77

DP42

DP40

DP41

0R

0R

0402

0402

DDR3_DR AMRST_R_N

AU13

AV16

AU16

AW17

AU17

AW18

AV17

AT18

AU18

AT19

AW11

AV19

AU19

AY10

AT20

AU21

AW10

AY8

AW9

AU8

AW33

AV33

AU31

AV31

AT33

AU33

AT31

AW31

AV12

AY11

AT21

AV22

AT23

AU22

AU23

AU14

AV9

AU10

AW8

AY15

AY16

AW15

AV15

AV14

AW14

AW13

AY13

AW12

AU12

AU11

AV20

AW27

AU9

AK22

2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_ODT0

SA_ODT1

SA_ODT2

SA_ODT3

SA_ECC_CB0

SA_ECC_CB1

SA_ECC_CB2

SA_ECC_CB3

SA_ECC_CB4

SA_ECC_CB5

SA_ECC_CB6

SA_ECC_CB7

SA_BS0

SA_BS1

SA_BS2

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS0SA_CS1SA_CS2SA_CS3-

SA_CK0

SA_CKN0

SA_CK1

SA_CKN1

SA_CK2

SA_CKN2

SA_CK3

SA_CKN3

RSVD_AW12

SA_RAS-

SA_WE-

RSVD_AV20

RSVD_AW27

SA_CAS-

SM_DRAMRST-

1of10

1of10

DDR_A

DDR_A

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS8

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSN8

HASW ELL

HASW ELL

AD38

AD39

AF38

AF39

AD37

AD40

AF37

AF40

AH40

AH39

AK38

AK39

AH37

AH38

AK37

AK40

AM40

AM39

AP38

AP39

AM37

AM38

AP37

AP40

AV37

AW37

AU35

AV35

AT37

AU37

AT35

AW35

AY6

AU6

AV4

AU4

AW6

AV6

AW4

AY4

AR1

AR4

AN3

AN4

AR2

AR3

AN2

AN1

AL1

AL4

AJ3

AJ4

AL2

AL3

AJ2

AJ1

AG1

AG4

AE3

AE4

AG2

AG3

AE2

AE1

AE39

AJ39

AN39

AV36

AV5

AP3

AK3

AF3

AV32

AE38

AJ38

AN38

AU36

AW5

AP2

AK2

AF2

AU32

3

M_D_A0

M_D_A1

M_D_A2

M_D_A3

M_D_A4

M_D_A5

M_D_A6

M_D_A7

M_D_A9

M_D_A13

M_D_A10

M_D_A11

M_D_A12

M_D_A8

M_D_A14

M_D_A15

M_D_A17

M_D_A21

M_D_A18

M_D_A19

M_D_A20

M_D_A16

M_D_A22

M_D_A23

M_D_A25

M_D_A29

M_D_A26

M_D_A27

M_D_A28

M_D_A24

M_D_A30

M_D_A31

M_D_A33

M_D_A37

M_D_A34

M_D_A35

M_D_A36

M_D_A32

M_D_A38

M_D_A39

M_D_A41

M_D_A45

M_D_A42

M_D_A43

M_D_A44

M_D_A40

M_D_A46

M_D_A47

M_D_A49

M_D_A53

M_D_A50

M_D_A51

M_D_A52

M_D_A48

M_D_A54

M_D_A55

M_D_A57

M_D_A61

M_D_A58

M_D_A59

M_D_A60

M_D_A56

M_D_A62

M_D_A63

M_DQS_A _DP0

M_DQS_A _DP1

M_DQS_A _DP2

M_DQS_A _DP3

M_DQS_A _DP4

M_DQS_A _DP5

M_DQS_A _DP6

M_DQS_A _DP7

M_DQS_A _DP8

M_DQS_A _DN0

M_DQS_A _DN1

M_DQS_A _DN2

M_DQS_A _DN3

M_DQS_A _DN4

M_DQS_A _DN5

M_DQS_A _DN6

M_DQS_A _DN7

M_DQS_A _DN8

J3A

J3A

4

M_D_A[0..6 3] 10

DQ REMAPPING IM PLEMENTED

TO IMPROVE BREA KOUT AND

MINIMIZE CH-2-C H COUPLING

M_DQS_A _DP[0..8] 10

M_DQS_A _DN[0..8] 10

M_DQS_B _DP[0..8]11

M_DQS_B _DN[0..8]11

5

6

7

8

CPU MEMORY

M_D_B[0..6 3]11

M_D_B0

M_D_B1

M_D_B2

M_D_B3

M_D_B4

M_D_B5

M_D_B6

M_D_B7

M_D_B8

M_D_B9

M_D_B10

M_D_B11

M_D_B12

M_D_B13

M_D_B14

M_D_B15

M_D_B17

M_D_B21

M_D_B19

M_D_B23

M_D_B20

M_D_B16

M_D_B18

M_D_B22

M_D_B25

M_D_B28

M_D_B27

M_D_B30

M_D_B24

M_D_B29

M_D_B26

M_D_B31

M_D_B32

M_D_B33

M_D_B34

M_D_B35

M_D_B36

M_D_B37

M_D_B38

M_D_B39

M_D_B45

M_D_B41

M_D_B47

M_D_B43

M_D_B44

M_D_B40

M_D_B46

M_D_B42

M_D_B52

M_D_B53

M_D_B50

M_D_B55

M_D_B48

M_D_B49

M_D_B54

M_D_B51

M_D_B61

M_D_B60

M_D_B59

M_D_B63

M_D_B56

M_D_B57

M_D_B58

M_D_B62

M_DQS_B _DP0

M_DQS_B _DP1

M_DQS_B _DP2

M_DQS_B _DP3

M_DQS_B _DP4

M_DQS_B _DP5

M_DQS_B _DP6

M_DQS_B _DP7

M_DQS_B _DP8

M_DQS_B _DN0

M_DQS_B _DN1

M_DQS_B _DN2

M_DQS_B _DN3

M_DQS_B _DN4

M_DQS_B _DN5

M_DQS_B _DN6

M_DQS_B _DN7

M_DQS_B _DN8

AE34

AE35

AG35

AH35

AD34

AD35

AG34

AH34

AL34

AL35

AK31

AL31

AK34

AK35

AK32

AL32

AN34

AP34

AN31

AP31

AN35

AP35

AN32

AP32

AM29

AM28

AR29

AR28

AL29

AL28

AP29

AP28

AR12

AP12

AL13

AL12

AR13

AP13

AM13

AM12

AR9

AP9

AR6

AP6

AR10

AP10

AR7

AP7

AM9

AM10

AL10

AM6

AM7

AH6

AH7

AE6

AE7

AF6

AF7

AF35

AL33

AP33

AN28

AN12

AP8

AG7

AN25

AF34

AK33

AN33

AN29

AN13

AR8

AM8

AG6

AN26

AL9

AL6

AL7

AJ6

AJ7

AL8

J3B

J3B

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

SB_DQSP8

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSN8

HASW ELL

HASW ELL

2of10

2of10

DDR_B

DDR_B

SB_ECC_CB0

SB_ECC_CB1

SB_ECC_CB2

SB_ECC_CB3

SB_ECC_CB4

SB_ECC_CB5

SB_ECC_CB6

SB_ECC_CB7

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_ODT0

SB_ODT1

SB_ODT2

SB_ODT3

SB_BS0

SB_BS1

SB_BS2

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS0SB_CS1SB_CS2SB_CS3-

SB_CK0

SB_CKN0

SB_CK1

SB_CKN1

SB_CK2

SB_CKN2

SB_CK3

SB_CKN3

SB_CAS-

RSVD_AL20

SB_RAS-

SB_WE-

AL19

AK23

AM22

AM23

AP23

AL23

AY24

AV25

AU26

AW25

AP18

AY25

AV26

AR15

AV27

AY28

AM17

AL16

AM16

AK15

AM26

AM25

AP25

AP26

AL26

AL25

AR26

AR25

AK17

AL18

AW28

AW29

AY29

AU28

AU29

AP17

AN15

AN17

AL15

AM20

AM21

AP22

AP21

AN20

AN21

AP19

AP20

AP16

AL20

AM18

AK16

AB39

AB40

M_MAA_B 0

M_MAA_B 1

M_MAA_B 2

M_MAA_B 3

M_MAA_B 4

M_MAA_B 5

M_MAA_B 6

M_MAA_B 7

M_MAA_B 8

M_MAA_B 9

M_MAA_B 10

M_MAA_B 11

M_MAA_B 12

M_MAA_B 13

M_MAA_B 14

M_MAA_B 15

M_ODT_B 0

M_ODT_B 1

M_ODT_B 2

M_ODT_B 3

M_DATA_ B_CB0

M_DATA_ B_CB1

M_DATA_ B_CB2

M_DATA_ B_CB3

M_DATA_ B_CB4

M_DATA_ B_CB5

M_DATA_ B_CB6

M_DATA_ B_CB7

M_SBS_B 0

M_SBS_B 1

M_SBS_B 2

M_SCKE_ B0

M_SCKE_ B1

M_SCKE_ B2

M_SCKE_ B3

M_SCS_B _N0

M_SCS_B _N1

M_SCS_B _N2

M_SCS_B _N3

DP33

DP33DP33

M_MAA_B [0..15] 11

M_ODT_B [0..3] 11

M_DATA_ B_CB[0..7] 11

M_SBS_B [0..2] 11

M_SCKE_ B[0..3] 11

M_SCS_B _N[0..3] 11

CLK_M_D DR0_B_DP 11

CLK_M_D DR0_B_DN 11

CLK_M_D DR1_B_DP 11

CLK_M_D DR1_B_DN 11

CLK_M_D DR2_B_DP 11

CLK_M_D DR2_B_DN 11

CLK_M_D DR3_B_DP 11

CLK_M_D DR3_B_DN 11

M_CAS_B _N 11

M_RAS_B _N 11

M_WE _B_N 11

DIMM_DQ_C PU_VREF_A 10

DIMM_DQ_C PU_VREF_B 11

TITLE:

TITLE:

TITLE:

Mississippi_uATX

Mississippi_uATX

F F

1

2

3

4

5

6

Mississippi_uATX

HASW ELL SOCKET

HASW ELL SOCKET

HASW ELL SOCKET

Document N umber :

Document N umber :

Document N umber :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

A3

<Doc>

<Doc>

<Doc>

Kerry Huang

Kerry Huang

Kerry Huang

Date: PAGE:

Date: PAGE:

Date: PAGE:

Friday, November 30, 2012

Friday, November 30, 2012

Friday, November 30, 2012

7

8

REV:

REV:

REV:

V0.4

V0.4

V0.4

6 63

6 63

6 63

of

of

of

Page 7

1

A A

B B

C C

D D

E E

V_CPU_V CCIO_RIGHT3,4,46

V_CPU_V CCIO2PCH19,21

2

VCC1.05V _PCH

R728 X_0R

R728 X_0R

VCCST4

0402

0402

C21

C21

C223

C223

0.1UF_16V_X7R

0.1UF_16V_X7R

VCC1.05V _PCH

CB279

CB279

R710 0R

R710 0R

0805

0805

4.7UF_6.3V_X5R

4.7UF_6.3V_X5R

0402

0402

3

X7R

X7R

0402

0402

R727 X_0R

R727 X_0R

R13420RR1342

0R

VCORE

R703

R703

0R

0R

VCCIO_OUT

0402

0402

VCORE

VCCIO2PCH

4

CPU POWER

J3F

J3F

6of10

VCC_2

VCCIO_OUT

VCCIO2PCH

VCC_3

VCC_4

VCC_5

VCC_6

VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56

VCC_57

VCC_58

VCC_59

VCC_60

VCC_61

VCC_62

VCC_63

VCC_64

VCC_65

VCC_66

VCC_67

VCC_68

VCC_69

VCC_70

VCC_71

VCC_72

VCC_73

VCC_74

VCC_75

HASW ELL

HASW ELL

6of10

VCC_76

VCC_77

VCC_78

VCC_79

VCC_80

VCC_81

VCC_82

VCC_83

VCC_84

VCC_85

VCC_86

VCC_87

VCC_88

VCC_89

VCC_90

VCC_91

VCC_92

VCC_93

VCC_94

VCC_95

VCC_96

VCC_97

VCC_98

VCC_99

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

VCC_127

VDDQ_1

VDDQ_2

VDDQ_3

VDDQ_4

VDDQ_5

VDDQ_6

VDDQ_7

VDDQ_8

VDDQ_9

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_24

VDDQ_25

VDDQ_26

L40

AB8

L31

L18

L17

A24

A25

A26

A27

A28

A29

A30

G33

B25

B27

B29

B31

B33

G31

B35

C24

C25

C26

C27

C28

C29

C30

C32

C34

C35

D25

D27

D29

D31

E33

D33

E31

D35

E24

E25

E26

E27

E28

E29

E30

E32

E34

F23

F25

F27

F29

F31

E35

F33

F35

G22

G23

G24

G25

G26

G27

G28

G29

G30

G32

G34

G35

H23

H25

H27

H29

H31

L34

P8

J33

J31

C31

C33

L16

L15

J35

H33

H35

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

J32

J34

K19

K21

K23

K25

K27

K29

K31

M13

K33

K35

L19

L20

L21

L22

L23

L24

L25

L26

L27

L28

L29

L30

L32

L33

M17

M15

M19

M21

M23

M25

M27

M29

M33

AJ12

AJ13

AJ15

AJ17

AJ20

AJ21

AJ24

AJ25

AJ28

AJ29

AJ9

AT17

AT22

AU15

AU20

AU24

AV10

AV11

AV13

AV18

AV23

AV8

AW16

AY12

AY14

AY9

5

VCORE

NOTE:

VCCIO_OUT(Typ. 1V):Processor p ower reference for I/O

VCCIO2PCH:Proce ssor power refe rence to PCH

VCC1.5V_ DDR3

6

7

8

TITLE:

TITLE:

TITLE:

Mississippi_uATX

Mississippi_uATX

F F

1

2

3

4

5

6

Mississippi_uATX

HASW ELL SOCKET

HASW ELL SOCKET

HASW ELL SOCKET

Document N umber :

Document N umber :

Document N umber :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

A3

<Doc>

<Doc>

<Doc>

Kerry Huang

Kerry Huang

Kerry Huang

Date: PAGE:

Date: PAGE:

Date: PAGE:

Friday, November 30, 2012

Friday, November 30, 2012

Friday, November 30, 2012

7

8

REV:

REV:

REV:

V0.4

V0.4

V0.4

7 63

7 63

7 63

of

of

of

Page 8

1

2

3

4

5

6

7

8

CPU GND

J3G

A13

A15

A17

A23

A11

AA3

AA33

AA35

AA38

AA6

AA7

AA8

AB34

AB37

AB5

AB7

AC3

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

AC6

AC7

AD1

AD2

AD3

AD33

AD36

AD4

AD5

AD6

AD7

AD8

AE33

AE36

AE37

AE40

AE5

AE8

AF1

AF33

AF36

AF4

AF5

AF8

AG33

AG36

AG37

AG38

AG39

AG40

AG5

AG8

AH1

AH2

AH3

AH33

AH36

AH4

AH5

AH8

AJ11

AJ14

AJ16

AJ18

AJ19

AJ22

AJ23

AJ26

AJ27

AJ30

AJ31

AJ32

AJ33

A5

A7

J3G

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

HASW ELL

HASW ELL

7of10

7of10

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

AJ34

AJ35

AJ36

AJ37

AJ40

AJ5

AJ8

AK1

AK10

AK11

AK12

AK13

AK14

AK18

AK19

AK24

AK25

AK26

AK27

AK28

AK29

AK30

AK36

AK4

AK5

AK6

AK7

AK8

AK9

AL11

AL14

AL17

AL21

AL22

AL24

AL27

AL30

AL36

AL37

AL38

AL39

AL40

AL5

AM1

AM11

AM14

AM15

AM19

AM2

AM24

AM27

AM3

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AM4

AM5

AN10

AN11

AN14

AN16

AN18

AN19

AN22

AN23

AN24

AN27

AN30

AN36

AN37

AN40

AN5

AN6

AN7

AN8

AN9

AP1

J3J

J3J

10of10

10of10

RSVD_TP_K12

AY18

DP3

DP3DP3

DP4

DP4DP4

DP5

DP5DP5

DP6

DP6DP6

DP7

DP7DP7

DP8

DP8DP8

DP9

DP9DP9

DP10

DP10DP10

R1344

R1344

6K04_1%

PWRG D_3V15,16,39,4 5

6K04_1%

0402

0402

VCCST_P WRGD

0402

0402

R1343

R1343

2K67_1%

2K67_1%

DP14DP14

DP15DP15

DP17DP17

DP18DP18

DP19DP19

DP20DP20

DP26DP26

DP27DP27

DP14

DP15

DP17

DP18

DP19

DP20

DP26

DP27

AW24

AW23

AV29

AV24

AU39

AU27

AU1

AT40

AK20

T34

R34

H12

Y7

J40

J17

J15

RSVD_AY18

RSVD_AW24

RSVD_AW23

RSVD_AV29

RSVD_AV24

RSVD_AU39

RSVD_AU27

RSVD_AU1

RSVD_AT40

RSVD_AK20

RSVD_Y7

RSVD_T34

RSVD_R34

RSVD_J40

RSVD_J17

RSVD_J15

RSVD_H12

RSVD_TP_J13

RSVD_TP_P37

RSVD_TP_N38

RSVD_TP_R36

RSVD_TP_C39

RSVD_TP_N36

HASW ELL

HASW ELL

VSS_467

VSS_468

VSS_469

VSS_470

VSS_471

VSS_472

VSS_473

VSS_474

VSS_475

VSS_476

VSS_477

VSS_478

K12

J13

P37

N38

R36

C39

U35

P40

R38

T37

V34

R39

T38

U36

P39

T36

R37

J14

N36

DP36

DP56

DP34

DP35

DP37

DP38

DP39

DP36DP36

DP56DP56

DP34DP34

DP35DP35

DP37DP37

DP38DP38

DP39DP39

J3I

J3H

J3H

8of10

A A

B B

C C

D D

E E

AP11

AP14

AP15

AP24

AP27

AP30

AP36

AP4

AP5

AR11

AR14

AR16

AR17

AR18

AR19

AR20

AR21

AR22

AR23

AR24

AR27

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AR37

AR38

AR39

AR40

AR5

AT1

AT10

AT11

AT12

AT13

AT14

AT15

AT16

AT2

AT24

AT25

AT26

AT27

AT28

AT29

AT3

AT30

AT32

AT34

AT36

AT38

AT39

AT4

AT5

AT6

AT7

AT8

AT9

AU2

AU25

AU3

AU30

AU34

AU38

AU5

AU7

AV21

AV28

AV3

AV30

AV34

AV38

AV7

AW26

AW3

AW30

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

HASW ELL

HASW ELL

8of10

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_271

VSS_272

VSS_273

VSS_274

VSS_275

VSS_276

VSS_277

VSS_278

VSS_279

VSS_280

VSS_281

VSS_282

VSS_283

VSS_284

VSS_285

VSS_286

VSS_287

VSS_288

VSS_289

VSS_290

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

AW32

AW34

AW36

AW7

AY17

AY23

AY26

AY27

AY30

AY5

AY7

B24

B26

B28

B30

B34

B36

B4

B8

C4

C6

C12

C14

C16

C18

C19

C21

C23

C36

B10

B23

C3

D9

D11

D13

D15

D17

D2

D23

D24

D26

D28

D30

D34

D36

D37

D5

D6

D7

E7

E8

E10

E18

E3

E20

E22

E23

E36

E38

B32

E6

F1

F32

F12

F14

F16

F19

F21

F22

F24

F26

F28

F30

F34

F36

F4

D32

F7

G9

G11

G12

G13

G14

G16

H11

G17

G21

H13

H22

H32

G36

G37

G15

H10

H17

H18

H20

H21

H24

H26

H28

H30

H34

H36

H39

K10

K14

K18

K20

K22

K24

K26

K28

K30

K34

K36

K40

K17

M12

M14

M18

M16

M20

M22

M24

M26

M28

M30

M32

M34

M37

J19

J20

J18

J36

J37

L11

L13

L14

L35

L38

G3

G6

G7

H1

H4

H7

H8

H9

J3

J6

K1

K4

K7

L7

L8

L9

L3

L6

M1

J3I

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

VSS_360

VSS_361

VSS_362

VSS_363

VSS_364

VSS_365

VSS_366

VSS_367

VSS_368

VSS_369

VSS_370

VSS_371

VSS_372

VSS_373

VSS_374

VSS_375

VSS_376

VSS_377

VSS_378

VSS_379

VSS_380

VSS_381

VSS_382

VSS_383

VSS_384

VSS_385

VSS_386

VSS_387

VSS_388

VSS_389

VSS_390

VSS_391

VSS_392

VSS_393

VSS_394

VSS_395

VSS_396

VSS_397

VSS_398

VSS_399

VSS_400

VSS_401

VSS_402

VSS_403

VSS_404

VSS_405

VSS_406

HASW ELL

HASW ELL

9of10

9of10

VSS_407

VSS_408

VSS_409

VSS_410

VSS_411

VSS_412

VSS_413

VSS_414

VSS_415

VSS_416

VSS_417

VSS_418

VSS_419

VSS_420

VSS_421

VSS_422

VSS_423

VSS_424

VSS_425

VSS_426

VSS_427

VSS_428

VSS_429

VSS_430

VSS_431

VSS_432

VSS_433

VSS_434

VSS_435

VSS_436

VSS_437

VSS_438

VSS_439

VSS_440

VSS_441

VSS_442

VSS_443

VSS_444

VSS_445

VSS_446

VSS_447

VSS_448

VSS_449

VSS_450

VSS_451

VSS_452

VSS_453

VSS_454

VSS_455

VSS_456

VSS_457

VSS_458

VSS_459

VSS_460

VSS_461

VSS_462

VSS_463

VSS_464

VSS_465

VSS_466

VSS_NCTF_1

VSS_NCTF_2

VSS_NCTF_3

VSS_NCTF_4

VSS_NCTF_5

VSS_NCTF_6

VSS_NCTF_7

VSS_NCTF_8

M4

M40

M5

M6

M7

K15

K16

N1

N2

N3

N7

N34

N4

N6

K32

P2

P34

P38

P5

P7

N8

R3

L36

R35

R40

R5

R6

R7

T1

T2

T33

M35

T39

T4

T5

T6

T7

R8

U2

U33

U34

U37

U4

U7

P35

V3

V33

V40

V6

V8

W1

W33

W35

W37

W4

W7

Y33

Y4

Y5

Y6

AU40

AV39

AW38

AY3

B38

B39

C40

D40

TITLE:

TITLE:

TITLE:

Mississippi_uATX

Mississippi_uATX

F F

1

2

3

4

5

6

Mississippi_uATX

HASW ELL SOCKET

HASW ELL SOCKET

HASW ELL SOCKET

Document N umber :

Document N umber :

Document N umber :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

A3

A3

A3

<Doc>

<Doc>

<Doc>

Kerry Huang

Kerry Huang

Kerry Huang

Date: PAGE:

Date: PAGE:

Date: PAGE:

Friday, November 30, 2012

Friday, November 30, 2012

Friday, November 30, 2012

7

8

REV:

REV:

REV:

V0.4

V0.4

V0.4

8 63

8 63

8 63

of

of

of

Page 9

1

A A

2

3

4

5

6

7

8

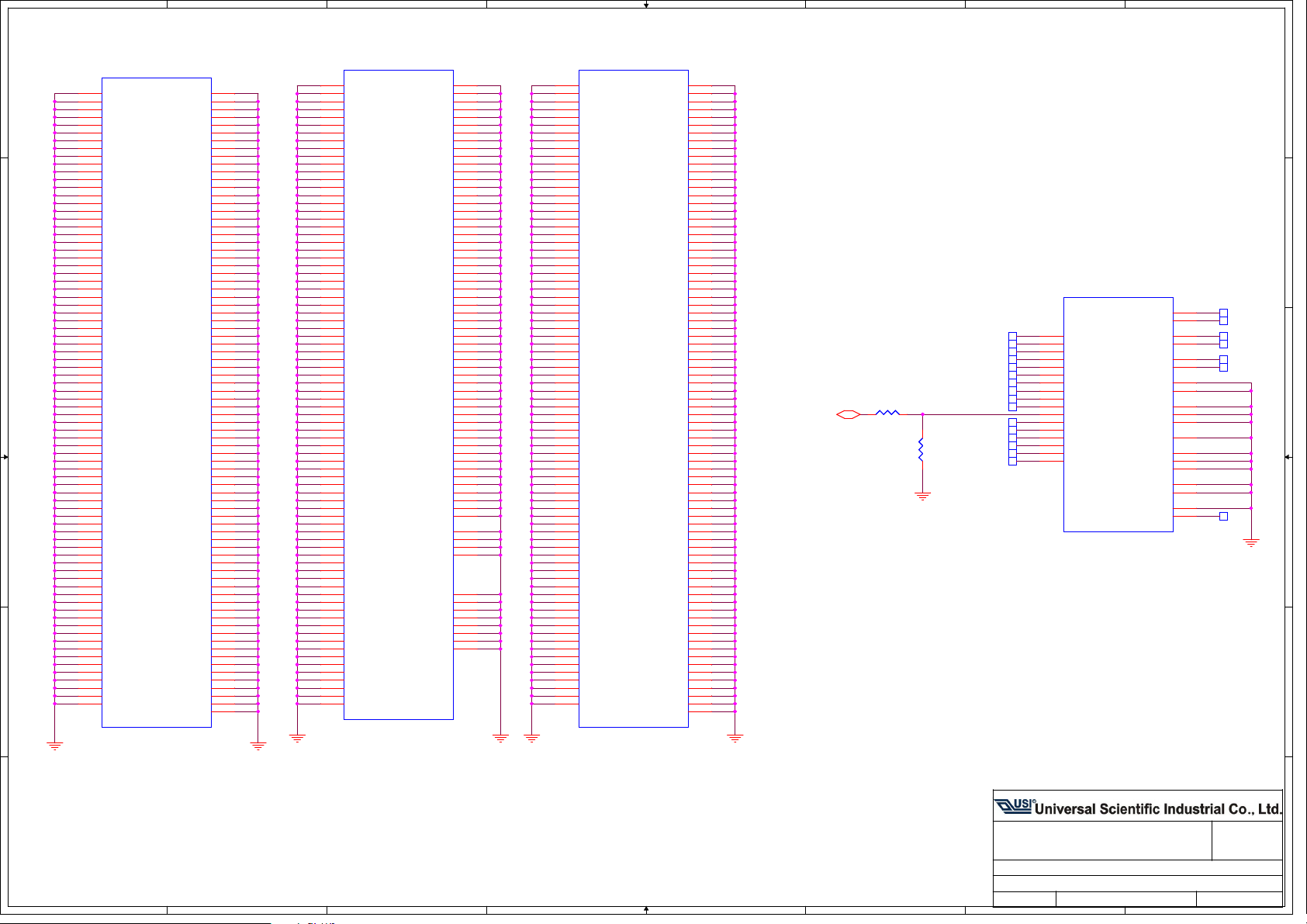

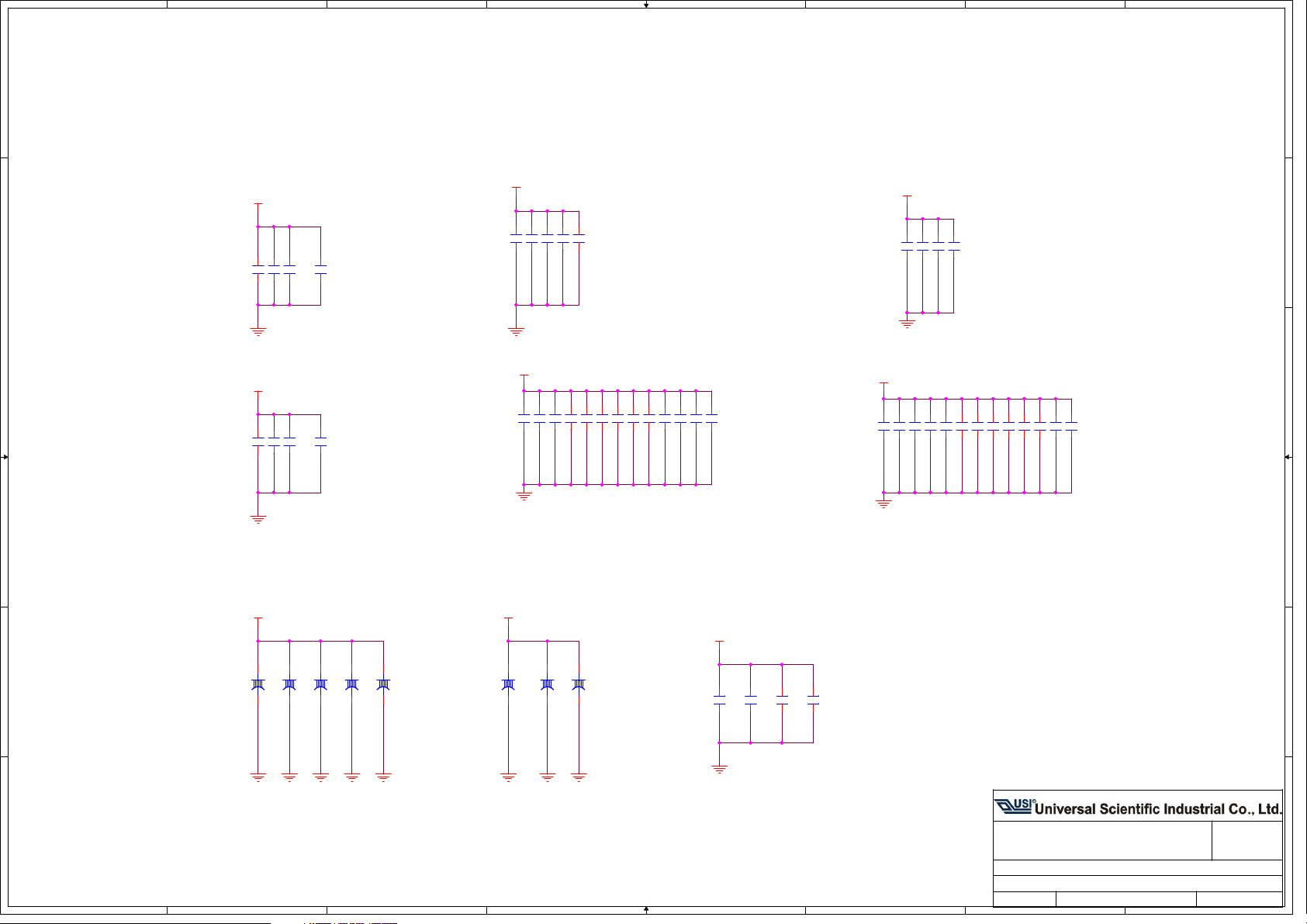

CPU DECOUPLING

B B

VCORE

C47

C47

0805

0805

0805

0805

0805

0805

0805

0805

0805

0805

C49

C49

C48

C48

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

0805

C50

C50

C51

C51

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

0805

0805

0805

0805

0805

0805

0805

0805

0805

0805

0805

0805

C53

C53

C54

C54

C55

C55

C56

C52

C52

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

C56

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

0805

0805

0805

C62

C57

C57

C58

C58

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

C62

C60

C60

22UF_6.3V_X5R

22UF_6.3V_X5R

0805

0805

0805

0805

C232

C232

C414

C414

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

0805

0805

0805

0805

0805

22UF_6.3V_X5R

22UF_6.3V_X5R

0805

C419

C419

C420

C420

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

Inside processor socket cavity

C C

VCC1.5V_ DDR3

0805

0805

C45

C45

0805

0805

0805

0805

0805

0805

C46

C46

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

0805

0805

0805

0805

0805

C61

C61

C63

C63

C64

C64

C87

22UF_6.3V_X5R

22UF_6.3V_X5R

C87

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

0805

0805

0805

0805

C88

C88

22UF_6.3V_X5R

22UF_6.3V_X5R

0805

C174

C174

C179

C179

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

Place to CPU cavity

VCORE

0805

0805

0805

0805

0805

0805

0805

C415

C415

C417

C416

C416

22UF_6.3V_X5R

22UF_6.3V_X5R

North of processor - as close

to RM keep-out as possible

D D

E E

C417

22UF_6.3V_X5R

22UF_6.3V_X5R

0805

C418

C418

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

22UF_6.3V_X5R

TITLE:

TITLE:

TITLE:

Mississippi_uATX

Mississippi_uATX

F F

1

2

3

4

5

6

Mississippi_uATX

SANDYBRIDGE S OCKET (Decouping)

SANDYBRIDGE S OCKET (Decouping)

SANDYBRIDGE S OCKET (Decouping)

Document N umber :

Document N umber :

Document N umber :

Prepared by :

Prepared by :

Prepared by :

SIZE :

SIZE :

SIZE :

Date: PAGE:

Date: PAGE:

Date: PAGE:

A3

A3

A3

7

<Doc>

<Doc>

<Doc>

Kerry Huang

Kerry Huang

Kerry Huang

Friday, November 30, 2012

Friday, November 30, 2012

Friday, November 30, 2012

8

REV:

REV:

REV:

V0.4

V0.4

V0.4

9 63

9 63

9 63

of

of

of

Page 10

1

M_ODT_A [0..3]

M_DQS_A _DN[0..8]10,6

M_DQS_A _DP[0..8]10,6

M_DATA_ A_CB[0..7]10,6

A A

M_ODT_A 0

M_ODT_A 1

M_DATA_A_CB0

M_DATA_A_CB1

68

53

167

195

79

J4

J4

NC-PAR_IN

NC-ERR_OUT

B B

GND1

GND2

239

235

CB039CB140CB245CB346CB4

ODT177ODT0

RSVD

NC_TEST4

GND3

GND4

GND5

GND6

GND7

GND8

232

229

226

223

220

217

214

SM BUS address : A0h

DDR3 CHANNEL A DIMM 0

M_ODT_A [0..3] 10,6

M_DATA_A_CB2

M_DATA_A_CB3

DDR3_24 0P_DIMM0_AT50_ PAD40_H28

GND9

GND10

211

208

M_DQS_A_DP0

M_DATA_A_CB4

M_DATA_A_CB5

M_DATA_A_CB6

M_DATA_A_CB7

158

159

164

165

7

CB5

CB6

CB7

DQS0

GND11

GND12

GND13

GND14

GND15

GND16

GND17

205

202

199

166

163

160

DIMM1

M_ODT_A [0..3]

M_DQS_A _DN[0..8]10,6

C C

M_ODT_A 2

M_ODT_A 3

D D

M_DQS_A _DP[0..8]10,6

M_DATA_ A_CB[0..7]10,6

M_DATA_A_CB0

M_DATA_A_CB1

68

53

167

195

79

J5

J5

NC-PAR_IN

NC-ERR_OUT

CB039CB140CB245CB346CB4

ODT177ODT0

RSVD

NC_TEST4

M_ODT_A [0..3] 10,6

M_DATA_A_CB2

M_DATA_A_CB3

M_DATA_A_CB4

M_DATA_A_CB5

M_DATA_A_CB6

M_DATA_A_CB7

M_DQS_A_DP0

158

159

164

165

7

CB5

CB6

CB7

DQS0

DDR3_24 0P_DIMM1_AT50_ PAD40_H28

2

3

4

5

6

7

8

DDR3 MEMORY CHANNEL A

M_D_A[0..6 3] 10,6

M_D_A0

M_D_A1

M_D_A2

M_D_A3

M_D_A4

M_D_A5

M_D_A6

M_D_A7

M_D_A8

M_D_A9

M_D_A10

M_D_A11

M_D_A12

M_D_A13

M_D_A14

M_D_A15

M_D_A16

M_D_A17

M_D_A18

M_D_A19

M_D_A20

M_D_A21

M_D_A22

M_D_A23

M_D_A24

M_D_A25

M_D_A26

M_D_A27

M_D_A28

M_D_A29

M_D_A30

M_D_A31

M_D_A32

M_D_A33

M_D_A34

M_D_A35

M_D_A36

M_D_A37

M_D_A38

M_D_A39

M_D_A40

M_D_A41

M_D_A42

M_D_A43

M_D_A44

M_D_A45

M_D_A46

M_D_A47

M_D_A48

M_D_A49

M_D_A50

M_D_A51

M_D_A52

M_D_A53

M_D_A54

M_D_A55

M_D_A56

M_D_A57

M_D_A58

M_D_A59

M_D_A60

M_D_A61

M_D_A62

M_DQS_A_DP1

M_DQS_A_DN0

6

16

DQS0-

GND18

GND19

157

154

151

M_DQS_A_DP1

M_DQS_A_DN0

6

16

DQS0-

M_DQS_A_DP3

M_DQS_A_DP2

M_DQS_A_DN1

15

25

DQS1

DQS1-

GND20

GND21

GND22

148

145

142

M_DQS_A_DP2

M_DQS_A_DN1

15

25

DQS1

DQS1-

M_DQS_A_DP4

M_DQS_A_DP5

M_DQS_A_DP6

M_DQS_A_DN2

M_DQS_A_DN3

M_DQS_A_DN4

24

34

33

85

84

94

DQS2

DQS3

DQS4

DQS2-

DQS3-

DQS4-

GND23

GND24

GND25

GND26

GND27

GND28

GND29

GND30

SA2

139

136

133

130

127

124

121

119

116

M_DQS_A_DP3

M_DQS_A_DP4

M_DQS_A_DN2

24

34

DQS2

DQS2-

M_DQS_A_DP5

M_DQS_A_DN3

M_DQS_A_DN4

33

85

84

94

DQS3

DQS4

DQS3-

DQS4-

M_DQS_A_DN5

93

DQS5

DQS5-

GREENDDR3_24 0P_DIMM0_AT50_ PAD40_H28

GREEN

GND32

GND33

113

M_DQS_A_DN5

93

DQS5

DQS5-

BLUEDDR3_24 0P_DIMM1_AT50_ PAD40_H28

BLUE

M_DQS_A_DP7

M_DQS_A_DN6

M_DQS_A_DN7

M_DQS_A_DP8

M_DQS_A_DN8

103

102

112

111

43

42

125

126

134

135

143

144

DQS6

DQS7

DQS8

DQS6-

DQS7-

DQS8-

NC_DQS9-

DM0_DQS9

NC_DQS10-

DM1_DQS10

DM2_DQS11

GND34

GND35

GND36

GND37

GND3898GND3995GND4092GND4189GND4286GND4383GND4480GND4547GND4644GND4741GND4838GND4935GND5032GND5129GND5226GND5323GND5420GND5517GND5614GND5711GND588GND595GND602FREE1

110

107

104

101

M_DQS_A_DP6

M_DQS_A_DP7

M_DQS_A_DN6

M_DQS_A_DN7

M_DQS_A_DP8

M_DQS_A_DN8

103

102

112

111

43

42

125

126

134

135

143

144

DQS6

DQS7

DQS8

DQS6-

DQS7-

DQS8-

NC_DQS9-

DM0_DQS9

NC_DQS10-

DM1_DQS10

DM2_DQS11

152

153

203

204

212

213

221

222

230

231

161

162

NC_DQS11-

NC_DQS12-

NC_DQS13-

NC_DQS14-

NC_DQS15-

NC_DQS16-

DM3_DQS12

DM4_DQS13

DM5_DQS14

DM6_DQS15

FREE249FREE348NC

198

VTT_MEM

152

153

203

204

212

213

221

222

NC_DQS11-

NC_DQS12-

NC_DQS13-

NC_DQS14-

DM3_DQS12

DM4_DQS13

NC_DQS15-

DM5_DQS14

DM6_DQS15

NC_DQS17-

DM7_DQS16

DM8_DQS17

VTT1

VTT2

VDD1

187

240

120

197

230

231

161

162

NC_DQS16-

NC_DQS17-

DM7_DQS16

DM8_DQS17

DQ03DQ14DQ29DQ310DQ4

VDD2

VDD3

VDD4

VDD5

VDD6

194

191

189

186

183

VCC1.5V_ DDR3

M_D_A0

M_D_A1

M_D_A2

DQ03DQ14DQ29DQ310DQ4

122

123

128

129

13

DQ5

DQ6

DQ7

DQ812DQ9

VDD7

VDD8

VDD9

VDD10

VDD11

VDD1278VDD1375VDD1472VDD1569VDD1666VDD1765VDD1862VDD1960VDD2057VDD2154VDD2251VDDSPD

182

179

176

173

170

SMB_CLK10,11 ,17,3,37

SMB_DAT A10,11,17,3 ,37

M_D_A[0..6 3] 10,6

M_D_A3

M_D_A4

M_D_A5

M_D_A6

M_D_A7

M_D_A8

M_D_A9

M_D_A10

122

123

128

129

13

DQ5

DQ6

DQ7

DQ812DQ9

131

132

137

138

DQ1018DQ1119DQ12

DQ13

DQ14

VCC3

DIMM_CA_V REF_A

DIMM_DQ_V REF_A

M_D_A11

M_D_A12

M_D_A13

M_D_A14

M_D_A15

131

132

137

138

DQ1018DQ1119DQ12

DQ13

DQ14

DQ15

DQ1621DQ1722DQ1827DQ1928DQ20

M_D_A16

M_D_A17

DQ15

DQ1621DQ1722DQ1827DQ1928DQ20

140

141

146

147

149

150

155

156

200

201

206

207

209

210

215

216

100

105

106

218

219

224

225

108

DQ21

DQ22

DQ23

DQ2430DQ2531DQ2636DQ2737DQ28

DQ29

DQ30

DQ31

DQ3281DQ3382DQ3487DQ3588DQ36

DQ37

DQ38

DQ39

DQ4090DQ4191DQ4296DQ4397DQ44

DQ45

DQ46

DQ47

DQ4899DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

SCL

SDA

SA1

SA0

BA252BA071CKE1

CKE050S1-76S0-

CK1_NU-64CK1_NU63CK0-

CK0

A261A3

A459A558A6

A756A8

A10_AP70A1155A12

VREFCA67VREFDQ

1

118

236

M_D_A18

M_D_A19

M_D_A20

M_D_A21

M_D_A22

M_D_A23

140

141

146

147

DQ21

DQ22

DQ23

238

237

117

M_D_A24

M_D_A25

M_D_A26

DQ2430DQ2531DQ2636DQ2737DQ28

BA1

169

M_D_A30

155

M_SBS_A0

M_D_A31

156

DQ30

M_SCKE_A1

M_D_A32

M_D_A33

DQ31