Page 1

5

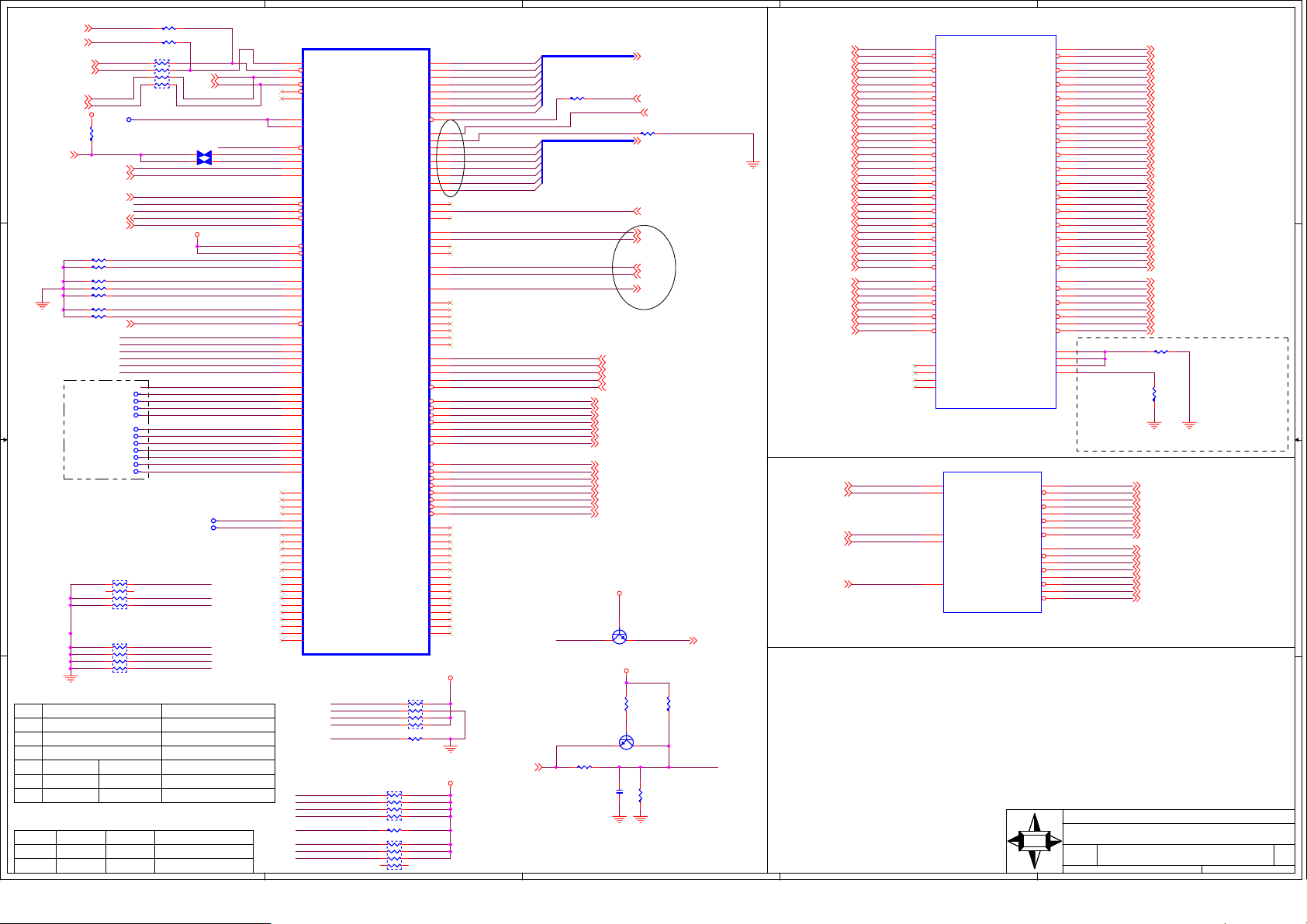

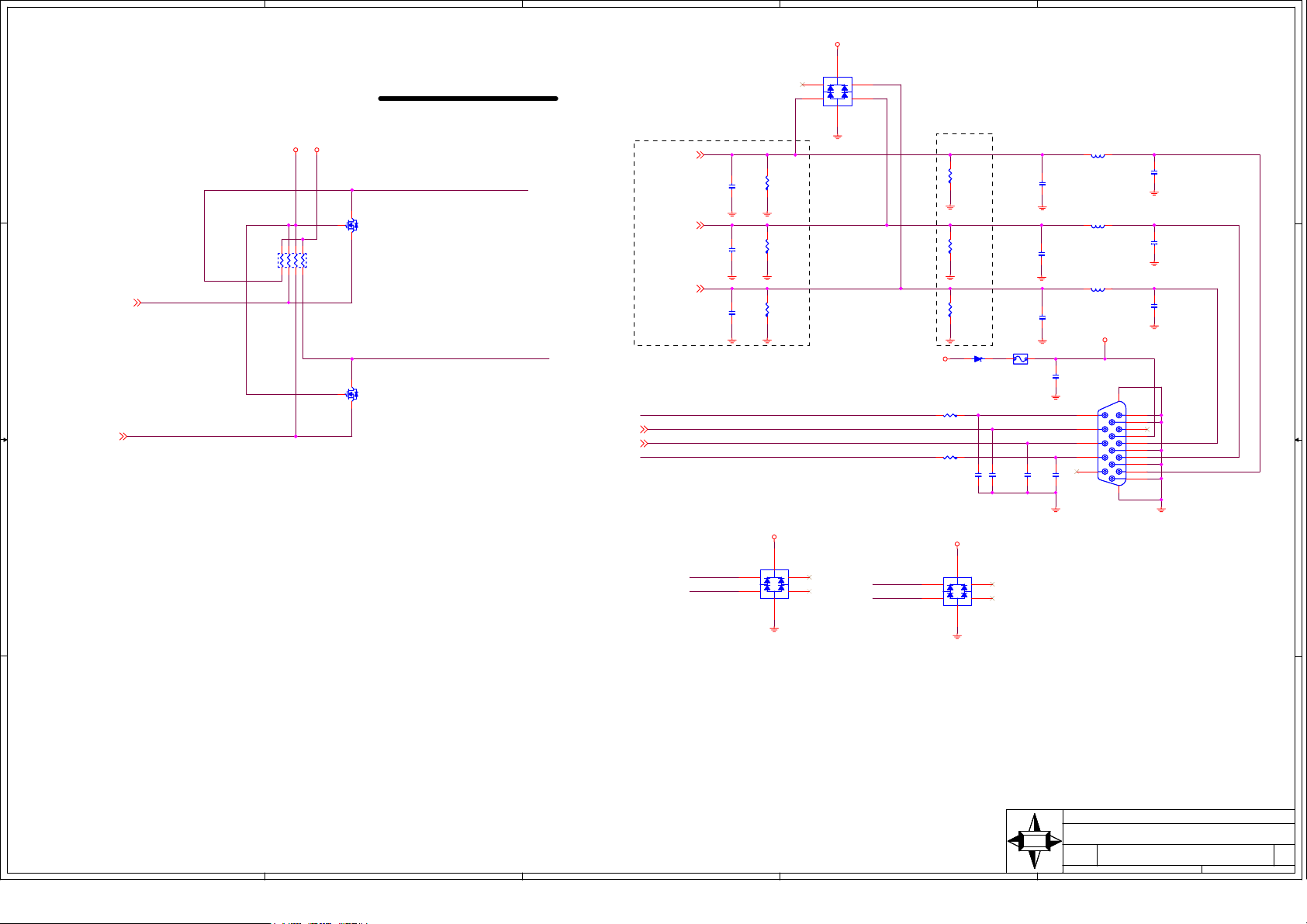

Cover Sheet 1

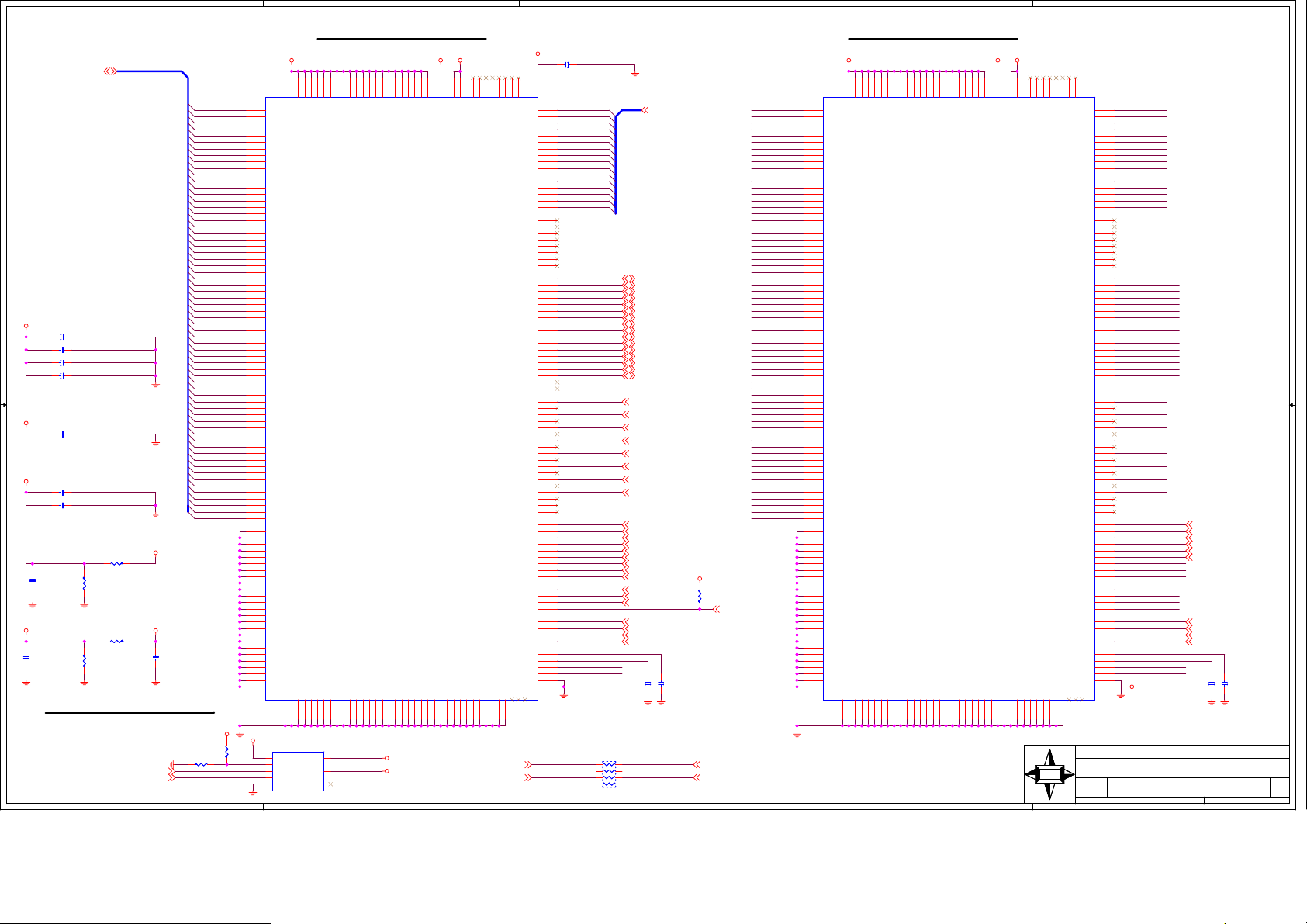

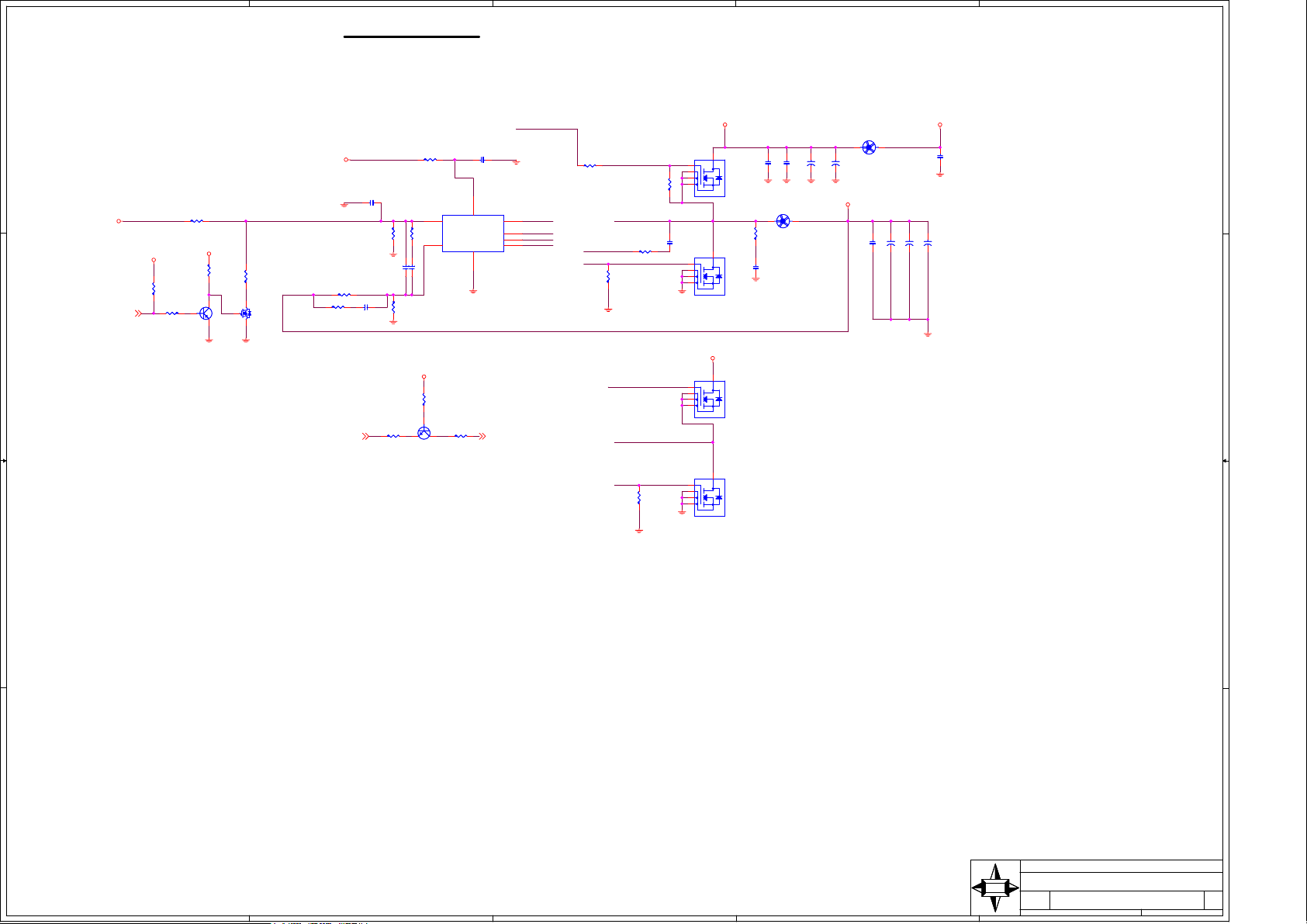

Block Diagram/Device Map/GPIO Table/Clock Distribution

4

3

2

1

PageTitle

MS-7586

2

Ver: 0A

CPU-CLK/Control/MISC/PEG

D D

CPU-Power,CPU-GND

,CPU-Memory

6

uATX(244mm X 244mm)

,9,78

CPU:

DDR III DIMM 1 / 2,DDR III DIMM 3 / 4

CLK GEN4100

10,11

12

INTEL -HAVENDALE/Lynnfied LGA 1156

System Chipset:

PCH-PCI/E/DMI/USB/CLK

PCH-SATA/HOST/FAN/GPIO/VGA

PCH-SMB/LPC/AUDIO/RTC/RST

13

14

15

INTEL-IBEXPEAK PCH

OnBoard Chipset:

PCH-POWER,GND/NVRAM

C C

PCIE x16 & x1 Slots

PCIEx1 & X3 SLOT

PCI Slot 1 & 2

1394 Controller - VT6315N-CD

16,17

18SIO-Fintek F71889F/KB/FDD

19

20

21

22

Clock Gen:IDT 4100

HD Audio Codec:RTL888S

LAN:Intel integrated Hanksville 10/100/1000 NIC

SIO:FIN71889

Flash ROM: 32 Mb SPI (CHIP)

Main Memory:

JMB-363 SATA X2/ IDE X1

LAN-RTL8111DL

Audio Codec ALC888S

DVI transfer

B B

VGA

23

24

25

26

27

DDRIII (1066/1333MHz) * 4 (Dual Channel)

Expansion Slots:

PCI Express (X16) Slot * 1

PCI Express (X1) Slot * 3

PCI Slot *3

SATA / FAN Control,USB Connector 28

ACPI Controller UPI

CPU_VTT - 6103 1Phase

GPU Power - ISL6314 1-Phase

DDR Power - 6103 1Phase

PCH Power - 6103 1Phase

GPU Power - ISL6334 4-Phase,(Dr.Mos)

A A

PHASE Dropping & PSI

ATX F_Panel/EMI/TPM

Power Meter/W604GPIO CTL,CPU/PCH XDP

5

,29

30

31

32

33

34

35 ,36

37

38,39

40

41,42

4

PWM:

Controller:ISL6334 ( 4-Phase 95W )

Controller:ISL

ACPI:

INTERSIL

Other:

SATA(SATA2-300MB/s) *4

USB2.0 *14 (Rear*6 Front*4 Intrenal *4)

DVI PORT*1

VGA PORT *1

PRINT Header *1

COM PORT *1

COM Header *1

3

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7586

MS-7586

Cover Sheet

Cover Sheet

Cover Sheet

MS-7586

1

Sheet of

Sheet of

Sheet of

140

140

140

0A

0A

0A

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, October 30, 2008

Date:

Thursday, October 30, 2008

Date:

2

Thursday, October 30, 2008

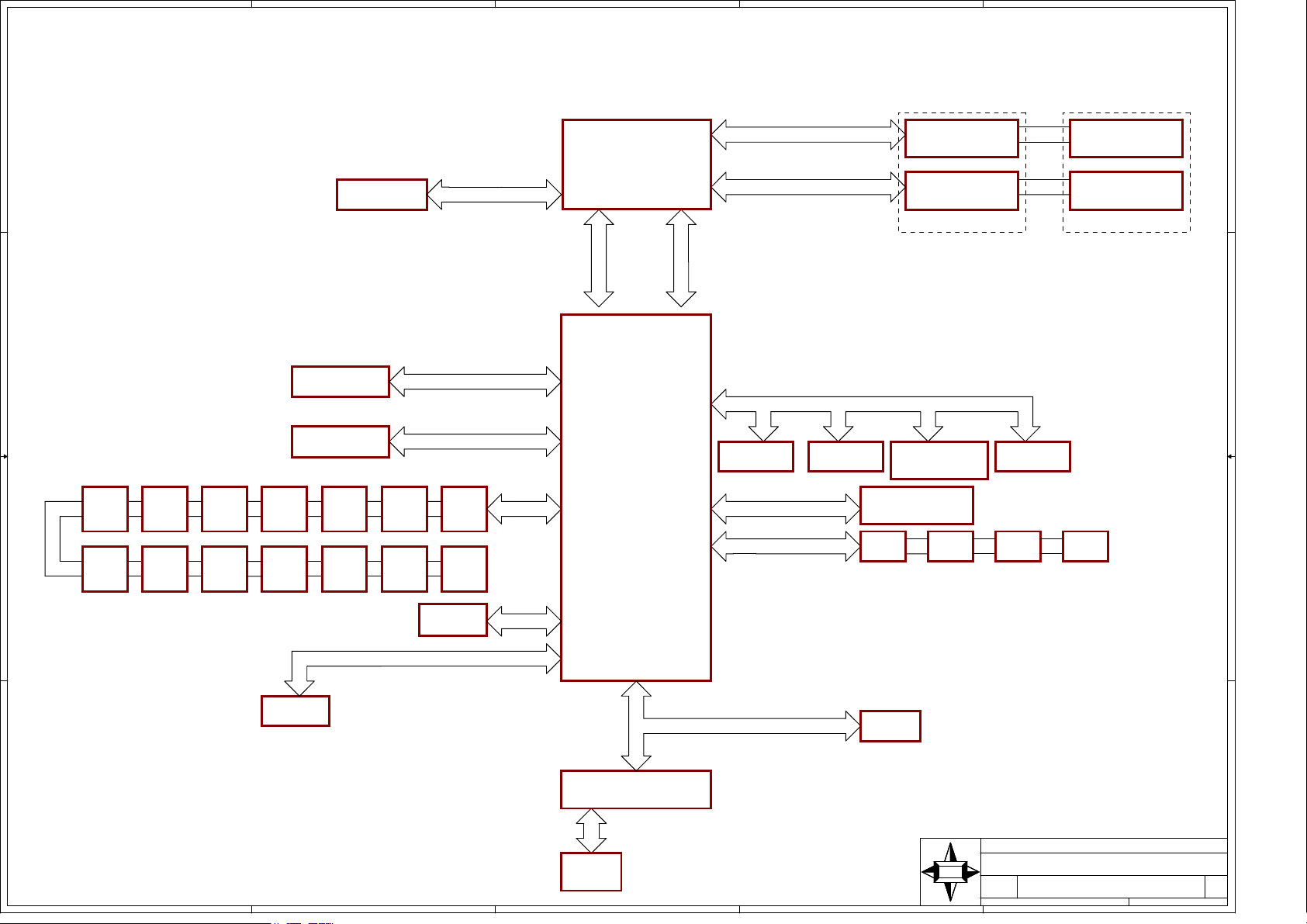

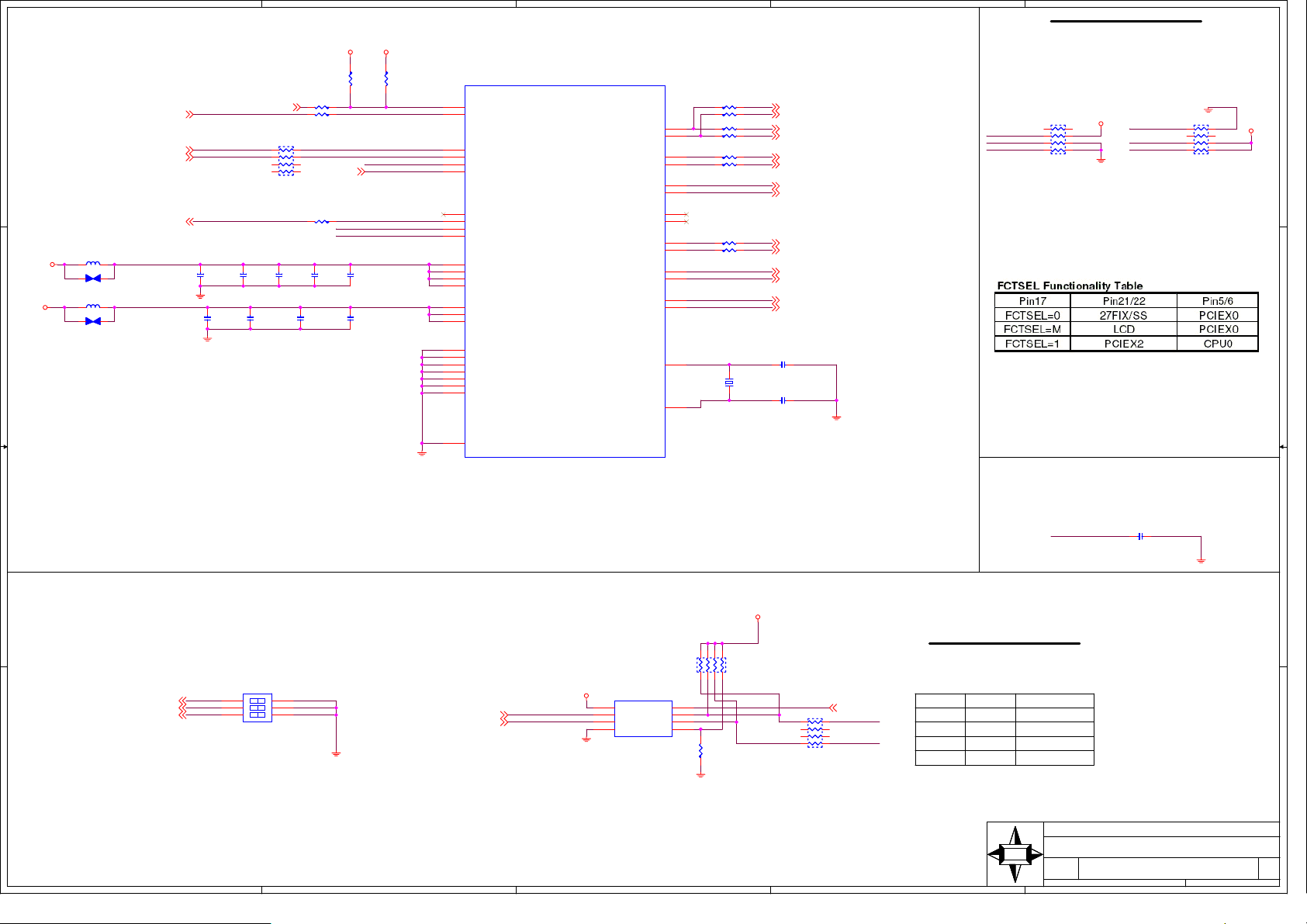

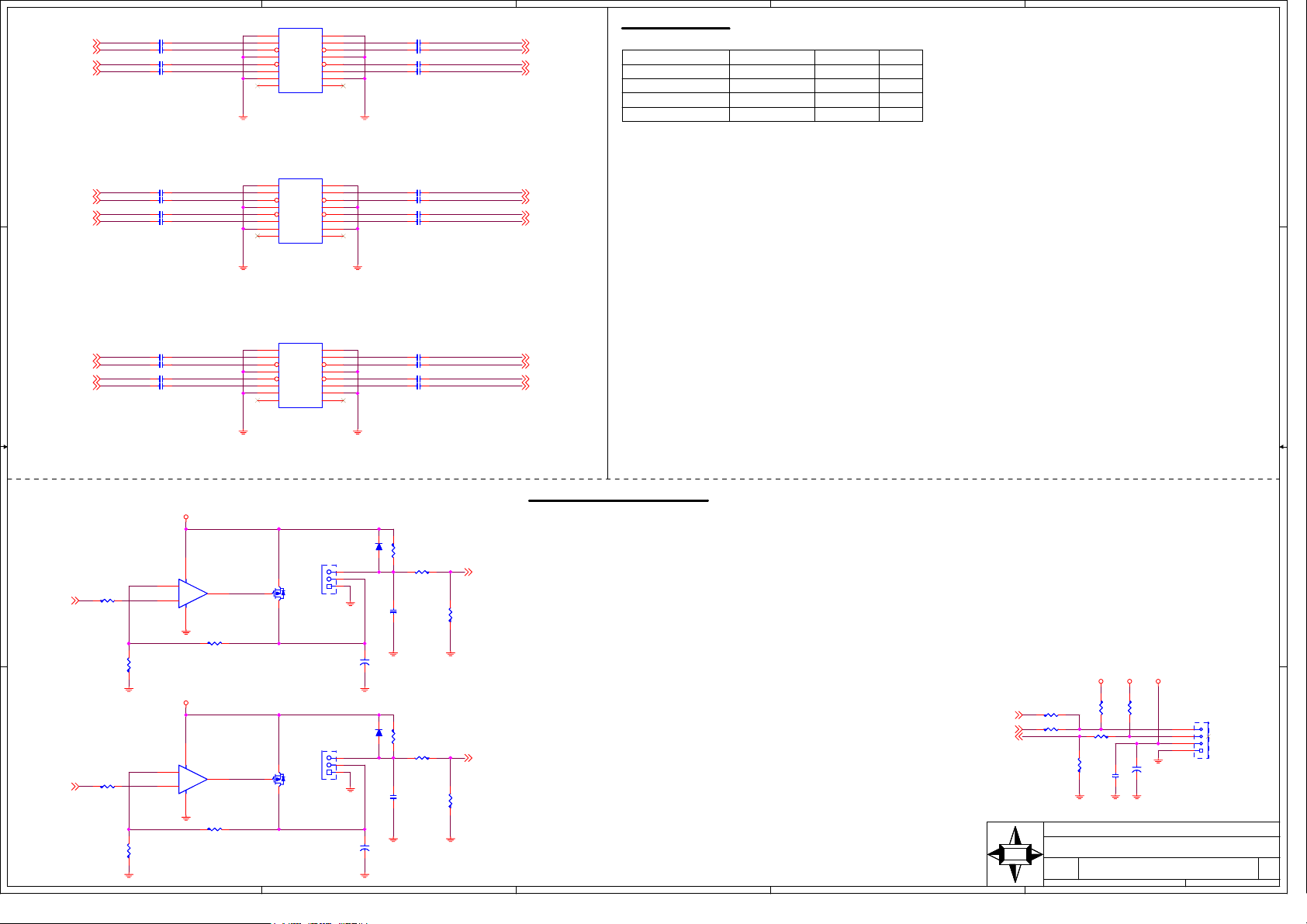

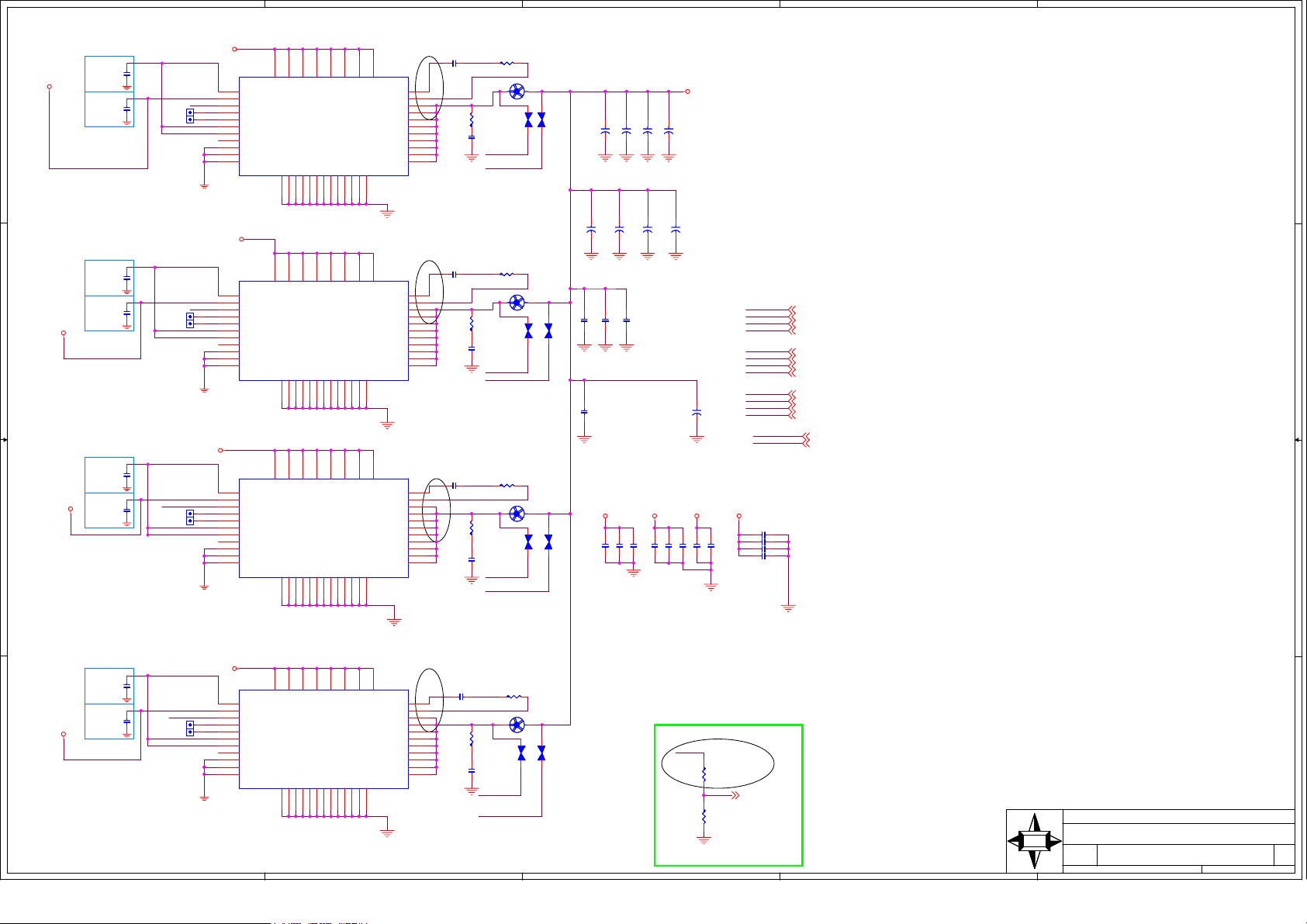

Page 2

5

INTEL CONFIDENTIAL

4

3

2

1

D D

INTEL

PCIE

SLOT

16X

16X

LGA 1160

DDRIII 1066,1333

128bit

DDRIII 1066,1333

UNBUFFERED

DDRIII DIMM1

UNBUFFERED

DDRIII DIMM2

DDRIII FIRST LOGICAL DIMM

UNBUFFERED

DDRIII DIMM3

UNBUFFERED

DDRIII DIMM4

DDRIII SECOND LOGICAL DIMM

FDI LINK DMI X4

IBEXPEAK

C C

DVI CON

VGA CON

PCIE X4

SLOT

PCIE X1

SLOT

GIGA LAN

PCIE X16

SLOT

PCH

USB-2USB-6 USB-3USB-4USB-5

B B

USB-7

USB-8 USB-9

USB-11 USB-12USB-10 USB-13

USB-1

USB-0

USB 2.0

HD AUDIO I/F

SATA II I/F

HD AUDIO ADI 1884

SATA#0 SATA#1 SATA#2 SATA#3

SPI ROM

SPI I/F

PCI BUS

PCI SLOT

#1

A A

KBD

MOUSE

COM

5

4

SIO

3

LPC I/F

TPM 1.2

2

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7586

MS-7586

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, October 22, 2008

Date:

Wednesday, October 22, 2008

Date:

Wednesday, October 22, 2008

MS-7586

Block Diagram

Block Diagram

Block Diagram

1

Sheet of

Sheet of

Sheet of

240

240

240

0A

0A

0A

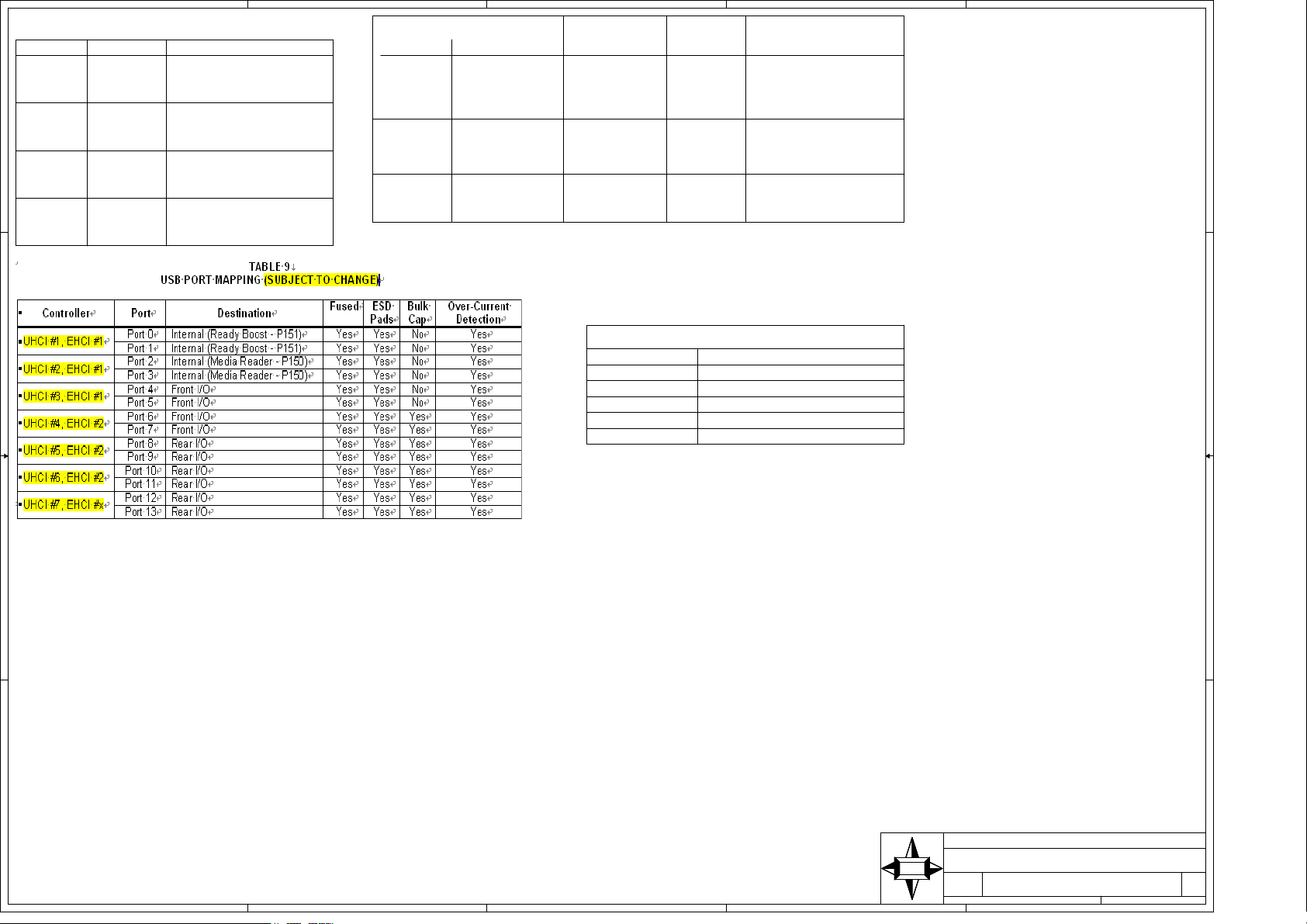

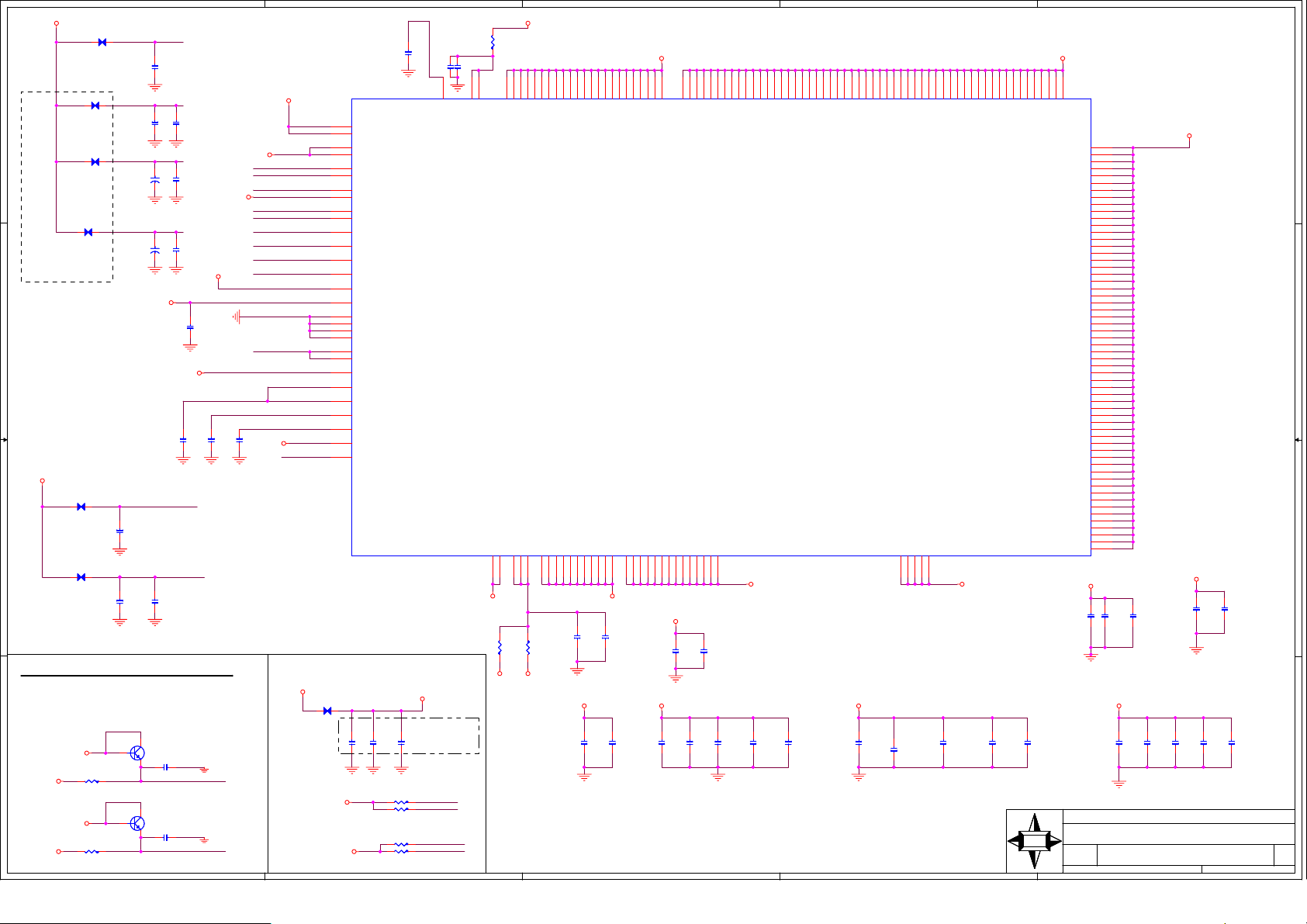

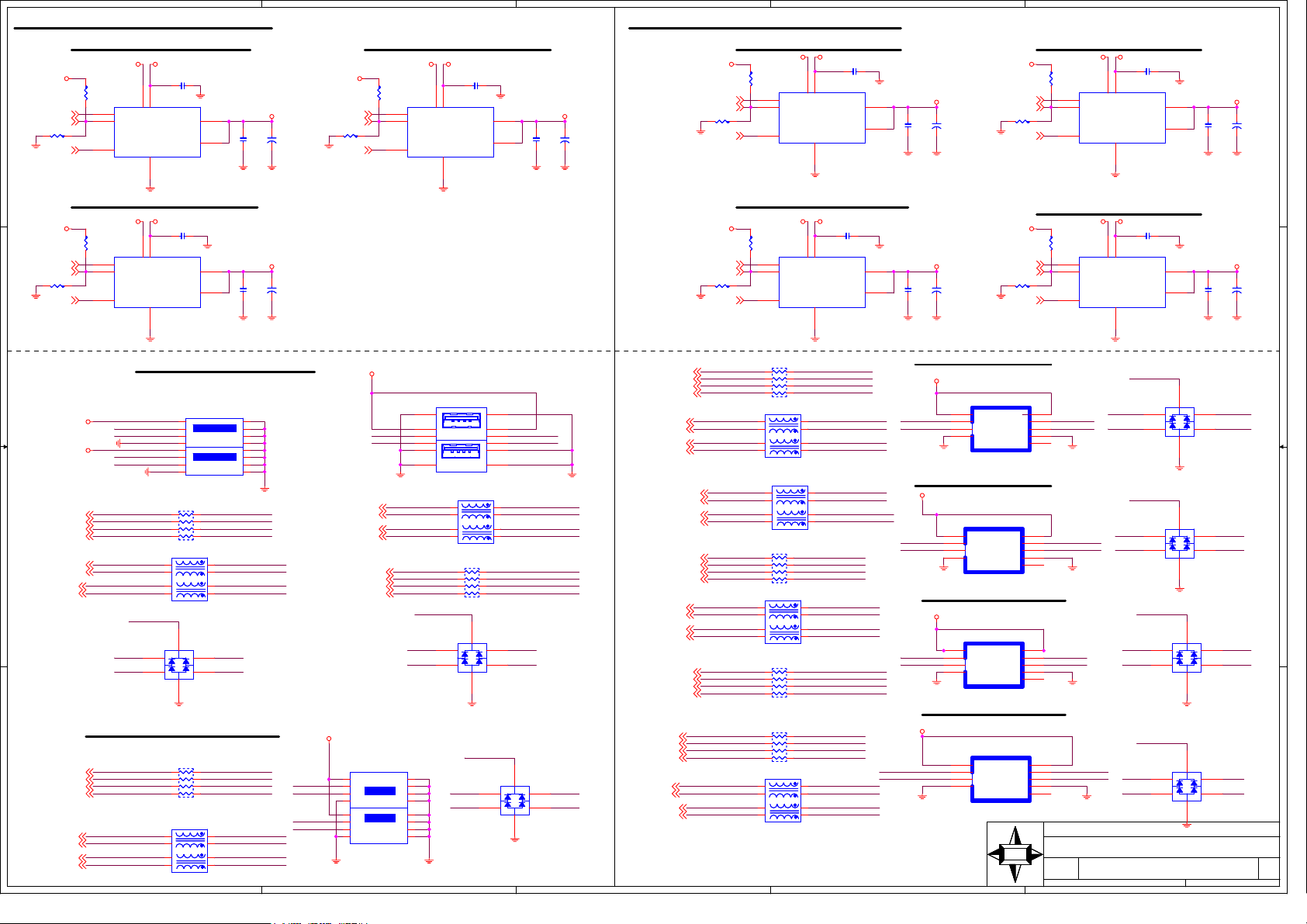

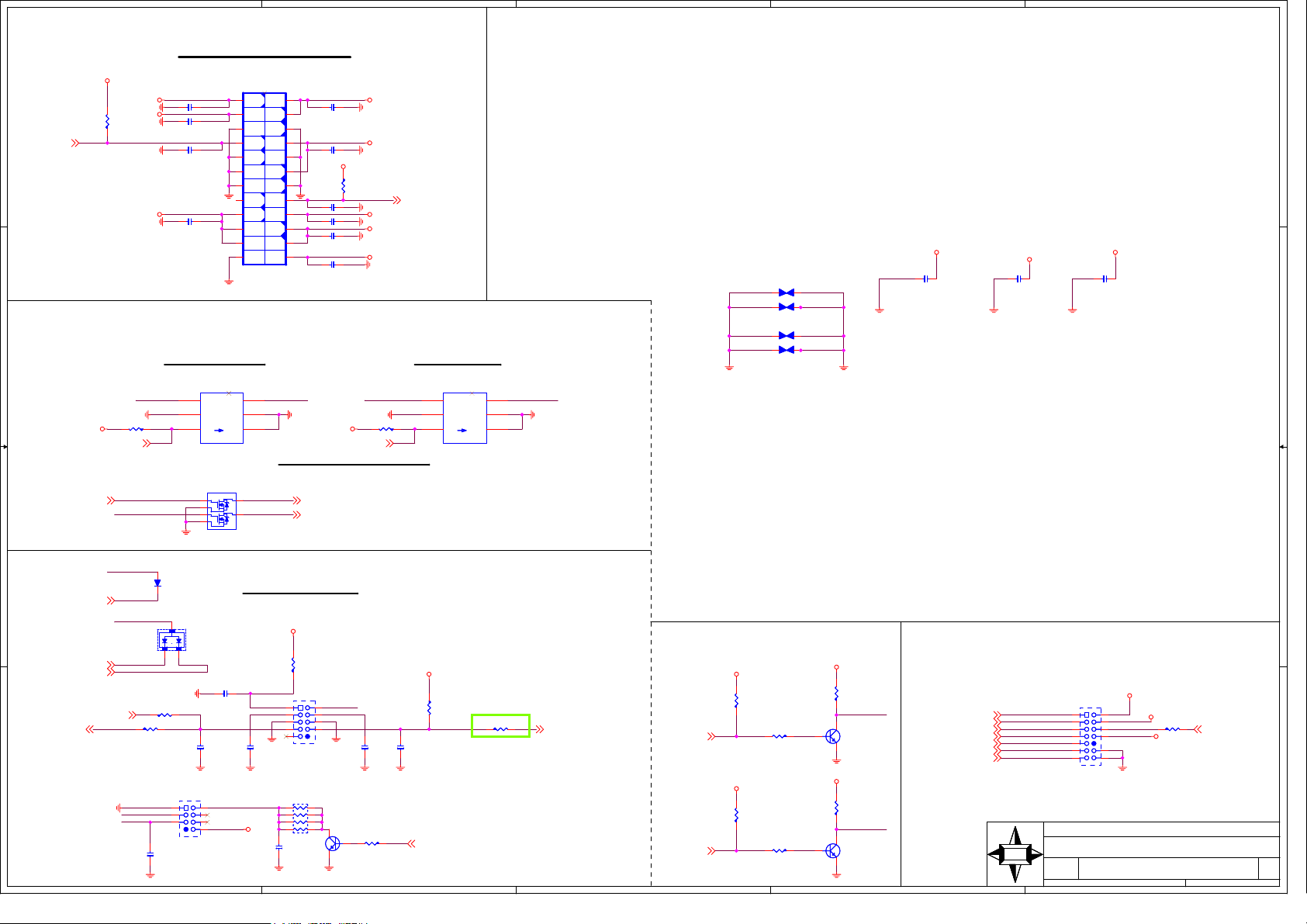

Page 3

5

4

3

2

1

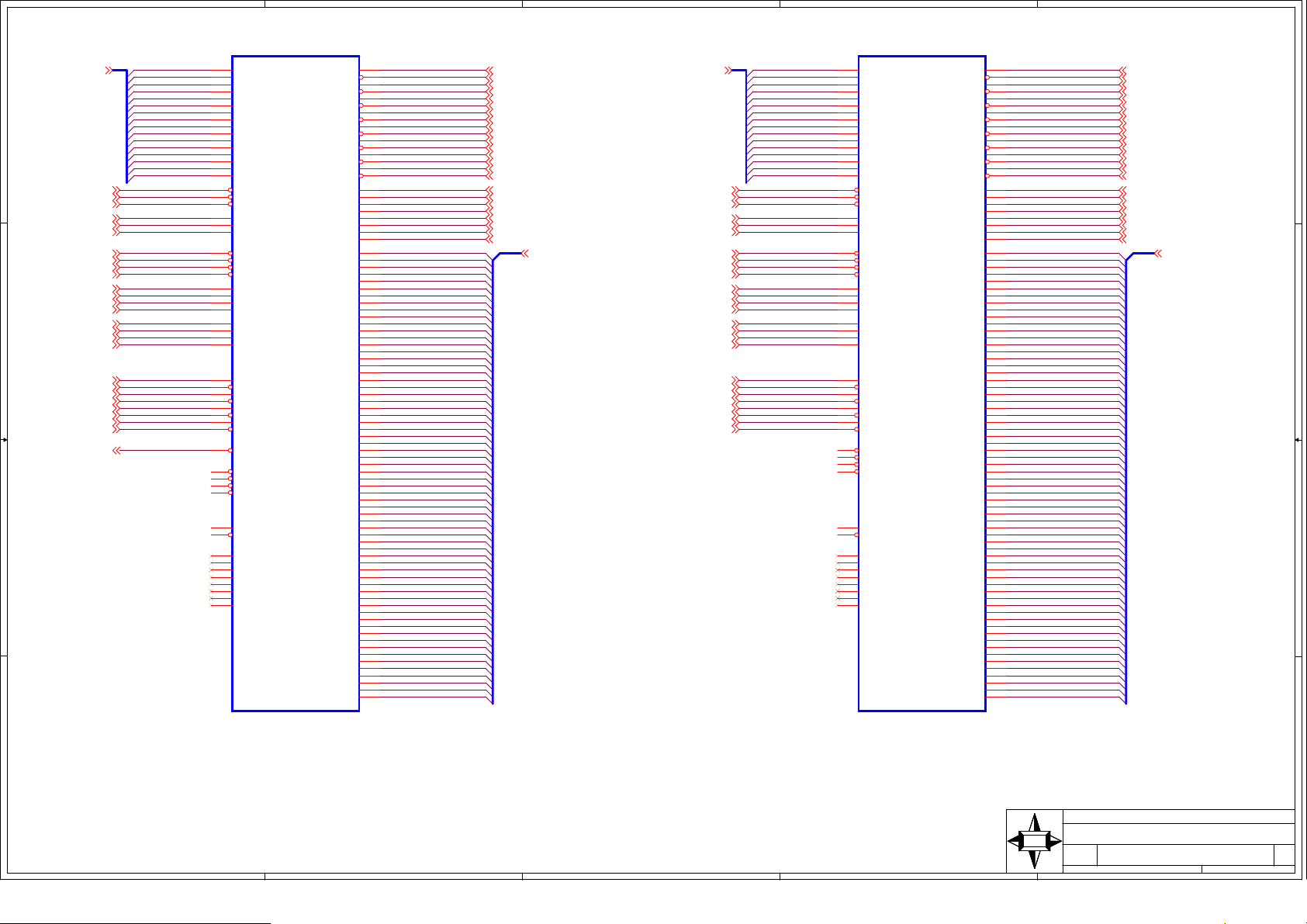

DDR DIMM Config.

DEVICE

DIMM 2

CH-A

D D

DIMM 4

10100000B

10100010B

CH-A

DIMM 1

CH-B

DIMM 3

CH-B

10100001B

10100011B

CLOCKADDRESS

MEM_MA0_CLK_H0/L0

MEM_MA0_CLK_H1/L1

MEM_MA0_CLK_H2/L2

MEM_MA1_CLK_H0/L0

MEM_MA1_CLK_H1/L1

MEM_MA1_CLK_H2/L2

MEM_MB0_CLK_H0/L0

MEM_MB0_CLK_H1/L1

MEM_MB0_CLK_H2/L2

MEM_MB1_CLK_H0/L0

MEM_MB1_CLK_H1/L1

MEM_MB1_CLK_H2/L2

PCI Config.

DEVICE MCP1 INT Pin

PCI_INT#E

PCI Slot 1

TPM

PCI_INT#F

PCI_INT#G

PCI_INT#H

REQ#/GNT#

PCI_REQ0#

PCI_GNT0#

IDSEL

AD16

CLOCK

CLK33M_PCISLOT_J20

LPCCLK0

LPCCLK1SIO

PCI RESET DEVICE

C C

Signals

PCIRST#

PE_RST#

PE_RST#

IBEXPEAK

Target

PCISLOT1

TPM_RST#

LPC/SIO

B B

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7586

MS-7586

Device Map

Device Map

Device Map

MS-7586

Sheet of

Sheet of

Sheet of

1

0A

0A

0A

340

340

340

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, October 22, 2008

Date:

Wednesday, October 22, 2008

Date:

5

4

3

2

Wednesday, October 22, 2008

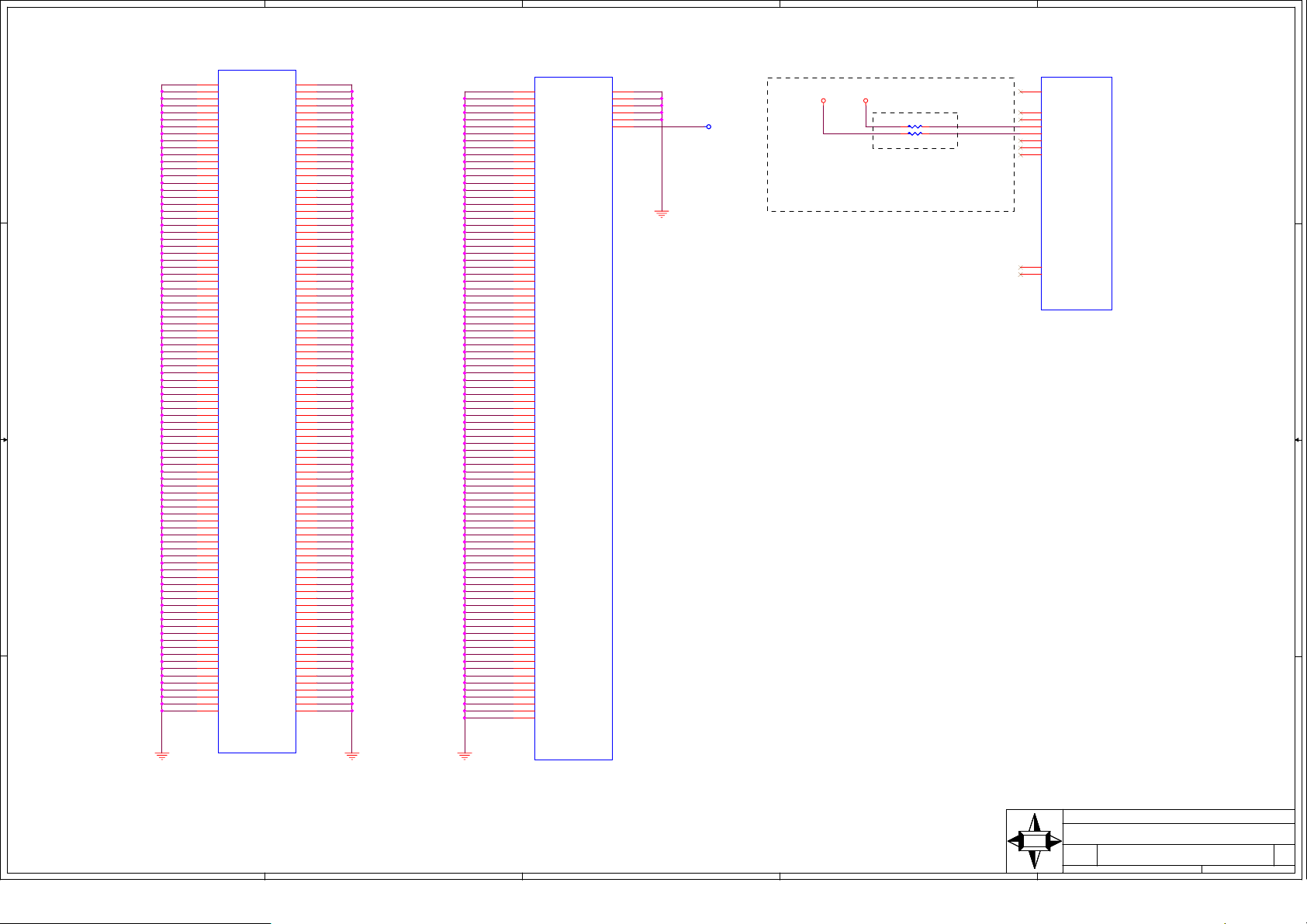

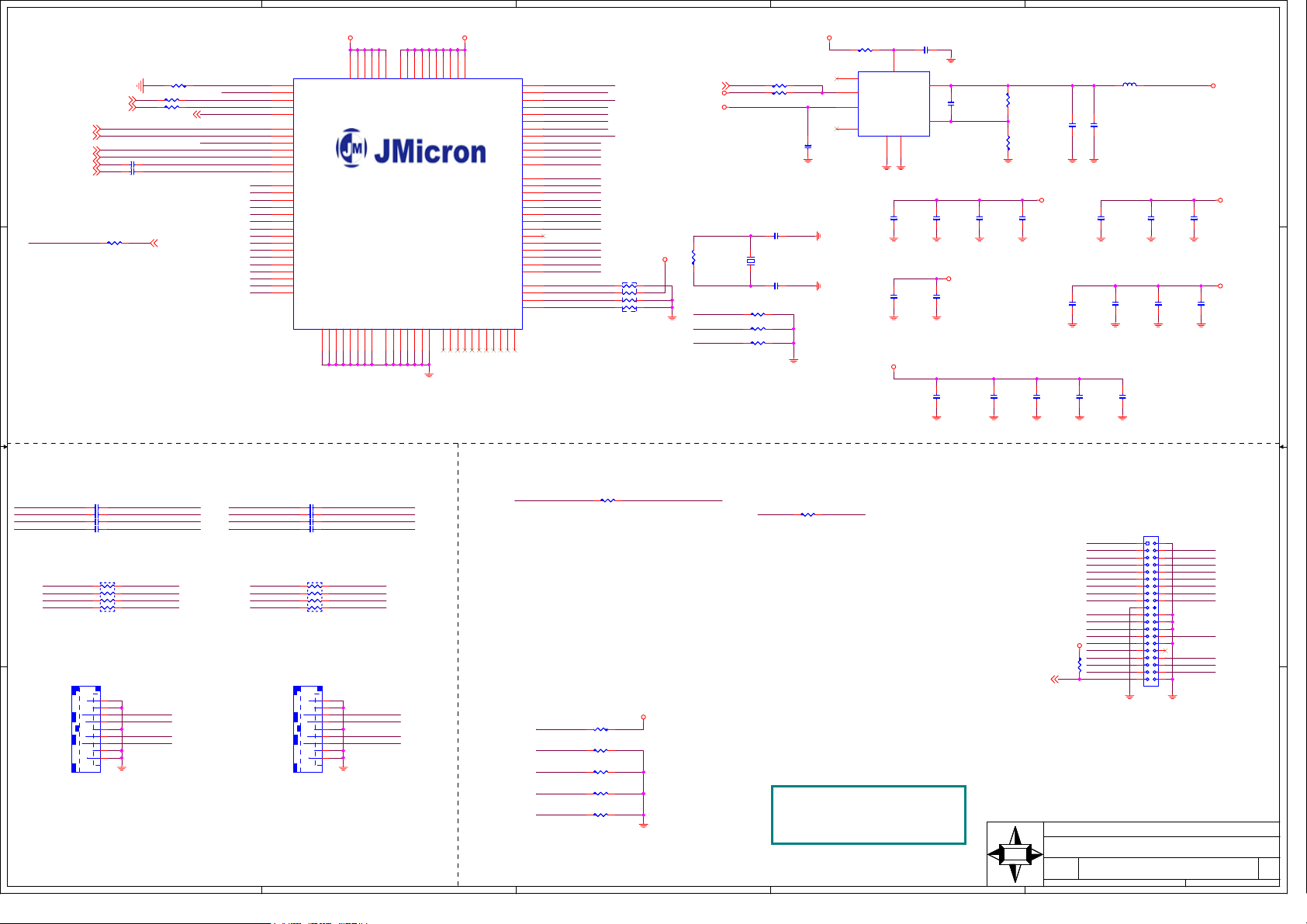

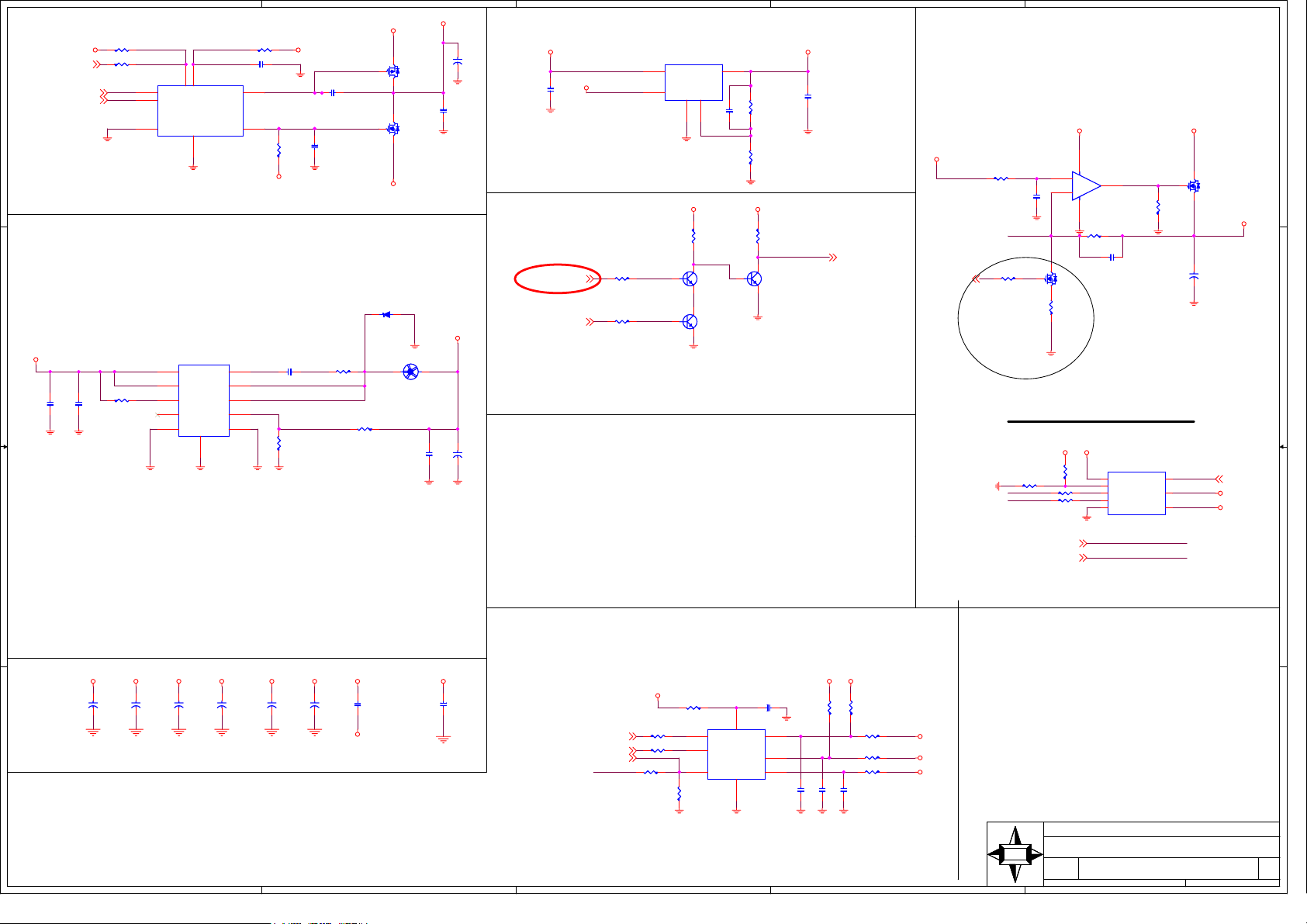

Page 4

5

D D

C C

4

3

2

1

B B

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7586

MS-7586

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

C

C

C

Date:

Wednesday, October 22, 2008

Date:

Wednesday, October 22, 2008

Date:

5

4

3

2

Wednesday, October 22, 2008

GPIO Table

GPIO Table

GPIO Table

MS-7586

1

440

440

440

Sheet of

Sheet of

Sheet of

0A

0A

0A

Page 5

5

D D

C C

4

3

2

1

B B

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7586

MS-7586

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

B

B

B

Date:

Wednesday, October 22, 2008

Date:

Wednesday, October 22, 2008

Date:

5

4

3

2

Wednesday, October 22, 2008

MS-7586

Clock Distribution

Clock Distribution

Clock Distribution

Sheet of

Sheet of

Sheet of

1

0A

0A

0A

540

540

540

Page 6

5

CPU_VTT

MEM_PWRGD15

H_THERMTRIP#14

PM_SYNC14

R235 20/4/1R235 20/4/1

R233 20/4/1R233 20/4/1

R248 100/4/1R248 100/4/1

R244 24.9/4/1R244 24.9/4/1

R247 130/4/1R247 130/4/1

R245 49.9/4/1R245 49.9/4/1

R178 49.9/4/1R178 49.9/4/1

SKTOCC#18

CLK133M_CPU_N

CLK133M_CPU_P

CPU_133M_N

CPU_133M_P

DMI_100M_P

DMI_100M_N

R162

R162

X_49.9/4/1

X_49.9/4/1

VTT_PGD35

H_PECI14,18

CLK133M_CPU_N13

CLK133M_CPU_P13

CPU_133M_N12

CPU_133M_P12

CK_DMI_P13

CK_DMI_N13

DMI_100M_P12

DMI_100M_N12

BACK SIDE

D D

CPU_PWRGD15

C C

測點在背面

B B

CFG 0~5 HAVE INTERNAL PULL-UPS

CFG HL

SEE PEG CONFIG TABLE

0

SEE PEG CONFIG TABLE

1

SEE PEG CONFIG TABLE

2

3

4

NORM

DISABLE

A A

5

PEG CONFIG TABLE

SEL2 SEL1 SEL0 PCIE CONFIG

1

1

1

1

R242 0/4R242 0/4

R243 0/4R243 0/4

CPU_133M_N_R

1

2

CPU_133M_P_R

3

4

6

8

X_COPPER

X_COPPER

X_COPPER

X_COPPER

CP3

CP3

CP2

CP2

CPU_VTT

TP9TP9

TP8TP8

CK_DMI_P

CK_DMI_N

For DP port

CPURST#

PROC_PWROK

VCCP_PWRGD

PM_EXT_TS0

PM_EXT_TS1

TP_GFX_DPRSLPVR

5

7

RN22

RN22

X_8P4R-0R0402

X_8P4R-0R0402

H_TDO_TDI_M CPU_PSI_R#

TP1TP1

VTT_PGD

MEM_PWRGD

H_PECI

H_CATERR#

H_PROCHOT#

H_THERMTRIP#

PM_SYNC

H_COMP2

H_COMP3

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

H_COMP1

H_COMP0

SKTOCC#

H_MCP_CFG0

H_MCP_CFG1

H_MCP_CFG2

H_MCP_CFG3

H_MCP_CFG4

H_MCP_CFG5

H_MCP_CFG6

H_MCP_CFG7

TP16TP16

H_MCP_CFG8

TP5TP5

H_MCP_CFG9

TP4TP4

H_MCP_CFG10

TP11TP11

H_MCP_CFG11

TP12TP12

H_MCP_CFG12

TP7TP7

H_MCP_CFG13

TP14TP14

H_MCP_CFG14

TP13TP13

H_MCP_CFG15

TP6TP6

H_MCP_CFG16

TP15TP15

H_MCP_CFG17

TP10TP10

1

3

5

7

RN18

RN18

X_8P4R-3.3KR

X_8P4R-3.3KR

1

3

5

7

RN17

RN17

X_8P4R-3.3KR

X_8P4R-3.3KR

H_MCP_CFG0

2

4

H_MCP_CFG1

6

H_MCP_CFG2

8

H_MCP_CFG3

2

H_MCP_CFG4

4

H_MCP_CFG5

6

H_MCP_CFG6

8

DESCRIPTION

PEG SEL0

PEG SEL1

PEG SEL2

REVERSED

ENABLED

PEG LANE REVERSAL

DP PRESENCE

1 1 X 16

0 2 X 8

5

CPU1E

CPU1E

AA7

BCLK[0]

AA6

BCLK[0]*

AA3

PEG_CLK

AA4

PEG_CLK*

Y8

BCLK[1]*

AA8

BCLK[1]

AF37

TDI_M

AF38

TD0_M

AF34

RSTIN*

AH36

PROC_PWROK

AH35

VCCPWRGOOD

AG37

VTTPWRGOOD

AH37

SM_DRAMPWROK

AG35

PECI

AG39

CATERR*

AH34

PROCHOT*

AF35

THERMTRIP*

AH39

PM_SYNC

AB5

PM_EXT_TS[0]*

AB4

PM_EXT_TS[1]*

B11

COMP2

C11

COMP3

AG1

SM_RCOMP[0]

AD1

SM_RCOMP[1]

AE1

SM_RCOMP[2]

AF2

COMP1

AF36

COMP0

AK38

SKTOCC*

E8

CFG0

G8

CFG1/RSVD

E10

CFG2/RSVD

F10

CFG3/PEG_LANE_REVERSAL

H10

CFG4/RSVD

H9

CFG5/VSS

E9

CFG6/FC_E9

F9

CFG7/FC_F9

G12

CFG8/FC_G12

H12

CFG9/FC_H12

K10

CFG10/FC_K10

K8

CFG11/FC_K8

J12

CFG12/FC_J12

L8

CFG13/FC_L8

K9

CFG14/FC_K9

K12

CFG15/FC_K12

H7

CFG16/FC_H7

L11

CFG17/FC_L11

A4

RSVD

B3

RSVD

C2

RSVD

D1

RSVD

J10

GFX_DPRSLPVR/RSVD

AK11

RSVD

AK12

RSVD

AK13

RSVD

AK14

RSVD

AL12

RSVD

AM15

RSVD

AM16

RSVD

AM18

RSVD

AM19

RSVD

AM20

RSVD

AM21

RSVD

AU40

RSVD

AV1

RSVD

AV39

RSVD

AW2

RSVD

AW38

RSVD

AY37

RSVD

H_CATERR#

CPURST#

PM_SYNC

H_PECI

CPU_RESET_OUT#

H_THERMTRIP#

H_PROCHOT#

XDP_CPU_PRDY#

CPU_TDO

CPU_TRST#

CPU_TDI

CPU_TMS

CPU_TCK

demo board empty

check list not empty

4

VID[0]/MSID[0]

VID[1]/MSID[1]

VID[2]/MSID[2]

VID[3]/MSID[3]

VID[4]/MSID[4]

VID[5]/MSID[5]

GFX_VR_EN

GFX_IMON/RSVD

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

FC_AE38

VTT_SELECT

FC_AG40

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

VAXG_SENSE

VSSAXG_SENSE

BCLK_ITP*

BCLK_ITP

TAPPWRGOOD

RESET_OBS*

MISC

MISC

5 OF 12

5 OF 12

N12-160A010-F02

RN11 8P4R-51R0402RN11 8P4R-51R0402

R173 51/4R173 51/4

RN9 8P4R-51R0402RN9 8P4R-51R0402

1

3

5

7

R167 X_51/4R167 X_51/4

RN10 8P4R-51R0402RN10 8P4R-51R0402

1

3

5

7

4

ISENSE

TRST*

PRDY*

PREQ*

BPM[0]*

BPM[1]*

BPM[2]*

BPM[3]*

BPM[4]*

BPM[5]*

BPM[6]*

BPM[7]*

1

3

5

7

2

4

6

8

2

4

6

8

VID[6]

VID[7]

PSI*

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

TDO

TCK

TMS

DBR*

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

3

EXP_A_RXP_019

U40

U39

U38

U37

U36

U35

U34

U33

AG38

F12

F6

G10

B12

E12

E11

C12

G11

J11

AE38

AF39

AG40

T35

T34

AE35

AE36

A13

B13

T40

AL18

AK18

T39

M12

L12

AL15

AL14

AM38

AM37

TDI

AN38

AN40

AM39

AJ38

AK37

AL40

AK40

AK39

AK34

AL39

AL33

AL32

AK33

AK32

AM31

AL30

AK30

AK31

AL17

AM17

AM25

AL29

AM30

AK29

AK28

AM29

AM28

AL27

AK27

AM26

AM27

AL26

AK26

AK25

CPU_VTT

2

4

6

8

CPU_VTT

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

H_VID7

H_GFX_VID0

H_GFX_VID1

H_GFX_VID2

H_GFX_VID3

H_GFX_VID4

H_GFX_VID5

H_GFX_VID6

CPU_VCC_SENSE

CPU_VSS_SENSE

VCCP_IMON

CPU_TDO

CPU_TDI

CPU_TCK

CPU_TMS

CPU_TRST#

XDP_CPU_PRDY#

XDP_CPU_PREQ#

FP_RST#

XDP_CPU_BCLK_N

XDP_CPU_BCLK_P

XDP_CPU_PWRGD

CPU_RESET_OUT#

XDP_CPU_BPM_N0

XDP_CPU_BPM_N1

XDP_CPU_BPM_N2

XDP_CPU_BPM_N3

XDP_CPU_BPM_N4

XDP_CPU_BPM_N5

XDP_CPU_BPM_N6

XDP_CPU_BPM_N7

PLTRST#15,18,39

R179 0/4R179 0/4

GFX_IMON

H_PROCHOT#

Demo board 1.1 change

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

R147 X_2K/4R147 X_2K/4

C81

C81

X_100p/50V/NPO/4

X_100p/50V/NPO/4

demo board no connect

H_VID[7..0] 35

CPU_PSI# 37

GFX_VR_EN 32

R240 0/4R240 0/4

H_GFX_VID[6..0] 32

VTT_SELECT 31

CPU_VCC_SENSE 35

CPU_VSS_SENSE 35

GFX_VCC_SENSE 32

GFX_VSS_SENSE 32

VCCP_IMON 18,37

CPU_TDO 39

CPU_TDI 39

CPU_TCK 39

CPU_TMS 39

CPU_TRST# 39

XDP_CPU_PRDY# 39

XDP_CPU_PREQ# 39

FP_RST# 15,38,39

XDP_CPU_BCLK_N 39

XDP_CPU_BCLK_P 39

XDP_CPU_PWRGD 39

CPU_RESET_OUT# 39

XDP_CPU_BPM_N0 39

XDP_CPU_BPM_N1 39

XDP_CPU_BPM_N2 39

XDP_CPU_BPM_N3 39

XDP_CPU_BPM_N4 39

XDP_CPU_BPM_N5 39

XDP_CPU_BPM_N6 39

XDP_CPU_BPM_N7 39

CPU_VTT

B

Q25

Q25

C E

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

CPU_VTT

R137

R137

4.7K/4

4.7K/4

B

Q26

Q26

CE

R149

R149

X_1K/4

X_1K/4

3

R141

R141

2.7K/4

2.7K/4

CPURST#

SIO_TRIP# 18

EXP_A_RXN_019

EXP_A_RXP_119

EXP_A_RXN_119

EXP_A_RXP_219

EXP_A_RXN_219

EXP_A_RXP_319

EXP_A_RXN_319

EXP_A_RXP_419

EXP_A_RXN_419

EXP_A_RXP_519

EXP_A_RXN_519

EXP_A_RXP_619

EXP_A_RXN_619

EXP_A_RXP_719

EXP_A_RXN_719

EXP_A_RXP_819

EXP_A_RXN_819

EXP_A_RXP_919

EXP_A_RXN_919

EXP_A_RXP_1019

EXP_A_RXN_1019

EXP_A_RXP_1119

EXP_A_RXN_1119

EXP_A_RXP_1219

EXP_A_RXN_1219

EXP_A_RXP_1319

EXP_A_RXN_1319

EXP_A_RXP_1419

EXP_A_RXN_1419

EXP_A_RXP_1519

EXP_A_RXN_1519

DMI_RX013

DMI_RX0#13

DMI_RX113

DMI_RX1#13

DMI_RX213

DMI_RX2#13

DMI_RX313

DMI_RX3#13

FDI_FSYNC014

FDI_LSYNC014

FDI_FSYNC114

FDI_LSYNC114

FDI_INT14

DMI_RX0

DMI_RX0#

DMI_RX1

DMI_RX1#

DMI_RX2

DMI_RX2#

DMI_RX3

DMI_RX3#

FDI_FSYNC0

FDI_FSYNC1

FDI_LSYNC1

FDI_INT

2

CPU1C

CPU1C

C9

PEG_RX[0]

D9

PEG_RX[0]*

B8

PEG_RX[1]

C8

PEG_RX[1]*

A7

PEG_RX[2]

A6

PEG_RX[2]*

B6

PEG_RX[3]

C6

PEG_RX[3]*

A5

PEG_RX[4]

B5

PEG_RX[4]*

B4

PEG_RX[5]

C4

PEG_RX[5]*

C3

PEG_RX[6]

D3

PEG_RX[6]*

D2

PEG_RX[7]

E2

PEG_RX[7]*

E1

PEG_RX[8]

F1

PEG_RX[8]*

G3

PEG_RX[9]

G2

PEG_RX[9]*

G1

PEG_RX[10]

H1

PEG_RX[10]*

J3

PEG_RX[11]

J2

PEG_RX[11]*

J1

PEG_RX[12]

K1

PEG_RX[12]*

L2

PEG_RX[13]

L3

PEG_RX[13]*

P3

PEG_RX[14]

P4

PEG_RX[14]*

T3

PEG_RE[15]

T4

PEG_RX[15]*

R1

DMI_RX[0]

T1

DMI_RX[0]*

U3

DMI_RX[1]

U2

DMI_RX[1]*

U1

DMI_RX[2]

V1

DMI_RX[2]*

W3

DMI_RX[3]

W2

DMI_RX[3]*

AM14

RSVD

AM13

RSVD

AK15

RSVD

AK16

RSVD

CPU1D

CPU1D

AC4

FDI_FSYNC[0]

AD4

FDI_LSYNC[0]

DISPLAY

DISPLAY

LINK

LINK

AC3

FDI_FSYNC[1]

AD3

FDI_LSYNC[1]

AC2

FDI_INT

4 OF 12

4 OF 12

2

PEG

PEG

DMI

DMI

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

3 OF 12

3 OF 12

VDDIO

VDDIO

FDI_TX[0]

FDI_TX[0]*

FDI_TX[1]

FDI_TX[1]*

FDI_TX[2]

FDI_TX[2]*

FDI_TX[3]

FDI_TX[3]*

FDI_TX[4]

FDI_TX[4]*

FDI_TX[5]

FDI_TX[5]*

FDI_TX[6]

FDI_TX[6]*

FDI_TX[7]

FDI_TX[7]*

PEG_TX[0]

PEG_TX[0]*

PEG_TX[1]

PEG_TX[1]*

PEG_TX[2]

PEG_TX[2]*

PEG_TX[3]

PEG_TX[3]*

PEG_TX[4]

PEG_TX[4]*

PEG_TX[5]

PEG_TX[5]*

PEG_TX[6]

PEG_TX[6]*

PEG_TX[7]

PEG_TX[7]*

PEG_TX[8]

PEG_TX[8]*

PEG_TX[9]

PEG_TX[9]*

PEG_TX[10]

PEG_TX[10]*

PEG_TX[11]

PEG_TX[11]*

PEG_TX[12]

PEG_TX[12]*

PEG_TX[13]

PEG_TX[13]*

PEG_TX[14]

PEG_TX[14]*

PEG_TX[15]

PEG_TX[15]*

DMI_TX[0]

DMI_TX[0]*

DMI_TX[1]

DMI_TX[1]*

DMI_TX[2]

DMI_TX[2]*

DMI_TX[3]

DMI_TX[3]*

PEG_RBIAS

MSI

MSI

MSI

C7

D7

E7

E6

E5

F5

F3

F4

G6

G5

H4

H3

F7

G7

J6

J5

K3

K4

H8

J8

L6

L5

M4

M3

K7

L7

N6

N5

M8

N8

R5

R6

DMI_TX0

L1

DMI_TX0#

M1

DMI_TX1

N3

DMI_TX1#

N2

DMI_TX2

N1

DMI_TX2#

P1

DMI_TX3

R2

DMI_TX3#

R3

D11

C10

B10

A11

U6

U5

V4

V3

U8

U7

W8

W7

W5

W4

R8

R7

Y4

Y3

Y6

Y5

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Date:

Date:

GRCOMP

GRBIAS

Break-out:10mil width, 6 mil space

Other Area:10mil width, 15 mil space

FDI_TX0

FDI_TX0#FDI_LSYNC0

FDI_TX1

FDI_TX1#

FDI_TX2

FDI_TX2#

FDI_TX3

FDI_TX3#

FDI_TX4

FDI_TX4#

FDI_TX5

FDI_TX5#

FDI_TX6

FDI_TX6#

FDI_TX7

FDI_TX7#

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

CPU-CNTL/CLK/MISC

CPU-CNTL/CLK/MISC

CPU-CNTL/CLK/MISC

Thursday, November 06, 2008

Thursday, November 06, 2008

Thursday, November 06, 2008

1

EXP_A_TXP_0 19

EXP_A_TXN_0 19

EXP_A_TXP_1 19

EXP_A_TXN_1 19

EXP_A_TXP_2 19

EXP_A_TXN_2 19

EXP_A_TXP_3 19

EXP_A_TXN_3 19

EXP_A_TXP_4 19

EXP_A_TXN_4 19

EXP_A_TXP_5 19

EXP_A_TXN_5 19

EXP_A_TXP_6 19

EXP_A_TXN_6 19

EXP_A_TXP_7 19

EXP_A_TXN_7 19

EXP_A_TXP_8 19

EXP_A_TXN_8 19

EXP_A_TXP_9 19

EXP_A_TXN_9 19

EXP_A_TXP_10 19

EXP_A_TXN_10 19

EXP_A_TXP_11 19

EXP_A_TXN_11 19

EXP_A_TXP_12 19

EXP_A_TXN_12 19

EXP_A_TXP_13 19

EXP_A_TXN_13 19

EXP_A_TXP_14 19

EXP_A_TXN_14 19

EXP_A_TXP_15 19

EXP_A_TXN_15 19

DMI_TX0 13

DMI_TX0# 13

DMI_TX1 13

DMI_TX1# 13

DMI_TX2 13

DMI_TX2# 13

DMI_TX3 13

DMI_TX3# 13

R236 49.9/4/1R236 49.9/4/1

R234

R234

750/4/1

750/4/1

FDI_TX0 14

FDI_TX0# 14

FDI_TX1 14

FDI_TX1# 14

FDI_TX2 14

FDI_TX2# 14

FDI_TX3 14

FDI_TX3# 14

FDI_TX4 14

FDI_TX4# 14

FDI_TX5 14

FDI_TX5# 14

FDI_TX6 14

FDI_TX6# 14

FDI_TX7 14

FDI_TX7# 14

MS-7586

MS-7586

MS-7586

1

Sheet of

Sheet of

Sheet of

640

640

640

0A

0A

0A

Page 7

5

CPU1A

MEM_MA_ADD[15..0]10

D D

MEM_MA_WE_L10

MEM_MA_CAS_L10

MEM_MA_RAS_L10

MEM_MA_BANK010

MEM_MA_BANK110

MEM_MA_BANK210

MEM_MA_CS_L010

MEM_MA_CS_L110

MEM_MA_CS_L210

MEM_MA_CS_L310

MEM_MA_CKE010

MEM_MA_CKE110

MEM_MA_CKE210

MEM_MA_CKE310

MEM_MA_ODT010

C C

B B

MEM_MA_ODT110

MEM_MA_ODT210

MEM_MA_ODT310

MEM_MA_CLK_H010

MEM_MA_CLK_L010

MEM_MA_CLK_H110

MEM_MA_CLK_L110

MEM_MA_CLK_H210

MEM_MA_CLK_L210

MEM_MA_CLK_H310

MEM_MA_CLK_L310

DDR3_DRAMRST#10,11

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15 MEM_MB_ADD15

MEM_MA_WE_L

MEM_MA_CAS_L

MEM_MA_RAS_L

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_CS_L0

MEM_MA_CS_L1

MEM_MA_CS_L2

MEM_MA_CS_L3

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MA_CKE2

MEM_MA_CKE3

MEM_MA_ODT0

MEM_MA_ODT1

MEM_MA_ODT2

MEM_MA_ODT3

MEM_MA_CLK_H0

MEM_MA_CLK_L0

MEM_MA_CLK_H1

MEM_MA_CLK_L1

MEM_MA_CLK_H2

MEM_MA_CLK_L2

MEM_MA_CLK_H3

MEM_MA_CLK_L3

DDR3_DRAMRST#

AW18

AY15

AV15

AU15

AW14

AY13

AV14

AW13

AU14

AW12

AT19

AU13

AW11

AU24

AT11

AT22

AU22

AT20

AV20

AU19

AU12

AV21

AW24

AU21

AU23

AT10

AW10

AV10

AY10

AV23

AV24

AW23

AY24

AR22

AR21

AP18

AN18

AN21

AP21

AP19

AN19

AK22

AM22

AL23

AK23

AL10

AM10

AR10

AP10

AR11

AP11

AM11

AT9

AV8

AN9

AL9

AK9

CPU1A

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

SA_WE*

SA_CAS*

SA_RAS*

SA_BA[0]

SA_BA[1]

SA_BA[2]

SA_CS[0]*

SA_CS[1]*

SA_CS[2]*

SA_CS[3]*

SA_CKE[0]

SA_CKE[1]

SA_CKE[2]

SA_CKE[3]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_CK[0]

SA_CK[0]*

SA_CK[1]

SA_CK[1]*

SA_CK[2]

SA_CK[2]*

SA_CK[3]

SA_CK[3]*

SM_DRAMRST*

SA_CS[4]*

SA_CS[5]*

SA_CS[6]*

SA_CS[7]*

SA_DQS[8]

SA_DQS[8]*

SA_ECC_CB[0]

SA_ECC_CB[1]

SA_ECC_CB[2]

SA_ECC_CB[3]

SA_ECC_CB[4]

SA_ECC_CB[5]

SA_ECC_CB[6]

SA_ECC_CB[7]

DDR_A

DDR_A

1 OF 12

1 OF 12

SA_DQS[0]

SA_DQS[0]*

SA_DQS[1]

SA_DQS[1]*

SA_DQS[2]

SA_DQS[2]*

SA_DQS[3]

SA_DQS[3]*

SA_DQS[4]

SA_DQS[4]*

SA_DQS[5]

SA_DQS[5]*

SA_DQS[6]

SA_DQS[6]*

SA_DQS[7]

SA_DQS[7]*

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AK3

AK4

AP2

AN3

AU4

AU3

AV7

AY6

AR28

AT29

AV32

AW32

AW36

AV35

AR39

AR38

AJ2

AN1

AU1

AW6

AN29

AW31

AT34

AR37

AH1

AJ3

AL2

AL1

AG2

AH2

AK1

AK2

AN4

AN2

AR3

AR2

AM3

AM2

AP1

AP4

AT4

AU2

AW3

AW4

AT3

AT1

AV2

AR5

AY5

AW5

AT8

AY8

AV4

AV5

AU7

AW7

AN27

AT28

AP28

AR30

AP25

AR27

AR29

AN30

AU30

AU31

AV33

AW34

AV30

AW30

AU33

AW33

AW35

AY35

AV38

AU37

AY34

AU34

AV36

AW37

AT39

AT40

AN37

AN39

AU38

AU39

AP39

AP40

4

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DQS_H0 10

MEM_MA_DQS_L0 10

MEM_MA_DQS_H1 10

MEM_MA_DQS_L1 10

MEM_MA_DQS_H2 10

MEM_MA_DQS_L2 10

MEM_MA_DQS_H3 10

MEM_MA_DQS_L3 10

MEM_MA_DQS_H4 10

MEM_MA_DQS_L4 10

MEM_MA_DQS_H5 10

MEM_MA_DQS_L5 10

MEM_MA_DQS_H6 10

MEM_MA_DQS_L6 10

MEM_MA_DQS_H7 10

MEM_MA_DQS_L7 10

MEM_MA_DM0 10

MEM_MA_DM1 10

MEM_MA_DM2 10

MEM_MA_DM3 10

MEM_MA_DM4 10

MEM_MA_DM5 10

MEM_MA_DM6 10

MEM_MA_DM7 10

MEM_MA_DATA[63..0] 10

3

CPU1B

MEM_MB_ADD[15..0]11

MEM_MB_WE_L11

MEM_MB_CAS_L11

MEM_MB_RAS_L11

MEM_MB_BANK011

MEM_MB_BANK111

MEM_MB_BANK211

MEM_MB_CS_L011

MEM_MB_CS_L111

MEM_MB_CS_L211

MEM_MB_CS_L311

MEM_MB_CKE011

MEM_MB_CKE111

MEM_MB_CKE211

MEM_MB_CKE311

MEM_MB_ODT011

MEM_MB_ODT111

MEM_MB_ODT211

MEM_MB_ODT311

MEM_MB_CLK_H011

MEM_MB_CLK_L011

MEM_MB_CLK_H111

MEM_MB_CLK_L111

MEM_MB_CLK_H211

MEM_MB_CLK_L211

MEM_MB_CLK_H311

MEM_MB_CLK_L311

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_WE_L

MEM_MB_CAS_L

MEM_MB_RAS_L

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_CS_L0

MEM_MB_CS_L1

MEM_MB_CS_L2

MEM_MB_CS_L3

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MB_CKE2

MEM_MB_CKE3

MEM_MB_ODT0

MEM_MB_ODT1

MEM_MB_ODT2

MEM_MB_ODT3

MEM_MB_CLK_H0

MEM_MB_CLK_L0

MEM_MB_CLK_H1

MEM_MB_CLK_L1

MEM_MB_CLK_H2

MEM_MB_CLK_L2

MEM_MB_CLK_H3

MEM_MB_CLK_L3

AU20

AU18

AV18

AU17

AY18

AV17

AW17

AU16

AT17

AY16

AY25

AW16

AW15

AW28

AY12

AV11

AU26

AW27

AW26

AU25

AW25

AV12

AY27

AW29

AV26

AV29

AW8

AU27

AU29

AV27

AU28

AR17

AR16

AT15

AR15

AN17

AN16

AR19

AR18

AM23

AM24

AL24

AK24

AR14

AR13

AR12

AT13

AN15

AP14

AN11

AN12

AN14

AP13

AY9

AU9

AV9

CPU1B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

SB_WE*

SB_CAS*

SB_RAS*

SB_BA[0]

SB_BA[1]

SB_BA[2]

SB_CS[0]*

SB_CS[1]*

SB_CS[2]*

SB_CS[3]*

SB_CKE[0]

SB_CKE[1]

SB_CKE[2]

SB_CKE[3]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_CK[0]

SB_CK[0]*

SB_CK[1]

SB_CK[1]*

SB_CK[2]

SB_CK[2]*

SB_CK[3]

SB_CK[3]*

SB_CS[4]*

SB_CS[5]*

SB_CS[6]*

SB_CS[7]*

SB_DQS[8]

SB_DQS[8]*

SB_ECC_CB[0]

SB_ECC_CB[1]

SB_ECC_CB[2]

SB_ECC_CB[3]

SB_ECC_CB[4]

SB_ECC_CB[5]

SB_ECC_CB[6]

SB_ECC_CB[7]

DDR_B

DDR_B

2 OF 12

2 OF 12

2

MEM_MB_DQS_H0

AF4

SB_DQS[0]

SB_DQS[0]*

SB_DQS[1]

SB_DQS[1]*

SB_DQS[2]

SB_DQS[2]*

SB_DQS[3]

SB_DQS[3]*

SB_DQS[4]

SB_DQS[4]*

SB_DQS[5]

SB_DQS[5]*

SB_DQS[6]

SB_DQS[6]*

SB_DQS[7]

SB_DQS[7]*

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AE5

AH6

AJ5

AP5

AN6

AR8

AN7

AT25

AR24

AP32

AR32

AR36

AT37

AL37

AM36

AE4

AJ4

AM6

AU6

AN24

AN32

AM33

AK35

AD7

AD6

AH8

AJ8

AC7

AC6

AF5

AE6

AH5

AH7

AK6

AL4

AG6

AH4

AJ7

AK7

AM5

AL6

AM8

AR6

AL5

AM4

AR4

AM7

AU5

AT7

AP8

AM9

AT6

AR7

AL8

AR9

AN23

AP23

AR25

AR26

AT23

AP22

AN26

AT26

AT32

AP31

AM32

AT35

AT31

AR31

AR33

AR34

AU36

AR35

AN33

AP36

AP34

AU35

AP35

AP37

AL35

AM35

AJ36

AJ37

AN35

AM34

AJ35

AL36

MEM_MB_DQS_L0

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

1

MEM_MB_DQS_H0 11

MEM_MB_DQS_L0 11

MEM_MB_DQS_H1 11

MEM_MB_DQS_L1 11

MEM_MB_DQS_H2 11

MEM_MB_DQS_L2 11

MEM_MB_DQS_H3 11

MEM_MB_DQS_L3 11

MEM_MB_DQS_H4 11

MEM_MB_DQS_L4 11

MEM_MB_DQS_H5 11

MEM_MB_DQS_L5 11

MEM_MB_DQS_H6 11

MEM_MB_DQS_L6 11

MEM_MB_DQS_H7 11

MEM_MB_DQS_L7 11

MEM_MB_DM0 11

MEM_MB_DM1 11

MEM_MB_DM2 11

MEM_MB_DM3 11

MEM_MB_DM4 11

MEM_MB_DM5 11

MEM_MB_DM6 11

MEM_MB_DM7 11

MEM_MB_DATA[63..0] 11

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7586

MS-7586

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, November 06, 2008

Date:

Thursday, November 06, 2008

Date:

5

4

3

2

Thursday, November 06, 2008

MS-7586

CPU-Memory

CPU-Memory

CPU-Memory

1

Sheet of

Sheet of

Sheet of

740

740

740

0A

0A

0A

Page 8

5

CPU1F

CPU1F

CPU

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

CPU

POWER

POWER

6 OF 12

6 OF 12

H26

VCC

H28

VCC

H29

VCC

H31

VCC

H32

VCC

H34

VCC

H35

VCC

H37

VCC

H38

VCC

H40

VCC

J18

VCC

J19

VCC

J21

VCC

J22

VCC

J24

VCC

J25

VCC

J27

VCC

J28

VCC

J30

VCC

J31

VCC

J33

VCC

J34

VCC

J36

VCC

J37

VCC

J39

VCC

J40

VCC

K17

VCC

K18

VCC

K20

VCC

K21

VCC

K23

VCC

K24

VCC

K26

VCC

K27

VCC

K29

VCC

K30

VCC

K32

VCC

K33

VCC

K35

VCC

K36

VCC

K38

VCC

K39

VCC

L17

VCC

L19

VCC

L20

VCC

L22

VCC

L23

VCC

L25

VCC

L26

VCC

L28

VCC

L29

VCC

L31

VCC

L32

VCC

L34

VCC

L35

VCC

L37

VCC

L38

VCC

L40

VCC

M17

VCC

M19

VCC

M21

VCC

M22

VCC

M24

VCC

M25

VCC

M27

VCC

M28

VCC

M30

VCC

M33

VCC

M34

VCC

M36

VCC

M37

VCC

M39

VCC

M40

VCC

N33

VCC

N35

VCC

N36

VCC

N38

VCC

N39

VCC

P33

VCC

P34

VCC

P35

VCC

P36

VCC

P37

VCC

P38

VCC

P39

VCC

P40

VCC

R33

VCC

R34

VCC

R35

VCC

R36

VCC

R37

VCC

R38

VCC

R39

VCC

R40

VCC

5

VCC1_8

A23

A24

A26

A27

A33

A35

A36

A38

D D

C C

B B

A A

B23

B25

B26

B28

B29

B31

B32

B34

B35

B37

B38

C23

C24

C25

C27

C28

C30

C31

C33

C34

C36

C37

C39

C40

D23

D24

D26

D27

D29

D30

D32

D33

D35

D36

D38

D39

E22

E23

E25

E26

E28

E29

E31

E32

E34

E35

E37

E38

E40

F21

F22

F24

F25

F27

F28

F30

F31

F33

F34

F36

F37

F39

F40

G20

G21

G23

G24

G26

G27

G29

G30

G32

G33

G35

G36

G38

G39

H19

H20

H22

H23

H25

AA33

AA34

AA35

AA36

AA37

AA38

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

AD33

AD34

AD35

AD36

AD37

AD38

AD39

AD40

AE33

AE34

AE39

AE40

AF33

AG33

AJ31

AJ32

AJ21

AJ25

AJ27

AJ29

AK20

AK21

AL20

AL21

AJ17

AJ19

AK19

AJ23

AG8

CPU1G

CPU1G

V33

V34

V35

V36

V37

V38

V39

V40

Y33

Y34

Y35

Y36

Y37

Y38

AC8

AE8

AC5

AF8

AF7

VTT_01

VTT_02

VTT_03

VTT_04

VTT_05

VTT_06

VTT_07

VTT_08

VTT_09

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VTT_23

VTT_24

VTT_25

VTT_26

VTT_27

VTT_28

VTT_29

VTT_30

VTT_31

VTT_32

VTT_33

VTT_34

VTT_35

VTT_36

VTT_37

VTT_38

VTT_39

VTT_40

VTT_41

VTT_42

VTT_43

VTT_44

VTT_45

VTT_46

VTT_47

VTT_48

VTT_49

VTT_50

VTT_51

VTT_52

VTT_53

VTT_54

VTT_55

VTT_56

VTT_57

VTT_58

VTT_60

VCCPLL_01

VCCPLL_02

VCCPLL_03

7 OF 12

7 OF 12

CPU

CPU

POWER

POWER

4

CPU1H

CPU1H

A14

VAXG_01

A15

VAXG_02

A17

VAXG_03

A18

VAXG_04

B14

VAXG_05

B15

VAXG_06

B17

VAXG_07

B18

VAXG_08

C14

VAXG_09

C15

VAXG_10

C17

VAXG_11

C18

VAXG_12

C20

VAXG_13

C21

VAXG_14

D14

VAXG_15

D15

VAXG_16

D17

VAXG_17

D18

VAXG_18

D20

VAXG_19

D21

VAXG_20

E14

VAXG_21

E15

VAXG_22

E17

VAXG_23

E18

VAXG_24

E20

VAXG_25

F14

VAXG_26

F15

VAXG_27

F17

VAXG_28

F18

VAXG_29

F19

VAXG_30

G14

VAXG_31

G15

VAXG_32

G17

VAXG_33

G18

VAXG_34

H14

VAXG_35

H15

VAXG_36

H17

VAXG_37

J14

VAXG_38

J15

VAXG_39

J16

VAXG_40

K14

VAXG_41

K15

VAXG_42

K16

VAXG_43

L14

VAXG_44

L15

VAXG_45

L16

VAXG_46

M14

VAXG_47

M15

VAXG_48

M16

VAXG_49

CPU

CPU

POWER

POWER

VTT_61

VTT_62

VTT_63

VTT_64

VTT_65

VTT_66

T6

T7

T8

V7

V8

AB7

3

VCC_DDR

2

CPU_VTTVCCPVCCP CPU_VTTCPU_VTT GPU_CORE

CPU1I

CPU1I

L10

VTT_67

M10

VTT_68

M11

VTT_69

M9

VTT_70

N7

VTT_71

P6

VTT_72

P7

VTT_73

P8

VTT_74

T2

VTT_75

V2

VTT_76

V6

VTT_77

W1

VTT_78

W6

VTT_79

GPU_CORE

C189

C189

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

+CPU_GFX Decoupling

C190

C190

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C201

C201

C200

C200

C206

C206

X_4.7u/10V/12

X_4.7u/10V/12

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

1

+1.5V_DDR3-Decoupling

VCC_DDR

C187

C187

C193

C193

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

CPU SOCKET CAVITY CAPS

CPU SOCKET CAVITY CAPS

AJ11

VDDQ_01

AJ13

VDDQ_02

AJ15

VDDQ_03

AT18

VDDQ_04

AT21

VDDQ_05

AU10

VDDQ_06

AU11

VDDQ_07

AV13

VDDQ_08

AV16

VDDQ_09

AV19

VDDQ_10

AV22

AV25

AV28

AW9

AY11

AY14

AY17

AY23

AY26

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

CPU

CPU

POWER

POWER

9 OF 12

9 OF 12

CPU_VTT

C162

C162

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

+CPU_VTT Decoupling

C161

C161

4.7u/10V/12

4.7u/10V/12

C153

C153

C181

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C181

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C152

C152

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C167

C167

4.7u/10V/12

4.7u/10V/12

C89

C89

X_4.7u/10V/12

X_4.7u/10V/12

C157

C157

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

C172

C172

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

CPU_VTT

C142

C142

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

C143

C143

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

C588

C588

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

背面

CPU SOCKET CAVITY CAPS

8 OF 12

8 OF 12

+CPU_VCCP-Decoupling

C147

C147

VCC1_8

C203

C203

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

VCCP

MSI

MSI

MSI

C148

C105

C105

X_1uF/10V/Y5V/6

X_1uF/10V/Y5V/6

X_1uF/10V/Y5V/6

X_1uF/10V/Y5V/6

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, November 06, 2008

Date:

Thursday, November 06, 2008

Date:

Thursday, November 06, 2008

C148

X_1uF/10V/Y5V/6

X_1uF/10V/Y5V/6

C104

C104

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

CPU-Power

CPU-Power

CPU-Power

C149

C149

X_1uF/10V/Y5V/6

X_1uF/10V/Y5V/6

MS-7586

MS-7586

MS-7586

1

C129

C129

X_1uF/10V/Y5V/6

X_1uF/10V/Y5V/6

Sheet of

Sheet of

Sheet of

0A

0A

0A

840

840

840

VCCP

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

C182

C182

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C159

C159

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C191

C191

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

C590

C590

C146

C146

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C188

C188

C163

C163

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C168

C168

C587

C587

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C177

C177

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C158

C158

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C178

C178

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

C586

C586

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

C176

C176

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C166

C166

C174

C174

C195

C195

22uF/6.3V/X5R/0805

22uF/6.3V/X5R/0805

C591

C591

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

C202

C202

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

C204

C204

X_22uF/6.3V/X5R/0805

X_22uF/6.3V/X5R/0805

PLACE ALL 08056 CAPS INSIDE CPU SOCKET CAVITY

4

3

2

Page 9

5

CPU1J

CPU1J

A16

VSS

A25

VSS

A28

VSS

A34

VSS

A37

VSS

D D

C C

B B

A A

AB33

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AE37

AF40

AG34

AG36

AG5

AG7

AH3

AH33

AH38

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

AJ24

AJ26

AJ28

AJ30

AJ33

AJ34

AJ40

AK10

AK17

AK36

AK5

AK8

AL11

AL13

AL16

AL19

AL22

AL25

AL28

AL31

AL34

AL38

AM1

AM40

AN10

AN13

AN20

AN22

AN25

AN28

AN31

AN34

AN36

AN5

AN8

AP12

AP15

AP16

AP17

AP20

AP24

AP26

AP27

AP29

AP3

AP30

AA5

VSS

AB3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB6

VSS

AB8

VSS

AC1

VSS

AD5

VSS

AD8

VSS

AE3

VSS

VSS

AE7

VSS

AF1

VSS

VSS

AF6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ6

VSS

AJ9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL3

VSS

VSS

VSS

VSS

AL7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

10 OF 12

10 OF 12

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AP33

AP38

AP6

AP7

AP9

AR1

AR20

AR23

AR40

AT12

AT14

AT16

AT2

AT24

AT27

AT30

AT33

AT36

AT38

AT5

AU32

AU8

AV3

AV31

AV34

AV37

AV6

AY33

AY36

AY4

AY7

B16

B24

B27

B30

B33

B36

B7

B9

C13

C16

C19

C22

C26

C29

C32

C35

C38

C5

D10

D12

D13

D16

D19

D22

D25

D28

D31

D34

D37

D4

D40

D5

D6

D8

E13

E16

E19

E21

E24

E27

E3

E30

E33

E36

E39

E4

F11

F13

F16

F2

F20

F23

F26

F29

F32

F35

F38

F8

G13

4

CPU1K

CPU1K

G16

W33

W34

VSS

G19

VSS

G22

VSS

G25

VSS

G28

VSS

G31

VSS

G34

VSS

G37

VSS

G4

VSS

G40

VSS

G9

VSS

H11

VSS

H13

VSS

H16

VSS

H18

VSS

H2

VSS

H21

VSS

H24

VSS

H27

VSS

H30

VSS

H33

VSS

H36

VSS

H39

VSS

H5

VSS

H6

VSS

J13

VSS

J17

VSS

J20

VSS

J23

VSS

J26

VSS

J29

VSS

J32

VSS

J35

VSS

J38

VSS

J4

VSS

J7

VSS

J9

VSS

K11

VSS

K13

VSS

K19

VSS

K2

VSS

K22

VSS

K25

VSS

K28

VSS

K31

VSS

K34

VSS

K37

VSS

K40

VSS

K5

VSS

K6

VSS

L13

VSS

L18

VSS

L21

VSS

L24

VSS

L27

VSS

L30

VSS

L33

VSS

L36

VSS

L39

VSS

L4

VSS

L9

VSS

M13

VSS

M18

VSS

M2

VSS

M20

VSS

M23

VSS

M26

VSS

M29

VSS

M32

VSS

M35

VSS

M38

VSS

M5

VSS

M6

VSS

M7

VSS

N34

VSS

N37

VSS

N4

VSS

N40

VSS

P2

VSS

P5

VSS

R4

VSS

T33

VSS

T36

VSS

T37

VSS

T38

VSS

T5

VSS

U4

VSS

V5

VSS

VSS

VSS

11 OF 12

11 OF 12

VSS

VSS

VSS

VSS

VSS

VSS_NCTF

GND

GND

W35

W36

W37

W38

Y7

B39

3

VREF_DQ_B

TP_CGC DIMM_VREFA

TP3TP3

NOTE:R378,R461 STUFFED,IF DDR3 DIMM VREFDQ OPTION 2 UNSTUFFED.

FOLLOW DDR3 DIMM VREFDQ Platform Design

Guide Change Option 3

VREF_DQ_A

2

R310 X_0/4R310 X_0/4

R316 X_0/4R316 X_0/4

close to DIMM

DIMM_VREFB

AH40

AJ39

AM12

AD2

AE2

AF3

AG3

AG4

AY3

A12

CPU1L

CPU1L

VDDIO

VDDIO

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

NC/SPARE

NC/SPARE

12 OF 12

12 OF 12

1

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7586

MS-7586

CPU-GND

CPU-GND

CPU-GND

MS-7586

1

Sheet of

Sheet of

Sheet of

940

940

940

0A

0A

0A

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, November 06, 2008

Date:

Thursday, November 06, 2008

Date:

5

4

3

2

Thursday, November 06, 2008

Page 10

5

4

3

2

1

DDRIII DIMM_A1 DDRIII DIMM_A2

VCC3

48

187

198

167

79

188

A0

RSVD

NC/TEST4

VSS

VSS

229

232

181

A1

FREE1

FREE249FREE3

FREE4

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

7

DQS0

6

DQS0#

16

DQS1

15

DQS1#

25

DQS2

24

DQS2#

34

DQS3

33

DQS3#

85

DQS4

84

DQS4#

94

DQS5

93

DQS5#

103

DQS6

102

DQS6#

112

DQS7

111

DQS7#

43

DQS8

42

DQS8#

125

DM0/DQS9

126

NC/DQS9#

134

DM1/DQS10

135

NC/DQS10#

143

DM2/DQS11

144

NC/DQS11#

152

DM3/DQS12

153

NC/DQS12#

203

DM4/DQS13

204

NC/DQS13#

212

DM5/DQS14

213

NC/DQS14#

221

DM6/DQS15

222

NC/DQS15#

230

DM7/DQS16

231

NC/DQS16#

161

DM8/DQS17

162

NC/DQS17#

195

ODT0

77

ODT1

50

CKE0

169

CKE1

193

CS0#

76

CS1#

71

BA0

190

BA1

52

BA2

73

WE#

192

RAS#

74

CAS#

168

RESET#

184

CK0

185

CK0#

63

CK1(NU)

64

CK1#(NU)

1

VREFDQ

67

VREFCA

118

SCL

238

SDA

237

SA1

117

SA0

VSS

VSS

MEC1

MEC2

MEC3

DDEIII-240_BLUE-R

DDEIII-240_BLUE-R

235

239

DIMM1(CHANNEL-A)

MEC1

MEC2

MEC3

ADDRESS = 0:0 [SA1:SA0]

SMBCLK_DDR

SMBDATA_DDR

C73 0.1u/16V/Y/4C73 0.1u/16V/Y/4

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15 MEM_MA_ADD15

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_ODT0

MEM_MA_ODT1

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MA_CS_L0

MEM_MA_CS_L1

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_CAS_L

DDR3_DRAMRST#

MEM_MA_CLK_H0

MEM_MA_CLK_L0

MEM_MA_CLK_H1

MEM_MA_CLK_L1

VREF_DQ_A

VREF_CA_A

SMBCLK_DDR

SMBDATA_DDR

C141

C141

0.1u/16V/Y/4

0.1u/16V/Y/4

1

3

5

7

RN7 8P4R-33R0402RN7 8P4R-33R0402

MEM_MA_ADD[15..0] 7

MEM_MA_DQS_H0 7

MEM_MA_DQS_L0 7

MEM_MA_DQS_H1 7

MEM_MA_DQS_L1 7

MEM_MA_DQS_H2 7

MEM_MA_DQS_L2 7

MEM_MA_DQS_H3 7

MEM_MA_DQS_L3 7

MEM_MA_DQS_H4 7

MEM_MA_DQS_L4 7

MEM_MA_DQS_H5 7

MEM_MA_DQS_L5 7

MEM_MA_DQS_H6 7

MEM_MA_DQS_L6 7

MEM_MA_DQS_H7 7

MEM_MA_DQS_L7 7

MEM_MA_DM0 7

MEM_MA_DM1 7

MEM_MA_DM2 7

MEM_MA_DM3 7

MEM_MA_DM4 7

MEM_MA_DM5 7

MEM_MA_DM6 7

MEM_MA_DM7 7

MEM_MA_ODT0 7

MEM_MA_ODT1 7

MEM_MA_CKE0 7

MEM_MA_CKE1 7

MEM_MA_CS_L0 7

MEM_MA_CS_L1 7

MEM_MA_BANK0 7

MEM_MA_BANK1 7

MEM_MA_BANK2 7

MEM_MA_WE_L 7

MEM_MA_RAS_L 7

MEM_MA_CAS_L 7

MEM_MA_CLK_H0 7

MEM_MA_CLK_L0 7

MEM_MA_CLK_H1 7

MEM_MA_CLK_L1 7

2

4

6

8

3

VCC_DDR

R220

R220

150R/2

150R/2

C253

C253

0.1u/16V/Y/4

0.1u/16V/Y/4

SMBCLK 12,15,19,20,23,30,33,39

SMBDATA 12,15,19,20,23,30,33,39

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

DDR3_DRAMRST# 7,11

VCC5

VCC_DDR

54

DIMM1

DIMM1

3

DQ0

VDD51VDD

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

1

2

5

4

3

U18

U18

VCC

BUS_SEL

SCL

SDA

GND

uP6262

uP6262

VSS

107

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

VSS

VSS

VSS

VSS

110

113

116

119

OUT1

OUT2

OUT3

4

9

10

122

123

128

129

12

13

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

80

83

86

89

92

95

98

101

104

170

173

176

179

VDD

VDD

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

121

124

127

130

133

136

139

142

145

148

151

VREF_CA_A

8

7

6

MEM_MA_DATA[63..0]7

D D

C C

Place close to DIMM1

VCC_DDR

C165 C1u16YC165 C1u16Y

C183 C1u6.3Y0402-RHC183 C1u6.3Y0402-RH

C171 C1u16YC171 C1u16Y

C199 C1u16YC199 C1u16Y

Place close to DIMM1 with DIMM2

VCC_DDR

C137 C1u6.3Y0402-RHC137 C1u6.3Y0402-RH

Place close to DIMM2

VCC_DDR

C194 C1u6.3Y0402-RHC194 C1u6.3Y0402-RH

C164 C1u6.3Y0402-RHC164 C1u6.3Y0402-RH

B B

UPI VOLTAGE CONSOLE

VREF_CA_A

VREF_CA_A

C207

C207

0.1u/16V/Y/4

0.1u/16V/Y/4

UPI VOLTAGE CONSOLE

VREF_DQ_A

VREF_DQ_A

C265

C265

0.1u/16V/Y/4

0.1u/16V/Y/4

A A

UPI VOLTAGE CONSOLE(3+1)

MEM_MA_DATA[63..0]

R223 1K/1%/4R223 1K/1%/4

R228

R228

1K/1%/4

1K/1%/4

R314 1K/1%/4R314 1K/1%/4

R309

R309

1K/1%/4

1K/1%/4

2.083325V

0x66:RH=18K,RL=13K

SMBCLK12,15,19,20,23,30,33,39

SMBDATA12,15,19,20,23,30,33,39

5

VCC_DDR

VCC_DDR

C268

C268

X_2.2u/6

X_2.2u/6

18KR1%0402

18KR1%0402

R232 13KR1%0402R232 13KR1%0402

SMBCLK

SMBDATA

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

VCC5

R231

R231

182

183

186

189

VDD

VDD

VDD

VSS

VSS

VSS

154

157

160

163

VREF_CA_A

VREF_CA_B

4

VCC3

VTT_DDR

68

236

120

240

191

194

197

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

166

199

202

53

VTT

VTT

VDDSPD

NC/PAR_IN

NC/ERR_OUT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

205

208

211

214

217

220

223

226

SMBCLK_DDR11

SMBDATA_DDR11

VCC_DDR VCC3

54

DIMM2

DIMM2

3

DQ0

VDD51VDD

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

VSS

VSS

VSS

VSS

107

110

113

116

119

VSS

4

9

10

122

123

128

129

12

13

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

80

83

86

89

92

95

98

101

104

170

173

176

179

VDD

VDD

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

121

124

127

130

133

136

139

142

145

148

151

2

VTT_DDR

48

187

198

68

167

236

120

182

183

186

189

191

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

154

157

160

163

166

240

194

197

VDD

VDD

VDD

VDDSPD

VSS

VSS

VSS

VSS

VSS

199

202

205

208

79

53

MEM_MA_ADD0

VTT

VTT

RSVD

NC/TEST4

NC/PAR_IN

NC/ERR_OUT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

211

214

217

220

223

226

229

232

MSI

MSI

MSI

188

A0

MEM_MA_ADD1

181

A1

FREE1

FREE249FREE3

FREE4

MEM_MA_ADD2

61

A2

MEM_MA_ADD3

180

A3

MEM_MA_ADD4

59

A4

MEM_MA_ADD5

58

A5

MEM_MA_ADD6

178

A6

MEM_MA_ADD7

56

A7

MEM_MA_ADD8

177

A8

MEM_MA_ADD9

175

A9

MEM_MA_ADD10

70

A10/AP

MEM_MA_ADD11

55

A11

MEM_MA_ADD12

174

A12

MEM_MA_ADD13

196

A13

MEM_MA_ADD14

172

A14

171

A15

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

MEM_MA_DQS_H0

7

DQS0

MEM_MA_DQS_L0

6

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

DQS8#

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

RESET#

CK1(NU)

CK1#(NU)

VREFDQ

VREFCA

VSS

VSS

MEC1

235

239

MEC1

MEM_MA_DQS_H1

16

DQS1

MEM_MA_DQS_L1

15

MEM_MA_DQS_H2

25

DQS2

MEM_MA_DQS_L2

24

MEM_MA_DQS_H3

34

DQS3

MEM_MA_DQS_L3

33

MEM_MA_DQS_H4

85

DQS4

MEM_MA_DQS_L4

84

MEM_MA_DQS_H5

94

DQS5

MEM_MA_DQS_L5

93

MEM_MA_DQS_H6

103

DQS6

MEM_MA_DQS_L6

102

MEM_MA_DQS_H7

112

DQS7

MEM_MA_DQS_L7

111

43

DQS8

42

MEM_MA_DM0

125

126

MEM_MA_DM1

134

135

MEM_MA_DM2

143

144

MEM_MA_DM3

152

153

MEM_MA_DM4

203

204

MEM_MA_DM5

212

213

MEM_MA_DM6

221

222

MEM_MA_DM7

230

231

161

162

MEM_MA_ODT2

195

ODT0

MEM_MA_ODT3

77

ODT1

MEM_MA_CKE2

50

CKE0

MEM_MA_CKE3

169

CKE1

MEM_MA_CS_L2

193

CS0#

MEM_MA_CS_L3

76

CS1#

MEM_MA_BANK0

71

BA0

MEM_MA_BANK1

190

BA1

MEM_MA_BANK2

52

BA2

MEM_MA_WE_L

73

WE#

MEM_MA_RAS_L

192

RAS#

MEM_MA_CAS_L

74

CAS#

DDR3_DRAMRST#

168

MEM_MA_CLK_H2

184

CK0

MEM_MA_CLK_L2

185

CK0#

MEM_MA_CLK_H3

63

MEM_MA_CLK_L3

64

VREF_DQ_A

1

VREF_CA_A

67

SMBCLK_DDR

118

SCL

SMBDATA_DDR

238

SDA

237

SA1

117

SA0