1

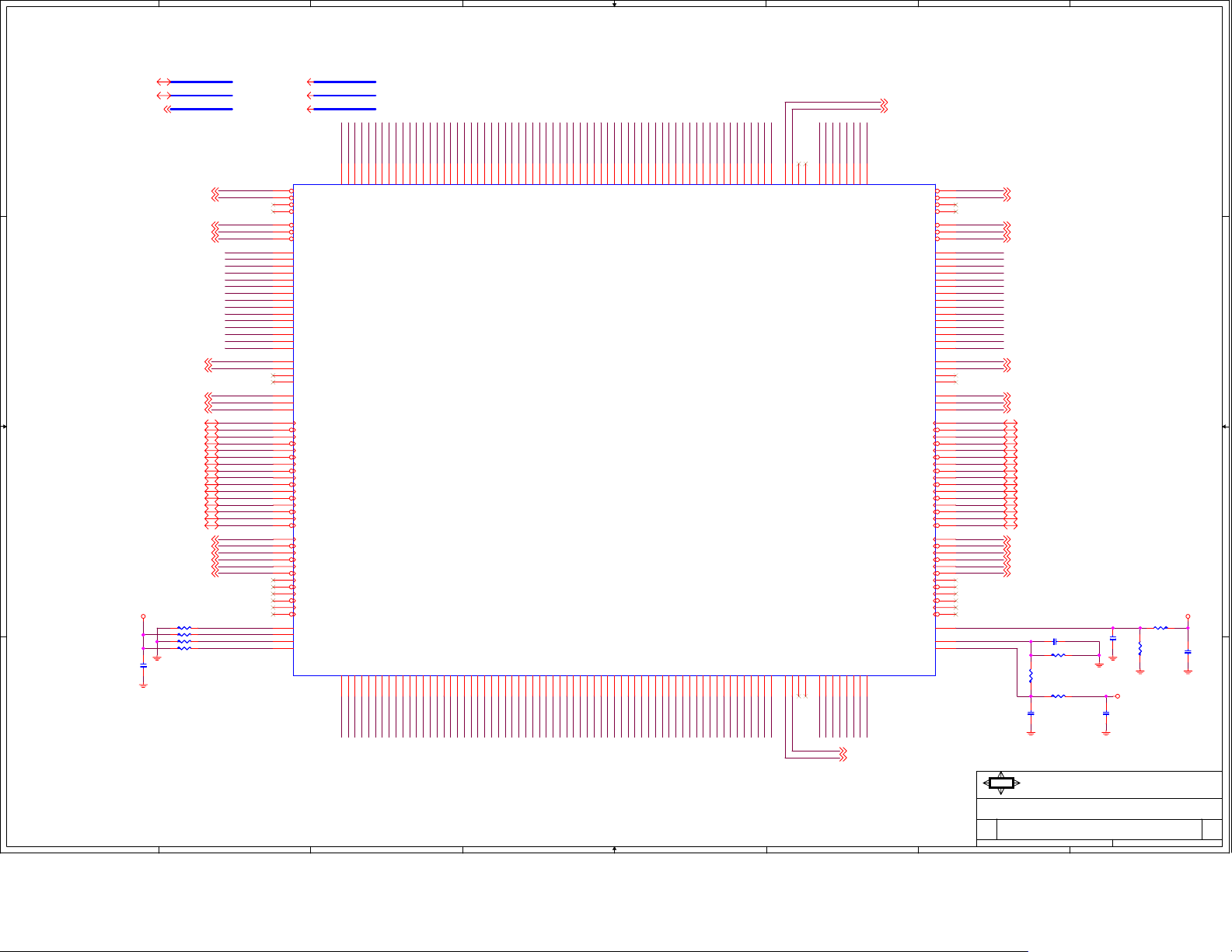

1Cover Sheet

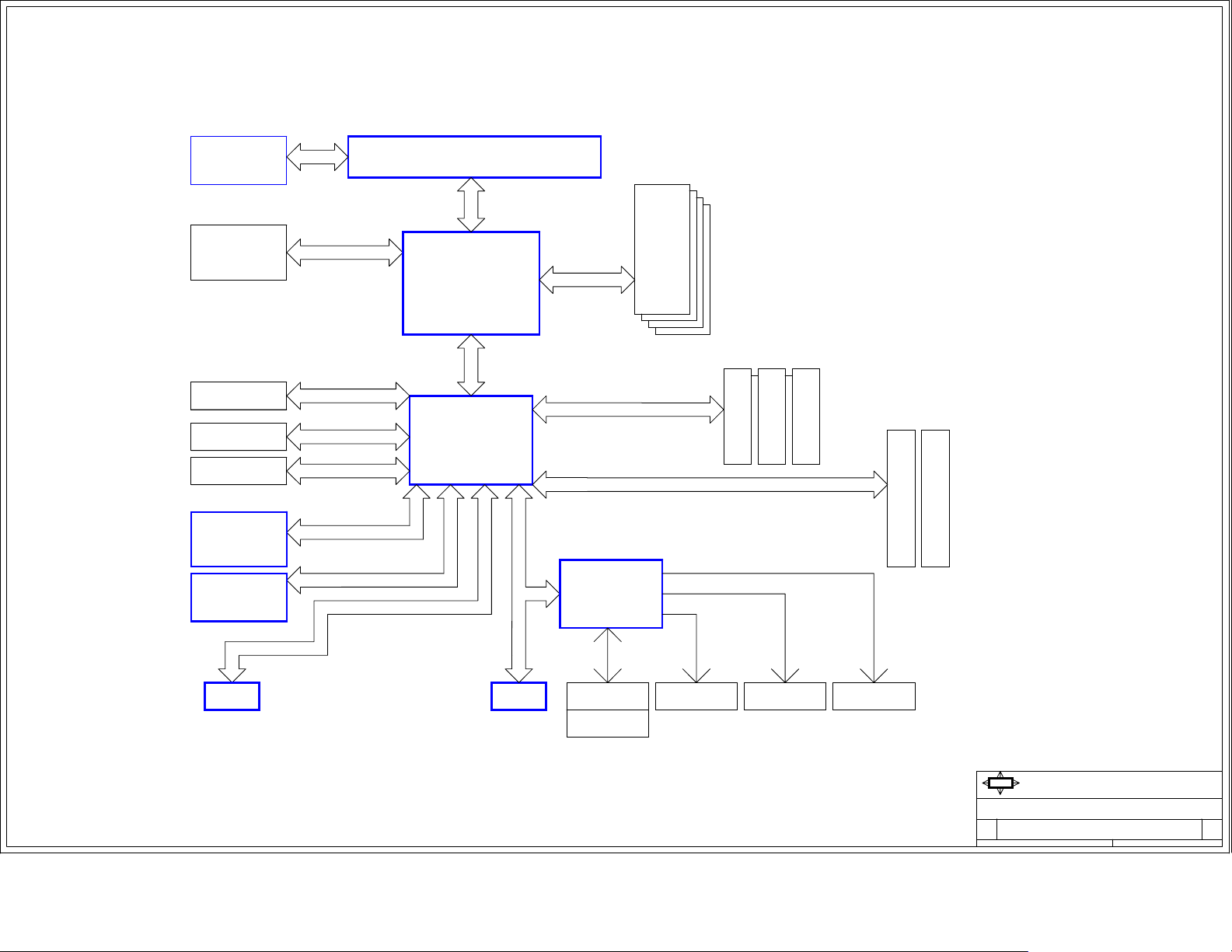

Block Diagram/Clock Map/Power Map

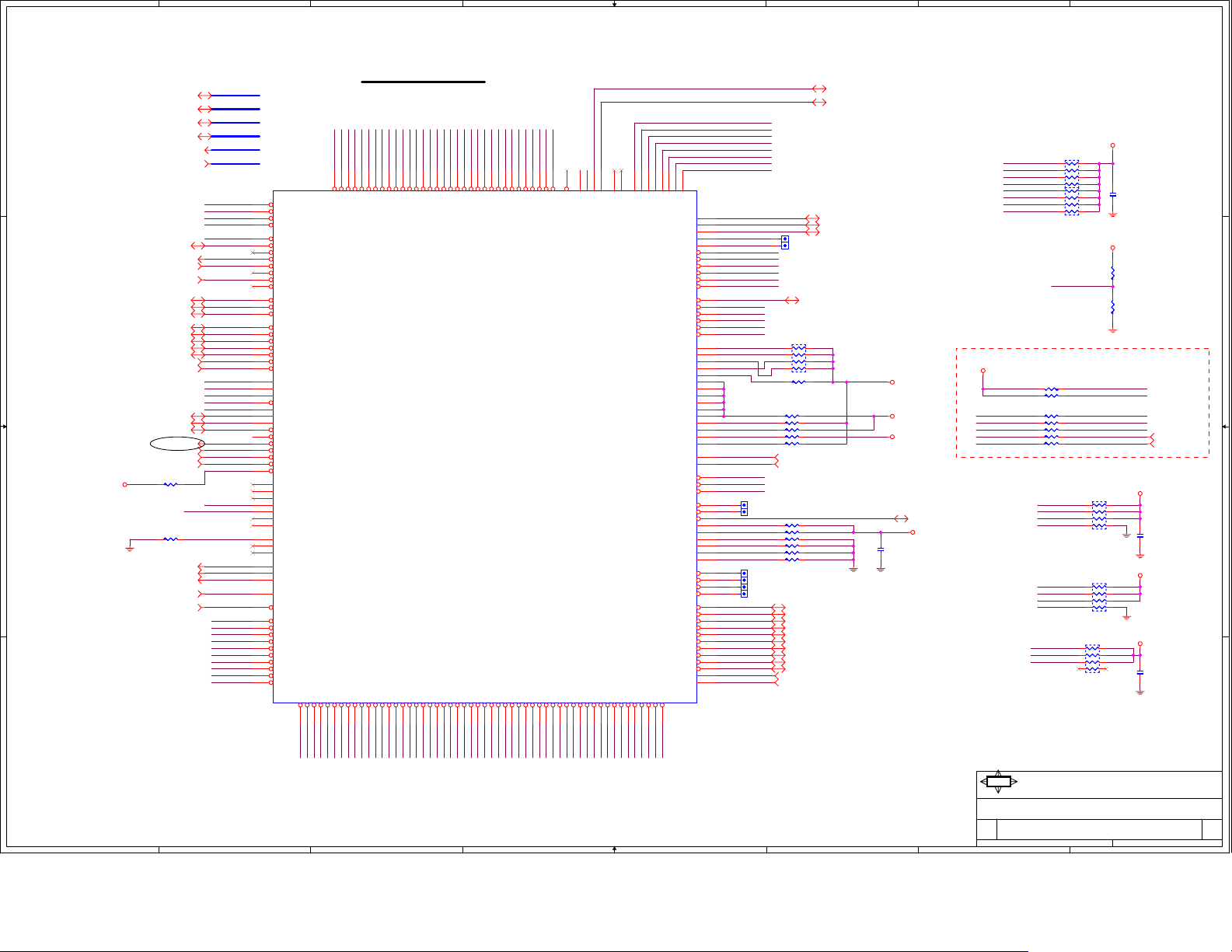

Intel LGA775 CPU

Intel Bearlake- MCH -P31/G31

Intel ICH7 - PCI & DMI & CPU & IRQ

2-4

5-7

8-11

12

Intel ICH7 - LPC & ATA & USB & GPIO 13

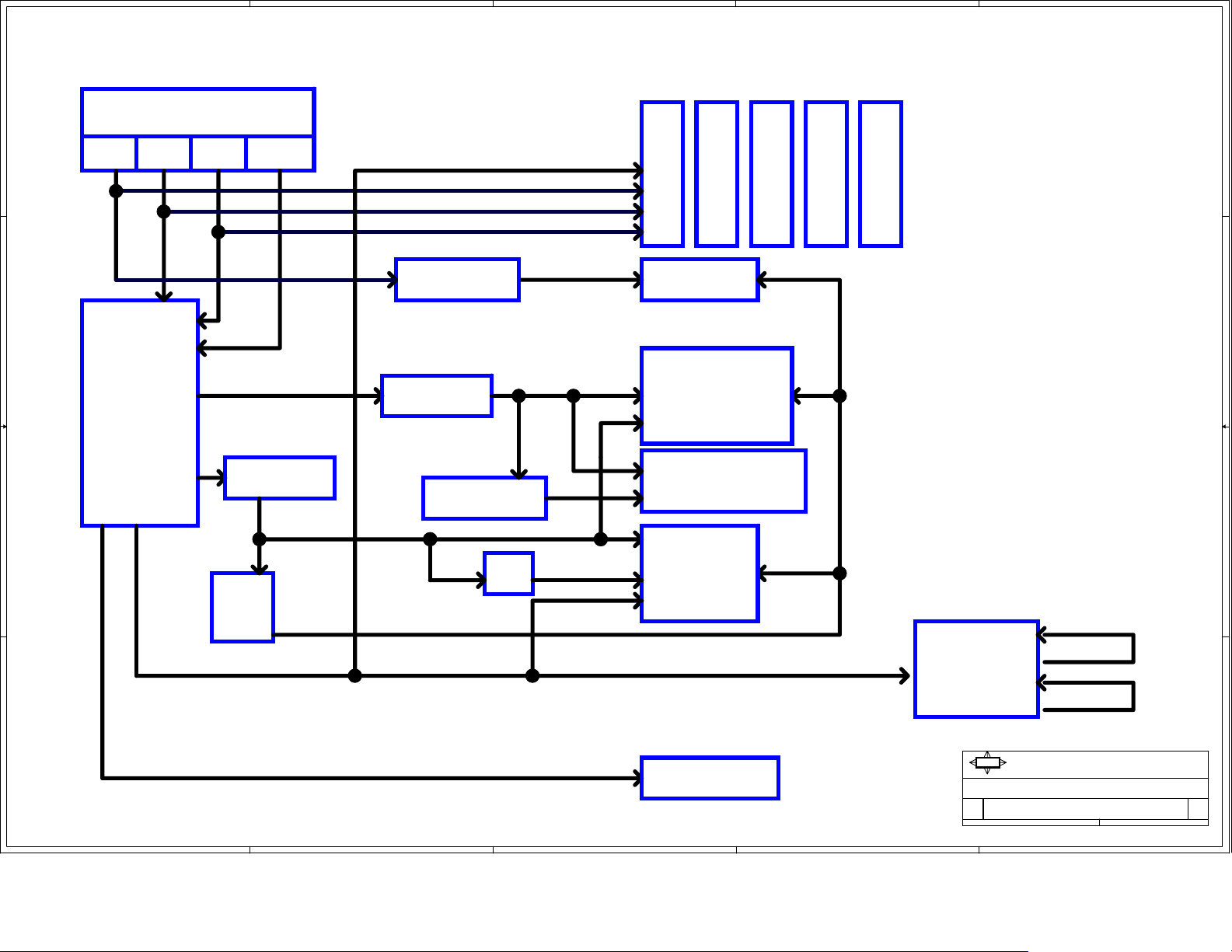

Intel ICH7 - POWER

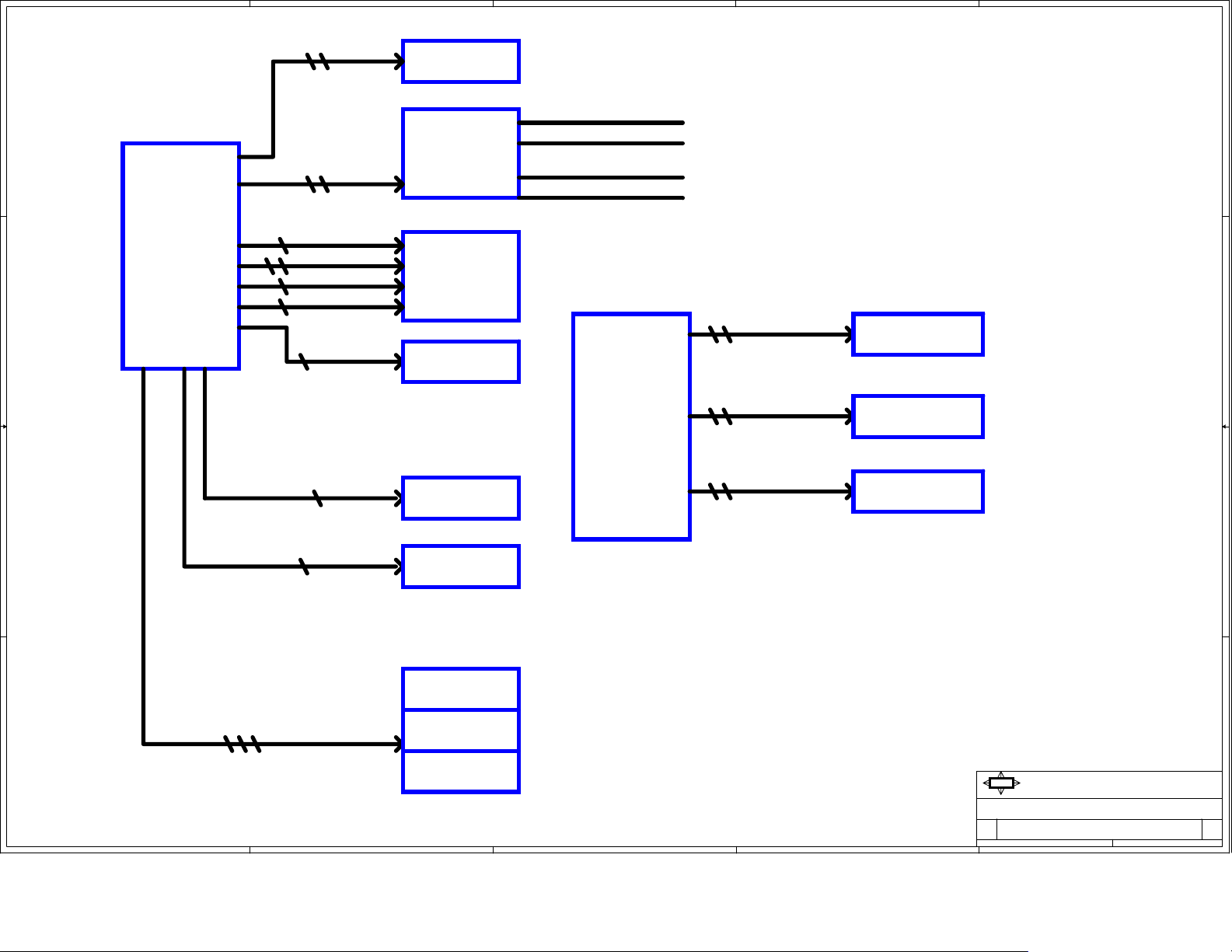

Clock - ICS9LPRS908DGLF

LPC I/O - F71882

HD- ALC888

LAN REALTEK RTL8111C/8111B

DDR II System Memory 1 & 2

DDR II System Memory 3 & 4

DDR II VTT Decoupling

PCI EXPRESS X16 & X1 Slot

A A

PCI Slot 1 & 2 & 3 Slot

14

15

16

17

18

19

20

21

22

23

24 IEEE-1394 VT6308

VGA Connectors

USB Connectors

ATX Connetcor Front Panel IDE & SATA Connectors

25

26

27

MS-7392

CPU:

Intel Pentium 4, Pentium D, Core2 Duo, Wolfdale, Kentsfield

and Yorkfield processors in LGA775 Package.

System Chipset:

Intel - MCH (North Bridge) P31

Intel ICH7R (South Bridge)

On Board Chipset:

BIOS -- SPI EEPROM

HD Codec -- ALC888

LPC Super I/O -- F71882

LAN-- REALTEK RTL8111C/8111B

CLOCK -- ICS9LPRS908DGLF

Main Memory:

DDR II * 4 (Max 4GB)

Expansion Slots:

PCI2.3 SLOT * 3

PCI EXPRESS X1 SLOT * 2

PCI EXPRESS X16 SLOT

INTELSIL PWM:

Controller: INTELSIL - ISL6322CR

Version: 2.2

CPU/SYSTEM/POWER FAN

ACPI CONTROLLER UPI

VRM 11.0 - INTELSIL - ISL6322CR

GMCH VCORE &DDR VOLTAGE

AutoBOM parts

28

29

30

31

32

MSI

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

1

Date: Sheet

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

COVER SHEET

COVER SHEET

COVER SHEET

MS-7392

MS-7392

MS-7392

of

of

of

135Wednesday, April 30, 2008

135Wednesday, April 30, 2008

135Wednesday, April 30, 2008

2.2

2.2

2.2

Controller:

ISL6322CR

1

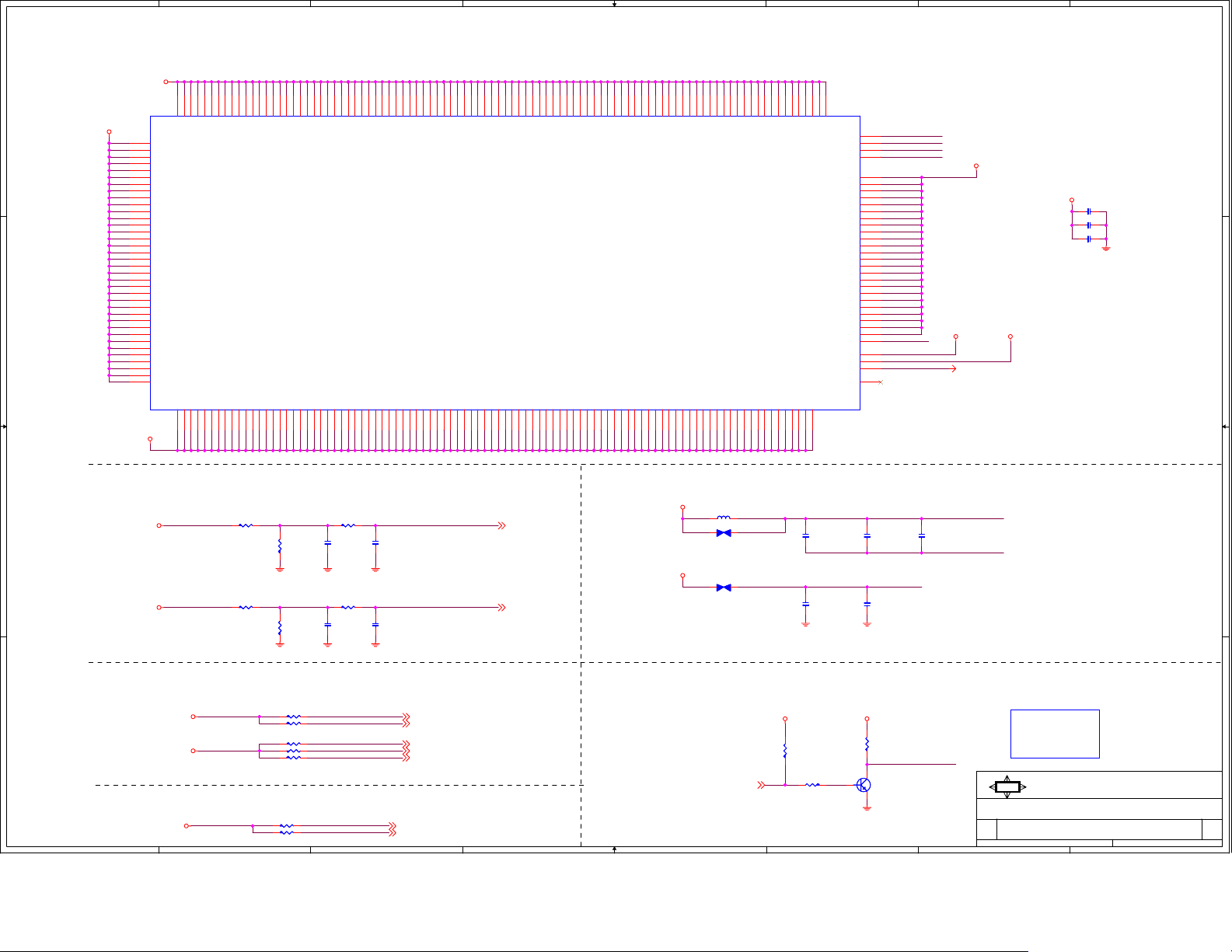

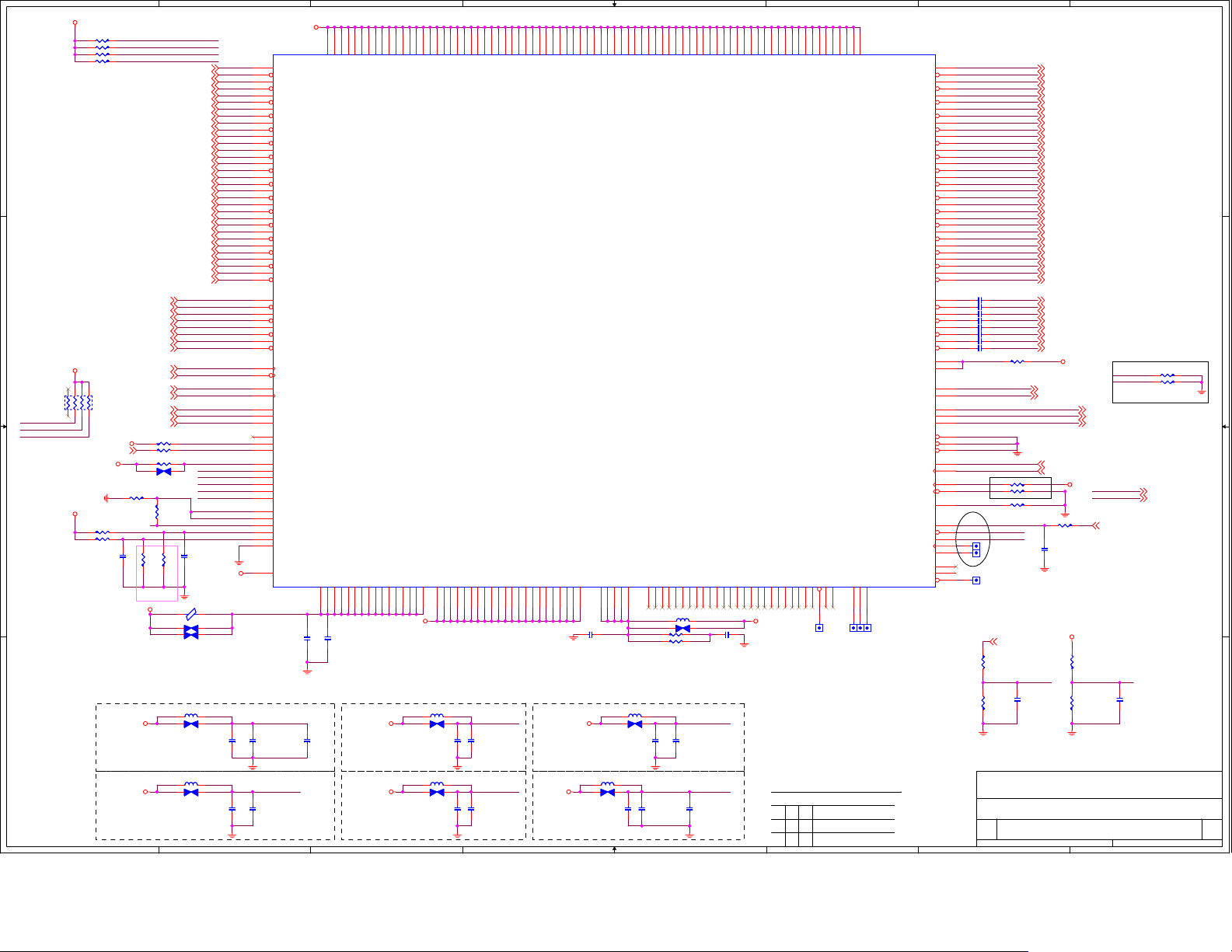

Block Diagram

Intel LGA775 Processor

FSB

PCI EXPRESS

X16

Connector

PCI EXPRESS X16

DDR2 667/800

DDRII

4 DDR II

DIMM

Modules

Bearlake

GMCH P31

DMI

UltraDMA

IDE Primary

33/66/100

A A

SATA 0~3

SATA

ICH7

USB

USB Port 0~7

ALC888

HD Codec

HD Audio Link

PCI

PCI

PCI EXPRESS X1

LPC Bus

LPC SIO

REALTEK

RTL8111C

SPI

SPI

Fintek

F71882

PCI Slot 1

PCI Slot 2

PCI Slot 3

PCI EXPRESS X1

PCI EXPRESS X1

EEPROM

TPM

Keyboard

Mouse

1

Floopy Parallel Serial

MSI

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-STAR INt'L CO., LTD.

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

MS-7392

MS-7392

MS-7392

235Thursday, April 24, 2008

235Thursday, April 24, 2008

235Thursday, April 24, 2008

of

of

of

2.2

2.2

2.2

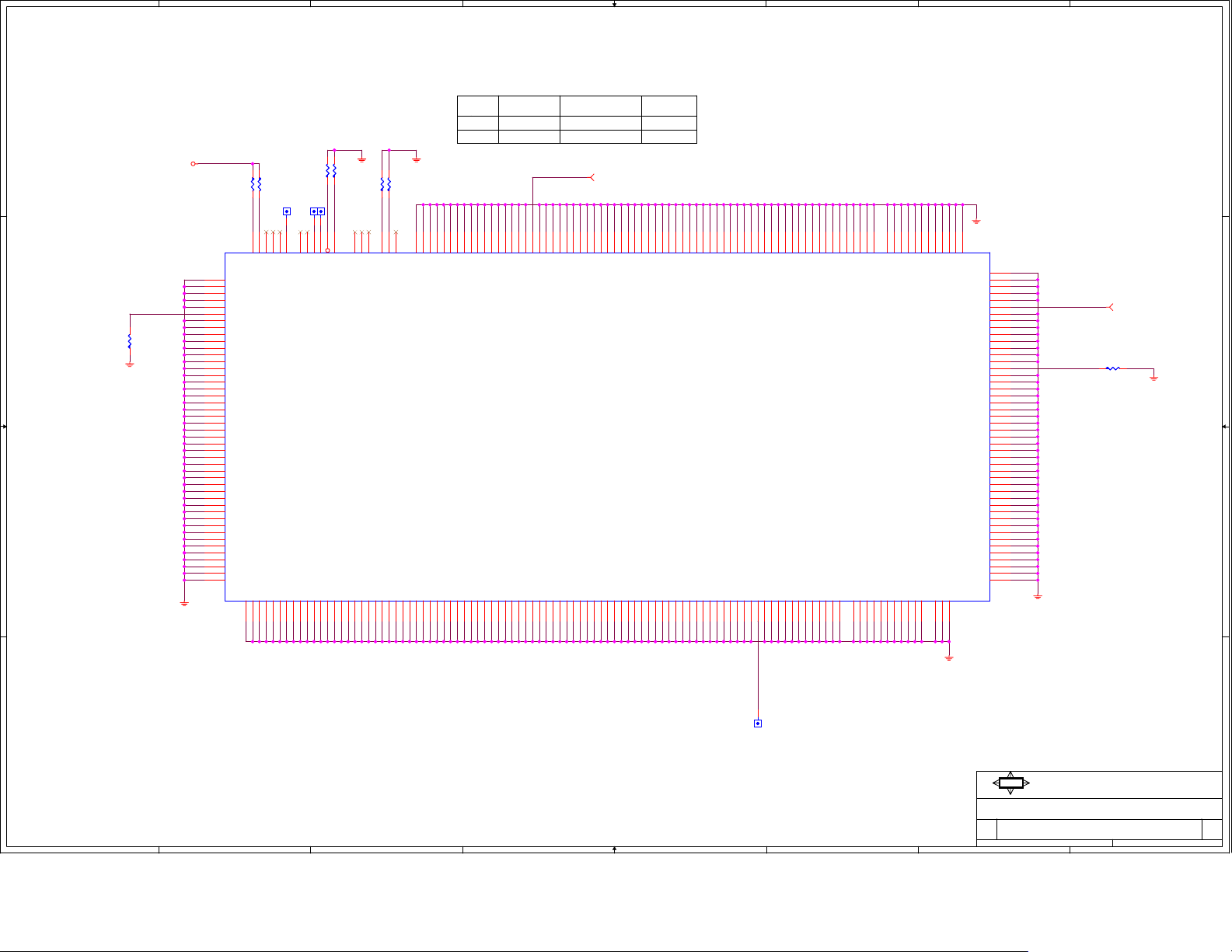

5

4

3

2

1

HCLK

LGA775

CLOCK MAP

D D

P31

MCHCLK

MCH

ICS

9LPRS906

ICHCLK

Clock

Generator

SATACLK

USB48MHz

ICH7

ICH14.318MHz

C C

SIO48MHz

LPC IO

AC_CLK

14.318MHz

B B

PCI_1394

33MHz

ALC888

VT6308

1394

CHANNEL A

CHANNEL A #

CHANNEL B

CHANNEL B#

ICS

9LPRS906

Clock

Generator

PCI_E1_100MHz

PCI_E2_100MHz

PCI_E3_100MHz

PCI_E1

PCI-Express X 16

PCI_E2

PCI-Express X 1

REALTEK

8111C

PCI1

A A

5

PCICLK[0..2]

33MHz

4

PCI2

PCI3

MSI

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

3

2

Date: Sheet

MICRO-STAR INt'L CO., LTD.

CLOCK MAP

CLOCK MAP

CLOCK MAP

MS-7392

MS-7392

MS-7392

335Thursday, April 24, 2008

335Thursday, April 24, 2008

335Thursday, April 24, 2008

of

of

1

of

2.2

2.2

2.2

5

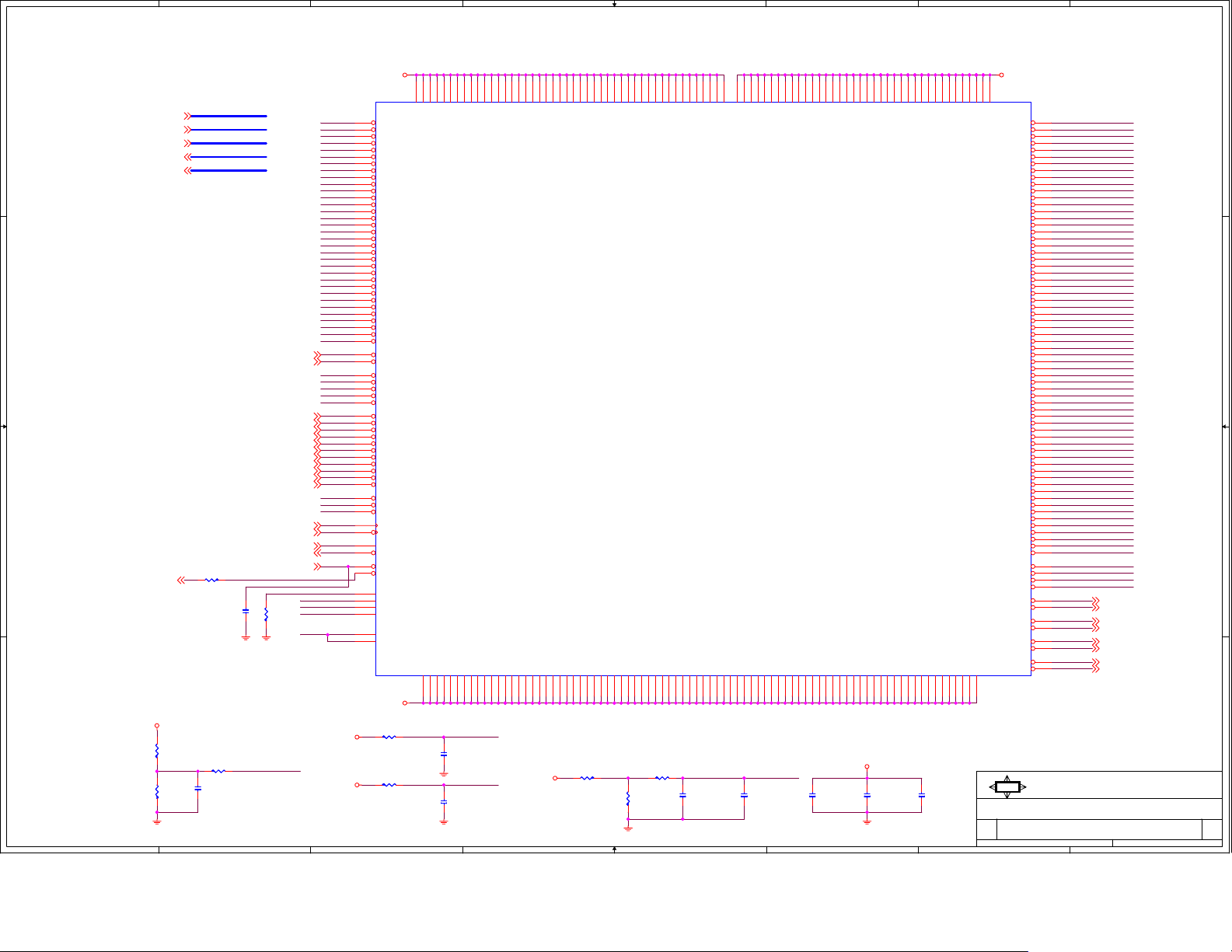

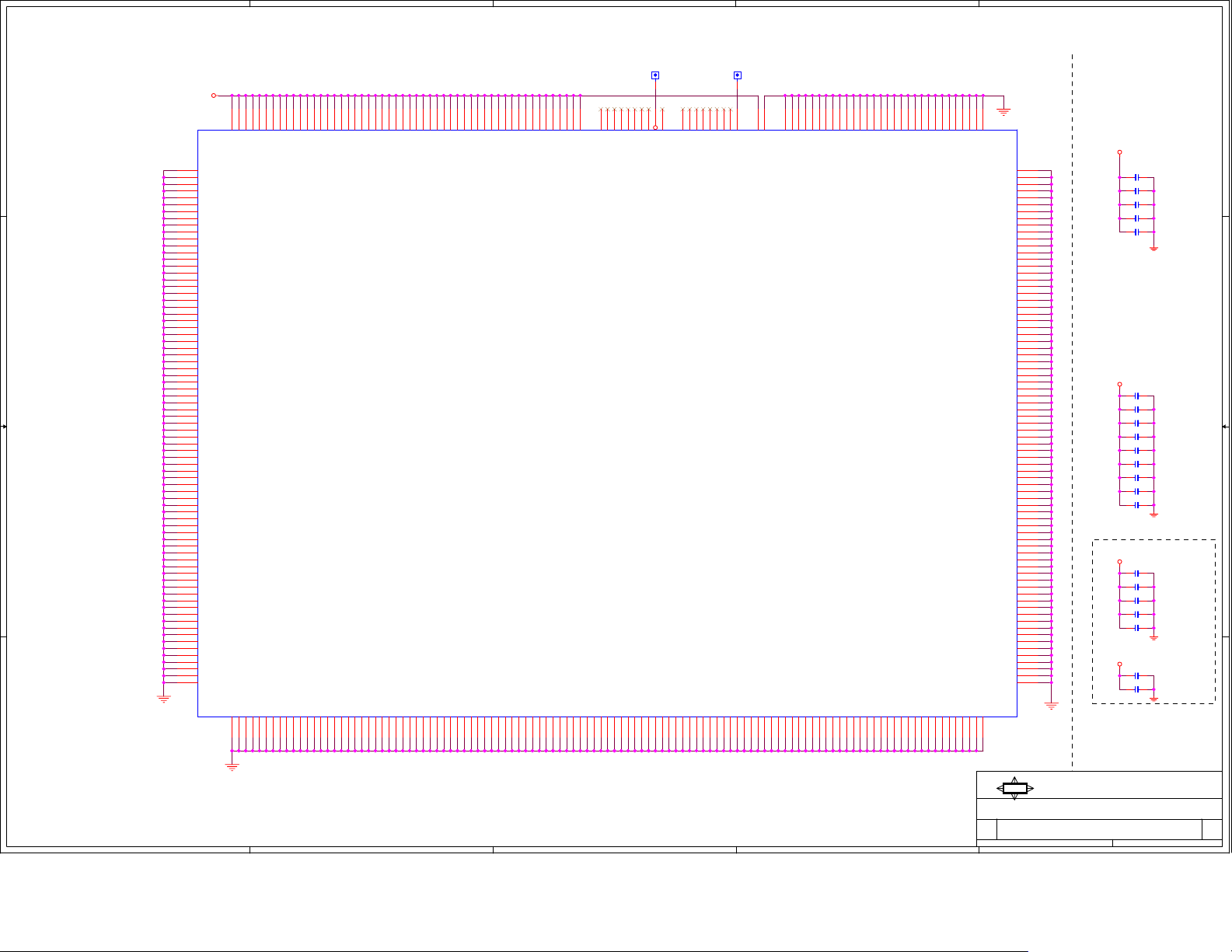

POWER MAP

4

3

2

1

D D

C C

ATX POWER

+12V +5V +3.3V +5VSB

25A 15A25.5A

2A

UPI

Controller

5VDIMM VCC_DDR

19A

937.5mA

6.5A

5A

12.1A

125A 5.3A

4+9.4+1.2 = 14.6A14.6*1.8/5/0.8 = 6.57A

UPI

8.58A

VR

15.3+1.31+6.2 = 22.81

B B

V_1P5_CORE

71882FG

1.2A

VTT_DDR

15.3A

PCI_E1(X16)

LGA775VRM 11.

P31

4A

13.8A + 1.5A

= 15.3A

9.4A

1.2A

1.71mA

PCI_E2*2(X1)

PCI1

MCH

0.9A

DDR2 X 4

PCI2

PCI3

6.2A

VR

1.31A

V_FSB_VTT

V_1P05_CORE

VR

6.2A

1.31A

0.7A

ICH7

14mA

VLAN25

REALTEK

VCC3_SB

1.5A

RTL8111C

VLAN12

RTL8111B

A A

MSI

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

5VDUAL

5

4.345A

4.345A

USB+PS2

4

3

2

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-STAR INt'L CO., LTD.

POWER MAP

POWER MAP

POWER MAP

MS-7392

MS-7392

MS-7392

1

2.2

2.2

2.2

of

of

of

435Thursday, April 24, 2008

435Thursday, April 24, 2008

435Thursday, April 24, 2008

8

7

6

5

4

3

2

1

CPU SIGNAL BLOCK

VID[0..7]30

CPU_GTLREF0

H_A#[3..35]

H_D#[0..63]

H_DBI#[0..3]

H_REQ#[0..4]

VID[0..7]

H_RS#[0..2]

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

CPU_GTLREF1

H_IERR#

H_FERR#

H_STPCLK#

H_INIT#

H_DBSY#

H_DRDY#

H_TRDY#

H_ADS#

H_LOCK#

H_BNR#

H_HIT#

H_HITM#

H_BPRI#

H_DEFER#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

CPU_TMPA

VTIN_GND

TRMTRIP#

H_PROCHOT#

H_IGNNE#

ICH_H_SMI#

H_A20M#

H_TESTHI13

H_TEST

CPU_BOOTSLT

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

H_PWRGD

H_CPURST#

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

A8

G11

D19

C20

F2

AB2

AB3

R3

M3

AD3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

AD1

AF1

AC1

AG1

AE1

AL1

AK1

M2

AE8

AL2

N2

P2

K3

L2

AH2

N5

AE6

C9

G10

D16

A20

Y1

V2

AA2

G29

H30

G30

N1

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

CPU1A

CPU1A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

H_D#53

H_A#8

H_A#10

H_A#7

H_A#6

H_A#5

H_A#4

H_A#31

H_A#30

H_A#28

H_A#29

H_A#26

H_A#24

H_A#25

H_A#27

H_A#23

H_A#22

H_A#21

H_A#19

H_A#17

H_A#18

H_A#20

H_A#15

H_A#16

H_A#14

H_A#11

H_A#12

A20#Y4A19#Y6A18#W6A17#

D33#

D32#

D31#

E15

G16

G15

H_D#30

H_D#31

H_D#32

H_A#13

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D30#

D29#

D28#

D27#

D26#

F15

F14

E13

G14

G13

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

D25#

D24#

F12

D13

H_D#23

H_D#24

H_A#35

H_A#34

H_A#33

H_A#32

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

AF4

AF5

AB4

AC5

AB5

AA5

AD6

AA4

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

A24#

A23#

A22#

A21#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

F21

F20

F18

A14

C14

H_D#52

E22

C15

D17

D20

D22

G22

G21

H_D#45

H_D#51

H_D#44

H_D#50

H_D#49

H_D#48

H_D#47

H_D#46

F17

E21

E19

E18

E16

G17

G18

H_D#43

H_D#42

H_D#41

H_D#40

H_D#39

H_D#38

H_D#37

H_D#33

H_D#34

H_D#35

H_D#36

H_A#9

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

F11

E10

D10

H_D#19

H_D#20

H_D#21

H_D#22

H_A#3

AJ3

AK3

AN6

AN5

VSS_SENSE

VCC_MB_REGULATION

D10#

B10

A11

H_D#9

H_D#10

ITP_CLK1

ITP_CLK0

VSS_MB_REGULATION

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A10

H_D#5

H_D#6

H_D#7

H_D#8

AM7

AM5

AL4

AK4

AL6

AM3

AL5

AM2

VID6#

VID5#

VID4#

VID3#

VID2#

VID1#

VID0#

VID_SELECT

RSVD#AM7

GTLREF0

GTLREF1

GTLREF_SEL

GTLREF2

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

RSVD#G6

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

B4

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_BLACK_TH-1

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_BLACK_TH-1

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

AN4

L5

AN3

AC2

DBR#

VCC_SENSE

D14#

D13#

D12#D8D11#

B12

D11

C12

C11

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_A#[3..35]8

D D

C C

VTT_OUT_LEFT

B B

A A

H_D#[0..63]8

H_DBI#[0..3]8

H_REQ#[0..4]8

H_RS#[0..2]8

H_IERR#6

H_FERR#6,12

H_STPCLK#12

H_INIT#12

H_DBSY#8

H_DRDY#8

H_TRDY#8

H_ADS#8

H_LOCK#8

H_BNR#8

H_HIT#8

H_HITM#8

H_BPRI#8

H_DEFER#8

CPU_TMPA16

VTIN_GND16

TRMTRIP#6,12

H_PROCHOT#6

H_IGNNE#12

ICH_H_SMI#12

H_A20M#12

R101 51R0402R101 51R0402

CPU_BSEL015,16

CPU_BSEL115

CPU_BSEL215

H_PWRGD6,12

H_CPURST#6,8

AN7

H1

H2

H29

E24

AG3

AF2

AG2

AD2

AJ1

AJ2

G5

J6

K6

M6

J5

K4

W2

P1

H5

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

A3

F5

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

VID7

VID6

VID5

VID4

VID3

VID2

VID1

VID0

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

PECI

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI_M

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

RSVD_AK6

RSVD_G6

CPUCLK#

CPUCLK

H_RS#2

H_RS#1

H_RS#0

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

H_ADSTB#1

H_ADSTB#0

H_DSTBP#3

H_DSTBP#2

H_DSTBP#1

H_DSTBP#0

H_DSTBN#3

H_DSTBN#2

H_DSTBN#1

H_DSTBN#0

H_NMI

H_INTR

VCC_VRM_SENSE

VSS_VRM_SENSE

VID_SELECT

CPU_GTLREF0

CPU_GTLREF1

RN13

RN13

8P4R-51R0402

8P4R-51R0402

1

3

5

7

R103 51R0402R103 51R0402

R322 51R0402R322 51R0402

R82 51R0402R82 51R0402

R327 51R0402R327 51R0402

R63 X_130R0402R63 X_130R0402

R99 X_51R0402R99 X_51R0402

CPUCLK# 15

CPUCLK 15

TP5TP5

TP4TP4

R83 X_49.9R1%0402R83 X_49.9R1%0402

R104 X_49.9R1%0402R104 X_49.9R1%0402

R105 49.9R1%0402R105 49.9R1%0402R68 X_51R0402R68 X_51R0402

R106 49.9R1%0402R106 49.9R1%0402

R85 49.9R1%0402R85 49.9R1%0402

R467 49.9R1%0402R467 49.9R1%0402

TP8TP8

TP6TP6

TP9TP9

TP7TP7

H_ADSTB#1 8

H_ADSTB#0 8

H_DSTBP#3 8

H_DSTBP#2 8

H_DSTBP#1 8

H_DSTBP#0 8

H_DSTBN#3 8

H_DSTBN#2 8

H_DSTBN#1 8

H_DSTBN#0 8

H_NMI 12

H_INTR 12

TP10TP10

TP14TP14

VCC_VRM_SENSE 30

VSS_VRM_SENSE 30

VID_SELECT 30

CPU_GTLREF0 6

CPU_GTLREF1 6

PECI 16

2

4

6

8

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_RIGHT

H_BR#0 6,8

VTT_OUT_LEFT

C64

C64

C0.1U16Y0402

C0.1U16Y0402

VTT_OUT_RIGHT

RN3

RN3

8P4R-680R

8P4R-680R

VID1

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

RN2

RN2

8P4R-680R

8P4R-680R

V_FSB_VTT

VID_SELECT

For HKB

kentsfield(Quad core)

RN6

RN6

H_TMS

2

H_TDI

4

H_BPM#2

6

H_TCK

8

8P4R-51R0402

8P4R-51R0402

RN5

RN5

H_TDO

2

H_BPM#4

4

H_BPM#3

6

H_TRST#

8

8P4R-51R0402

8P4R-51R0402

RN4

RN4

H_BPM#5

2

H_BPM#1

4

H_BPM#0

6

8

8P4R-51R0402

8P4R-51R0402

TP_CPU_G1

H_TEST

H_TESTHI8H_BPM#3

H_TESTHI9

H_TEST

TP_CPU_G1

TP_CPU_U1

VTT_OUT_RIGHT

1

3

5

7

VTT_OUT_RIGHT

1

3

5

7

VTT_OUT_RIGHT

1

3

5

7

VTT_OUT_LEFT

H_BPM#2

H_BPM#1

H_BPM#0

H_TESTHI_M

VID0

VID5

VID6

VID7

VID3

VID4

VID2

R108 X_51R0402R108 X_51R0402

R61 X_51R0402R61 X_51R0402

R76 X_0R0402R76 X_0R0402

R66 0R0402R66 0R0402

R59 X_0R0402R59 X_0R0402

R109 0R0402R109 0R0402

R110 0R0402R110 0R0402

PLACE BPM/TCK/TDI/TMS TERMINATION NEAR CPU

PLACE TDO TERMINATION NEAR CONNECTOR

C49

C49

C0.1U16Y0402

C0.1U16Y0402

R38

R38

680R0402

680R0402

R37

R37

X_62R0402

X_62R0402

C61

C61

C0.1U16Y0402

C0.1U16Y0402

C58

C58

C0.1U16Y0402

C0.1U16Y0402

TP_CPU_G1 7

TP_CPU_U1 7

MSI

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

Intel LGA775 CPU - Signals

Intel LGA775 CPU - Signals

Intel LGA775 CPU - Signals

MS-7392

MS-7392

MS-7392

535Tuesday, April 29, 2008

535Tuesday, April 29, 2008

535Tuesday, April 29, 2008

1

2.2

2.2

2.2

of

of

of

8

VCCP

AF22

AF21

CPU1B

AF19

AF18

AF15

AF14

AF12

AF11

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AE9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AD8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AC8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AB8

VCC

AA8

VCC

VCC

VCC

Y8

Y30

VCCP

D D

C C

VCCP

7

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y23

Y24

Y25

Y26

Y27

Y28

Y29

W24

W25

W26

W27

W28

W29

W30

U27

U28

U29

U30

W23

6

AH27

AH26

AH25

AH22

AH21

AH19

AH18

U26

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCT8VCC

VCC

VCC

T23

T24

T25

T26

T27

T28

T29

T30

U23

U24

U25

N24

N25

N26

N27

N28

N29

N30

5

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

K23

K24

K25

K26

K27

K28

K29

N23

M27

M28

M29

M30

K30

M23

M24

M25

M26

4

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

AN8

AN9

AN30

3

AN15

AN18

AN19

AN21

AN22

VCC

VCC

VCC

VCC

VCC

VCCA

VSSA

VCCPLL

VCC-IOPLL

VTTPWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

RSVD#F29

VCC

VCC

VCC

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_BLACK_TH-1

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_BLACK_TH-1

AN25

AN26

AN29

H_VCCA

A23

H_VSSA

B23

H_VCCPLL

D23

H_VCCA

C23

A25

VTT

A26

VTT

A27

VTT

A28

VTT

A29

VTT

A30

VTT

B25

VTT

B26

VTT

B27

VTT

B28

VTT

B29

VTT

B30

VTT

C25

VTT

C26

VTT

C27

VTT

C28

VTT

C29

VTT

C30

VTT

D25

VTT

D26

VTT

D27

VTT

D28

VTT

D29

VTT

D30

VTT

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

VTT_SEL

F27

F29

2

VCCA ------ 120mA

VCCIOPLL -- 100mA

V_FSB_VTT

VTT_OUT_RIGHT VTT_OUT_LEFT

VTT_SEL 29

V_FSB_VTT

C275

C275

C10U10Y0805

C10U10Y0805

C283

C283

X_C10U10Y0805

X_C10U10Y0805

C285

C285

X_C22U6.3X1206

X_C22U6.3X1206

CAPS FOR FSB GENERIC

1

GTLREF VOLTAGE SHOULD BE0.635*VTT

57.6ohm and 100ohm divider

B B

VTT_OUT_RIGHT

VTT_OUT_RIGHT

VTT_OUT_RIGHT

VTT_OUT_RIGHT

R221 115R1%0402-RHR221 115R1%0402-RH

R219

R219

200R1%0402

200R1%0402

R201

R201

200R1%0402

200R1%0402

R346 10R0402R346 10R0402R195 115R1%0402-RHR195 115R1%0402-RH

C90

C90

C1U16Y

C1U16Y

R112 10R0402R112 10R0402

C84

C84

C1U16Y

C1U16Y

C87

C87

X_C220P16X0402

X_C220P16X0402

C76

C76

X_C220P16X0402

X_C220P16X0402

CPU_GTLREF0 5

CPU_GTLREF1 5

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE NO SMALLER THAN 12MILS

V_FSB_VTT

V_1P5_CORE

CP8CP8

CP7CP7

L14

L14

X_10U100m_0805

X_10U100m_0805

21

C259

C259

C1U16Y

C1U16Y

C273

C273

X_C10U10Y0805

X_C10U10Y0805

C274

C274

X_C10U10Y0805

X_C10U10Y0805

C286

C286

X_C0.1U16Y0402

X_C0.1U16Y0402

H_VCCPLL

C276

C276

C10U10Y0805

C10U10Y0805

H_VCCA

H_VSSA

PLACE AT CPU END OF ROUTE

VTT_OUT_RIGHT

A A

VTT_OUT_LEFT

VTT_OUT_RIGHT

VTT_OUT_LEFT

R60 130R1%0402R60 130R1%0402

R353 62R0402R353 62R0402

R111 62R0402R111 62R0402

R226 X_100R/2R226 X_100R/2

R120 62R0402R120 62R0402

H_PROCHOT#

H_IERR#

H_CPURST#

H_PWRGD

H_BR#0

H_PROCHOT# 5

H_IERR# 5

H_CPURST# 5,8

H_PWRGD 5,12

H_BR#0 5,8

PLACE AT ICH END OF ROUTE

V_FSB_VTT

8

V_FSB_VTT TRMTRIP#

7

R330 62R0402R330 62R0402

R466 62R0402R466 62R0402

H_FERR#

TRMTRIP# 5,12

H_FERR# 5,12

6

5

4

VCC5_SB VTT_OUT_LEFT

R47

R47

1KR0402

1KR0402

VID_GD#29,30

R55 10KR0402R55 10KR0402

VTT_PWG SPEC :

High > 0.9V

R57

R57

1.25V VTT_PWRGOOD

680R0402

680R0402

VTT_PWG

Q17

Q17

C

C

B

B

E

E

2N3904S

2N3904S

3

Low < 0.3V

Trise < 150ns

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MSI

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

2

Intel LGA775 CPU - Power

Intel LGA775 CPU - Power

Intel LGA775 CPU - Power

MS-7392

MS-7392

MS-7392

635Tuesday, April 29, 2008

635Tuesday, April 29, 2008

635Tuesday, April 29, 2008

1

of

of

of

2.2

2.2

2.2

8

7

6

5

4

3

2

1

2005 Performance

D D

FMB platform 1

MSID1 0 0 0

2005 Mainstream/Value

FMB platform 2

2006 65W FMB

platform 3

MSID0 0 NC NC

VTT_OUT_RIGHT

C C

B B

TP_CPU_A24

R354

R354

X_0R0402

X_0R0402

VTT_OUT_RIGHT

R355

R355

X_49.9R1%0402

X_49.9R1%0402

CPU1C

CPU1C

A12

VSS

A15

VSS

A18

VSS

A2

VSS

A21

VSS

A24

VSS

A6

VSS

A9

VSS

AA23

VSS

AA24

VSS

AA25

VSS

AA26

VSS

AA27

VSS

AA28

VSS

AA29

VSS

AA3

VSS

AA30

VSS

AA6

VSS

AA7

VSS

AB1

VSS

AB23

VSS

AB24

VSS

AB25

VSS

AB26

VSS

AB27

VSS

AB28

VSS

AB29

VSS

AB30

VSS

AB7

VSS

AC3

VSS

AC6

VSS

AC7

VSS

AD4

VSS

AD7

VSS

AE10

VSS

AE13

VSS

AE16

VSS

AE17

VSS

AE2

VSS

AE20

VSS

AE24

VSS

AE25

VSS

AE26

VSS

AE27

VSS

AE28

VSS

AE29

H_COMP6

COMP6Y3COMP7

VSS

VSS

AE30

R347

R347

X_49.9R1%0402

X_49.9R1%0402

TP12TP12

H_COMP7

D14

AE3

AE4

D1

RSVD#D1

RSVD#D14

RSVD#AE4

VSS

VSS

VSS

VSS

AE5

AE7

AF10

AF13

E23

AF16

RSVD#E23

VSS

VSS

AF17

R350

R350

51R0402

51R0402

RSVD#E5E5RSVD#E6E6RSVD#E7

VSS

VSS

AF20

AF23

TP13TP13

E7

AF24

VSS

TP11TP11

F23

AF25

RSVD#F23

VSS

IMPSEL

F6

IMPSEL#

VSS

AF26

R352

R352

24.9R1%0402

24.9R1%0402

H_COMP8

B13

RSVD#B13

VSS

VSS

VSS

AF27

AF28

AF29

R348

R348

51R0402

51R0402

J3

N4

RSVD#J3

RSVD#N4

VSS

VSS

AF3

AF30

V27

V26

VSS

VSS

VSS

VSS

AH3

AH6

V25

V24

V23

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

AH7

AJ10

AJ13

AJ16

TP_CPU_U1

VSS

VSS

AJ17

AJ20

AJ23

R351

R351

51R0402

51R0402

MSID1

MSID0

P5

W1

AC4

MSID[1]V1MSID[0]

RSVD#P5

RSVD#AC4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF6

AF7

AG10

AG13

AG16

AG17

AG20

AG23

V30

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH1

AG7

AH10

AH13

AH16

AH17

AG24

V29

V28

VSSV3VSS

VSS

VSS

VSS

VSS

VSS

AH20

AH23

AH24

TP_CPU_U1 5

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

R30

R29

R28

R27

R26

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AJ24

AJ27

AJ28

AJ29

AJ30

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

L30

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL16

AL17

AL20

AL23

AL24

AL27

AL28

VSS

VSSL3VSS

VSS

AL3

TP_MPG_NOBOOT_N

L29

L28

L27

VSS

VSS

VSS

AL7

AM1

AM10

K2

L26

L25

L24

L23

K5

VSS

VSS

VSS

VSS

VSS

VSSK7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM17

AM20

AM23

AM24

AM27

AM28

AM4

AM13

AM16

H28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSB1VSS

AN1

AN2

AN10

AN13

AN16

AN17

AN20

B11

AN23

AN24

AN27

AN28

H14

VSS

H13

VSS

H12

VSS

H11

VSS

H10

VSS

G1

VSS

F7

VSS

F4

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

E8

VSS

E29

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E2

VSS

E17

VSS

E14

VSS

E11

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

C7

VSS

C4

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

B8

VSS

B5

VSS

B24

VSS

B20

VSS

B17

VSS

VSS

B14

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_BLACK_TH-1

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_BLACK_TH-1

TP_CPU_G1

TP_CPU_E29

TP_CPU_G1 5

R465 X_0R0402R465 X_0R0402

TP3TP3

A A

MSI

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

Intel LGA775 CPU - GND

Intel LGA775 CPU - GND

Intel LGA775 CPU - GND

MS-7392

MS-7392

MS-7392

2.2

2.2

2.2

of

735Tuesday, April 29, 2008

of

735Tuesday, April 29, 2008

of

735Tuesday, April 29, 2008

1

8

D D

C C

B B

A A

8

H_A#[3..35]5

H_REQ#[0..4]5

H_RS#[0..2]5

H_D#[0..63]5

H_DBI#[0..3]5

ICH_SYNC#13

V_FSB_VTT

HXSWING S/B 1/4*VTT +/- 2%

R462

R462

301R1%0402

301R1%0402

R340

R340

100R/2

100R/2

H_A#[3..35]

H_REQ#[0..4]

H_RS#[0..2]

H_D#[0..63]

H_DBI#[0..3]

R356 0R0402R356 0R0402

R342

R342

49.9R1%0402

49.9R1%0402

C376

C376

C0.01U/25X/2

C0.01U/25X/2

7

7

H_ADSTB#05

H_ADSTB#15

H_ADS#5

H_TRDY#5

H_DRDY#5

H_DEFER#5

H_HITM#5

H_HIT#5

H_LOCK#5

H_BR#05,6

H_BNR#5

H_BPRI#5

ICH_SYNC#_R

16.5R/1%/2

16.5R/1%/2

C375

X_C22P50N0402

C375

X_C22P50N0402

HXSWING

6

P29

P27

P26

P24

P23

N29

N26

N24

N23

M29

M24

VTT

VTT

VTT

VTT

VCC

VCC

VCC

VCC

AJ8

AJ7

AJ6

AJ5

HXSCOMP

C359

C359

X_C2.7P/25N/2

X_C2.7P/25N/2

HXSCOMPB

C542

C542

X_C2.7P/25N/2

X_C2.7P/25N/2

M23

VTT

VTT

VTT

VCC

VCC

VCC

AJ4

AJ3

AJ2

U7A

U7A

VTT

VTT

VTT

AJ12

VTT

VCC

VCC

VCC

AJ9

AJ11

AJ10

H_A#3

J42

L39

J40

L37

L36

K42

N32

N34

M38

N37

M36

R34

N35

N38

U37

N39

R37

P42

R39

V36

R38

U36

U33

R35

V33

V35

Y34

V42

V38

Y36

Y38

Y39

AA37

M34

U34

F40

L35

L38

G43

J37

W40

Y40

W41

T43

Y43

U42

V41

AA42

W42

G39

U40

U41

AA41

U39

R32

U32

AM17

C31

AM18

J13

D23

C25

D25

B25

D24

B24

V_1P25_CORE

R341

R341

49.9R1%0402

49.9R1%0402

R339

R339

49.9R1%0402

49.9R1%0402

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HA32#

HA33#

HA34#

HA35#

HADSTB0#

HADSTB1#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HADS#

HTRDY#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HRS0#

HRS1#

HRS2#

HCLKP

HCLKN

PWROK

HCPURST#

RSTIN#

ICH_SYNC#

HRCOMP

HSCOMP

HSCOMP#

HSWING

HDVREF

HACCVREF

6

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_DBSY#5

CK_H_MCH15

CK_H_MCH#15

CHIP_PWGD10,13,29

H_CPURST#5,6

R357

R357

PLTRST#10,12,16

H_RS#0

H_RS#1

H_RS#2

PLTRST#

HXRCOMP

HXSCOMP

HXSCOMPB

HXSWING

MCH_GTLREF

V_FSB_VTT

V_FSB_VTT

5

L24

L23

K24

K23

J24

J23

H24

H23

G26

G24

G23

F26

F24

F23

E29

E27

E26

E23

D29

D28

D27

C30

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AH4

AH2

AH1

AG9

AG8

AG7

AG6

AG5

AG4

AG3

AG2

AF13

AF12

AF11

AD24

AD22

AD20

AG13

AG12

AG11

AG10

AC25

4

C29

C27

B30

B29

B28

B27

A30

A28

R27

R26

R24

R23

AG19

AG18

AG17

AG15

AG14

AF26

AF25

AF24

AF22

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCY6VCC

VCC

VCC

Y24

Y22

Y20

Y13

V13

V12

AB20

AA25

AA23

AA21

AA19

AA13

AA3

AC6

AB24

AB22

AC23

AC21

AC19

AC13

V10

AF20

3

AF18

AF17

AF15

AF14

AE27

AE26

AE25

AE23

AE21

AE19

AE17

AD27

AD26

AD18

AD17

AD15

AD14

AC27

AC26

AC17

AC15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCV9VCC

VCC

VCCU9VCCU6VCCU3VCC

VCC

VCCN9VCCN8VCCN6VCCN3VCCL6VCCJ6VCCJ3VCCJ2VCCG2VCC

U13

U10

N12

N11

VCCF9VCCD4VCC

VCCC9VCC

F11

C13

2

V_1P25_COREV_FSB_VTT

AC14

AB27

AB26

AB18

AB17

AA27

AA26

VCC

VCC

VCC

VCC

VCC

VCC

VCC

HDINV0#

HDINV1#

HDINV2#

HDINV3#

HDSTBP0#

HDSTBN0#

HDSTBP1#

HDSTBN1#

HDSTBP2#

HDSTBN2#

HDSTBP3#

HDSTBN3#

VCC

VCC

VCC

VCC

P20

Y11

AG25

AG21

AG20

H_D#0

R40

HD0#

H_D#1

P41

HD1#

H_D#2

R41

HD2#

H_D#3

N40

HD3#

H_D#4

R42

HD4#

H_D#5

M39

HD5#

H_D#6

N41

HD6#

H_D#7

N42

HD7#

H_D#8

L41

HD8#

H_D#9

J39

HD9#

H_D#10

L42

HD10#

H_D#11

J41

HD11#

H_D#12

K41

HD12#

H_D#13

G40

HD13#

H_D#14

F41

HD14#

H_D#15

F42

HD15#

H_D#16

C42

HD16#

H_D#17

D41

HD17#

H_D#18

F38

HD18#

H_D#19

G37

HD19#

H_D#20

E42

HD20#

H_D#21

E39

HD21#

H_D#22

E37

HD22#

H_D#23

C39

HD23#

H_D#24

B39

HD24#

H_D#25

G33

HD25#

H_D#26

A37

HD26#

H_D#27

F33

HD27#

H_D#28

E35

HD28#

H_D#29

K32

HD29#

H_D#30

H32

HD30#

H_D#31

B34

HD31#

H_D#32

J31

HD32#

H_D#33

F32

HD33#

H_D#34

M31

HD34#

H_D#35

E31

HD35#

H_D#36

K31

HD36#

H_D#37

G31

HD37#

H_D#38

K29

HD38#

H_D#39

F31

HD39#

H_D#40

J29

HD40#

H_D#41

F29

HD41#

H_D#42

L27

HD42#

H_D#43

K27

HD43#

H_D#44

H26

HD44#

H_D#45

L26

HD45#

H_D#46

J26

HD46#

H_D#47

M26

HD47#

H_D#48

C33

HD48#

H_D#49

C35

HD49#

H_D#50

E41

HD50#

H_D#51

B41

HD51#

H_D#52

D42

HD52#

H_D#53

C40

HD53#

H_D#54

D35

HD54#

H_D#55

B40

HD55#

H_D#56

C38

HD56#

H_D#57

D37

HD57#

H_D#58

B33

HD58#

H_D#59

D33

HD59#

H_D#60

C34

HD60#

H_D#61

B35

HD61#

H_D#62

A32

HD62#

H_D#63

D32

HD63#

INTEL-NR88BOBVBVA[G31]-A1-RH

INTEL-NR88BOBVBVA[G31]-A1-RH

H_DBI#0

M40

H_DBI#1

J33

H_DBI#2

G29

H_DBI#3

E33

L40

M43

G35

H33

G27

H27

B38

D38

H_DSTBP#0 5

H_DSTBN#0 5

H_DSTBP#1 5

H_DSTBN#1 5

H_DSTBP#2 5

H_DSTBN#2 5

H_DSTBP#3 5

H_DSTBN#3 5

1

GTLREF VOLTAGE SHOULD BE 0.67*VTT=0.804V

C374

C374

C0.1U/16Y/2

C0.1U/16Y/2

V_FSB_VTT

3

C378

C378

C0.1U/16Y/2

C0.1U/16Y/2

C350

C350

C0.1U/16Y/2

C0.1U/16Y/2

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MSI

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

2

Intel Bearlake G31 - CPU Signals

Intel Bearlake G31 - CPU Signals

Intel Bearlake G31 - CPU Signals

MS-7392

MS-7392

MS-7392

of

835Friday, May 16, 2008

of

835Friday, May 16, 2008

of

835Friday, May 16, 2008

1

2.2

2.2

2.2

V_FSB_VTT

5

R464

R464

100R/2

100R/2

R463

R463

51R0402

51R0402

R345

R345

200R1%0402

200R1%0402

C355

C355

C0.1U/16Y/2

C0.1U/16Y/2

4

MCH_GTLREF

C373

C373

X_C220P16X0402

X_C220P16X0402

8

7

6

5

4

3

2

1

DATA_B[0..63]20

DATA_A[0..63]19

D D

C C

B B

A A

MAA_A[0..14]19,21

VCC_DDR

8

DATA_B[0..63]

DATA_A[0..63]

MAA_A[0..14]

SCS_A#019,21

SCS_A#119,21

RAS_A#19,21

CAS_A#19,21

WE_A#19,21

ODT_A019,21

ODT_A119,21

SBS_A019,21

SBS_A119,21

SBS_A219,21

DQS_A019

DQS_A#019

DQS_A119

DQS_A#119

DQS_A219

DQS_A#219

DQS_A319

DQS_A#319

DQS_A419

DQS_A#419

DQS_A519

DQS_A#519

DQS_A619

DQS_A#619

DQS_A719

DQS_A#719

P_DDR0_A19

N_DDR0_A19

P_DDR1_A19

N_DDR1_A19

P_DDR2_A19

N_DDR2_A19

R461 20R1%0402R461 20R1%0402

R334 20R1%0402R334 20R1%0402

R336 20R1%0402R336 20R1%0402

R358 20R1%0402R358 20R1%0402

C372

C372

C0.1U16Y0402

C0.1U16Y0402

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

SRCOMP0

SRCOMP1

SRCOMP2

SRCOMP3

7

DQM_B[0..7]20

DQM_A[0..7]19

MAA_B[0..14]20,21

AW35

BA35

BA34

BB38

BB33

AY35

BB34

BA31

BB25

BA26

BA25

AY25

BA23

AY24

AY23

BB23

BA22

AY33

BB22

AW21

AY38

BA21

AY37

BA38

BB35

BA39

BA33

AW32

BB21

AT20

AU18

AR41

AR40

AL41

AL40

AG42

AG41

AC42

AC41

AU31

AR31

AP27

AN27

AV33

AW33

AP29

AP31

AM26

AM27

AT33

AU33

BB40

BA40

DQM_B[0..7]

DQM_A[0..7]

MAA_B[0..14]

DATA_B1

DATA_B0

DATA_B2

AN7

AN8

U7B

U7B

SCS_A0#

SCS_A1#

Reserved18

Reserved24

SRAS_A#

SCAS_A#

SWE_A#

SMA_A0

SMA_A1

SMA_A2

SMA_A3

SMA_A4

SMA_A5

SMA_A6

SMA_A7

SMA_A8

SMA_A9

SMA_A10

SMA_A11

SMA_A12

SMA_A13

SMA_A14

SODT_A0

SODT_A1

Reserved23

Reserved19

SBS_A0

SBS_A1

SBS_A2

AU4

SDQS_A0

AR3

SDQS_A0#

BB3

SDQS_A1

BA4

SDQS_A1#

BB9

SDQS_A2

BA9

SDQS_A2#

SDQS_A3

SDQS_A3#

SDQS_A4

SDQS_A4#

SDQS_A5

SDQS_A5#

SDQS_A6

SDQS_A6#

SDQS_A7

SDQS_A7#

SCLK_A0

SCLK_A0#

SCLK_A1

SCLK_A1#

SCLK_A2

SCLK_A2#

Reserved3

Reserved4

Reserved1

Reserved2

Reserved5

Reserved6

AN2

SRCOMP0

AN3

SRCOMP1

SRCOMP2

SRCOMP3

INTEL-NR88BOBVBVA[G31]-A1-RH

INTEL-NR88BOBVBVA[G31]-A1-RH

AW5

SDQ_B0

SDQ_B1

SDQ_B2

SDQ_A0

SDQ_A1

SDQ_A2

AV3

AR5

AR4

DATA_A0

DATA_A2

DATA_A1

SCKE_B0

SCKE_B1

DQM_B0

DQM_B1

DQM_B3

DQM_B4

AY12

SCKE_B0

SCKE_A0

BC20

AW12

BB11

SCKE_B1

Reserved20

SCKE_A1

Reserved13

AY20

AY21

SCKE_A1

SCKE_A0

BA11

BA19

Reserved16

Reserved17

DQM_B2

AR7

AW9

AW13

AP23

AU37

SDM_B0

SDM_B1

SDM_B2

SDM_B3

SDM_A0

SDM_A1

SDM_A2

SDM_A3

BA2

AY9

AR2

AN18

AU43

DQM_A1

DQM_A2

DQM_A0

DQM_A3

DQM_A4

3

DATA_B3

DATA_B9

DATA_B8

DATA_B7

DATA_B4

DATA_B10

DATA_B6

DATA_B5

DATA_B11

DATA_B13

DATA_B12

DATA_B16

DATA_B15

DATA_B14

DATA_B18

DATA_B19

DATA_B21

DATA_B17

DATA_B20

DATA_B22

AW7

AN5

AN6

AN9

AU7

AT11

AU11

AP13

AR13

AR11

AU9

AV12

AU12

AU15

AV13

AU17

AT17

AU13

AM13

SDQ_B3

SDQ_B4

SDQ_B5

SDQ_B6

SDQ_B7

SDQ_B8

SDQ_B9

SDQ_B10

SDQ_B11

SDQ_B12

SDQ_B13

SDQ_B14

SDQ_B15

SDQ_B16

SDQ_B17

SDQ_B18

SDQ_B19

SDQ_B20

SDQ_B21

SDQ_A3

SDQ_A4

SDQ_A5

SDQ_A6

SDQ_A7

SDQ_A8

SDQ_A9

SDQ_A10

SDQ_A11

SDQ_A12

SDQ_A13

SDQ_A14

SDQ_A15

SDQ_A16

SDQ_A17

SDQ_A18

SDQ_A19

SDQ_A20

SDQ_A21

AV2

AP3

AP2

AV4

AY2

AY3

BB5

AY6

BA5

BB4

AY7

BB6

AU1

AW2

AW3

DATA_A3

DATA_A4

DATA_A8

DATA_A9

DATA_A6

DATA_A7

DATA_A5

DATA_A11

DATA_A12

DATA_A10

DATA_A14

DATA_A13

6

BA6

BC7

AY11

AW11

DATA_A19

DATA_A21

DATA_A16

DATA_A22

DATA_A18

DATA_A15

DATA_A20

DATA_A17

AV15

SDQ_B22

SDQ_A22

BA10

DATA_B23

AW17

BB10

DATA_A23

DATA_B24

AV24

SDQ_B23

SDQ_A23

AT18

DATA_A24

DATA_B25

AT23

SDQ_B24

SDQ_B25

SDQ_A24

SDQ_A25

AR18

DATA_A25

DATA_B26

AT26

AU21

DATA_A26

DATA_B27

AP26

SDQ_B26

SDQ_B27

SDQ_A26

SDQ_A27

AT21

DATA_A27

DATA_B28

AU23

AP17

DATA_A28

DATA_B29

AW23

SDQ_B28

SDQ_A28

AN17

DATA_A29

5

DATA_B30

AR24

SDQ_B29

SDQ_B30

SDQ_A29

SDQ_A30

AP20

DATA_A30

DATA_B31

AN26

AV20

DATA_A31

DATA_B32

AW37

SDQ_B31

SDQ_B32

SDQ_A31

SDQ_A32

AV42

DATA_A32

DATA_B33

AV38

AU40

DATA_A33

DATA_B34

AN36

SDQ_B33

SDQ_A33

AP42

DATA_A34

DATA_B35

AN37

SDQ_B34

SDQ_B35

SDQ_A34

SDQ_A35

AN39

DATA_A35

DATA_B36

AU35

AV40

DATA_A36

DATA_B37

AR35

SDQ_B36

SDQ_B37

SDQ_A36

SDQ_A37

AV41

DATA_A37

DATA_B38

AN35

AR42

DATA_A38

DATA_B39

AR37

SDQ_B38

SDQ_B39

SDQ_A38

SDQ_A39

AP41

DATA_A39

DATA_B40

AM35

AN41

DATA_A40

DATA_B41

AM38

SDQ_B40

SDQ_B41

SDQ_A40

SDQ_A41

AM39

DATA_A41

DATA_B42

AJ34

AK42

DATA_A42

DATA_B43

AL38

SDQ_B42

SDQ_B43

SDQ_A42

SDQ_A43

AK41

DATA_A43

DATA_B44

AR39

AN40

DATA_A44

DATA_B45

AM34

SDQ_B44

SDQ_B45

SDQ_A44

SDQ_A45

AN42

DATA_A45

DATA_B46

AL37

AL42

DATA_A46

DATA_B47

AL32

SDQ_B46

SDQ_B47

SDQ_A46

SDQ_A47

AL39

DATA_A47

DATA_B48

AG38

AJ40

DATA_A48

DATA_B49

AJ38

SDQ_B48

SDQ_A48

AH43

DATA_A49

DATA_B50

AF35

SDQ_B49

SDQ_B50

SDQ_A49

SDQ_A50

AF39

DATA_A50

DATA_B51

AF33

AE40

DATA_A51

4

DATA_B52

AJ37

SDQ_B51

SDQ_B52

SDQ_A51

SDQ_A52

AJ42

DATA_A52

DATA_B53

DATA_A53

AJ35

SDQ_B53

SDQ_A53

AJ41

DATA_B54

AG33

AF41

DATA_A54

DATA_B55

AF34

SDQ_B54

SDQ_B55

SDQ_A54

SDQ_A55

AF42

DATA_A55

DATA_B56

DATA_A56

DATA_B62

DATA_B57

DATA_B63

DATA_B60

DATA_B59

DATA_B61

DATA_B58

AD36

AC33

AA34

AA36

AD34

AF38

AC34

AA33

SDQ_B56

SDQ_B57

SDQ_B58

SDQ_B59

SDQ_B60

SDQ_B61

SDQ_B62

SDQ_B63

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_A62

SDQ_A63

AB41

AA40

AE42

AE41

AD40

PLACE 0.1UF CAP CLOSE TO MCH

AB42

AD43

AC39

DATA_A63

DATA_A62

DATA_A61

DATA_A59

DATA_A58

DATA_A60

DATA_A57

SCKE_B0 20,21

SCKE_B1 20,21

DQM_B6

DQM_B5

DQM_B7

AM37

AG39

AD38

SDM_B4

SDM_B5

SDM_B6

SDM_B7

SMRCOMPVOL

SMRCOMPVOH

SDM_A4

SDM_A5

SDM_A6

SDM_A7

AC40

AG40

AM43

DQM_A5

DQM_A6

DQM_A7

SCKE_A1 19,21

SCKE_A0 19,21

SCS_B0#

SCS_B1#

Reserved14

Reserved15

SRAS_B#

SCAS_B#

SWE_B#

SMA_B0

SMA_B1

SMA_B2

SMA_B3

SMA_B4

SMA_B5

SMA_B6

SMA_B7

SMA_B8

SMA_B9

SMA_B10

SMA_B11

SMA_B12

SMA_B13

SMA_B14

SODT_B0

SODT_B1

Reserved21

Reserved22

SBS_B0

SBS_B1

SBS_B2

SDQS_B0

SDQS_B0#

SDQS_B1

SDQS_B1#

SDQS_B2

SDQS_B2#

SDQS_B3

SDQS_B3#

SDQS_B4

SDQS_B4#

SDQS_B5

SDQS_B5#

SDQS_B6

SDQS_B6#

SDQS_B7

SDQS_B7#

SCLK_B0

SCLK_B0#

SCLK_B1

SCLK_B1#

SCLK_B2

SCLK_B2#

Reserved7

Reserved8

Reserved9

Reserved10

Reserved11

Reserved12

SVREF

BB27

BB30

AY27

AY31

AW26

AW29

BA27

MAA_B0

BB17

MAA_B1

AY17

MAA_B2

BA17

MAA_B3

BC16

MAA_B4

AW15

MAA_B5

BA15

MAA_B6

BB15

MAA_B7

BA14

MAA_B8

AY15

MAA_B9

BB14

MAA_B10

AW18

MAA_B11

BB13

MAA_B12

BA13

MAA_B13

AY29

MAA_B14

AY13

BA29

BA30

BB29

BB31

AY19

BA18

BC12

DQS_B0

AV6

DQS_B#0

AU5

DQS_B1

AR12

DQS_B#1

AP12

DQS_B2

AP15

DQS_B#2

AR15

DQS_B3

AT24

DQS_B#3

AU26

DQS_B4

AW39

DQS_B#4

AU39

DQS_B5

AL35

DQS_B#5

AL34

DQS_B6

AG35

DQS_B#6

AG36

DQS_B7

AC36

DQS_B#7

AC37

P_DDR0_B

AV31

N_DDR0_B

AW31

P_DDR1_B

AU27

N_DDR1_B

AT27

P_DDR2_B

AV32

N_DDR2_B

AT32

AU29

AR29

AV29

AW27

AN33

AP32

MCH_VREF_A

AM6

DDR_RCOMPVOL

AM8

DDR_RCOMPVOH

AM10

DDR_RCOMPVOH = 0.8 * VCC_DDR

DDR_RCOMPVOL = 0.2 * VCC_DDR

SCS_B#0 20,21

SCS_B#1 20,21

RAS_B# 20,21

CAS_B# 20,21

WE_B# 20,21

ODT_B0 20,21

ODT_B1 20,21

SBS_B0 20,21

SBS_B1 20,21

SBS_B2 20,21

DQS_B0 20

DQS_B#0 20

DQS_B1 20

DQS_B#1 20

DQS_B2 20

DQS_B#2 20

DQS_B3 20

DQS_B#3 20

DQS_B4 20

DQS_B#4 20

DQS_B5 20

DQS_B#5 20

DQS_B6 20

DQS_B#6 20

DQS_B7 20

DQS_B#7 20

P_DDR0_B 20

N_DDR0_B 20

P_DDR1_B 20

N_DDR1_B 20

P_DDR2_B 20

N_DDR2_B 20

C0.1U16Y0402

C538

C538

C0.1U16Y0402

C0.1U16Y0402

MS-7392

MS-7392

MS-7392

C0.1U16Y0402

VCC_DDR

C371 C0.01U25X0402C371 C0.01U25X0402

R335 1KR1%0402R335 1KR1%0402

R361

R361

3.01KR1%0402

3.01KR1%0402

R337 1KR1%0402R337 1KR1%0402

C370

C370

C0.01U25X0402

C0.01U25X0402

MSI

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

Intel Bearlake G31 - CPU Signals

Intel Bearlake G31 - CPU Signals

Intel Bearlake G31 - CPU Signals

2

C380

C380

R359

R359

1KR1%0402

1KR1%0402

R360

1KR1%0402

R360

1KR1%0402

of

935Friday, May 16, 2008

of

935Friday, May 16, 2008

of

935Friday, May 16, 2008

1

VCC_DDR

C540

X_C0.1U16Y0402

C540

X_C0.1U16Y0402

2.2

2.2

2.2

8

V_1P25_CORE

Close to MCH A.S.A.P

R369 5.1KR0402R369 5.1KR0402

R367 5.1KR0402R367 5.1KR0402

R371 5.1KR0402R371 5.1KR0402

R372 5.1KR0402R372 5.1KR0402

D D

DMI_MCH_IT_MR_0_DP12

DMI_MCH_IT_MR_0_DN12

DMI_MCH_IT_MR_1_DP12

C C

RN28

RN28

470/4/8P4R

470/4/8P4R

H_BSL0

H_BSL1

H_BSL2

B B

DMI_MCH_IT_MR_1_DN12

DMI_MCH_IT_MR_2_DP12

DMI_MCH_IT_MR_2_DN12

DMI_MCH_IT_MR_3_DP12

DMI_MCH_IT_MR_3_DN12

V_FSB_VTT

135

7

246

8

V_1P25_CORE

EXP_PRSNT_N22

V_1P25_CORE

Route solder side

4mils width

V15SFR

R214 X_0R0402R214 X_0R0402

R212 X_0R0402R212 X_0R0402

I = 225mA

A A

I = 90.6mA I = 0.36mA

8

CK_PE_100M_MCH15

CK_PE_100M_MCH#15

SDVO_CTRL_DATA22

SDVO_CTRL_CLK22

R531 0R0402R531 0R0402

X_C0.1U16Y0402

X_C0.1U16Y0402

Stuff 0-ohm for P31

V_1P25_CORE

V_1P25_CORE

V_1P25_CORE

DMI_MCH_IT_MR_0_DP

DMI_MCH_IT_MR_1_DP

DMI_MCH_IT_MR_2_DP

DMI_MCH_IT_MR_3_DP

EXP_A_RXP_022

EXP_A_RXN_022

EXP_A_RXP_122

EXP_A_RXN_122

EXP_A_RXP_222

EXP_A_RXN_222

EXP_A_RXP_322

EXP_A_RXN_322

EXP_A_RXP_422

EXP_A_RXN_422

EXP_A_RXP_522

EXP_A_RXN_522

EXP_A_RXP_622

EXP_A_RXN_622

EXP_A_RXP_722

EXP_A_RXN_722

EXP_A_RXP_822

EXP_A_RXN_822

EXP_A_RXP_922

EXP_A_RXN_922

EXP_A_RXP_1022

EXP_A_RXN_1022

EXP_A_RXP_1122

EXP_A_RXN_1122

EXP_A_RXP_1222

EXP_A_RXN_1222

EXP_A_RXP_1322

EXP_A_RXN_1322

EXP_A_RXP_1422

EXP_A_RXN_1422

EXP_A_RXP_1522

EXP_A_RXN_1522

H_BSL015,16

H_BSL115,16

H_BSL215,16

R458 1KR0402R458 1KR0402

R316 0R0402R316 0R0402

R475 X_0R0402R475 X_0R0402

CP28CP28

VCCA_DAC VCCA_GPLL

R549

R549

X_0R0402

X_0R0402

VCCA_EXP

C361

C361

R215

0R0402

R215

0R0402

R216

0R0402

R216

0R0402

L29 X_80L4_30_1206L29 X_80L4_30_1206

CP17CP17

L12 X_0.1U50mL12 X_0.1U50m

CP14CP14

L16 X_0.1U50mL16 X_0.1U50m

CP19CP19

DMI_MCH_IT_MR_0_DP

DMI_MCH_IT_MR_0_DN

DMI_MCH_IT_MR_1_DP

DMI_MCH_IT_MR_1_DN

DMI_MCH_IT_MR_2_DP

DMI_MCH_IT_MR_2_DN

DMI_MCH_IT_MR_3_DP

DMI_MCH_IT_MR_3_DN

SDVO_CTRL_DATA

SDVO_CTRL_CLK

H_BSL0

H_BSL1

H_BSL2

X_C4.7U10Y0805

X_C4.7U10Y0805

EXP_SLR

EXP_EN

VCC_CL_PLL

VCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCD_CRT

VCCDQ_CRT

C387

C387

VCC3

21

C532

C532

X_C0.22U16X

X_C0.22U16X

21

C388

C388

C10U10Y0805

C10U10Y0805

7

V_1P25_CORE

U7C

U7C

F15

EXP_RXP0

G15

EXP_RXN0

K15

EXP_RXP1

J15

EXP_RXN1

F12

EXP_RXP2

E12

EXP_RXN2

J12

EXP_RXP3

H12

EXP_RXN3

J11

EXP_RXP4

H11

EXP_RXN4

F7

EXP_RXP5

E7

EXP_RXN5

E5

EXP_RXP6

F6

EXP_RXN6

C2

EXP_RXP7

D2

EXP_RXN7

G6

EXP_RXP8

G5

EXP_RXN8

L9

EXP_RXP9

L8

EXP_RXN9

M8

EXP_RXP10

M9

EXP_RXN10

M4

EXP_RXP11

L4

EXP_RXN11

M5

EXP_RXP12

M6

EXP_RXN12

R9

EXP_RXP13

R10

EXP_RXN13

T4

EXP_RXP14

R4

EXP_RXN14

R6

EXP_RXP15

R7

EXP_RXN15

W2

DMI_RXP0

V1

DMI_RXN0

Y8

DMI_RXP1

Y9

DMI_RXN1

AA7

DMI_RXP2

AA6

DMI_RXN2

AB3

DMI_RXP3

AA4

DMI_RXN3

B12

GCLKP

B13

GCLKN

G17

SDVO_CTRLDATA

E17

SDVO_CTRLCLK

G20

BSEL0

J20

BSEL1

J18

BSEL2

G18

RESERVED53

E18

EXP_SLR

J17

EXP_EN

Y32

VCC2

C23

VCCA_HPLL

A24

VCCA_MPLL

A22

VCCA_DPLLA

C22

VCCA_DPLLB

B15

VCCA_EXPPLL

C17

VCCA_DAC

B16

VCCA_DAC

A16

VCCA_EXP

C21

VCCD_CRT

B21

VCCDQ_CRT

D16

VSS

B17

VCC3_3

INTEL-NR88BOBVBVA[G31]-A1-RH

INTEL-NR88BOBVBVA[G31]-A1-RH

V_1P25_EXP

VCCA_MPLL

C386

C386

C10U10Y0805

C10U10Y0805

VCCA_DPLLB

C395

C395

C0.1U16Y0402

C0.1U16Y0402

7

AD11

C339

C10U10Y0805

C339

C10U10Y0805

C384

C0.1U16Y0402

C384

C0.1U16Y0402

AL26

AL24

AL23

VCC2

VCC2

VCC2

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

AD9

AD8

AD10

C360

C0.1U16Y0402

C360

C0.1U16Y0402

V_1P25_CORE

I = 67.9mA

V_1P25_CORE

6

AL21

AL20

AL18

AL17

AL15

AK30

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

AD7

AD6

AD5

AD4

AD2

AD1

VCC_DDR

I = 90.6mA

6

AK29

AK27

AJ31

AG31

AF31

AD32

AC32

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXP

AE4

AE3

AE2

AC4

AC3

AC2

L15 X_0.1U50mL15 X_0.1U50m

CP13CP13

C356

C356

C10U10Y0805

C10U10Y0805

L13 X_0.1U50mL13 X_0.1U50m

CP12CP12

C357

C357

C10U10Y0805

C10U10Y0805

AA32

BC39

5

AJ30

AJ29

AJ27

AG30

AG29

AG27

AG26

AF30

AF29

AF27

AD30

AD29

AC30

AC29

AL12

AL11

AL10

AL9

AL8

AL7

AL6

AL5

AL4

AL3

AL2

AK26

AK24

AK23

AK21

AK20

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCC_SMCLK

VCC_SMCLK

VCC_SMCLK

VCC_SMCLK

VCC_SMCLK

BB39

BB37

BB32

BB28

BB26

BB24

BB20

BB18

BB16

BB12

AY32

AV26

AV18

BB41

BA42

AY42

BB42

BC34

BC30

BC26

BC22

BC18

21

21

BC14

VCCA_DPLLA

C349

C349

C0.1U16Y0402

C0.1U16Y0402

VCCA_HPLL

C354

C354

C0.1U16Y0402

C0.1U16Y0402

AW24

AW20

I = 71.6mA

V_1P25_CORE

VCC3

5

C340 C1U16YC340 C1U16Y

L28 X_0.1U50mL28 X_0.1U50m

CP15CP15

BA43

V_CKDDR

L27 X_0.1U50mL27 X_0.1U50m

CP16CP16

C368

C368

C10U10Y0805

C10U10Y0805

21

C369

C369

C10U10Y0805

C10U10Y0805

4

AK18

AK17

AK15

AK3

AK2

AK1

AJ13

AD31

AC31

AA31

Y31

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

RESERVED25

RESERVED26

RESERVED27

RESERVED28

RESERVED29

RESERVED30

RESERVED31

RESERVED32

RESERVED33

RESERVED34

RESERVED35

H18

BB2

BB19

AN21

L10 X_10U100m_0805L10 X_10U100m_0805

CP11CP11

R459 X_1R1%R459 X_1R1%CP18CP18

R308 X_1R1%R308 X_1R1%

21

VCCA_EXP

C367

C367

C0.1U16Y0402

C0.1U16Y0402

AN32

AG32

AM31

AW42

21

VCCA_GPLL

C366

C366

C0.1U16Y0402

C0.1U16Y0402

C365

C365

C0.01U25X0402

C0.01U25X0402

4

AL31

AF32

AM21

C363 X_C10U10Y0805C363 X_C10U10Y0805

3

AJ26

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AJ15

AJ14

AA30

AA29

Y30

Y29

V30

V29

U29

U27

AL13

AK14

AL29

AL27

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

RESERVED36

RESERVED37

RESERVED38

RESERVED39

RESERVED40

RESERVED41

RESERVED42

RESERVED43

RESERVED44

RESERVED45

RESERVED46

RESERVED47

RESERVED48

RESERVED49

RESERVED50

RESERVED51

RESERVED52

TEST0

TEST1

TEST2

Y12

U30

U31

R29

AA9

AJ32

AA10

AA11

VCC_DDR

VCCA_HPLL ---- >50mA ; Min Vout -- 1.121V

VCCA_MPLL ---- >130mA ; Min Vout -- 1.128V

VCCA_DPLLA --- >80mA ; Min Vout -- 1.132V

VCCA_DPLLB --- >80mA ; Min Vout -- 1.131V

VCCA_DAC ----- 70mA ; Min Vout -- 3.14V

VCCD_CRT ----- 20mA ; Min Vout -- 1.425V

VCCDQ_CRT ---- 0.5mA ; Min Vout -- 1.425V

VCCA_EXPPLL -- 50mA ; Min Vout -- 1.129V

VCC_SMCLK ---- 250mA

F13

V31

R30

U12

U11

R12

R13

AP21

TP19TP19

BSEL

2

0

1

0

0

0

0

1

A43

BC1

AA39

BC43

TP16TP16

TP15TP15

TP21TP21

TABLE

PSB FREQUENCY

200 MHZ (800)1

133 MHZ (533)

3

EXP_TXP0

EXP_TXN0

EXP_TXP1

EXP_TXN1

EXP_TXP2

EXP_TXN2

EXP_TXP3

EXP_TXN3

EXP_TXP4

EXP_TXN4

EXP_TXP5

EXP_TXN5

EXP_TXP6

EXP_TXN6

EXP_TXP7

EXP_TXN7

EXP_TXP8

EXP_TXN8

EXP_TXP9

EXP_TXN9

EXP_TXP10

EXP_TXN10

EXP_TXP11

EXP_TXN11

EXP_TXP12

EXP_TXN12

EXP_TXP13

EXP_TXN13

EXP_TXP14

EXP_TXN14

EXP_TXP15

EXP_TXN15

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

EXP_COMPO

EXP_COMPI

HSYNC

VSYNC

RED

GREEN

BLUE

RED#

GREEN#

BLUE#

DDC_DATA

DDC_CLK

DREFCLKP

DREFCLKN

REFSET

PWROK2

V_1P25_PLTRST#

VREF2

RESERVED54

RESERVED55

ALLZTEST

XORTEST

RESERVED56

2

D11

D12

B11

A10

C10

D9

B9

B7

D7

D6

B5

B6

B3

B4

F2

E2

F4

G4

J4

K3

L2

K1

N2

M2

P3

N4

R2

P1

U2

T2

V3

U4

C341 C0.1U16Y0402C341 C0.1U16Y0402

V7

C343 C0.1U16Y0402C343 C0.1U16Y0402

V6

C342 C0.1U16Y0402C342 C0.1U16Y0402

W4

C344 C0.1U16Y0402C344 C0.1U16Y0402

Y4

C346 C0.1U16Y0402C346 C0.1U16Y0402

AC8

C348 C0.1U16Y0402C348 C0.1U16Y0402

AC9

C345 C0.1U16Y0402C345 C0.1U16Y0402

Y2

C347 C0.1U16Y0402C347 C0.1U16Y0402

AA2

GRCOMP

AC11

AC12

C15

D15

B18

C19

B20

C18

D19

D20

L13

M13

C14

D13

A20

AM15

AA12

AM5

AD13

AD12

K20

F20

A14

R460 24.9R1%0402R460 24.9R1%0402

HSYNC

VSYNC

VGA_BLUE VGA_BLUE

MCH_DDC_DATA

MCH_DDC_CLK

DOTCLK

R456 10KR/2R456 10KR/2

DOTCLK#

R452 0R0402R452 0R0402

Stuff for P31

REFSET

R451 0R0402R451 0R0402

MCH_CLPWROK

CL_RST#

CL_VREF_MCH

TP17TP17

TP18TP18

TP2TP2

R377

R377

1.65KR1%0402

1.65KR1%0402

R376

R376

1KR0402

1KR0402

PLTRST# 8,12,16

EXP_A_TXP_0 22

EXP_A_TXN_0 22

EXP_A_TXP_1 22

EXP_A_TXN_1 22

EXP_A_TXP_2 22

EXP_A_TXN_2 22

EXP_A_TXP_3 22

EXP_A_TXN_3 22

EXP_A_TXP_4 22

EXP_A_TXN_4 22

EXP_A_TXP_5 22

EXP_A_TXN_5 22

EXP_A_TXP_6 22

EXP_A_TXN_6 22

EXP_A_TXP_7 22

EXP_A_TXN_7 22

EXP_A_TXP_8 22

EXP_A_TXN_8 22

EXP_A_TXP_9 22

EXP_A_TXN_9 22

EXP_A_TXP_10 22

EXP_A_TXN_10 22

EXP_A_TXP_11 22

EXP_A_TXN_11 22

EXP_A_TXP_12 22

EXP_A_TXN_12 22

EXP_A_TXP_13 22

EXP_A_TXN_13 22

EXP_A_TXP_14 22

EXP_A_TXN_14 22

EXP_A_TXP_15 22

EXP_A_TXN_15 22

DMI_ICH_MT_IR_0_DP 12

DMI_ICH_MT_IR_0_DN 12

DMI_ICH_MT_IR_1_DP 12

DMI_ICH_MT_IR_1_DN 12

DMI_ICH_MT_IR_2_DP 12

DMI_ICH_MT_IR_2_DN 12

DMI_ICH_MT_IR_3_DP 12

DMI_ICH_MT_IR_3_DN 12

HSYNC 25

VSYNC 25

VGA_REDVGA_RED

VGA_GREENVGA_GREEN

MCH_DDC_DATA 25

MCH_DDC_CLK 25

R445 0R0402R445 0R0402

C553

C553

C10P50N0402

C10P50N0402

CL_RST#

C382

C382

X_C0.01U25X0402

X_C0.01U25X0402

V_1P25_CORE

V_1P25_CORE

HSYNC

VSYNC

Stuff 0-ohm for P31

VGA_RED 25

VGA_GREEN 25

VGA_BLUE 25

DOTCLK

DOTCLK#

CHIP_PWGD 8,13,29

MCH CORE DECOUPLING

V_1P25_CORE

R375

R375

1KR0402

1KR0402

CL_VREF_MCHCL_RST#

C383

R366

R366

392R1%0402

392R1%0402

C383

C0.01U25X0402

C0.01U25X0402

CL_VREF_MCH = 0.352V (FOR NOW)

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

Title

Title

Title

Intel Bearlake G31 - CPU Signals

Intel Bearlake G31 - CPU Signals

Intel Bearlake G31 - CPU Signals

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

2

MS-7392

MS-7392

MS-7392

1

R559 0R0402R559 0R0402

R558 0R0402R558 0R0402

DOTCLK 15

DOTCLK# 15

of

10 35Friday, May 16, 2008

of

10 35Friday, May 16, 2008

of

10 35Friday, May 16, 2008

1

2.2

2.2

2.2

5

4

3

2

1

TP25TP25

V_1P25_CORE

D D

BC37

BC32

BC28

BC24

BC10

BC5

BB7

AY41

AY4

AW43

AW41

AW1

AV37

AV35

AV27

AV23

AV21

AV17

AV11

AV9

AV7

AU42

C C

B B

A A

5

AU38

AU32

AU24

AU20

AT31

AT29

AT15

AT13

AT12

AR38

AR33

AR32

AR27

AR26

AR23

AR21

AR20

AR17

AP43

AP24

AP18

AN38

AN31

AN29

AN24

AN23

AN20

AN15

AN13

AN12

AN11

AM42

AM40

AM36

AM33

AM29

AM24

AM23

AM20

AM11

AL36

AL33

AK43

AU6

AU2

AR9

AR6

AN4

AM9

AM7

AM4

AM2

AM1

AP1

AA17

AA15

AA14

Y27

Y26

Y18

Y17

Y15

Y14

W27

W26

W25

W23

W21

W19

W18

W17

V27

V26

V25

V24

V23

V22

V21

V20

V19

V18

V17

V15

V14

U26

U25

U24

U23

U22

U21

U20

U19

U18

U17

U15

U14

R20

R18

R17

R15

R14

VCC

VSS

VCC

VSS

J27

VCC

VCC

VSS

VSSJ9VSSJ7VSSJ5VSS

J21

P15

VCC

VCC

VCC

H31

H29

U7D

U7D

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS