MSI MS-7374 Schematics

5

4

3

2

1

Title Page

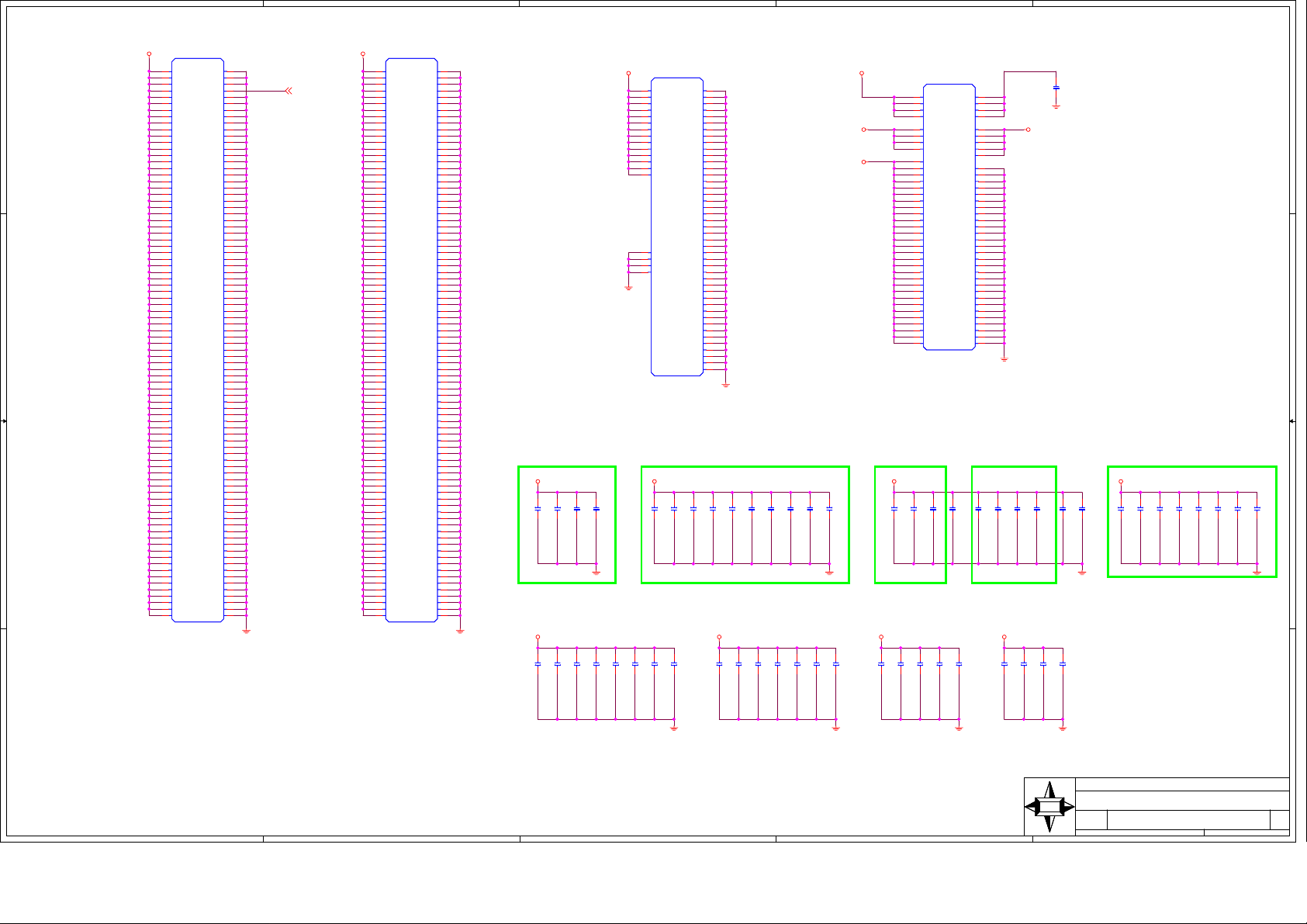

Cover Sheet 1

D D

MS-7374 Ver: 0A

CPU:

AMD M2 Athlon 64/Athlon 64 FX/AM2r2

System Chipset:

MCP72P (Single Chip)

MSI

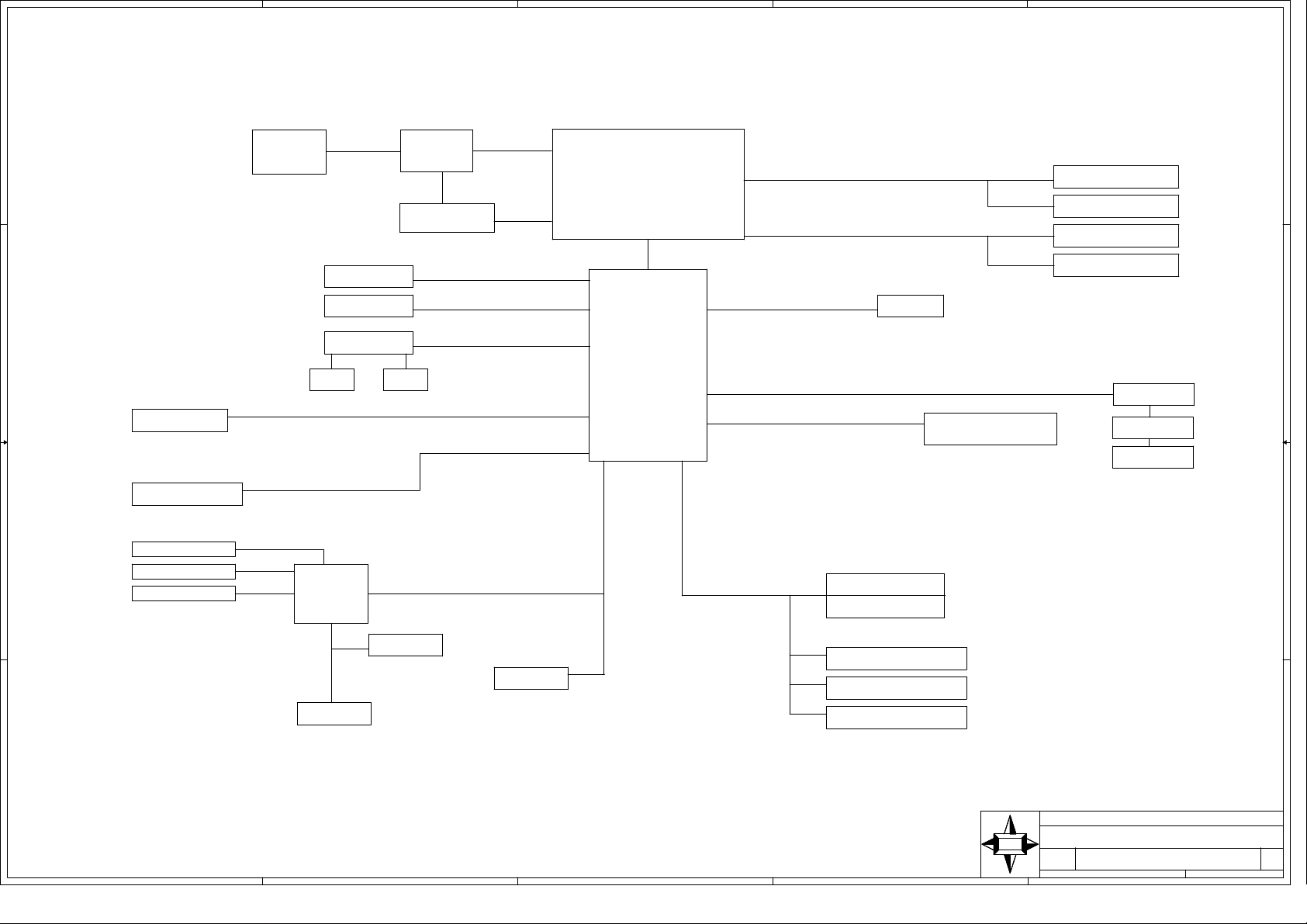

Block Diagram

AM2+ HT I/F, CTRL & DEBEG

AM2+ DDR II MEMORY I/F

AM2+ POWER & GND

DDR II DIMM 1 / 3

DDR II DIMM 2 / 4

DDR II Terminator

On Board Chipset:

Winbond Super I/O -- FINTEK 71882FG

LAN -- RTL8211BL

HD Codec --ALC888

C C

BIOS --SPI FLASH ROM 8M

IEEE-1394 -- VIA - VT6308P

JMB-363 (PATA X 1 & e-SATA X 2)

MCP72P HT

MCP72P PCI-E X16

MCP72P PCI-E X1 & MII & JTAG

MCP72P PCI & LPC 12

MCP72P SATA X6 & IDE X1

MCP72P AUDIO & USB & MISC

2

3

4

5

6

7

8

9

10

11

13

14

MCP72P POWER & GND 15

Main Memory:

DDR II * 4 (Max 4GB)

Expansion Slots:

PCI-E X 1 *1

PCI-E X 16 *2

PCI 2.2 Slot X 2

PWM:

B B

Controller -- Intersil ISL6312CRZ + 6612 -- 4 Channel 8 Phase

FINTEK -- F75125 P/SVID to PVID

Clock Generator:

MCP72P inner builded

A A

5

4

PCI-E X16 & X1 Slot

PCI-E X8/X1 Slot & Digital switch

PCI Slot 1 & 2 & 3

SIO F71882FG-BIOS & FDD & K/M & COM1

LAN - Realtek 8211BL

HD Audio - ALC888

1394 Controller-VT6308

JMicron 363 e-SATA X2 & IDE X1

USB connectors

ISL6312CRZ+6612 4 PHASE 8 CHANNEL

F75125 - PVID/SIVD to PVID

uPI ACPI Controller + DC POWER

DDR / NB / VCCP_NB POWER

FAN CONTROL

ATX / Front Panel / TPM / LED Function

D-LED / EMI / Front panel define

MANUAL PARTS

GPIO & JUMPER SETTING

POWER MAP

POWER OK MAP

RESET MAP

HISTORY

3

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

2

MSI

MSI

MSI

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7374

MS-7374

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Monday, August 06, 2007

Date:

Monday, August 06, 2007

Date:

Monday, August 06, 2007

MS-7374

Cover Sheet

Cover Sheet

Cover Sheet

1

137

137

137

Sheet of

Sheet of

Sheet of

0A

0A

0A

5

4

3

2

1

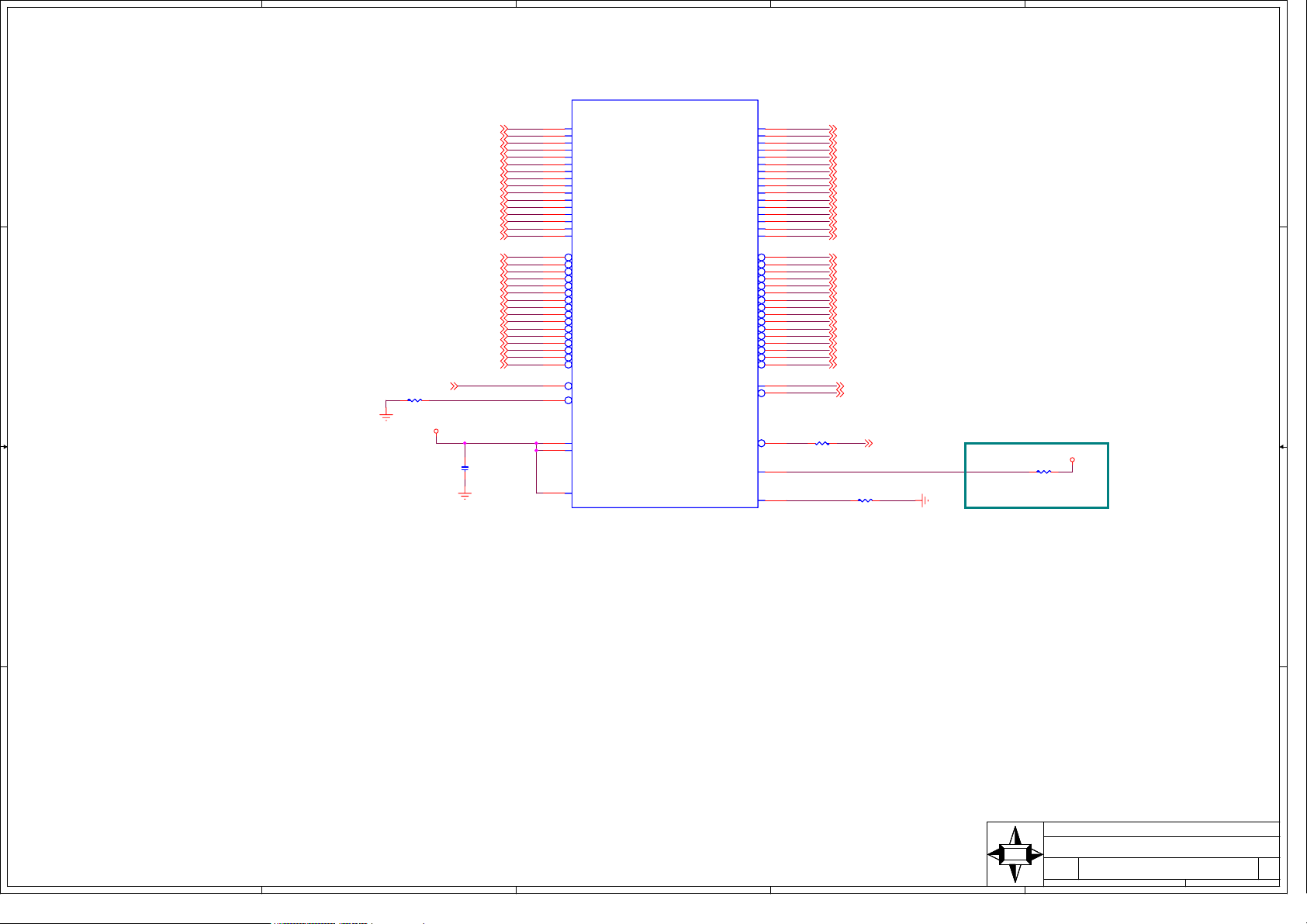

BLOCK DIAGRAM

D D

POWER

SUPPLY

CONNECTOR

PEX X16 SLOT1,2

PEX X1 SLOT1

VREG

Intersil 6312CRZ

F75125 - VID S to P, P to P

PCI EXPRESS

PCI EXPRESS

SOCKET 940

AM2/AM2+

HT 16X16 1GHZ

128-BIT 400/533MHZ

RGMII

DDR SDRAM CONN 0

DDR SDRAM CONN 2

DDR SDRAM CONN 1

DDR SDRAM CONN3

LAN-RTL-8211BL

C C

JMB-363

PCI EXPRESS

MCP72P

SLAVE IDE

PRIMARY IDE

X6 - SATA II CONN

B B

A A

FLOPPY CONN

PS2/KBRD CONN

SERIAL PINHEADER

ATA 133

INTEGRATED SATA 1/2

SIO

LPC SUPER I/O

F71882-FG

8MB FLASH

e-SATA X 2

SPI HDR

TPM HDR

PCI 33MHZ

AZAILIA

LPC BUS 33MHZ

BACK PANEL CONN

X12 USB2.0

USB2 PORTS 0-3

USB 2 X 2 CONN

USB2 PORTS 4-5

X2/GBIT LAN

FRONT PANEL HDR

USB2 PORTS 6-7

USB2 PORTS 8-9

USB2 PORTS 10-11

Realtek ALC 888 (HD, 7.1Channel)

IEEE1394-VT6308

PCI SLOT 1

PCI SLOT 2

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7374

MS-7374

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Monday, August 06, 2007

Date:

Monday, August 06, 2007

Date:

5

4

3

2

Monday, August 06, 2007

MS-7374

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

1

Sheet of

Sheet of

Sheet of

237

237

237

0A

0A

0A

5

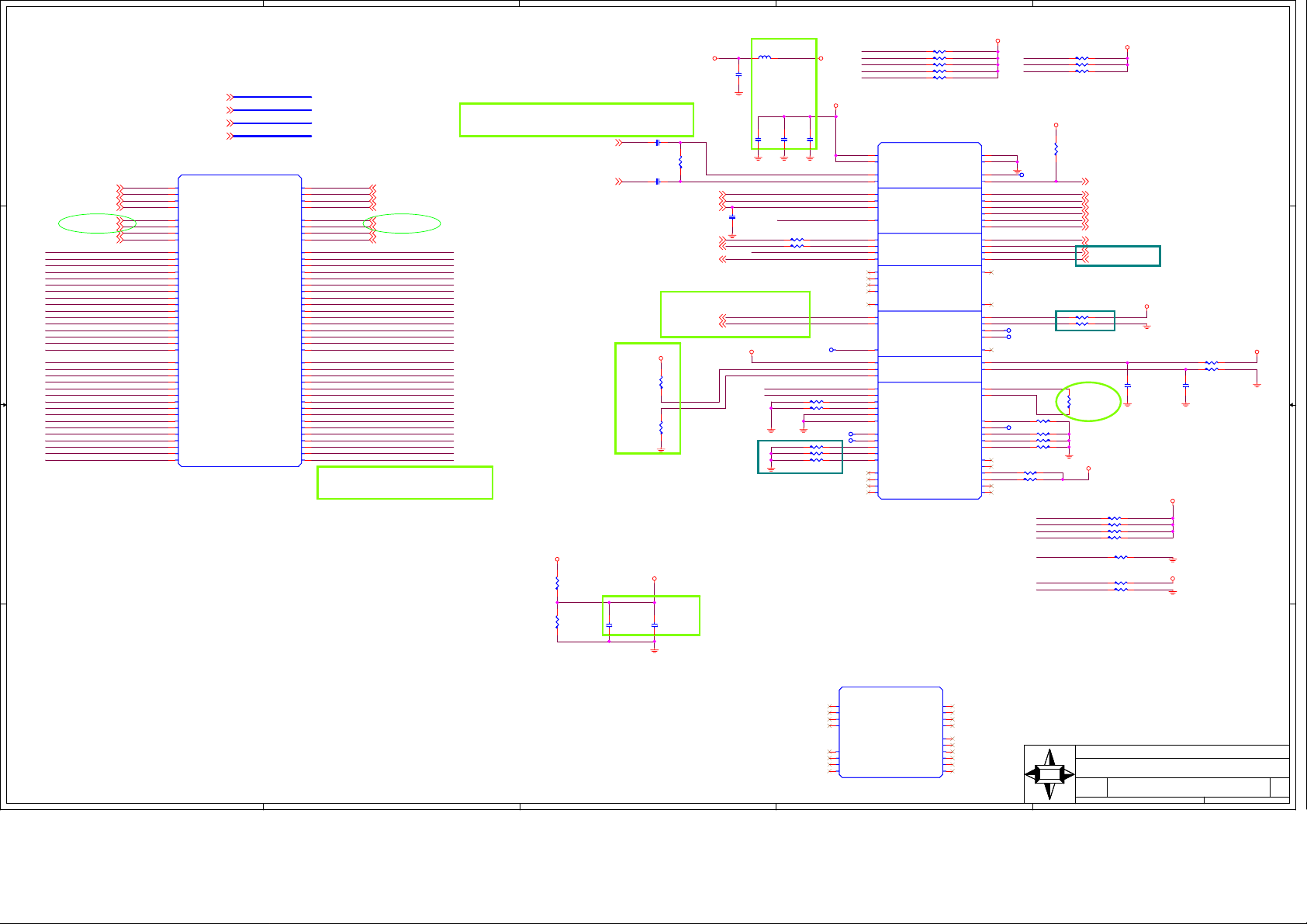

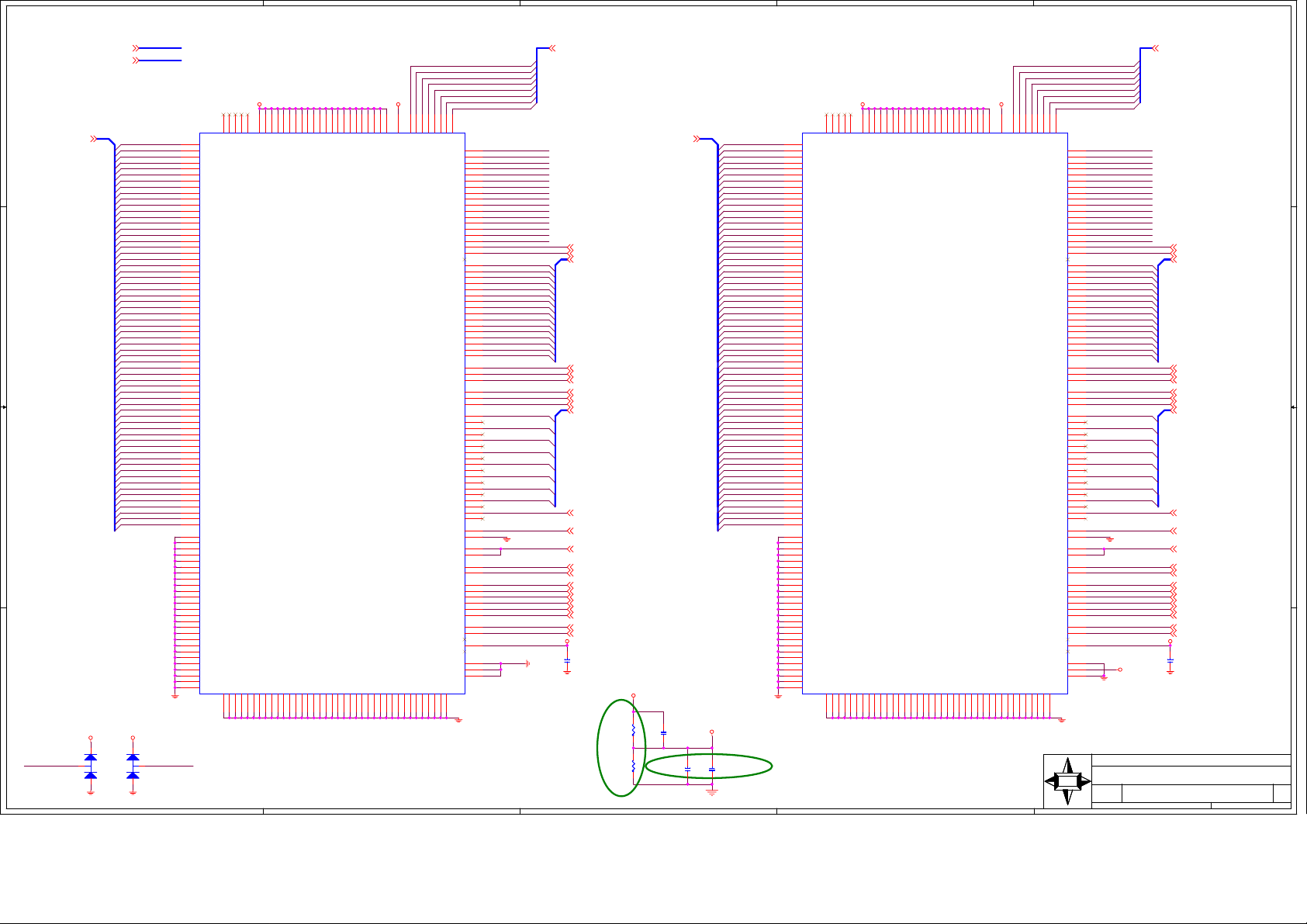

If routing to a chipset that doesn't support HyperTransport 3:

- L0_CTLIN_H(1) should be connected to VLDT_RUN using 49.9 Ohm resistor

- L0_CTLIN_L(1) should be connected to GND using 49.9 Ohm resistor

D D

HT_CLKIN_H19

HT_CLKIN_L19

HT_CLKIN_H09

HT_CLKIN_L09

HT_CTLIN_H19

HT_CTLIN_L19

HT_CTLIN_H09

HT_CTLIN_L09

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

C C

B B

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

HT_CADIN_H[15..0]9

HT_CADIN_L[15..0]9

HT_CADOUT_H[15..0]9

HT_CADOUT_L[15..0]9

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

CPU1A

CPU1A

L0_CLKIN_H[1]

L0_CLKIN_L[1]

L0_CLKIN_H[0]

L0_CLKIN_L[0]

L0_CTLIN_H[1]

L0_CTLIN_L[1]

L0_CTLIN_H[0]

L0_CTLIN_L[0]

L0_CADIN_H[15]

L0_CADIN_L[15]

L0_CADIN_H[14]

L0_CADIN_L[14]

L0_CADIN_H[13]

L0_CADIN_L[13]

L0_CADIN_H[12]

L0_CADIN_L[12]

L0_CADIN_H[11]

L0_CADIN_L[11]

L0_CADIN_H[10]

L0_CADIN_L[10]

L0_CADIN_H[9]

L0_CADIN_L[9]

L0_CADIN_H[8]

L0_CADIN_L[8]

L0_CADIN_H[7]

L0_CADIN_L[7]

L0_CADIN_H[6]

L0_CADIN_L[6]

L0_CADIN_H[5]

L0_CADIN_L[5]

L0_CADIN_H[4]

L0_CADIN_L[4]

L0_CADIN_H[3]

L0_CADIN_L[3]

L0_CADIN_H[2]

L0_CADIN_L[2]

L0_CADIN_H[1]

L0_CADIN_L[1]

L0_CADIN_H[0]

L0_CADIN_L[0]

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

HYPERTRANSPORT

HYPERTRANSPORT

L0_CLKOUT_H[1]

L0_CLKOUT_L[1]

L0_CLKOUT_H[0]

L0_CLKOUT_L[0]

L0_CTLOUT_H[1]

L0_CTLOUT_L[1]

L0_CTLOUT_H[0]

L0_CTLOUT_L[0]

L0_CADOUT_H[15]

L0_CADOUT_L[15]

L0_CADOUT_H[14]

L0_CADOUT_L[14]

L0_CADOUT_H[13]

L0_CADOUT_L[13]

L0_CADOUT_H[12]

L0_CADOUT_L[12]

L0_CADOUT_H[11]

L0_CADOUT_L[11]

L0_CADOUT_H[10]

L0_CADOUT_L[10]

L0_CADOUT_H[9]

L0_CADOUT_L[9]

L0_CADOUT_H[8]

L0_CADOUT_L[8]

L0_CADOUT_H[7]

L0_CADOUT_L[7]

L0_CADOUT_H[6]

L0_CADOUT_L[6]

L0_CADOUT_H[5]

L0_CADOUT_L[5]

L0_CADOUT_H[4]

L0_CADOUT_L[4]

L0_CADOUT_H[3]

L0_CADOUT_L[3]

L0_CADOUT_H[2]

L0_CADOUT_L[2]

L0_CADOUT_H[1]

L0_CADOUT_L[1]

L0_CADOUT_H[0]

L0_CADOUT_L[0]

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

Layout: Keep HT bus less than 8 inch.

mismatch 26mil.

HT_CLKOUT_H1 9

HT_CLKOUT_L1 9

HT_CLKOUT_H0 9

HT_CLKOUT_L0 9

HT_CTLOUT_H1 9

HT_CTLOUT_L1 9

HT_CTLOUT_H0 9

HT_CTLOUT_L0 9

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

4

Layout: Keep trace to 169 OHM less than 600mils

from CPU, and trace to 3900pf less than 1250mils.

The mismatch tolerance for CLKIN_H and CLKIN_L is 30mils.

VCC_DDR

CPU_CLK9

CPU_CLK#9

Keep trace to resistors

less than 1 inch from CPU pins.

R112

R112

15RST/8

15RST/8

CPU_M_VREF

R113

R113

15RST/8

15RST/8

39.2RST/4

39.2RST/4

39.2RST/4

39.2RST/4

C100

C100

0.1u/25V/4

0.1u/25V/4

3

C108 3900P/16V/4C108 3900P/16V/4

R124

R124

169RST/4

169RST/4

C112 3900P/16V/4C112 3900P/16V/4

VCC_DDR

R152

R152

R144

R144

CPU_M_VREF

C104

C104

1000p/50V/4

1000p/50V/4

Place as close as

possible to CPU Socket.

Keep 20mils.

X_4.7u/10V/8

X_4.7u/10V/8

LDT_PWRGD9,26

LDT_STOP#9

LDT_RST#9

CPU_SIC14,19

CPU_SID14,19

route as diff pair 10/10/10

COREFB+26

COREFB-25

VDDA_25

C96

C96

CPU_M_VREF

L3

L3

80L3_70_0805

80L3_70_0805

VDDA25

C102 4.7u/10V/8C102 4.7u/10V/8

C110

C110

X_C1000p50X0402

X_C1000p50X0402

CPU_SIC

CPU_SID

COREFB+

COREFB-

21

AM2r2 DTX CPU Centric Schmatics

Keep 20mils.

C107 0.22u/16V/6C107 0.22u/16V/6

CPUCLKIN

CPUCLKIN#

LDT_PWRGD

LDT_STOP#

LDT_RST#

CPU_PRESENT_L

R155 0R/4R155 0R/4

R156 0R/4R156 0R/4

CPU_SA[0]

CPU_ALERT

MEMZN

MEMZP

CPU_TEST25_H

CPU_TEST25_L

R116 300/4R116 300/4

R123 300/4R123 300/4

R118 300/4R118 300/4

R115 300/4R115 300/4

R143 300/4R143 300/4

2

LDT_PWRGD

VDDA25VDDA_25

VDDA25

C111 3300P/50V/6C111 3300P/50V/6

TP6TP6

LDT_STOP#

LDT_RST#

CPU_THRIP#

CPU_PROCHOT#

Keep 20mils. This trace should be kept

at least 20mils away from all other signals.

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AK4

AL4

AL10

AJ10

AH10

AL9

A5

G2

G1

E12

F12

AH11

AJ11

A10

B10

F10

E9

AJ7

F6

TP2TP2

D6

TP3TP3

E7

F8

C5

AH9

E5

AJ5

AH7

AJ6

CPU1D

CPU1D

VDDA

VDDA

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

SA[0]

ALERT_L

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST3

TEST2

R122 300/4R122 300/4

R121 300/4R121 300/4

R120 300/4R120 300/4

R160 300/4R160 300/4

R159 300/4R159 300/4

MISC

MISC

PLATFORM_TYPE

KEY/VSS

KEY/VSS

CORE_TYPE

VID[5]

VID[4]

SVC/VID[3]

SVD/VID[2]

PVIEN/VID[1]

VID[0]

THERMDC

THERMDA

THERMTRIP_L

PROCHOT_L

DBRDY

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

VCC_DDR

H22

AE9

F2

G5

D2

D1

C1

E3

E2

E1

AG9

AG8

AK7

AL7

AK10

TDO

B6

DDR_FB_H

AK11

DDR_FB_L

AL11

G4

TP4TP4

G3

TP5TP5

F1

V8

V7

FBCLKOUT

C11

FBCLKOUT#

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

R150 300/4R150 300/4

AK9

R158 300/4R158 300/4

AK5

G7

D4

CPU_SA[0] has internal pull high

CPU_VID2

CPU_VID3

CPU_VID1

VCC_DDR

TP1TP1

CPU_VID5

CPU_VID4

CPU_VID3

CPU_VID2

CPU_VID1

CPU_VID0

CPU_THRIP#

CPU_PROCHOT#

CPU_HTREF1

CPU_HTREF0

R141 300/4R141 300/4

TP7TP7

R151 300/4R151 300/4

R149 300/4R149 300/4

R142 300/4R142 300/4

CPU_SIC

CPU_SID

CPU_ALERT

CPU_PRESENT_L

CPU_SA[0]

CPU_TEST25_H

CPU_TEST25_L

R109 300/4R109 300/4

R107 300/4R107 300/4

R108 300/4R108 300/4

R110

R110

300/4

300/4

CPU_CORE_TYPE 26

CPU_VID5 26

CPU_VID4 26

CPU_VID3 26

CPU_VID2 26

CPU_VID1 26

CPU_VID0 26

THERMDC_CPU 19

THERMDA_CPU 19

CPU_THRIP# 9

CPU_PROCHOT# 9CPU_ALERT9

in back of MB

R153 X_0R/4R153 X_0R/4

R145 X_0R/4R145 X_0R/4

R119

R119

80.6RST/4

80.6RST/4

VCC_DDR

R162 390R0402R162 390R0402

R163 1K/4R163 1K/4

R148 1K/4R148 1K/4

R157 1K/4R157 1K/4

1

VCC_DDR

not need level shifter.

VCC_DDR

C216

C216

X_C1000p50X0402

X_C1000p50X0402

Route as 80.6-ohms differential

impedance.

Keep trace to resistor < 0.5inch

from CPU pins.

VCC_DDR

AM2+ Design Guide SIC, SID, ALERT

all need 1K Ohm.

R140 0R/4R140 0R/4

R114 510/4R114 510/4

R117 510/4R117 510/4

VCC_DDR

Keep CPU_HTREF less

than 1.5" from in length.

R154 44.2RST/6R154 44.2RST/6

R147 44.2RST/6R147 44.2RST/6

C210

C210

X_C1000p50X0402

X_C1000p50X0402

VCC1_2HT

Place within 500 mils of the CPU socket.

CPU1E

CPU1E

INTERNAL

INTERNAL

MISC

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

MISC

L30

RSVD

L31

RSVD

V29

RSVD

W30

RSVD

F3

RSVD

G24

RSVD

G25

RSVD

H25

RSVD

L25

RSVD

L26

RSVD

2

MSI

MSI

MSI

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7374

MS-7374

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Monday, September 03, 2007

Date:

Monday, September 03, 2007

Date:

Monday, September 03, 2007

MS-7374

AM2+ HT I/F,CTRL&DEBUG

AM2+ HT I/F,CTRL&DEBUG

AM2+ HT I/F,CTRL&DEBUG

Sheet of

Sheet of

Sheet of

1

337

337

337

0A

0A

0A

A A

5

4

3

AD25

AE24

AE25

AJ18

AJ20

AK3

C18

C20

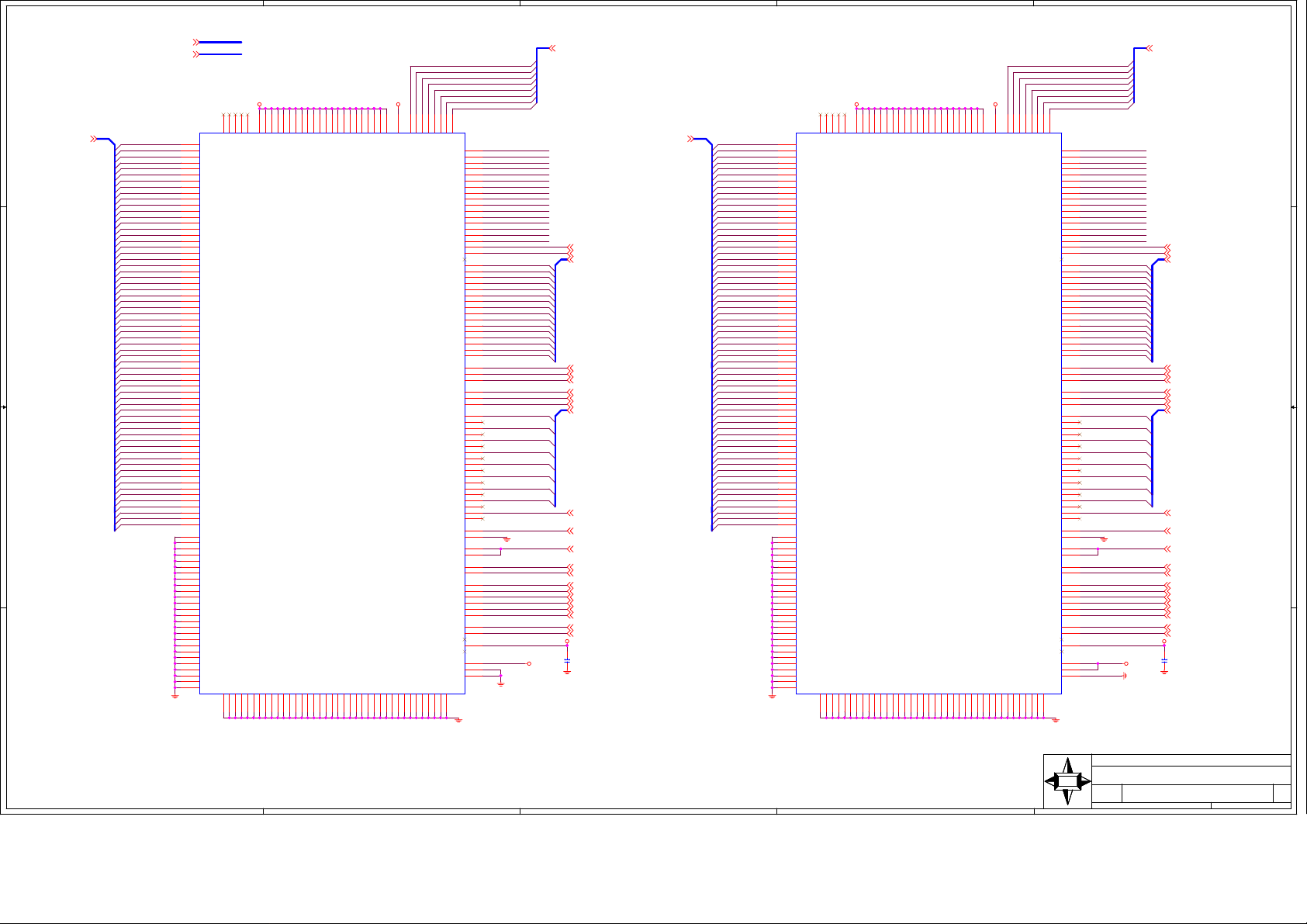

5

MEM_MA_DQS_L[7..0]6 MEM_MB_DQS_L[7..0]7

MEM_MA_DQS_H[7..0]6

MEM_MA_DM[7..0]6

MEM_MA0_CLK_H26,8

MEM_MA0_CLK_L26,8

D D

C C

MEM_MA_ADD[15..0]6,8

B B

MEM_MA1_CLK_H26,8

MEM_MA1_CLK_L26,8

MEM_MA0_CLK_H06,8

MEM_MA0_CLK_L06,8

MEM_MA1_CLK_H06,8

MEM_MA1_CLK_L06,8

MEM_MA0_CLK_H16,8

MEM_MA0_CLK_L16,8

MEM_MA1_CLK_H16,8

MEM_MA1_CLK_L16,8

MEM_MA0_CS_L16,8

MEM_MA0_CS_L06,8

MEM_MA0_ODT06,8

MEM_MA1_CS_L16,8

MEM_MA1_CS_L06,8

MEM_MA1_ODT06,8

MEM_MA_CAS_L6,8

MEM_MA_WE_L6,8

MEM_MA_RAS_L6,8

MEM_MA_BANK26,8

MEM_MA_BANK16,8

MEM_MA_BANK06,8

MEM_MA_CKE16,8

MEM_MA_CKE06,8

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AG21

AG20

AE20

AE19

AC25

AA24

AE28

AC28

AD27

AA25

AE27

AC27

AB25

AB27

AA26

AA27

AC26

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

U27

U26

V27

W27

W26

W25

U24

V24

G19

H19

G20

G21

E20

N25

Y27

L27

M25

M27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

D29

C29

C25

D25

E19

F19

F15

G15

B29

E24

E18

H15

CPU1B

CPU1B

MA_CLK_H[7]

MA_CLK_L[7]

MA_CLK_H[6]

MA_CLK_L[6]

MA_CLK_H[5]

MA_CLK_L[5]

MA_CLK_H[4]

MA_CLK_L[4]

MA_CLK_H[3]

MA_CLK_L[3]

MA_CLK_H[2]

MA_CLK_L[2]

MA_CLK_H[1]

MA_CLK_L[1]

MA_CLK_H[0]

MA_CLK_L[0]

MA0_CS_L[1]

MA0_CS_L[0]

MA0_ODT[1]

MA0_ODT[0]

MA1_CS_L[1]

MA1_CS_L[0]

MA1_ODT[1]

MA1_ODT[0]

MA_RESET_L

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK[2]

MA_BANK[1]

MA_BANK[0]

MA_CKE[1]

MA_CKE[0]

MA_ADD[15]

MA_ADD[14]

MA_ADD[13]

MA_ADD[12]

MA_ADD[11]

MA_ADD[10]

MA_ADD[9]

MA_ADD[8]

MA_ADD[7]

MA_ADD[6]

MA_ADD[5]

MA_ADD[4]

MA_ADD[3]

MA_ADD[2]

MA_ADD[1]

MA_ADD[0]

MA_DQS_H[7]

MA_DQS_L[7]

MA_DQS_H[6]

MA_DQS_L[6]

MA_DQS_H[5]

MA_DQS_L[5]

MA_DQS_H[4]

MA_DQS_L[4]

MA_DQS_H[3]

MA_DQS_L[3]

MA_DQS_H[2]

MA_DQS_L[2]

MA_DQS_H[1]

MA_DQS_L[1]

MA_DQS_H[0]

MA_DQS_L[0]

MA_DM[7]

MA_DM[6]

MA_DM[5]

MA_DM[4]

MA_DM[3]

MA_DM[2]

MA_DM[1]

MA_DM[0]

MEMORY

MEMORY

INTERFACE

INTERFACE

MA_DATA[63]

MA_DATA[62]

MA_DATA[61]

MA_DATA[60]

MA_DATA[59]

MA_DATA[58]

MA_DATA[57]

MA_DATA[56]

MA_DATA[55]

MA_DATA[54]

MA_DATA[53]

MA_DATA[52]

MA_DATA[51]

MA_DATA[50]

MA_DATA[49]

MA_DATA[48]

MA_DATA[47]

MA_DATA[46]

MA_DATA[45]

MA_DATA[44]

MA_DATA[43]

MA_DATA[42]

MA_DATA[41]

MA_DATA[40]

MA_DATA[39]

MA_DATA[38]

MA_DATA[37]

MA_DATA[36]

MA_DATA[35]

MA_DATA[34]

MA_DATA[33]

MA_DATA[32]

MA_DATA[31]

MA_DATA[30]

MA_DATA[29]

MA_DATA[28]

MA_DATA[27]

MA_DATA[26]

MA_DATA[25]

MA_DATA[24]

MA_DATA[23]

MA_DATA[22]

MA_DATA[21]

MA_DATA[20]

MA_DATA[19]

MA_DATA[18]

MA_DATA[17]

MA_DATA[16]

MA_DATA[15]

MA_DATA[14]

MA_DATA[13]

MA_DATA[12]

MA_DATA[11]

MA_DATA[10]

MA_DATA[9]

MA_DATA[8]

MA_DATA[7]

MA_DATA[6]

MA_DATA[5]

MA_DATA[4]

MA_DATA[3]

MA_DATA[2]

MA_DATA[1]

MA_DATA[0]

MA_DQS_H[8]

MA_DQS_L[8]

MA_DM[8]

MA_CHECK[7]

MA_CHECK[6]

MA_CHECK[5]

MA_CHECK[4]

MA_CHECK[3]

MA_CHECK[2]

MA_CHECK[1]

MA_CHECK[0]

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

4

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_CHECK7

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA_DATA[63..0] 6

MEM_MA_DQS_H8 6

MEM_MA_DQS_L8 6

MEM_MA_DM8 6

MEM_MA_CHECK[7..0] 6

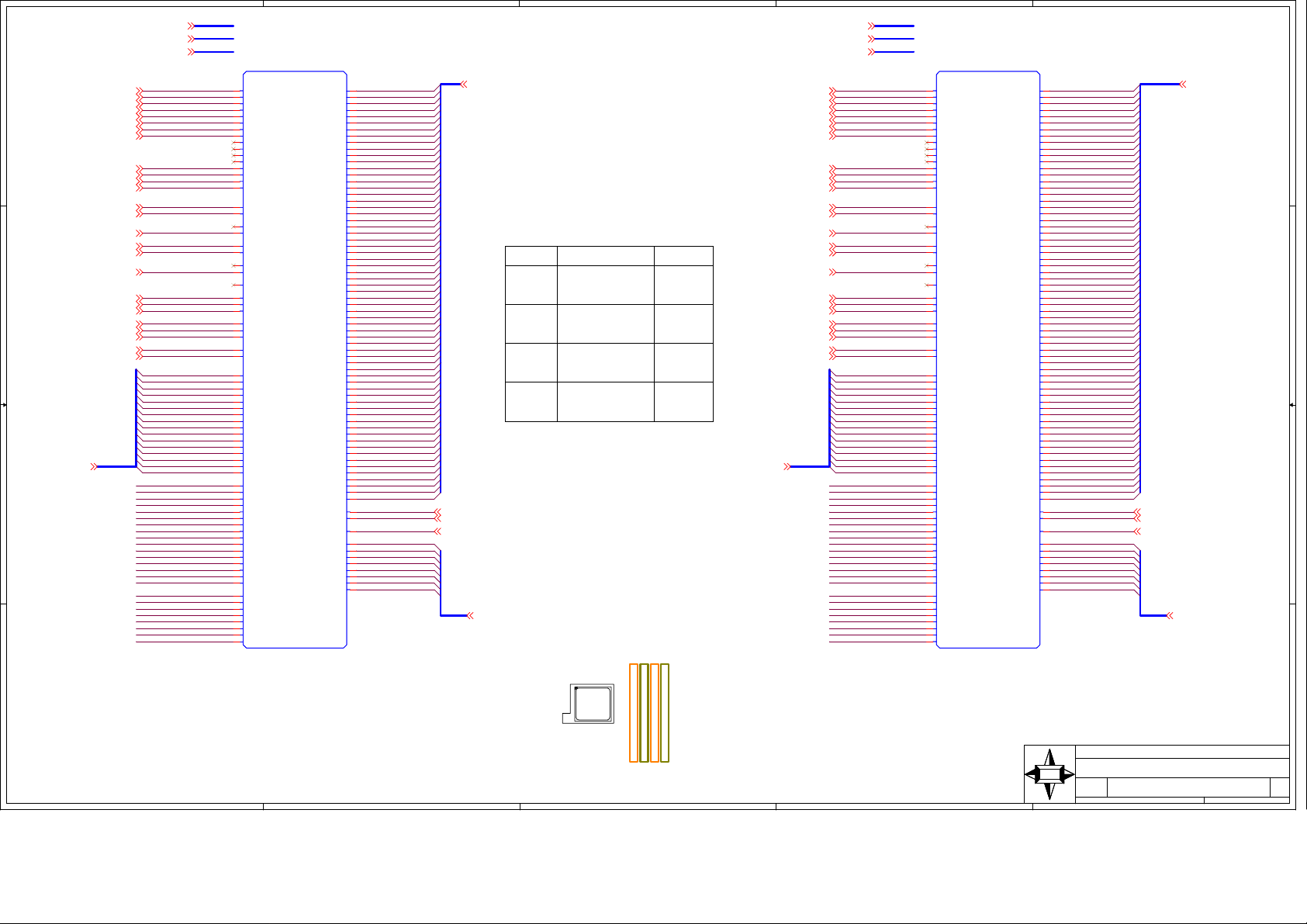

MEMORY CLOCK TRANSLATION

DIMM

DIMM A0

DIMM A1

DIMM B0

DIMM B1

DDR2 Memory Signal

MEM_MA0_CLK(2)

MEM_MA0_CLK(1)

MEM_MA0_CLK(0)

MEM_MA1_CLK(2)

MEM_MA1_CLK(1)

MEM_MA1_CLK(0)

MEM_MB0_CLK(2)

MEM_MB0_CLK(1)

MEM_MB0_CLK(0)

MEM_MB1_CLK(2)

MEM_MB1_CLK(1)

MEM_MB1_CLK(0)

3

CPU Signal

MA_CLK(7)

MA_CLK(1)

MA_CLK(5)

MA_CLK(6)

MA_CLK(0)

MA_CLK(4)

MB_CLK(7)

MB_CLK(1)

MB_CLK(5)

MB_CLK(6)

MB_CLK(0)

MB_CLK(4)

2

MEM_MB_DQS_H[7..0]7

MEM_MB_DM[7..0]7

MEM_MB0_CLK_H27,8

MEM_MB0_CLK_L27,8

MEM_MB1_CLK_H27,8

MEM_MB1_CLK_L27,8

MEM_MB0_CLK_H07,8

MEM_MB0_CLK_L07,8

MEM_MB1_CLK_H07,8

MEM_MB1_CLK_L07,8

MEM_MB0_CLK_H17,8

MEM_MB0_CLK_L17,8

MEM_MB1_CLK_H17,8

MEM_MB1_CLK_L17,8

MEM_MB0_CS_L17,8

MEM_MB0_CS_L07,8

MEM_MB0_ODT07,8

MEM_MB1_CS_L17,8

MEM_MB1_CS_L07,8

MEM_MB1_ODT07,8

MEM_MB_CAS_L7,8

MEM_MB_WE_L7,8

MEM_MB_RAS_L7,8

MEM_MB_BANK27,8

MEM_MB_BANK17,8

MEM_MB_BANK07,8

MEM_MB_CKE17,8

MEM_MB_CKE07,8

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD[15..0]7,8

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AJ19

AK19

AL19

AL18

W29

W28

W31

AE30

AC31

AF31

AD29

AE29

AB31

AG31

AD31

AC29

AC30

AB29

AA31

AA28

M31

M29

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

U31

U30

Y31

Y30

V31

A18

A19

C19

D19

B19

N31

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

CPU1C

CPU1C

MB_CLK_H[7]

MB_CLK_L[7]

MB_CLK_H[6]

MB_CLK_L[6]

MB_CLK_H[5]

MB_CLK_L[5]

MB_CLK_H[4]

MB_CLK_L[4]

MB_CLK_H[3]

MB_CLK_L[3]

MB_CLK_H[2]

MB_CLK_L[2]

MB_CLK_H[1]

MB_CLK_L[1]

MB_CLK_H[0]

MB_CLK_L[0]

MB0_CS_L[1]

MB0_CS_L[0]

MB0_ODT[1]

MB0_ODT[0]

MB1_CS_L[1]

MB1_CS_L[0]

MB1_ODT[1]

MB1_ODT[0]

MB_RESET_L

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK[2]

MB_BANK[1]

MB_BANK[0]

MB_CKE[1]

MB_CKE[0]

MB_ADD[15]

MB_ADD[14]

MB_ADD[13]

MB_ADD[12]

MB_ADD[11]

MB_ADD[10]

MB_ADD[9]

MB_ADD[8]

MB_ADD[7]

MB_ADD[6]

MB_ADD[5]

MB_ADD[4]

MB_ADD[3]

MB_ADD[2]

MB_ADD[1]

MB_ADD[0]

MB_DQS_H[7]

MB_DQS_L[7]

MB_DQS_H[6]

MB_DQS_L[6]

MB_DQS_H[5]

MB_DQS_L[5]

MB_DQS_H[4]

MB_DQS_L[4]

MB_DQS_H[3]

MB_DQS_L[3]

MB_DQS_H[2]

MB_DQS_L[2]

MB_DQS_H[1]

MB_DQS_L[1]

MB_DQS_H[0]

MB_DQS_L[0]

MB_DM[7]

MB_DM[6]

MB_DM[5]

MB_DM[4]

MB_DM[3]

MB_DM[2]

MB_DM[1]

MB_DM[0]

MEMORY

MEMORY

INTERFACE

INTERFACE

MB_DATA[63]

MB_DATA[62]

MB_DATA[61]

MB_DATA[60]

MB_DATA[59]

MB_DATA[58]

MB_DATA[57]

MB_DATA[56]

MB_DATA[55]

MB_DATA[54]

MB_DATA[53]

MB_DATA[52]

MB_DATA[51]

MB_DATA[50]

MB_DATA[49]

MB_DATA[48]

MB_DATA[47]

MB_DATA[46]

MB_DATA[45]

MB_DATA[44]

MB_DATA[43]

MB_DATA[42]

MB_DATA[41]

MB_DATA[40]

MB_DATA[39]

MB_DATA[38]

MB_DATA[37]

MB_DATA[36]

MB_DATA[35]

MB_DATA[34]

MB_DATA[33]

MB_DATA[32]

MB_DATA[31]

MB_DATA[30]

MB_DATA[29]

MB_DATA[28]

MB_DATA[27]

MB_DATA[26]

MB_DATA[25]

MB_DATA[24]

MB_DATA[23]

MB_DATA[22]

MB_DATA[21]

MB_DATA[20]

MB_DATA[19]

MB_DATA[18]

MB_DATA[17]

MB_DATA[16]

MB_DATA[15]

MB_DATA[14]

MB_DATA[13]

MB_DATA[12]

MB_DATA[11]

MB_DATA[10]

MB_DATA[9]

MB_DATA[8]

MB_DATA[7]

MB_DATA[6]

MB_DATA[5]

MB_DATA[4]

MB_DATA[3]

MB_DATA[2]

MB_DATA[1]

MB_DATA[0]

MB_DQS_H[8]

MB_DQS_L[8]

MB_DM[8]

MB_CHECK[7]

MB_CHECK[6]

MB_CHECK[5]

MB_CHECK[4]

MB_CHECK[3]

MB_CHECK[2]

MB_CHECK[1]

MB_CHECK[0]

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

1

MEM_MB_DQS_H8 7

MEM_MB_DQS_L8 7

MEM_MB_DM8 7

MEM_MB_CHECK[7..0] 7

MEM_MB_DATA[63..0] 7

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

A0 A1B0 B1

5

4

3

2

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, August 29, 2007

Date:

Wednesday, August 29, 2007

Date:

Wednesday, August 29, 2007

MS-7374

MS-7374

MS-7374

AM2+ DDR MEMORY I/F

AM2+ DDR MEMORY I/F

AM2+ DDR MEMORY I/F

Sheet of

Sheet of

Sheet of

1

0A

0A

0A

437

437

437

5

4

3

2

1

VCCP VCCP

CPU1F

CPU1F

VDD

VDD

B3

VDD

C2

VDD

C4

VDD

D3

VDD

D5

VDD

E4

VDD

E6

D D

C C

B B

VDD

F5

VDD

F7

VDD

G6

VDD

G8

VDD

H7

VDD

H11

VDD

H23

VDD

J8

VDD

J12

VDD

J14

VDD

J16

VDD

J18

VDD

J20

VDD

J22

VDD

J24

VDD

K7

VDD

K9

VDD

K11

VDD

K13

VDD

K15

VDD

K17

VDD

K19

VDD

K21

VDD

K23

VDD

L4

VDD

L5

VDD

L8

VDD

L10

VDD

L12

VDD

L14

VDD

L16

VDD

L18

VDD

L20

VDD

L22

VDD

M2

VDD

M3

VDD

M7

VDD

M9

VDD

M11

VDD

M13

VDD

M15

VDD

M17

VDD

M19

VDD

M21

VDD

M23

VDD

N8

VDD

N10

VDD

N12

VDD

N14

VDD

N16

VDD

N18

VDD

N20

VDD

N22

VDD

P7

VDD

P9

VDD

P11

VDD

P13

VDD

P15

VDD

P17

VDD

P19

VDD

P21

VDD

P23

VDD

R4

VDD

R5

VDD

R8

VDD

R10

VDD

R12

VDD

R14

VDD

R16

VDD

R18

VDD

R20

VDD

R22

VDD

T2

VDD

T3

VDD

T7

VDD

T9

VDD

T11

VDD

T13

VDD

A3

VSS

A7

VSS

A9

VSS

SLOTOCC#

A11

VSS

B4

VSS

B9

VSS

B11

VSS

B14

VSS

B16

VSS

B18

VSS

B20

VSS

B22

VSS

B24

VSS

B26

VSS

B28

VSS

B30

VSS

C3

VSS

D14

VSS

D16

VSS

D18

VSS

D20

VSS

D22

VSS

D24

VSS

D26

VSS

D28

VSS

D30

VSS

E11

VSS

F4

VSS

F14

VSS

F16

VSS

F18

VSS

F20

VSS

F22

VSS

F24

VSS

F26

VSS

F28

VSS

F30

VSS

G9

VSS

G11

VSS

H8

VSS

H10

VSS

H12

VSS

H14

VSS

H16

VSS

H18

VSS

H24

VSS

H26

VSS

H28

VSS

H30

VSS

J4

VSS

J5

VSS

J7

VSS

J9

VSS

J11

VSS

J13

VSS

J15

VSS

J17

VSS

J19

VSS

J21

VSS

J23

VSS

K2

VSS

K3

VSS

K8

VSS

K10

VSS

K12

VSS

K14

VSS

K16

VSS

K18

VSS

K20

VSS

K22

VSS

K24

VSS

K26

VSS

K28

VSS

K30

VSS

L7

VSS

L9

VSS

L11

VSS

L13

VSS

L15

VSS

L17

VSS

L19

VSS

L21

VSS

L23

VSS

M8

VSS

M10

VSS

SLOTOCC# 26

W10

W12

W14

W16

W18

W20

W22

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AC4

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AD2

AD3

AD7

AD9

AD11

AD23

AE10

AE12

AF11

AG4

AG5

AG7

AH2

AH3

CPU1G

CPU1G

VDD

VDD

T15

VDD

T17

VDD

T19

VDD

T21

VDD

T23

VDD

U8

VDD

U10

VDD

U12

VDD

U14

VDD

U16

VDD

U18

VDD

U20

VDD

U22

VDD

V9

VDD

V11

VDD

V13

VDD

V15

VDD

V17

VDD

V19

VDD

V21

VDD

V23

VDD

W4

VDD

W5

VDD

W8

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

Y2

VDD

Y3

VDD

Y7

VDD

Y9

VDD

Y11

VDD

Y13

VDD

Y15

VDD

Y17

VDD

Y19

VDD

Y21

VDD

Y23

VDD

AA8

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

AB7

VDD

AB9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

AF7

VDD

AF9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

M12

VSS

M14

VSS

M16

VSS

M18

VSS

M20

VSS

M22

VSS

N4

VSS

N5

VSS

N7

VSS

N9

VSS

N11

VSS

N13

VSS

N15

VSS

N17

VSS

N19

VSS

N21

VSS

N23

VSS

P2

VSS

P3

VSS

P8

VSS

P10

VSS

P12

VSS

P14

VSS

P16

VSS

P18

VSS

P20

VSS

P22

VSS

R7

VSS

R9

VSS

R11

VSS

R13

VSS

R15

VSS

R17

VSS

R19

VSS

R21

VSS

R23

VSS

T8

VSS

T10

VSS

T12

VSS

T14

VSS

T16

VSS

T18

VSS

T20

VSS

T22

VSS

U4

VSS

U5

VSS

U7

VSS

U9

VSS

U11

VSS

U13

VSS

U15

VSS

U17

VSS

U19

VSS

U21

VSS

U23

VSS

V2

VSS

V3

VSS

V10

VSS

V12

VSS

V14

VSS

V16

VSS

V18

VSS

V20

VSS

V22

VSS

W7

VSS

W9

VSS

W11

VSS

W13

VSS

W15

VSS

W17

VSS

W19

VSS

W21

VSS

W23

VSS

Y8

VSS

Y10

VSS

Y12

VSS

Y14

VSS

Y16

VSS

Y18

VSS

Y20

VSS

Y22

VSS

AA4

VSS

AA5

VSS

AA7

VSS

AA9

VSS

VCCP_NB

C82 22u/6.3V/12C82 22u/6.3V/12

BACK SIDE

C97 0.22u/16V/6C97 0.22u/16V/6

C89 22u/6.3V/12C89 22u/6.3V/12

C84 0.22u/16V/6C84 0.22u/16V/6

C103 4.7u/10V/8C103 4.7u/10V/8C564 103P/16V/4C564 103P/16V/4

VCCP_NB

C563 103P/16V/4C563 103P/16V/4

C113 X_0.1u/10VC113 X_0.1u/10V

C116 X_4.7u/10V/8C116 X_4.7u/10V/8

A4

A6

B5

B7

C6

C8

D7

D9

E8

E10

F9

F11

G10

G12

5

6

7

8

C90 180P/50V/4C90 180P/50V/4

CPU1H

CPU1H

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

VDDNB

GND

GND

GND

GND

C587 22u/6.3V/12C587 22u/6.3V/12

C106 X_1000p/50V/4C106 X_1000p/50V/4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C584 X_22u/6.3V/12C584 X_22u/6.3V/12

C580 X_22u/6.3V/12C580 X_22u/6.3V/12

C93 X_1000p/50V/4C93 X_1000p/50V/4

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

VTT_DDRVTT_DDR

C572 22u/6.3V/12C572 22u/6.3V/12

C577 22u/6.3V/12C577 22u/6.3V/12

C225 0.22u/16V/6C225 0.22u/16V/6

C589 0.22u/16V/6C589 0.22u/16V/6

C228 0.22u/16V/6C228 0.22u/16V/6

C601 0.22u/16V/6C601 0.22u/16V/6

C219 4.7u/10V/8C219 4.7u/10V/8

C206 X_4.7u/10V/8C206 X_4.7u/10V/8

C582 X_0.1u/10VC582 X_0.1u/10V

C215 180P/50V/4C215 180P/50V/4

VCC_DDR

C598 180P/50V/4C598 180P/50V/4

C212 1000p/50V/4C212 1000p/50V/4

VCC1_2HT

C593 X_22u/6.3V/12C593 X_22u/6.3V/12

AJ1

AJ2

AJ3

AJ4

A12

B12

C12

D12

M24

M26

M28

M30

P24

P26

P28

P30

T24

T26

T28

T30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

C578 22u/6.3V/12C578 22u/6.3V/12

CPU1I

CPU1I

IO PWR

IO PWR

VLDT_A

VLDT_A

VLDT_A

VLDT_A

VTT

VTT

VTT

VTT

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

C581 22u/6.3V/12C581 22u/6.3V/12

C585 X_4.7u/10V/8C585 X_4.7u/10V/8

BACK SIDEBACK SIDE BACK SIDE

VCCP_NB VCC1_2HT

C122 10u/16V/12C122 10u/16V/12

C208 1000p/50V/4C208 1000p/50V/4

C115 10u/16V/12C115 10u/16V/12

C123 0.22u/16V/6C123 0.22u/16V/6

C114 0.22u/16V/6C114 0.22u/16V/6

VLDT_B

VLDT_B

VLDT_B

VLDT_B

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C94 4.7u/10V/8C94 4.7u/10V/8

VTT

VTT

VTT

VTT

VTT

C118 103P/16V/4C118 103P/16V/4

H1

H2

H5

H6

AG12

AH12

AJ12

AK12

AL12

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

AK20

AK22

AK24

AK26

AK28

AK30

AL5

C594 0.22u/16V/6C594 0.22u/16V/6

VLDT_RUN_B

C602 0.22u/16V/6C602 0.22u/16V/6

C573 0.22u/16V/6C573 0.22u/16V/6

C217 4.7u/10V/8C217 4.7u/10V/8

VTT_DDRVTT_DDR

C588 0.22u/16V/6C588 0.22u/16V/6

C220 4.7u/10V/8C220 4.7u/10V/8

C150

C150

4.7u/10V/8

4.7u/10V/8

C214 0.22u/16V/6C214 0.22u/16V/6

C98 103P/16V/4C98 103P/16V/4

C207 180P/50V/4C207 180P/50V/4

C221 180P/50V/4C221 180P/50V/4

VCCPVCCP VCC_DDR

C571 X_22u/6.3V/12C571 X_22u/6.3V/12

BACK SIDE

C579 22u/6.3V/12C579 22u/6.3V/12

C576 X_22u/6.3V/12C576 X_22u/6.3V/12

C586 22u/6.3V/12C586 22u/6.3V/12

C583 X_22u/6.3V/12C583 X_22u/6.3V/12

C597 22u/6.3V/12C597 22u/6.3V/12

C599 22u/6.3V/12C599 22u/6.3V/12

C592 22u/6.3V/12C592 22u/6.3V/12

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7374

MS-7374

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Monday, September 03, 2007

Date:

Monday, September 03, 2007

Date:

5

4

3

2

Monday, September 03, 2007

MS-7374

AM2+ POWER & GND

AM2+ POWER & GND

AM2+ POWER & GND

Sheet of

Sheet of

Sheet of

1

0A

0A

0A

537

537

537

5

4

3

2

1

MEM_MA_DQS_H[7..0]4

MEM_MA_DQS_L[7..0]4

DIMM1 / A0 DIMM3 / A1

D D

MEM_MA_DATA[63..0]4

C C

B B

A A

D11

D11

BAV99-7-F_SOT23-LF

BAV99-7-F_SOT23-LF

3

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

3VDUAL3VDUAL

2

2

3

BAV99-7-F_SOT23-LF

BAV99-7-F_SOT23-LF

1

1

5

DDRII-240_GREEN-RH

DDRII-240_GREEN-RH

D10

D10

SMB_MEM_CLKSMB_MEM_DATA

3

4

9

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

VCC_DDR VCC3 VCC3

55

DIMM1

DIMM1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

19

68

102

NC

RC118RC0

NC#19

NC/TEST

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

VDD051VDD156VDD262VDD372VDD478VDD5

VSS

VSS

VSS

VSS

115

118

121

124

127

191

194

181

75

VDD6

VDD3

VSS

VSS

VSS

VSS

VSS

130

133

136

139

142

ADDRESS=000

0xA0

VDD7

VSS

175

170

VDD8

VSS

145

148

VDDQ0

VDDQ153VDDQ259VDDQ364VDDQ4

VSS

VSS

VSS

151

154

197

VSS

VSS

157

160

163

172

187

184

178

VDDQ5

VDDQ6

VDDQ7

VDDQ469VDDQ7

VSS

VSS

VSS

VSS

VSS

166

169

198

201

189

204

VDDQ8

VSS

67

207

VDDQ9

VSS

238

CB042CB143CB248CB349CB4

VDDSPD

VSS

VSS

VSS

VSS

VSS

210

213

216

219

222

4

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK1#(CK0#)

VSS

VSS

225

228

161

162

167

CB5

CB6

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

A10_AP

A16/BA2

CAS#

RAS#

DM0/DQS9

NC/DQS9#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

CK0(DU)

CK0#(DU)

CK1(CK0)

CK2(DU)

CK2#(DU)

VREF

VSS

VSS

VSS

231

234

237

MEM_MA_CHECK0

MEM_MA_CHECK1

MEM_MA_CHECK2

MEM_MA_CHECK3

MEM_MA_CHECK4

MEM_MA_CHECK5

MEM_MA_CHECK6

MEM_MA_CHECK7

168

CB7

MEM_MA_DQS_H0

7

MEM_MA_DQS_L0

6

MEM_MA_DQS_H1

16

MEM_MA_DQS_L1

15

MEM_MA_DQS_H2

28

MEM_MA_DQS_L2

27

MEM_MA_DQS_H3

37

MEM_MA_DQS_L3

36

MEM_MA_DQS_H4

84

MEM_MA_DQS_L4

83

MEM_MA_DQS_H5

93

MEM_MA_DQS_L5

92

MEM_MA_DQS_H6

105

MEM_MA_DQS_L6

104

MEM_MA_DQS_H7

114

MEM_MA_DQS_L7

113

46

45

X3

X3

MEM_MA_ADD0

188

A0

MEM_MA_ADD1

183

A1

MEM_MA_ADD2

63

A2

MEM_MA_ADD3

182

A3

MEM_MA_ADD4

61

A4

MEM_MA_ADD5

60

A5

MEM_MA_ADD6

180

A6

MEM_MA_ADD7

58

A7

MEM_MA_ADD8

179

A8

MEM_MA_ADD9

177

A9

MEM_MA_ADD10

70

MEM_MA_ADD11

57

A11

MEM_MA_ADD12

176

A12

MEM_MA_ADD13

196

A13

MEM_MA_ADD14

174

A14

MEM_MA_ADD15

173

A15

54

190

BA1

71

BA0

73

WE#

74

192

MEM_MA_DM0

125

126

MEM_MA_DM1

134

135

MEM_MA_DM2

146

147

MEM_MA_DM3

155

156

MEM_MA_DM4

202

203

MEM_MA_DM5

211

212

MEM_MA_DM6

223

224

MEM_MA_DM7

232

233

164

165

195

77

52

171

193

76

185

186

137

138

220

221

120

SCL

119

SDA

X1

X1

VDDR_VREF VDDR_VREF

1

X2

X2

239

SA0

240

SA1

101

SA2

MEM_MA_CHECK[7..0] 4

MEM_MA_DQS_H8 4

MEM_MA_DQS_L8 4

MEM_MA_ADD[15..0] 4,8

MEM_MA_BANK2 4,8

MEM_MA_BANK1 4,8

MEM_MA_BANK0 4,8

MEM_MA_WE_L 4,8

MEM_MA_CAS_L 4,8

MEM_MA_RAS_L 4,8

MEM_MA_DM[7..0] 4

MEM_MA_DM8 4

MEM_MA0_ODT0 4,8

MEM_MA_CKE0 4,8

MEM_MA0_CS_L0 4,8

MEM_MA0_CS_L1 4,8

MEM_MA0_CLK_H0 4,8

MEM_MA0_CLK_L0 4,8

MEM_MA0_CLK_H1 4,8

MEM_MA0_CLK_L1 4,8

MEM_MA0_CLK_H2 4,8

MEM_MA0_CLK_L2 4,8

SMB_MEM_CLK 7,14

SMB_MEM_DATA 7,14

VDDR_VREF

C68

C68

0.1u/25V/4

0.1u/25V/4

56.2RST/4

56.2RST/4

56.2RST/4

56.2RST/4

VCC_DDR

R102

R102

R101

R101

MEM_MA_DATA[63..0]4

0.1u/25V/4

0.1u/25V/4

C78

C78

0.1u/25V/4

0.1u/25V/4

3

VDDR_VREF

C77

C77

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

DDRII-240_GREEN-RH

DDRII-240_GREEN-RH

VDDR_VREF

Layout: Place within 500 mils

of the DIMM-B1 socket.

C76

C76

1000p/50V/4

1000p/50V/4

MEM_MA_CHECK0

MEM_MA_CHECK1

MEM_MA_CHECK2

MEM_MA_CHECK3

MEM_MA_CHECK4

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK1#(CK0#)

VSS

VSS

225

228

161

162

167

CB5

CB6

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

A10_AP

A16/BA2

WE#

CAS#

RAS#

DM0/DQS9

NC/DQS9#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

CK0(DU)

CK0#(DU)

CK1(CK0)

CK2(DU)

CK2#(DU)

VREF

VSS

VSS

VSS

231

234

237

MEM_MA_CHECK5

MEM_MA_CHECK6

MEM_MA_CHECK7

168

CB7

MEM_MA_DQS_H0

7

MEM_MA_DQS_L0

6

MEM_MA_DQS_H1

16

MEM_MA_DQS_L1

15

MEM_MA_DQS_H2

28

MEM_MA_DQS_L2

27

MEM_MA_DQS_H3

37

MEM_MA_DQS_L3

36

MEM_MA_DQS_H4

84

MEM_MA_DQS_L4

83

MEM_MA_DQS_H5

93

MEM_MA_DQS_L5

92

MEM_MA_DQS_H6

105

MEM_MA_DQS_L6

104

MEM_MA_DQS_H7MEM_MA_DATA15

114

MEM_MA_DQS_L7

113

46

45

X3

X3

MEM_MA_ADD0

188

A0

MEM_MA_ADD1

183

A1

MEM_MA_ADD2

63

A2

MEM_MA_ADD3

182

A3

MEM_MA_ADD4

61

A4

MEM_MA_ADD5

60

A5

MEM_MA_ADD6

180

A6

MEM_MA_ADD7

58

A7

MEM_MA_ADD8

179

A8

MEM_MA_ADD9

177

A9

MEM_MA_ADD10

70

MEM_MA_ADD11

57

A11

MEM_MA_ADD12

176

A12

MEM_MA_ADD13

196

A13

MEM_MA_ADD14

174

A14

MEM_MA_ADD15

173

A15

54

190

BA1

71

BA0

73

74

192

MEM_MA_DM0

125

126

MEM_MA_DM1

134

135

MEM_MA_DM2

146

147

MEM_MA_DM3

155

156

MEM_MA_DM4

202

203

MEM_MA_DM5

211

212

MEM_MA_DM6

223

224

MEM_MA_DM7

232

233

164

165

195

77

52

171

193

76

185

186

137

138

220

221

120

SCL

119

SDA

X1

X1

1

X2

X2

239

SA0

240

SA1

101

SA2

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Monday, September 03, 2007

Date:

Monday, September 03, 2007

Date:

Monday, September 03, 2007

VCC_DDR

55

19

68

102

DIMM3

DIMM3

3

RC118RC0

DQ0

4

NC#19

DQ1

9

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NC/TEST

VSS

VSS

VSS

VSS

100

103

106

109

112

NC

VDD051VDD156VDD262VDD372VDD478VDD5

VSS

VSS

VSS

VSS

115

118

121

124

191

75

VDD3

VSS

VSS

VSS

VSS

127

130

133

136

194

181

175

170

197

VDD6

VDD7

VDD8

VDDQ0

VDDQ153VDDQ259VDDQ364VDDQ4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

139

142

145

148

151

154

157

160

ADDRESS=010

0xA4

2

172

187

184

VDDQ5

VDDQ6

VDDQ7

VDDQ469VDDQ7

VSS

VSS

VSS

VSS

163

166

169

198

238

189

67

178

CB042CB143CB248CB349CB4

VDDQ8

VDDQ9

VDDSPD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

201

204

207

210

213

216

219

222

MEM_MA_CHECK[7..0] 4

MEM_MA_DQS_H8 4

MEM_MA_DQS_L8 4

MEM_MA_ADD[15..0] 4,8

MEM_MA_BANK2 4,8

MEM_MA_BANK1 4,8

MEM_MA_BANK0 4,8

MEM_MA_WE_L 4,8

MEM_MA_CAS_L 4,8

MEM_MA_RAS_L 4,8

MEM_MA_DM[7..0] 4

MEM_MA_DM8 4

MEM_MA1_ODT0 4,8

MEM_MA_CKE1 4,8

MEM_MA1_CS_L0 4,8

MEM_MA1_CS_L1 4,8

MEM_MA1_CLK_H0 4,8

MEM_MA1_CLK_L0 4,8

MEM_MA1_CLK_H1 4,8

MEM_MA1_CLK_L1 4,8

MEM_MA1_CLK_H2 4,8

MEM_MA1_CLK_L2 4,8

SMB_MEM_CLK 7,14

SMB_MEM_DATA 7,14

VDDR_VREF

C70

C70

0.1u/25V/4

VCC3

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

0.1u/25V/4

MS-7374

MS-7374

MS-7374

AM2+ DIMM1/3

AM2+ DIMM1/3

AM2+ DIMM1/3

1

637

637

637

Sheet of

Sheet of

Sheet of

0A

0A

0A

5

4

3

2

1

MEM_MB_DQS_H[7..0]4

MEM_MB_DQS_L[7..0]4

DIMM2 / B0

197

172

187

VDDQ5

VDDQ469VDDQ7

VSS

VSS

VSS

160

163

166

169

VDDQ6

VSS

184

198

VDDQ7

VSS

VCC3

238

189

67

178

CB042CB143CB248CB349CB4

VDDQ8

VDDQ9

VDDSPD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

201

204

207

210

213

216

219

222

D D

MEM_MB_DATA[63..0]4

C C

B B

A A

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

DDRII-240_ORANGE-RH

DDRII-240_ORANGE-RH

3

4

9

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

VCC_DDR VCC3

55

DIMM2

DIMM2

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

19

68

102

NC

RC118RC0

NC#19

NC/TEST

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

VDD051VDD156VDD262VDD372VDD478VDD5

VSS

VSS

VSS

VSS

115

118

121

124

127

191

194

181

175

75

170

VDD6

VDD7

VDD8

VDD3

VDDQ0

VDDQ153VDDQ259VDDQ364VDDQ4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

130

133

136

139

142

145

148

151

154

157

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK1#(CK0#)

VSS

VSS

225

228

161

162

167

CB5

CB6

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

A10_AP

A16/BA2

CAS#

RAS#

DM0/DQS9

NC/DQS9#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

CK0(DU)

CK0#(DU)

CK1(CK0)

CK2(DU)

CK2#(DU)

VREF

VSS

VSS

VSS

231

234

237

MEM_MB_CHECK0

MEM_MB_CHECK1

MEM_MB_CHECK2

MEM_MB_CHECK3

MEM_MB_CHECK4

MEM_MB_CHECK5

MEM_MB_CHECK6

MEM_MB_CHECK7

168

CB7

MEM_MB_DQS_H0

7

MEM_MB_DQS_L0

6

MEM_MB_DQS_H1

16

MEM_MB_DQS_L1

15

MEM_MB_DQS_H2

28

MEM_MB_DQS_L2

27

MEM_MB_DQS_H3

37

MEM_MB_DQS_L3

36

MEM_MB_DQS_H4

84

MEM_MB_DQS_L4

83

MEM_MB_DQS_H5

93

MEM_MB_DQS_L5

92

MEM_MB_DQS_H6

105

MEM_MB_DQS_L6

104

MEM_MB_DQS_H7

114

MEM_MB_DQS_L7

113

46

45

X3

X3

MEM_MB_ADD0

188

A0

MEM_MB_ADD1

183

A1

MEM_MB_ADD2

63

A2

MEM_MB_ADD3

182

A3

MEM_MB_ADD4

61

A4

MEM_MB_ADD5

60

A5

MEM_MB_ADD6

180

A6

MEM_MB_ADD7

58

A7

MEM_MB_ADD8

179

A8

MEM_MB_ADD9

177

A9

MEM_MB_ADD10

70

MEM_MB_ADD11

57

A11

MEM_MB_ADD12

176

A12

MEM_MB_ADD13

196

A13

MEM_MB_ADD14

174

A14

MEM_MB_ADD15

173

A15

54

190

BA1

71

BA0

73

WE#

74

192

MEM_MB_DM0

125

126

MEM_MB_DM1

134

135

MEM_MB_DM2

146

147

MEM_MB_DM3

155

156

MEM_MB_DM4

202

203

MEM_MB_DM5

211

212

MEM_MB_DM6

223

224

MEM_MB_DM7

232

233

164

165

195

77

52

171

193

76

185

186

137

138

220

221

120

SCL

119

SDA

X1

X1

VDDR_VREF VDDR_VREF

1

X2

X2

239

SA0

240

SA1

101

SA2

MEM_MB_CHECK[7..0] 4

MEM_MB_DQS_H8 4

MEM_MB_DQS_L8 4

MEM_MB_ADD[15..0] 4,8

MEM_MB_BANK2 4,8

MEM_MB_BANK1 4,8

MEM_MB_BANK0 4,8

MEM_MB_WE_L 4,8

MEM_MB_CAS_L 4,8

MEM_MB_RAS_L 4,8

MEM_MB_DM[7..0] 4

MEM_MB_DM8 4

MEM_MB0_ODT0 4,8

MEM_MB_CKE0 4,8

MEM_MB0_CS_L0 4,8

MEM_MB0_CS_L1 4,8

MEM_MB0_CLK_H0 4,8

MEM_MB0_CLK_L0 4,8

MEM_MB0_CLK_H1 4,8

MEM_MB0_CLK_L1 4,8

MEM_MB0_CLK_H2 4,8

MEM_MB0_CLK_L2 4,8

SMB_MEM_CLK 6,14

SMB_MEM_DATA 6,14

VDDR_VREF

C69

C69

0.1u/25V/4

0.1u/25V/4

MEM_MB_CHECK[7..0] 4

MEM_MB_CHECK0

MEM_MB_CHECK1

DM1/DQS10

DM2/DQS11

DM3/DQS12

DM4/DQS13

DM5/DQS14

DM6/DQS15

DM7/DQS16

DM8/DQS17

CK1#(CK0#)

VSS

VSS

225

228

161

162

167

CB5

CB6

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

A10_AP

A16/BA2

CAS#

RAS#

DM0/DQS9

NC/DQS9#

NC/DQS10#

NC/DQS11#

NC/DQS12#

NC/DQS13#

NC/DQS14#

NC/DQS15#

NC/DQS16#

NC/DQS17#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

CK0(DU)

CK0#(DU)

CK1(CK0)

CK2(DU)

CK2#(DU)

VREF

VSS

VSS

VSS

231

234

237

MEM_MB_CHECK2

MEM_MB_CHECK3

MEM_MB_CHECK4

MEM_MB_CHECK5

MEM_MB_CHECK6

MEM_MB_CHECK7

168

CB7

7

6

16

15

28

27

37

36

84

83

93

92

105

104

114

113

46

45

X3

X3

188

A0

183

A1

63

A2

182

A3

61

A4

60

A5

180

A6

58

A7

179

A8

177

A9

70

57

A11

176

A12

196

A13

174

A14

173

A15

54

190

BA1

71

BA0

73

WE#

74

192

125

126

134

135

146

147

155

156

202

203

211

212

223

224

232

233

164

165

195

77

52

171

193

76

185

186

137

138

220

221

120

SCL

119

SDA

X1

X1

1

X2

X2

239

SA0

240

SA1

101

SA2

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

VCC3VCC3

MEM_MB_DQS_H8 4

MEM_MB_DQS_L8 4

MEM_MB_ADD[15..0] 4,8

MEM_MB_BANK2 4,8

MEM_MB_BANK1 4,8

MEM_MB_BANK0 4,8

MEM_MB_WE_L 4,8

MEM_MB_CAS_L 4,8

MEM_MB_RAS_L 4,8

MEM_MB_DM[7..0] 4

MEM_MB_DM8 4

MEM_MB1_ODT0 4,8

MEM_MB_CKE1 4,8

MEM_MB1_CS_L0 4,8

MEM_MB1_CS_L1 4,8

MEM_MB1_CLK_H0 4,8

MEM_MB1_CLK_L0 4,8

MEM_MB1_CLK_H1 4,8

MEM_MB1_CLK_L1 4,8

MEM_MB1_CLK_H2 4,8

MEM_MB1_CLK_L2 4,8

SMB_MEM_CLK 6,14

SMB_MEM_DATA 6,14

VDDR_VREF

C73

C73

0.1u/25V/4

0.1u/25V/4

DIMM4 / B1

VCC_DDR

55

19

68

102

DIMM4

MEM_MB_DATA[63..0]4

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

DDRII-240_ORANGE-RH

DDRII-240_ORANGE-RH

DIMM4

3

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

21

DQ10

22

DQ11

131

DQ12

132

DQ13

140

DQ14

141

DQ15

24

DQ16

25

DQ17

30

DQ18

31

DQ19

143

DQ20

144

DQ21

149

DQ22

150

DQ23

33

DQ24

34

DQ25

39

DQ26

40

DQ27

152

DQ28

153

DQ29

158

DQ30

159

DQ31

80

DQ32

81

DQ33

86

DQ34

87

DQ35

199

DQ36

200

DQ37

205

DQ38

206

DQ39

89

DQ40

90

DQ41

95

DQ42

96

DQ43

208

DQ44

209

DQ45

214