Page 1

8

7

6

5

4

3

2

1

Version 0A

MS-7061

D D

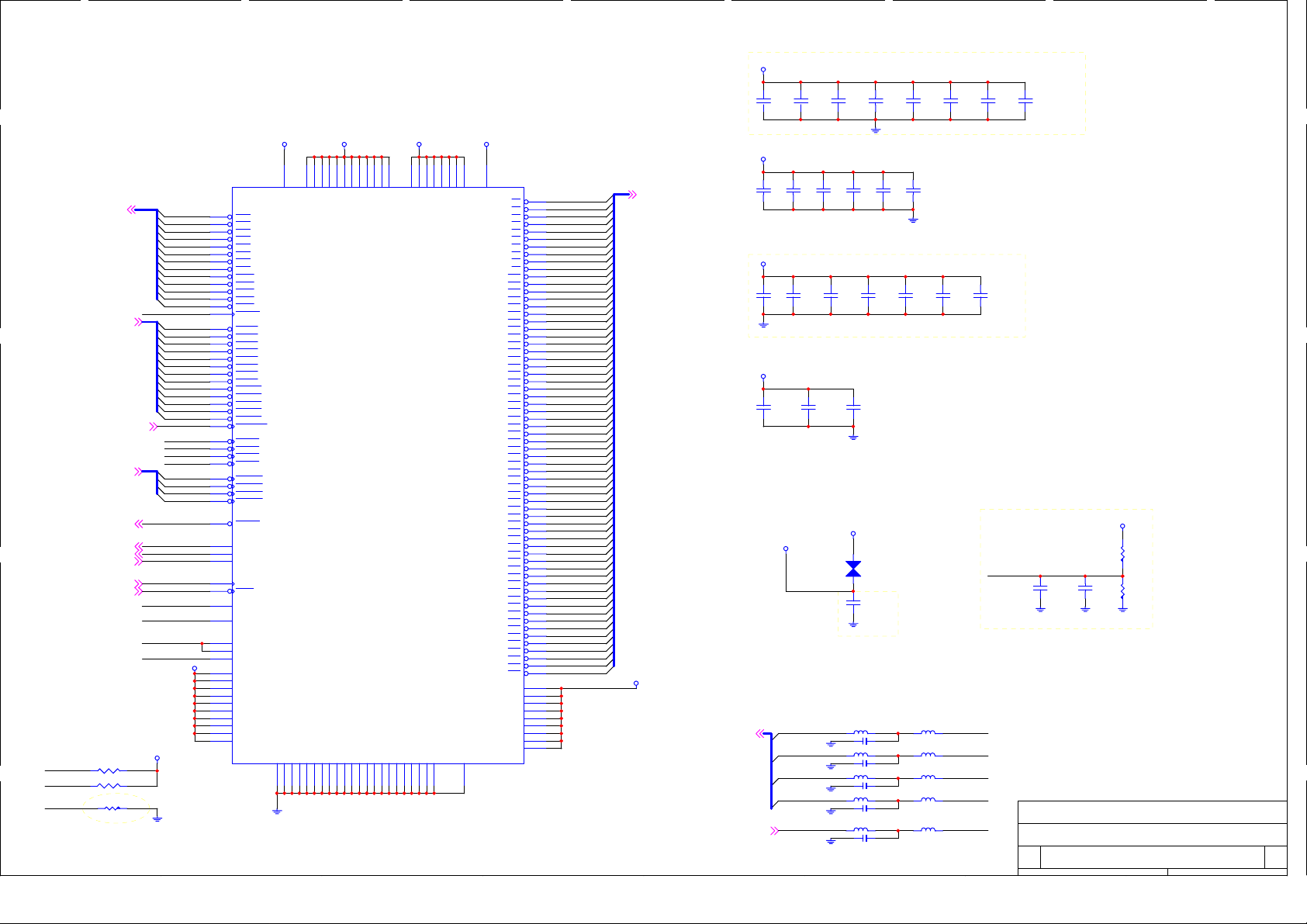

VIA (R) KM266 / VT8237 Chipset

AMD PGA 462 Processor Schematic s

02/10/2004 Update

*AMD PGA 462 Processor

*VIA KM266 / VT8237 Chipset

(DDR 333 / AGP 4X / VLink 4X)

*Winbond 83697HF-VF LPC I/O

*VT6103 PHY 10 / 100

*AC'97 Codec VIA1617A Codec

*USB 2.0 support (integrated into VT8237)

C C

*AGP SLOT * 1 ( 4X )

*PCI SLOT * 3

*DDR DIMM * 2

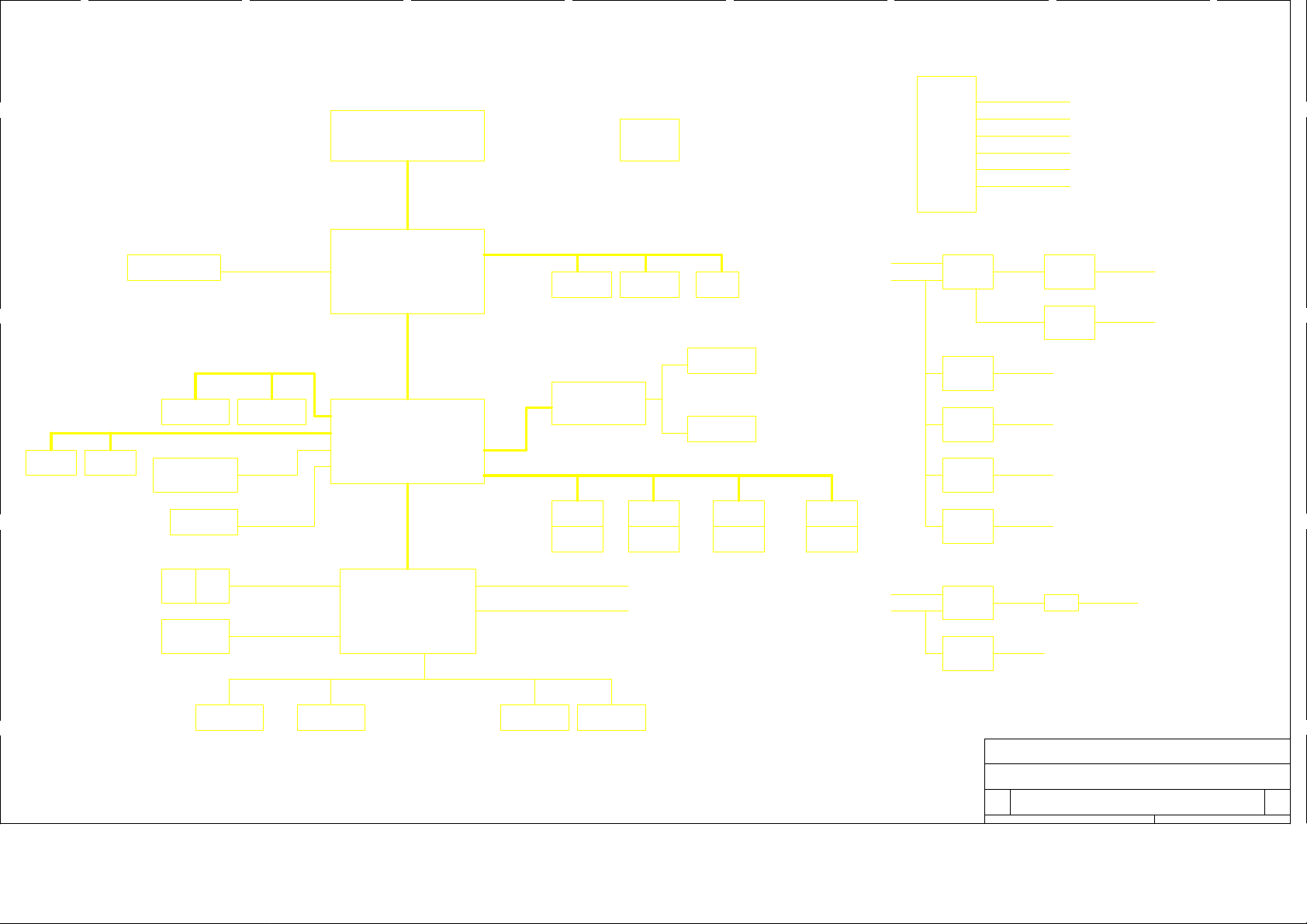

Cover Sheet

Block Diagram

CLOCK GEN

AMD CPU Sockets 462

Via KM266 North Bridge

DDR SLOT

DDR TERMINATOR

AGP SLOT

Via VT8237 South Bridge

PCI SLOTS

KB/MS & Rear I/O

VIA VT6103 LAN PHY

IDE CONNECTOR

USB CONNECTOR

AC'97 CODEC

LPC I/O(W83697HF)

H/W MONITOR,ROM,Thermal-Protect

Fan Control & PWROK circuit

1

2

3

4 - 5

6 - 8

9

10

11

12 - 14

15

16

17

18

19

20

21

22

23

VRM 9.X

B B

ACPI Controller, Regulators

Front Panel,ATX connector & VGA Connector

Decoupling Capacitor

24

25

26

27

28

A A

MICRO-STAR INT'L CO.,LTD.

Title

COVER PAGE

Size Document Number Rev

MS-7061 100

Custom

8

7

6

5

4

3

Date: Sheet

2

of

129Tuesday, February 24, 2004

1

Page 2

8

7

6

5

4

3

2

1

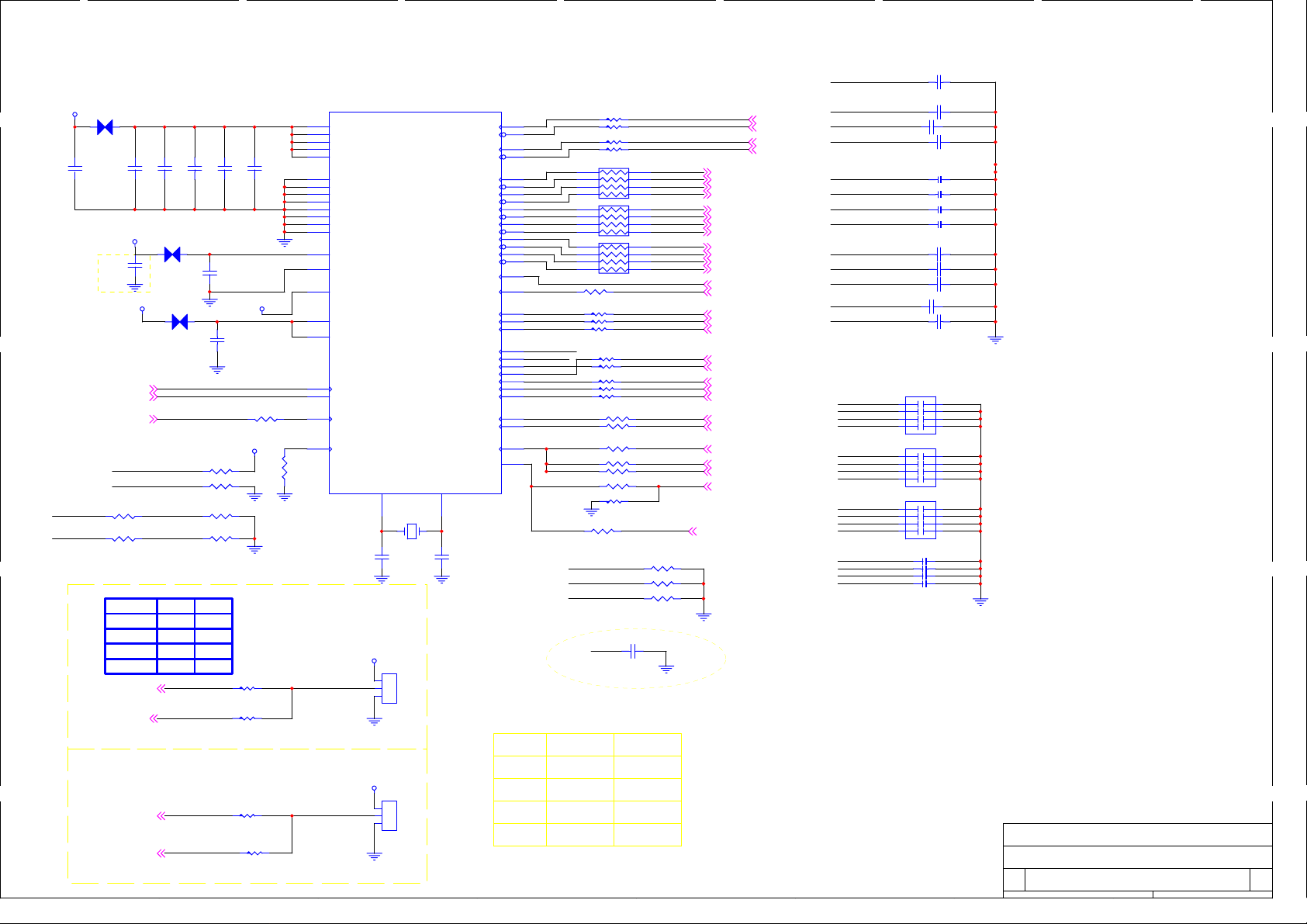

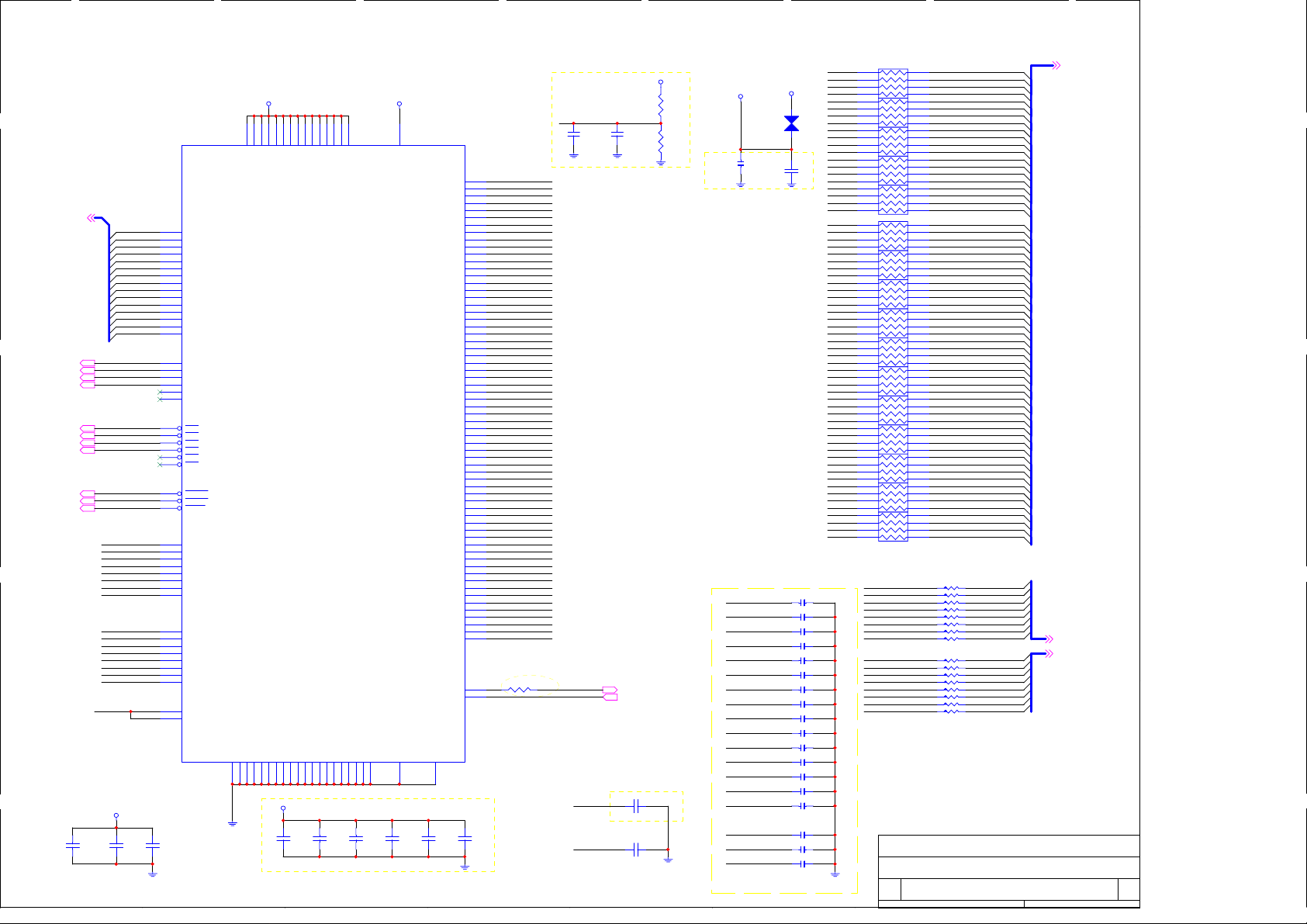

System Block Diagram

D D

SOCKET-462

Host Bus

AGP Connector

C C

PCI SLOT 2 PCI SLOT 1

AGP CONNECTOR

VIA KM266

V-Link

Host CLK

DDR SDRAM

DIMM 1 DIMM 2

Audio Codec

AC'97

Mem. CLK

SSTL-2 Termination

(Only for DDR)

PCI CLK

AGP CLK

Rtt

Analog In

Analog Out

ATX Conn.Clock Gen.

VCC5SBY

VCC3

+ 12V

- 12V

+ 5V

- 5V

3.3V

VCC5SBY

VCC3SBY VCCM

VCC25SBY

VCC5SBY

DDR_VTT

VCC2_5

VIA 8237

IDE 1

B B

IDE 2

/MOUSE

Lan Phy

FAN1FAN

Legacy

ROM

2

PS/2KEYBOARD

FAN CONTROL

FAN CONTROL

LPC Bus

LPC Super I/O

USB 0

USB 1

VOLTAGE MONITOR

TEMPERATURE MONITOR

USB 3

USB 4

USB 5

USB 6

USB 7

USB 8

VCC5SBY

VCC5

VDDQ

VCCA_PLL

5VDUAL

VCORE

USB_5V

GPIOs

SERIAL PARALLEL FLOPPY

A A

MICRO-STAR INT'L CO.,LTD.

Title

System Block Diagram

Size Document Number Rev

MS-7061 100

Custom

229Tuesday, February 24, 2004

8

7

6

5

4

3

Date: Sheet

2

of

1

Page 3

8

7

6

5

4

3

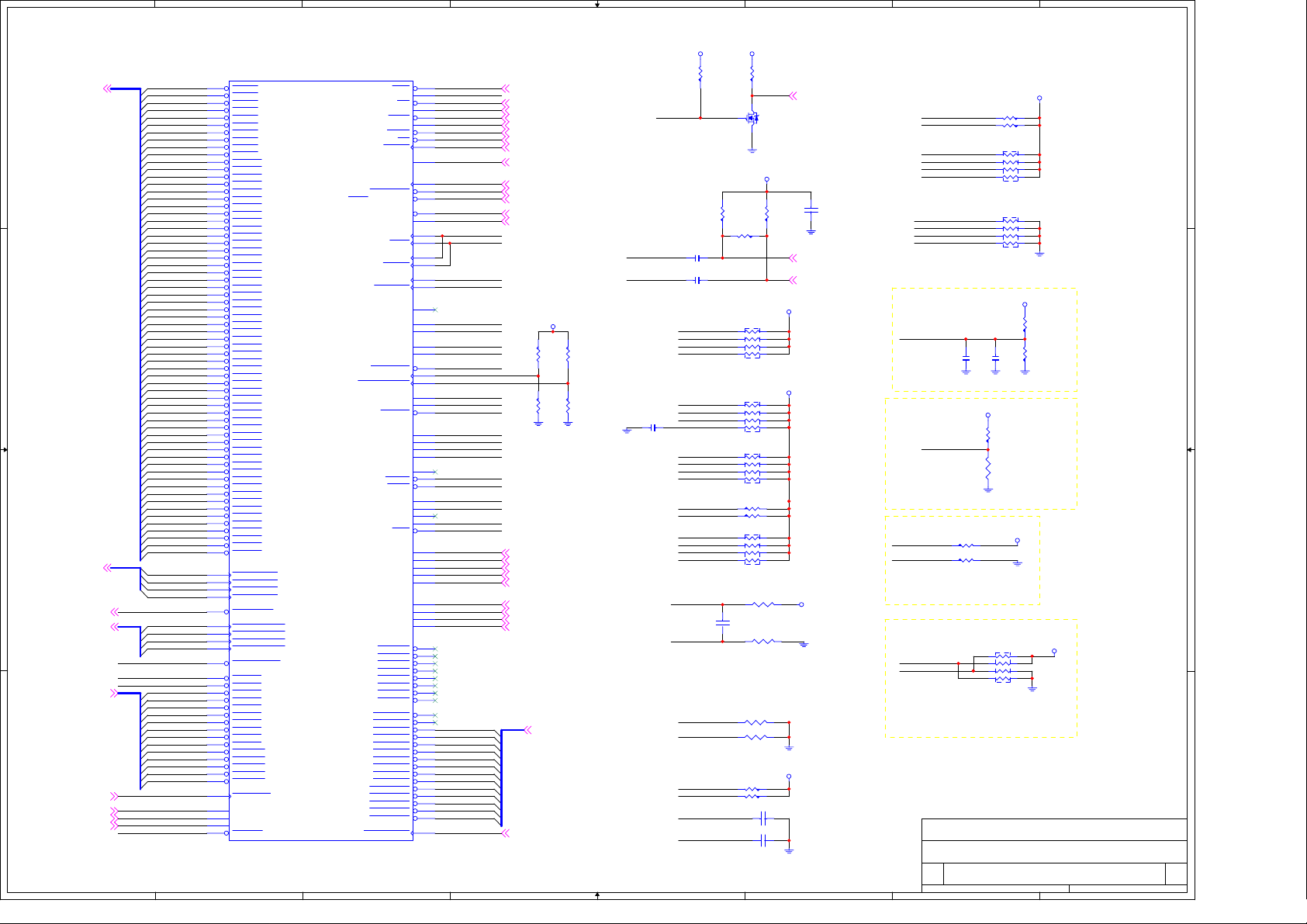

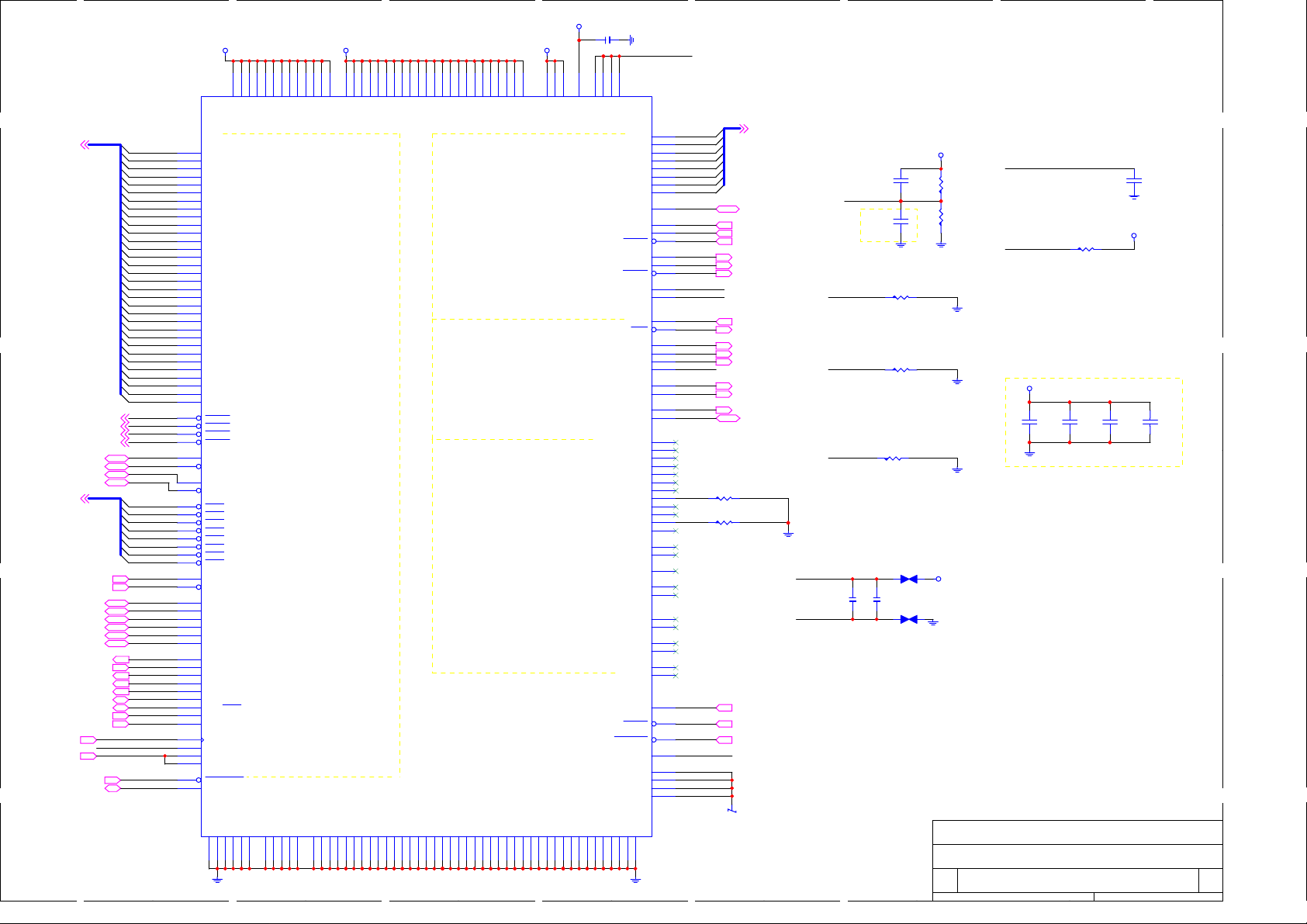

By-Pass Capacitors

Place near to the Clock Outputs

2

1

XIN

3

14.318MHZ32P_D

VCC3

1

2

3

VCC3

SW2

YJ103

1

2

3

Damping Resistors

Place near to the

Clock Outputs

PCICLK0/SEL_SD_DDR#

Y1

C164

18P

SW1

YJ103

6

CPUCLK_PPT

CPUCLK_PPC

CPUCLKST

CPUCLKSC

DDRT0

DDRC0

DDRT1

DDRC1

DDRT2

DDRC2

DDRT3

DDRC3

DDRT4

DDRC4

DDRT5

DDRC5

BUFFER_IN

FBOUT

AGP0/MODE

AGP1/SEL_CPU

AGP2/PCI_STOP#

PCICLK_F/FS1

PCICLK1/MULTSEL0

PCICLK2

PCICLK3

PCICLK4

PCICLK5/CPU_STP#

48M/FS3RESET/PD#

24_48M/FS2

VTT_PWRGD#/REF1

XOUT

4

C165

18P

48

49

53

52

44

43

42

41

38

37

36

35

32

31

30

29

45

46

MODE

6

SELCPU

7

8

10

11

12

14

15

17

18

2026

21

56

8237/8235

100

133

166

200

R184 10

R181 10

R175 10

R176 10

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R186

R185 22R

R187 22R

R190 22R

FS1

SELDDR#

MULTSEL0

FS3

FS2

FS0

REF1

R174

R200

R205

R170

R171

R177

R167

R197 22R

R196 22R

R194 22R

R198 22R

R199 22R

MULTSEL0

SELCPU

SELDDR#

R161 270RST

DCLKO

For EMI Reserved@20030819

PDA2/SDA2 PDA0/SDA0

0

0

1

5

RN638P4R-10R

DDRCLK0

DDRCLK-0

DDRCLK1

DDRCLK-1

DDRCLK2

RN648P4R-10R

DDRCLK-2

DDRCLK3

DDRCLK-3

DDRCLK4

RN658P4R-10R

DDRCLK-4

DDRCLK5

DDRCLK-5

DCLKO

DCLKI

22R

VCLKNB

VCLKSB

AGPCLK1

PCICLK1

PCICLK2

PCICK3

PCLKSB

SIOPCLK

USBCLK

22R

SIO48M

22R

SBCLK14

33R

GCLK14

33R

XTL_IN

33R

62R

APICSB

22R

R195 4.7K

R189 4.7K

R193 4.7K

C179

X_10P

0

1

11

0

APICCPU

HCLK

HCLK#

CPUCLK

CPUCLK#

APICSB <14>

DDRCLK0 <9>

DDRCLK-0 <9>

DDRCLK1 <9>

DDRCLK-1 <9>

DDRCLK2 <9>

DDRCLK-2 <9>

DDRCLK3 <9>

DDRCLK-3 <9>

DDRCLK4 <9>

DDRCLK-4 <9>

DDRCLK5 <9>

DDRCLK-5 <9>

DCLKO <7>

DCLKI <7>

VCLKNB <8>

VCLKSB <14>

AGPCLK1 <11>

PCICLK1 <15>

PCICLK2 <15>

PCICLK3 <15>

PCLKSB <14>

SIOPCLK <22>

USBCLK <12>

SIO48M <22>

SBCLK14 <13>

GCLK14 <8>

XTL_IN <21>

APICCPU <4>

4

HCLK <6>

HCLK# <6>

CPUCLK <4>

CPUCLK# <4>

Main Clock Generator

VCC3

CE1

4.7u

FS1_S

FS0_S

CP7

X_COPPER

C157

R192 10K

R169 10K

CB66

CB64

1u

1u

VCC3

CP12

X_COPPER

X_0.1u

VCC2_5 VCC2_5

CP11

X_COPPER

SMBCLK<9,13,26>

SMBDAT<9,13,26>

FP_RST#<24,26,27>

FS3

FS2

FS1

FS0

CB69

1u

R191

X_2.7K

R178

X_4.7K

CB68

1u

CB78

0.1u

VADDR25

CB70

1u

R201 X_0

VCC3

R2024.7K

R2044.7K

CB67

0.1u

D D

Reserved for

EMI(near R3)

C C

B B

SW2

SW1

FS0FS1

0

100MHz

133MHz

166MHz

200MHz

0

0

1

1

1

1

0

SDA2<13,18>

PDA2<13,18>

R341 X_820

R340 2.2K

A A

R342 X_820

SDA0<13,18>

PDA0<13,18>

8

SDA0

R339 2.2K

7

U7

ICS950910

5

VDDAGP

16

VDDPCI

22

VDD48M

51

VDDCPU

55

VDDREF

2

GND2

9

GND9

13

GND13

19

GND48M

33

GND33

39

GND39

47

GNDI

54

GND54

23

AVDD

24

AGND

50

VDDI

34

VDD3.3/2.5-34

40

VDD3.3/2.5-40

27

SCLK

28

SDATA

25 1

IREF REF0/FS0

R203

475R1%

FS1_SSDA2

FS0_S

DCLKI

VCLKNB

VCLKSB

AGPCLK1

PCICLK2

PCICLK1

PCLKSB

SIOPCLK

APICCPU

APICSB

SBCLK14

USBCLK

SIO48M

By-Pass Capacitors

Place near to the Clock Buffer

DDRCLK0

DDRCLK-0

DDRCLK1

DDRCLK-1

DDRCLK2

DDRCLK-2

DDRCLK3

DDRCLK-3

DDRCLK4

DDRCLK-4

DDRCLK5

DDRCLK-5

CPUCLK

CPUCLK#

HCLK#

HCLK

C177 X_10P

C197 10P

CN8 8P4C-10P50N

1 2

3 4

5 6

7 8

CN10 8P4C-10P50N

1 2

3 4

5 6

7 8

CN12 8P4C-10P50N

1 2

3 4

5 6

7 8

3

C171 X_10P

C174 X_10P

C181 X_10P

X_10PC183

X_10PC185

X_10PC187

X_10PC196

C156 X_10P

C162 10P

C169 10P

C204 10P

10PC160

10PC161

22PC166

22PC167

MICRO-STAR INT'L CO.,LTD.

Title

CLOCK GEN

Size Document Number Rev

MS-7061 100

Custom

Date: Sheet

2

329Wednesday, February 25, 2004

of

1

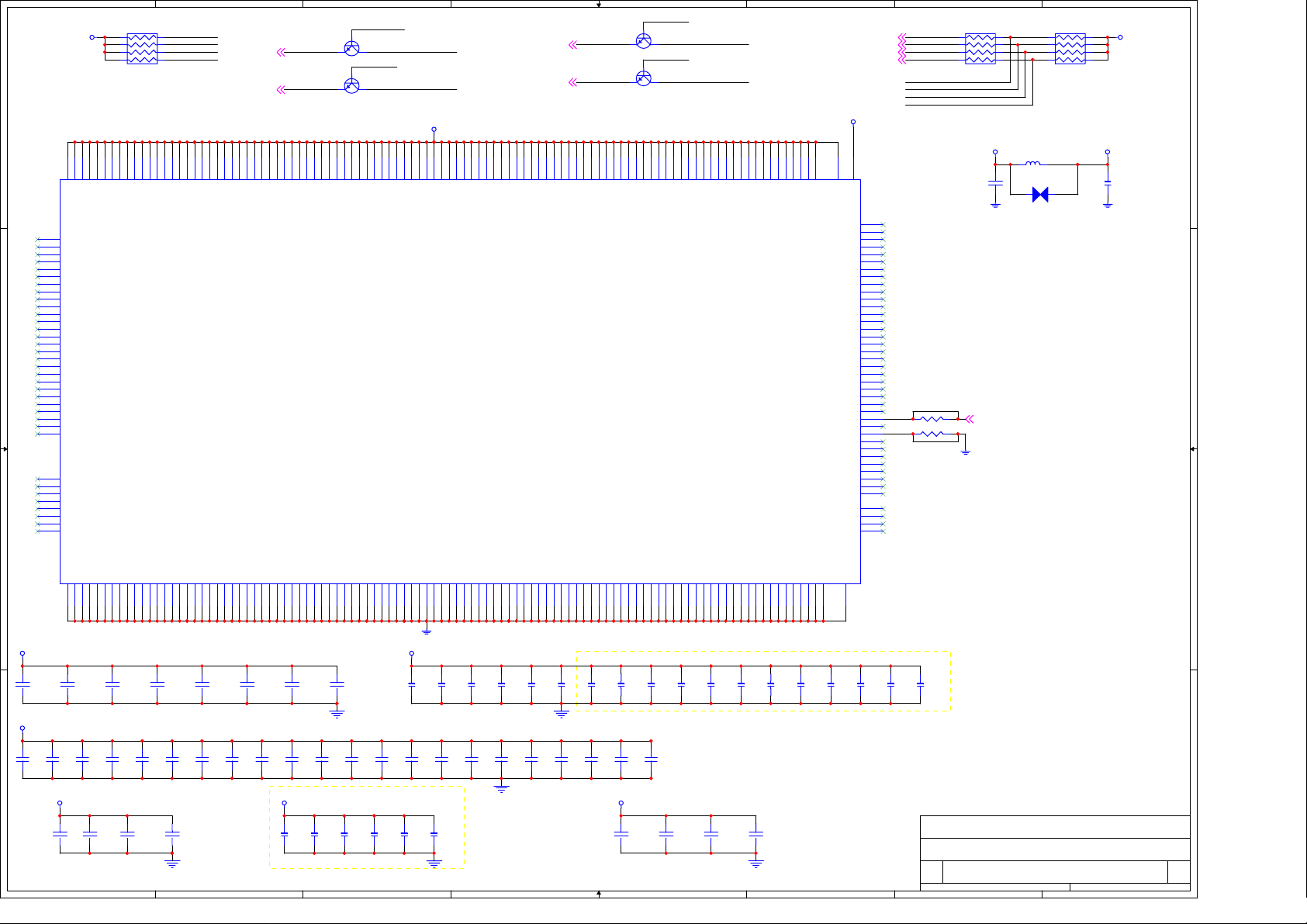

Page 4

8

7

6

5

4

3

2

1

R23

680R1%

G

R93

R94

301R1%

C97

C98

1 2

3 4

5 6

7 8

8P4R-330R

RN7 8P4R-680R

1 2

3 4

5 6

7 8

RN6 8P4R-680R

1 2

3 4

5 6

7 8

R74 56R

R78 56R

RN32 8P4R-680R

1 2

3 4

5 6

7 8

R26 10K

C25

X_4.7u

R28 10K

VCC3

RN2

R22

510R

DS

VCORE

R3430RST

R4430RST

Q7

FDV301N

R95

60.4R1%

VCC2_5

VCORE

R100270R

R99270R

VCC2_5

C1556P

C4220p

FERR# <14>

C112

10000p

CPUCLK <3>

CPUCLK# <3>

VCORE

3

VCORE

RN4

1 2

3 4

5 6

7 8

R1510R

R10510R

TRST#

PLLTEST#

DBREQ#

TDI

TMS

TCK

8P4R-510R

SCANCLK1

SINTVAL

SCANCLK2

SSHIFTEN

RN1

1 2

3 4

5 6

7 8

8P4R-270R

CB12

100P

CB9

X_0.1u

VCORE

R49

56R1%

R57

56R1%

0.5 *

VCORE

VREF_SYS

VCORE

for internal

R11

X_1K

VREFMODE

VREFSYS

R12

270R

VREFMODE=Low=No voltage scaling

ZN

R15 40.2R1%

ZP

R16 40.2R1%

match the transmission line

Push-pull compensation circuit

CLKOUT

CLKOUT#

* Trace lengths of CLKOUT

and -CLKOUT are between

2" and 3"

MICRO-STAR INT'L CO.,LTD.

Title

Socket 462 - 1

Size Document Number Rev

MS-7061 100

Custom

Date: Sheet

VCORE

RN27 8P4R-100R

2

VCORE

78

56

34

12

429Thursday, March 25, 2004

of

1

VCORE

CPU1A

A20M

FERR

INTR

IGNNE

RESET

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TCK

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

6

INIT

NMI

SMI

ZN

ZP

TDI

AE1

AG1

AJ3

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

AE5

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

AOUT#2

C7

AOUT#3

A7

AOUT#4

E5

AOUT#5

A5

AOUT#6

E7

AOUT#7

C1

AOUT#8

C5

AOUT#9

C3

AOUT#10

G1

AOUT#11

E1

AOUT#12

A3

AOUT#13

G5

AOUT#14

G3

E3

ZIF-SOCKET462

FERR

NMI_SB

STPCLK#

COREFB#

COREFB

CPUCLK_R

CPUCLK#_R

CLKOUT

CLKOUT#

VREFMODE

VREF_SYS

ZN

ZP

PLLBP#

PLLMON1

PLLMON2

PLLTEST#

SCANCLK1

SCANCLK2

SINTVAL

SSHIFTEN

DBREQ#

FLUSH#

TCK

TDI

TMS

TRST#

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

A20M# <14>

CPUINIT# <14>

INTR <14>

IGNNE# <14>

NMI_SB <14>

CPURST# <26>

SMI# <14>

STPCLK# <14>

PWRGD_CPU <26>

APICCPU <3>

APICD0 <14>

APICD1 <14>

COREFB#

COREFB

VCORE

100R1%

R81

100R1%

R82

VID0 <25>

VID1 <25>

VID2 <25>

VID3 <25>

VID4 <25>

FID0 <5>

FID1 <5>

FID2 <5>

FID3 <5>

AOUT#[2:14] <6>

AOCLK# <6>

5

100R1%

R88

100R1%

R84

FERR

Near socket-A

CPUCLK_R

CPUCLK#_R

X_39PC16

4

60.4R1%

680P

680P

FID3

FID2

FID1

FID0

CPUINIT#

IGNNE#

CPURST#

A20M#

SMI#

NMI_SB

INTR

STPCLK#

PLLMON1

PLLMON2

FLUSH#

AIN#0

AIN#1

PLLBP#

COREFB

COREFB#

DOVAL#

FILVAL#

APICD0

APICD1

CPURST#

PWRGD_CPU

DIVAL#

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

DICLK#0

DICLK#1

DICLK#2

DICLK#3

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

SDATA#[0:63]<6>

D D

C C

B B

DICLK#[0:3]<6>

DIVAL#<6>

DOCLK#[0:3]<6>

DOVAL#

AIN#0

AIN#[2:14]<6>

A A

AICLK#<6>

CFWDRST<6>

CONNECT<6>

PROCRDY<6>

8

AIN#1

CFWDRST

CONNECT

PROCRDY

FILVAL#

AICLK#

AIN#2

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

AA35

W37

W35

U35

U33

AA33

AE37

AC33

AC37

AA37

AC35

Q37

Q35

N37

G33

G37

G35

Q33

N33

N35

C23

C27

C35

C33

C31

C29

C25

C15

C21

C19

C17

W33

AN33

AE35

C37

C11

AL31

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AJ33

AJ21

AL23

AN23

AJ31

Y35

S37

S33

Y37

S35

J33

E37

L33

L37

J37

A37

E35

E31

E29

A27

A25

E21

A23

A35

A29

E23

E17

E13

E11

E9

A13

C9

A9

A21

E19

A11

A17

A15

J35

E27

E15

A33

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

7

Page 5

8

RN9

VCC2_5

7 8

5 6

3 4

1 2

BASS0

BASS1

BASS2

BASS3

8P4R-4.7K

D D

7

FID0<4>

FID1<4>

6

BASS0

B

Q8

NB_FID0

2N3904S

CE

BASS1

B

Q9

NB_FID1

2N3904S

CE

VCORE

5

FID2<4>

FID3<4>

4

BASS2

B

Q12

NB_FID2

2N3904S

CE

BASS3

B

Q13

NB_FID3

2N3904S

CE

3

GPIOC<13>

GPIOA<13>

GPIOB<13>

GPIOD<13>

GPIOC

GPIOA

GPIOB

GPIOD

NB_FID0

NB_FID1

NB_FID2

NB_FID3

2

RN5

8P4R-10KR

1

78

56

34

12

RN8

78

VCC3

56

34

12

8P4R-10KR

VCCA_PLL

VCCA_PLLVCCA_PLL1

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

VCC_CORE6

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

AH30

AH8

AJ9

AK8

AL9

AM8

C C

F30

F8

H10

H28

H30

H32

H6

H8

K30

K8

AJ7

AL7

AN7

G25

G17

G9

N7

Y7

AG7

AG15

AG29

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

AF14

AF18

AF22

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

AF26

AM34

AK36

AK34

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

AK30

AK26

AK22

AK18

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

AK14

AK10

AL5

AH26

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

AM30

AH22

AH18

AH14

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

AH10

AH4

AH2

AF36

VCC_CORE32

VCC_CORE33

VCC_CORE34

VCC_CORE35

AF34

AD6

AM26

AD4

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

AD2

AB36

AB34

AB32Z6Z4Z2X36

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

X34

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VCC_CORE48

AM22

X32V6V4V2T36

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

T34

T32R6R4R2AM18

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

VCC_CORE57

P36

P34

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

VCC_CORE62

P32M4M6M2K36

VCC_CORE63

VCC_CORE64

VCC_CORE65

VCC_CORE66

K34

K32H4H2

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

VCC_CORE71

AM14

F36

F34

F32

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

F28

F24

F20

F16

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

F12

D32

D28

AM10

VCC_CORE80

VCC_CORE81

VCC_CORE82

VCC_CORE83

D24

D20

D16

D12D8D4D2B36

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

B32

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

AM2

B28

B24

B20

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

B16

B12B8B4

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

AJ5

AC7

VCC_Z

NC1

VCC_CORE101

NC2

NC3

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC42

NC43

NC44

NC45

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

AJ23

VCC_A

AA31

AC31

AE31

AG23

AG25

AG31

AG5

AJ11

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

J31

J5

L31

N31

Q31

S31

S7

U31

U7

W31

W7

Y31

Y5

AG19

G21

AG21

G19

AN27

AL27

AN25

AL25

CPU1B

ZIF-SOCKET462

R5

X_0

X_0

R2

C99

0.1u

CPUTD <23>

L5

X_60S

CP2 X_Copper

21

2.5V

C100

X_39P

B B

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS_Z

H14

H18

H22

H26

M30P8R30T8V30X8Z30

VCORE

C86

C55

X_4.7u

X_4.7u

VCORE

C68

C50

X_0.22u

C82

X_0.22u

X_0.22u

A A

VCORE

C95

C58

X_1u

X_1u

8

C75

X_4.7u

C73

X_0.22u

C56

X_1u

AB8

C74

X_0.22u

AF12

AF16

C35

X_4.7u

AF20

AF24

C87

X_0.22u

C77

X_1u

AM36

AK32

AK28

AK24

C78

4.7u

C47

X_0.22u

AK20

AK16

7

AK12

AK4

C63

X_0.22u

AK2

AH36

AM32

AH34

AH32

AH28

AH24

AH20

AH16

AH12

AF4

AF2

AD36

AD34

AD32

C76

C54

4.7u

C49

X_0.22u

VCORE

C324

X_39P

C46

4.7u

4.7u

C89

X_0.22u

C79

X_0.22u

C60

X_0.22u

5020 5020 5020 5020 5020 5020

C323

C320

X_39P

X_39P

Solder Side

AB6

AB4

AB2

C325

X_39P

6

Z36

Z34

C6

X_0.22u

Z32X6AM28X4X2

VCORE

C69

X_39P

C61

X_0.22u

C322

X_39P

V36

C321

X_39P

V34

C37

X_39P

C36

X_0.22u

V32T6T4T2R36

C66

X_39P

C81

X_0.22u

R34

AM24

R32P6P4P2M36

C88

X_39P

C67

X_0.22u

C70

X_39P

C80

X_0.22u

5

M34

M32K6K4K2AM20

C90

X_39P

C64

X_0.22u

H36

H34

F26

C17

X_39P

C48

X_0.22u

F22

F18

VCORE

F14

F10F6F4F2AM16

C9

X_39P

C57

X_0.22u

C40

10u

C7

X_39P

C62

X_0.22u

D36

D34

D30

D26

D22

D18

D14

D10D6B34

AM12

B30

B26

B22

B18

B14

B10B6B2

AM4

AK6

AM6

AE7

C133

C10

X_39P

C110

X_39P

C111

X_39P

C5

X_39P

C39

X_39P

C104

X_39P

C84

X_39P

X_39P

CB31

X_39P

Alone VCORE edge

C85

10u

4

C44

C83

10u

10u

3

MICRO-STAR INT'L CO.,LTD.

Title

Socket 462 - 2

Size Document Number Rev

MS-7061 100

Custom

Date: Sheet

2

529Thursday, February 26, 2004

of

1

Page 6

8

7

6

5

4

3

2

1

VCC2_5

NORTH BRIDGE 1 of 3 ( HOST BUS)

D D

AVDD1VCORE VCC2_5VCC2_5

B17

D20

B20

C20

A20

C21

E19

B21

B18

E18

A17

C18

A18

D18

C17

E20

A21

D21

C22

A26

C25

C23

D24

B26

E21

A23

B23

A22

D23

A25

C26

C24

E26

F26

G25

G26

J26

H26

G24

H24

E22

E24

D25

D26

F25

F24

J25

H22

L26

M26

M25

M23

M24

K23

N22

M22

J24

K22

K25

K26

J23

N23

J22

K24

C11

D11

E11

A12

B12

C12

D12

E12

W22

KM266pro

NB1A

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

SDATA#[0:63] <4>

VCC2_5

DICLK#[0:3]<4>

J18

J14

M21

J13

J15

J17

L18

R18

K18

P18

N18

M18

J16

VTT

VTT

VTT

VTT

VTT

VTT

VTT

AIN#[2:14]<4>

AOUT#[2:14]<4>

C C

AOCLK#<4>

DOCLK#[0:3]<4>

DIVAL#<4>

CFWDRST<4>

B B

TESTIN0

A A

TESTIN1

S2KCOMP

CONNECT<4>

PROCRDY<4>

HCLK<3>

HCLK#<3>

R129 1K

R132 1K

R337 49.9R1%

R93 at solder

AIN#2

E17

G23

C19

B24

E13

D14

C14

E14

G21

E10

N21

U26

V26

V25

U24

V24

V23

U22

V22

C16

A14

D17

A15

E16

B14

C15

E15

A16

D15

A13

C13

B15

N26

P22

N24

P26

N25

T22

P24

R22

T24

T23

R23

R26

R24

R25

A19

A24

L24

F23

L22

F22

L21

F17

F12

T26

T25

AIN2

AIN3

AIN4

AIN5

AIN6

AIN7

AIN8

AIN9

AIN10

AIN11

AIN12

AIN13

AIN14

AINCLK

AOUT2

AOUT3

AOUT4

AOUT5

AOUT6

AOUT7

AOUT8

AOUT9

AOUT10

AOUT11

AOUT12

AOUT13

AOUT14

AOUTCLK

DICLK0

DICLK1

DICLK2

DICLK3

DOCLK0

DOCLK1

DOCLK2

DOCLK3

DINVAL

CFWDRST

CONNECT

PROCRDY

HCLK

HCLK

TESTIN1

S2KCOMP

S2KVREF0

S2KVREF1

TESTIN0

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS2K

K21

B13

AOCLK#

HCLK

HCLK#

TESTIN1

S2KCOMP

S2KVREF

TESTIN0

VCC2_5

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

-AICLK

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

-DICLK_0

-DICLK_1

-DICLK_2

-DICLK_3

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

VCC2_5

KM400(Revision:A)-->R93=300RST

KM266PRO(Revision:B)-->R93=49.9RST

VDS2K

VSS

VSS

D13

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F14

T21

B16

D16

B19

D19

B22

D22

B25

F10

F15

F19

F20

VTT

VTT

VTT

VTT

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E23

E25

H23

H25

L23

L25

P23

P25

U23

U25

G22

P21

R21

V21

W21

VDD

VDD

VDD

VDD

D0

D1

AVDD1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

AGND1

F21

CB114

X_10u

VCC2_5

CB71

0.1u

VCORE

CB102

0.1u

VCORE

CB27

X_0.1u

POWER/GROUND FOR

INTERNAL CPU

CLOCK LOGIC

AVDD1

DICLK#0 -DICLK_0

DICLK#1

DICLK#2 -DICLK_2

DICLK#3 -DICLK_3

AICLK#<4>

CB111

CB113

0.1u

X_10u

CB61

CB5

X_0.1u

CP24

X_0.1u

CB104

0.1u

CB58

X_0.1u

CB20

X_0.1u

VCC2_5

CB90

10000p

CB2

X_0.1u

CB93

X_0.1u

X_CP

Solder

At The Center Between CPU & NB

L10 4.7nH

3PC123

L18 4.7nH

3PC339

L6 4.7nH

3PC116

L17 4.7nH

3PC338

L19 4.7nH

3PC342

CB112

0.1u

CB100

0.1u

CB47

X_0.1u

L12

4.7nH

L20

4.7nH

L8

4.7nH

L21

4.7nH

L22

4.7nH

CB116

0.1u

CB49

0.1u

CB105

X_0.1u

CB97

0.1u

Solder Side

CB110

X_0.1u

R348 change to 130RST for Vref-margin@NB

-DICLK_1

-AICLKAICLK#

KM400A(Revision:?)-->R93=49.9RST

8

7

6

5

4

3

Solder Side

CB95

CB96

0.1u

0.1u

CB107

0.1u

VCORE

R336

S2KVREF

CB98

10000p

CB92

10000p

130R1%

R335

100R1%

Solder

(2003/10/17)

MICRO-STAR INT'L CO.,LTD.

Title

KM266/KM400 HOST BUS & POWER

Size Document Number Rev

MS-7061 0A

Custom

Date: Sheet

2

629

of

1

Page 7

8

7

6

5

4

3

2

1

NORTH BRIDGE 2 of 3 ( ME MOR Y)

VCCM AVDD2

D D

RMA[0..14]<9,10>

C C

CKE0<9,10>

CKE1<9,10>

CKE2<9,10>

CKE3<9,10>

RCS-0<9,10>

RCS-1<9,10>

RCS-2<9,10>

RCS-3<9,10>

RSRAS#<9,10>

RSCAS#<9,10>

RSWE#<9,10>

DQM0

DQM1

DQM2

DQM3

CB22

0.1u

DQM4

DQM5

DQM6

DQM7

-DQS_0

-DQS_1

-DQS_2

-DQS_3

-DQS_4

-DQS_5

-DQS_6

-DQS_7

MVREF0

VCCM

CB50

X_0.1u

B B

A A

8

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5

RMA6

RMA7

RMA8

RMA9

RMA10

RMA11

RMA12

RMA13

RMA14

AC11

AB12

AC12

AB14

AB16

AB17

AB15

AC18

AE17

AC17

AB10

AC9

AF17

AB18

AB19

AC21

AD24

AB22

AC24

AB20

AF24

AD6

AC5

AC6

AB6

AB7

AD5

AB11

AD7

AB9

Y26

AD25

AD22

AF19

AE15

AF12

AB8

AF4

Y24

AD26

AF22

AD19

AF15

AE12

AC8

AD4

AA10

AA18

CB46

X_0.1u

NB1B

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

CS0

CS1

CS2

CS3

CS4

CS5

SRASA

SCASA

SWEA

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

MVREF1

MVREF0

AA7V9V10

VCC3

VCC3

VCC3

V11

V12

VCC3

V13

VCC3

V14

VCC3

V15

VCC3

V16

VCC3

V17

VCC3

V18

VCC3

T18

VCC3

U18

VCC3

AA15

VCC3

AA21

VCC3

VCC3

AA22Y21

AVDD2AGND2

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

W23

W24

AA25

AB26

W26

W25

AA26

AA24

AB25

AB24

AF25

AE24

AB23

AC26

AE26

AF26

AD23

AE23

AD21

AF21

AC23

AF23

AE21

AB21

AC20

AF20

AF18

AD18

AD20

AE20

AE18

AD17

AF16

AC15

AC14

AE14

AD16

AD15

AD14

AF14

AF13

AD12

AD11

AF11

AD13

AB13

AE11

AD10

AF10

AE9

AE8

AF7

AF9

AD9

AF8

AD8

AE6

AF5

AE3

AF1

AF6

AE5

AF3

AF2

MD_0

MD_1

MD_2

MD_3

MD_4

MD_5

MD_6

MD_7

MD_8

MD_9

MD_10

MD_11

MD_12

MD_13

MD_14

MD_15

MD_16

MD_17

MD_18

MD_19

MD_20

MD_21

MD_22

MD_23

MD_24

MD_25

MD_26

MD_27

MD_28

MD_29

MD_30

MD_31

MD_32

MD_33

MD_34

MD_35

MD_36

MD_37

MD_38

MD_39

MD_40

MD_41

MD_42

MD_43

MD_44

MD_45

MD_46

MD_47

MD_48

MD_49

MD_50

MD_51

MD_52

MD_53

MD_54

MD_55

MD_56

MD_57

MD_58

MD_59

MD_60

MD_61

MD_62

MD_63

R92 at solder

R333 22R

Y22

DCLKO

AA23

DCLKIN

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AC3

AE2

AC4

AE4

AC7

AE7

AC10

AE10

AC13

AE13

Y23

AC16

AE16

Y25

AC19

AE19

AC22

AE22

AC25

AE25

VCCM

CB109

0.1u

CB103

X_0.1u

6

CB99

0.1u

7

VSS

AA13

Solder Side

CB108

CB106

X_0.1u

0.1u

KM266pro

CB115

0.1u

5

SSTL_2 RECEIVER VREF FOR DDR

Solder

MVREF0

CB94

CB101

1000P

1000P

DCLKO

DCLKI

DCLKO

DCLKO <3>

DCLKI <3>

C341 X_10P

Solder

DCLKI

C175 X_10P

4

VCCM

R332

1K

R334

1K

POWER FOR DRAM CLCO K

DESKEW CIRCUIT

AVDD2

X_CP

C337

0.1u

VCC2_5

CP25

CB91

1u

Solder

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5

RMA6

RMA7

RMA8

RMA9

RMA10

RMA11

RMA12

RMA13

RMA14

RSRAS#

RSCAS#

RSWE#

Solder

3

MD_4

1 2

MD_0

3 4

MD_5

5 6

MD_1

7 8

MD_2

1 2

MD_6

3 4

MD_7

5 6

MD_3

7 8

MD_8

1 2

MD_9

3 4

MD_12

5 6

MD_13

7 8

MD_10

1 2

MD_15

3 4

MD_14

5 6

MD_11

7 8

MD_20

1 2

MD_16

3 4

MD_17

5 6

MD_21

7 8

MD_18

1 2

MD_19

3 4

MD_22

5 6

MD_23

7 8

MD_28

1 2

MD_24

3 4

MD_25

5 6

MD_29

7 8

MD_26

1 2

MD_30

3 4

MD_27

5 6

MD_31

7 8

MD_42

1 2

MD_43

3 4

MD_46

5 6

MD_47

7 8

MD_40

1 2

MD_44

3 4

MD_45

5 6

MD_41

7 8

MD_36

1 2

MD_32

3 4

MD_33

5 6

MD_37

7 8

MD_34

1 2

MD_38

3 4

MD_39

5 6

MD_35

7 8

MD_48

1 2

MD_49

3 4

MD_52

5 6

MD_53

7 8

MD_54

1 2

MD_50

3 4

MD_55

5 6

MD_51

7 8

MD_60

1 2

MD_56

3 4

MD_61

5 6

MD_57

7 8

MD_62

1 2

MD_58

3 4

MD_63

5 6

MD_59

7 8

C340X_33p

C336X_33p

C335X_33p

C334X_33p

C333X_33p

C331X_33p

C332X_33p

C329X_33p

C330X_33p

C328X_33p

C343X_33p

C346X_33p

C344X_33p

C327X_33p

C326X_33p

C347X_33p

C349X_33p

C348X_33p

RN13

8P4R-10R

RN15

8P4R-10R

RN17

8P4R-10R

RN21

8P4R-10R

RN24

8P4R-10R

RN28

8P4R-10R

RN31

8P4R-10R

RN35

8P4R-10R

RN50

8P4R-10R

RN45

8P4R-10R

RN40

8P4R-10R

RN42

8P4R-10R

RN52

8P4R-10R

RN56

8P4R-10R

RN58

8P4R-10R

RN62

8P4R-10R

-DQS_0

-DQS_1

-DQS_2

-DQS_3

-DQS_4

-DQS_5

-DQS_6

-DQS_7

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6 RDQM6

DQM7

Title

Size Document Number Rev

Date: Sheet

R48 10

R71 10

R89 10

R105 10

R122 10

R133 10

R157 10

R182 10

R45 10

R72 10

R87 10

R101 10

R121 10

R137 10

R153 10

R179 10

MICRO-STAR INT'L CO.,LTD.

KM266/KM400M M E M O R Y

MS-7061 100

Custom

RMD4

RMD0

RMD5

RMD1

RMD2

RMD6

RMD7

RMD3

RMD8

RMD9

RMD12

RMD13

RMD10

RMD15

RMD14

RMD11

RMD20

RMD16

RMD17

RMD21

RMD18

RMD19

RMD22

RMD23

RMD28

RMD24

RMD25

RMD29

RMD26

RMD30

RMD27

RMD31

RMD42

RMD43

RMD46

RMD47

RMD40

RMD44

RMD45

RMD41

RMD36

RMD32

RMD33

RMD37

RMD34

RMD38

RMD39

RMD35

RMD48

RMD49

RMD52

RMD53

RMD54

RMD50

RMD55

RMD51

RMD60

RMD56

RMD61

RMD57

RMD62

RMD58

RMD63

RMD59

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM7

2

RMD[63:0] <9,10>

RDQS[7:0] <9,10>

RDQM[7:0] <9,10>

of

729Thursday, February 26, 2004

1

Place these damping resistors close to DIMM1

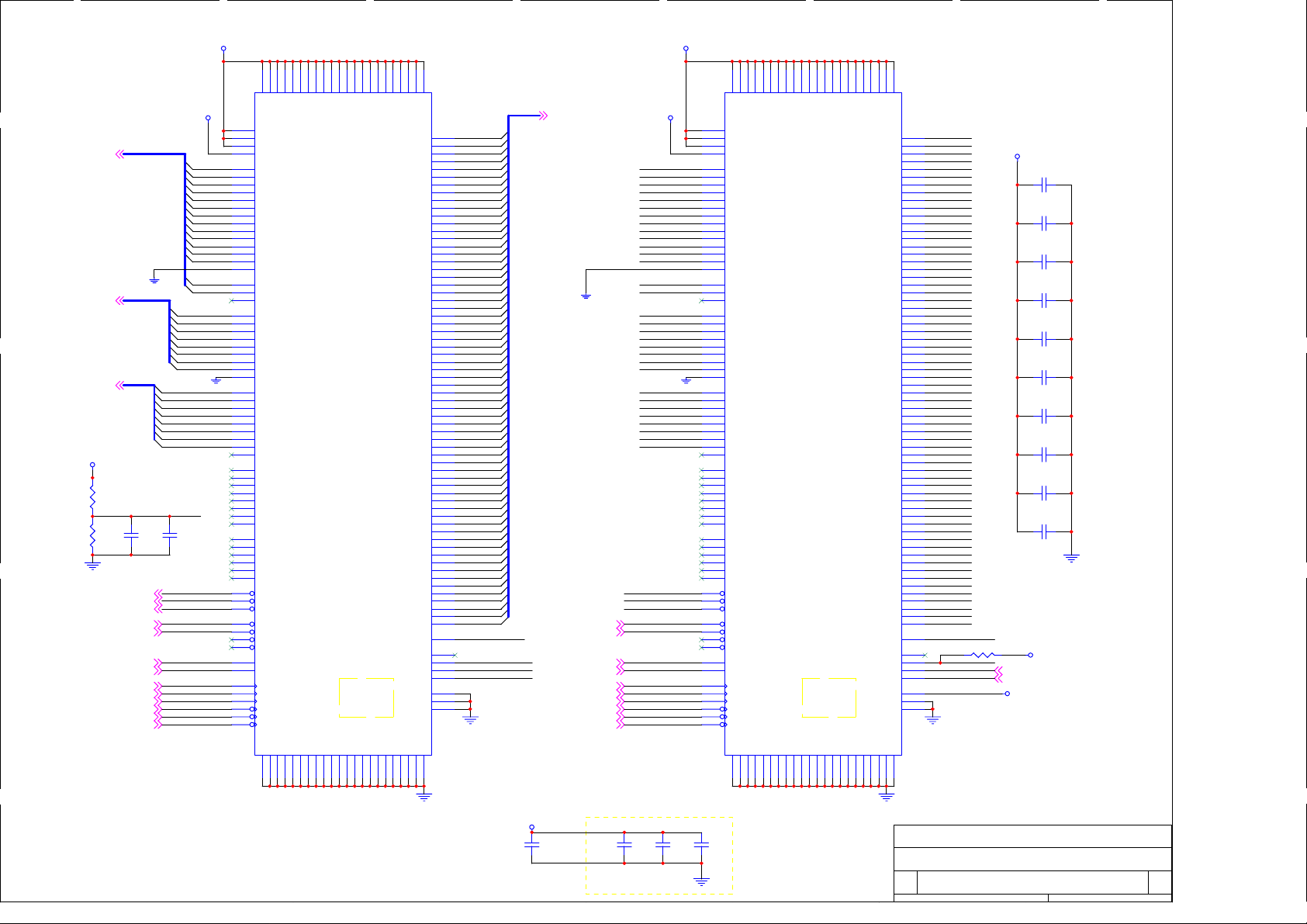

Page 8

8

NORTH BRIDGE 3 of 3 (AGP,VLINK,VGA)

D D

AAD[0..31]<11>

C C

ACBE#0<11>

ACBE#1<11>

ACBE#2<11>

ACBE#3<11>

ADSTB0<11>

ADSTB#0<11>

ADSTB1<11>

ADSTB#1<11>

SBA[0..7]<11>

B B

AVREFGC<11>

A A

SBSTB<11>

SBSTB#<11>

AFRAME#<11>

AIRDY#<11>

ATRDY#<11>

ASTOP#<11>

ADEVSEL#<11>

APAR<11>

AGNT#<11>

AREQ#<11>

ST0<11>

ST1<11>

ST2<11>

DBIL<11>

D-PIPE<11>

WBF#<11>

RBF#<11>

VCLKNB<3>

AGP8X#<11>

ASERR<11>

8

VCLKNB

AGPNCOMP

AVREFGC

AAD0

AAD1

AAD2

AAD3

AAD4

AAD5

AAD6

AAD7

AAD8

AAD9

AAD10

AAD11

AAD12

AAD13

AAD14

AAD15

AAD16

AAD17

AAD18

AAD19

AAD20

AAD21

AAD22

AAD23

AAD24

AAD25

AAD26

AAD27

AAD28

AAD29

AAD30

AAD31

ACBE#0

ACBE#1

ACBE#2

ACBE#3

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

D-PIPE

7

NB1C

W2

GD0/FPD10

W1

GD1/FPD11

V3

GD2/FPDVICLK

W3

GD3/FPD09

V1

GD4/FPD08

U2

GD5/FPD07

U1

GD6/FPD06

U3

GD7/FPD05

T4

GD8/FPDVIDET

T5

GD9/FPDVIHS

R3

GD10/FPD01

P2

GD11/FPD23

R1

GD12/FPD00

P1

GD13/FPD22

P3

GD14/FPD21

N3

GD15/FPD20

N2

GD16/FPD18

M1

GD17/FPD17

M3

GD18/FPD16

M5

GD19/FPDE

L1

GD20/FPD14

L4

GD21/FPCLK

L2

GD22/FPD13

L3

GD23/FPD15

J1

GD24/DVP1D09

H5

GD25

J3

GD26/DVP1D10

H4

GD27

H1

GD28/DVP1D07

H3

GD29/DVP1D06

H2

GD30/DVP1D08

G4

GD31/DVP1D04

T1

GCBE0/FPD03

P4

GCBE1/SB_DA

N1

GCBE2/FPD19

K3

GCBE3/DVP1D11

T3

ADSTB0F/FPD04

T2

ADSTB0S/FPD02

K2

ADSTB1F/FPD12

K1

ADSTB1S/FPDET

D2

SBA0/DVP1VS

D3

SBA1/DVP1DE

E3

SBA2/DVP1D00

D1

SBA3/DVP1HS

G3

SBA4/DVP1D05

F1

SBA5/DVP1D03

G1

SBA6/DVP1CLK

G2

SBA7/DVP1CLK_N

E1

SBSTBF/DVP1D01

E2

SBSTBS/DVP1D02

N5

GFRAME/FPHS

P5

GIRDY/SB_CK

R5

GTRDY

U5

GSTOP/FPDVICLK_N

N4

GDEVSEL/FPVS

U4

GPAR/FPDVIVS

E4

GGNT/DVI_DDCDA

F5

GREQ/DVI_DDCCK

G5

ST0

F3

ST1/DVP1DET

J5

ST2

J4

DBIL

K5

DBIH/PIPE

L5

WBF/FPCLK_N

K4

RBF

V5

GCLK

C1

AGPCOMP

M6

AGPVREF0

H6

AGPVREF1

G6

AGP8XDET

R4

GSERR/FPDVIDE

VSS

VSS

VSS

F2J2M2R2V2F4M4V4J9

7

J6N6P6R6T6U6K9L9M9N9P9

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VSS

VSS

VSS

VSS

VSSQQ

AA3

VSS

VSS

VSS

6

VCC2_5VDDQ

AA6

Y6T9U9

VCC1

B1C2R9

VCC1

VCCQQ

VCC2

VCC2

VCC2

AA8

VCC2

K6L6V6W6AA11

AA9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

AA12

VDD

AGP I/F VLINK I/F

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M14

M15

M16

N11

N12

N13

AA5

VSS

L11

L12

L13

L14

L15

L16

M11

M12

M13

6

5

VCC25SBY

VCC3

J11

J10

VDD

J12

AA17

VDD

VCC5

VCC5

VCC5

AA19

VDD

AA20F8F9

VDD

VDD

VDD

F16

F18

H21

J21

AA16

AA14

VDD

VDD

VDD

VDD

VDD

CRT I/F

TFT FLAT PANEL / EXTERNAL

TV ENCODER I/F

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N14

N15

N16

P11

P12

P13

P14

P15

P16

R11

R12

R13

R14

R15

R16

T11

T12

5

C159

0.1u

AD3

C4

C3

B4

A4

VSUS25

VCCDAC

VCCRGB

PLLVDD1

LCOMPP

SPCLK2

TVD00/DVP0D00

TVD01/DVP0D01

TVD02/DVP0D02

TVD03/DVP0D03

TVD04/DVP0D04

TVD05/DVP0D05

TVD06/DVP0D06

TVD07/DVP0D07

TVD08/DVP0D08

TVD09/DVP0D09

TVD10/DVP0D10

TVD11/DVP0D11

TVVS/DVP0VS

TVHS/DVP0HS

TVCLK/DVP0DCLK

TVCLKIN/DVP0DET

TVDE/DVP0DE

DISPCLKO

DISPCLKI

SPCLK1

PWROK

SUSSTAT

GNDDAC

GNDRGB

PLLGND1

PLLGND2

VSS

VSS

VSS

VSS

VSS

VSS

T13

T14

T15

T16

U21

C10

VCC_RGB

PLLVDD2

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VD7

VBE

UPCMD

UPSTB

UPSTB

DNCMD

DNSTB

DNSTB

LVREF

XIN

INTA

AR

AG

AB

RSET

HSYNC

VSYNC

SPD2

GPO0

GPOUT

SPD1

RESET

BISTIN

VSS

VSS

F11

F13

VSS

W4

W5

AA4

Y1

AC2

Y2

AB4

AC1

Y3

Y4

AA1

AA2

AB3

AB1

AB2

AB5

Y5

E6

F6

A3

A2

B3

B5

B6

A6

C6

D6

D9

C9

B9

A9

E9

E8

B8

A8

C8

C7

B7

A7

B11

B10

D8

A10

A11

C5

D5

D10

E7

F7

D7

AD1

AE1

AD2

A5

B2

A1

E5

D4

KM266pro

4

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

LCOMPP

LVREF_NB

RSET

R138 4.7K

R142 4.7K

BISTIN

4

VLAD[0..7] <14>

-VBE <14>

UPCMD <14>

UPSTB+ <14>

UPSTB- <14>

DNCMD <14>

DNSTB+ <14>

DNSTB- <14>

GCLK14 <3>

INTA# <11,12,15>

RED <27>

GREEN <27>

BLUE <27>

HSYNC <27>

VSYNC <27>

SPCLK2 <27>

SPD2 <27>

PWRGD_NB <13>

PCIRST1# <22,26>

SUSST# <13>

PLL_GND

3

VLINK

1. VLINK REFERENCE VOLTAGE - 0.625V

LVREF_NB

CB117

10000p

solder

2. VLINK P-CHANNEL COMPENSATION

LCOMPP

R164 360R1%

BISTIN

R145 1K

R143 147R1%

RSET

VCC_RGB

PLL_GND

C142

X_0.1u

C141

4.7u

VCC2_5

CB62

X_0.1u

CP6

1 2

1 2

CP4

Title

Size Document Number Rev

Date: Sheet

3

2

AGP

1. AGPVREF (PROVIDED BY AGP 4X CARD OR BY

SYSTEM FOR OTHERS)

AVREFGC

R172

3KR1%

R165

1K

2. AGPNCOMP : AGP N-CHANNEL

COMPENSATION

AGPNCOMP

R162 60.4R1%

VDDQ

3. AGP POWER : VCCAGP

VDDQ

C352

X_0.1u

C354

0.1u

C350

0.1u

Solder Side

VCC2_5

MICRO-STAR INT'L CO.,LTD.

KM266/KM400 AGP & CRT & VLINK

MS-7061 100

Custom

2

1

CB75

1u

C353

0.1u

829Thursday, February 26, 2004

of

1

Page 9

8

7

6

5

4

VCCMVCCM

3

2

1

VDDQ

VSS

VDDQ

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDID

SDA

VSS

VSS

SCL

SA0

SA1

SA2

WP

15223054627796

VDDQ

VDDQ

VSS

VSS

3111826344250586674818993

DIMM2

2

4

6

8

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

1

82

90

92

91

181

182

183

DIMM-184

RMD0

RMD1

RMD2

RMD3

RMD17

RMD18

RMD21

RMD22

RMD31

RMD32

RMD41

RMD42

RMD43

RMD44

RMD45

RMD46

RMD47

RMD48

RMD49

RMD50

RMD51

RMD52

RMD53

RMD54

RMD55

RMD56

RMD57

RMD58

RMD62

R188 4.7K

WP

DIMM DECOUPLING

VCCM

CB54

0.1u

CB45

0.1u

CB59

0.1u

CB40

0.1u

CB11

X_0.1u

CB6

0.1u

CB36

X_0.1u

CB16

X_0.1u

CB33

X_0.1u

CB30

0.1u

VCC3

SMBCLK <3,13,26>

SMBDAT <3,13,26>

VCC3

DIMM1

VDDQ

VDDQ

VSS

VSS

VDDQ

VSS

VDDQ

VDDQ

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDID

VSS

VSS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

SCL

SDA

SA0

SA1

SA2

WP

15223054627796

VDDQ

VDDQ

VSS

VSS

3111826344250586674818993

VDD

120

148

168

184

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

97

107

119

129

149

159

169

177

140

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

10

101

102

173

103

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

VDD

VDD

VDD

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

5

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

9

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

VDD

VSS

VSS

160

176

RMD[63:0] <7,10>

RMD0

2

RMD1

4

RMD2

6

RMD3

8

RMD4

94

RMD5

95

RMD6

98

RMD7

99

RMD8

12

RMD9

13

RMD10

19

RMD11

20

RMD12

105

RMD13

106

RMD14

109

RMD15

110

RMD16

23

RMD17

24

RMD18

28

RMD19

31

RMD20

114

RMD21

117

RMD22

121

RMD23

123

RMD24

33

RMD25

35

RMD26

39

RMD27

40

RMD28

126

RMD29

127

RMD30

131

RMD31

133

RMD32

53

RMD33

55

RMD34

57

RMD35

60

RMD36

146

RMD37

147

RMD38

150

RMD39

151

RMD40

61

RMD41

64

RMD42

68

RMD43

69

RMD44

153

RMD45

155

RMD46

161

RMD47

162

RMD48

72

RMD49

73

RMD50

79

RMD51

80

RMD52

165

RMD53

166

RMD54

170

RMD55

171

RMD56

83

RMD57

84

RMD58

87

RMD59

88

RMD60

174

RMD61

175

RMD62

178

RMD63

179

DDRVREF DDRVREF

1

82

90

92

91

181

182

183

DIMM-184

SMBDAT SMBDAT

RCS-2<7,10>

RCS-3<7,10>

CKE2<7,10>

CKE3<7,10>

DDRCLK3<3>

DDRCLK1<3>

DDRCLK5<3>

DDRCLK-3<3>

DDRCLK-1<3>

DDRCLK-5<3>

VCC3

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5

RMA6

RMA7

RMA8

RMA9

RMA10

RMA13

RMA14

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

RDQM7

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

RCS-2 RMD63

RCS-3

104

112

128

136

143

156

164

172

180738467085108

VDD

VDD

VDD

VDD

VDD

120

148

168

184

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

97

107

119

129

149

159

169

177

140

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

10

101

102

173

103

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

VDD

VDD

VDD

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

5

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

9

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

VDD

VSS

VSS

160

176

VDDQ

VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

100

116

124

132

139

145

152

VDDQ

VSS

VDDQ

VDDQ

addr =

1010000b

VSS

VSS

VDDQ

VSS

VDDQ

VDDQ

VSS

VSS

VDDQ

VSS

D D

RMA[0..14]<7,10>

RDQM[7:0]<7,10>

C C

RDQS[7:0]<7,10>

VCCM

R29

1K

CB3

R34

0.1u

1K

VCC3

RMA0 RMD4

RMA1 RMD5

RMA2 RMD6

RMA3 RMD7

RMA4 RMD8

RMA5 RMD9

RMA6 RMD10

RMA7 RMD11

RMA8 RMD12

RMA9 RMD13

RMA10 RMD14

RMA13 RMD15

RMA14 RMD16

RMA11 RMA11 RMD19

RMA12 RMA12 RMD20

RDQM0 RMD23

RDQM1 RMD24

RDQM2 RMD25

RDQM3 RMD26

RDQM4 RMD27

RDQM5 RMD28

RDQM6 RMD29

RDQM7 RMD30

RDQS0 RMD33

RDQS1 RMD34

RDQS2 RMD35

RDQS3 RMD36

RDQS4 RMD37

RDQS5 RMD38

RDQS6 RMD39

RDQS7 RMD40

DDRVREF

CB7

10000p

B B

RSRAS#<7,10>

RSCAS#<7,10>

DDRCLK2<3>

DDRCLK0<3>

DDRCLK4<3>

DDRCLK-2<3>

DDRCLK-0<3>

DDRCLK-4<3>

RSRAS# RSRAS# RMD59

RSCAS# RSCAS# RMD60

RSWE# RSWE# RMD61

RSWE#<7,10>

RCS-0<7,10>

RCS-1<7,10>

CKE0 WP CKE2

CKE0<7,10>

CKE1 SMBCLK CKE3 SMBCLK

CKE1<7,10>

164

172

180738467085108

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

100

116

124

132

139

145

152

143

156

VDDQ

VDDQ

addr =

1010001b

VSS

VSS

136

VDDQ

VDDQ

VSS

VSS

128

VDDQ

VSS

112

104

VDDQ

VDDQ

VSS

VSS

VDDQ

VDDQ

VSS

VSS

A A

VCCM

C30

X_0.1u

8

7

6

5

C430,C431 & C432 at solder side

C319

C355

C345

X_0.1u

X_0.1u

Reserved for EMI

X_0.1u

4

MICRO-STAR INT'L CO.,LTD.

Title

DDR1 & DDR2

Size Document Number Rev

MS-7061 100

B

3

Date: Sheet

2

of

929Wednesday, February 25, 2004

1

Page 10

SSTL-2 Termination Resistors

RMD1

RMD5

RMD4

RMD0

RMD6

RMD2

RDQS0

RDQM0

RMD9

RMD8

RMD3

RMD7

RDQM1

RDQS1

RMD13

RMD12

RMD10

RMD15

RMD11

RMD14

RDQM2

RMA13

RDQS2

RMD21

RMD17

RMA14

RMD16

RMD20

RMA5

RMD23

RMD19

RMA8

RMD31

RMD26

RMA3

RMD30

RMA4

RDQS3

RDQM3

RMD29

RMA7

RMD22

RMD18

RMA9

RMD25

RMD28

RMD24

RMA6

RMA0

RMA1

RMA2

RMD27

RMD35

RDQM4

RMA11

RMD38

RMD[63:0] <7,9>

RDQM[7:0] <7,9>

RDQS[7:0] <7,9>

RMA[0..14] <7,9>

DDR_VTT DDR_VTT

1

2

RN10

3

4

8P4R-56

5

6

7

8

1

2

RN12

3

4

8P4R-56

5

6

7

8

1

2

RN14

3

4

8P4R-56

5

6

7

8

1

2

RN16

3

4

8P4R-56

5

6

7

8

1

2

RN18

3

4

8P4R-56

5

6

7

8

1

2

RN23

3

4

8P4R-56

5

6

7

8

1

2

RN22

3

4

8P4R-56

5

6

7

8

1

2

RN29

3

4

8P4R-56

5

6

7

8

1

2

RN34

3

4

8P4R-56

5

6

7

8

1

2

RN33

3

4

8P4R-56

5

6

7

8

1

2

RN26

3

4

8P4R-56

5

6

7

8

1

2

RN30

3

4

8P4R-56

5

6

7

8

1

2

RN36

3

4

8P4R-56

5

6

7

8

1

2

RN39

3

4

8P4R-56

5

6

7

8

MD/DQM(/DQS)

MA/Control

CS

CKE

RSRAS#<7,9>

RCS-1<7,9>

RCS-3<7,9>

RCS-0<7,9>

RCS-2<7,9>

RSCAS#<7,9>

RSWE#<7,9>

CKE1<7,9>

CKE3<7,9>

CKE0<7,9>

CKE2<7,9>

RMD36

RMD32

RMA12

RMA10

RMD37

RMD34

RDQS4

RMD33

RSRAS#

RMD44

RMD40

RMD49

RMD48

RMD47

RMD43

RMD53

RMD52

RMD50

RMD54

RDQS6

RDQM6

RMD59

RMD63

RMD58

RMD62

RMD56

RMD60

RMD51

RMD55

RDQS7

RDQM7

RMD57

RMD61

RMD46

RMD42

RDQS5

RDQM5

RMD41

RMD45

RSWE#

SDR

LV-CMOS

LV-CMOS

LV-CMOS

OD 3.3V OD 2.5V

1

2

RN37

3

4

8P4R-56

5

6

7

8

1

2

RN38

3

4

8P4R-56

5

6

7

8

1

2

RN41

3

4

8P4R-56

5

6

RMD39

7

8

1

2

RN51

3

4

8P4R-56

5

6

7

8

1

2

RN46

3

4

8P4R-56

5

6

7

8

1

2

RN53

3

4

8P4R-56

5

6

7

8

1

2

RN54

3

4

8P4R-56

5

6

7

8

1

2

RN61

3

4

8P4R-56

5

6

7

8

1

2

RN57

3

4

8P4R-56

5

6

7

8

1

2

RN60

3

4

8P4R-56

5

6

7

8

1

2

RN47

3

4

8P4R-56

5

6

7

8

1

2

RN44

3

4

8P4R-56

5

6

7

8

7

8

RN20

5

6

8P4R-56

3

4

1

2

Rs

0/10/- 47

10

0

DDR

SSTL-2

SSTL-2

SSTL-2

Rs

10

0

0

DDR_VTT DDR_VTTDDR_VTT

10u

10u

10u

10u

CB24

0.1u

CB63

0.1u

CB4

0.1u

CB10

0.1u

CB21

0.1u

CB29

X_0.1u

CB48

CB56

CB38

CB15

Rtt

47

47

CB41

0.1u

CB8

0.1u

CB35

0.1u

CB65

0.1u

CB43

0.1u

CB26

X_0.1u

CB32

0.1u

CB28

0.1u

CB60

X_0.1u

CB53

0.1u

C366

1 2

1000P

For EMI

CB39

0.1u

CB51

X_10u

CB17

X_10u

CB34

0.1u

CB55

0.1u

CB57

0.1u

CB42

X_0.1u

CB37

X_0.1u

CB44

0.1u

CB13

0.1u

VCC5VCC3

MICRO-STAR INT'L CO.,LTD.

Title

DDR TERMINATOR

Size Document Number Rev

MS-7061 100

Custom

Date: Sheet

10 29Wednesday, February 25, 2004

of

Page 11

KM266

no stuff

8

7

6

5

4

3

2

1

12V

USBGND

RST#

GNT#

ST1

GND

SBA1

SBA3

GND

SBA5

SBA7

GND

AD30

AD28

AD26

AD24

GND

AD22

AD20

GND

AD18

AD16

GND

GND

PAR

AD15

AD13

AD11

GND

AD9

AD6

GND

AD4

AD2

AD0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

+12V

VDDQ

VCC3

AGP8XGC#

R222 X_0

D-PIPE <8>

ST1

SBA1

SBA3

SBA5

SBA7

AAD15

KM400 stuff

KM266 no stuff

INTA# <8,12,15>

PCIRST# <12,26>

AGNT# <8>

ST1 <8>

WBF# <8>

SBSTB# <8>

ADSTB#1 <8>

ACBE#3 <8>

AFRAME# <8>

ATRDY# <8>

ASTOP# <8>

APAR <8>

ACBE#0 <8>

ADSTB#0 <8>

C351

1u

SBA[0..7]<8>

AAD[0..31]<8>

D D

INTB#<12,15>

AGPCLK1<3>

AREQ#<8>

SBSTB<8>

DBIL<8>

C C

ADSTB1<8>

ACBE#2<8>

AIRDY#<8>

ADEVSEL#<8>

ASERR<8>

ACBE#1<8>

B B

ADSTB0<8>

ST0

ST0<8>

ST2

ST2<8>

RBF#<8>

DBIL

SBA0

SBA2

SBA4

SBA6

DBIL

AAD31 AAD30

AAD29 AAD28

AAD27 AAD26

AAD25 AAD24

ADSTB1 ADSTB#1

AAD23 ACBE#3

AAD21 AAD22

AAD19 AAD20

AAD17 AAD18

ACBE#2 AAD16

APERR#

ACBE#1

AAD14 AAD13

AAD12 AAD11

AAD10 AAD9

AAD8 ACBE#0

ADSTB0 ADSTB#0

AAD7 AAD6

AAD5 AAD4

AAD3 AAD2

AAD1 AAD0

AVREFCG

VCC3SBY VCC5

VCC3

VDDQ

AGP1

B1

OVRCNT#

B2

5V

B3

5V

B4

USB+

B5

GND

B6

INTB#

B7

CLK

B8

REQ#

B9

VCC3.3

B10

ST0

B11

ST2

B12

RBF#

B13

GND

B14

RSVD(REFCLK)

B15

SBA0

B16

VCC3.3

B17

SBA2

B18

SB_STB

B19

GND

B20

SBA4

B21

SBA6

B22

RSVD(DBIL)

B23

GND

B24

3.3VAUX

B25

VCC3.3

B26

AD31

B27

AD29

B28

VCC3.3

B29

AD27

B30

AD25

B31

GND

B32

AD_STB1

B33

AD23

B34

VDDQ

B35

AD21

B36

AD19

B37

GND

B38

AD17

B39

C/BE#2

B40

VDDQ

B41

IRDY#

B42

3.3VAUX

B43

GND

B44

RSVD(CSYNC)

B45

VCC3.3

B46

DEVSEL#

B47

VDDQ

B48

PERR#

B49

GND

B50

SERR#

B51

C/BE1#

B52

VDDQ

B53

AD14

B54

AD12

B55

GND

B56

AD10

B57

AD8

B58

VDDQ

B59

AD_STB0

B60

AD7

B61

GND

B62

AD5

B63

AD3

B64

VDDQ

B65

AD1

B66

VREFCG

SLOT-AGP1.5_LATCH

TYPEDET#

RSVD(GC_AGP8XDET#)

INTA#

VCC3.3

RSVD(MB_AGP8XDET#)

PIPE#

WBF#

VCC3.3

SB_STB#

RSVD(DBIH)

RSVD(VBDET#)

VCC3.3

VCC3.3

AD_STB1#

C/BE3#

VDDQ

VDDQ

FRAME#

RSVD(RSYNC)

RSVD(LSYNC)

VCC3.3

TRDY#

STOP#

PME#

VDDQ

C/BE0#

VDDQ

AD_STB0#

VDDQ

VREFGC

C135 at solder

R137

KM400 3.32K

KM266Pro 1.02K

A A

CB80

10000p

8

1u

C207

VDDQ

R230

1.02KR1%

R221

1.02KR1%

DS

Q31

G

X_N-2N7002-SOT23

R239X_1.47KR1%

KM400 stuff

KM266 no stuff

7

+12V

R237

X_4.7K

AGP8XGC#

X_N-2N7002-SOT23

Q29

VCC2_5

VDDQ

X_1K

R236

DS

1K

G

R344

AGP8X# <8>

X_10K

R220

4X -> 1

8X -> 0

6

AGP8XGC#AVREFCG

5

+12V

X_4.7K

R249

C

R238X_2.2K

Q33

B

X_2N3904S

E

DS

G

4

R222

AVREFGC <8>

APERR#

Q32

X_N-2N7002-SOT23

X_200R

R253

VCC3

C226

X_0.1u

CB1

0.1u

CB52

0.1u

CB119

0.1u

CB78 at solder

VCC5

+12V

VCC3SBY

3

VDDQ

VDDQ

C210

1u

PCIRST#

VDDQVDDQ

R225 8.2KR

C214

X_1u

C217

X_33p

C211

1u

C212

X_1u

C198

1u

C213

1u

CB82

X_0.1u

11 29Wednesday, March 24, 2004

CB74

X_0.1u

of

1

APERR#

CB79X_0.1u

CB250.1u

CB88X_0.1u

CB81X_0.1u

CB72X_0.1u

CB76X_0.1u

CB73X_0.1u

C200X_0.1u

MICRO-STAR INT'L CO.,LTD.

Title

AGP SLOT

Size Document Number Rev

MS-7061 0A

Custom

Date: Sheet

2

Page 12

8

7

6

VCC3

5

4

3

2

1

D D

AD[31..0]<15>

C C

C/BE#[3..0]<15>

B B

AD[31..0]

C/BE#[3..0]

FRAME#<15>

DEVSEL#<15>

IRDY#<15>

TRDY#<15>

STOP#<15>

SERR#<15>

PERR#<15>

PCIRST#<11,26>

INTA#<8,11,15>

INTB#<11,15>

INTC#<15>

INTD#<15>

PREQ#0<15>

PREQ#1<15>

PREQ#2<15>

PREQ#3<15>

PREQ#4<15>

PGNT#0<15>

PGNT#1<15>

PGNT#2<15>

PGNT#3<15>

PGNT#4<15>

H9

H10

H12J8K8L8M8N8P8R8R19

GND

GND

H11

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33