Page 1

5

4

3

2

1

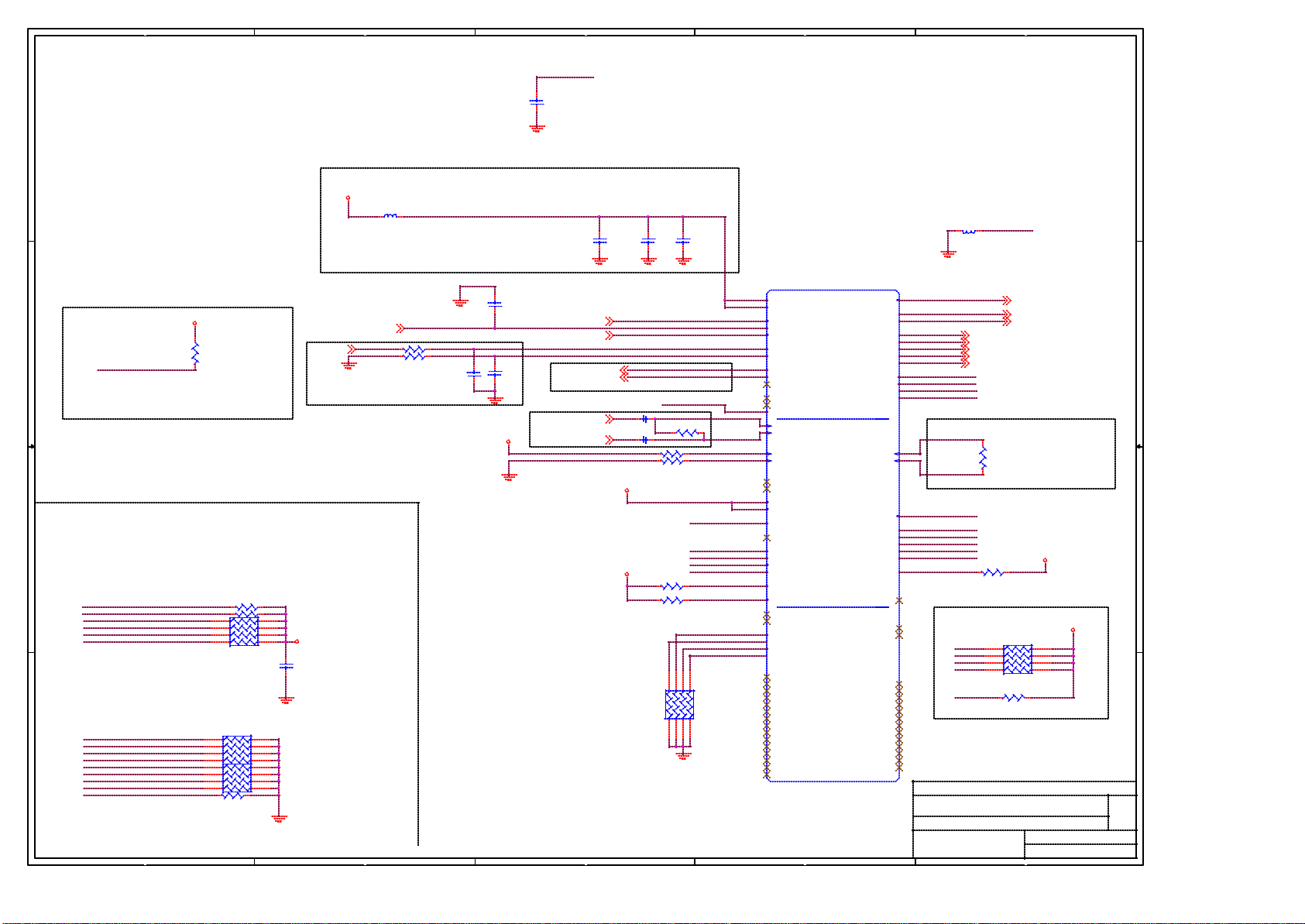

MS-7032 VER:100 ATX

*AMD PGA 754 K8-Processor (DDR 400)

D D

*VIA K8M800 /K8T800 Pro

*VIA VT8237

*Winbond 83297THF-VF LPC I/O

*RTL 8110S Giga/ 8201BL 100/10 Bit LAN Support

*USB 2.0 support (integrated into VT8237)

*Vcore Jumpless support

*ALC655 6 channel S/W Audio

C C

*DDR DIMM * 2

*AGP SLOT * 1 ( 8X )

*PCI SLOT * 5

B B

A A

(AGP 8X / VLink 8X)

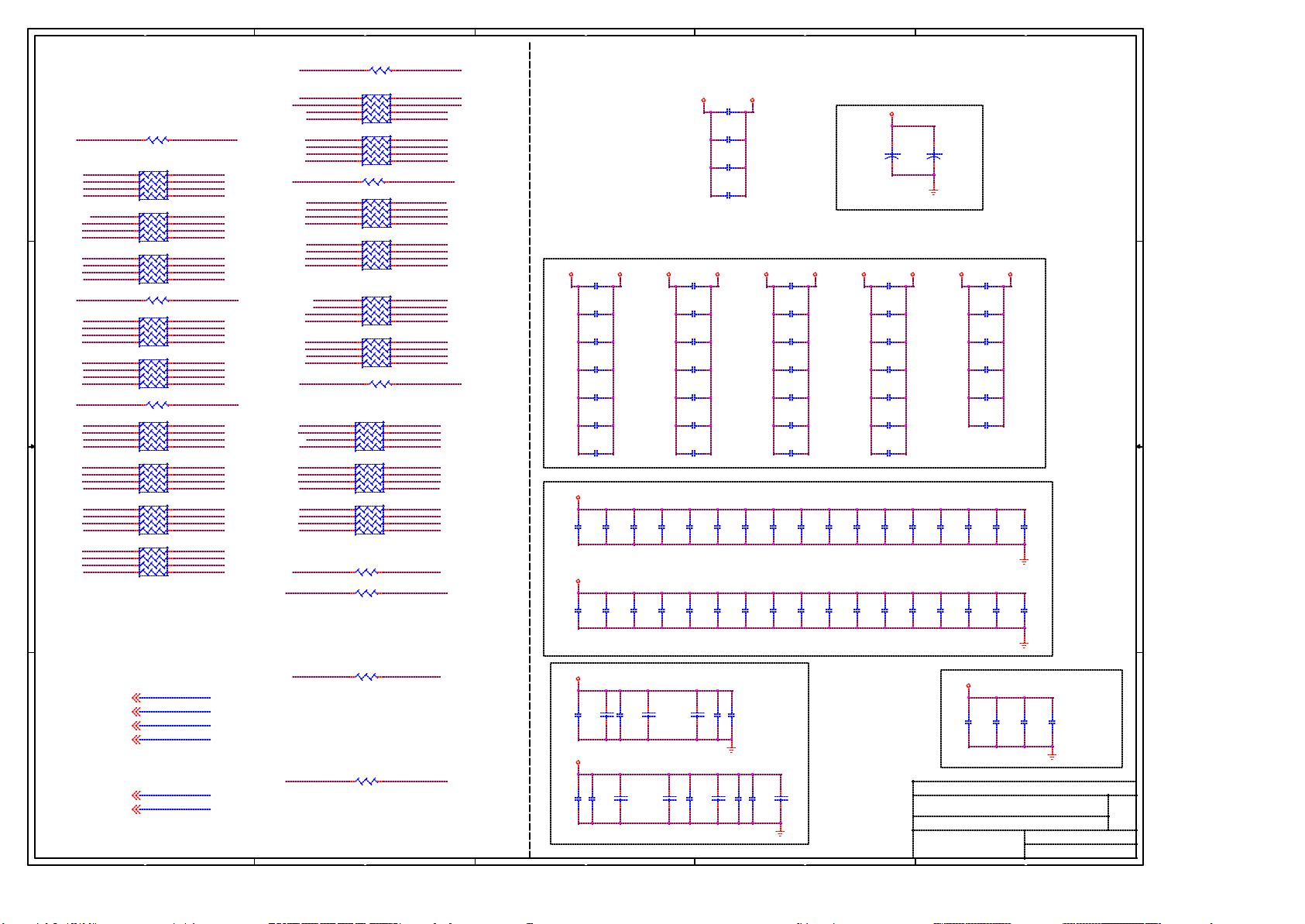

Cover Sheet

Block Diagram 2

GPIO SPEC

AMD K8 -> 754 PGA Socket 4,5,6

Clock Synthesizer

System Memory

DDR Terminations R & C

DDR Damping R & Bypass Cap.

NB VIA K8T800A/K8M800 (HT)

K8 Vcore

AGP SLOT 8X

VT8237

PCI Connectors * 5

ALC650/ALC655 6 channel S/W Audio

IDE ATA 66/100 Connectors * 2

Front and Rear USB Port

Hardware monitor & FAN

Keyboard/Mouse Connectors

LPT/COM Port

10/100 LAN & VGA

Giga-Bit LAN RTL8110S

ACPI Power CONTROLLER (MS-6)

VOLTAGE REGULATOR & ROM

Front Panel & POWER OK CIRCUIT

Decoupling Cap.

Power Sequence

History

OPTION PARTS

DDR DIMM 1 & 2

PageTitle

1

3

7

8

9

10

11,12,13

14

15

16,17,18

19,20,21

22

23

24,25

26LPC I/O W83697HF & Floppy

27

28

29

30

31

32

33

34

35

36

37

38

Micro Star Restricted Secret

Title

Document Number

5

4

3

2

Cove r Sheet

MS-7032

1

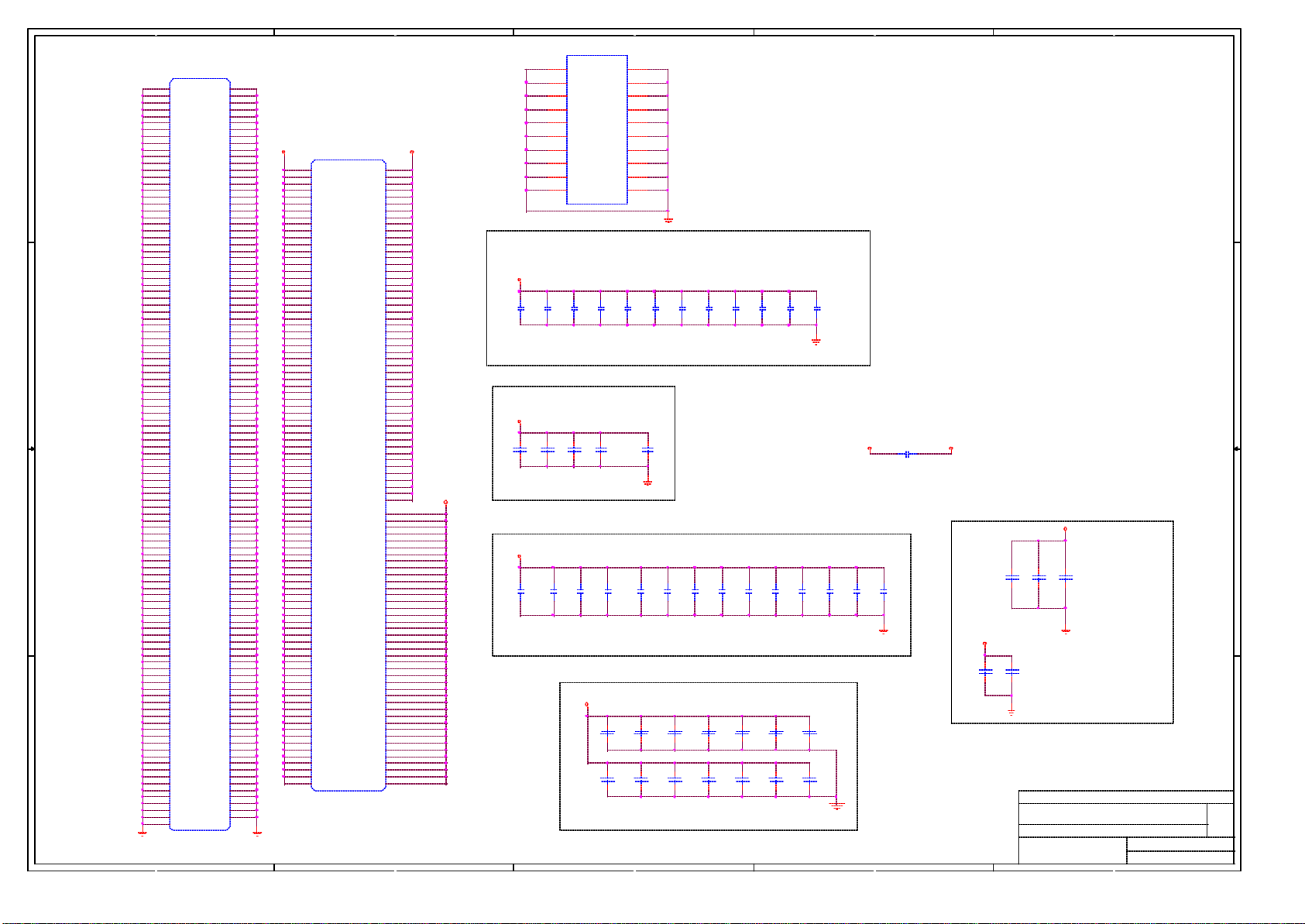

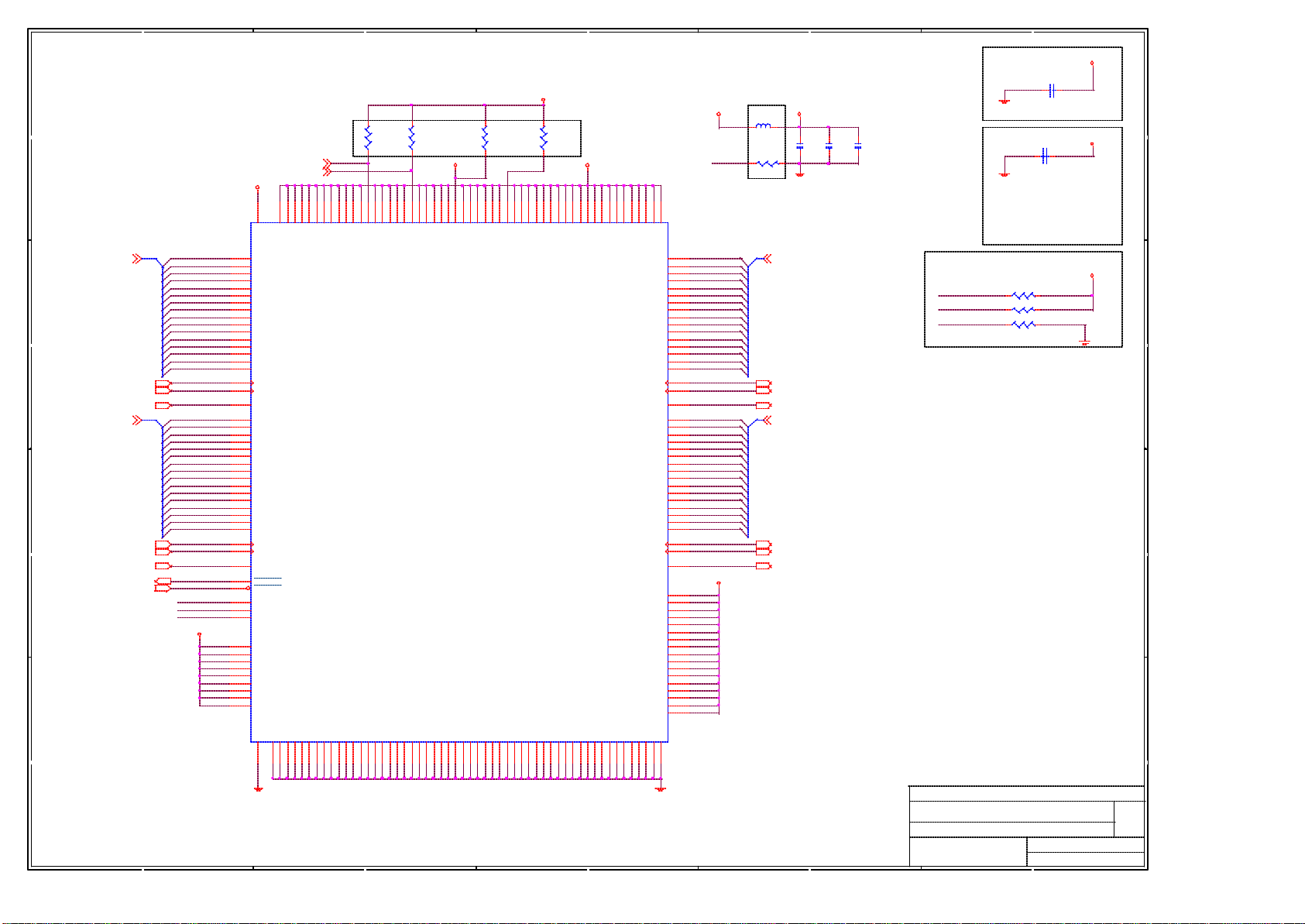

Page 2

5

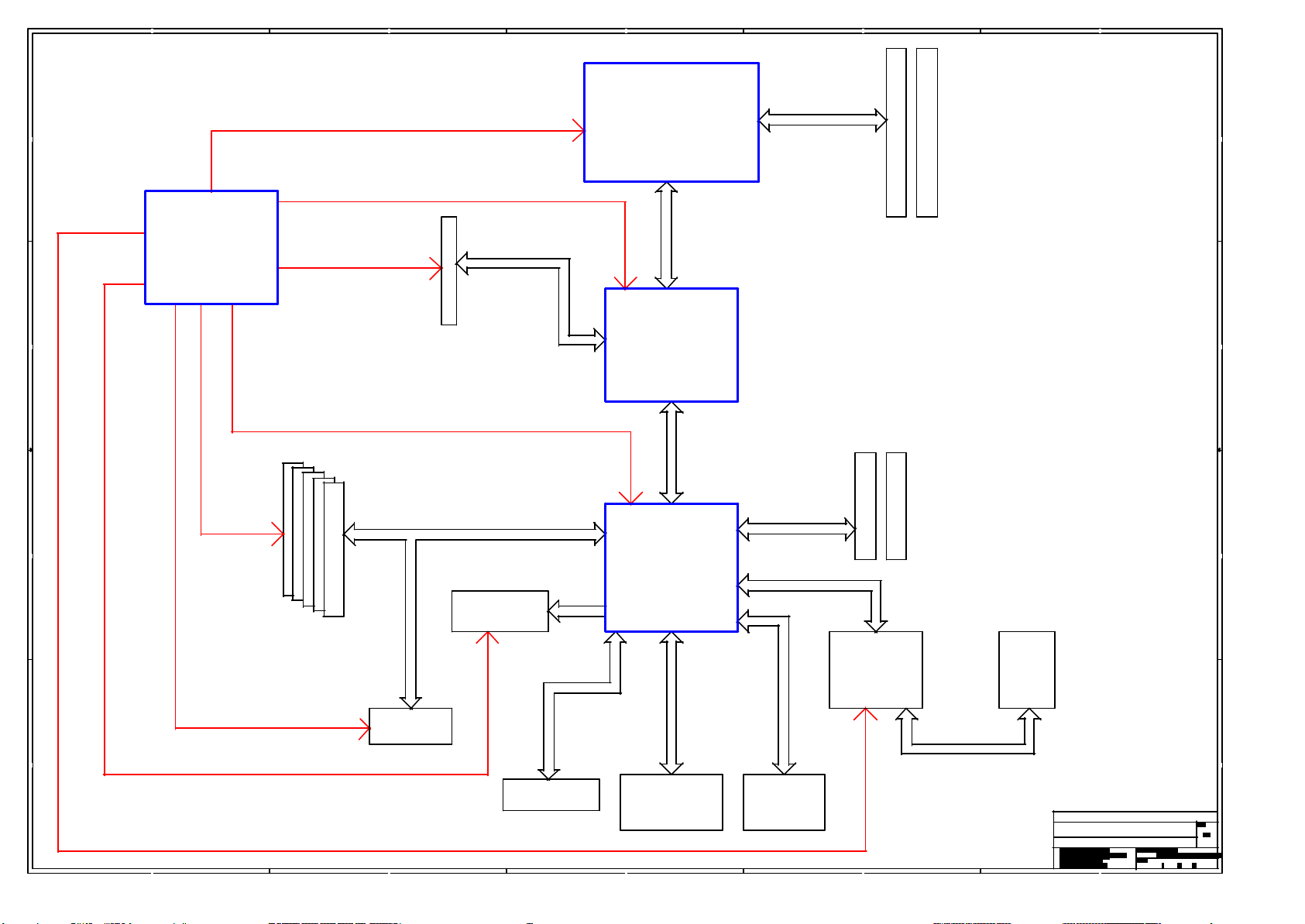

Block Diagram

4

3

2

1

D D

CPUCLK+ & CPUCLK-(100/133/166/200)

AMD K8 Socket 754

DDR400

HCLK+ & HCLK-(100/133/166/200) / GCLK(66)

SYSTEM CLOCK

Synthesizer

C C

AGPCLK(66)

A

G

AGP 8X /Fast Write

P

S

L

O

T

K8T800/K8T800A

VCLK(66) / OSC(14) / PCISB(33) / USBCLK(48) / APICCLK(14)

PCICLK[0~5]

B B

5 PCI Slots

PCI-33

AC97 => S/W Audio

ALC655 / 6 channel

AC97

HT

VIA

VT8237

VLINK

Dual ATA 100/133

LPC BUS

IDE Slot

==>ATA66,100,133 *2

DDR * 2

SUPER I/O

USB

GLANCLK(33)

A A

AC_14(14)

Giga Bit LAN

RTL8110S

SERIAL ATA *2

Dual USB 1.1 O HCI

/2.0 EHCI 8 Ports

==> Front-Port * 4 ,

Back-Port *4

MII

10/100 LAN

RTL8201BL

W83697HF

X BUS

SIOPCLK(33)/SIO48M(48)

5

4

3

2

ROM

Micro Star Restricted Se cret

Title

Document Number

Block Diagram

MS-7032

1

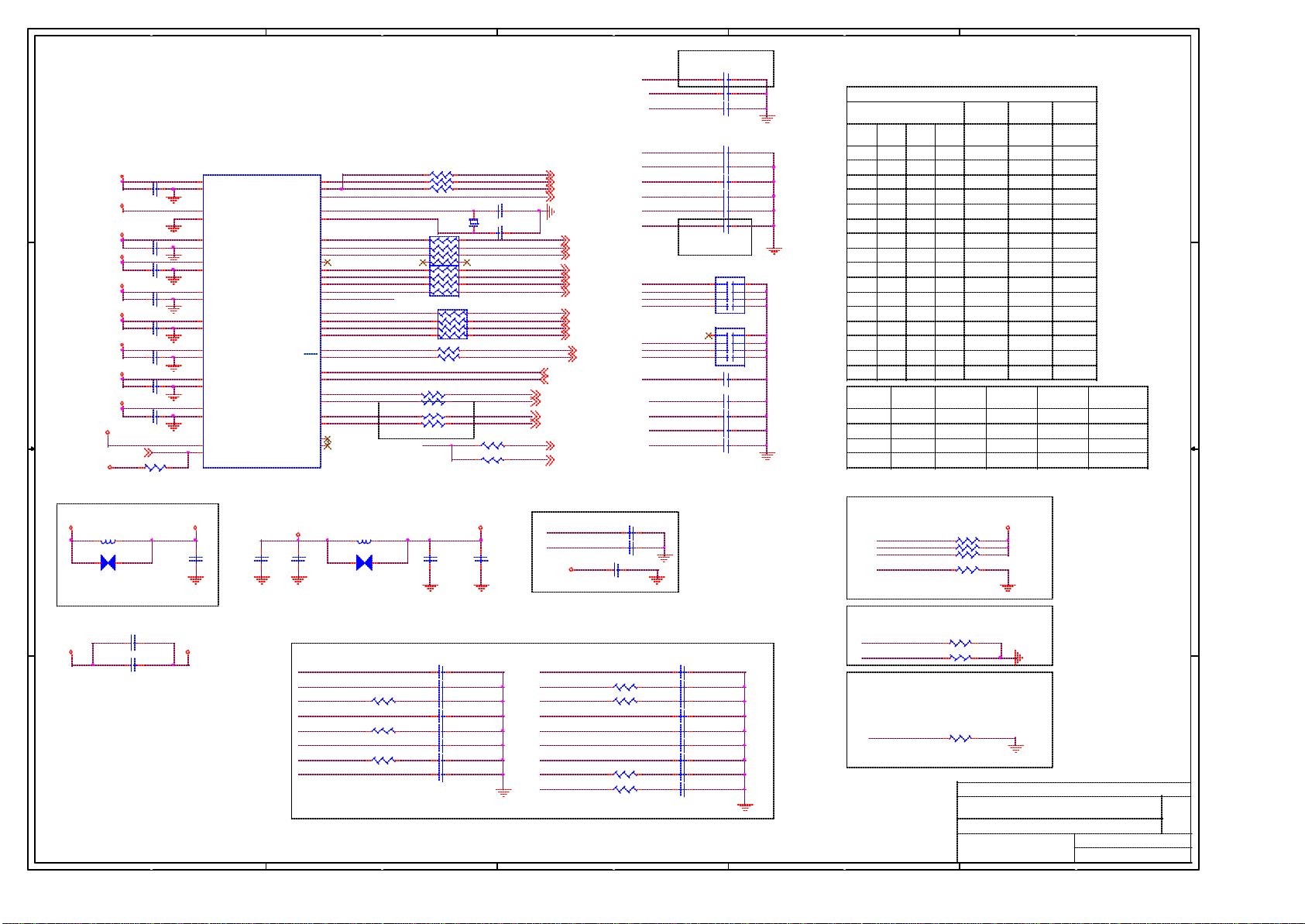

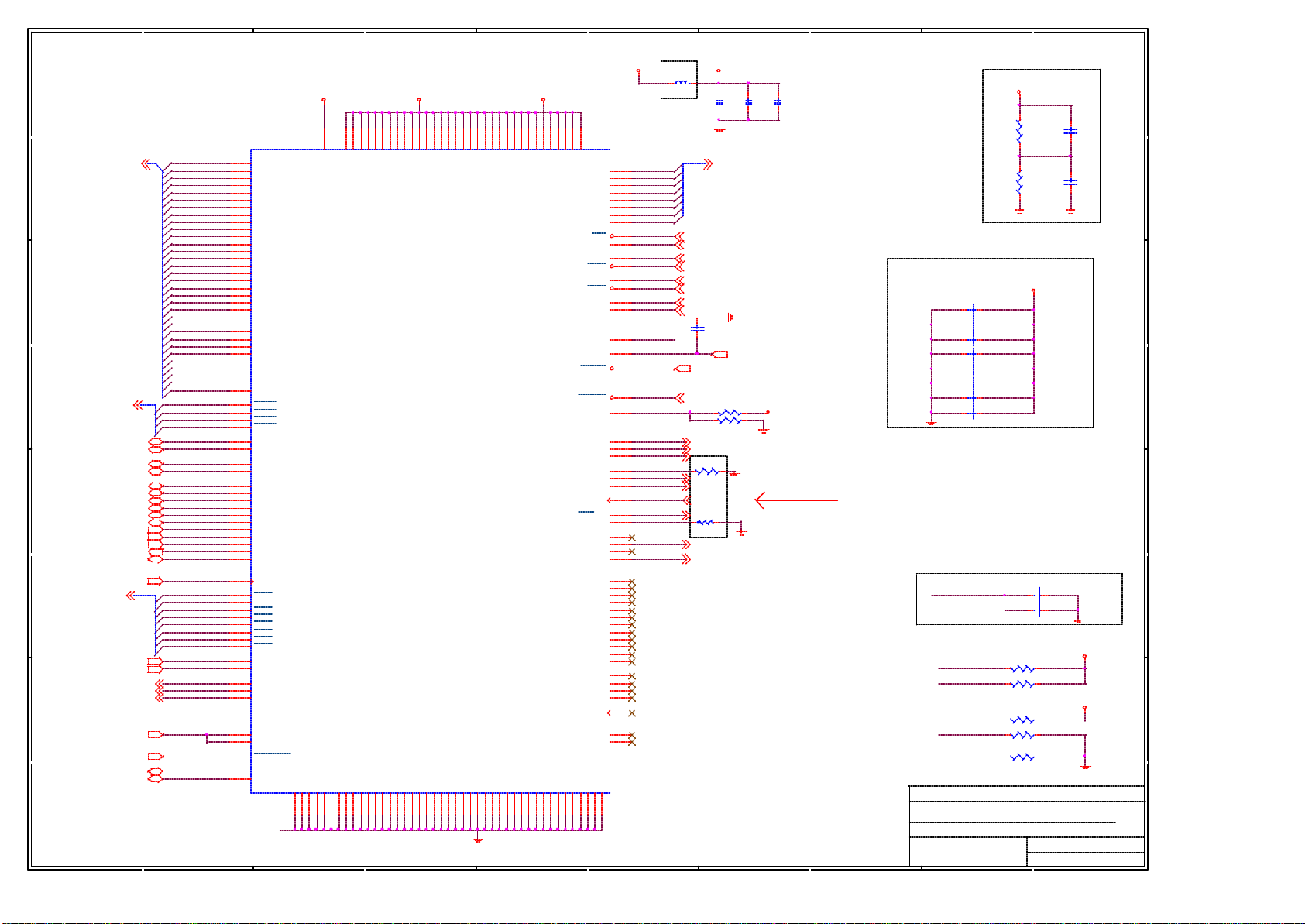

Page 3

5

4

3

2

1

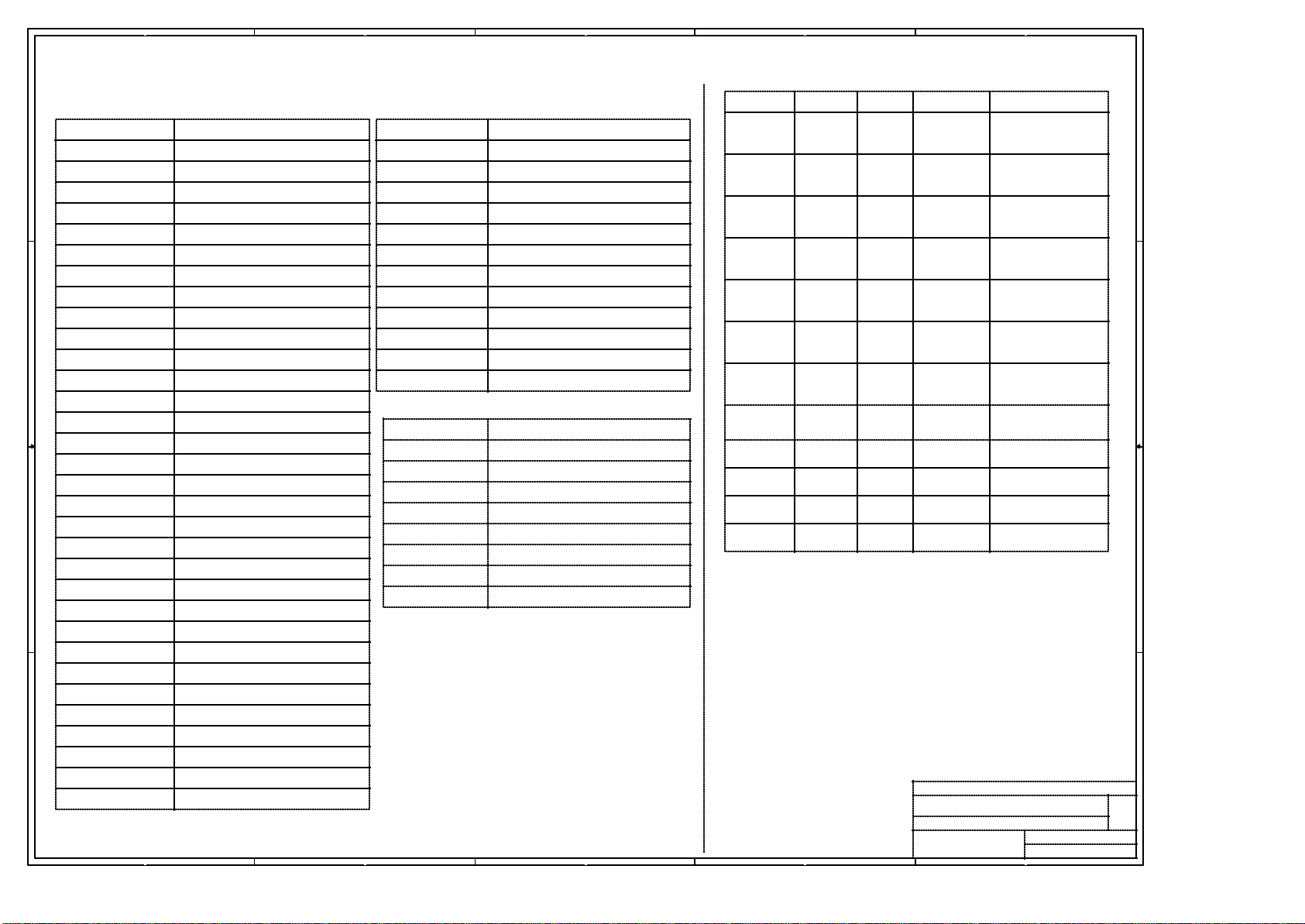

GPIO FUNCTION

VT8237 GPIO Function Define

PIN NAME

D D

GPO0 (VSUS33)

GPO1/SUSA#(VSUS33)

GPO2/SUSB#(VSUS33)

GPO3/SUSST1#(VSUS33)

GPO4/SUSCLK(VSUS33)

GPO5/CPUSTP#

GPO6/PCISTP#

GPO7/SLP#

GPO8/GPI8/IPBIN0

GPO9/GPI9/IPBIN1

C C

GPO10/GPI10/IPBRDFR

GPO11/GPI11/IPBRDCK

GPO12/GPI12/INTE#

GPO13/GPI13/INTF#

GPO14/GPI14/INTG#

GPO15/GPI15/INTH#

GPO16/SA16/STRAP

GPO17/SA17/STRAP

GPO18/SA18/STRAP

GPO19/SA19/STRAP

B B

GPO20/GPI20

/ACSDIN2/PCS0#/EI

GPO21/GPI21/ACSDIN3

/PCS1#/SLPBTN#

GPO22/GPI22/IOR#

GPO23/GPI23/DPSLP

GPO24/GPI24/GPIOA

GPO25/GPI25/GPIOC

GPO26/GPI26/SMBDT2

(VSUS33)

GPO27/GPI27/SMBCK2

(VSUS33)

GPO28/GPI28/

VIDSEL

GPO29/GPI29/

A A

VRDSLP

GPO30/GPI30/GPIOD

GPO31/GPI31/GPIOE

5

NA

NA

SUSB#

SUSST#

NA (Exteranl Pull up to 3VDUAL)

NA (Exteranl Pull up to VCC3)

NA (Exteranl Pull up to VCC3)

LDTSTOP#

NA

NA

NA

NA

VSET0

VSET1

VSET2

NA

LDT Freq Strapping Bit0

LDT Freq Strapping Bit1

LDT Width (Low=8 Bit)

Fast Command (Low=Disable)

POWERF1

POWERF2

NA

ROMLOCK

NA

NA

SMBDATA2/Slave SMBUS

SMBCLK2/Slave SMBUS

NA

NA

NA

NA

PIN NAME Function defineFunction define

GPI0

GPI1

GPI2/EXTSMI#

GPI3/RING#

GPI4/LID#

GPI5/BATLOW#

GPI6/AGPBZ#

GPI7/REQ#5

GPI16/INTRUDER#

GPI17/CPUMISS

GPI18/AOLGP1/THRM#

GPI19/IORDY

(Exteranl Pull up to VBAT)NA

ATADET0=>Detect IDE1 ATA100/66

EXTSMI#

RING#

ATADET1=>Detect IDE2 ATA100/66

(Exteranl Pull up to 3VDUAL)

NA

POWERF3

(Exteranl Pull up to 3VDUAL)

NA

(Exteranl Pull up to VBAT)

NA

(Exteranl Pull up to 3VDUAL)

NA

THRM#

(Exteranl Pull up to VCC3)NA

S/IO GPIO Function Define

PIN NAME Function define

GPBX/GP13

GPAY/GP15

GPAS1/GP10

GPAS2/GP17

GPAX/GP12

GPBY/GP14

GPBS1/GP11

GPBS2/GP16

4

LED#4

LED#2

LED1

LED4

LED#3

LED#1

LED2

LED3

3

PCI Routing

DEVICES

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

PCI SLOT 5

Giga-Bit

LAN

INT#

INT#A

INT#B

INT#C

INT#D

INT#B

INT#C

INT#D

INT#A

INT#C

INT#D

INT#A

INT#B

INT#D

INT#A

INT#B

INT#C

INT#B

INT#C

INT#D

INT#A

INT#A AD22 GLAN_PCLK

2

IDSEL

AD16

AD17

AD18

AD19

AD21

REQ#/GNT#

PREQ#6

PGNT#6

PREQ#3

PGNT#3

PREQ#4

PGNT#4

PREQ#7

PGNT#7

PREQ#8

PGNT#8

PREQ#1

PGNT#1

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

CLOCK

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

GPIO Spec.

MS-7032

Last Revision Date:

Wednesday, January 28, 2004

Sheet

3 37

1

Rev

100

of

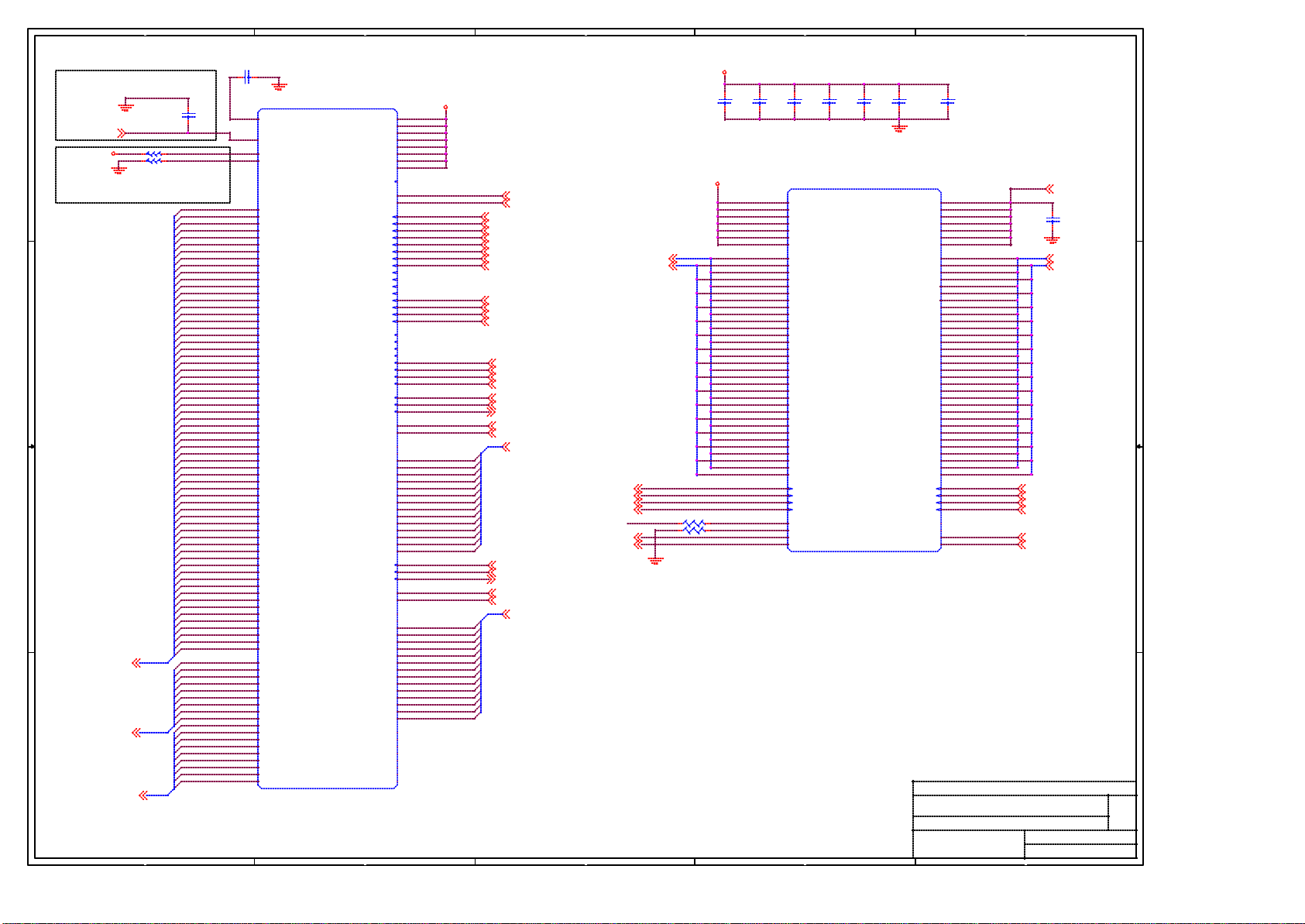

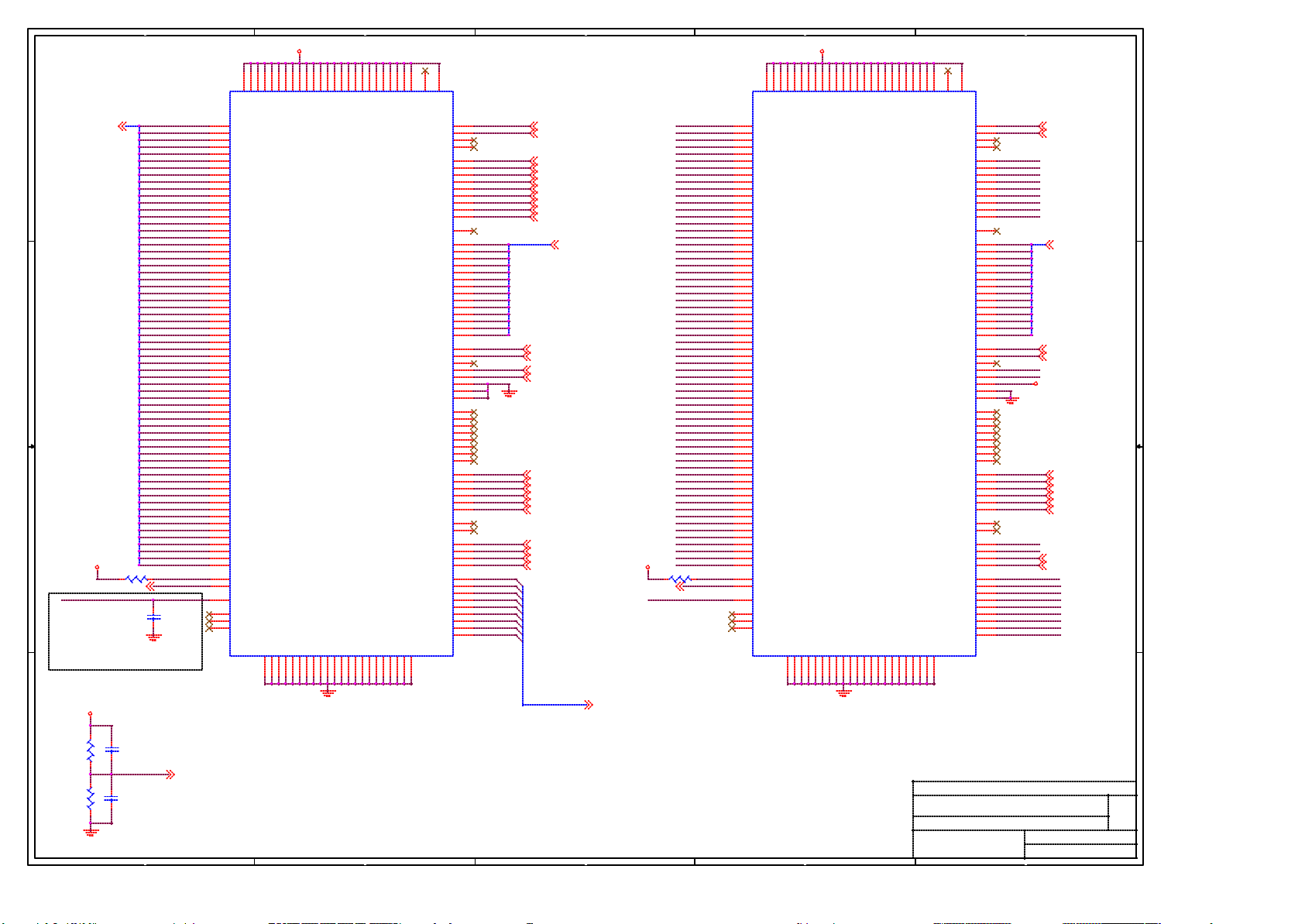

Page 4

5

4

3

2

1

MEMZN

MEMZP

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

DM8

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

-MDQS8

-MDQS7

-MDQS6

-MDQS5

-MDQS4

-MDQS3

-MDQS2

-MDQS1

-MDQS0

C38

X_C1000P50N

AE13

VTT_SENSE

AG12

MEMVREF1

D14

MEMZN

C14

MEMZP

A16

MEMDATA63

B15

MEMDATA62

A12

MEMDATA61

B11

MEMDATA60

A17

MEMDATA59

A15

MEMDATA58

C13

MEMDATA57

A11

MEMDATA56

A10

MEMDATA55

B9

MEMDATA54

C7

MEMDATA53

A6

MEMDATA52

C11

MEMDATA51

A9

MEMDATA50

A5

MEMDATA49

B5

MEMDATA48

C5

MEMDATA47

A4

MEMDATA46

E2

MEMDATA45

E1

MEMDATA44

A3

MEMDATA43

B3

MEMDATA42

E3

MEMDATA41

F1

MEMDATA40

G2

MEMDATA39

G1

MEMDATA38

L3

MEMDATA37

L1

MEMDATA36

G3

MEMDATA35

J2

MEMDATA34

L2

MEMDATA33

M1

MEMDATA32

W1

MEMDATA31

W3

MEMDATA30

AC1

MEMDATA29

AC3

MEMDATA28

W2

MEMDATA27

Y1

MEMDATA26

AC2

MEMDATA25

AD1

MEMDATA24

AE1

MEMDATA23

AE3

MEMDATA22

AG3

MEMDATA21

AJ4

MEMDATA20

AE2

MEMDATA19

AF1

MEMDATA18

AH3

MEMDATA17

AJ3

MEMDATA16

AJ5

MEMDATA15

AJ6

MEMDATA14

AJ7

MEMDATA13

AH9

MEMDATA12

AG5

MEMDATA11

AH5

MEMDATA10

AJ9

MEMDATA9

AJ10

MEMDATA8

AH11

MEMDATA7

AJ11

MEMDATA6

AH15

MEMDATA5

AJ15

MEMDATA4

AG11

MEMDATA3

AJ12

MEMDATA2

AJ14

MEMDATA1

AJ16

MEMDATA0

R1

MEMDQS17

A13

MEMDQS16

A7

MEMDQS15

C2

MEMDQS14

H1

MEMDQS13

AA1

MEMDQS12

AG1

MEMDQS11

AH7

MEMDQS10

AH13

MEMDQS9

T1

MEMDQS8

A14

MEMDQS7

A8

MEMDQS6

D1

MEMDQS5

J1

MEMDQS4

AB1

MEMDQS3

AJ2

MEMDQS2

AJ8

MEMDQS1

AJ13

MEMDQS0

U7B

RSVD_MEMADDA15

RSVD_MEMADDA14

RSVD_MEMADDB15

RSVD_MEMADDB14

MEMORY INTERFACE

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

4

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

VTT_DDR_SUS

MCKE0

MCKE1

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

-MCS3

-MCS2

-MCS1

-MCS0

-MSRASA

-MSCASA

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

MCKE0 8,9

MCKE1 8,9

MEMCLK_H7 8,9

MEMCLK_L7 8,9

MEMCLK_H6 8,9

MEMCLK_L6 8,9

MEMCLK_H5 8,9

MEMCLK_L5 8,9

MEMCLK_H4 8,9

MEMCLK_L4 8,9

MEMCLK_H1 8,9

MEMCLK_L1 8,9

MEMCLK_H0 8,9

MEMCLK_L0 8,9

-MCS3 8,9

-MCS2 8,9

-MCS1 8,9

-MCS0 8,9

-MSRASA 8,9

-MSCASA 8,9

-MSWEA 8,9

MEMBANKA1 8,9

MEMBANKA0 8,9

MAA[13..0] 8,9

-MSRASB 8,9

-MSCASB 8,9

-MSWEB 8,9

MEMBAKB1 8,9

MEMBAKB0 8,9

MAB[13..0] 8,9

CADIP[0..15]11

CLKIP111

CLKIN111

CLKIP011

CLKIN011

VLDT0

CTLIP011

CTLIN011

3

VREF routed as 40~50 mils trace wide ,

Space>25 mils

D D

C C

B B

A A

DDR_VREF8

MD[63..0]10

DM[8..0]10

-MDQS[8..0]10

R95 15R1%

R98 15R1%

5

VDD_25_SUS

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

C1000P50X

VDD_12_A

X_C0.22U16Y

VDD_12_A

CADIN15

CADIN14

CADIN13

CADIN12

CADIN11

CADIN10

CADIN9

CADIN8

CADIN7

CADIN6

CADIN5

CADIN4

CADIN3

CADIN2

CADIN1

CADIN0

R51 49.9R1%

R56 49.9R1%

C149

CADIP15

CADIP14

CADIP13

CADIP12

CADIP11

CADIP10

CADIP9

CADIP8

CADIP7

CADIP6

CADIP5

CADIP4

CADIP3

CADIP2

CADIP1

CADIP0

CTLIP1

CTLIN1

C0.22U16Y

C134

D29

D27

D25

C28

C26

B29

B27

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

Y25

W25

Y27

Y28

R27

R26

T29

R29

C136

C0.22U16Y

U7A

N12-7540020-A10

VLDT0_A6

VLDT0_A5

VLDT0_A4

VLDT0_A3

VLDT0_A2

VLDT0_A1

VLDT0_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

2

X_C0.22U16Y

C147

C0.22U16Y

HYPER TRANSPORT - LINK0

C210

C0.22U16Y

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

C227

C135

C0.22U16YC29

AH29

AH27

AG28

AG26

AF29

AE28

AF25

CADOP15

N26

CADON15

N27

CADOP14

L25

CADON14

M25

CADOP13

L26

CADON13

L27

CADOP12

J25

CADON12

K25

CADOP11

G25

CADON11

H25

CADOP10

G26

CADON10

G27

CADOP9

E25

CADON9

F25

CADOP8

E26

CADON8

E27

CADOP7

N29

CADON7

P29

CADOP6

M28

CADON6

M27

CADOP5

L29

CADON5

M29

CADOP4

K28

CADON4

K27

CADOP3

H28

CADON3

H27

CADOP2

G29

CADON2

H29

CADOP1

F28

CADON1

F27

CADOP0

E29

CADON0

F29

CLKOP1

J26

CLKON1

J27

CLKOP0

J29

CLKON0

K29

N25

P25

CTLOP0

P28

CTLON0

P27

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

VLDT0

CLKOP1 11

CLKON1 11

CLKOP0 11

CLKON0 11

CTLOP0 11

CTLON0 11

K8 DDR & HT

MS-7032

Last Revision Date:

Sheet

1

VLDT0 5

C39

C4.7U10Y0805

CADOP[0..15] 11

CADON[0..15] 11CADIN[0..15]11

Rev

Friday, January 30, 2004

4 37

of

100

Page 5

5

D D

4

LAYOUT: Route VDDA trace approx. 50 mils wide (use 2x25 mil

VDDA_25

traces to exit ball field) and 500 mils long.

FB2 300L700m_250_0805

CPU_VDDA_25

C37

X_C1000P50N

VDDIO_SENSE

3

C55

C4.7U10Y0805

C34

C0.22U16Y

VCCA_PLL trace length from the VR1 to the

PGA must be 0.75".

2

Place al filters close to the PGA.

Keep all power and signal trce away from

the VR1.

Place a cut in the GND plane around the

VCCA_PLL regulator circuit.

C44

C1000P50X

FB1

X_120S/0603

1

THERMDC_CPU

AH25

C27

VCC2_5

C C

-LDTSTOP

R168

1KR

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

CPU_GD31

VLDT0

VLDT04

R62 44.2R1%

R63 44.2R1%

HDT Test Port Signal .

B B

DBREQ_L

DBRDY

TMS

TCK

TRST_L

TDI

NC_AH18

NC_AJ18

A A

NC_AG18

NC_AG17

NC_C19

NC_D18

NC_D20

NC_B19

NC_C21

5

R50 1KR

R49 1KR

1 2

3 4

5 6

7 8

RN44 8P4R-1KR

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R101 1KR

VCC2_5

C18

C4.7U10Y0805

RN4

8P4R-1KR

8P4R-1KR

RN39

4

X_C1000P50N

C52

C1000P50X

C53

C1000P50X

VDD_25_SUS

-CPURST33

-LDTSTOP11,18

COREFB_H14

COREFB_L14

Differential , "10:10:5:10:10" .

CPUCLK0_H7

Near CPU in 0.5" .

CPUCLK0_L7

3

CPU_GD

L0_REF1

L0_REF0

C47 C0.039U16X

C46 C0.039U16X

R54 820R

R47 820R

VTT_DDR_SUS

VCC2_5

R100 1KR

R99 1KR

VDDIO_SENSE

169R1%

R65

3 4

5 6

7 8

1 2

NC_AJ23

NC_AH23

DBRDY

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

NC_AE23

NC_AF23

NC_AF22

NC_AF21

RN8

8P4R-1KR

CLKIN_H

CLKIN_L

AJ25

AF20

AE18

AJ27

AF27

AE26

AE12

AF12

AE11

AJ21

AH21

AJ23

AH23

AE24

AF24

C16

AG15

AH17

C15

C18

AJ28

AE23

AF23

AF22

AF21

AG2

AH1

AE21

C20

AG4

AG6

AG9

A23

A24

B23

E20

E17

B21

A21

A19

A28

C1

J3

R3

AA2

D3

B18

C6

AE9

VDDA1

VDDA2

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

VTT_A5

VTT_B5

DBRDY

NC_C15

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

KEY1

KEY0

NC_AE23

NC_AF23

NC_AF22

NC_AF21

FREE29

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

FREE7

FREE11

FREE12

FREE13

FREE14

FREE40

U7C

THERMTRIP_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

G_FBCLKOUT_H

G_FBCLKOUT_L

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

NC_AF18

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

2

THRM#

A20

THERMDA_CPU

A26

THERMDC_CPU

A27

VID4

AG13

VID3

AF14

VID2

AG14

VID1

AF15

VID0

AE15

NC_AG18

AG18

NC_AH18

AH18

NC_AG17

AG17

NC_AJ18

AJ18

FBCLKOUT_H

AH19

AJ19

AE19

D20

C21

D18

C19

B19

A22

AF18

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

R64

80.6R1%

FBCLKOUT_L

Zdiff = 80 ohm

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

VID2

VID3

VID1

VID0

VID4

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

THRM# 31

THERMDA_CPU 25,26

THERMDC_CPU 25

VID4 14

VID3 14

VID2 14

VID1 14

VID0 14

LAYOUT: Route

FBCLKOUT_H/L differentially

with 20/8/5/8/20 spacing and

trace width. ( In CPU

breakout => routed 5:5:5 )

VDD_25_SUS

R102

1KR

RN5

1 2

3 4

5 6

7 8

X_8P4R-4.7KR

R36 X_4.7KR

K8 HDT & MISC

MS-7032

Last Revision Date:

Sheet

1

VCC2_5

Rev

Friday, January 30, 2004

5 37

of

100

Page 6

5

U7E

B2

VSS1

AH20

VSS3

AB21

VSS4

W22

VSS5

M23

VSS6

L24

VSS7

AG25

VSS8

AG27

VSS9

AA10

AE16

G20

R20

U20

W20

AA20

AC20

AE20

AG20

AJ20

D21

H21

M21

AD21

AG21

G22

N22

R22

U22

AG29

AA22

AC22

AG22

AH22

AJ22

D23

H23

AB23

AD23

AG23

G24

N24

R24

U24

W24

AA24

AC24

AG24

AJ24

C25

D26

H26

M26

AD26

AF26

AH26

C27

D28

G28

H15

AB17

AD17

G18

AA18

AC18

D19

H19

AB19

AD19

AF19

N20

D2

VSS10

AF2

VSS11

W6

VSS12

Y7

VSS13

AA8

VSS14

AB9

VSS15

VSS16

J12

VSS17

B14

VSS18

Y15

VSS19

VSS20

J18

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

F21

VSS32

VSS33

K21

VSS34

VSS35

P21

VSS36

T21

VSS37

V21

VSS38

Y21

VSS39

VSS40

VSS41

B22

VSS42

E22

VSS43

VSS44

J22

VSS45

L22

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

F23

VSS57

VSS58

K23

VSS59

P23

VSS60

T23

VSS61

V23

VSS62

Y23

VSS63

VSS64

VSS65

VSS66

E24

VSS67

VSS68

J24

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

B25

VSS78

VSS79

B26

VSS80

VSS81

VSS82

VSS83

T26

VSS84

Y26

VSS85

VSS86

VSS87

VSS88

VSS89

B28

VSS90

VSS91

VSS92

F15

VSS187

VSS188

VSS206

VSS207

B16

VSS208

VSS209

VSS210

VSS211

VSS212

F19

VSS213

VSS214

K19

VSS215

Y19

VSS216

VSS217

VSS218

VSS219

J20

VSS220

L20

VSS221

VSS222

GROUND

5

D D

C C

B B

A A

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

VCORE

GNDGND

AC15

H18

H22

H24

G13

AB14

G15

AA15

H16

AB16

G17

AA17

AC17

AE17

AB18

AD18

AG19

G19

AC19

AA19

H20

M20

AB20

AD20

G21

N21

R21

U21

W21

AA21

AC21

M22

AB22

AD22

G23

N23

R23

U23

W23

AA23

AC23

D24

M24

AB24

AD24

AH24

AE25

U7D

L7

VDD1

VDD2

VDD3

B20

VDD4

E21

VDD5

VDD6

J23

VDD7

VDD8

F26

VDD9

N7

VDD10

L9

VDD11

V10

VDD12

VDD13

K14

VDD14

Y14

VDD15

VDD16

VDD17

J15

VDD18

VDD19

VDD20

K16

VDD21

Y16

VDD22

VDD23

VDD24

J17

VDD25

VDD26

VDD27

VDD28

F18

VDD29

K18

VDD30

Y18

VDD31

VDD32

VDD33

VDD34

E19

VDD35

VDD36

VDD39

VDD38

J19

VDD37

F20

VDD40

VDD41

K20

VDD42

VDD43

P20

VDD44

T20

VDD45

V20

VDD46

Y20

VDD47

VDD48

VDD49

VDD50

J21

VDD51

L21

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

F22

VDD59

K22

VDD60

VDD61

P22

VDD62

T22

VDD63

V22

VDD64

Y22

VDD65

VDD66

VDD67

E23

VDD68

VDD69

L23

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

B24

VDD77

VDD78

F24

VDD79

K24

VDD80

VDD81

P24

VDD82

T24

VDD83

V24

VDD84

Y24

VDD85

VDD86

VDD87

VDD88

VDD89

K26

VDD90

P26

VDD91

V26

VDD92

POWER

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

4

VDD_25_SUS

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

4

VCORE

3

U7F

1

GND

2

GND

3

GND

4

GND

5

GND

6

GND

7

GND

8

GND

9

GND

10

GND

LAYOUT: Place 6 EMI caps along bot tom right side of Clawhammer,

2 in middle of HT link, and 12 along bottom left side of

Claw-hammer.

VCORE

C490

C488

Place between DIMN1 & 2

VDD_25_SUS

C0.1U25Y

VDD_25_SUS

C61

X_C1U16Y

C62

C0.1U25Y

C83

{nopop}

X_C0.22U16Y

C491

X_C6.8P50N

C154

C82

C0.1U25Y

C117

X_C4.7U10Y0805

VCORE

11

GND

12

GND

13

GND

14

GND

15

GND

16

GND

17

GND

18

GND

19

GND

20

GND

GND

C481

C60

C486

X_C6.8P50N

C233

C0.1U25Y

C482

X_C6.8P50N

{nopop}

C484

X_C1U16Y

{nopop}

X_C6.8P50N

C208

C0.1U25Y

X_C1U16Y

GND

LAYOUT: Place beside processor.

C145

{nopop}

X_C0.22U16Y

X_C4.7U10Y0805

C198

C196

C1000P50X

C69

X_C0.22U16Y

X_C4.7U10Y0805

In CPU.

C95

C180P50N

C104

C180P50N

C99

C8.2P50N

C96

C0.22U16Y

C89

C0.22U16Y

C90

C180P50N

3

C131

{nopop}

X_C6.8P50N

C76

C0.22U16Y

C101

C0.22U16Y

C100

C8.2P50N

C175

X_C6.8P50N

C93

C1U16Y0805

C103

C0.22U16Y

C102

C0.22U16Y

C485

X_C6.8P50N

C119

C1U16Y0805

C108

C0.22U16Y

C105

C0.22U16Y

C483

X_C6.8P50N

GND

C141

C1U16Y0805

C92

C0.22U16Y

C107

C8.2P50N

2

X_C1U16Y

VDD_25_SUS VTT_DDR_SUS

C213

C151

C0.22U16Y

C144

X_C0.22U16Y

GND

2

C228

X_C0.2 2U16Y

{nopop}

C0.22U16Y

C494

X_C0.1U25Y

VTT_DDR_SUS

C495

X_C0.1U25Y

VDD_25_SUS

C478

C489

X_C0.1U25Y

BACK

GND

C496

X_C0.1U25Y

GND

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

1

X_C0.1U25Y

K8 POWER & GND

MS-7032

1

Last Revision Date:

Wednesday, January 28, 2004

Sheet

6 37

Rev

100

of

Page 7

5

4

3

2

1

For K8T800 Pro

VCLK

C590 T_C10P50N

GCLK_NB

Clock Synthesizer

D D

CLKVCC3

C324 C0.1U25Y

CLKVCC3

CLKVCC3

C335 C0.1U25Y

CLKVCC3

C347 X_C0.1U25Y

CLKVCC3

C350 C0.1U25Y

CLKVCC3

C321 C0.1U25Y

CLKVCC3

CLKVCC3

CLKVDDA

CLKVCC3

C339 X_C0.1U25Y

CLKVCC3

C357 C0.1U25Y

C332 C0.1U25Y

TURBO#25

R251 10KR

C C

U16

ICS950407AF_SSOP48

46

VDDREF

47

GND

2

VDDHTT

5

GND

9

VDDPCI

10

GND

16

VDDPCI

15

GND

19

VDDPCI

20

GND

28

AVDD48

29

GND

40

VDDCPU

37

GND

36

VDDCPU

33

GND

44

VDDA

43

GND

31

PD#

32

Turbo#

FS0/REF0

FS1/REF1

RESET#

ModeA/HTT66_0

ModeB/PCI33_8/HTT66_1

PCI33_9/HT66_2

PCI33_11/HT66_3

FS2/PCI33_10

PCI33_0

PCI33_1

PCI33_2

PCI33_3

PCI33_4

PCI33_5

PCI33_6

PCI33_7

FS3/48M

24_48MHZ/SEL

SDATA

CPUCLK8T0

CPUCLK8C0

CPUCLK8T1

CPUCLK8C1

CPUCLK8T2

CPUCLK8C2

XOUT

SCLK

1

FS1 GUICLK

48

45

CLKX1

3

XIN

CLKX2

4

MODEA

6

MODEB

7

8

11

FS2

12

13

14

17

PCI33_3

18

21

22

23

24

30

SEL_24 USBCLK_SB

27

SMBDATA1

26

SMBCLK1

25

42

41

39

38

35

34

R396 33R

R232 33R

R240 M_33R

For K8M800

7 8

5 6

3 4

RN78 8P4R-22R1 2

7 8

5 6

3 4

1 2

RN81 8P4R-22R

7 8

5 6

3 4

1 2

RN129 8P4R-22R

R261 33R

R263 33R

R255 15R1%

R256 15R1%

R397 15R1%

R398 15R1%

For K8T800 Pro

PCI33_3 PCICLK5

AC_14

APICCLKFS0

C314 C27P50N

Y5 14.318MHZ32P_D

C315 C27P50N

VCLK

GCLK_NB

GCLK_SLOT

PCICLK1

PCICLK2

PCICLK3

PCICLK4

SBPCLK

GLAN_PCLK

CPUCLK0_H

CPUCLK0_L

HCLK+

HCLK-

R420 22R

R443 22R

SIOPCLK

LPC_PCLK

SIO48MFS3

SMBDATA1 8,17,21,31

SMBCLK1 8,17,21,31

CPUCLK0_H 5

CPUCLK0_L 5

HCLK+ 11

HCLK- 11

PCICLK6

AC_14 22

APICCLK 17,18

GUICLK 12

CLK_RESET# 33

VCLK 18

GCLK_NB 12

GCLK_SLOT 15

PCICLK1 19

PCICLK2 19

PCICLK3 20

PCICLK4 20

SIOPCLK 25

LPC_PCLK 32

SBPCLK 18

GLAN_PCLK 30

SIO48M 25

USBCLK_SB 16

PCICLK5 21

PCICLK6 21

SIO48M

USBCLK_SB

AC_14

APICCLK

GUICLK

FS1

PCICLK1

PCICLK2

PCICLK3

PCICLK4

SIOPCLK

LPC_PCLK

SBPCLK

GLAN_PCLK

GCLK_SLOT

For K8M800

PCICLK5

HCLK+

HCLK-

PCICLK6

C591 X_C10P50N

C592 X_C10P50N

C349 X_C10P50N

C352 X_C10P50N

C326 X_C10P50N

C310 X_C10P50N

C619 X_C10P50N

C611 M_C10P50N

CN23

7 8

5 6

3 4

1 2

X_8P4C-10P50N

CN24

7 8

5 6

3 4

1 2

X_8P4C-10P50N

C348 X_C10P50N

C594 X_C10P50N

C595 C10P50N

C596 C10P50N

C602 X_C10P50N

0 0 0 0

0 0 0

0 0 0

0 0

0 0 0

0 0

0 0

0

***

1

1 1

1 1

1 1 1

1 1

1 1 1

1 1 1

1 1 1 1

ModeA ModeB

***

Strapping CPU

0 0

0 1

1 0

1 1

ICS950410AF

FS0FS2FS3

FS1

1

1 1

1

1 1

1 1

1 1 1

0 0 0

0 0

0 0

0

0 0

0

HTTCLK0

ModeA In

PCICLK7 PCICLK8 PCICLK9 PCICLK10

ModeA In

HTT

MHz

100.90

1

133.90

168.00

202.00

100.20

133.50

166.70

200.40

150.00

180.00

210.00

240.00

270.00

233.33

0

266.67

300.00

Pin6 Pin7

MHz

67.27 33.63

66.95

67.20

67.33

66.80

66.75

66.68

66.80

60.00

60.00

70.00

60.00

67.50

66.67

66.67

75.00

HTTCLK1 HTTCLK2 PCICLK10

HTTCLK1 HTTCLK2 HTTCLK3

PCICLK8 PCICLK9 PCICLK10

PCI

MHz

33.48

33.60

33.67

33.40

33.38

33.34

33.40

33.00

33.00

35.00

30.00

33.75

33.33

33.33

37.50

Pin8 Pin11

"FS0~FS3" are all internal

pull-up via 100K ohm ..

FS0

FS2

FS1

FS3

ModeA,B=0:0 ( Set Pin 7,8 clock

-> 66 MHz Pin11->33Mhz )

MODEB

MODEA

"24_48MHZ/SEL" Freq.-Out select

pin => Low->48MHz , Hi->24MHz .

( Internal pull-up via 100K ohm )

SEL_24

R230 10KR

R236 10KR

R233 10KR

R258 10KR

R252 10KR

R237 10KR

R262 10KR

CLKVCC3

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

Clock Synthesizer

MS-7032

Last Revision Date:

Sheet

1

Rev

Thursday, February 05, 2004

7 37

of

100

VCC3

FB3 X_120S/0805

B B

X_COPPER

For EMI

A A

C398 C0.1U25Y

VCC3 VCC

C446 X_C0.1U25Y

C1U16Y0805

5

C333

CLKVDDA

C293

X_C0.1U25Y

C365

C1U16Y0805

CLKVCC3

C360

C0.1U25Y

VCC3

Decoupling Cap for CPU Clock

VCC3

C371

C0.1U25Y

FB5 X_120S/0805

CP17

X_COPPERCP15

EMI Request(close to Trace Ending)

HCLK+

HCLKGCLK_SLOT

GCLK_NB

VCLK

USBCLK_SB

SBPCLK

PCICLK1

C620 X_C10P50N

C622 X_C10P50N

R460 X_22R

R464 X_22R C628 X_C10P50N

R468 X_22R C632 X_C10P50N

C624 X_C10P50N

C626 X_C10P50N

C630 X_C10P50N

C634 X_C10P50N

4

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

SIOPCLK

SIO48M

GLAN_PCLK

LPC_PCLK

CPUCLK0_H

CPUCLK0_L

C251 C0.1U25Y

R459 X_22R

R461 X_22R

R472 X_22R

N ear CK-Gen in 0.5" .

C338 C8.2P50N

C340 C8.2P50N

C621 X_C10P50N

C623 X_C10P50N

C625 X_C10P50N

C627 X_C10P50N

C629 X_C10P50N

C631 X_C10P50N

C633 X_C10P50N

C635 X_C10P50NR471 X_22R

C636 X_C10P50N

3

Page 8

5

C30

C0.1U25Y

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP1

-MSWEA

DR_MD[63..0]9,10

D D

C C

B B

VDD_25_SUS

R148 4.7KR

-MSWEA4,9

DDR_VREF

VREF routed as 40~50

mils trace wide ,

Space>25 mils

2

4

6

8

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

90

63

1

9

101

102

Place 104p and 1000p Cap. near the DIMM

Place near the DIMM

VDD_25_SUS

R53

1KR1%

A A

R52

1KR1%

C477

X_C0.1U25Y

DDR_VREF

C31

C1U10Y

VREF routed as 40~50 mils trace wide ,

Space>25 mils

DDR_VREF 4

5

VDD_25_SUS

738467085

108

VDD0

VDD1

VDD2

VDD3

VDD4

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

WP(NC)

WE#

VREF

NC2

NC3

NC4

VSS0

VSS1

3111826344250586674818993

120

148

168223054627796

VDD5

VDD6

VDD7

VSS2

VSS3

VSS4

VDD8

VSS5

VDDQ0

VSS6

4

SYSTEM MEMORY

104

112

128

136

143

156

164

172

1801582

184

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

184

DDR DIMM

SOCKET

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

100

116

124

132

139

DIMM1 SLAVE ADDRESS

= (1010000X)B = A0

4

VDDQ11

VDDQ12

VDDQ13

PIN

VSS17

VSS18

VSS19

145

152

160

VDDID

VDDQ14

VDDQ15

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC(RESET#)

VSS20

VSS21

DDR1

DIMM-184_green

176

N13-1840061-K06

CS0#

CS1#

CS2#

CS3#

SCL

SDA

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

BA0

BA1

BA2

SA0

SA1

SA2

3

-MCS0

157

158

71

163

5

14

25

36

56

67

78

86

47

103

MAA0

48

MAA1

43

MAA2

41

MAA3

130

MAA4

37

MAA5

32

MAA6

125

MAA7

29

MAA8

122

MAA9

27

MAA10

141

MAA11

118

MAA12 MAB12

115

MAA13

167

59

52

113

SMBCLK1

92

SMBDATA1

91

181

182

183

44

45

49

51

134

135

142

144

MEMCLK_H5

16

MEMCLK_L5

17

MEMCLK_H0

137

MEMCLK_L0

138

MEMCLK_H7

76

MEMCLK_L7

75

173

10

MCKE0

21

MCKE1

111

-MSCASA

65

-MSRASA

154

DR_DM0

97

DR_DM1

107

DR_DM2

119

DR_DM3

129

DR_DM4

149

DR_DM5

159

DR_DM6

169

DR_DM7

177

DR_DM8

140

-MCS1

-DR_MDQS0

-DR_MDQS1

-DR_MDQS2

-DR_MDQS3

-DR_MDQS4

-DR_MDQS5

-DR_MDQS6

-DR_MDQS7

-DR_MDQS8

MAA[13..0]

-MCS0 4,9

-MCS1 4,9

-DR_MDQS0 9,10

-DR_MDQS1 9,10

-DR_MDQS2 9,10

-DR_MDQS3 9,10

-DR_MDQS4 9,10

-DR_MDQS5 9,10

-DR_MDQS6 9,10

-DR_MDQS7 9,10

-DR_MDQS8 9,10

MAA[13..0] 4,9

MEMBANKA0 4,9

MEMBANKA1 4,9

SMBCLK1 7,17,21,31

SMBDATA1 7,17,21,31

MEMCLK_H5 4,9

MEMCLK_L5 4,9

MEMCLK_H0 4,9

MEMCLK_L0 4,9

MEMCLK_H7 4,9

MEMCLK_L7 4,9

MCKE0 4,9

MCKE1 4,9

-MSCASA 4,9

-MSRASA 4,9

DR_DM[8..0]

DR_DM[8..0] 9,10

VDD_25_SUS

-MSWEB4,9

R147 4.7KR

DDR_VREF

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP2

-MSWEB

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

102

NC4

2

VDD_25_SUS

738467085

108

120

148

168223054627796

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VSS0

VSS1

VSS2

VSS3

VSS4

3111826344250586674818993

DIMM2 SLAVE ADDRESS

= (1010001X)B = A2

104

112

128

VDD8

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

DDR DIMM

SOCKET

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

100

116

136

143

156

VDDQ8

VDDQ9

VDDQ10

VDDQ11

184

VSS14

VSS15

VSS16

VSS17

124

132

139

164

172

1801582

184

VDDID

VDDQ12

VDDQ13

VDDQ14

VDDQ15

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

A11

A12

A13

BA0

BA1

BA2

SCL

PIN

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC5

NC(RESET#)

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VSS18

VSS19

VSS20

VSS21

145

152

160

176

Micro Star Restricted Secret

Title

System Memory : DDR DIMM 1

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

VDDSPD

157

158

71

163

5

14

25

36

56

67

78

86

47

103

48

A0

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

118

115

167

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

DDR2

DIMM-184_green

N13-1840061-K06

-MCS2

-MCS3

-DR_MDQS0

-DR_MDQS1

-DR_MDQS2

-DR_MDQS3

-DR_MDQS4

-DR_MDQS5

-DR_MDQS6

-DR_MDQS7

-DR_MDQS8

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB13

MEMBAKB0

MEMBAKB1

SMBCLK1

SMBDATA1

MCKE0

MCKE1

-MSCASB

-MSRASB

MS-7032

1

-MCS2 4,9

-MCS3 4,9

MAB[13..0] 4,9

MEMBAKB0 4,9

MEMBAKB1 4,9

VDD_25_SUS

MEMCLK_H4 4,9

MEMCLK_L4 4,9

MEMCLK_H1 4,9

MEMCLK_L1 4,9

MEMCLK_H6 4,9

MEMCLK_L6 4,9

-MSCASB 4,9

-MSRASB 4,9

DR_DM0

DR_DM1

DR_DM2

DR_DM3

DR_DM4

DR_DM5

DR_DM6

DR_DM7

DR_DM8

Last Revision Date:

Friday, January 30, 2004

Sheet

8 37

1

Rev

100

of

Page 9

5

4

3

2

1

DDR Terminations

VTT_DDR_SUS VTT_DDR_SUS

DR_MD40

DR_MD39

DR_MD35

D D

DR_MD59

DR_MD63

DR_MD58

DR_MD62

-DR_MDQS7

DR_DM7

DR_MD57

DR_MD61

DR_MD56

DR_MD60

DR_MD51

DR_MD55

C C

B B

MEMBANKA04,8

MEMBAKB04,8

MEMBANKA14,8

DR_MD50

DR_MD54

-DR_MDQS6

DR_DM6

MAA13

MAB13

DR_MD53

DR_MD52

DR_MD49

DR_MD48

DR_MD47

DR_MD46

DR_MD43

DR_MD42

DR_DM5

-DR_MDQS5

-MCS1

-MCS14,8

-MCS0

-MCS04,8

-MSCASA

-MSCASA4,8

DR_MD41

-MSWEB

-MSWEB4,8

DR_MD45

-MSRASB

-MSRASB4,8

DR_MD44

-MSRASA

-MSRASA4,8

RN68 8P4R-27R0402

7 8

5 6

3 4

1 2

RN67 8P4R-27R0402

7 8

5 6

3 4

1 2

RN66 8P4R-27R0402

7 8

5 6

3 4

1 2

RN64 8P4R-27R0402

7 8

5 6

3 4

1 2

RN62 8P4R-27R0402

7 8

5 6

3 4

1 2

RN60 8P4R-27R0402

7 8

5 6

3 4

1 2

RN58 8P4R-27R0402

7 8

5 6

3 4

1 2

RN57 8P4R-27R0402

7 8

5 6

3 4

1 2

RN53 8P4R-27R0402

7 8

5 6

3 4

1 2

RN52 8P4R-27R0402

7 8

5 6

3 4

1 2

MEMBAKB14,8

DR_MD38

DR_MD34

DR_DM4

-DR_MDQS4

DR_MD37

DR_MD33

DR_MD36

DR_MD32

MAB0

MAB10

DR_DM8

-DR_MDQS8

MAA1

MAB1

MAA2

MAB2

MAA3

MAA4

MAB4

MAA6

DR_MD30

MAB3

DR_MD26

DR_DM3

-DR_MDQS3

DR_MD25

DR_MD29

DR_MD28

MAB6

MAB5

MAA5

MAA8

VTT_DDR_SUS

RN50 8P4R-27R0402

7 8

5 6

3 4

1 2

RN48 8P4R-27R0402

7 8

5 6

3 4

1 2

RN47 8P4R-27R0402

7 8

5 6

3 4

1 2

RN43 8P4R-27R0402

7 8

5 6

3 4

1 2

RN36 8P4R-27R0402

7 8

5 6

3 4

1 2

RN32 8P4R-27R0402

7 8

5 6

3 4

1 2

RN35 8P4R-27R0402

7 8

5 6

3 4

1 2

RN34 8P4R-27R0402

7 8

5 6

3 4

1 2

RN29 8P4R-27R0402

7 8

5 6

3 4

1 2

DR_MD24

DR_MD19

DR_MD23

MAA7

DR_DM2

MAA9

MAA11

MAA12

MAB8

DR_MD22

MAB7

DR_MD18

MAB9

MAB11

DR_MD21

-DR_MDQS2

DR_MD17

MAB12

DR_MD16

DR_MD20

DR_MD11

DR_MD10

DR_MD15

DR_MD14

DR_DM1

DR_MD13

-DR_MDQS1

DR_MD12

DR_MD9

DR_MD8

DR_MD3

DR_MD7

DR_MD6

DR_MD2

DR_DM0

-DR_MDQS0

DR_MD1

DR_MD5

DR_MD4

DR_MD0

MAA10

MAA0

DR_MD31

DR_MD27

RN27 8P4R-27R0402

7 8

5 6

3 4

1 2

RN25 8P4R-27R0402

7 8

5 6

3 4

1 2

RN23 8P4R-27R0402

7 8

5 6

3 4

1 2

RN20 8P4R-27R0402

7 8

5 6

3 4

1 2

RN19 8P4R-27R0402

7 8

5 6

3 4

1 2

RN14 8P4R-27R0402

7 8

5 6

3 4

1 2

RN11 8P4R-27R0402

7 8

5 6

3 4

1 2

RN9 8P4R-27R0402

7 8

5 6

3 4

1 2

RN7 8P4R-27R0402

7 8

5 6

3 4

1 2

RN3 8P4R-27R0402

7 8

5 6

3 4

1 2

RN41 8P4R-27R0402

7 8

5 6

3 4

1 2

-MCS2

-MCS24,8

-MCS3

-MCS34,8

MAB13

MAA13

VTT_DDR_SUS

MCKE04,8

MCKE14,8

-MCS3

-MCS34,8

-MCS2

-MCS24,8

-MSCASB

-MSCASB4,8

-MSWEA

-MSWEA4,8

R72 27R0402

R71 27R0402

RN55 8P4R-27R0402

7 8

5 6

3 4

1 2

MEMBAKB14,8

MEMBANKA14,8

MEMBAKB04,8

MEMBANKA04,8

MAB12

MAA12

MAB11

MAA11

MAB1

MAA1

MAB3

MAA3

MAB2

MAA2

MAB6

MAA6

MAB4

MAA4

MAB8

MAA8

MAA5

MAB5

MAA0

MAA10

MAB0

MAB10

-MSCASB

-MSCASB4,8

-MCS0

-MCS04,8

-MSCASA

-MSCASA4,8

-MCS1

-MCS14,8

MAA9

MAB9

MAB7

MAA7

-MSRASB

-MSRASB4,8

-MSRASA

-MSRASA4,8

-MSWEA

-MSWEA4,8

-MSWEB

-MSWEB4,8

MCKE14,8

MCKE04,8

CN20

12

34

56

78

X_8P4C-10P50N

CN6

12

34

56

78

X_8P4C-10P50N

CN14

12

34

56

78

X_8P4C-10P50N

CN13

12

34

56

78

X_8P4C-10P50N

CN12

12

34

56

78

X_8P4C-10P50N

CN10

12

34

56

78

X_8P4C-10P50N

CN15

12

34

56

78

X_8P4C-10P50N

CN19

12

34

56

78

X_8P4C-10P50N

CN8

12

34

56

78

X_8P4C-10P50N

CN18

12

34

56

78

X_8P4C-10P50N

CN17

12

34

56

78

X_8P4C-10P50N

CN4

12

34

56

78

X_8P4C-10P50N

A A

For DIMM2 Clock

MEMCLK_H4

MEMCLK_H44,8 MEMCLK_L5 4,8

MEMCLK_H14,8

MEMCLK_H64,8

MEMCLK_H1

5

C564 C10P50N

C565 C10P50N

C566 C10P50N

MEMCLK_L4

MEMCLK_L1

MEMCLK_L6MEMCLK_H6

MEMCLK_L4 4,8

MEMCLK_L1 4,8

MEMCLK_L6 4,8

4

For DIMM1 Clock

MEMCLK_H54,8

MEMCLK_H74,8

MEMCLK_H04,8

MEMCLK_H5

MEMCLK_H7

C567 C10P50N

C568 C10P50N

C569 C10P50N

MEMCLK_L5

MEMCLK_L7

MEMCLK_L0MEMCLK_H0

3

MEMCLK_L7 4,8

MEMCLK_L0 4,8

DR_DM[8..0]8,10

-DR_MDQS[8..0]8,10

DR_MD[63..0]8,10

MAB[13..0]4,8

MAA[13..0]4,8

DR_DM[8..0]

-DR_MDQS[8..0]

DR_MD[63..0]

MAB[13..0]

MAA[13..0]

2

Micro Star Restricted Secret

Title

DDR Terminations Bank 0

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-7032

Last Revision Date:

Friday, January 30, 2004

Sheet

9 37

1

Rev

100

of

Page 10

5

DM8 DR_DM8

DDR Terminations

-MDQS0 -DR_MDQS0

D D

C C

B B

R66 10R

RN10 8P4R-10R

MD0

1 2

MD4

3 4

MD5

5 6

MD1

7 8

RN13 8P4R-10R

DM0

1 2

3 4

MD6 DR_MD6

5 6

MD7 DR_MD7

7 8

RN16 8P4R-10R

1 2

MD8 DR_MD8

3 4

MD9 DR_MD9

5 6

7 8

MD15

R75 10R

RN18 8P4R-10R

-MDQS1

1 2

MD13 DR_MD13

3 4

DM1

5 6

MD14 DR_MD14

7 8

RN24 8P4R-10R

1 2

MD17

3 4

MD21 DR_MD21

5 6

DM2

7 8

MD18

R78 10R

RN21 8P4R-10R

MD10

1 2

3 4

MD20 DR_MD20

5 6

MD16 DR_MD16

7 8

RN28 8P4R-10R

1 2

MD23 DR_MD23

3 4

5 6

MD24

7 8

RN30 8P4R-10R

1 2

MD29

3 4

5 6

-MDQS3

7 8

RN37 8P4R-10R

MD26

1 2

3 4

MD27

5 6

MD31 DR_MD31

7 8

DR_MD0

DR_MD4

DR_MD5

DR_MD1

DR_DM0

DR_MD2MD2

DR_MD3MD3

DR_MD12MD12

DR_MD15

-DR_MDQS1

DR_DM1

-DR_MDQS2-MDQS2

DR_MD17

DR_DM2

DR_MD18

DR_MD10

DR_MD11MD11

DR_MD22MD22

DR_MD19MD19

DR_MD24

DR_MD28MD28

DR_MD29

DR_MD25MD25

-DR_MDQS3

DR_MD26

DR_MD30MD30

DR_MD27

-MDQS4 -DR_MDQS4

MD42

MD50

MD55

MD56

MD61 DR_MD61

MD57 DR_MD57

DM7

-MDQS7

MD62 DR_MD62

MD58

MD63

4

MD38

R110 10R

RN45 8P4R-10R

1 2

3 4

5 6

7 8

RN49 8P4R-10R

1 2

3 4

DM4

5 6

MD34 DR_MD34

7 8

R116 10R

RN51 8P4R-10R

MD35 DR_MD35

1 2

MD39 DR_MD39

3 4

5 6

MD44 DR_MD44

7 8

RN54 8P4R-10R

1 2

MD41 DR_MD41

3 4

-MDQS5 -DR_MDQS5

5 6

DM5 DR_DM5

7 8

RN56 8P4R-10R

MD43

1 2

MD46 DR_MD46

3 4

MD47 DR_MD47

5 6

7 8

RN59 8P4R-10R

1 2

3 4

MD53 DR_MD53

5 6

7 8

MD51

R135 10R

RN61 8P4R-10R

1 2

3 4

5 6

7 8

RN63 8P4R-10R

1 2

3 4

5 6

7 8

RN65 8P4R-10R

1 2

3 4

5 6

7 8

R145 10R

R141 10R

DR_MD38

DR_MD32MD32

DR_MD36MD36

DR_MD33MD33

DR_MD37MD37

DR_DM4

DR_MD42

DR_MD40MD40

DR_MD45MD45

DR_MD43

DR_MD48MD48

DR_MD49MD49

DR_MD52MD52

DR_DM6DM6

DR_MD51

-DR_MDQS6-MDQS6

DR_MD54MD54

DR_MD50

DR_MD55

DR_MD60MD60

DR_MD56

DR_DM7

-DR_MDQS7

DR_MD58

DR_MD59MD59

DR_MD63

VDD_25_SUS

VTT_DDR_SUS

C25

VTT_DDR_SUS

3

2

LAYOUT: Place on backside,

evenly spaced around VTT fill.

VDD_25_SUS

VDD_25_SUS VDD_25_SUS VDD_25_SUS VDD_25_SUS

C19

X_C0.1U25Y

C28

C0.1U25Y

C43

X_C0.1U25Y

C54

X_C0.1U25Y

C58

X_C0.1U25Y

C63

C0.1U25Y

C68

X_C0.1U25Y

C74

X_C0.1U25Y

C79

C0.1U25Y

C84

X_C0.1U25Y

C91

X_C0.1U25Y

C177

X_C0.1U25Y

C111

X_C0.1U25Y

C113

X_C0.1U25Y

VTT_DDR_SUS

C192

C1000P50X

{nopop}

C242

X_C0.22U16Y

{nopop}

C35

X_C0.22U16Y

{nopop}

X_C0.22U16Y

{nopop}

C240

C123

C0.1U25Y

C129

X_C0.1U25Y

C142

X_C0.1U25Y

C148

X_C0.1U25Y

C153

X_C0.1U25Y

C157

C0.1U25Y

C164

C0.1U25Y

LAYOUT: Locate close

to Clawhammer

socket.

VTT_DDR_SUS

+

EC16

X_.CD1000U6.3EL15

GND

C168

X_C0.1U25Y

C174

X_C0.1U25Y

C172

C0.1U25Y

C184

X_C0.1U25Y

C188

X_C0.1U25Y

C194

C0.1U25Y

C202

C0.1U25Y

+

EC4

.CD1000U6.3EL15

LAYOUT: Place alternating caps to GND and VDD_2.5_SUS in a single line along VTT island.

C40

C1U10Y

C48

C1U10Y

C57

X_C0.1U25Y

C59

X_C0.1U25Y

C66

X_C0.1U25Y

C71

C1U10Y

C77

C1U10Y

C80

X_C0.1U25Y

C86

X_C0.1U25Y

C97

X_C0.1U25Y

C13

C0.1U25Y

C112

X_C0.1U25Y

C121

X_C0.1U25Y

C1U10Y

C127

VTT_DDR_SUSVTT_DDR_SUSVTT_DDR_SUSVTT_DDR_SUSVTT_DDR_SUS

C207

X_C0.1U25Y

C211

X_C0.1U25Y

C214

X_C0.1U25Y

C217

X_C0.1U25Y

C223

C0.1U25Y

C230

X_C0.1U25Y

C133

C1U10Y

1

C146

X_C0.1U25Y

GND

X_C0.1U25Y

C1U10Y

C143

C187

X_C0.1U25Y

C0.22U16Y

C166

GND

C190

C0.1U25Y

C1U16Y0805

2

C197

C204

X_C0.1U25Y

C209

C1U10Y

C212

C216

C1U10Y

X_C0.1U25Y

VDD_25_SUS

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

C219

X_C0.1U25Y

C607

C231

C224

C1U10Y

C0.1U25Y

C0.1U25Y

C0.1U25Y

GND

LAYOUT: Locate close to

Dimm2 socket.

C609

C0.1U25Y

C610

C0.1U25Y

GND

C608

Micro Star Restricted Secret

DDR Terminations Bank 1

MS-7032

Last Revision Date:

Friday, January 30, 2004

Sheet

1

C0.1U25Y

10 37

of

Rev

100

C1U10Y

C248

3

C155

X_C0.1U25Y

C1U16Y0805

C36

C41

X_C1000P50X

C238

C160

C165

X_C0.1U25Y

C33

C1U16Y0805

X_C0.22U16Y

X_C4.7U10Y0805

C150

-MDQS8 -DR_MDQS8

R445 10R

-MDQS[8..0]4

-DR_MDQS[8..0]8,9

DR_MD[63..0]8,9

MD[63..0]4

A A

DR_DM[8..0]8,9

DM[8..0]4

-MDQS[8..0]

-DR_MDQS[8..0]

DR_MD[63..0]

MD[63..0]

DR_DM[8..0]

DM[8..0]

5

DM3

R80 10R

4

DR_DM3

VTT_DDR_SUS

C0.22U16Y

C56

VTT_DDR_SUS

C1000P50NC250

C176

X_C0.1U25Y

C12

C11

X_C4.7U10Y0805

C1000P50X

C246

C181

C1U10Y

C6

C1000P50X

X_C100P50N

GND

C1000P50X

C161

C1U16Y0805

C171

X_C0.1U25Y

LAYOUT: Locate close to

Clawhammer socket.

C203

C182

X_C4.7U10Y0805

Page 11

A

B

C

D

E

VDD_12_A

VDD_12_A

VCC3

CADIP0

CADIP1

CADIP2

CADIP3

CADIP4

CADIP5

CADIP6

CADIP7

CADIP8

CADIP9

CADIP10

CADIP11

CADIP12

CADIP13

CADIP14

CADIP15

CLKIP0

CLKIP1

CTLIP0

CADIN0

CADIN1

CADIN2

CADIN3

CADIN4

CADIN5

CADIN6

CADIN7

CADIN8

CADIN9

CADIN10

CADIN11

CADIN12

CADIN13

CADIN14

CADIN15

CLKIN0

CLKIN1

CTLIN0

VDD_12_A

FB37 T_0R

HCKGND

R395 T_0R

F14

E11

VLDT

VSS

F17

E21

VLDT

VSS

F18

E22

VLDT

VSS

F26

E23

E24E9F10

VLDT

VLDT

VSS

VSS

G25H1H23

R393

M_0R

VLDT

VSS

VLDT

VSS

VLDT

VSS

R392

4 4

HCLK-7

C22

AVDD2

RCADP0

RCADP1

RCADP2

RCADP3

RCADP4

RCADP5

RCADP6

RCADP7

RCADP8

RCADP9

RCADP10

RCADP11

RCADP12

RCADP13

RCADP14

RCADP15

RCLKP0

RCLKP1

RCTLP

RCADN0

RCADN1

RCADN2

RCADN3

RCADN4

RCADN5

RCADN6

RCADN7

RCADN8

RCADN9

RCADN10

RCADN11

RCADN12

RCADN13

RCADN14

RCADN15

RCLKN0

RCLKN1

RCTLN

LDTRST

LDTSTP

RPCOMP

RNCOMP

RTCOMP

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

AGND2

C21

A23

A10

VSS

A8

A24

VLDT

VSS

B8

A25

VLDT

VSS

B13

HCLK+7

A26A9B10

U10A

VLDT

VLDT

VSS

VSS

B15

B17

VLDT

VSS

B19

B23

B24

VLDT

VLDT

VSS

VSS

B21

B22C8D8

B25

VLDT

VSS

B26B9C10

VLDT

VLDT

VSS

VSS

D6

VLDT

VSS

D12

C11

VLDT

VSS

D14

C23

VLDT

VSS

D16

AVDD2

From Claw Hammer To Claw Hammer

CADOP[0..15]4

3 3

CLKOP04

CLKOP14

CTLOP04

CADON[0..15]4

CLKON04

2 2

CLKON14

CTLON04

-LDTRST33

-LDTSTOP5,18

CADOP0

CADOP1

CADOP2

CADOP3

CADOP4

CADOP5

CADOP6

CADOP7

CADOP8

CADOP9

CADOP10

CADOP11

CADOP12

CADOP13

CADOP14

CADOP15

CLKOP0

CLKOP1

CTLOP0

CADON0

CADON1

CADON2

CADON3

CADON4

CADON5

CADON6

CADON7

CADON8

CADON9

CADON10

CADON11

CADON12

CADON13

CADON14

CADON15

CLKON0

CLKON1

CTLON0

-LDTRST

-LDTSTOP

RPCOMP

PNCOMP

RTCOMP

VDD_12_A

1 1

T26

P24

P26

M24

K24

K26

H24

H26

R24

R22

N24

N22

L22

J24

J22

G24

M26

L24

F24

R26

P25

N26

M25

K25

J26

H25

G26

R23

P22

N23

M22

K22

J23

H22

G23

L26

L23

F25

B11

A12

D25

D26

C26

U24

U25

U26

V21

V22

V23

V24

V25

V26

M_0R

C24

VLDT

VSS

D18

VLDT

VSS

C25C9D10

VLDT

VLDT

VSS

VSS

D20

E5E6E8F7F8

D11

VLDT

VSS

D22

VLDT

VSS

R391

M_0R

D23

VLDT

VSS

D24D9E10

VLDT

VLDT

VSS

VSS

F13

F12

VLDT

VSS

HCKGND

F11

F15

VLDT

VLDT

VSS

VSS

J18

F16

J2

F19

VLDT

VSS

J3

F20

VLDT

VSS

J21

F21

VLDT

VSS

J25

R394

M_0R

F22

VLDT

VSS

K4G1K10

VLDT

VSS

F23

G21

VLDT

VSS

K11

G22

VLDT

VSS

K12

VLDT

VSS

FOR K8M800

VDD_12_AVCC3HCK

H21

J11

J12

J13

J14

J10

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VSS

VSS

VSS

VSS

VSS

VSS

K16

K17

K23H2L10

K15

K13

K14

J15

J16

VLDT

TCADP10

TCADP11

TCADP12

TCADP13

TCADP14

TCADP15

TCADN10

TCADN11

TCADN12

TCADN13

TCADN14

TCADN15

VSS

L11

J17

K18

VLDT

VLDT

TCADP0

TCADP1

TCADP2

TCADP3

TCADP4

TCADP5

TCADP6

TCADP7

TCADP8

TCADP9

TCLKP0

TCLKP1

TCTLP

TCADN0

TCADN1

TCADN2

TCADN3

TCADN4

TCADN5

TCADN6

TCADN7

TCADN8

TCADN9

TCLKN0

TCLKN1

TCTLN

VSS

VSS

L13

L12

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VSS

K21

L14

L18

VLDT

VSS

L15

VLDT

VSS

FOR K8T800A

B12

A13

B14

A15

A17

B18

A19

B20

E12

D13

E14

D15

D17

E18

D19

E20

B16

E16

A21

C12

A14

C14

A16

A18

C18

A20

C20

E13

C13

E15

C15

C17

E19

C19

D21

C16

E17

A22

L21

M18

N18

N21

P18

P21

R18

T18

T21

T22

T23

T24

T25

U18

U21

U22

U23

(VIA-K8M800-VT8380 )

VCC3HCK

C560

C1000P50X

CADIP[0..15] 4

CLKIP0 4

CLKIP1 4

CTLIP0 4

CADIN[0..15] 4

CLKIN0 4

CLKIN1 4

CTLIN0 4

C561

C1U10Y

CB38

X_C1000P50X

5020

PNCOMP

RTCOMP

RPCOMP

C201 C0.1U25Y

Around NB

VDD_12_A

C506

X_C0.1U25Y

Decoupling capacitors

at NB BGA Area (On

Solder Layer)

VDD_12_A

R127 49.9R1%

R120 100R1%

R126 49.9R1%

Micro Star Restricted Secret

Title

NORTH BRIDGE (HT)

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

A

B

C

D

http://www.msi.com.tw

MS-7032

Last Revision Date: