Page 1

5

4

3

2

1

Title Page

Suzaku

D D

MS-6270

MS-7017

MS-6925-100

MS-6977-10A

MS-6979-10E 505/605-6979-010

C C

ERP Number

501/601-7017-010

501/605-6925-010

505/605-6977-010

Version 1.0c

Functiom

Mainboard

Power Buttom/LED board

PCI Adapter card

Slim type CD-ROM Adapter

Cover Sheet 1

Block Diagram

2

3GPIO SPEC

4,5Intel mPGA478B

Clock Synthesizer 6

Intel Springdale 7,8,9

System Memory

AGP SLOT

ICH5

PCI conn.

82547EI

AD1981B

Audio connector

Intel IDE connector

/ DDR Terminations

SATA connector

10,11

12

13,14

15

162117

18

19

20

MS-7 ACPI Controller

VRM 10.0

1394

*INTEL mPGA 478B Processor

*INTEL Springdale GMCH / ICH5 Chipset

(DDR 400 / AGP 8X) / (integrated serial ATA)

Rear & Front USB Port

LPC I/O SMSC47M287/ FWH

KB/MS/LPT/COM Port/FAN

ATX connector / Front Panel

Manual Part

B B

*Audio codec 1981B

*SMSC47M287 LPC I/O

HISTORY

22

23

24

25

26

27

28

29

*USB 2.0 support x4 (integrated into ICH5)

Model option table

Model type Function BOM Config ERP BOM No.

A A

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

Cover Sheet

MS-7017

Last Revision Date:

Wednesday, January 28, 2004

Sheet

1

1 29

Rev

1.0c

of

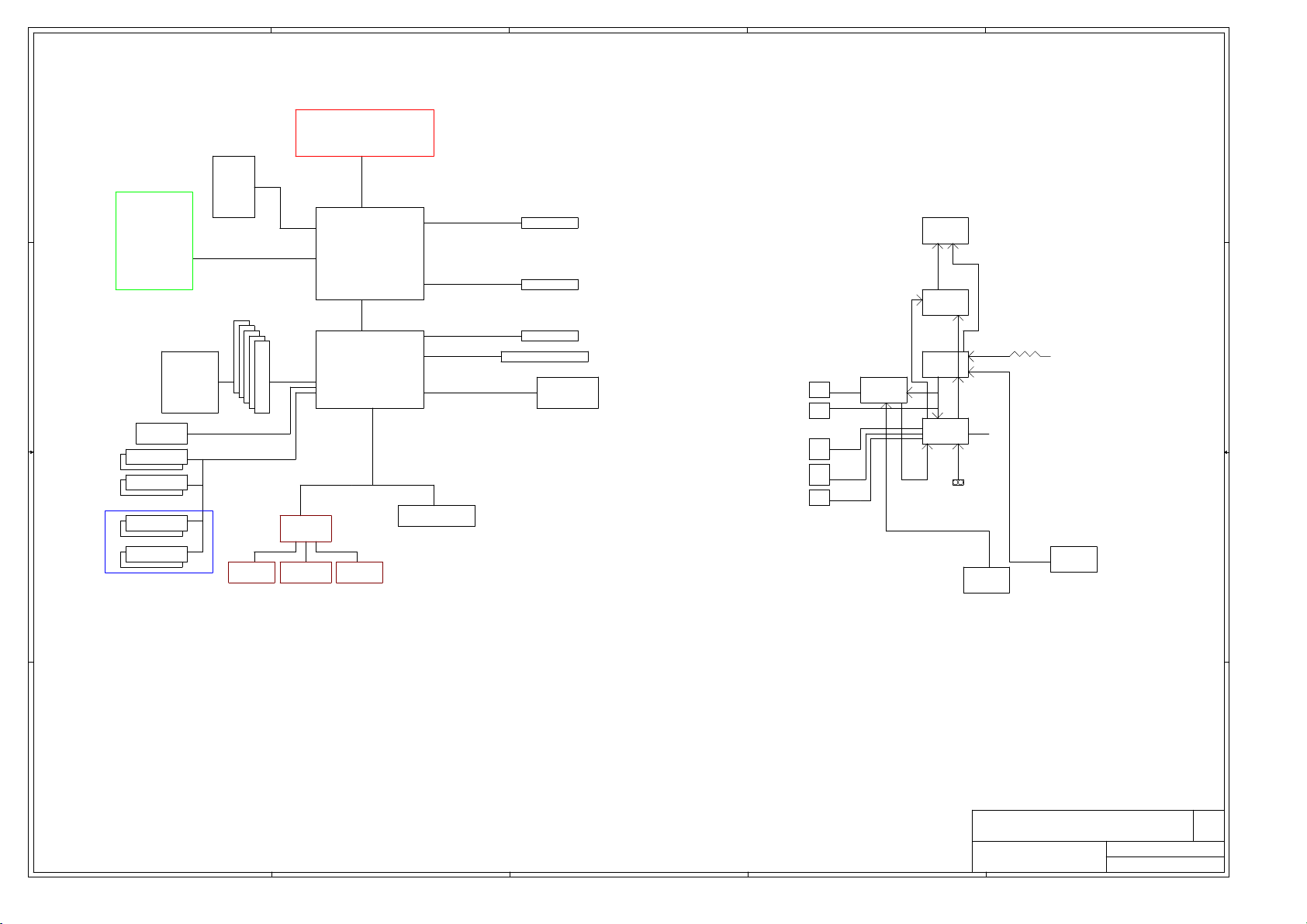

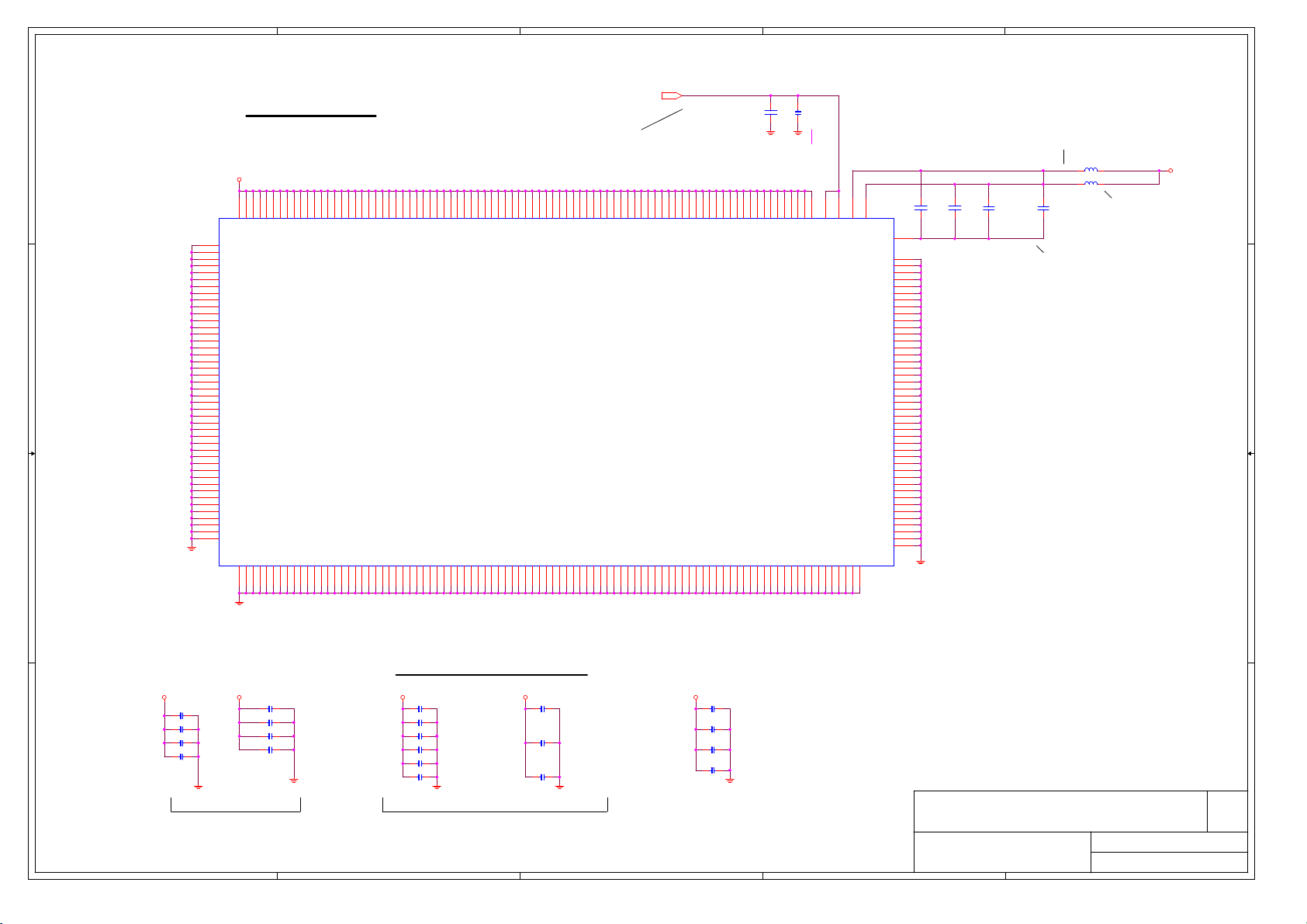

Page 2

5

Block Diagram

4

3

2

1

D D

Intel mPGA478B

FSB 400/533/667

VIA

Lan

1394

Controller

TI

1394

82547EI

AGP 8X /Fast Write

5 PCI Slots

ATA33/ATA66/ATA100

Dual USB 1.1 OHCI

/2.0 EHCI 6 Ports

PS2 Mouse &

Keyboard

CSA

PCI-33

SUPER I/O

SMSC

LPC I/O

47M287

Parallel (1)

Serial (2)

Springdale

Controller HUB

LPC Bus

Floppy Disk

Drive

HUB Interface

ICH5

(33MHz)

(200/266/333/400 MHz)

(200/266/333/400 MHz)

LPC BUS

FWH: Firmware HUB

DDR DIMM1

2 channel DDR 400

DDR DIMM2

Serial ATA

Dual ATA 33/66/100

AC Link

AC97 Codec

1885

SATA Con x2

PCIRST#

HDD

PCIRST#

FWH

PCI

SLOT

PCIRST#

LAN

PCIRST#

PCIRST#

1394

PCIRST_0 for 82547EI

PCIRST_1 for GMCH

PCIRST_2 for 1394

PCIRST_3 PCI Slot

PCIRST_4 for AGP

A

G

P

AGP 8X/4X

(1.5V)

VGA CONN

C C

TSB43AB22A

USB 2.0

Rear x4

Front X4

B B

IDE CONN 1&2

USB Port 0:1

USB Front Panel

USB Port 6:7

USB Front Panel

USB Port 2:3

USB Front Panel

USB Port 4:5

USB Front Panel

RSEST MAP

AJ31

PCIRST#

MS-7

82 LPCPWRGD

CPU

AB25 CPURST# D22

GMCH

ICH5

U5 PCIRST# 25

I/O

AB23

E7

Y23

AB6 PWROK 83

81 FPRST

CPU Power GD

Y3 System RST#

V19 VRMPWRGD

ATX Power GD

ATX

Power

VRM Power GD

3VSB

VRM

+5V : VCC5

+3.3V : VCC3

+12V : +12V

5VSB : VCC5_SB

-12V : -12V

+2.6V for DDR : VCC_DDR

1.3V for DDR VTT : VTT_DDR

Dual 3.3V : 3VSB

1.2V for CPU VID : VCC_VID

1.5V for AGP VI/O : VCC_AGP

A A

Dual 5V : 5VDUAL

CPU Vcore : VCCP

+5V for analog CODEC : +5VR

+1.8VSB for 82547EI : VCCL1.8

+1.2VSB for 82547EI : VCCL1.2

5

4

3

2

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Block Diagram

MS-7017

Last Revision Date:

Sheet

1

Tuesday, January 27, 2004

2 29

of

Rev

1.0c

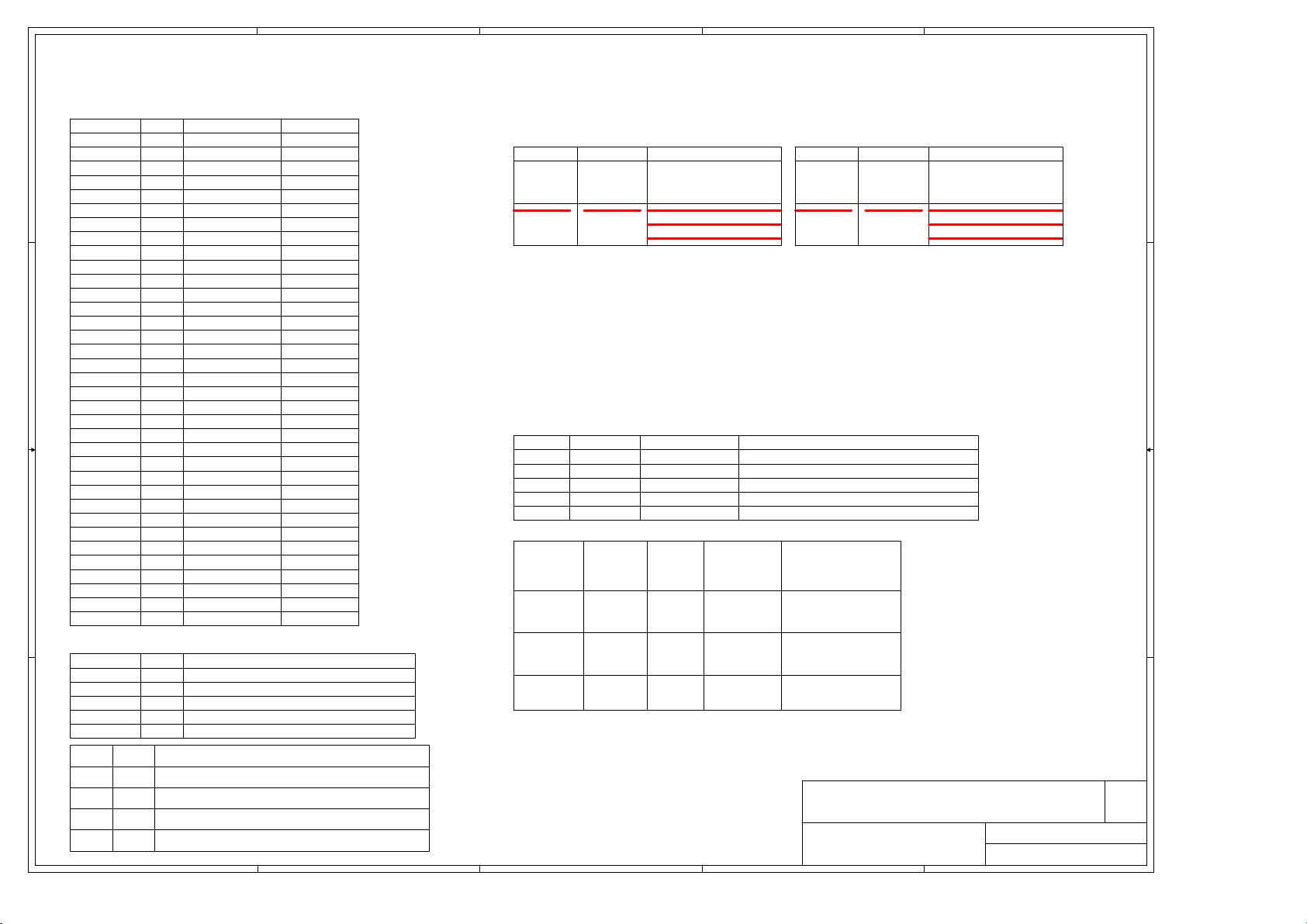

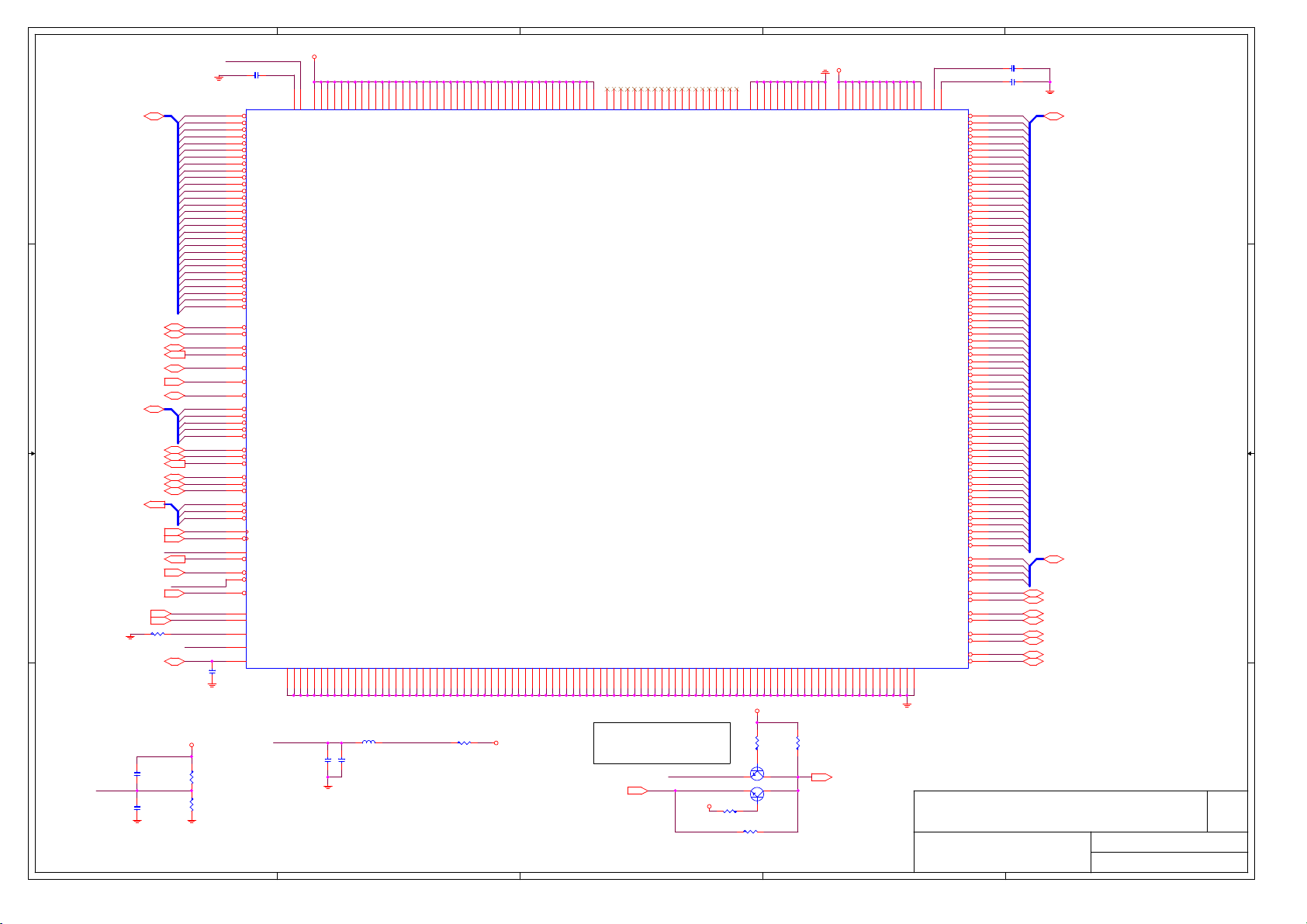

Page 3

5

4

3

2

1

GPIO FUNCTION

ICH5

D D

GPIO 0

GPIO 1

GPIO 2

GPIO 3

GPIO 4

GPIO 5

GPIO 6

GPIO 7

GPIO 8

GPIO 9

GPIO 10

GPIO 11

GPIO 12

GPIO 13

C C

GPIO 14

GPIO 15

GPIO 16

GPIO 17

GPIO 18

GPIO 19

GPIO 20

GPIO 21

GPIO 22

GPIO 23

GPIO 24 I/O

GPIO 25 I/O

GPIO 27

GPIO 28

*

GPIO 32

B B

GPIO 33

GPIO 34

GPIO 40 PREQ#4

GPIO 41

GPIO 48

GPIO 49

FunctionTypeGPIO Pin

I

PREQ#A

I

PREQ#B

I

PIRQ#E

I

PIRQ#F

I

PIRQ#G

I

PIRQ#H

I

GPI6

I

GPI7

I

CSA_PME#

I

OC4#

I

OC5#

I

SIO_SMI#

I

GPI12

I

SIO_PME#

I OC#6

OC#7

I

PGNT#A

O

O

PGNT#B

O NC

O

NC

O

NC

O

NC

OD

NC

O

NC

NC

LAN_DISABLE#

I/O

NC

I/O

NC

I/O

BIOS_WP#

I/O

SATA_LED

I/O

GPIO34

I

GPI41

I

O PGNT#4

CPUPWRGD

OD

FWH

Function

GPI 0 PD_DET

GPI 1

*

GPI 3

GPI 4

*

A A

GPI 4 GPI 2

0 0

0 1

1 0

1 1

TypeGPIO Pin

I

I

SD_DET

I

BOM strapping for Bit 0GPI 2

Pull down through 1K ohms (unused)

I

I

BOM strapping for Bit 1

version control bit

Suzaku-S

Suzaku-M

reserve

reserve

5

Power well

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

IDE-2

80-pin cable = Low

IDE-1

80-pin cable = Low

default output

default output

default output

default output

default output

default output

default output

4

DDR DIMM Config.

DEVICE

DIMM 1 MCLK_A0/MCLK_A0#

1010000B

CLOCKADDRESS

DDR DIMM Config.

DEVICE

DIMM 3 MCLK_B0/MCLK_B0#

MCLK_A1/MCLK_A1#

MCLK_A2/MCLK_A2#

DIMM 2

1010001B

MCLK_A3/MCLK_A3#

DIMM 4

MCLK_A4/MCLK_A4#

MCLK_A5/MCLK_A5#

LPC I/O 47M287

GP 27

GP 42

GP 43

GP 60

GP 61

I : VTR

I : VTR

OD : VTR for LPC PME

I : VTR GP-I

I : VTR GP-I

Default functionDefault typeGPIO Pin

GP-I

GP-I

PME_S5(Default)

alt function

for LPC SMI

for clear password

no connect

no connect

PCI

DEVICES

PCI SLOT 1 PCICLK1-Pin-14

PCI SLOT 2

1394

INT# CLOCK

INT#A

INT#B

INT#C

INT#D

INT#B

INT#C

INT#D

INT#A

INT#F 1394_PCLK-Pin-16

3

IDSEL REQ#/GNT#

AD16

AD17

AD18

PREQ#0

PGNT#0

PREQ#1

PGNT#1

PREQ#2

PGNT#2

PCICLK2-Pin-15

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

2

1010010B

CLOCKADDRESS

MCLK_B1/MCLK_B1#

MCLK_B2/MCLK_B2#

1010011B

MCLK_B3/MCLK_B3#

MCLK_B4/MCLK_B4#

MCLK_B5/MCLK_B5#

Micro Star Restricted Secret

GPIO Spec.

MS-7017

Last Revision Date:

Tuesday, January 27, 2004

Sheet

3 29

1

Rev

1.0c

of

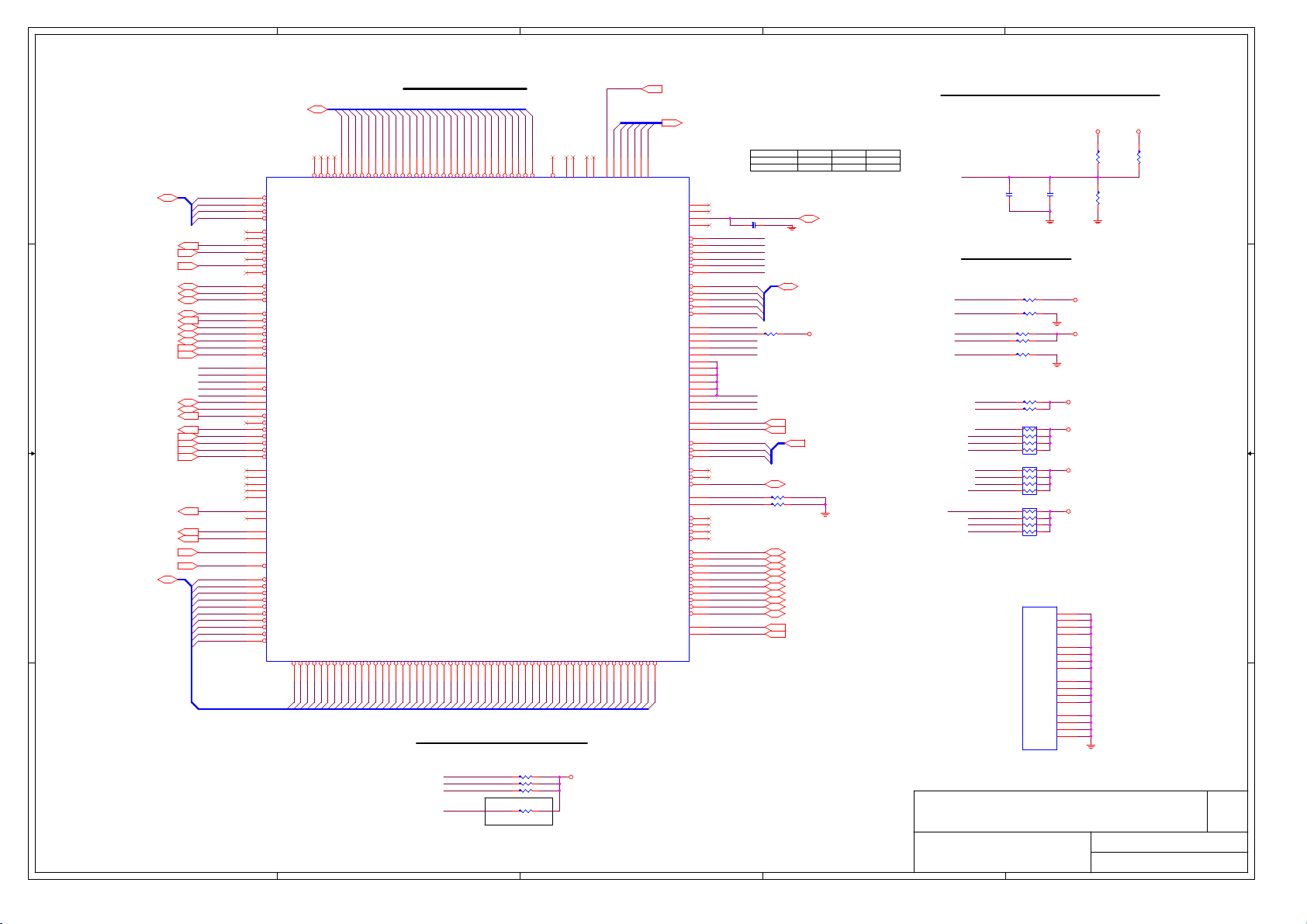

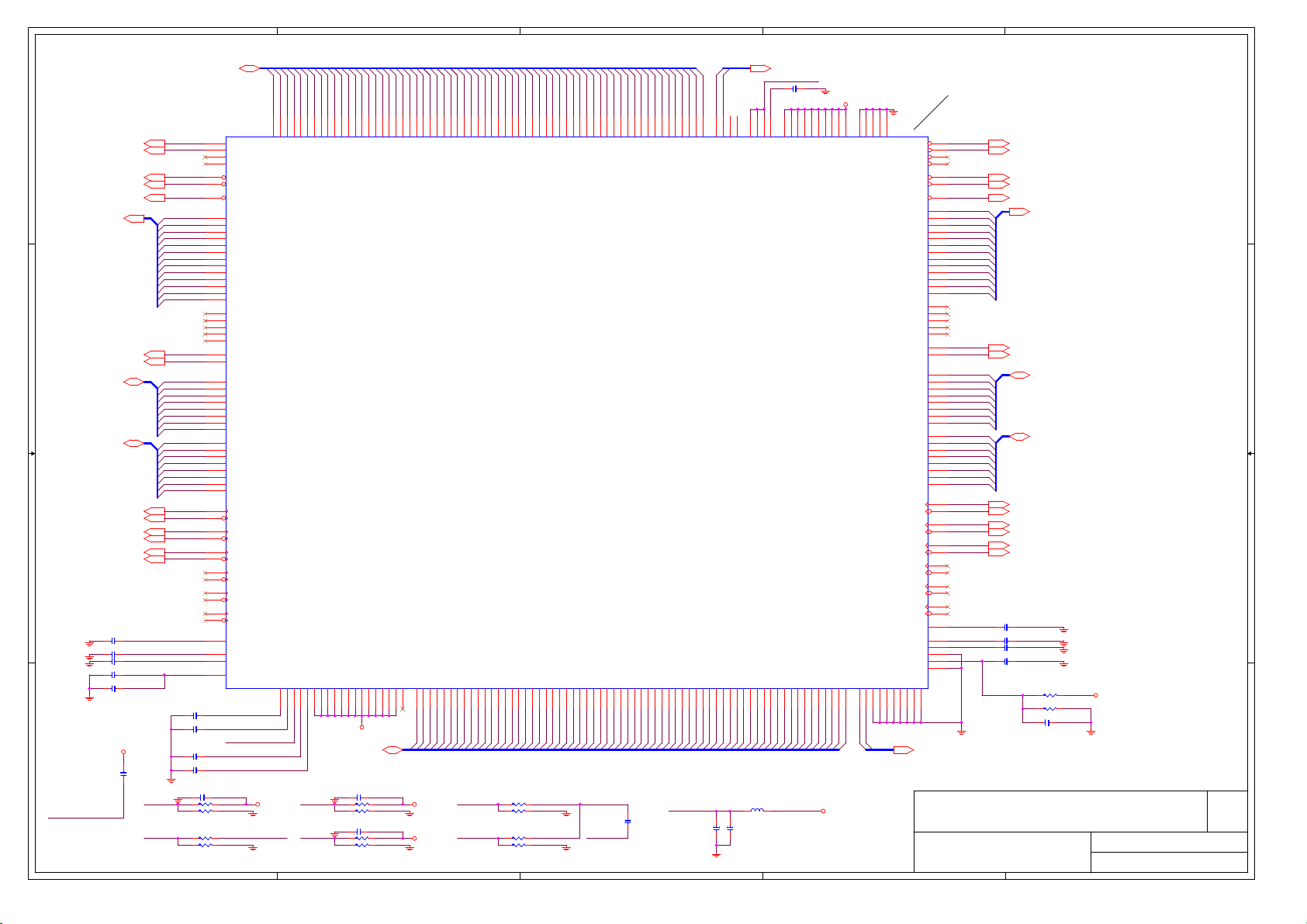

Page 4

5

4

3

2

1

CPU SIGNAL BLOCK

HA#[3..31]7

D D

CPU1A

HDBI#0

HDBI#[0..3]7

FERR#14

STPCLK#14

HINIT#14,25

HDBSY#7

HDRDY#7

HTRDY#7

HADS#7

HLOCK#7

HBNR#7

HIT#7

HITM#7

C C

B B

HBPRI#7

HDEFER#7

CPU_TMPA25

VTIN_GND25

TRMTRIP#14

PROCHOT#7

IGNNE#14

SMI#14

A20M#14

SLP#14

BOOT22,27

BSEL06

BSEL16

CPU_GD14

CPURST#7

HD#[0..63]7

HDBI#1

HDBI#2

HDBI#3

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

BOOT

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

E21

DBI0#

G25

DBI1#

P26

DBI2#

V21

DBI3#

AC3

IERR#

V6

MCERR#

B6

FERR#

Y4

STPCLK#

AA3

BINIT#

W5

INIT#

AB2

RSP#

H5

DBSY#

H2

DRDY#

J6

TRDY#

G1

ADS#

G4

LOCK#

G2

BNR#

F3

HIT#

E3

HITM#

D2

BPRI#

E2

DEFER#

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

D4

TCK

B3

THERMDA

C4

THERMDC

A2

THERMTRIP#

AF26

GND/SKTOCC#

C3

PROCHOT#

B2

IGNNE#

B5

SMI#

C6

A20M#

AB26

SLP#

A22

RESERVED0

A7

RESERVED1

AE21

RESERVED2

AF24

RESERVED3

AF25

RESERVED4

AD1

BOOTSELECT

AE26

OPTIMIZED/COMPAT#

AD6

BSEL0

AD5

BSEL1

AB23

PWRGOOD

AB25

RESET#

AA24

D63#

AA22

D62#

AA25

D61#

Y21

D60#

Y24

D59#

Y23

D58#

W25

D57#

Y26

D56#

W26

D55#

V24

D54#

D53#

V22

U21

HD#53

HD#52

HA#30

HA#27

HA#22

HA#25

HA#23

A24#

D39#

N26

HD#38

A23#

D38#

M26

HD#37

HA#21

A22#

D37#

N23

HD#36

HA#20

A21#

D36#

M24

HD#35

A20#

D35#

HA#19

P21

HD#34

HA#18

A19#

D34#

N22

HD#33

HA#17

A18#

D33#

M23

HD#32

HA#16

A17#

D32#

H25

HD#31

HA#29

HA#31

HA#28

HA#26

HA#24

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

T22

T25

HD#45

HD#46

T26

HD#44

R24

HD#42

HD#43

R25

P24

R21

HD#40

HD#41

D40#

N25

HD#39

V25

HD#51

U23

HD#50

U24

HD#49

U26

HD#48

T23

HD#47

HA#15

A16#

D31#

K23

HD#30

A15#

D30#

HA#14

J24

HD#29

HA#13

A14#

D29#

L22

HD#28

A13#

D28#

HA#12

M21

HD#27

HA#11

A12#

D27#

H24

HD#26

HA#10

A11#

D26#

G26

HD#25

A10#

D25#

HA#9

L21

HD#24

HA#8

A9#

D24#

D26

HD#23

A8#

D23#

HA#7

F26

HD#22

HA#6

A7#

D22#

E25

HD#21

HA#5

A6#

D21#

F24

HD#20

A5#

D20#

HA#4

F23

HD#19

HA#3

A4#

D19#

G23

HD#18

A3#

D18#

E24

HD#17

D17#

H22

HD#16

AE25A5A4

DBR#

D16#

D15#

D25

J21

HD#15

HD#14

VSS_SENSE

VCC_SENSE

D14#

D13#

D12#

D23

C26

H21

HD#13

HD#12

HD#11

AD26

ITP_CLK1

D11#

D10#

G22

HD#10

AC26

ITP_CLK0

D9#

D8#

B25

C24

HD#9

HD#8

VID5

AD2

AD3

VIDPWRGD

D7#

C23

B24

HD#6

HD#7

CPU STRAPPING RESISTORS

A A

5

ALL COMPONENTS CLOSE TO CPU

PROCHOT#

CPU_GD

HBR#0

BOOT

4

Ver

0C

R316 62

R221 300

R317 220

R245 X_300

VCCP

0402 R : 1/16W

Ver 0C: can't be install , that will be

disable CPU VID function when you install

Prescott CPU.

VID4

AE1

VID5#

D6#

D22

HD#5

VID3

AE2

VID4#

D5#

C21

HD#4

VID3#

D4#

VID2

AE3

A25

HD#3

VID1

AE4

VID2#

D3#

A23

HD#2

3

VID0

AE5

VID1#

D2#

B22

HD#1

VID0#

D1#

CPUVID_GD 22

VID[0..5] 22

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D0#

PGA-S478-GD10-F02

B21

{Priority}

HD#0

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

VIDPWRGD DC Specifications

VIL

VIH

It must rout to the enable pin of PWM and CK-409.

VIDGD to Vccp delay time is from 1ms to 10ms.

VIDGD rising time is 150ns.

C201 220p/16V/X7R

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI2

TESTHI1

TESTHI0

HRS#2

HRS#1

HRS#0

HBR#0

COMP1

COMP0

R315 62

CPU_CLK# 6

CPU_CLK 6

HBR#0 7

R286 61.9RST

R288 61.9RST

HADSTB#1 7

HADSTB#0 7

HDSTBP#3 7

HDSTBP#2 7

HDSTBP#1 7

HDSTBP#0 7

HDSTBN#3 7

HDSTBN#2 7

HDSTBN#1 7

HDSTBN#0 7

NMI 14

INTR 14

HREQ#[0..4] 7

Min

0.9

GTLREF 7

VCCP

HRS#[0..2] 7

Typ

0402 R : 1/16W

CPU GTL REFERNCE VOLTAGE BLOCK

Max

0.3

GTLREF

0.1u/10V/X7R

CPU ITP BLOCK

ITP_TDI

ITP_TRST#

ITP_TMS

ITP_TDO

ITP_TCK

BPM#1

BPM#0

BPM#3

TESTHI10

TESTHI9

TESTHI8

BPM#2

BPM#5

BPM#4

TESTHI1

CPURST#

TESTHI12

TESTHI2

TESTHI0

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

2

Micro Star Restricted Secret

{VOLTAGE}

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

Socket

X_P4-HS

C178

0.1u/16V/Y5V

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

0.63*Vccp

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

C184

R280 1K

R287 1K

R289 1K

R291 X_75

R292 1K

R231 62

R226 62

RN76 62

RN77 62

RN78 62

Intel mPGA478B - Signals

VCCP

R214

200RST

R220

169RST

VCCP

VCCP

0402 R : 1/16W

VCCP

VCCP

VCCP

VCCP

MS-7017

Last Revision Date:

Sheet

VTT

R199

200RST

0402 R : 1/16W

Tuesday, January 27, 2004

4 29

of

1

Rev

1.0c

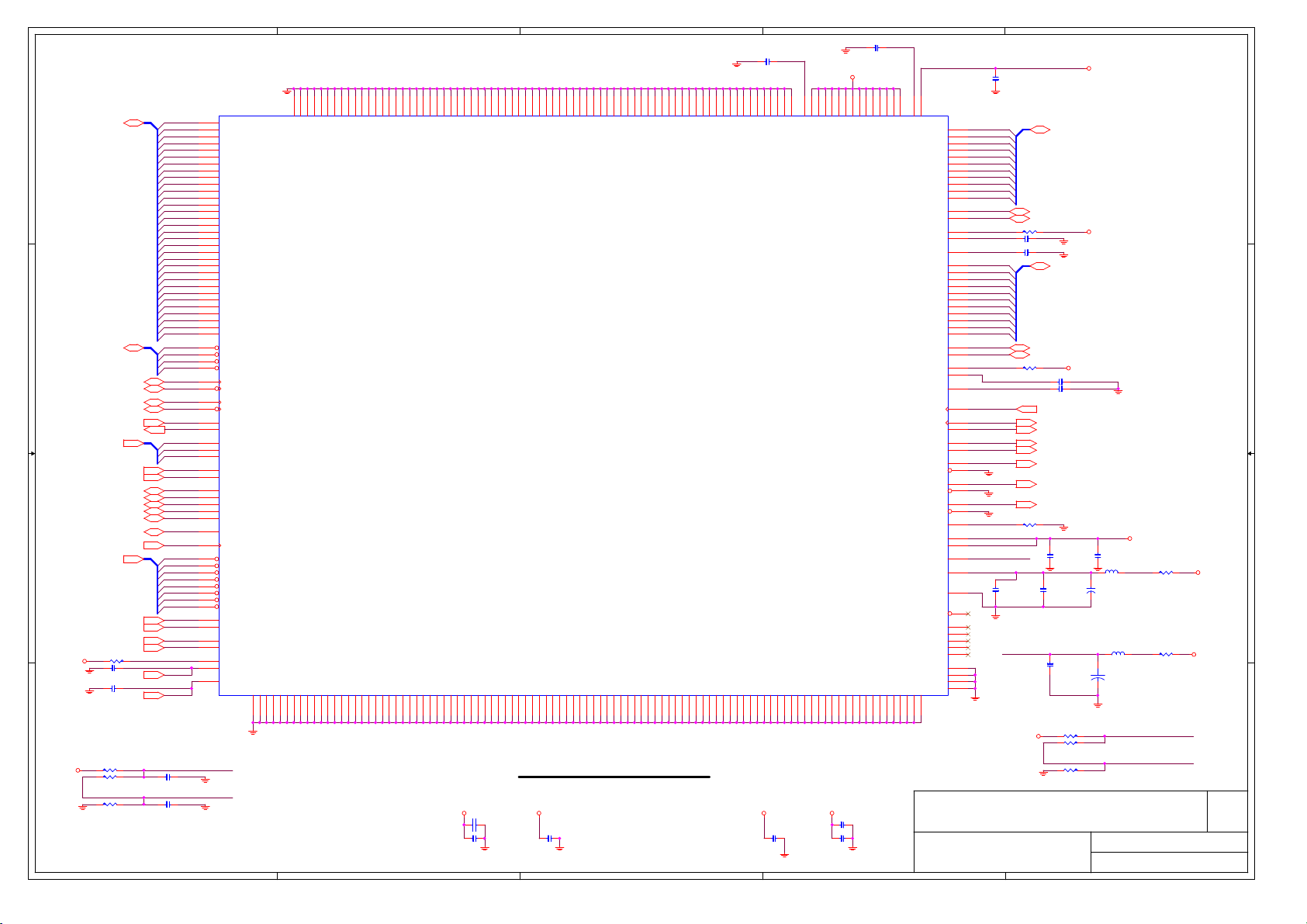

Page 5

5

4

3

2

1

D15

VCC

VCC

VSS

VSS

E7E9F10

D17

D19D7D9

VCC

VSS

VCC

VSS

VCC_VID

C0603

E10

E12

E14

E16

E18

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

F12

F14

F16

F18F2F22

F25F5F8

CPU VOLTAGE BLOCK

VCC_VID21,22

VID Voltage is from 1.14V to 1.32V.

D D

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

VCC

VSS

AF19

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

C15

C17C2C19

C22

C25C5C7C9D12

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

C C

B B

AA19

AA23

AA26

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC22

AC25

VSS

VSS

VSS

VSS

AA4

VSS

AA7

VSS

AA9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB3

VSS

AB6

VSS

AB8

VSS

VSS

VSS

VSS

VSS

VSS

AC2

VSS

VSS

VSS

AC5

VSS

AC7

VSS

AC9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

VSS

AF6

AF8

B10

B12

B14

B16

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B18

B23

B20

B26B4B8

C11

C13

It is derived from 3.3V.

It should be able to source 150mA.

It drives the power logic of BSEL[1:0] and VID[5:0].

VID to VIDGD delay time is from 1ms to 10ms.

VID to VIDGD deassertion time is 1ms for max.

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D16

D18

D20

VSS

D21D3D24D6D8E1E11

D14

VCC

VSS

C10

C12

C14

C16

C18

C20C8D11

D13

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E13

E15

E17

E19

E23

E4

E26

E20E8F11

VCC

VCC

VSS

VSS

C220

105P

VCC

VSS

G21G6G24

Near processor

F13

F15

VCC

VCC

VCC

VSS

VSS

VSS

G3H1H23

1.2V 150mA

C223

C0402

0.1u/16V/Y5V

F17

F19

F9

VCC

VCC

VCC

VSS

VSS

VSS

VSS

H26H4J2

AF4

VCC-VID

VSS

VSS

AD20

AF3

VCC-IOPLL

VCC-VIDPRG

VSS

VSS

VSS

J22

J25J5K21

AE23

AD22

VCCA

VSSA

Y5

VSS

Y25

VSS

Y22

VSS

Y2

VSS

W6

VSS

W3

VSS

W24

VSS

W21

VSS

V4

VSS

V26

VSS

V23

VSS

V1

VSS

U5

VSS

U25

VSS

U22

VSS

U2

VSS

T6

VSS

T3

VSS

T24

VSS

T21

VSS

R4

VSS

R26

VSS

R23

VSS

R1

VSS

P5

VSS

P25

VSS

P22

VSS

P2

VSS

N6

VSS

N3

VSS

N24

VSS

N21

VSS

M5

VSS

M25

VSS

M22

VSS

M2

VSS

L4

VSS

L26

VSS

L23

VSS

L1

VSS

K6

VSS

K3

VSS

K24

VSS

VSS

PGA-S478-GD10-F02

{Priority}

C208

105P

It support DC current if 100mA.

CPU_IOPLL

C191

C219

X_22u/1206

105P

VSSA

The ESL is less than 5nH, and the ESR is less than 0.3ohm.

L20 10uH-1206-100mA

L19 10uH-1206-100mA

C188

10U/1206

DC voltage drop should

be less than 70mV.

VCCP

CPU DECOUPLING CAPACITORS

C71-471022E-S03

C265

10U/1206

C268

10U/1206

C266

10U/1206

C269

A A

5

10U/1206

C260

470U/2V

C273

220U/2V

C205

220U/2V C214

X_220U/2V

VCCPVCCP VCCP VCCP

C215

X_10U/1206

C217

X_10U/1206

C209

X_10U/1206

C210

X_10U/1206

C211

X_10U/1206

C212

X_10U/1206

Place these caps within north side of processorPlace these caps within socket cavity

4

VCCP

C216

X_10U/1206

X_10U/1206C524

C213

X_10U/1206

C474

22U/1206

C475

X_10U/1206

C476

X_10U/1206

C477

22U/1206

Ver 0B

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

http://www.msi.com.tw

2

Micro Star Restricted Secret

Intel mPGA478B - Power

MS-7017

Last Revision Date:

Tuesday, February 10, 2004

Sheet

5 29

of

1

Rev

1.0c

Page 6

5

4

3

2

1

Clock Synthesizer

CP4 X_COPPER

VCC3

D D

C C

B B

CP1 X_COPPER

C120

0.1u/16V/Y5V

Use 2 VIA hole on BEAD both side

VCC3

Use 2 VIA hole on BEAD both side

VCC3

X_80-0805-3A

FB3

EC11

+

X_10U/16V/S

CP11 X_COPPER

CP2 X_COPPER

FB1 X_80-0805-3A

0.1u/16V/Y5V

R124 X_4.7K

R125 X_4.7K

VCC3V

C87

SMBDATA_ISO

SMBCLK_ISO

C90

0.1u/16V/Y5V

C103

0.1u/16V/Y5V

C95

0.1u/16V/Y5V

C102

0.1u/16V/Y5V

C92

0.1u/16V/Y5V

C107

0.1u/16V/Y5V

C114

0.1u/16V/Y5V

C82

103P/10V/X7R

U9

41 39

CPU_VDD CPU0#

44

CPU_GND

35

SRC_VDD

38

SRC_GND

28

3V66_VDD

10

PCI_VDD

11

PCI_GND

17

PCI_VDD

18

PCI_GND

25

48_VDD

24

48_GND

3

REF_VDD

6

REF_GND

48

47

33

32

*120k Pull-up

VDDA

**120k Pull-down

GND

SDATA

SCLK

SMBDATA_ISO 10,11,21,25

SMBCLK_ISO 10,11,21,25

**SEL24_48#/24_48

CPU0

CPU1

CPU1#

SRC

SRC#

3V66_0

3V66_1

3V66_2

3V66_3/VCH3V66_GND

**FS2/PCI_F0

**FS4/PCI_F1

PCI_F2

PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

PCI6

PCI7

**FS3/48M_0

*FS_A/REF_0

*FS_B/REF_1

XOUT

VTT_PWRGD/PD#

RESET#

IREF

ICS952607

XIN

40

43

42

37

36

31

30

27

2629

7

8

9

12

13

14

15

16

19

20

21

22

23

1

2

4

5

34

45

R93 475

46

Iref = 2.32mA

*Trace less 0.5"

56P/50VC84

CPU_CLK

CPU_CLK#

MCH_CLK

MCH_CLK#

SATA_100#

MCH_66

ICH_66

AGP_CLK

LAN_CLK66LANCLK66

SIO_PCLK

PCI_CLK2

FWH_PCLKFWHPCLK

ICH_PCLKICHPCLK

2N3904S

Q11

CPU_CLK 4

CPU_CLK# 4

MCH_CLK 7

MCH_CLK# 7

SATA_100 14

SATA_100# 14

MCH_66 9

ICH_66 14

AGP_CLK 12

LAN_CLK66 16

SIO_PCLK 25

PCI_CLK1 15

PCI_CLK2 15

FWH_PCLK 25

1394_PCLK 23

ICH_PCLK 13

TPM_PCLK 25

DOT_48 9

USB_48 14

ICH_14 14

LPC_14 25

AC97_14 18

R121 10K

Q10

2N3904S

Ver

0C

R122 10K

R127 10K

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

SATA100 SATA_100

SATA100#

MCH66

ICH66

AGPCLK

SIOPCLK

PCICLK1 PCI_CLK1

PCICLK2

1394PCLK 1394_PCLK

TPMPCLK TPM_PCLK

DOT48

FS_3

SEL0

SEL1

R109 33

R111 33

R100 33

R103 33

R114 33

R120 33

R129 33

R130 33

R133 33

R135 33

FS_2

FS_4

PCI0 PCI0

7 8

RN7

5 6

10

3 4

1 2

R128 33

R131 33

R51 33

R132 33

R134 33

R89 33

R101 33

R105 33

Y1

14.318M

CG_PWRGD# VCC3V

FRST# 14,27

CPU_CLK

R107 49.9RST

CPU_CLK#

R110 49.9RST

MCH_CLK

R98 49.9RST

MCH_CLK#

R104 49.9RST

0402 R : 1/16W

SATA_100

R112 49.9RST

SATA_100#

R119 49.9RST

MCH_66

ICH_66

AGP_CLK

LAN_CLK66

USB_48

DOT_48

CN4 8P4C-10P

7 8

5 6

3 4

1 2

10P/25VC112

10P/25VC109

R113 X_10K

0402 R : 1/16W

EMC HF filter capacitors, located close to PLL

SIO_PCLK

PCI_CLK1

PCI_CLK2

FWH_PCLK

1394_PCLK

ICH_PCLK

ICH_14

LPC_14

TPM_PCLK

AC97_14

VCC3

VCCP

CN3 8P4C-10P

7 8

5 6

3 4

1 2

10P/25VC105

10P/25VC106

10P/25VC81

10P/25VC88

10P/25VC3856P/50VC85

10P/25VC94

VCC3V

R96

1K

SEL0 SEL1

R92 10K R99 10K

BSEL04

A A

BSEL0_SPG7

R94

2KST

R91

2.49KST

5

R102

1K

R97

2KST

R95

2.49KST

BSEL1 4

BSEL1_SPG 7

FS_4 FS_3 FS_2

0

0 0

0

4

FS_2

FS_4

FS_3

FS_A

FS_B

BSEL1

0

1

CPU

133.3

166.7

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

http://www.msi.com.tw

Micro Star Restricted Secret

Clock Synthesizer

MS-7017

Last Revision Date:

Tuesday, January 27, 2004

Sheet

6 29

2

of

Rev

1.0c

1

BSEL0

00

1

1

R106 1K

R108 1K

R136 1K

Page 7

5

VCC_AGP

A31

B4

J6J7J8J9K6K7K8K9L6L7L9

VCC

VCC

VCC

VCC

VCC

VCC

VCCA_FSB

VCCA_FSB

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C14

C176

C16

C18

C20

VSS

C22

C24

C26

L16 0.82uH-30mA

C166

VSS

VSS

C12

C10

C8

I=30mA ICH_SYNC# MS5_POK ICH_PWROK

0.1u/10V/X7RC162

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HRCOMP

HSWING

C238

VTT

R191

301RST

R197

100RST

VCCA_FSB

C259 0.1u/16V/Y5V

U17A

D26

HA3#

D30

HA4#

L23

HA5#

E29

HA6#

B32

HA7#

K23

HA8#

C30

HA9#

C31

HA10#

J25

HA11#

B31

HA12#

E30

HA13#

B33

HA14#

J24

HA15#

F25

HA16#

D34

HA17#

C32

HA18#

F28

HA19#

C34

HA20#

J27

HA21#

G27

HA22#

F29

HA23#

E28

HA24#

H27

HA25#

K24

HA26#

E32

HA27#

F31

HA28#

G30

HA29#

J26

HA30#

G26

HA31#

B30

HAD_STB0#

D28

HAD_STB1#

B24

BREQ0#

B26

BPRI#

B28

BNR#

E25

HLOCK#

F27

ADS#

B29

HREQ0#

J23

HREQ1#

L22

HREQ2#

C29

HREQ3#

J21

HREQ4#

K21

HIT#

E23

HITM#

L21

DEFER#

D24

HTRDY#

E27

DBSY#

G24

DRDY#

G22

RS0#

C27

RS1#

B27

RS2#

B7

HCLKP

C7

HCLKN

AE14

PWROK

E8

CPURST#

AK4

RSTIN#

AJ8

ICH_SYNC#

L20

PROCHOT#

L13

BSEL0

L12

BSEL1

E24

HDRCOMP

C25

HDSWING

F23

HDVREF

B01-0865G05-I06

HA#[3..31]4

D D

HADSTB#04

HADSTB#14

HREQ#[0..4]4

HRS#[0..2]4

BSEL0_SPG6

BSEL1_SPG6

1/4*Vccp

HBR#04

HBPRI#4

HBNR#4

HLOCK#4

HADS#4

HIT#4

HITM#4

HDEFER#4

HTRDY#4

HDBSY#4

HDRDY#4

MCH_CLK6

MCH_CLK#6

CPURST#4

PCIRST_125

PROCHOT#4

R237 20RST

GTLREF4

X_103P/10V/X7R

C170

103P/10V/X7R

CHIPPWROK

ICH_SYNC#

220p/16V/X7R

5

C C

B B

A A

VCC

VCC

VCC

VSS

VSS

VSS

C28D1D11

D9

10U/1206

VCC

VSS

4

N11N9P10

P11

R11

T16

T17

T18

T19

U16

U17

U20

V16

V18

V20

W16

VCC

VSS

W19

W20

Y16

Y17

Y18

Y19

Y20

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F18

F20

F14

F16

F12

VSS

VSS

VSS

VSS

VSS

G31

G35

F22

H5

F24

F26

G28

CHIPPWROK25

N10

M10

M11M8M9

L10

L11

VCC

VCC

VCC

VCC

VSS

VSS

D13

D15

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D17

4

VSS

D19

D21

D23

D25

D27

D29

D31

D33

FSBVCCA_FSB

VCC

VSS

D35

R185

VCC

VSS

T20

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

F3F5F8

E3

F1

E1

F10

VCC_AGP

1

3

A3

A33

A35B2B25

B34C1C23

C35

E26

M31

AF13

AF23

AJ12

R25

NCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H12

H14

H16H2H20

H18

H8

H9

0 0

1

1 1 1

NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H26

10

0

H30

H33

CHIPPWROKHSWING

VSS

J10

J12

J14

J16

0

0

0

ICH_SYNC#

VCC3

R206 X_220

H22

H24

3

AN1

AP2

AR3

VSS

VSS

VSS

J18

J20

J22

AR33

AR35

A7A9A11

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J28

J32

J35

K11

K12

K14

VCC3

R212

Q30 X_2N3904S

Q29 X_2N3904S

R215 0

A13

VSS

VSS

K16

X_220

2

VTT

D5D6D7E6E7

F7

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

L26

L35

L31

ICH_PWROK 14

A4A5A6B5B6C5C6

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

M26

M27

M28

M30

M33N1N4

A16

A20

A23

A25

A27

A29

A32

C4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K18

VSS

K33

K20

K22

K25

K27

K29

L24M3M6

L25

R217

X_1K

VTT

VSS

VTT

VSS

VTT

VSS

VTT_FSB1

VTT_FSB2

A15

A21

HD0#

VTT

HD1#

HD2#

HD3#

VTT_FSB

VTT_FSB

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DINV_0#

DINV_1#

DINV_2#

DINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

Intel Springdale-N

{Priority}

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

2

C0603

C204 0.47u

C227 0.47u

HD#0

B23

HD#1

E22

HD#2

B21

HD#3

D20

HD#4

B22

HD#5

D22

HD#6

B20

HD#7

C21

HD#8

E18

HD#9

E20

HD#10

B16

HD#11

D16

HD#12

B18

HD#13

B17

HD#14

E16

HD#15

D18

HD#16

G20

HD#17

F17

HD#18

E19

HD#19

F19

HD#20

J17

HD#21

L18

HD#22

G16

HD#23

G18

HD#24

F21

HD#25

F15

HD#26

E15

HD#27

E21

HD#28

J19

HD#29

G14

HD#30

E17

HD#31

K17

HD#32

J15

HD#33

L16

HD#34

J13

HD#35

F13

HD#36

F11

HD#37

E13

HD#38

K15

HD#39

G12

HD#40

G10

HD#41

L15

HD#42

E11

HD#43

K13

HD#44

J11

HD#45

H10

HD#46

G8

HD#47

E9

HD#48

B13

HD#49

E14

HD#50

B14

HD#51

B12

HD#52

B15

HD#53

D14

HD#54

C13

HD#55

B11

HD#56

D10

HD#57

C11

HD#58

E10

HD#59

B10

HD#60

C9

HD#61

B9

HD#62

D8

HD#63

B8

HDBI#0

C17

HDBI#1

L17

HDBI#2

L14

HDBI#3

C15

B19

C19

L19

K19

G9

F9

D12

E12

HD#[0..63] 4

HDBI#[0..3] 4

HDSTBP#0 4

HDSTBN#0 4

HDSTBP#1 4

HDSTBN#1 4

HDSTBP#2 4

HDSTBN#2 4

HDSTBP#3 4

HDSTBN#3 4

Micro Star Restricted Secret

Intel Springdale - CPU

MS-7017

1

Last Revision Date:

Tuesday, January 27, 2004

Sheet

7 29

1

Rev

1.0c

of

Page 8

5

4

3

2

1

MDQ_A[0..63]10 MCKE_A[0..1] 10

MDQ_A4

MDQ_A9

MDQ_A3

MDQ_A6

MDQ_A8

MDQ_A1

MDQ_A2

MDQ_A7

MDQ_A5

MDQ_A0

AP10

AP11

AM12

AN13

AM10

D D

C C

B B

A A

XCOMPH

MA_A[0..12]10

MDQM_A[0..7]10

MDQS_A[0..7]10

C280 103P/10V/X7R

C275 103P/10V/X7R

C277 103P/10V/X7R

C261 0.1u/16V/Y5V

C262 105P

103P/10V/X7R

MCS_A#010

MCS_A#110

MRAS_A#10

MCAS_A#10

MWE_A#10

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11 MA_B12

MA_A12

MBA_A010

MBA_A110

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

MCLK_A010

MCLK_A#010

MCLK_A110

MCLK_A#110

MCLK_A210

MCLK_A#210

XRCOMP

XCOMPH

XCOMPL

XVREF

C0603

C263 0.47u

C287 224P

VCC_DDR

C274

C295 224P

C281 0.1u/16V/Y5V

YRCOMP VCC_DDR_C3

5

U17B

AA34

SCS_A0#

Y31

SCS_A1#

Y32

SCS_A2#

W34

SCS_A3#

AC33

SRAS_A#

Y34

SCAS_A#

AB34

SWE_A#

AJ34

SMAA_A0

AL33

SMAA_A1

AK29

SMAA_A2

AN31

SMAA_A3

AL30

SMAA_A4

AL26

SMAA_A5

AL28

SMAA_A6

AN25

SMAA_A7

AP26

SMAA_A8

AP24

SMAA_A9

AJ33

SMAA_A10

AN23

SMAA_A11

AN21

SMAA_A12

AL34

SMAB_A1

AM34

SMAB_A2

AP32

SMAB_A3

AP31

SMAB_A4

AM26

SMAB_A5

AE33

SBA_A0

AH34

SBA_A1

AP12

SDM_A0

AP16

SDM_A1

AM24

SDM_A2

AP30

SDM_A3

AF31

SDM_A4

W33

SDM_A5

M34

SDM_A6

H32

SDM_A7

AN11

SDQS_A0

AP15

SDQS_A1

AP23

SDQS_A2

AM30

SDQS_A3

AF34

SDQS_A4

V34

SDQS_A5

M32

SDQS_A6

H31

SDQS_A7

AK32

SMDCLK_A0

AK31

SMDCLK_A0#

AP17

SMDCLK_A1

AN17

SMDCLK_A1#

N33

SMDCLK_A2

N34

SMDCLK_A2#

AK33

SMDCLK_A3

AK34

SMDCLK_A3#

AM16

SMDCLK_A4

AL16

SMDCLK_A4#

P31

SMDCLK_A5

P32

SMDCLK_A5#

AK9

SMXRCOMP

AN9

SMXCOMPVOH

AL9

SMXCOMPVOL

E34

SMVREF_A

C0603

C0603

VCC_DDR_C2

VCC_DDR_C3

C0603

C296 105P

R302 42.2RST

R309 42.2RST

R304 42.2RST

R306 42.2RST R293 30.1KST

values still need verification

AL10

SDQ_A0

SDQ_A1

SDQ_A2

SDQ_A3

SDQ_A4

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

E35

AA35

R35

AR15

AR21

XCOMPLXRCOMP

VCC_DDR VCC_DDR

XCOMPH

AA35AA33

AL12

AP13

AP14

SDQ_A5

SDQ_A6

SDQ_A7

VCC_DDR

VCC_DDR

VCC_DDR

AM1

AL7

AL6

MDQ_A12

MDQ_A11

MDQ_A10

AM14

AL18

AP19

AL14

SDQ_A8

SDQ_A9

SDQ_A10

SDQ_A11

SDQ_A12

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

AM2

AN8

AP3

AP4

VCC_DDR

MDQ_B[0..63]11

C291 105P

R298 30.1KST

R303 10KST

C278 105P

R294 10KST

MDQ_A15

MDQ_A13

MDQ_A14

AN15

AP18

AM18

SDQ_A13

SDQ_A14

VCC_DDR

VCC_DDR

AP5

AP6

AP7

MDQ_A18

MDQ_A17

MDQ_A16

AP22

AM22

AL24

SDQ_A15

SDQ_A16

SDQ_A17

VCC_DDR

VCC_DDR

VCC_DDR

AR4

AR5

AR7

MDQ_A21

MDQ_A20

MDQ_A19

AN27

AP21

AL22

SDQ_A18

SDQ_A19

SDQ_A20

VCC_DDR

VCC_DDR

AR31

AJ10

MDQ_B0

4

MDQ_A25

MDQ_A28

MDQ_A23

MDQ_A22

AP25

AP27

SDQ_A21

SDQ_A22

SDQ_A23

SDQ_B0

SDQ_B1

SDQ_B2

AE15

AL11

MDQ_B1

MDQ_B2

VCC_DDR

MDQ_A24

AP28

AE16

MDQ_B3

MDQ_A31

MDQ_A30

MDQ_A29

MDQ_A27

MDQ_A26

AP29

AP33

AM33

AM28

AN29

AM31

AN34

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_A27

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_B3

SDQ_B4

SDQ_B5

SDQ_B6

SDQ_B7

SDQ_B8

SDQ_B9

AL8

AF12

AK11

AG12

AE17

AL13

AK17

MDQ_B9

MDQ_B8

MDQ_B4

MDQ_B5

MDQ_B6

MDQ_B7

MDQ_B10

YCOMPL VCC_DDR_C2

R33

YCOMPH

R34

MDQ_A33

MDQ_A35

MDQ_A32

MDQ_A34

AH32

AG34

AF32

AD32

SDQ_A31

SDQ_A32

SDQ_A33

SDQ_A34

SDQ_B10

SDQ_B11

SDQ_B12

SDQ_B13

AL17

AK13

AJ14

AJ16

MDQ_B11

MDQ_B12

MDQ_B14

MDQ_B13

R297 30.1KST

R295 10KST

R296 10KST

R301 30.1KST

MDQ_A36

MDQ_A37

AH31

AG33

SDQ_A35

SDQ_A36

SDQ_A37

SDQ_B14

SDQ_B15

SDQ_B16

AJ18

AE19

MDQ_B16

MDQ_B15

MDQ_A38

AE34

AE20

MDQ_B17

MDQ_A40

MDQ_A39

AD34

AC34

SDQ_A38

SDQ_A39

SDQ_A40

SDQ_B17

SDQ_B18

SDQ_B19

AG23

AK23

MDQ_B19

MDQ_B18

MDQ_A43

MDQ_A42

MDQ_A41

AB31

V32

V31

SDQ_A41

SDQ_A42

SDQ_B20

SDQ_B21

AL19

AK21

AJ24

MDQ_B22

MDQ_B21

MDQ_B20

MDQ_A45

MDQ_A44

AD31

AB32

SDQ_A43

SDQ_A44

SDQ_A45

SDQ_B22

SDQ_B23

SDQ_B24

AE22

AK25

MDQ_B23

MDQ_B24

R35

MDQ_A46

MDQ_A48

MDQ_A47

U34

U33

T34

SDQ_A46

SDQ_A47

SDQ_B25

SDQ_B26

AH26

AG27

AF27

MDQ_B27

MDQ_B26

MDQ_B25

YCOMPH

MDQ_A50

MDQ_A49

T32

K34

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_B27

SDQ_B28

SDQ_B29

AJ26

AJ27

MDQ_B29

MDQ_B28

MDQ_A51

MDQ_A53

MDQ_A52

K32

T31

P34

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_B30

SDQ_B31

SDQ_B32

AD25

AF28

AE30

MDQ_B30

MDQ_B32

MDQ_B31

C282

103P/10V/X7R

MDQ_A54

MDQ_A55

L34

L33

SDQ_A54

SDQ_A55

SDQ_B33

SDQ_B34

AC27

AC30

MDQ_B33

MDQ_B34

3

MDQ_A58

MDQ_A56

MDQ_A57

J33

H34

E33

SDQ_A56

SDQ_A57

SDQ_B35

SDQ_B36

Y29

AE31

AB29

MDQ_B36

MDQ_B37

MDQ_B35

MDQ_A59

F33

SDQ_A58

SDQ_B37

AA26

MDQ_B38

VCCA_DDR

0.1u/16V/Y5V

MDQ_A61

MDQ_A60

K31

J34

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_B38

SDQ_B39

SDQ_B40

AA27

AA30

MDQ_B39

MDQ_B40

MDQ_A62

MDQ_A63

G34

F34

SDQ_A62

SDQ_B41

W30

U27

MDQ_B42

MDQ_B41

C177

MCKE_A0

AL20

SDQ_A63

SCKE_A0

SDQ_B42

SDQ_B43

SDQ_B44

T25

AA31

MDQ_B43

MDQ_B44

MCKE_A1

AN19

AM20

SCKE_A1

SDQ_B45

V29

U25

MDQ_B45

MDQ_B46

AP20

SCKE_A2

SCKE_A3

SDQ_B46

SDQ_B47

SDQ_B48

R27

P29

MDQ_B49

MDQ_B48

MDQ_B47

C167

10U/1206

AC26

AB25

AC25

AL35

VCCA_DDR

VCCA_DDR

VCCA_DDR

SDQ_B49

SDQ_B50

SDQ_B51

R30

K28

L30

R31

MDQ_B52

MDQ_B50

MDQ_B51

L15

1uH-1206-1A

{Prority}

VCCA_DDR

C298 0.1u/16V/Y5V

AN4

AM3

AN5

AM5

AM6

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCCA_DDR

SDQ_B52

SDQ_B53

SDQ_B54

SDQ_B55

SDQ_B56

SDQ_B57

SDQ_B58

R26

P25

L32

K30

H29

F32

MDQ_B56

MDQ_B53

MDQ_B55

MDQ_B58

MDQ_B57

MDQ_B54

VCC_DDR

AM7

AM8

AN2

VCC_DDR

VCC_DDR

SDQ_B59

SDQ_B60

G33

N25

M25

MDQ_B59

MDQ_B60

MDQ_B61

VCC_AGP

AN6

AN7

VCC_DDR

VCC_DDR

VCC_DDR

SDQ_B61

SDQ_B62

SDQ_B63

J29

G32

MDQ_B63

MDQ_B62

P3P6P8

N35

N32

VSS

VSS

SCKE_B0

SCKE_B1

AK19

AF19

AG19

MCKE_B0

MCKE_B1

Its current is 5.1A.

U26

SCS_B0#

VSS

SCS_B1#

SCS_B2#

SCS_B3#

SRAS_B#

SCAS_B#

SWE_B#

SMAA_B0

SMAA_B1

SMAA_B2

SMAA_B3

SMAA_B4

SMAA_B5

SMAA_B6

SMAA_B7

SMAA_B8

SMAA_B9

SMAA_B10

SMAA_B11

SMAA_B12

SMAB_B1

SMAB_B2

SMAB_B3

SMAB_B4

SMAB_B5

SBA_B0

SBA_B1

SDM_B0

SDM_B1

SDM_B2

SDM_B3

SDM_B4

SDM_B5

SDM_B6

SDM_B7

SDQS_B0

SDQS_B1

SDQS_B2

SDQS_B3

SDQS_B4

SDQS_B5

SDQS_B6

SDQS_B7

SMYRCOMP

SMVREF_B

VSS

VSS

VSS

VSS

1234576

T29

V25

W25

W26

W31

W27

AG31

AJ31

AD27

AE24

AK27

AG25

AL25

AF21

AL23

AJ22

AF29

AL21

AJ20

AE27

AD26

AL29

AL27

AE23

Y25

AA25

AG11

AG15

AE21

AJ28

AC31

U31

M29

J31

AF15

AG13

AG21

AH27

AD29

U30

L27

J30

AG29

AG30

AF17

AG17

N27

N26

AJ30

AH29

AK15

AL15

N31

N30

AA33

R34

R33

8

VSS

AP9

VSS

VSS

VSS

MCKE_B[0..1] 11

MA_B0

MA_B1

MA_B2

MA_B3

MA_B4

MA_B5

MA_B6

MA_B7

MA_B8

MA_B9

MA_B10

MA_B11

MDQM_B0

MDQM_B1

MDQM_B2

MDQM_B3

MDQM_B4

MDQM_B5

MDQM_B6

MDQM_B7

MDQS_B0

MDQS_B1

MDQS_B2

MDQS_B3

MDQS_B4

MDQS_B5

MDQS_B6

MDQS_B7

YRCOMP

YCOMPH

YCOMPL

Intel Springdale-N

{Priority}

VSS

VSS

SCMDCLK_B0

SCMDCLK_B0#

SCMDCLK_B1

SCMDCLK_B1#

SCMDCLK_B2

SCMDCLK_B2#

SCMDCLK_B3

SCMDCLK_B3#

SCMDCLK_B4

SCMDCLK_B4#

SCMDCLK_B5

SCMDCLK_B5#

SMYCOMPVOH

SMYCOMPVOL

SCKE_B2

SCKE_B3

AE18

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

2

MCS_B#0 11

MCS_B#1 11

MRAS_B# 11

MCAS_B# 11

MWE_B# 11

MA_B[0..12] 11

MBA_B0 11

MBA_B1 11

MDQM_B[0..7] 11

MDQS_B[0..7] 11

MCLK_B0 11

MCLK_B#0 11

MCLK_B1 11

MCLK_B#1 11

MCLK_B2 11

MCLK_B#2 11

C286 103P/10V/X7R

C272 103P/10V/X7R

C271 103P/10V/X7R

C276 0.1u/16V/Y5V

YVREF

R299 150RST

R300 150RST

C283 105P

C0603

VCC_DDR

Micro Star Restricted Secret

Intel Springdale - Memory

MS-7017

Last Revision Date:

Tuesday, January 27, 2004

Sheet

8 29

of

1

Rev

1.0c

Page 9

5

P26

P27

P28

P30

P33R1R4

VSS

VSS

AE13

VSS

VSS

AE25

VSS

VSS

AE26

VSS

VSS

AE32

VSS

VSS

AE35

VSS

VSS

AF3

R32T1T3

VSS

VSS

AF6

VSS

VSS

VSS

AD30

VSS

AD33

AD28

VSS

P9

VSS

VSS

VSS

VSS

VSS

AE1

AE10

AE11

AE12

AE4

GAD[0..31]12

D D

VCC_AGP

VCC_AGP

GC_BE#[0..3]12

AD_STB012

AD_STB#012

AD_STB112

AD_STB#112

ST[0..2]12

GFRAME#12

GDEVSEL#12

SBA[0..7]12

R241 43.2RST

C232 103P/10V/X7R

C233 103P/10V/X7R

AGP_REF12

R248 226

R254 147

R257 113

GREQ#12

GGNT#12

GIRDY#12

GTRDY#12

GSTOP#12

MCH_666

SB_STB12

SB_STB#12

DBI_LO12

GSWING12

C C

B B

A A

GAD0

GAD1

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC_BE#0

GC_BE#1

GC_BE#2

GC_BE#3

ST0

ST1

ST2

RBF#

RBF#12

WBF#

WBF#12

GPAR12

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

PIPE#12

GRCOMP

GSWING

H_SWING=(0.8*VCC_AGP)+-2%

HL_SWING

C240 0.1u/16V/Y5V

HL_VREF

C242 0.1u/16V/Y5V

H_SWING=(0.233*VCC_AGP)+-2%

5

U17C

AE6

GAD0/DVOB_HSYNC

AC11

GAD1/DVOB_VSYNC

AD5

GAD2/DVOB_D1

AE5

GAD3/DVOB_D0

AA10

GAD4/DVOB_D3

AC9

GAD5/DVOB_D2

AB11

GAD6/DVOB_D5

AB7

GAD7/DVOB_D4

AA9

GAD8/DVOB_D6

AA6

GAD9/DVOB_D9

AA5

GAD10/DVOB_D8

W10

GAD11/DVOB_D11

AA11

GAD12/DVOB_D10

W6

GAD13/DVOBC_CLKINT

W9

GAD14/DVOB_FLDSTL

V7

GAD15/MDDC_DATA

AA2

GAD16/DVOC_VSYNC

Y4

GAD17/DVOC_HSYNC

Y2

GAD18/DVOC_BLANK#

W2

GAD19/DVOC_D0

Y5

GAD20/DVOC_D1

V2

GAD21/DVOC_D2

W3

GAD22/DVOC_D3

U3

GAD23/DVOC_D4

T2

GAD24/DVOC_D7

T4

GAD25/DVOC_D6

T5

GAD26/DVOC_D9

R2

GAD27/DVOC_D8

P2

GAD28/DVOC_D11

P5

GAD29/DVOC_D10

P4

GAD30/DVOBC_INTR#

M2

GAD31/DVOC_FLDSTL

Y7

GCBE0/DVOB_D7

W5

GCBE1/DVOB_BLANK#

AA3

GCBE2

U2

GCBE3/DVOC_D5

AC6

GADSTBF0/DVOB_CLK

AC5

GADSTBS0/DVOB_CLK#

V4

GADSTBF1/DVOC_CLK

V5

GADSTBS1/DVOC_CLK#

N6

GREQ

M7

GGNT

N3

GST0

N5

GST1

N2

GST2

R10

GRBF

R9

GWBF

U6

GFRAME/MDVI_DATA

V11

GIRDY/MI2CCLK

AB5

GTRDY/MDVI_CLK

AB4

GDEVSEL/MI2CDATA

W11

GSTOP/MDDC_CLK

AB2

GPAR/ADD_DETECT

H4

GCLKIN

R6

GSBA0#/ADD_ID0

P7

GSBA1#/ADD_ID1

R3

GSBA2#/ADD_ID2

R5

GSBA3#/ADD_ID3

U9

GSBA4#/ADD_ID4

U10

GSBA5#/ADD_ID5

U5

GSBA6#/ADD_ID6

T7

GSBA7#/ADD_ID7

U11

GSBSTBF

T11

GSBSTBS

M4

DBI_HI

M5

DBI_LO

AC2

GRCOMP/DVOBC_RCOMP

AC3

GVSWING

AD2

GVREF

800mV

4

V6

U4

U18

U19

VSS

VSS

T30

AF30

VSS

VSS

T33

AF33

VSS

VSS

T35

VSS

VSS

AG4

VSS

VSS

VSS

VSS

AG8

AG14

U32V3V8V9V10

VSS

VSS

VSS

VSS

VSS

VSS

AG16

AG18

AG20

AG22

T6T8T9

T10

T26

T27

T28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF16

AF18

AF20

AF22

AF24

AF14

AF25

AF11

AF9

VSS

VSS

AG24

VSS

VSS

AG26

VSS

VSS

AG28

VSS

VSS

V17

AG32

VSS

VSS

V19

AG35

VSS

VSS

V26

AH3

V27

VSS

VSS

AH6

V28

V30W4W17

VSS

VSS

VSS

VSS

AH12

AH10

VSS

VSS

V33

AH14

VSS

VSS

AH16

W18

W32Y6Y8Y9Y26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH18

AH20

AH22

Y3

AH24

VSS

VSS

AH30

VSS

VSS

AH33

VSS

VSS

AJ1

Springdale Decoupling Capacitors

All caps trace length is less than 100mils.350mV

VCC_DDR VCC_DDRVCC_AGP

C200

1 2

1uF/10V/Y5V

C197

Close AG1 and Y1 of GMCH Close E35, R35, AA35, AL35, AR31, AR21 and AR15 of GMCH

4

X_0.1u/16V/Y5V

C267

0.1u/16V/Y5V

VSS

VSS

3

C222 0.1u/16V/Y5V

Y28

Y30

Y33

Y35

Y27

AA1

AA4

AA32

AB10

AB26

AC1

AC4

AC32

VSS

VSS

AB28

AL32

VSS

VSS

AB30

AM9

VSS

VSS

AB33

VSS

VSS

AM11

AM13

VSS

VSS

VSS

VSS

AM15

VSS

VSS

AM17

AC35

AM19

AD3

VSS

VSS

AM21

AB27

AB3

AB6

AB8

VSS

VSS

AK12

VSS

VSS

AK14

VSS

VSS

AK16

VSS

VSS

AK18

VSS

VSS

AK20

VSS

VSS

AK22

VSS

VSS

AB9

AK24

VSS

VSS

AK26

VSS

VSS

AK28

VSS

VSS

AL1

Y10

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK3

AJ4

AJ9

AJ32

AJ35

AK8

AK10

3

VSS

VSS

AD6

AM23

AD8

VSS

VSS

AM25

AD9

AD10

VSS

VSS

VSS

VSS

AM27

AM29

C264

0.1u/16V/Y5V

VSS

VSS

VSS

AM35

AN10

L1L5Y1J1J2J3K2K3K4K5J4J5L4L2L3

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VSS

VSS

VSS

VSS

VSS

AN12

AN14

AN16

AN18

VTT

C247 0.1u/16V/Y5V

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VSS

VSS

VSS

VSS

VSS

AN20

AN22

AN24

AN26

AN28

AN30

C187

0.1u/16V/Y5V

C189

0.1u/16V/Y5V

2

AG1

Y11

HL0

AF5

HI0

HL1GAD2

AG3

HI1

HL2

AK2

HI2

HL3

VCCA_AGP

VCCA_AGP

HI_STRF

HI_STRS

HI_RCOMP

HI_SWING

HI_VREF

CISTRF

CISTRS

CI_RCOMP

CI_SWING

CI_VREF

DREFCLK

DDCA_CLK

DDCA_DATA

VSYNC

HSYNC

BLUE

BLUE#

GREEN

GREEN#

RED#

REFSET

VCC_DAC

VCC_DAC

VCCA_DPLL

VCCA_DAC

VSSA_DAC

EXTTS#

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

VSS

VSS

VSS

AR23

AR16

AR20

Intel Springdale-N

{Priority}

HI10

CI10

RED

VSS

VSS

VSS

VSS

AG5

HI3

HL4

AK5

HI4

HL5

AL3

HI5

HL6

AL2

HI6

HL7

AL4

HI7

HL8

AJ2

HI8

HL9

AH2

HI9

HL10

AJ3

AH5

AH4

HL_COMP

AD4

HL_SWING

AE3

HL_VREF

AE2

CI0

AK7

CI0

CI1

AH7

CI1

CI2

AD11

CI2

CI3

AF7

CI3

CI4

AD7

CI4

CI5

AC10

CI5

CI6

AF8

CI6

CI7

AG7

CI7

CI8

AE9

CI8

CI9

AH9

CI9

CI10

AG6

AJ6

AJ5

CI_RCOMP

AG2

AF2

AF4

DOT_48

G4

F2

H3

E2

G3

H7

G6

H6

G5

F4

E4

D2

G1

G2

VCCA_DPLL

B3

C2

D3

AP8

AG9

AG10

AN35

AP34

AR1

AR25

AR27

AR29

AR32

VCC_AGP

VCC_AGP

VCC_AGP

VSS

VSS

VSS

AR9

AN32

AR11

VCC_AGP

VCC_AGP

VSS

VSS

AR13

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

2

1

HL[0..10] 14

CI[0..10] 16

VCC_AGP

C194

103P/10V/X7R

C180

103P/10V/X7R

VCC_AGP

VCC_AGP

C195

0.1u/16V/Y5V

L17

+

EC27

470u

EC26

+

100u_25V

L18

100nH

VCC3

100n

DPLLVCCA_DPLL

CI_SWING

CI_VREF

GSET

VCCA_DAC

C183

103P/10V/X7R

C173

10U/1206

HI_RCOMP Calculation

R=[(1.5V-08V)/0.8V]*60ohm=52.5ohm

HL_STRF 14

HL_STRS 14

R243 52.3RST

C235 103P/10V/X7R

C237 103P/10V/X7R

CI_STRF 16

CI_STRS 16

R252 52.3RST

C239 103P/10V/X7R

C241 103P/10V/X7R

DOT_48 6

3VDDCCL 24

3VDDCDA 24

CRT_VSYNC 24

CRT_HSYNC 24

CRT_B 24

CRT_G 24

CRT_R 24

R201 137RST

C181

0.1u/16V/Y5V

I=35mA

R256 226

VCC_AGP

R253 147

R258 113

Micro Star Restricted Secret

Intel Springdale - AGP & LAN

MS-7017

Last Revision Date:

Tuesday, January 27, 2004

Sheet

9 29

1

R190

1

5%

R188

1

CI_SWING

CI_VREF

of

VCC_DAC

1.6V/60mA

VCC_AGP

Rev

800mV

350mV

1.0c

Page 10

5

4

3

2

1

DDR Terminational Resisitors

DDR DIMM1

MDQ_A9

1 2

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

157

158

71

163

154

65

63

5

14

25

36

56

67

78

86

47

97

107

119

129

149

159

169

177

140

44

45

49

51

134

135

142

144

21

111

92

91

181

182

183

16

17

137

138

76

75

82

184

7

38

46

70

85

108

120

148

168

81

89

93

100

116

124

132

139

145

152

160

176

DIMM1

SIGNALS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/NC

A13/NC

BA0

BA1

NC/BA2

CS0#

CS1#

NC/CS2#

NC/CS3#

RAS#

CAS#

WE#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQM0/DQS9

DQM1/DQS10

DQM2/DQS11

DQM3/DQS12

DQM4/DQS13

DQM5/DQS14

DQM6/DQS15

DQM7/DQS16

DQM8/DQS17

MECC0

MECC1

MECC2

MECC3

MECC4

MECC5

MECC6

MECC7

CKE0

CKE1

SCL

SDA

SA0

SA1

SA2

CK0/NC

CK0#/NC

CK1/CK0

CK1#/CK0#

CK2/NC

CK2#/NC

ID_VDD

SPD_VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DIMM-D184-BK

POWER

VREF

FETEN/NC

NC/RESET#

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC3

VCC_DDR

MA_A0

MA_A1

MA_A2

MA_A3

MA_A4

MA_A5

MA_A6

MA_A7

MA_A8

MA_A9

MA_A10

MA_A11

MA_A12

MBA_A0

MBA_A1

MRAS_A#

MCAS_A#

MWE_A#

MDQS_A0

MDQS_A1

MDQS_A2

MDQS_A3

MDQS_A4

MDQS_A5

MDQS_A6

MDQS_A7

MDQM_A0

MDQM_A1

MDQM_A2

MDQM_A3

MDQM_A4

MDQM_A5

MDQM_A6

MDQM_A7

MA_A[0..12]8

D D

MBA_A08

MBA_A18

MCS_A#08

MCS_A#18

MRAS_A#8

MCAS_A#8

MWE_A#8

MDQS_A[0..7]8

C C

B B

A A

MDQM_A[0..7]8

MCKE_A08

MCKE_A18

SMBCLK_ISO6,11,21,25

SMBDATA_ISO6,11,21,25

MCLK_A18

MCLK_A#18

MCLK_A08

MCLK_A#08

MCLK_A28

MCLK_A#28

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

MDQ_A0

2

DQ0

MDQ_A1

4

DQ1

MDQ_A2

6

DQ2

MDQ_A3

8

DQ3

MDQ_A4

94

DQ4

MDQ_A5

95

DQ5

MDQ_A6

98

DQ6

MDQ_A7

99

DQ7

MDQ_A8

12

DQ8

MDQ_A9

13

DQ9

MDQ_A10

19

MDQ_A11

20

MDQ_A12

105

MDQ_A13

106

MDQ_A14

109

MDQ_A15

110

MDQ_A16

23

MDQ_A17

24

MDQ_A18

28

MDQ_A19

31

MDQ_A20

114

MDQ_A21

117

MDQ_A22

121

MDQ_A23

123

MDQ_A24

33

MDQ_A25

35

MDQ_A26

39

MDQ_A27

40

MDQ_A28

126

MDQ_A29

127

MDQ_A30

131

MDQ_A31

133

MDQ_A32

53

MDQ_A33

55

MDQ_A34

57

MDQ_A35

60

MDQ_A36

146

MDQ_A37

147

MDQ_A38

150

MDQ_A39

151

MDQ_A40

61

MDQ_A41

64

MDQ_A42

68

MDQ_A43

69

MDQ_A44

153

MDQ_A45

155

MDQ_A46

161

MDQ_A47

162

MDQ_A48

72

MDQ_A49

73

MDQ_A50

79

MDQ_A51

80

MDQ_A52

165

MDQ_A53

166

MDQ_A54

170

MDQ_A55

171

MDQ_A56

83

MDQ_A57

84

MDQ_A58

87

MDQ_A59

88

MDQ_A60

174

MDQ_A61

175

MDQ_A62

178

MDQ_A63

179

9

NC

101

NC

102

NC

173

NC

WP

DDR_VREF1

1

C394

90

103

0.1u/16V/Y5V

10

15

22

30

54

62

77

96

104

112

128

136

143

156

164

172

180

3

11

18

26

34

42

50

58

66

74

VCC_DDR

VCC_DDR

MDQ_A[0..63] 8

R394

75RST

R395

75RST

VCC_DDR

C373

0.1u/16V/Y5V

C375

0.1u/16V/Y5V

C376

0.1u/16V/Y5V

C468

0.1u/16V/Y5V

C465

0.1u/16V/Y5V

C378

0.1u/16V/Y5V

C372

0.1u/16V/Y5V

MDQS_A7

MDQM_A7

MDQ_A57

MDQ_A56

MDQ_A37

MDQ_A33

MDQ_A36

MDQ_A32

MDQ_A53

MDQ_A52

MDQ_A49

MDQ_A48

MDQ_A11

MDQ_A10

MDQ_A15

MDQ_A14

MDQS_A5

MDQM_A5

MDQ_A41

MDQ_A45

MDQ_A20

MA_A5

MA_A8

MA_A7

MA_A10

MA_A0

MA_A1

MA_A2

MCS_A#1

MCAS_A#

MCS_A#0

MCKE_A0

MCKE_A1

MA_A12

MA_A11

MA_A9

MA_A6

MA_A4

MA_A3

MBA_A1

MBA_A0

MRAS_A#

MWE_A#

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R401 56

R412 56

R411 56

R410 56

R403 56

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R400 47

R399 47

R398 47

R404 47

R405 47

R406 47

R407 47

R408 47

R409 47

R397 47

R413 47

R402 47

RN46

56

RN30

56

RN29

56

RN35

56

RN38

47

RN42

47

RN43

47

VTT_DDR

VTT_DDR

Ver 0C

those cap change

packet from 0402

to 0603

Ver 1.0

those cap value

change 2.2uF

ADDR.=1010000B

5

4

3

MDQ_A8

3 4

MDQ_A3

5 6

MDQ_A7

7 8

MDQ_A6

1 2

MDQ_A2

3 4

MDQM_A0

5 6

MDQS_A0

7 8

MDQM_A1

1 2

MDQ_A13

3 4

MDQS_A1

5 6

MDQ_A12

7 8

MDQS_A2

1 2

MDQ_A21

3 4

MDQ_A17

5 6

MDQ_A16

7 8

1 2

MDQ_A22

3 4

MDQ_A18

5 6

MDQM_A2

7 8

MDQM_A3

1 2

MDQS_A3

3 4

MDQ_A29

5 6

MDQ_A25

7 8

MDQ_A31

1 2

MDQ_A27

3 4

MDQ_A26

5 6

MDQ_A30

7 8

MDQ_A38

1 2

MDQM_A4

3 4

MDQ_A34

5 6

MDQS_A4

7 8

MDQ_A40

1 2

MDQ_A44

3 4

MDQ_A35

5 6

MDQ_A39

7 8

MDQ_A28

1 2

MDQ_A24

3 4

MDQ_A19

5 6

MDQ_A23

7 8

MDQ_A1

1 2

MDQ_A5

3 4

MDQ_A4

5 6

MDQ_A0

7 8

MDQ_A47

1 2

MDQ_A46

3 4

MDQ_A43

5 6

MDQ_A42

7 8

MDQ_A61

1 2

MDQ_A60

3 4

MDQ_A51

5 6

MDQ_A50

7 8

MDQ_A58

1 2

MDQ_A59

3 4

MDQ_A63

5 6

MDQ_A62

7 8

MDQ_A55

1 2

MDQ_A54

3 4

MDQS_A6

5 6

MDQM_A6

7 8

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

2

VTT_DDR

RN32

56

RN33

56

RN48

56

RN36

56

RN37

56

RN40

56

RN41

56

RN49

56

RN31

56

RN39

56

RN34

56

RN28

56

RN45

56

RN47

56

RN44

56

DECOUPLING CAPACITORS

C451

1 2

2.2uF/6.3V/Y5V

C411

1 2

2.2uF/6.3V/Y5V

C414

1 2

2.2uF/6.3V/Y5V

C406

1 2

2.2uF/6.3V/Y5V

C438

1 2

2.2uF/6.3V/Y5V

C463

1 2

2.2uF/6.3V/Y5V

C447

1 2

2.2uF/6.3V/Y5V

C457

1 2

2.2uF/6.3V/Y5V

C443

1 2

2.2uF/6.3V/Y5V

C434

1 2

2.2uF/6.3V/Y5V

C428

1 2

2.2uF/6.3V/Y5V

C448

1 2

2.2uF/6.3V/Y5V

Place these decoupling capacitors close to VTT_DDR termination resistors.

One decoupling capacitor for each R-pack.

VTT_DDRVTT_DDR

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

C403

2.2uF/6.3V/Y5V

C398

2.2uF/6.3V/Y5V

C462

2.2uF/6.3V/Y5V

C405

2.2uF/6.3V/Y5V

C425

2.2uF/6.3V/Y5V

C437

2.2uF/6.3V/Y5V

C461

2.2uF/6.3V/Y5V

C453

2.2uF/6.3V/Y5V

C445

2.2uF/6.3V/Y5V

C442

2.2uF/6.3V/Y5V

C426

2.2uF/6.3V/Y5V

C454

2.2uF/6.3V/Y5V

C459

2.2uF/6.3V/Y5V

Micro Star Restricted Secret

DDR DIMM 1

MS-7017

Last Revision Date:

Tuesday, January 27, 2004

Sheet

10 29

of

1

Rev

1.0c

Page 11

5

4

3

2

1

SYSTEM MEMORY

DDR DIMM3

DIMM2

48

SIGNALS

A0

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

A10/AP

118

A11

115

A12/NC

167

A13/NC

59

BA0

52

BA1

113

NC/BA2

157

CS0#

158

CS1#

71

NC/CS2#

163

NC/CS3#

154

RAS#

65

CAS#

63

WE#

5

DQS0

14

DQS1

25

DQS2

36

DQS3

56

DQS4

67

DQS5

78

DQS6

86

DQS7

47

DQS8

97

DQM0/DQS9

107

DQM1/DQS10

119

DQM2/DQS11

129

DQM3/DQS12

149

DQM4/DQS13

159

DQM5/DQS14

169

DQM6/DQS15

177

DQM7/DQS16

140

DQM8/DQS17

44

MECC0

45

MECC1

49

MECC2

51

MECC3

134

MECC4

135

MECC5

142

MECC6

144

MECC7

21

CKE0

111

CKE1

92

SCL

91

SDA

181

SA0

182

SA1

183

SA2

16

CK0/NC

17

CK0#/NC

137

CK1/CK0

138

CK1#/CK0#

76

CK2/NC

75

CK2#/NC

82

ID_VDD

184

SPD_VDD

7

VDD

38

VDD

46

VDD

70

VDD

85

VDD

108

VDD

120

VDD

148

VDD

168

VDD

81

GND

89

GND

93

GND

100

GND

116

GND

124

GND

132

GND

139

GND

145

GND

152

GND

160

GND

176

GND