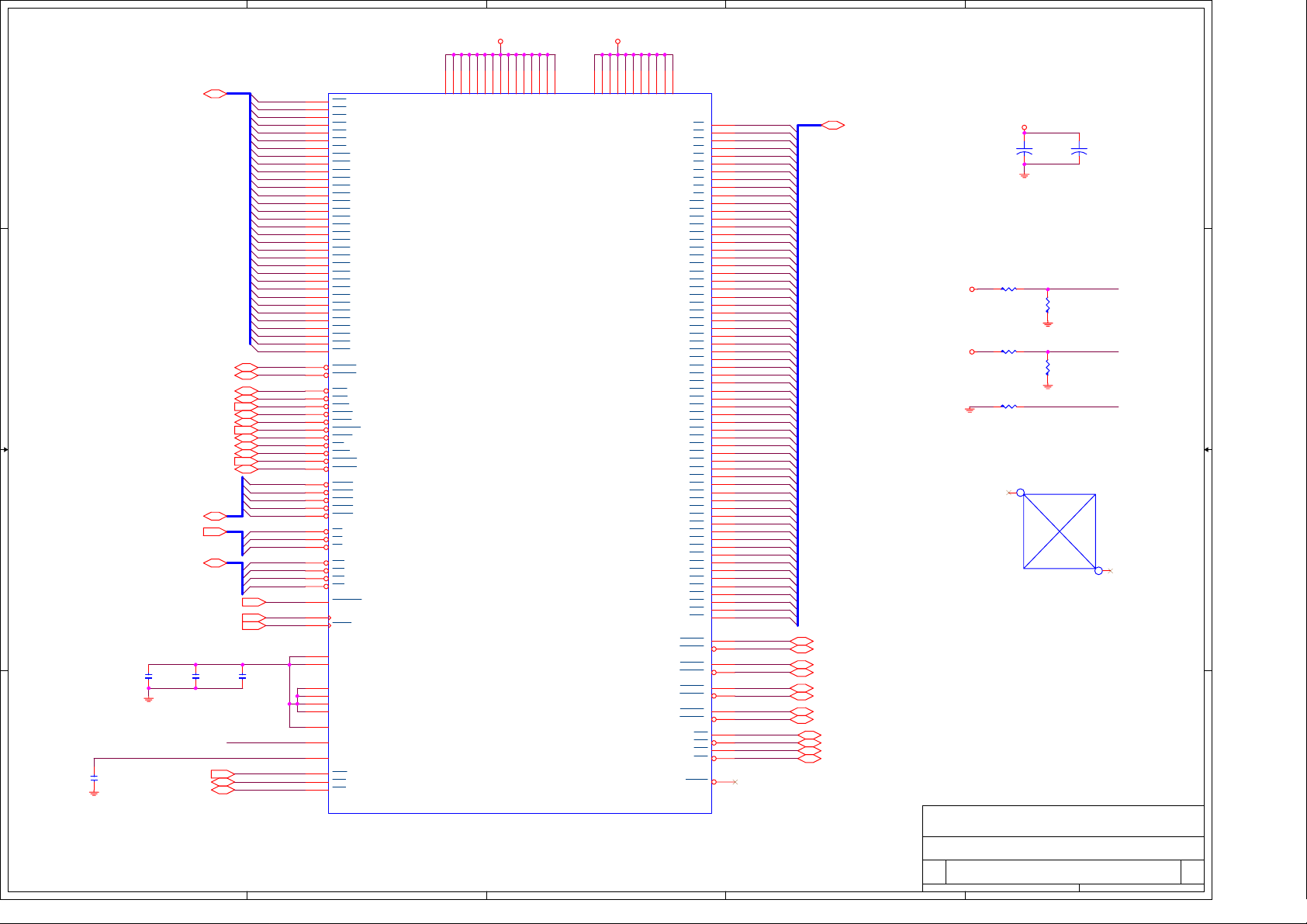

Page 1

A

MS7004V10A

B

C

D

E

TITLE

4 4

COVER SHEET

SHEET

1

CPU:

BLOCK DIAGRAM

PWR MAP/CLOCK MAP

GPIO/MEMORY/PCI/HW STRPPING

PROCESSOR (SOCKET478)

NORTH BRIDGE PM800/PT800CE

DIMM1 / DIMM2

3 3

DDR TERMINATIONS

AGP SLOT

2

3

4

5,6

7 -- 10

11

12

13

Intel Northwood/Prescott

Up to 3.6GHz

System Chipset:

PM800/PT800 (North Bridge)

VIA 8237 (South Bridge)

On Board Chipset:

BIOS -- ISA EEPROM

AC'97 Codec --ALC655

LPC Super I/O -- W83697HF

SOUTH BRIDGE VT8237/VT8235CE

PCI SLOTS 1-3

AC'97 AUDIO

LAN

IDE CONNECTORS & CNR

14 -- 16

17

18

19

20

LAN -- PHY RTL8201

CLOCK -- CY28341-3

Main Memory:

DDR * 2 (Max 2GB)

Expansion Slots:

USB CONNECTORS

2 2

LPC SUPER IO & FLOPPY CONNECTOR

PARALLEL / SERIAL / VGA

ATX POWER CONNECTOR / FRONT PANEL

CLOCK GEN.

21

22

23

24

25

AGP * 1

PCI2.3 SLOT * 3

CNR * 1

PWM:

Controller: STL6710

MS7 ACPI CONTROLLER

VRM10.0(FMB1)

EMI & MISC.

1 1

HISTORY

A

B

26

27

28

29

Title

Size Document Number Rev

C

D

Date: Sheet

Micro-Star

COVER SHEET

MS-7004

10A

of

129Wednesday, February 25, 2004

E

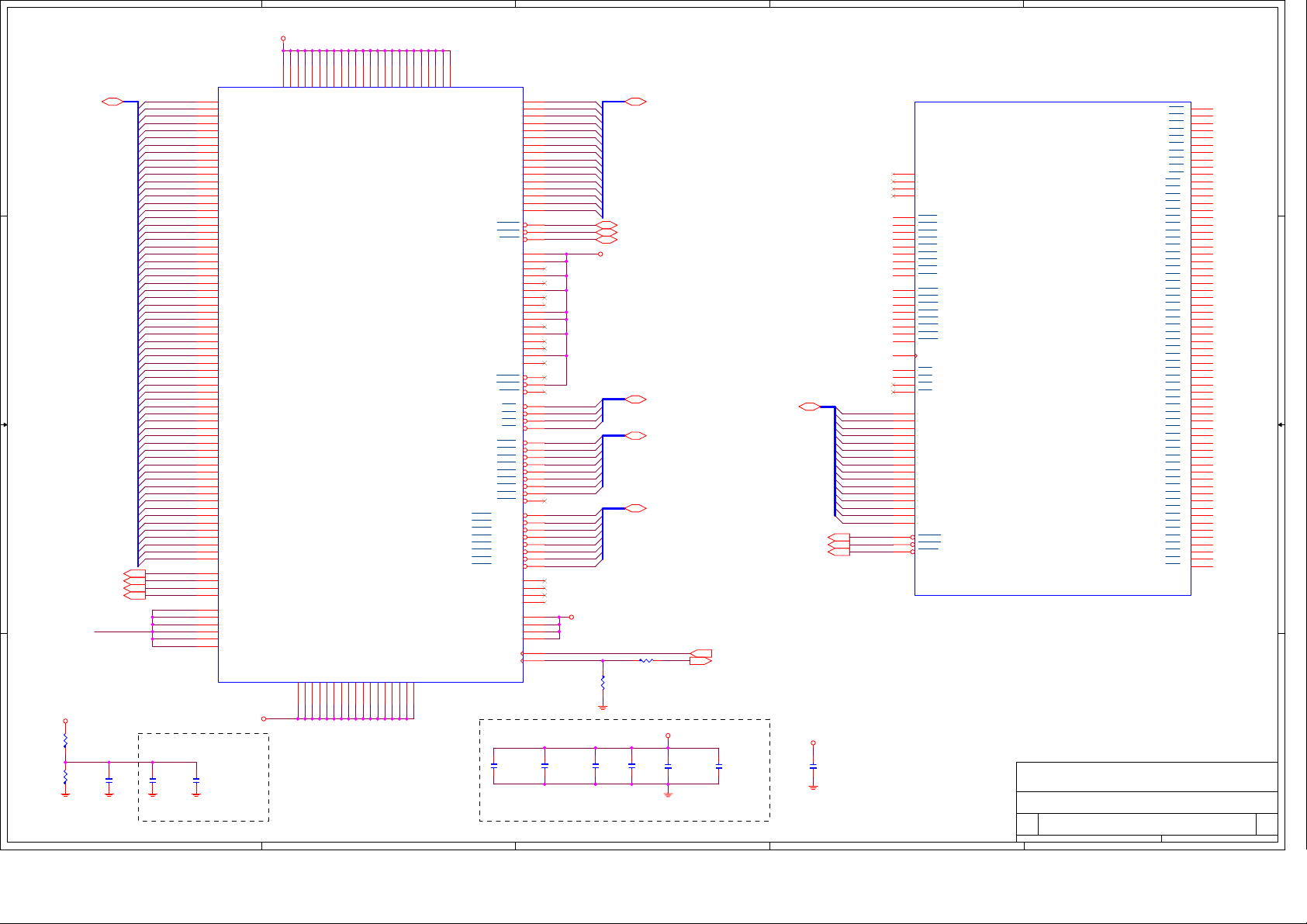

Page 2

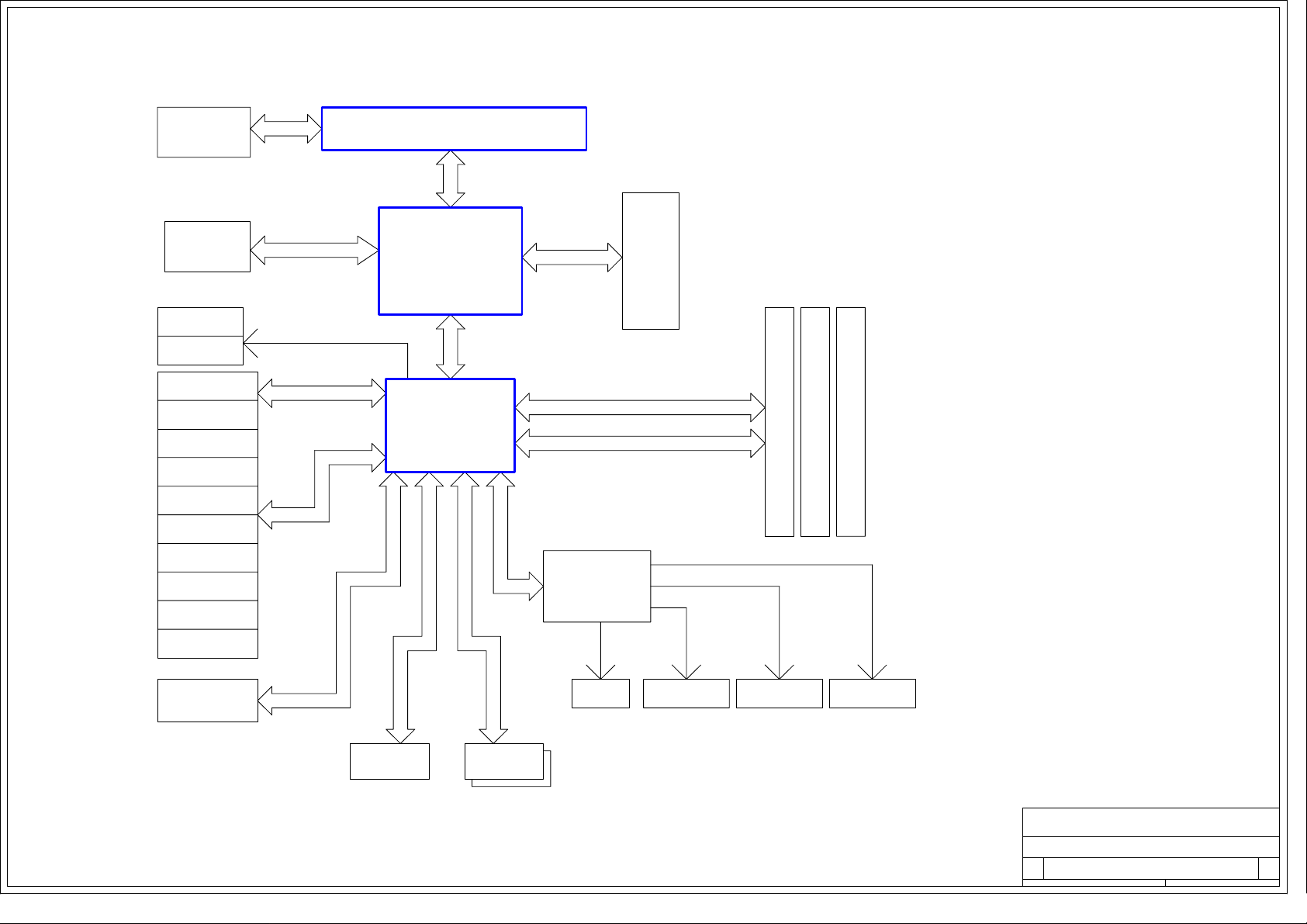

Block Diagram

1

VRM 10

ISL6563

Intel mPAG478B Processor

2-Phase PWM

FSB

AGP 1.5V

Connector

Keyboard

4X/8X

PM800/

PT800

V-Link

64bit DDR

2 DDR

DIMM

Modules

Mouse

IDE Primary

IDE Secondary

A A

USB Port 0

UltraDMA 33/66/100

VT8237

PCI CNTRL

PCI ADDR/DATA

PCI Slot 1

PCI Slot 2

PCI Slot 3

USB Port 1

USB Port 2

USB

LPC Bus

USB Port 3

USB Port 4

LPC SIO

USB Port 5

Winbond

83697HF

USB Port 6

USB Port 7

AC'97 Codec

AC'97 Link

Floopy

SATA 1 & 2Lan Phy

1

ParallelFlash

Serial

Title

Size Document Number Rev

Date: Sheet

Micro-Star

BLOCK DIAGRAM

MS-7004

229Wednesday, February 25, 2004

of

10A

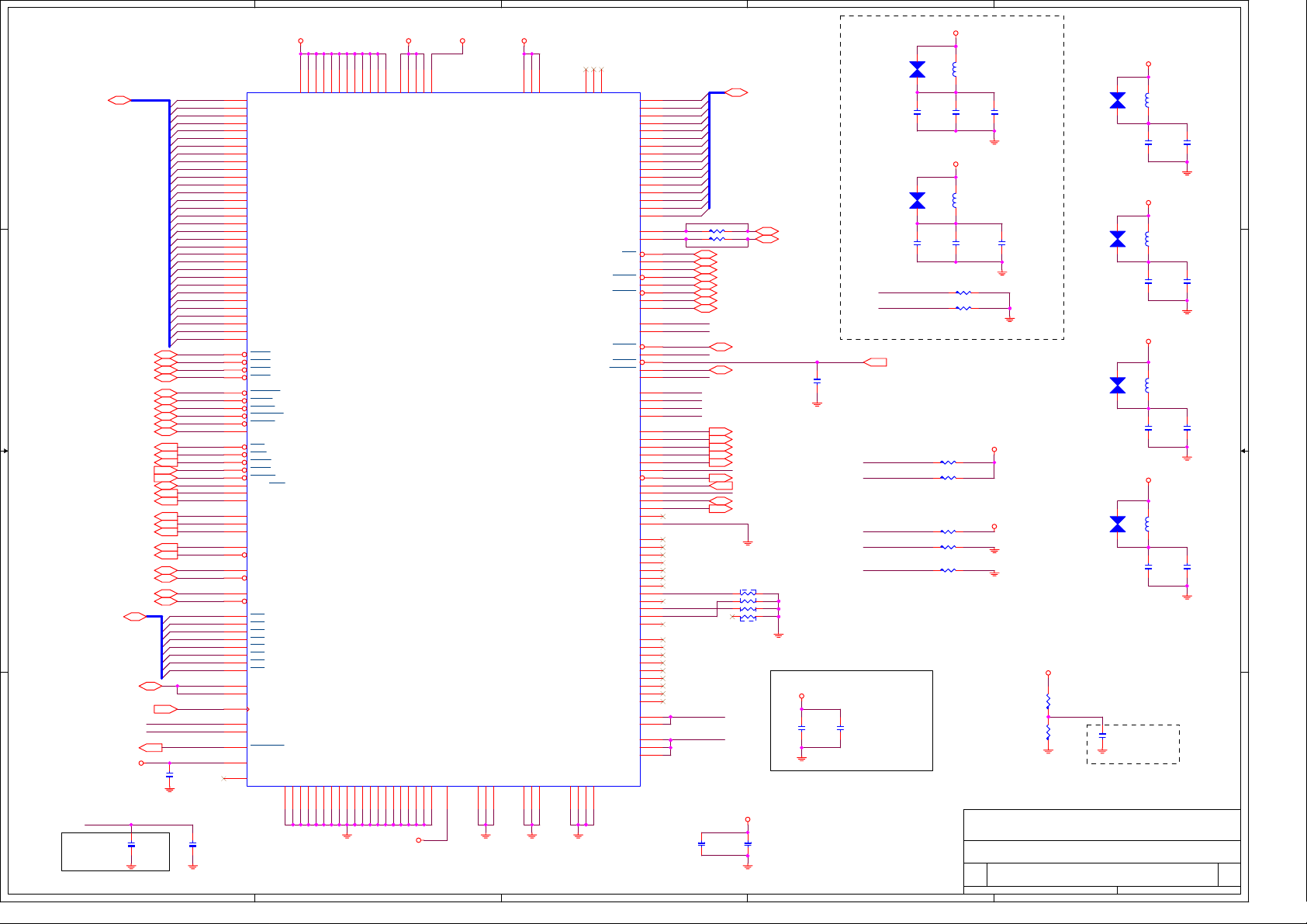

Page 3

8

7

6

5

4

3

2

1

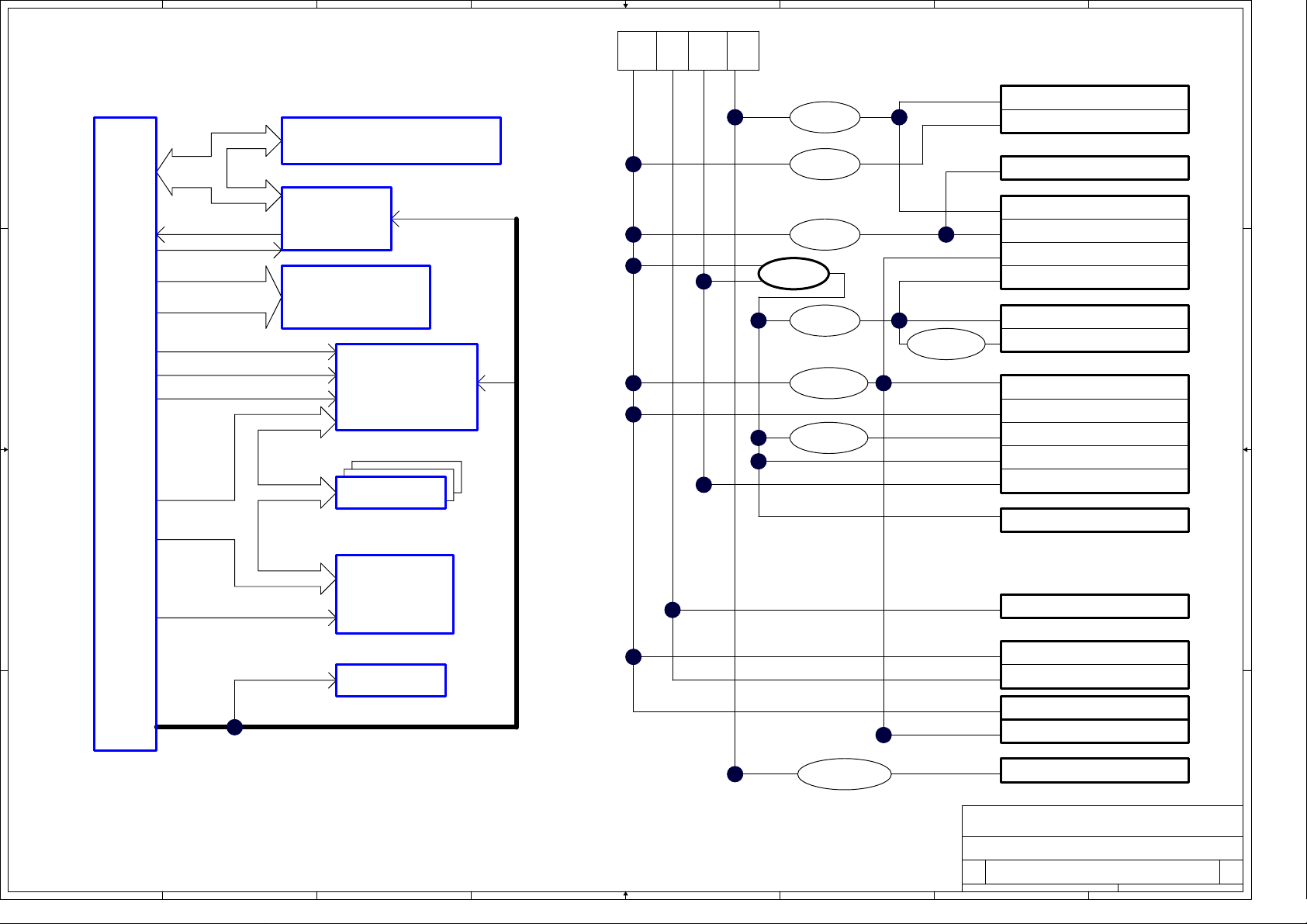

PT800 PLATFORM CLOCK GENERATOR MAP

3.3V 5V 5VSB 12V

PT800 PLATFORM POWER DELIVERY MAP

PROCESSOR VCCP

D D

VRM

PROCESSOR 1.2V

Intel mPAG478B Processor

CPU HOST

CLK

DCLKO

PT800A

AGP CLK

DCLKI

CLOCK GENERATOR

MEM CLK

C C

14.318MHZ

2 DDR Dimm

1.2V VREG

1.5V VREG

3VSB VREG

DDR 2.5V

VREG

VTT 1.25V

VREG

APIC

48MHZ

VT8237

2.5V VREG

PCI CLK

2.5VSB

VREG

PCI CLK 0~2

PCI Slot 1~3

AGP SLOT 1.5V

NORTH BRIDGE VCCP

NORTH BRIDGE VCC_AGP

NORTH BRIDGE +2.5V

NORTH BRIDGE SYSEM MEMORY

VCC_DDR

DDR DIMM1 / DIMM2 / DIMM3 2.5V

DDR VTT 1.25V

SOUTH BRIDGE +2.5V

SOUTH BRIDGE VCC3

SOUTH BRIDGE RESUME 2.5V_SB

SOUTH BRIDGE RESUME VCC3_SB

SOUTH BRIDGE RTC 3.3V

LAN-PHY VCC3_SB

B B

48MHZ

PCI CLK

LPC SIO

Winbond

83697HF

BIOS 5V

LPC SUPER I/O 3.3V

AGP CLK

AGP SLOT

LPC SUPER I/O VCC5

CLK 3.3V

DDR BUFFER +2.5V

AC97 VDD5

A A

8

7

6

5

4

VREG

Title

Size Document Number Rev

3

Date: Sheet

AC97 VDD5

Micro-Star

PWR AND CLOCK MAP

MS-7004

2

10A

329Wednesday, February 25, 2004

of

1

Page 4

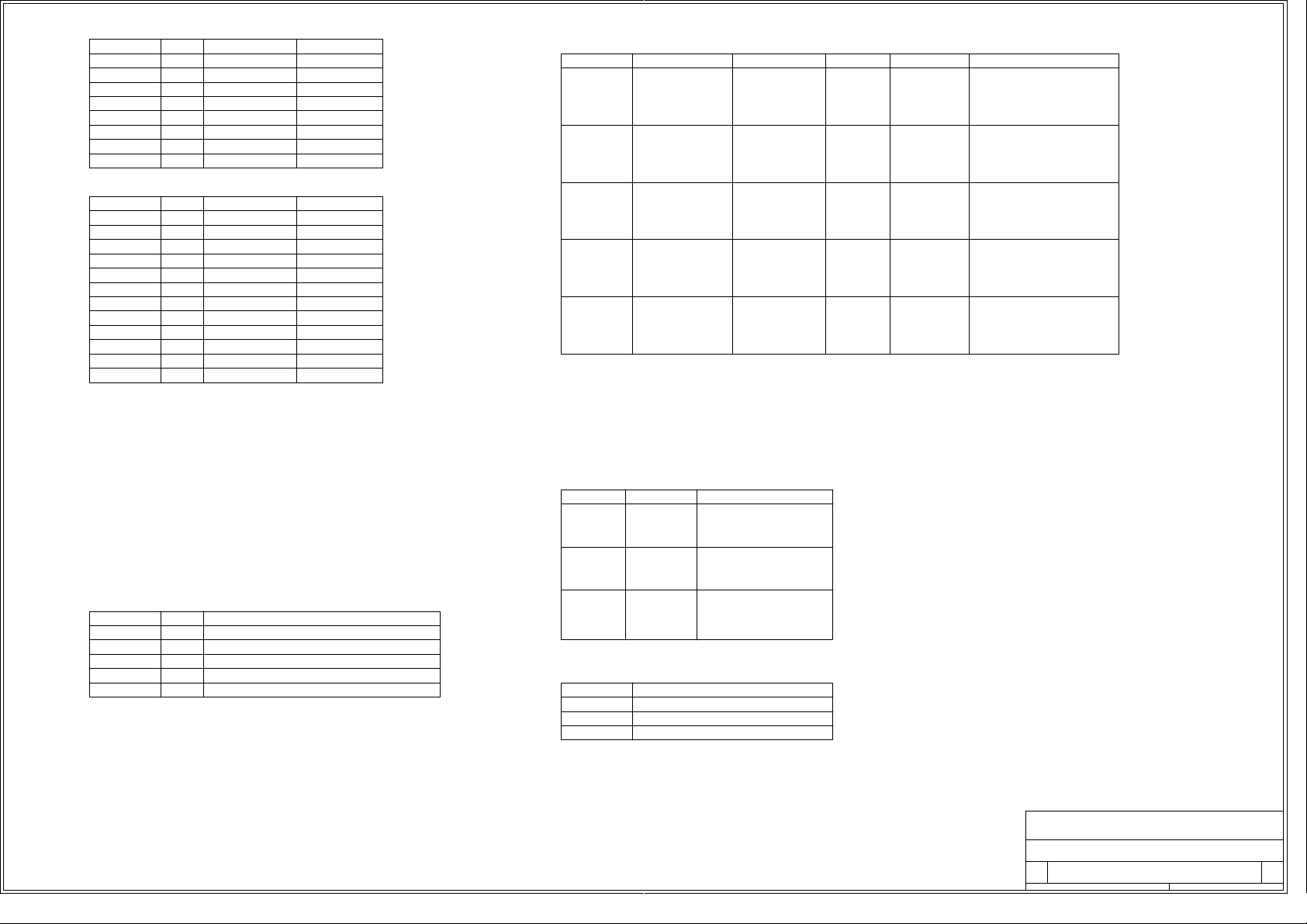

1

NB

PCI Config.

DEVICE

INTA#

INTB#

PCI_REQ#0PCI Slot 1

PCI_GNT#0

INTC#

INTD#

PCI Slot 2

INTB#

INTC#

PCI_REQ#1 AD20 PCICLK1

PCI_GNT#1

INTD#

INTA#

PCI Slot 3 PCI_REQ#2 AD21

INTC#

INTD#

PCI_GNT#2

INTA#

INTB#

INTD#

PCI_REQ#3PCI Slot 4 AD22

INTA# PCI_GNT#3

INTB#

INTC#

PCI Slot 5

INTA#

INTB#

PCI_REQ#4 AD23 PCICLK4

PCI_GNT#4

INTC#

INTD#

IDSEL

AD19

CLOCKREQ#/GNT#

PCICLK0

PCICLK2

PCICLK3

CLK GEN PIN OUTMCP1 INT Pin

18 (PCI_CLK0)

19 (PCI_CLK1)

21 (PCI_CLK2)

14 (PCI_CLK3)

17 (PCI_CLK4)

GPI 0

GPI 1

GPO 0

GPO 1 I

GPIO A

GPIO B

GPIO C

GPIO D

I

I

I

I

I

I

I

FunctionTypeGPIO Pin

GPI 0

IDE2 CBD

GPO 0

GPO 0

NB STR S

IOQ DEPH

NB STR S

GTL PULL

Power well

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

I/O

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16

GPIO 17

GPIO 18

GPIO 19

GPIO 20

GPIO 21

GPIO 22

A A

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

HI

HI

HI

NA

NA

NA

NA

NA

NA

NA

NA

NA

NA

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

default output

default output

default output

FWH

GPI 0

GPI 1

GPI 2

GPI 3

GPI 4

Function

TypeGPIO Pin

Pull UP through 1K ohms (unused)

I

Pull UP through 1K ohms (unused)

I

Pull UP through 1K ohms (unused)

I

Pull UP through 1K ohms (unused)

I

Pull UP through 1K ohms (unused)

I

DDR DIMM Config.

DEVICE

DIMM 1 MCLK0/MCLK#0

DIMM 2

1010000B

1010001B

DIMM 3 1010010B

CLOCKADDRESS

MCLK1/MCLK#1

MCLK2/MCLK#2

MCLK3/MCLK#3

MCLK4/MCLK#4

MCLK5/MCLK#5

MCLK6/MCLK#6

MCLK7/MCLK#7

MCLK8/MCLK#8

PCI RESET DEVICE

Signals

PCIRST#1

HD_RST#

SB, NB

PCI slot 1-3, 1394,PCIRST#2

Primary, Scondary IDE

Target

FWH

1

Title

Size Document Number Rev

Date: Sheet

Micro-Star

General Purpose Spec

MS-7004

429Wednesday, February 25, 2004

of

10A

Page 5

8

7

6

5

4

3

2

1

D17#

E24

HD#16

HD#17

AE25A5A4

D16#

H22

D25

HD#15

DBR#

D15#

J21

HD#14

D14#

D23

HD#13

DBRESET

AD26

AC26

ITP_CLK1

VSS_SENSE

VCC_SENSE

D13#

D12#

D11#

D10#

C26

H21

G22

B25

HD#9

HD#12

HD#10

HD#11

VID5

AD2

ITP_CLK0

VIDPWRGD

D9#

D8#

D7#

C24

C23

HD#6

HD#7

HD#8

AD3

B24

VID4

AE1

VID5#

D6#

D22

HD#5

VID3

AE2

VID4#

D5#

C21

HD#4

VID2

AE3

VID3#

D4#

A25

HD#3

VID1

AE4

VID2#

D3#

A23

HD#2

VID0

AE5

VID1#

D2#

B22

HD#1

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D1#

D0#

ZIF-SOCKET478

B21

HD#0

CPU_VID_GD 27

VID[0..5] 27

AA21

AA6

F20

F6

BPM#5

AB4

BPM#4

AA5

BPM#3

Y6

BPM#2

AC4

BPM#1

AB5

BPM#0

AC6

HREQ#4

H3

HREQ#3

J3

HREQ#2

J4

HREQ#1

K5

HREQ#0

J1

TESTHI12

AD25

TESTHI11

A6

TESTHI10

Y3

TESTHI9

W4

TESTHI8

U6

AB22

AA20

AC23

TESTHI2

AC24

AC20

AC21

AA2

TESTHI0

AD24

AF23

AF22

HRS#2

F4

HRS#1

G5

HRS#0

F1

AP#1

V5

AP#0

AC1

HBR#0

H6

COMP1

P1

COMP0

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

NMI

E5

INTR

D1

VIDPWRGD DC Specifications

HREQ#[0..4] 7

12

34

56

78

CPUCLK# 25

CPUCLK 25

HRS#[0..2] 7

AP#1 7

AP#0 7

HBR#0 7

HADSTB#1 7

HADSTB#0 7

HDSTBP#3 7

HDSTBP#2 7

HDSTBP#1 7

HDSTBP#0 7

HDSTBN#3 7

HDSTBN#2 7

HDSTBN#1 7

HDSTBN#0 7

INTR 16

Min MaxTyp

0.9

VCCP

RN102

62X4

C318

0.1u

VIL

VIH

It must rout to the enable pin of PWM and CK-409.

VIDGD to Vccp delay time is from 1ms to 10ms.

VIDGD rising time is 150ns.

X7R

GTLREF

C163 220p

R129 62

TESTHI10

TESTHI9

TESTHI8

TESTHI11

R126 62

R130 62

R189 61.9R1%

R163 61.9R1%

DP#3 7

DP#2 7

DP#1 7

DP#0 7

CPU GTL REFERNCE VOLTAGE BLOCK

0.3

VCCP

R173

GTLREF

0.64*Vccp

C164

0.1u

X7R

56R1%

R174

100R1%

CPU ITP BLOCK

ITP_TDI

ITP_TRST#

ITP_TMS

ITP_TDO

ITP_TCK

IGNNE#

A20M#

SLP#

SMI#

INTR

NMI

HINIT#

STPCLK#

BOOT

DBRESET

FERR#

THERMTRIP#

PROCHOT#

BPM#3

BPM#0

IERR#

BPM#4

BPM#5

BPM#1

BPM#2

CPURST#

R175 X_150

R167 680

R170 X_39

R127 X_75

R128 X_27

150X8

NMI

RN24

1

1

2

2

3

3

4

4

6

6

7

7

8

8

9510

9510

R168X_300

12

34

62X4

56

78

12

34

62X4

56

78

12

34

62X4

56

78

R11662

RN22

RN23

RN26

VCCP

VCCP

VCCP

VCCP

NMI_SB 16

C338

0.1u

VCCP

CPU SIGNAL BLOCK

HA#[3..35]7

HA#17

A18#

D33#

M23

HD#32

HA#16

A17#

D32#

H25

HD#31

HA#15

A16#

D31#

K23

HD#30

HA#14

A15#

D30#

J24

HD#29

HA#13

A14#

D29#

HD#28

L22

HA#12

A13#

D28#

M21

HD#27

HA#11

A12#

D27#

H24

HD#26

HA#25

HA#34

A35#

D50#

U24

HD#49

HA#33

A34#

D49#

U26

HD#48

HA#32

A33#

D48#

T23

HD#47

A32#

D47#

T22

HD#46

A31#

D46#

HD#45

A30#

D45#

T25

HA#28

A29#

D44#

T26

HD#43

HD#44

R24

A28#

D43#

R25

HD#42

A27#

D42#

P24

HD#41

A26#

D41#

R21

HD#40

D D

CPU1A

HDBI#[0..3]7

FERR#16

STPCLK#16

HINIT#16

RSP#7

HDBSY#7

HDRDY#7

HTRDY#7

HADS#7

HLOCK#7

HBNR#7

HITM#7

HBPRI#7

C C

B B

HDEFER#7

CPU_TMPA22

CPUMISS15

IGNNE#16

A20M#16

BOOT27

BSEL015,25

BSEL115,25

CPU_GD26

CPURST#7

HD#[0..63]7

HDBI#0

HDBI#1

HDBI#2

HDBI#3

HIT#7

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

THERMTRIP#

PROCHOT#

IGNNE#

SMI#

SMI#16

A20M#

SLP#

SLP#16

BOOT

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

IERR#

FERR#

STPCLK#

HINIT#

RSP#

CPUMISS

G25

AC3

AA3

AB2

AF26

AB26

AE21

AF24

AF25

AD1

AE26

AD6

AD5

AB23

AB25

AA24

AA22

AA25

W25

W26

E21

P26

V21

V6

B6

Y4

W5

H5

H2

J6

G1

G4

G2

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A22

A7

Y21

Y24

Y23

Y26

V24

HA#35

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

BOOTSELECT

OPTIMIZED/COMPAT#

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

D52#

D51#

V22

U21

V25

U23

HD#50

HD#52

HD#53

HD#51

HA#27

HA#30

HA#26

HA#29

HA#31

HA#24

A25#

D40#

N25

HD#39

HA#23

A24#

D39#

HD#38

N26

HA#22

A23#

D38#

M26

HD#37

HA#21

A22#

D37#

HD#36

N23

A21#

D36#

HA#20

HA#19

A20#

D35#

M24

P21

HD#35

HD#34

HA#18

A19#

D34#

N22

HD#33

HA#10

A11#

D26#

G26

HD#25

HA#9

A10#

D25#

L21

HD#24

HA#8

A9#

D24#

D26

HD#23

HA#7

A8#

D23#

F26

HD#22

HA#6

A7#

D22#

E25

HD#21

HA#5

A6#

D21#

F24

HD#20

HA#4

A5#

D20#

F23

HD#19

HA#3

A4#

D19#

G23

HD#18

A3#

D18#

CPU STRAPPING RESISTORS

A A

ALL COMPONENTS CLOSE TO CPU

CPU_GD

HBR#0

8

7

R131 300

R186 220

VCCP

6

RSMRST#16

5

VCCP

R395

X_4.7K

B

RSMRST# THERMTRIP#

C E

Q41

X_N-MMBT3904_SOT23

THERM#15

4

VCCP

R191

4.7K

B

THERM# PROCHOT#

C E

Q25

N-MMBT3904_SOT23

3

BSEL0

BSEL1

Title

Size Document Number Rev

Date: Sheet

2

R3801K

R3811K

Micro-Star

Intel mPGA478B - Signals

MS-7004

VCC3

529Wednesday, February 25, 2004

1

10A

of

Page 6

8

7

6

5

4

3

2

1

E20E8F11

VCC

VCC

VSS

VSS

Near processor

F13

F15

VCC

VCC

VCC

VSS

VSS

VSS

G21G6G24

G3H1H23

1.2V 150mA

C109

0.1u

F17

F19

F9

VCC

VCC

VCC

VSS

VSS

VSS

VSS

H26H4J2

It support DC current if 100mA.

CPU_IOPLL

AE23

AD20

AF4

AF3

AD22

VCCA

VSS

J22

VCC-VIDPRG

VSS

VSS

J25J5K21

VSSA

VCC-IOPLL

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

ZIF-SOCKET478

<Priority>

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

VCC-VID

VSS

C123

10u-1206

VSSA

The ESL is less than 5nH, and the ESR is less than 0.3ohm.

L8 10U100m_0805

L9 10U100m_0805

C111

X_10u-1206

DC voltage drop should

be less than 70mV.

CPU1_X

CPU Fan Retention

VCCP

+

close to CPU

D13

D15

VCC

VCC

VCC

VSS

VSS

VSS

E7E9F10

E4

E26

C107

10u-0805

D17

D19D7D9

VCC

VCC

VSS

VSS

VCC_VID

VCC

VSS

F12

F14

VCC

VSS

E10

VCC

VSS

F16

E12

E14

VCC

VCC

VSS

VSS

F18F2F22

X_1u

E16

C120

E18

VCC

VSS

F25F5F8

VCC

VSS

VCC_VID26

CPU VOLTAGE BLOCK

VID Voltage is from 1.14V to 1.32V.

It is derived from 3.3V.

It should be able to source 150mA.

D D

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

AA19

VSS

AA23

C C

B B

AA26

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC22

AC25

AA4

AA7

AA9

AB3

AB6

AB8

AC2

AC5

AC7

AC9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

VSS

AD12

VSS

AD14

VSS

AD16

VSS

AD18

VSS

AD21

VSS

AD23

AD4

VSS

AD8

VSS

AE11

VSS

VSS

AE13

AE15

VSS

VSS

AE17

VSS

AE19

VSS

AE22

VSS

AE24

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF6

AF8

B10

B12

B14

B16

B18

AE20

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B23

B20

B26B4B8

C11

C13

It drives the power logic of BSEL[1:0] and VID[5:0].

VID to VIDGD delay time is from 1ms to 10ms.

VID to VIDGD deassertion time is 1ms for max.

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C15

C17C2C19

C22

C25C5C7C9D12

D14

D16

D18

B13

B15

B17

B19B7B9

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

D20

D21D3D24D6D8E1E11

VCC

VSS

C10

C12

C14

C16

C18

C20C8D11

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E13

E15

E17

E19

E23

CPU DECOUPLING CAPACITORS

VCCP

C179

VCCP

22u-1206

C178

22u-1206

C158

22u-1206

C147

A A

8

22u-1206

7

C282

X_C100U6.3SP

C281

C100U2SP

C337

C100U2SP

6

VCCP

C113

X_10u-1206

C114

X_10u-1206

C115

X_10u-1206

C116

X_22u-1206

C117

X_10u-1206

C118

X_10u-1206

Title

Size Document Number Rev

5

4

3

Date: Sheet

2

Micro-Star

Intel mPGA478B - Power

MS-7004

629Wednesday, February 25, 2004

1

10A

of

Page 7

A

HA#[3..35]5

4 4

3 3

HADSTB#05

HADSTB#15

HADS#5

HBNR#5

HBPRI#5

HBR#05

HDBSY#5

HDEFER#5

HDRDY#5

HIT#5

HITM#5

HLOCK#5

HTRDY#5

HREQ#[0..4]5

HRS#[0..2]5

2 2

HDBI#[0..3]5

CPURST#5

NBHCLK25

NBHCLK#25

near NB

GTLVREF_NB

C289

103p_B

C286

103p_B

Solder side

1 1

C169

103P

RSP#5

AP#05

AP#15

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HA#34

HA#35

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

C285

103P_B

HRCOMP

HCOMPVREF

B22

A20

F20

A21

B21

E23

C21

D21

E22

F21

C22

E21

D22

F22

C25

C24

D24

E24

E25

F26

B26

B23

E26

D25

E27

C23

F27

D27

D28

C27

C28

E28

F28

A22

C26

A19

C18

C16

E18

B19

E17

C19

C17

F16

F18

G18

D19

C20

D20

E19

F19

B18

D18

B17

B13

H19

G22

H11

H14

H17

F15

G14

F23

F25

F24

A6

J3

A5

K6

M5

M6

K7

J7

NB1A

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

HA32

HA33

HA34

HA35

ADSTB0

ADSTB1

ADS

BNR

BPRI

BREQ0

DBSY

DEFFER

DRDY

HIT

HITM

HLOCK

HTRDY

HREQ0

HREQ1

HREQ2

HREQ3

HREQ4

RS0

RS1

RS2

DBI0

DBI1

DBI2

DBI3

CPURST

HCLK

HCLK

HAVREF0

HAVREF1

HDVREF0

HDVREF1

HDVREF2

HDVREF3

GTLREF

HRCOMP

HCOMPVREF

RSP/RESEVE

AP0/RESEVE

AP1/RESEVE

B

VCCP VCCP

C29

F29

H27

N13

N14

N15

N16

N17

N18

N19

N20

R13

T13

U13

P13

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

C

P14

P15

P16

P17

P18

P19

P20

R14

T14

U14

V14

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

DSTBP0

DSTBN0

DSTBP1

DSTBN1

DSTBP2

DSTBN2

DSTBP3

DSTBN3

RESEVE/DP0

RESEVE/DP1

RESEVE/DP2

RESEVE/DP3

DPWR

G10

D9

C9

B9

F10

B7

A9

F9

E7

E9

F7

C7

A8

C8

D7

A7

D16

E16

B14

D15

E15

C14

E14

C15

D12

C13

B12

B10

C11

B11

A10

C12

H6

G7

J4

G6

H5

G3

H4

G4

K1

J5

H1

J6

J1

J2

K4

K3

C3

C4

B4

D3

A4

C5

D4

E4

E2

E3

F3

F4

C2

F1

G1

F2

F8

D8

E13

D13

H3

H2

D1

E1

B6

D6

C6

E6

G15

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

D

HD#[0..63] 5

HDSTBP#0 5

HDSTBN#0 5

HDSTBP#1 5

HDSTBN#1 5

HDSTBP#2 5

HDSTBN#2 5

HDSTBP#3 5

HDSTBN#3 5

DP#0 5

DP#1 5

DP#2 5

DP#3 5

VCCP

VCCP

VCCP

+

X_10u-0805

R155 56R1%

R177 100R1%

R180 20.5R1%

NB Heatsink

2

NB1_X1

HEATSINKL400W400H100

C166

X_10u-0805

GTLVREF_NB

R150

100R1%

HCOMPVREF

R179

49.9R1%

HRCOMP

E

C165

+

1

Title

Size Document Number Rev

A

B

C

D

Date: Sheet

Micro-Star

NORTH BRIDGE (PART 1 & PART4)

MS-7004

729Wednesday, February 25, 2004

E

10A

of

Page 8

A

B

C

D

E

VCC_DDR

P24

R24

T24

U24

V24

W24

Y24

AA24

AB24

AC24

N21

N22

AD19

AD20

AD21

AD22

AD23

AD24

AK32

AK33

AP34

VCC3

VCC3

VCC3

VCC3

VCC25MEM

VCC25MEM

VCC25MEM

AC22

AC23

AP36

VCC3

VCC3

VCC3

VCC3

VCC25MEM/MAC0

VCC25MEM/MAC1

VCC25MEM/MAC3

VCC25MEM/MAC5

VCC25MEM/MAC8

VCC25MEM/MAC9

VCC25MEM/MAC11

VCC25MEM/MAC14

VCC25MEM/SCASC

DQMA0/MPDA0

DQMA1/MPDA1

DQMA2/MPDA2

DQMA3/MPDA3

DQMA4/MPDA4

DQMA5/MPDA5

DQMA6/MPDA6

DQMA7/MPDA7

RESEVE/QBMMEA0

RESEVE/QBMMEA1

RESEVE/QBMSBA0

RESEVE/QBMSBA1

VCC25MEM/QBMMEB0

VCC25MEM/QBMMEB1

VCC25MEM/QBMSBB0

VCC25MEM/QBMSBB1

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

MAA15

SRASA

SCASA

SWEA

MAC2

MAC4

MAC6

MAC7

MAC10

MAC12

MAC13

MAC15

SRASC

SWEC

CSA0

CSA1

CSA2

CSA3

DQSA0

DQSA1

DQSA2

DQSA3

DQSA4

DQSA5

DQSA6

DQSA7

DQSA8

DCLKIA

DCLKOA

C331

10u-0805_B

AJ33

AH35

AH34

AD33

AD36

AB34

AB35

V32

W36

V35

AT36

AT31

AT35

U36

T34

AT20

AP26

AN25

AR26

AE31

AB32

AA35

Y36

AA34

W30

Y31

R33

R31

N36

AF31

AH31

AE32

P33

M30

AN22

AN30

AN29

AP30

AT25

AR25

AP29

AP25

D35

L31

U34

AD34

AT33

AT24

AN20

AR16

AH36

D36

L33

V34

AD35

AN32

AP24

AP20

AT16

G36

G35

G33

G34

F36

F34

F33

F32

A32

B31

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

MAA15

-CS0

-CS1

-CS2

-CS3

-DQS0

-DQS1

-DQS2

-DQS3

-DQS4

-DQS5

-DQS6

-DQS7

-DQM0

-DQM1

-DQM2

-DQM3

-DQM4

-DQM5

-DQM6

-DQM7

VCC_DDR

DCLKI

DCLKO_A

CB113

10u-0805_B

Solder side

-SRASA 11,12

-SCASA 11,12

-SWEA 11,12

VCC_DDR

R185 22

R392

X_1K

4.7U_0603_B

CB109

1u_B

MAA[0:15] 11,12

-CS[0:3] 11,12

-DQS[0:7] 11,12

-DQM[0:7] 11,12

VCC_DDR

CB114

C

C295

10u-0805_B

DCLKI 25

DCLKO 25

C193

0.1u_B

MAB[0:15]11,12

-SRASB11,12

-SCASB11,12

-SWEB11,12

DCLKO as short as passable

DCLKI = DCLKx + 2 "

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

MAB14

MAB15

VCC_DDR

C196

10u-0805

Decoupling capacitors

NB1D

K32

K31

A33

H34

N34

Y34

AG33

AT28

AR22

AP18

AG31

A34

H36

N35

Y33

AG32

AR28

AP22

AN18

A31

AT30

AT29

AR29

AP28

AE33

AF30

AE30

AA30

AA36

Y30

W31

R32

P31

N31

AF34

AJ36

AF36

P36

M31

AN23

AL29

AN28

AN31

D

J33

J35

CKEB0

CKEB1

CKEB2

CKEB3

DQSB0

DQSB1

DQSB2

DQSB3

DQSB4

DQSB5

DQSB6

DQSB7

DQSB8

DQMB0/MPDB0

DQMB1/MPDB1

DQMB2/MPDB2

DQMB3/MPDB3

DQMB4/MPDB4

DQMB5/MPDB5

DQMB6/MPDB6

DQMB7/MPDB7

DCLKOB

CSB0

CSB1

CSB2

CSB3

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

MAB14

MAB15

SRASB

SCASB

SWEB

C32

MDB0

D33

MDB1

A35

MDB2

C34

MDB3

C33

MDB4

B33

MDB5

A36

MDB6

B34

MDB7

G31

MDB8

G32

MDB9

J34

MDB10

J31

MDB11

H31

MDB12

H33

MDB13

J32

MDB14

J36

MDB15

M32

MDB16

N32

MDB17

P34

MDB18

P30

MDB19

N30

MDB20

N33

MDB21

R34

MDB22

R30

MDB23

AA31

MDB24

AA32

MDB25

AA33

MDB26

AB31

MDB27

W32

MDB28

W33

MDB29

AB33

MDB30

AB30

MDB31

AG36

MDB32

AG35

MDB33

AH33

MDB34

AH30

MDB35

AF33

MDB36

AG34

MDB37

AH32

MDB38

AJ34

MDB39

AL30

MDB40

AM29

MDB41

AL28

MDB42

AN27

MDB43

AM31

MDB44

AM28

MDB45

AP27

MDB46

AL27

MDB47

AL23

MDB48

AM23

MDB49

AN21

MDB50

AK21

MDB51

AL22

MDB52

AM22

MDB53

AT22

MDB54

AL21

MDB55

AL18

MDB56

AN19

MDB57

AL17

MDB58

AM17

MDB59

AL19

MDB60

AM19

MDB61

AT18

MDB62

AN17

MDB63

Rev0.4

Title

Size Document Number Rev

Date: Sheet

Micro-Star

NORTH BRIDGE (PART 2)

MS-7004

E

of

829Wednesday, February 25, 2004

10A

MD0

NB1B

4 4

3 3

2 2

MD[0:63]11,12

CKE011,12

CKE111,12

CKE211,12

CKE311,12

MVREF_NB

VCC_DDR

1 1

R192

150R1%

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

CKE0

CKE1

CKE2

CKE3

W35

W34

AB36

AC34

AD32

AE35

AC33

AC36

AE36

AE34

AR34

AP33

AP32

AR31

AT34

AR33

AT32

AP31

AN26

AM25

AN24

AR23

AT27

AT26

AT23

AP23

AP21

AM20

AR19

AL20

AT21

AR20

AT19

AP19

AT17

AN16

AT15

AN15

AP17

AR17

AP16

AP15

AK17

AK22

AE29

W29

B36

D34

E33

C35

C36

E34

E36

K33

K35

M36

M33

K34

K36

M34

V36

R36

U33

V33

M35

R35

R29

MDA0

MDA1

MDA2

F35

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

L36

MDA14

MDA15

T35

MDA16

T36

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

T33

CKEA0

CKEA1

CKEA2

L34

CKEA3

MVREF5

MVREF4

MVREF3

MVREF2

MVREF1

J29

MVREF0

VCC_DDR

N24

VCC3

VCC3

VCC3

VCC3

VCC25MEM

VCC25MEM

P21

P22

VCC3

VCC3

VCC3

VCC25MEM

VCC25MEM

VCC25MEM

P23

R23

T23

VCC3

VCC3

VCC3

VCC25MEM

VCC25MEM

VCC25MEM

U23

V23

W23

Y23

N23

VCC3

VCC3

VCC3

VCC3

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

AA23

AB23

AC18

VCC3

VCC3

VCC25MEM

VCC25MEM

AC19

AC20

AC21

MVREF_NB

R194

150R1%

C176

0.1u

C296

1u_B

C297

1u_B

Solder side

A

B

Page 9

A

VCC_AGP NBVCC15 VCC3

NB1C

GD0

GD[0:31]13

4 4

3 3

2 2

1 1

Solder

side

GDEVSEL13

AGP8X_DET_NB13

AD_STBF013

AD_STBS013

AD_STBF113

AD_STBS113

SBA[0:7]13

AGPVREF13

NBCLK6625

AGPBZ16

VCCSBY_NB

AGPVREF

GBE013

GBE113

GBE213

GBE313

GFRAME13

GIRDY13

GTRDY13

GSTOP13

GPAR13

RBF13

WBF13

GREQ13

GGNT13

GSERR13

DBIH13

DBIL13

ST013

ST113

ST213

SB_STBF13

SB_STBS13

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

AGPNCOMP0

AGPPCOMP0

C319

0.1u

CB106

0.1u_B

A

GD1

GD2

GD3

GD4

GD5

GD6

GD7

GD8

GD9

GD10

GD11

GD12

GD13

GD14

GD15

GD16

GD17

GD18

GD19

GD20

GD21

GD22

GD23

GD24

GD25

GD26

GD27

GD28

GD29

GD30

GD31

CB12

0.1u

AT2

AP2

AP4

AT5

AR4

AT1

AN5

AT4

AM1

AP3

AR1

AM4

AL2

AN2

AL1

AP1

AJ3

AJ1

AJ4

AK6

AH1

AH2

AK4

AH3

AG5

AJ6

AH5

AG2

AH4

AF3

AG6

AF1

AN4

AL3

AK2

AK5

AL4

AL5

AK3

AK1

AM3

AN3

AE7

AB2

AD4

AD5

AN1

AF4

AG4

AB1

AD6

AE5

AE6

AD3

AD1

AT3

AR3

AG3

AG1

AC1

AC4

AC3

AD2

AE2

AE3

AE4

AE1

AF7

AD7

AB3

AC6

AL14

AT14

N7

W6

GD0

GD1

GD2

GD3

GD4

GD5

GD6

GD7

GD8

GD9

GD10

GD11

GD12

GD13

GD14

GD15

GD16

GD17

GD18

GD19

GD20

GD21

GD22

GD23

GD24

GD25

GD26

GD27

GD28

GD29

GD30

GD31

GCBE0

GCBE1

GCBE2

GCBE3

GFRAME

GIRDY

GTRDY

GDEVSEL

GSTOP

GPAR

RBF

WBF

GREQ

GGNT

GSERR

DBIH/PIPE

DBIL

AGP8XDET

ST0

ST1

ST2

SBSTBF

SBSTBS

ADSTBF0

ADSTBS0

ADSTBF1

ADSTBS1

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

AGPVREF0

AGPVREF1

GCLK

AGPNCOMP

AGPPCOMP

AGPBUSY

VSUS15

TCLK

AR5

VSS

AD14

AD15

AA13

AB13

VCC1

VCC1

VCC1

VCC1

VSS

VSS

VSS

VSS

VSS

AM30

AM32

AM34

AM36

AN8

AC13

VCC1

VSS

AN11

AD13

VCC1

VSS

AR2

AC15

VCC1

VSS

AR14

AC14

VCC1

VSS

AR15

AB14

VCC1

VSS

AR18

AA14

VCC1

VSS

AR21

B

Y14

AR24

B

AC16

W14

VCC1

VCC1

VSS

VSS

VSS

AR27

AR30

AR32

NBVCC15

AC17

VCC2

VSS

AR35

AD16

VCC2

VSS

AT8

AD17

VCC2

VSS

AT11

AD18

VCC2

VSS

A29

VCC25MEM

VSS

VCC_DDR

VDD

AE12

C

W13

Y13

V13

AA2

AA3

AB4

VD0

VD1

RES1

RES2

VCC4

VCC4

VCC4

DACAGND1

GNDPLL1

GNDPLL2

GNDPLL3

N6N1N2

DACAGND2

DACAGND3

T6

P2

P5

R4

RES3

VD10

VD11

VD12

VD13

VD14

VD15

RESERVE/VIIN

RESERVE/VIOUT

VPAR

UPSTB

UPSTB

DNSTB

DNSTB

UPCMD

DNCMD

VLREF

VCOMPP

SUSST

TESTIN NB

RESET

PWROK

DFTIN

AVDD1

AVDD2

AVDD3

AVDD4

HSYNC

VSYNC

RSET

BISTIN

SPD2

SPDCLK2

DISPCLKO

DISPCLKI

TVD00/DVP0D00

TVD01/DVP0D01

TVD02/DVP0D02

TVD03/DVP0D03

TVD04/DVP0D04

TVD05/DVP0D05

TVD06/DVP0D06

TVD07/DVP0D07

TVD08/DVP0D08

TVD09/DVP0D09

TVD10/DVP0D10

TVD11/DVP0D11

TVVS/DVP0VS

TVHS/DVP0HS

TVDE/DVP0DE

VTCLK/DVP0DCLK

TVCLKIN/DVP0DET

SPD1

SPDCLK1

GPO0

GPOUT

DACAVDD1

DACAVDD2

VCCPLL1

VCCPLL2

VCCPLL3

AGND1

AGND2

AGND4

AGND3

M3

E31

L2

M2

VD2

VD3

VD4

VD5

VD6

VD7

VD8

VD9

VBE

INTA

VLAD0

AP8

VLAD1

AR8

VLAD2

AN10

VLAD3

AR11

VLAD4

AR7

VLAD5

AP7

VLAD6

AM11

VLAD7

AP11

VLAD8

AM7

VLAD9

AN6

VLAD10

AP12

VLAD11

AM12

VLAD12

AT6

VLAD13

AR6

VLAD14

AN13

VLAD15

AP13

AP5

AP6

AN7

AT7

AM10

AM9

AN9

AP9

AN12

AP10

AL7

AM6

AN14

C31

AM13

AP14

D32

M4

D31

M1

L1

R1

AR

R3

AB

R2

AG

U4

U3

V7

U2

N5

XIN

V6

T4

T3

N4

N3

W1

W2

AA5

Y3

Y2

AA4

Y5

Y6

Y7

AB5

AB6

AA6

V1

W4

W3

Y4

V2

V4

V3

V5

W5

T5

P4

P3

P6

C

LVREF_NB

LCOMPP

TESTIN_NB

DFTIN_NB

AVDD1

AVDD2

AVDD3

AVDD4

RSET

BISTIN

VCCDAC1

VCCPLL1

R389 X_0R

R390 X_0R

VBE0 16

VPAR 16

UPSTB 16

-UPSTB 16

DNSTB 16

-DNSTB 16

UPCMD 16

DNCMD 16

C175

X_0.1u

VLAD[0:15] 16

-SUSST 15

-PWROK_NB 15

AR 23

AB 23

AG 23

HSYNC 23

VSYNC 23

PIRQ#A 14,17

GUICLK 25

SPD2 23

SPCLK2 23

4.7KX4

7 8

5 6

3 4

1 2

RN103

VCC_AGP

C97

0.1u

VIIN 16

VIOUT 16

NBVCC15

C328

X_0.1u

PCIRST#1

C335

20p_B

C329

0.1u

D

CP19

X_COPPER

X_0.1u

CP16

X_COPPER

X_0.1u

RSET

BISTIN

PCIRST#1 22,26

DFTIN_NB

TESTIN_NB

AGPNCOMP0

AGPPCOMP0

LCOMPP

RGB

D

C103

C131

跨切割

E

NBVCC15

12

FB10

C134

X_1000p

VCC3

12

C130

X_1000p

R122 X_82R1%

R119 X_4.7K

X_220L2_50_0805

VCCPLL1

C140

X_4.7u-0805

FB8

X_220L2_50_0805

VCCDAC1

C137

X_4.7u-0805_B

CP14

X_COPPER

CP13

X_COPPER

12

12

For PM800

12

CP20

X_COPPER

R190 4.7K

R187 4.7K

R153 60.4R1%

R159 60.4R1%

R193 360R1%

VCC_DDR

VCC_AGP

NBVCC15

R203

1.4KR1%_B

LVREF_NB

R202

1KR1%

CP36

X_COPPER

C294

1u_B

12

Solder side

LVREF_NB => +2.5V/4=0.625

Title

Size Document Number Rev

Date: Sheet

Micro-Star

NORTH BRIDGE (PART 3)

MS-7004

E

C108

1000p

C106

1000p

C173

1000p

C326

1000p

VCC3

FB6

X_220L2_50_0805

AVDD4

VCC3

FB5

X_220L2_50_0805

AVDD3

VCC3

FB11

X_220L2_50_0805

AVDD2

VCC3

FB24

X_220L2_50_0805

AVDD1

929Wednesday, February 25, 2004

4.7u-0805

4.7u-0805

4.7u-0805

4.7u-0805

of

C102

C112

C172

C327

10A

Page 10

A

B

C

D

E

4 4

3 3

2 2

NBVCC15

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

AE15

AE14

AE13

M25

M24

M23

M22

M21

M20

M19

M18

M17

M16

M15

M14

M13

M12

U25

U12

T25

T12

R25

R12

P25

P12

N25

N12

AD25

AD12

AC25

AC12

AB25

AB12

AA25

AA12

Y25

Y12

W25

W12

V25

V12

NB1E

VSS

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

R15

VSS

R16

VSS

R17

VSS

R18

VSS

R19

VSS

R20

VSS

R21

VSS

R22

VSS

T15

T16

T17

T18

T19

T20

T21

T22

U15

U16

U17

U18

U19

U20

U21

U22

V15

V16

V17

V18

V19

V20

V21

V22

W15

W16

W17

W18

W19

W20

W21

W22

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y15

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y16

Y17

Y18

Y19

Y20

Y21

Y22

AA15

AA16

AA17

AA18

AA19

AA20

AA21

AA22

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

A11

A14

A17

A23

A26

B3

B5

B8

B20

B32

B35

D2

D5

D11

D14

D17

D23

D26

D29

E8

E20

E32

E35

F17

G2

G5

G8

G11

G16

G23

G26

G27

H20

H30

H32

H35

NBVCC15

CB4 1u-0805

Solder side

0.1uCB11

0.1uCB10

0.1uCB13

VCC_AGP

CB111

10u_B

Decoupling capacitors

VCC3

C287

10u_B

CB108

0.1u_B

NBVCC15

VCCP

C290

10u_B

10u_BCB107

CB117 10u_B

CB115 10u_B

10u_BCB105

10u_BCB104

C291

10u_B

10u_B

C292

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K2K5L32

L35

M29

P29

P32

P35

U32

U35

Y29

Y32

Y35

AB29

AC2

AC5

AC32

AC35

AF2

AF5

AF29

AF32

AF35

AH29

AJ2

AJ5

AJ32

AJ35

AK20

AK27

AK30

AM2

AM5

AM14

AM15

AM16

AM18

AM21

AM24

AM27

1 1

Title

Size Document Number Rev

A

B

C

D

Date: Sheet

Micro-Star

NORTH BRIDGE (PART4)

MS-7004

E

10 29Wednesday, February 25, 2004

10A

of

Page 11

8

7

6

5

4

3

2

1

VCC_DDR

VDD

GND

145

VDD

GND

DIMM1

120

148

168

VDD

VDD

VDD

VDD

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

WP

GND

GND

GND

152

160

176

DIMM-184

MD0

2

MD1

4

MD2

6

MD3

8

MD4

94

MD5

95

MD6

98

MD7

99

MD8

12

MD9

13

MD10

19

MD11

20

MD12

105

MD13

106

MD14

109

MD15

110

MD16

23

MD17

24

MD18

28

MD19

31

MD20

114

MD21

117

MD22

121

MD23

123

MD24

33

MD25

35

MD26

39

MD27

40

MD28

126

MD29

127

MD30

131

MD31

133

MD32

53

MD33

55

MD34

57

MD35

60

MD36

146

MD37

147

MD38

150

MD39

151

MD40

61

MD41

64

MD42

68

MD43

69

MD44

153

MD45

155

MD46

161

MD47

162

MD48

72

MD49 MD50

73

MD50

79

MD51

80

MD52

165

MD53

166

MD54

170

MD55

171

MD56

83

MD57

84

MD58

87

MD59

88

MD60

174

MD61

175

MD62

178

MD63

179

44

45

49

51

134

135

142

144

DDR_WP

90

R259 4.7K

MD[0:63] 8,12

VCC_DDR

5

VCC_DDR

MAB[0:15]8,12

-CS28

-CS38

-SWEB8,12

-SCASB8,12

-SRASB8,12

CKE28,12

CKE38,12

MDCLKB025

MDCLKB#025

MDCLKB125

MDCLKB#125

MDCLKB225

MDCLKB#225

VCC_DDR

VCC_DDR

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB13

MAB14

MAB15

MAB11

MAB12

-DQM0

-DQM1

-DQM2

-DQM3

-DQM4

-DQM5

-DQM6

-DQM7

-SWEB

-SCASB

-SRASB

-DQS0

-DQS1

-DQS2

-DQS3

-DQS4

-DQS5

-DQS6

-DQS7

SMBDATA_ISO

SMBCLK_ISO

MVREF_DIM

130

125

122

141

118

115

167

113

157

158

163

107

119

129

149

159

169

177

140

154

111

137

138

181

182

183

184

101

102

173

103

48

43

41

37

32

29

27

59

52

71

97

63

65

21

16

17

76

75

14

25

36

56

67

78

86

47

91

92

82

10

5

1

9

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

CS0

CS1

NC/CS2

NC/CS3

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0/DNU

CK0/DNU

CK1

CK1

CK2/DNU

CK2/DNU

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VDDID

VDDSPD

NC

NC/RESET

NC

NC

NC

NC/FETEN

VCC_DDR

X_0.1uCB54

0.1uCB40

0.1uCB51

0.1uCB55

0.1uCB35

0.1uCB32

0.1uCB38

X_0.1uCB36

0.1uCB31

X_0.1uCB37

X_0.1uCB50

X_0.1uCB34

4

X_0.1uCB56

X_0.1uCB47

0.1uCB53

X_0.1uCB58

0.1uCB30

0.1uCB57

0.1uCB39

X_0.1uCB49

X_0.1uCB48

0.1uCB46

X_0.1uCB52

0.1uCB33

15223054627796

D D

MAA[0:15]8,12

-CS08

-CS18

-DQM[0:7]8,12

C C

-SWEA8,12

-SCASA8,12

-SRASA8,12

CKE08,12

CKE18,12

MDCLKA025

MDCLKA#025

MDCLKA125

MDCLKA#125

MDCLKA225

MDCLKA#225

B B

-DQS[0:7]8,12

SMBDATA_ISO15,20,25,26

SMBCLK_ISO15,20,25,26

VCC_DDR

A A

R274

75R1%

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA13

MAA14

MAA15

MAA11

MAA12

-CS0

-CS1

-DQM0

-DQM1

-DQM2

-DQM3

-DQM4

-DQM5

-DQM6

-DQM7

-SWEA

-SCASA

-SRASA

-DQS0

-DQS1

-DQS2

-DQS3

-DQS4

-DQS5

-DQS6

-DQS7

MVREF_DIM

VCC_DDR

130

125

122

141

118

115

167

113

157

158

163

107

119

129

149

159

169

177

140

154

111

137

138

181

182

183

184

101

102

173

103

48

43

41

37

32

29

27

59

52

71

97

63

65

21

16

17

76

75

5

14

25

36

56

67

78

86

47

91

92

1

82

9

10

VDDQ

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

CS0

CS1

NC/CS2

NC/CS3

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

WE

CAS

RAS

CKE0

CKE1

CK0/DNU

CK0/DNU

CK1

CK1

CK2/DNU

CK2/DNU

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

SDA

SCL

SA0

SA1

SA2

VREF

VDDID

VDDSPD

NC

NC/RESET

NC

NC

NC

NC/FETEN

104

112

128

136

143

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

GND

GND

GND

GND

GND

3111826344250586674818993

VDDQ

GND

156

VDDQ

GND

164

VDDQ

GND

172

VDDQ

GND

180738467085108

VDD

VDD

VDD

VDDQ

GND

GND

GND

GND

GND

100

116

124

132

139

MVREF_DIM

R275

75R1%

8

C225

0.1u

C214

1u

7

6

VCC_DDR

15223054627796

VDDQ

VDDQ

VDDQ

VDDQ

GND

VDDQ

GND

VDDQ

GND

VDDQ

GND

104

112

VDDQ

VDDQ

GND

GND

3111826344250586674818993

3

128

136

143

156

164

172

180738467085108

VDD

VDD

VDDQ

GND

VDDQ

GND

100

GND

VDD

GND

GND

GND

116

124

132

139

VDDQ

GND

VDDQ

GND

VDDQ

GND

VDDQ

GND

VDDQ

GND

Title

Size Document Number Rev

Date: Sheet

2

DIMM2

120

148

168

VDD

VDD

VDD

VDD

VDD

VDD

2

D0

4

D1

6

D2

8

D3

94

D4

95

D5

98

D6

99

D7

12

D8

13

D9

19

D10

20

D11

105

D12

106

D13

109

D14

110

D15

23

D16

24

D17

28

D18

31

D19

114

D20

117

D21

121

D22

123

D23

33

D24

35

D25

39

D26

40

D27

126

D28

127

D29

131

D30

133

D31

53

D32

55

D33

57

D34

60

D35

146

D36

147

D37

150

D38

151

D39

61

D40

64

D41

68

D42

69

D43

153

D44

155

D45

161

D46

162

D47

72

D48

73

D49

79

D50

80

D51

165

D52

166

D53

170

D54

171

D55

83

D56

84

D57

87

D58

88

D59

174

D60

175

D61

178

D62

179

D63

44

CB0

45

CB1

49

CB2

51

CB3

134

CB4

135

CB5

142

CB6

144

GND

CB7

WP

GND

GND

GND

GND

145

152

160

176

DIMM-184

DDR_WP

90

Micro-Star

DDR MODULES_DIMM1&2

MS-7004

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

11 29Wednesday, February 25, 2004

1

10A

of

Page 12

A

B

C

D

E

VTT_DDR VTT_DDR

MD6

MD[0:63]

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

-DQS0

-DQS1

-DQS2

-DQS3

-DQS4

-DQS5

-DQS6

-DQS7

-DQM0

-DQM1

-DQM2

-DQM3

-DQM4

-DQM5

-DQM6

-DQM7

MD0

MD4

MD1

MD2

MD6

MD7

MD3

MD8

MD12

MD9

MD13

MD14

MD15

MD10

MD11

MD18

MD22

MD23

MD19

MD20

MD16

MD17

MD21

MD24

MD28

MD25

MD29

MD26

MD30

MD27

MD31

R263 X_0R

R261 X_0R

R265 X_0R

R255 X_0R

R270 X_0R

R269 X_0R

R267 X_0R

R273 X_0R

R262 X_0R

R256 X_0R

R266 X_0R

R254 X_0R

R272 X_0R

R271 X_0R

R268 X_0R

R264 X_0R

RN58

X_0X4

RN57

X_0X4

RN56

X_0X4

RN55

X_0X4

RN54

X_0X4

RN53

X_0X4

RN51

X_0X4

RN52

X_0X4

MD0

RN45

4 4

3 3

MD4

X_0X4

MD5 MD5

MD1

MD2

RN49

MD6

X_0X4

MD7

MD3

MD8

MD12

RN48

X_0X4

MD9

MD13

MD14

MD15

MD10

MD11

MD18

RN50

MD22

MD23

X_0X4

MD19

MD20

RN47

MD16

X_0X4

MD17

MD21

MD24

RN44

MD28

X_0X4

MD25

MD29

RN46

MD30

X_0X4

MD27

MD31

R257 X_0R

R258 X_0R

R260 X_0R

R252 X_0R

-DQS[0:7]8,11 -DQS[0:7] 8,11

-DQM[0:7]8,11

2 2

MD[0:63]

MD32

MD36

MD33

MD37

MD34 MD34

MD38

MD39

MD35

MD40

MD44

MD45

MD41

MD42 MD42

MD46

MD43

MD47

MD48

MD49

MD52

MD53

MD54

MD50

MD55

MD51

MD62

MD58

MD63

MD59

MD60

MD56

MD61

MD57

-DQS0

-DQS1

-DQS2

-DQS3

-DQS4

-DQS5

-DQS6

-DQS7

-DQM0

-DQM1

-DQM2

-DQM3

-DQM4

-DQM5

-DQM6

-DQM7

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

MD[0:63] 8,11MD[0:63]8,11

MD32

MD36

MD33

MD37

MD38

MD39

MD35

MD40

MD44

MD45

MD41

MD46

MD43

MD47

MD48

MD49

MD52

MD53

MD54

MD50

MD55

MD51

MD62

MD58

MD63

MD59

MD60MD26

MD56

MD61

MD57

-DQM[0:7] 8,11

VTT_DDR

0.1uCB71

VTT_DDR

X_0.1uCB74

X_0.1uCB79

X_0.1uCB65

X_0.1uCB89

X_0.1uCB98

0.1uCB67

1 1

A

VTT_DDRVTT_DDR

X_0.1uCB75

VTT_DDR

0.1uCB76

X_0.1uCB92

X_0.1uCB81

0.1uCB63

0.1uCB94

0.1uCB82

X_0.1uCB62

0.1uCB96

X_0.1uCB68

X_0.1uCB95

0.1uCB93

VTT_DDR

X_0.1uCB77

0.1uCB97

X_0.1uCB83

0.1uCB64 0.1uCB88

X_0.1uCB87

0.1uCB69

B

0.1uCB90

0.1uCB80

0.1uCB84

0.1uCB86

X_0.1uCB91

0.1uCB70

X_0.1uCB72

0.1uCB73

0.1uCB78

0.1uCB61

X_0.1uCB85

0.1uCB66

0.1uCB99

-SCASB8,11

-CS28

C

MD2

-DQM0

-DQS0

MD0

MD4

MD5

MD1

MD7

MD3

MD8

MD12

MD9

MD13

-DQS1

MAA14

MD17

MD21

-DQS2

MAA7

MAB8

MAA8

MD23

CKE2

MD20

MAB14

MD16

MAB13

MAA13

-DQM2

MAB9

MD29

-DQS3

MAB4

-DQM3

MAB2

MAA2

MAB1

MAA1

MAA4

MAA3

MAB3

MD26

-DQS4

-DQM4

MD34

MD38

MAB12

MAA12

MD43

MD47

MD48

MD49

MD40

MD44

MAB11

MAA11

MD39

MD35

MD52

MD53

MAB15

MAA15

-DQM6

-DQS6

MD54

MD50

MD45

MD41

7 8

5 6

3 4

1 2

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN95

56X4-0402

RN96

56X4-0402

RN94

56X4-0402

RN93

56X4-0402

RN89

56X4-0402

RN86

56X4-0402

RN90

56X4-0402

RN88

56X4-0402

RN83

56X4-0402

RN80

56X4-0402

RN82

56X4-0402

RN77

56X4-0402

RN78

56X4-0402

RN71

56X4-0402

RN64

56X4-0402

RN76

56X4-0402

RN70

56X4-0402

RN69

56X4-0402

RN74

56X4-0402

-SCASA8,11

-SRASB8,11

-SRASA8,11

-SWEB8,11

-SWEA8,11

D

MD62

1 2

MD58

3 4

MD63

5 6

MD59

7 8

MD61

1 2

MD57

3 4

-DQM7

5 6

-DQS7

7 8

MD55

1 2

MD51

3 4

MD60

5 6

MD56

7 8

1 2

-DQM1

MD14

MD15

MD10

-DQS5

-DQM5

MD42

MD46

MAB0

MAA0

MAA10

MAB10

MAA6

MD24

MD28

MD25

MD32

MD36

MD33

MD37

CKE3

CKE1

MD11

CKE0

MD30

MD27

MD31

MD19

MAB5

MAA5

MAB6

MAA9

MD18

MAB7

MD22

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

-CS08

-CS18

-CS38

RN66

56X4-0402

RN67

56X4-0402

RN68

56X4-0402

RN73

56X4-0402

RN92

56X4-0402

RN72

56X4-0402

RN79

56X4-0402

RN84

56X4-0402

RN65

56X4-0402

RN91

56X4-0402

RN81

56X4-0402

RN85

56X4-0402

RN87

56X4-0402

RN75

56X4-0402

MAA[0:15]8,11

MAB[0:15]8,11

CKE[0:3]8,11

Title

Size Document Number Rev

Date: Sheet

Micro-Star

DDR TERMINALS

MS-7004

12 29Wednesday, February 25, 2004

10A

E

of

Page 13

A

B

C

D

E

SBA[0:7]9

GD[0:31]9

4 4

PIRQ#B14,17

AGPCLK25

GREQ9

SB_STBF9

3 3

AD_STBF19

GBE29

GIRDY9

2 2

GDEVSEL9

GSERR9

GBE19

AD_STBF09

1 1

SBA[0:7]

GD[0:31]

VCC_AGP

VCC3

VCC5

OVRCNT#

PIRQ#B

GREQ

ST09

ST29

RBF9

DBIL9

RBF

DBIL

SBA0

SBA2

SB_STBF

SBA4

SBA6

VCC3_SB

GD31

GD29

GD27

GD25

AD_STBF1

GD23

GD21

GD19

GD17

GBE2

GIRDY

GDEVSEL

GPERR

GSERR

GBE1

GD14 GPERR

GD12

GD10

GD8

AD_STBF0

GD7

GD5

GD3

GD1

VREF_CG

C183

1u

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

B1

B2

B3

B4

B5

B6

B7

B8

B9

+3.3V ==> 6A

+1.5VAGP ==>1A

+5V===>2A

+12V==>1A

+3.3AUX==>750mA

AGP1

OVRCNT#

+5V

+5V

USB+

GND

INTB#

CLK

REQ

VCC3.3

ST0

ST2

RBF

GND

DBI_LO

SBA0#

VCC3.3

SBA2#

SB_STBF

GND

SBA4#

SBA6#

RESERVED

GND

VCC3_AUX

AD31

AD29

VCC3.3

AD27

AD25

GND

AD_STBF1

AD23

VDDQ1.5V

AD21

AD19

GND

AD17

C#/BE2

VDDQ1.5V

IRDY

KEY

KEY

KEY

KEY

DEVEL

VDDQ1.5V

PERR

GND

SERR

C#/BE1

VDDQ1.5V

AD14

AD12

GND

AD10

AD8

VDDQ1.5V

AD_STBF0

AD7

GND

AD5

AD3

VDDQ1.5V

AD1

VREF_CG

GC_AGP8X_DET

MB_AGP8X_DET

AGP3.0 Ver 0.95

SLOT-AGP1.5LATCH_red

+12V

TYPEDET#

USB-

GND

INTA#

RST#

GNT

VCC3.3

ST1

DBI_HI

GND

WBF

SBA1#

VCC3.3

SBA3#

SB_STBS

GND

SBA5#

SBA7#

RESERVED

GND

RESERVED

VCC3.3VCC3.3

AD30

AD28

VCC3.3

AD26

AD24

GND

AD_STBS1

C#/BE3

VDDQ1.5V

AD22

AD20

GND

AD18

AD16

VDDQ1.5V

FRAME

KEY

KEY

KEY

KEY

TRDY

STOP

PME#

GND

PAR

AD15

VDDQ1.5V

AD13

AD11

GND

AD9

C#/BE0

VDDQ1.5V

AD_STBS0

AD6

GND

AD4

AD2

VDDQ1.5V

AD0

VREF_GC

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25B25

A26

A27

A28

A29

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

+12V

VCC_AGP

VCC3

GC_AGP8X_DET

PIRQ#A

PCIRST#

GGNT

DBIH

WBF

SBA1

SBA3

SB_STBS

SBA5

SBA7

GD30

GD28

GD26

GD24

AD_STBS1

GBE3

GD22

GD20

GD18

GD16

GFRAME

GTRDY

GSTOP

GPAR

GD15

GD13

GD11

GD9

GBE0

AD_STBS0

GD6

GD4

GD2

GD0