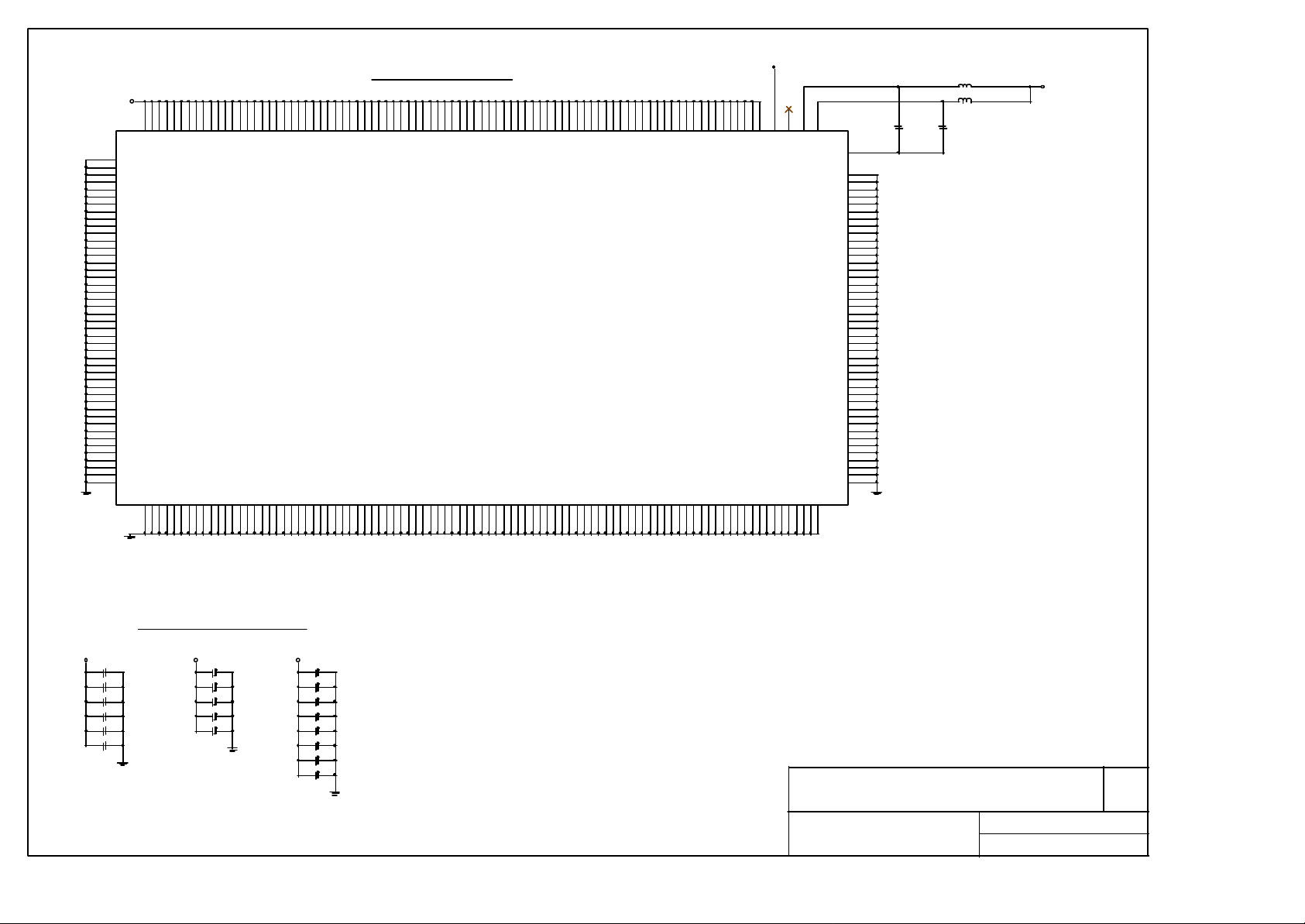

Cover Sheet

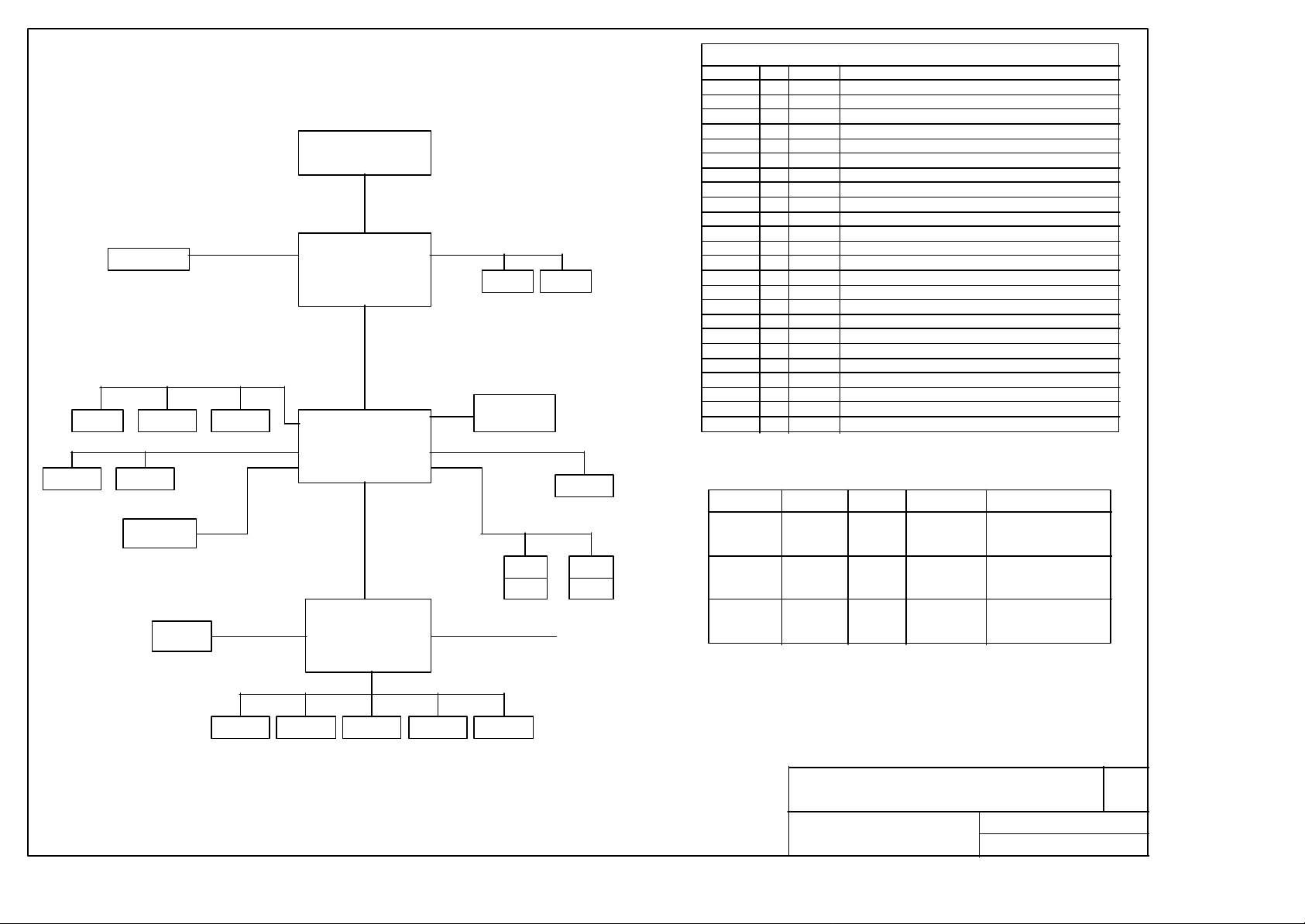

Block Diagram

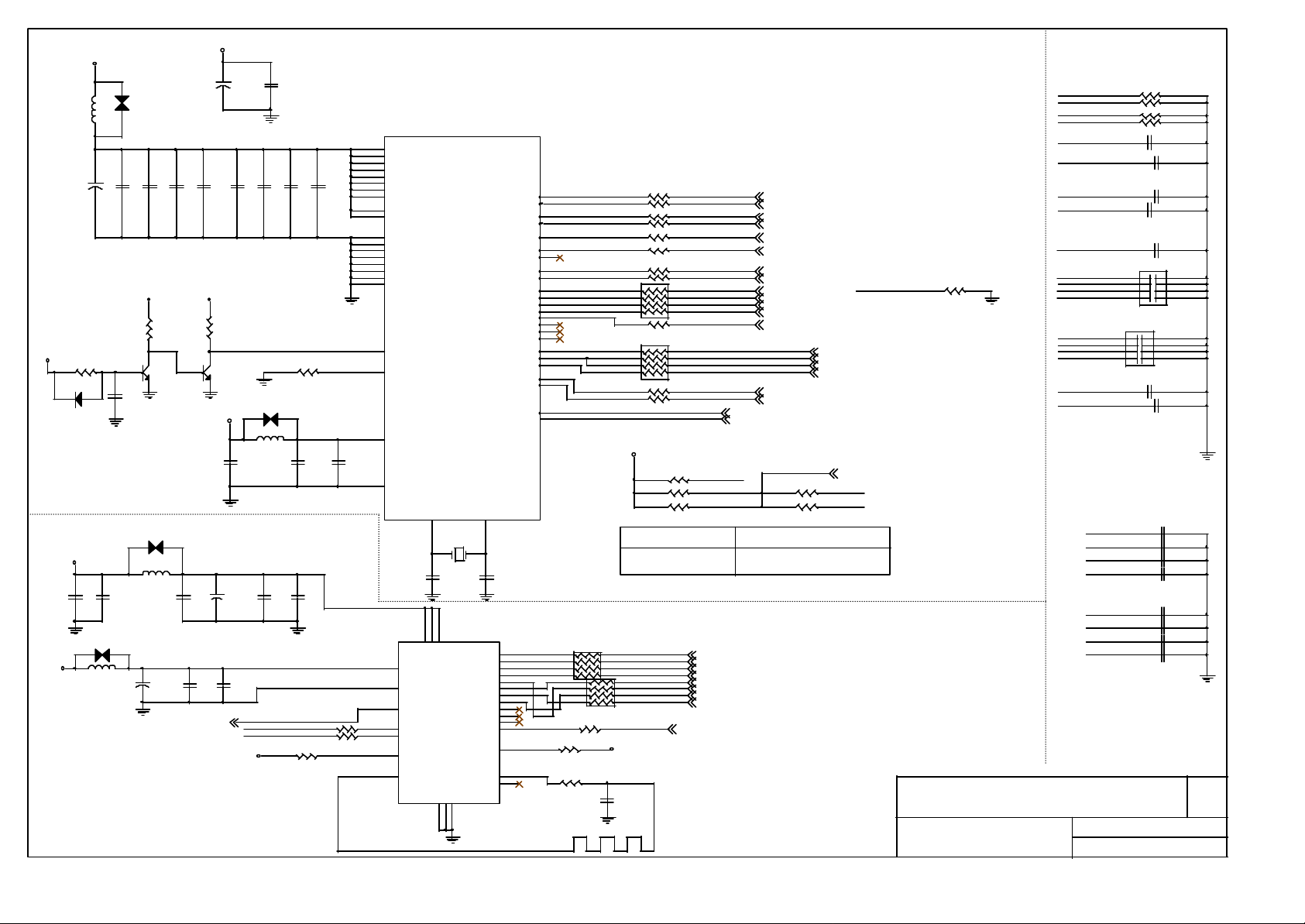

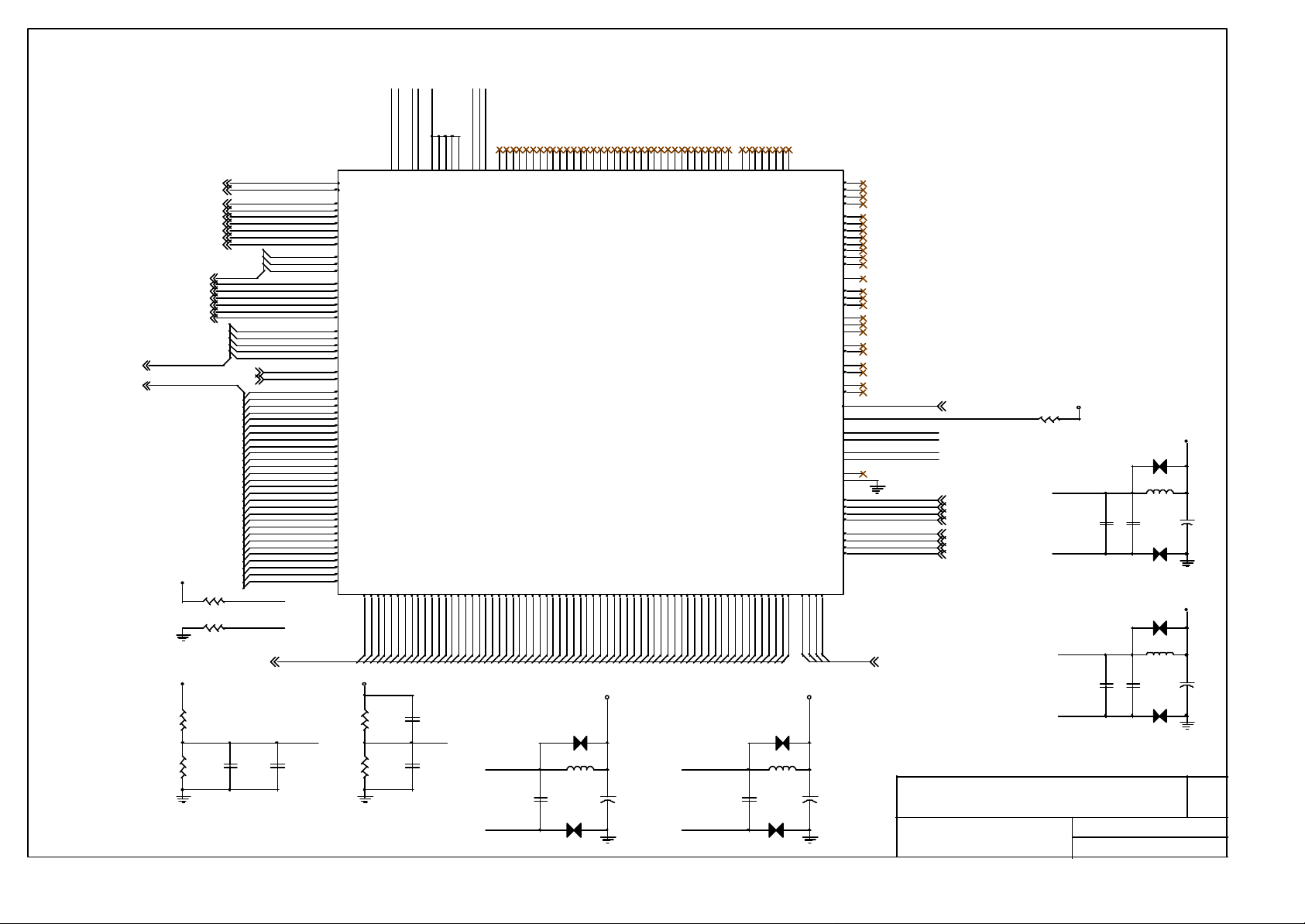

MAIN CLOCK GEN &

DDR CLOCK BUFFER

1

2

3

MS6721

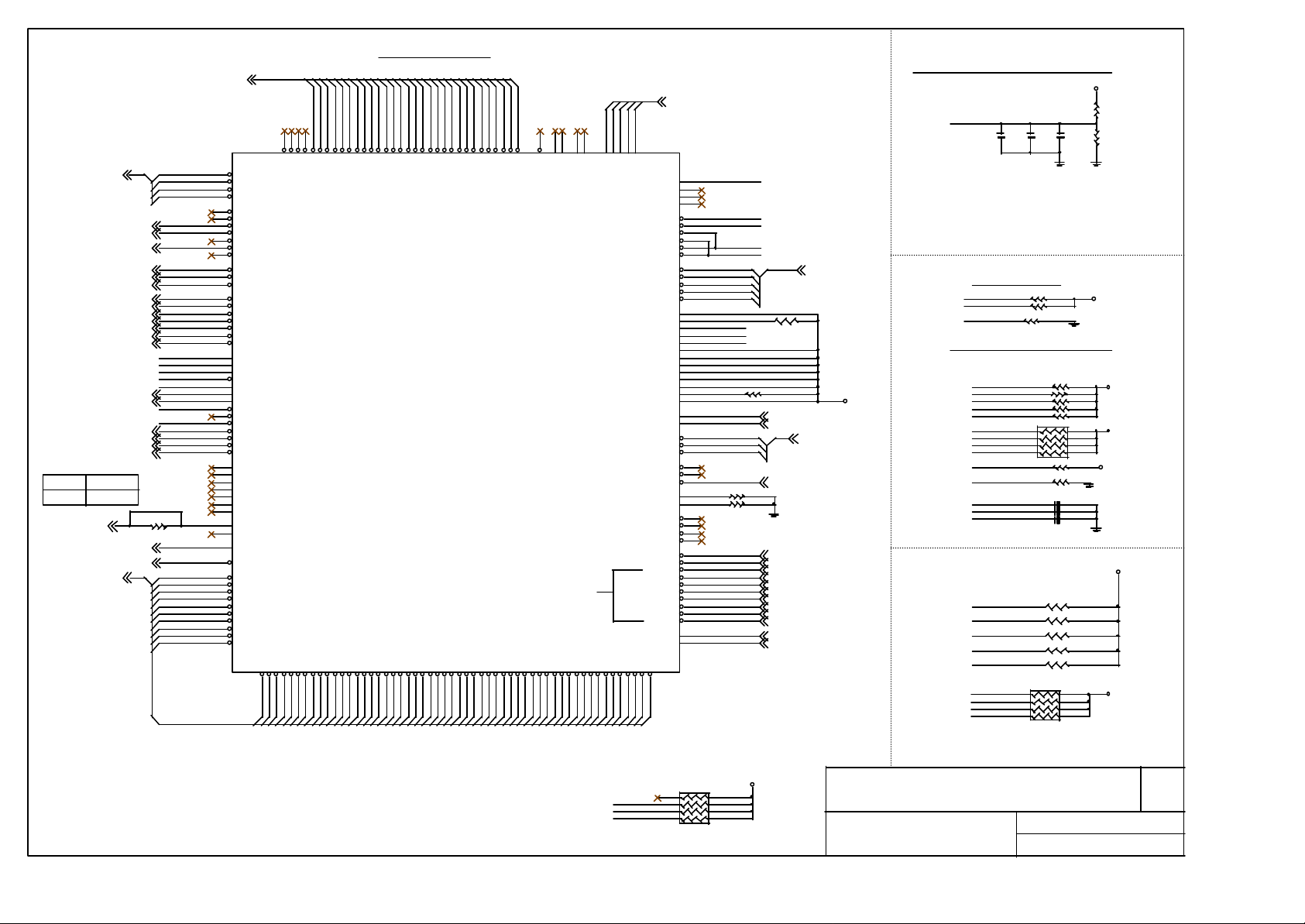

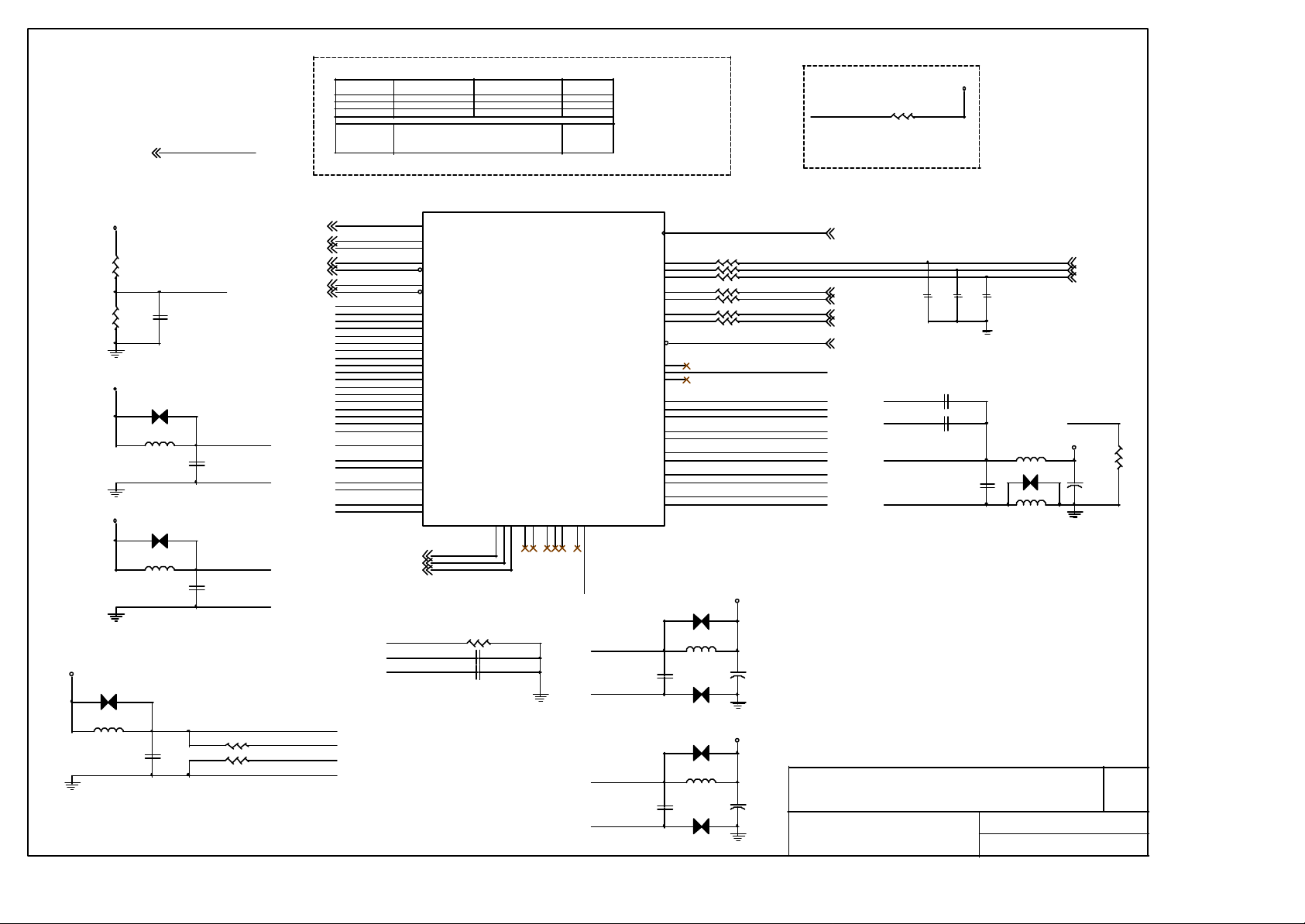

SIS 650GL CHIPSET

Willamette/Northwood 478pin mPGA-B Processor Schematics

VERSION:0A

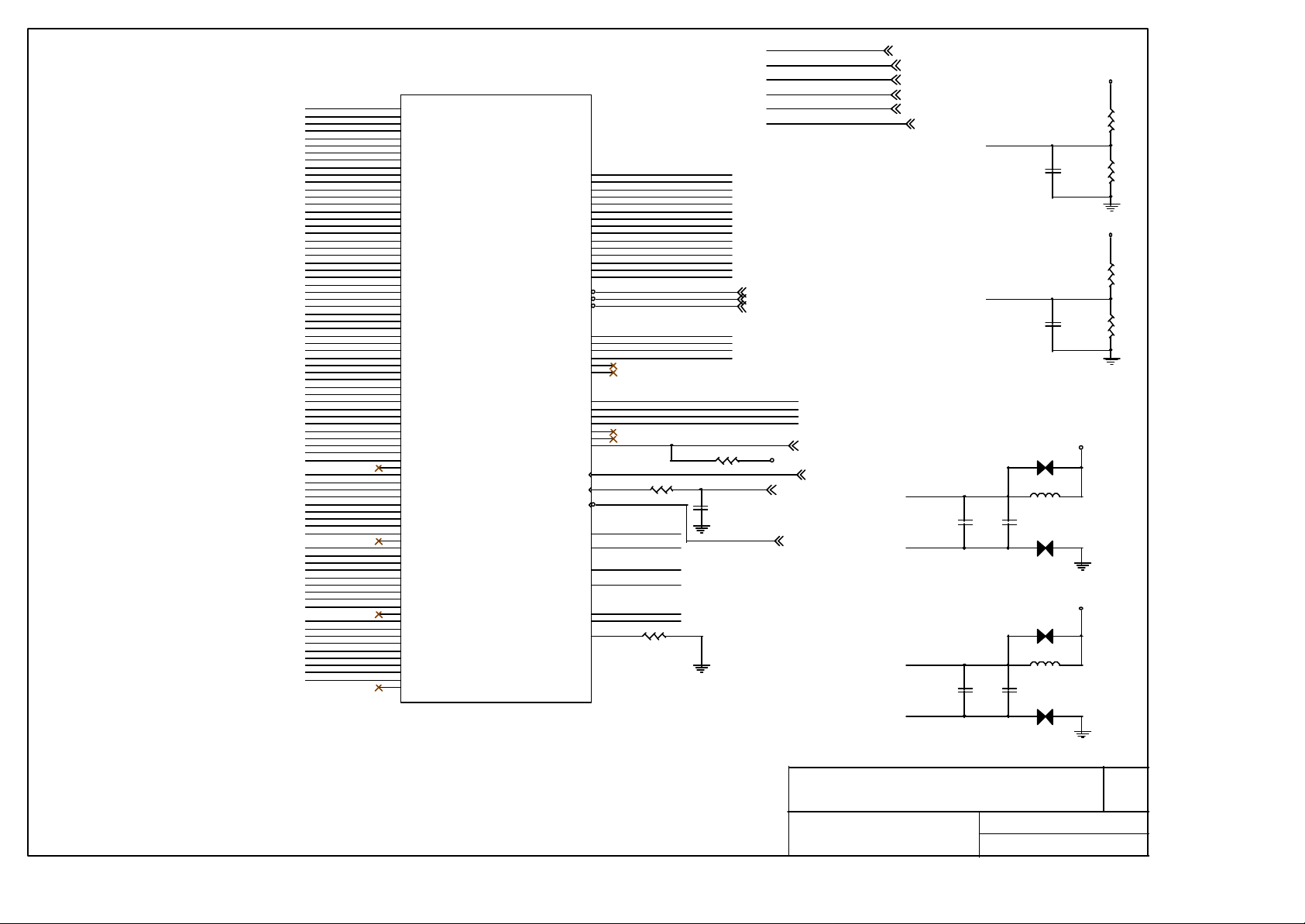

mPGA478-B INTEL CPU Sockets

SIS 650GL NORTH BRIDGE

DIMM SLOT

AUDIO CODEC

SIS 962L SOUTH BRIDGE

LAN CONTROLLER (RTL8201BL MII PHY)

PCI SLOTS ( PCI 1-3 )

KB/MS Connector & FAN Connector

IDE Connectors

USB Connector

ATX POWER Connector & VGA Connector

LPC I/O(W83697HF) & BIOS

PARALLEL & SERIAL PORTS

VRM 9.0 (INTERSIL HIP6302)

MS-5 ACPI CONTROLLER

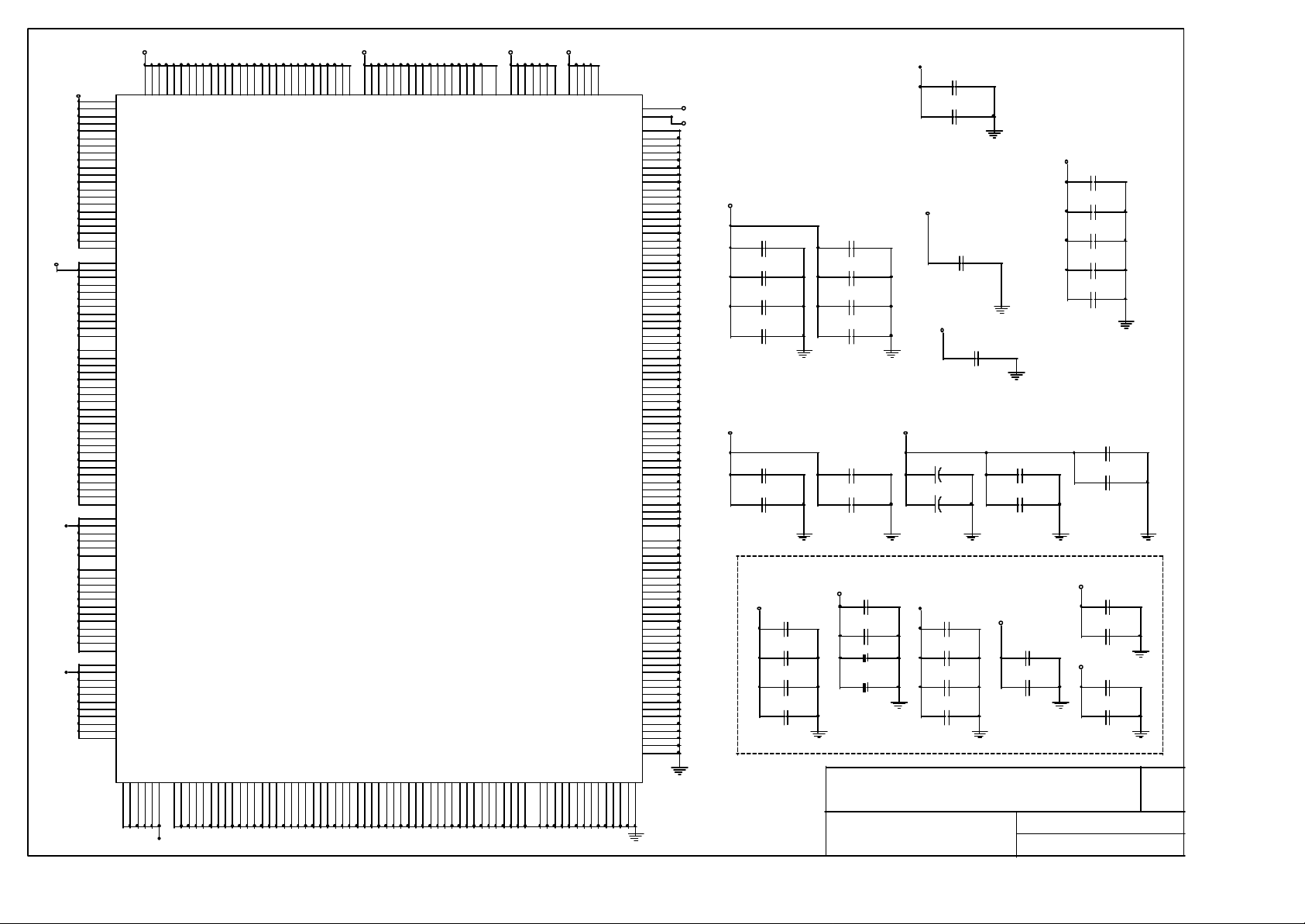

Decoupling Capacitor

4 - 5

6 - 9

10

11

12 - 14

15

16

17

18

19

20

21

22

23

24

25

CPU:

Willamette/Northwood mPGA-478B Processor

System Brookdale Chipset:

SIS 650GL (North Bridge) + 962L (South Bridge)

On Board Chipset:

LPC Super I/O -- W83697HF

RTL8201BL MII PHY

Expansion Slots:

PCI2.2 SLOT* 3

AC'97 Codec :

Realtek ALC101

FRONT PANEL

MANUAL PARTS

26

27

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

BLOCK DIAGRAM

MS-6721

Last Revision Date:

Sheet

Rev

0A

Thursday, September 26, 2002

1 27

of

VGA CON.

PCI slot 3 PCI slot 2 PCI slot 1

IDE 2 IDE 1

KEYBOARD

/MOUSE

LEGACY

ROM

System Block Diagram

VGA CONNECTOR

PS/2

SOCKET 478

Host Bus

SIS 650GL

Hyper ZIP

SIS 962L

LPC BUS

LPC SUPER I/O

SDRAM DIMM

AC'97

AUDIO CODEC

H/W MONITOR

USB 0

USB 1

GPIO_0

GPIO_1

GPIO_2

GPIO_3 EXTSMI#

GPIO_4 Pull-Down

GPIO_5

GPIO_6

GPIO_7 AUX

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12 I/O

GPIO_13

DIMM2DIMM1

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

GPIO_22

GPIO_23

GPIO_24 I

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

MAIN

I/O

AUX

I/O

AUX

I/O

AUX

I/O

I/O

AUX

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I/O

AUX

I

AUX EESK

I

AUX

I

AUX

AUX

PCI Routing

Lan

USB 3

USB 4

DEVICES

PCI SLOT 2

PCI SLOT 3

PCI SLOT 1

INT#

INT#B

INT#C

INT#D

INT#A

INT#C

INT#D

INT#A

INT#B

INT#D

INT#A

INT#B

INT#C

Flash Rom protection H: Disable, L: Enable

Pull-Down

THERM#

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

RESERVED

Pull-Down(for SIS962L)

Pull-Up

RESERVED

Pull-Down

KBDAT

KBCLK

MSDAT

MSCLK

SMBCLK

SMBDAT

EEDI

DDEO

EECS

IDSEL

AD17

AD18

AD19

REQ#/GNT#

PREQ#0

PGNT#0

PREQ#1

PGNT#1

PREQ#2

PGNT#2

CLOCK

PCICLK0

PCICLK1

PCICLK2

GPIO Table on SIS962L

FLOPPYPRINTERCOMGAME/MIDIGPIOS

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

BLOCK DIAGRAM

MS-6721

Last Revision Date:

Friday, October 04, 2002

Sheet

2 27

of

Rev

0A

VCC3

AC

CB47

X_0.01u

CP35

X_COPPER

CB115

0.1u

VCC3 VCC3

C130

10p

CP10 X_COPPER

L20

X_80_0805

L42

X_80_0805

C140

4.7U/0805

NPN-MBT3904LT1-S-SOT23

VCCP

R154

10K

D13

X_1N4148-S-LL34-75V

VCC3

CB48

0.1u

CP12 X_COPPER

VCC3

L21 X_80_0805 CB52

CB98

0.1u

R155

10K

Q21

C67

X_4.7U/0805

4.7U/0805

CB107

0.1u

CB42

0.1u

0.1u

FWDSDCLKO7

C124

VCC3

CB99

CB102

0.1u

0.1u

R157

10K

Q20

NPN-MBT3904LT1-S-SOT23

CP37 X_COPPER

VCC3

L43

X_80_0805

CB2

0.1u

CBVDD

C63

X_4.7U/0805

CB51

X_0.01u

FWDSDCLKO

VCC3

CB96

0.1u

CB103

CB100

0.1u

R170

CB46

0.1u

SMBCLK

SMBDAT

Hi:ID=6D

Lo:ID=2D(internal pull-down 150K)

CB116

0.1u

0.1u

475

CB104

0.1u

CB50

0.1u

R75 10

R70 10

R71 X_2.7K

CB101

102P

CBVDD

Main Clock Generator

U13

REALTEK/RTM360-645R

1

VDDREF

11

VDDZ

13

VDDPCI

19

VDDPCI

28

VDD48

29

VDDAGP

42

VDDCPU

48

VDDSD

12

PCI_STOP#

45

CPU_STOP#

5

VSSREF

8

VSSZ

18

VSSPCI

24

VSSPCI

25

VSS48

32

VSSAGP

41

VSSCPU

46

VSSSD

33

PD#/VTT_PWRGD

38

IREF

36

VDDA

37

VSSA

10

11

8

7

22

21

20

RTM680-627

U7

3

VDD_CORE

GND_CORE

BUF_IN

SCLK

SDATA

SEL D6/D2

FB_IN

XIN

6

14M-16pf-HC49S-D

C155

16p

236

12

VDDCLK_IN

VDD

VDD

15

Y2

SDR00/DDR0C

SDR01/DDR0T

SDR02/DDR1T

SDR03/DDR1C

SDR04/DDR2T

SDR05/DDR2C

SDR06/DDR3C

SDR07/DDR3T

SDR08/DDR4T

SDR09/DDR4C

SDR10/DDR5T

SDR11/DDR5C

SEL SDR/DDR

FB_OUT

FB_OUT2

VDD

GND

28

PCICLK_F0/FS3

PCICLK_F1/FS4

24_48M/MULTISEL

XOUT

7

C150

16p

1

2

4

5

13

14

16

17

24

25

26

27

9

19

18

40

CPUCLK0

39

CPUCLK#0

44

CPUCLK1

43

CPUCLK#1

47

SDCLK

31

AGPCLK0

30

AGPCLK1

9

ZCLK0

10

ZCLK1

FS3 96XPCLK

14

FS4 SIOPCLK

15

16

PCICLK0

17

PCICLK1

20

PCICLK2

21

PCICLK3

22

PCICLK4

23

PCICLK5

2

SCLK

FS0

FS1

3

FS2

4

27

48M

26

35

34

REF0/FS0

REF1/FS1

REF2/FS2

SDATA

Clock Buffer (DDR)

7 8

5 6

3 4

1 2

R69 10

R76 2.7K

Hi:SDR

Lo:DDR(internal pull-down 150K)

R73 22

RN15 10

7 8

5 6

3 4

1 2

RN11 10

RN26 8P4R-33

RN27 8P4R-33

VCC3

C52

10p

R186

R182

R184 33

R185

R183

R187 33

R218

R219 22

7 8

5 6

3 4

1 2

R217

7 8

5 6

3 4

1 2

R188

R189

VCC3

R222 4.7K

R227

R226

FS4 FS3 FS2 FS1 FS0 CPU SDRAM ZCLK AGP PCI

0 0 0 0

0 01111

SDCLK0

SDCLK1

SDCLK2

SDCLK3

SDCLK5

SDCLK4

SDCLK7

SDCLK6

SDCLKI

FB_OUT

CPUCLK1

33

CPUCLK-1

33

CPUCLK0

CPUCLK-0

33

SDCLK

22

AGPCLK0

ZCLK0

22

ZCLK1

PCICLK1

PCICLK2

33

UCLK48M

22

SIO48MMULTISEL

22

SMBCLK

SMBDAT

SMBCLK 10,13,24

SMBDAT 10,13,24

F0~F4 internal Pull-Down 120K

FS0

2.7K

2.7K

100 100

SDCLK0 10

SDCLK1 10

SDCLK2 10

SDCLK3 10

SDCLK5 10

SDCLK4 10

SDCLK7 10

SDCLK6 10

SDCLKI 7

CPUCLK1 6

CPUCLK-1 6

CPUCLK0 4

CPUCLK-0 4

SDCLK 7

AGPCLK0 6

ZCLK0 8

ZCLK1 12

96XPCLK 12

SIOPCLK 21

PCICLK1 16

PCICLK2 16

PCICLK3 16

REFCLK0

REFCLK1

APICCLK

REFCLK2

UCLK48M 14

SIO48M 21

R221

R228

100133

REFCLK0 8

REFCLK1 13

APICCLK 13

REFCLK2 11

BSEL0 4

FS2

10K

FS4

10K

6666666633

MULTISEL internal Pull-Up 120K

MULTISEL

33

R180 X_4.7K

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

CLOCK GEN & DDR CLOCK BUFFER

CPUCLK0

CPUCLK-0

CPUCLK1

CPUCLK-1

SDCLK

AGPCLK0

ZCLK0

ZCLK1

PCICLK3

PCICLK2

PCICLK1

SIOPCLK

96XPCLK

REFCLK2

APICCLK

REFCLK1

REFCLK0

UCLK48M

SIO48M

SDCLK0

SDCLK1

SDCLK2

SDCLK3

SDCLK4

SDCLK5

SDCLK6

SDCLK7

MS-6721

Last Revision Date:

Sheet

R171

R172

R173 49.9

R174

1 2

3 4

5 6

7 8

C144 X_10p

C141 X_10p

C172 X_10p

C173 X_10p

C158 X_10p

CN9

1 2

3 4

5 6

7 8

X_8P4C_10p

CN10

8P4C_10p

C142 10p

C143 10p

C68 X_10p

C69 X_10p

C70 X_10p

C71 X_10p

C60 X_10p

C61 X_10p

C53 X_10p

C55 X_10p

49.9

49.9

49.9

Rev

Thursday, October 03, 2002

3 27

of

0A

Trace : 10

mil width

10mil

space

BSEL0

0

1

HDBI#[0..3]6

BSEL03

HD#[0..63]6

HDEFER#6

CPU_TMPA21

VTIN_GND21

CPUSLP#13

FSB

100 MHz

133 MHz

CPURST#6

FERR#13

STPCLK#13

HINIT#13

HDBSY#6

HDRDY#6

HTRDY#6

HADS#6

HLOCK#6

HBNR#6

HITM#6

HBPRI#6

IGNNE#13

A20M#13

CPU_GD6

HIT#6

SMI#13

R220 X_0

HDBI#0

HDBI#1

HDBI#2

HDBI#3

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

CPU_TMPA

THERMTRIP#

PROCHOT#

IGNNE#

SMI#

A20M#

CPUSLP#

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

HA#[3..31]6

G25

AC3

AA3

AB2

AF26

AB26

AD2

AD3

AE21

AF24

AF25

AD6

AD5

AB23

AB25

AA24

AA22

AA25

W25

W26

E21

P26

V21

V6

B6

Y4

W5

H5

H2

J6

G1

G4

G2

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A22

A7

Y21

Y24

Y23

Y26

V24

U4A

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

V22

HD#53

CPU SIGNAL BLOCK

HA#31

HA#30

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

U21

V25

HD#52

HD#51

D45#

U23

U24

U26

T23

T22

T25

HD#50

HD#49

HD#48

HD#45

HD#47

HD#46

HA#23

HA#24

HA#28

HA#27

HA#26

HA#29

HA#25

A29#

A28#

A27#

A26#

A25#

A24#

A23#

D44#

D43#

D42#

D41#

D40#

D39#

T26

HD#44

D38#

R24

R25

P24

R21

N25

N26

HD#39

HD#40

HD#38

HD#43

HD#41

HD#42

M26

HA#16

HA#17

HA#18

HA#21

HA#19

HA#20

HA#22

A22#

A21#

A20#

A19#

A18#

A17#

A16#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

N23

M24

P21

N22

M23

H25

HD#32

HD#34

HD#33

HD#31

HD#35

HD#37

HD#36

HA#9

HA#8

HA#13

HA#15

HA#10

HA#12

HA#14

HA#11

A9#

A15#

A14#

A13#

A12#

A11#

A10#

D30#

D29#

D28#

D27#

D26#

D25#

K23

HD#30

D24#

J24

L22

M21

H24

G26

L21

D26

HD#24

HD#25

HD#27

HD#28

HD#26

HD#29

HD#23

A8#

D23#

F26

CPU GTL REFERNCE VOLTAGE BLOCK

VCCP

VID[0..4] 23

HA#7

HA#3

HA#5

HA#4

HA#6

AE25A5A4

AD26

AC26

A7#

A6#

A5#

A4#

A3#

DBR#

ITP_CLK1

ITP_CLK0

VCC_SENSE

VSS_SENSE

Differential

Host Data

Strobes

D22#

D21#

D20#

D19#

D18#

D17#

D16#

D15#

D14#

D13#

D12#

D11#

D10#

E25

F24

F23

G23

E24

H22

D25

HD#17

HD#19

HD#15

HD#18

HD#21

HD#20

HD#22

HD#16

D9#

J21

D23

C26

H21

G22

B25

HD#9

HD#10

HD#14

HD#13

HD#12

HD#11

VID0

VID1

VID2

VID4

VID3

AE1

AE2

AE3

AE4

AE5

VID4#

VID3#

VID2#

VID1#

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D8#

D7#

D6#

D5#

D4#

D3#

D2#

D1#

C24

C23

B24

HD#6

HD#7

HD#8

D0#

D22

C21

A25

A23

B22

B21

PGA-S478-A10

HD#0

HD#2

HD#1

HD#4

HD#5

HD#3

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

GTLREF1

BPM#5

BPM#4

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

TESTHI11

TESTHI10

TESTHI9

TESTHI8

RS#2

RS#1

RS#0

R52 49.9

R55 49.9

R51 56

R32 1K

HREQ#[0..4] 6

CPUCLK-0 3

CPUCLK0 3

RS#[0..2] 6

HBR#0 6

* Short trace

HADSTB#1 6

HADSTB#0 6

HDSTBP#3 6

HDSTBP#2 6

HDSTBP#1 6

HDSTBP#0 6

HDSTBN#3 6

HDSTBN#2 6

HDSTBN#1 6

HDSTBN#0 6

NMI 13

INTR 13

VCCP

Length < 1.5inch.

GTLREF1

2/3*Vccp

C37 R39

C32

220p

220p

R38

49.9RST

C27

1u

100RST

Every pin put one 220pF cap near it.

Trace Width 15mils, Space 15mils.

Keep the voltage dividers within 1.5 inches of the

first GTLREF Pin

CPU ITP BLOCK

ITP_TMS

ITP_TDO

ITP_TCK

R41 39

R43 75

R49 27

VCCP

CPU STRAPPING RESISTORS

CLOSED TO SOCKET478

PROCHOT#

CPU_GD

HBR#0

CPURST#

THERMTRIP#

BPM#4

BPM#5

BPM#1

BPM#0

ITP_TDI

ITP_TRST#

CPU_GD

CPURST#

CPUSLP#

CLOSED TO SOCKET478

STPCLK#

CPUSLP#

SMI#

HINIT#

FERR#

IGNNE#

NMI

INTR

A20M#

R44 62

R29 62

R68 49.9

R35 49.9

R66 62

RN3 8P4R-56

7 8

5 6

3 4

1 2

R67 150

R45 680

X_102pC22

X_102pC24

X_0.022uC23

R42 X_56

R31 X_56

R33 X_56

R46 56

R40 X_62

RN7

7 8

5 6

3 4

1 2

X_8P4R-56

VCCP

VCCP

VCCP

VCCP

VCCP

TESTHI9

TESTHI8

TESTHI10

RN4

7 8

5 6

3 4

1 2

8P4R-56

VCCP

Title

Micro Star Restricted Secret

mPGA478-B Intel CPU Socket Part 1

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-6721

Last Revision Date:

Sheet

Rev

Thursday, October 03, 2002

4 27

of

0A

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

VCC

VSS

F13

VCC

VSS

G21G6G24

F15

F17

VCC

VCC

VSS

VSS

G3H1H23

VCC

VSS

F19

VCC

VSS

VCC_VID

F9

VCC

VSS

VSS

AF4

VCC-VID

VSS

VSS

H26H4J2

AE23

AF3

VCC-IOPLL

VCC-VIDPRG

VSS

VSS

VSS

J22

J25J5K21

AD20

VCCA

VSSA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PGA-S478-A10

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

C19

10u-1206

L9 4.7u-10%

L10 4.7u-10%

C20

10u-1206

VCCP

CPU VOLTAGE BLOCK

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

E12

E14

E16

E18

VCC

VSS

E20E8F11

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

F12

VSS

F14

F16

F18F2F22

F25F5F8

U4B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VCC

VSS

VSS

VSS

VSS

VSS

VSS

E19

E23

E7E9F10

E4

E26

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B23

B20

B26B4B8

C11

C13

C15

C17C2C19

C22

C25C5C7C9D12

D14

D16

D18

D20

D21D3D24D6D8E1E11

VSS

E13

E15

E17

CPU DECOUPLING CAPACITORS

VCCP VCCPVCCP

CB41

10u-0805

CB5

10u-0805

CB40

10u-0805

CB39

10u-0805

CB4

10u-0805

CB38

10u-0805

PLACE CAPS WITHIN CPU CAVITY

CB8

10u-1206

CB18

10u-1206

CB7

10u-1206

CB16

10u-1206

CB6

10u-1206

CB21

10u-1206

CB20

10u-1206

CB19

10u-1206

CB30

10u-1206

CB29

10u-1206

CB28

10u-1206

CB27

10u-1206

CB22

10u-1206

Title

Micro Star Restricted Secret

mPGA478-B Intel CPU Socket Part 2

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-6721

Last Revision Date:

Sheet

Rev

Thursday, October 03, 2002

5 27

of

0A

C1XAVSS

C1XAVDD

C4XAVSS

C4XAVDD

HPCOMP

HNCOMP

HVREF

HNCVREF

AC/BE#3

AC/BE#2

AC/BE#1

AC/BE#0

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

AGP8XDET

SB_STB

SB_STB#

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

AGPCLK

AGPRCOMP

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AGPVSSREF

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

DBI#3

DBI#2

DBI#1

A27

H27

HDBI#3

HDBI#2

HDBI#1

CT16

X_10u_0805

R25

APAR

RBF#

WBF#

PIPE#

ADBIH

ADBIL

DBI#0

HDBI#0

U8A

F6

F3

H4

K5

C9

A6

G2

G1

G3

G4

H5

H1

H3

E8

F8

D9

D10

B3

C4

B5

A4

K1

L1

C1

D1

B10

M1

B9

A9

B8

A8

M3

M2

F20

F23

K24

P24

F21

F24

L24

N25

SIS-SIS650GL

AGPCLK0

AGPRCOMP

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

HDBI#[0..3] 4

AGPCLK0 3

HDSTBN#3 4

HDSTBN#2 4

HDSTBN#1 4

HDSTBN#0 4

HDSTBP#3 4

HDSTBP#2 4

HDSTBP#1 4

HDSTBP#0 4

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

SIS 650 PART1

VDDQ

R140

60.4

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

MS-6721

Last Revision Date:

Sheet

VCC3

CP24

1 2

X_COPPER_0

L34

X_0

CP23

1 2

CP26

1 2

L35

X_80_0603

CP25

1 2

CT22

X_10u_0805

VCC3

CT23

X_10u_0805

CB77

0.1u

CB78

0.1u

CB75

0.01u

X_COPPER_0

X_COPPER_0

CB80

0.01u

X_COPPER_0

Rev

Thursday, October 03, 2002

6 27

of

0A

AH25

AJ25

AH27

AJ27

U21

T21

P21

N21

J17

B20

B19

A19A7F9B7M6M5M4L3L6L4K6L2K3J3K4J2J6J4J1H6F4F1G6E3F5E2E4E1D3D4C2F7C3E6B2D5D6A3D7C5A5C6D8

RS#2

RS#1

RS#0

HD#[0..63]

HVREF

CB65

0.1u

AJ26

AH26

W26

W28

W29

W24

W25

AD24

AA24

AF26

AE25

AH28

AD26

AG29

AE26

AF28

AC24

AG28

AE29

AD28

AC25

AD27

AE28

AF27

AB24

AB26

AC28

AC26

AC29

AA26

AB28

AB27

AA25

AA29

AA28

U26

U24

V26

C20

D19

T27

U25

T24

T26

U29

V28

T28

U28

V24

V27

Y27

Y26

Y24

Y28

CPUCLK

CPUCLK#

DEFER#

HLOCK#

HTRDY#

CPURST#

CPUPWRGD

BPRI#

BREQ0#

RS#2

RS#1

RS#0

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HASTB#1

HASTB#0

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

B21

HD#63

C1XAVSS

C4XAVSS

C1XAVDD

HOST

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

F19

A21

E19

D22

D20

B22

C22

B23

HD#59

HD#58

HD#57

HD#62

HD#61

HD#55

HD#60

HD#56

R80

150

HNCVREF

R81

75

HVREF0

C4XAVDD

HD#55

HD#54

HD#53

A23

D21

HD#54

HD#53

CB57

X_0.1u

CB55

0.1u

HVREF1

HD#52

F22

HD#52

HVREF2

HD#51

D24

D23

HD#51

ST0

ST1

ST2

AAD0

AAD1

AAD2

AAD3

AAD4

AAD5

AAD6

AAD7

AAD8

AAD9

AAD10

AAD11

AAD12

AAD13

AAD14

HVREF3

HVREF4

HPCOMP

HNCOMP

HNCOMPVREF

AAD15

650GL-1

HD#50

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

HD#32

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

C24

B24

E25

E23

D25

A25

C26

B26

B27

D26

B28

E26

F28

G25

F27

F26

G24

H24

HD#39

HD#38

HD#37

HD#36

CB45

0.01u

X_COPPER_0

HD#32

HD#33

HD#35

HD#34

CP8

1 2

X_COPPER_0

L19

X_0

CP11

1 2

HD#44

HD#43

HD#46

HD#45

HD#42

HD#41

HD#50

HD#49

HD#48

HD#47

HD#40

C1XAVDD

C1XAVSS

HD#25

G29

J26

G26

J25

H26

G28

H28

J24

HD#31

HD#30

HD#29

HD#24

HD#28

HD#27

HD#26

HD#25

CT15

X_10u_0805

AAD16

AAD17

HD#24

HD#23

K28

HD#23

J29

HD#22

AAD18

AAD19

HD#22

HD#21

K27

HD#21

J28

HD#20

AAD20

AAD21

HD#20

HD#19

M24

HD#19

L26

HD#18

AAD22

AAD23

HD#18

HD#17

K26

HD#17

L25

AAD24

AAD25

HD#16

HD#15

L28

M26

HD#14

HD#15

HD#16

C4XAVDD

C4XAVSS

AAD26

HD#14

P26

HD#13

AAD27

AAD28

AAD29

AAD30

AAD31

AGP

HD#13

HD#12

HD#11

HD#10

HD#9

HD#8

L29

N24

N26

M27

N28

HD#9

HD#8

HD#12

HD#11

HD#10

HLOCK#4

HTRDY#4

HBPRI#4

HBR#04

RS#[0..2]

HADSTB#14

HADSTB#04

R83

20

R78

110

CPUCLK1

CPUCLK-1

HDEFER#

HLOCK#

HTRDY#

CPURST#

CPU_GD

HBPRI#

HBR#0

HADS#

HITM#

HIT#

HDRDY#

HDBSY#

HBNR#

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HADSTB#1

HADSTB#0

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

HNCOMP

Rds-on(n) = 10 ohm

HNCVERF = 1/3 VCCP

HPCOMP

Rds-on(p) = 56 ohm

HPCVERF = 2/3 VCCP

HD#[0..63]4

CB66

0.01u

place this capacitor

under 650 solder side

CPUCLK13

CPUCLK-13

HDEFER#4

CPURST#4

CPU_GD4

RS#[0..2]4

HADS#4

HITM#4

HIT#4

HDRDY#4

HDBSY#4

HBNR#4

HREQ#[0..4]4

HA#[3..31]4

HREQ#[0..4]

HA#[3..31]

VCCP

VCCP VCCP

R90

75

R89

150

SBA7

HD#7

P27

HD#7

N29

HD#6

CB49

0.01u

SBA6

HD#6

R24

HD#5

SBA5

HD#5

SBA4

SBA3

SBA2

HD#4

HD#3

HD#2

R28

M28

P28

R26

HD#3

HD#2

HD#4

HD#1

CP7

1 2

X_COPPER_0

L18

X_80_0603

CP9

1 2

X_COPPER_0

C7

SBA1

HD#1

R29

HD#0

SBA0

HD#0

E21

VCC3VCC3

MD63

MD30

MD29

MD59

MD31

MD62

MD60

MD28

MD61

CSB#0

MD27

MD58

MD55

MD23

MD26

MD57

MD56

MD24

MD25

CSB#1

MD22

MD53

MD20

MD19

MD54

MD21

MD51

MD50

MD52

CSB#2

MD18

MD17

DQM7

DQM6

MD49

MD48

DQM3

DQM2

MD16

CSB#3

DQM5

DQM4

MD47

MD45

DQM1

DQM0

MD46

MD14

MD15

MD13

MD43

MD42

MD10

MD44

MD12

MD41

MD9

MD11

MD40

MD8

MD37

MD36

MD39

MD7

MD6

MD5

MD38

MD35

MD34

MD1

MD0

MD4

MD3

MD33

MD32

MD2

AJ23

AG22

AH21

AJ21

AD23

AE23

AF22

AF21

AD22

AH22

AD21

AG20

AE19

AF19

AE21

AD20

AD19

AH19

AF20

AH20

AF18

AG18

AH17

AD16

AD18

AD17

AF17

AJ17

AE17

AH18

AD14

AG14

AJ13

AE13

AJ15

AF14

AD13

AF13

AH13

AH14

AD10

AH10

AE9

AD8

AG10

AF10

AH9

AF9

AD9

AH5

AG4

AE5

AH3

AG6

AF6

AF5

AF4

AH4

AE4

AD6

AE2

AC5

AG2

AG1

AF3

AC6

AD4

AF2

AB6

AD3

AA6

AB3

AC4

AE1

AD2

AC1

AB4

AC2

AJ9

AJ3

U8B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0/CSB#0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1/CSB#1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2/CSB#2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3/CSB#3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4/CSB#4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5/CSB#5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6/CSB#6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7/CSB#7

SIS-SIS650GL

650GL-2

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

SRAS#

SCAS#

SWE#

CS#0

CS#1

CS#2

CS#3

CS#4

CS#5

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

SDCLK

FWDSDCLKO

SDRCLKI

SDAVDD

SDAVSS

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

DRAM_SEL

AH11

AF12

AH12

AG12

AD12

AH15

AF15

AH16

AE15

AD15

AF11

AG8

AJ11

AG16

AF16

AH8

AJ7

AH7

AE7

AF7

AH6

AJ5

AF8

AD7

AB2

AA4

AB1

Y6

AA5

Y5

Y4

AA3

R103 22

AD11

AE11

Y1

Y2

AA1

AA2

AJ19

AH2

R147 4.7K

W3

Rs place close to DIMM1

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

SRAS#

SCAS#

SWE#

CSA#0

CSA#1

CSA#2

CSA#3

CKE: Open Drain

S3AUXSW#

R143 4.7K

FWDSDCLKO

C92

SDAVDD

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

10p_0603

SDCLKI

Low for

SDR

MD[0..63]

DQM[0..7]

CSB#[0..4]

MA[0..14]

CSA#[0..3]

CKE[0..3]

SRAS# 10

SCAS# 10

SWE# 10

CKE0

CKE1

CKE2

CKE3

VCC3SBY

SDCLK

FWDSDCLKO 3

SDCLKI 3

S3AUXSW# 24

SDCLK 3

MD[0..63] 10

DQM[0..7] 10

CSB#[0..4] 10

MA[0..14] 10

CSA#[0..3] 10

CKE[0..3] 10

SDAVDD

SDAVSSSDAVSS

DDRAVDD

DDRAVSS

CB82

0.1u

CB92

0.1u

CB90

0.01u

DDRVREFA

DDRVREFB

CP33

1 2

X_COPPER_0

L40

X_80_0603

CB81

0.01u

CP32

1 2

X_COPPER_0

CP31

1 2

X_COPPER_0

L39

X_80_0603

CP29

1 2

X_COPPER_0

CB64

0.1u

CB79

0.1u

VCC3

VCC3

VCCM

VCCM

R86

150

R88

150

R129

150

R128

150

Title

Micro Star Restricted Secret

SIS 645DX / 651 PART2

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-6721

Last Revision Date:

Sheet

Rev

Thursday, October 03, 2002

7 27

of

0A

VCC1_8

ZAD[0..15]12

VCC1_8

150

VCC3

VCC3

CP27

1 2

X_COPPER_0

L36

X_80_0603

R148

R150

150

CB91

0.1u

CP28

1 2

X_COPPER_0

L37

X_80_0603

CP30

1 2

X_COPPER_0

L38

X_80_0603

C118

0.1u

ZAD[0..15]

ZVREF

C112

0.1u

0.1u

Z1XAVDD

Z1XAVSS

Z4XAVDD

C119

Z4XAVSS

R142 56

R141 56

NOTE: This page is for universal PCB design( suitable for both 645 or 650)

NB Hardware Trap Table

0

enable PLL disable PLL

SDR DDR

normal NB debug mode

TV selection, NTSC/PAL(0/1) 0

enable VB

enable VGA interface

enable panel link

U8C

SIS-SIS650GL

V3

ZCLK

U6

ZUREQ

U1

ZDREQ

T3

ZSTB0

T1

ZSTB#0

P1

ZSTB1

P3

ZSTB#1

T4

ZAD0

R3

ZAD1

T5

ZAD2

T6

ZAD3

R2

ZAD4

R6

ZAD5

R1

ZAD6

R4

ZAD7

P4

ZAD8

N3

PCIRST1#21,24

PWRGD13,23,24

RSMRST#13,15,24

ENTEST

PWRGD

RSMRST#

P5

P6

N1

N6

N2

N4

U3

V5

U4

U2

V6

W1

W2

V2

V1

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZVREF

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

PCIRST1#

PWRGD

RSMRST#

R122 4.7K

C125 0.1u

C122 0.1u

HyperZip

650GL-3

PCIRST#

PWROK

Y3W4W6

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

DLLEN#

DRAM_SEL

TRAP0

TRAP1

CSYNC

RSYNC

LSYNC

ZCLK0

ZCLK03

ZUREQ12

ZDREQ12

ZUREQ

ZDREQ

ZSTB0

ZSTB012

ZSTB-0

ZSTB-012

ZSTB1

ZSTB112

ZSTB-1

ZSTB-112

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13 VCOMP

ZAD14 VRSET

ZAD15

ZVREF

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

1

VGA

Stereo

Glass

AUXOK

TRAP1

D11

TRAP0

E10

Default

1(DDR)

TESTMODE2

TESTMODE1

TESTMODE0

A10

F11

C11

DLLEN#

E11

F10

0

0

0

1

0

ENTEST

ENTEST

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

embedded pull-low

(30~50K Ohm)

yes

yes

yes

C15

VOSCI

A12

ROUT

B13

GOUT

A13

BOUT

F13

HSYNC

E13

VSYNC

D13

VGPIO0

D12

VGPIO1

B11

INT#A

E12

CSYNC

A11

RSYNC

F12

LSYNC

E14

VCOMP

D14

VRSET

F14

VVBWN

B12

DACAVDD1

C12

DACAVSS1

C13

DACAVDD2

C14

DACAVSS2

B15

DCLKAVDD

A15

DCLKAVSS

B14

ECLKAVDD

A14

ECLKAVSS

1 2

X_COPPER_0

L25

CB70

0.1u

1 2

X_COPPER_0

1 2

X_COPPER_0

L29 X_80_0603

CB71

0.1u

1 2

X_COPPER_0

R114

R105 0

R97

R96 15

R92 15

R93 100

R95

100

VCC3

CP15

X_80_0603

CP16

VCC3

CP17

CP18

REFCLK0

0

0

HSYNC

VSYNC

DDC1CLK

DDC1DATA

INTA#

RSYNC

VVBWN

DACAVDD1

DACAVSS1

DACAVDD1

DACAVSS1

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

C76

X_10u_0805

C84

X_10u_0805

for 650 only

RSYNC

Title

R118 4.7K

REFCLK0 3

HSYNC 20

VSYNC 20

DDC1CLK 20

DDC1DATA 20

INTA# 12,16

VVBWN

VCOMP

DACAVDD1

DACAVSS1

CB61

CB59

C96

X_47p

Micro Star Restricted Secret

SIS 650 PART3

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

VCC3

C91

C94

X_47p

X_47p

0.1u

0.1u

CB72

0.1u

MS-6721

Last Revision Date:

Sheet

ROUT

GOUT

BOUT

L31

CP22

1 2

X_COPPER_0

80_0603

VCC1_8

L33X_80_0603

ROUT 20

GOUT 20

BOUT 20

VRSET

C100

X_10u_0805

Rev

Thursday, October 03, 2002

8 27

of

R91

130

0A

VCCM

VDDQ

VCC1_8

VCCP

VCCP VCC1_8 VCC3

H21

H22

J16

J20

J21

J22

K16

K17

K18

K19

K20

K21

L20

M20

N20

P20

R20

R21

T20

U20

V20

W20

Y20

Y21

AA20

AA21

AA22

AB21

AB22

L12

L14

L15

L16

L18

M11

M19

N11

IVDD

VSS

T12

IVDD

VSS

T13

IVDD

VSS

T14

IVDD

VSS

T15

IVDD

VSS

T16

IVDD

VSS

T17

P19

IVDD

VSS

T18

AB5

AD5

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE22

W18

AA8

AA9

AA10

AA13

AA14

AA15

AA16

AA17

AB8

AB9

AB13

AB17

A16

VTT

A17

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

A18

VTT

B16

VTT

B17

VTT

B18

VTT

C16

VTT

C17

VTT

C18

VTT

D15

VTT

D16

VTT

D17

VTT

D18

VTT

E15

VTT

E16

VTT

E17

VTT

E18

VTT

F15

VTT

F16

VTT

F17

VTT

F18

VTT

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

V10

VDDM

V11

VDDM

VDDM

Y9

VDDM

Y10

VDDM

Y12

VDDM

Y14

VDDM

Y16

VDDM

Y18

VDDM

Y19

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

E5

VDDQ

E7

VDDQ

E9

VDDQ

G5

VDDQ

J5

VDDQ

L5

VDDQ

H8

VDDQ

H9

VDDQ

J8

VDDQ

J9

VDDQ

J10

VDDQ

J13

VDDQ

K9

VDDQ

K11

VDDQ

K13

VDDQ

L10

VDDQ

N9

VDDQ

N10

VDDQ

N5

VDDZ

R5

VDDZ

U5

VDDZ

W5

VDDZ

P9

VDDZ

P10

VDDZ

R9

VDDZ

R10

VDDZ

T9

VDDZ

T10

VDDZ

T11

VDDZ

PVDDP

PVDDP

PVDDP

PVDDP

PVDDP

PVDDP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L17

L19

N19

R19

U19

W19

M12

M13

M14

M15

M16

M17

M18

N12

N13

N14

N15

N16

N17

N18

VCC1_8

VSS

P12

P13

P14

P15

P16

P17

P18

IVDD

650GL-4

Power

VSS

VSS

VSS

VSS

VSS

VSS

VSS

R12

R13

R14

R15

R16

R17

R18

R11

IVDD

VSS

U12

T19

IVDD

VSS

U13

U11

IVDD

VSS

U14

V19

IVDD

VSS

U15

W11

IVDD

VSS

U16

W13

IVDD

VSS

U17

W15

IVDD

VSS

U18

W17

IVDD

VSS

V12

IVDD

VSS

V13

P11

VSS

V14

PVDDZ

VSS

VSS

V15

J14

V16

J15

OVDD

OVDD

VSS

VSS

V17

K15

V18

K10

OVDD

VSS

K12

PVDD

B25

K14

PVDD

VSS

C28

M10

PVDD

VSS

C29

PVDD

VSS

VCC3SBY

W10

Y11

PVDDM

VSS

VSS

D27

D28

E28

Y13

Y15

PVDDM

PVDDM

VSS

VSS

E29

AF23

Y17

PVDDM

PVDDM

VSS

VSS

AF24

AF25

AUX1.8

AUX3.3

VSS

VSS

AG24

VSS

AG26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH23

VSS

VSS

AH24

U8D

U10

U9

A20

A22

A24

A26

C19

C21

C23

C25

C27

E20

E22

E24

F25

H25

K25

M25

P25

T25

V25

Y25

AB25

AD25

E27

G27

J27

L27

N27

R27

U27

W27

AA27

AC27

AE27

D29

F29

H29

K29

M29

P29

T29

V29

Y29

AB29

AD29

AF29

AE24

AG25

B4

B6

C8

C10

D2

F2

H2

K2

P2

T2

V4

AD1

AF1

AC3

AE3

AG3

AG5

AG7

AG9

AG11

AG13

AG15

AG17

AG19

AG21

AG23

AJ4

AJ6

AJ8

AJ10

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

AJ24

AG27

SIS-SIS650GL

VCC1_8SBY

VCC3SBY

VCCP

VDDQ

VCCP

CB56

1u

CB62

1u

CB1

1u

CB9

1u

CB89

0.1u

CB84

0.1u

CB133

X_0.1u

CB134

X_0.1u

CB136

X_0.1u

CB132

X_0.1u

VCC3

CB67

1u

CB119

0.1u

VCC3SBY

VCC1_8

Title

CB68

0.1u

CB15

0.1u

CB63

0.1u

CB25

0.1u

CB86

0.1u

CB85

0.1u

CB149

CB146

X_0.1u

X_1u-0805

X_1u-0805

VCCM

10u_0805

10u_0805

Place these capacitors under 645 solder side

VCCM

X_0.1u

CB143

CB135

Micro Star Restricted Secret

VCC1_8SBY

CT20

CT21

CB137

X_0.1u

CB138

X_0.1u

CB144

X_0.1u

CB141

X_0.1u

CB97

1u

SIS 650 PART4

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

CB87

0.1u

VCC3

MS-6721

VCC1_8

CB44

0.1u

CB69

0.1u

VCC3SBY

CB142

VDDQ

X_0.1u

CB139

X_0.1u

Last Revision Date:

Thursday, October 03, 2002

Sheet

9 27

CB88

0.1u

CB83

0.1u

CB110

0.1u

CB73

0.1u

CB111

0.1u

of

CB53

1u

CB74

0.1u

CB140

X_0.1u

CB148

X_0.1u

CB147

X_0.1u

CB145

X_0.1u

Rev

0A

MD[0..63]7

MA[0..14]7

DQM[0..7]7

CSA#[0..5]7

CSB#[0..5]7

SDCLK[0..7]3

CKE[0..5]7

MD[0..63]

MA[0..14]

DQM[0..7]

VCCM

DIMM1

168

157

143

133

124

110

1029084735949414026186

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

MA0 REOE MA0

MA1 MA1

MA2 MA2

MA3 MA3

MA4 MA4

MA5 MA5

MA6 MA6

MA7 MA7

MA8 MA8

MA9 MA9

MA10 MA10

MA13 MA13

MA14 MA14

MA11 MA11

MA12 MA12

DQM0 DQM0

DQM1 DQM1

DQM2 DQM2

DQM3 DQM3

DQM4 DQM4

DQM5 DQM5

DQM6 DQM6

RN20X_47K

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

SRAS# SRAS#

SRAS#7

SCAS# SCAS#

SCAS#7

SWE# SWE#

SWE#7

SMBCLK SMBCLK

SMBCLK3,13,24

SMBDAT SMBDAT

SMBDAT3,13,24

CSA#[0..3]

CSB#[0..3]

SDCLK[0..7]

CKE[0..3]

RN9X_47K

DQM7 DQM7

CB4 CB0

CB0 CB1

CB1 CB2

CB5 CB3

CB2 CB4

CB3 CB5

CB6 CB6

CB7 CB7

CSA#0

CSA#1

CSB#0

CSB#1

SDCLK0 SDCLK2

SDCLK1 SDCLK3

SDCLK6 SDCLK4

SDCLK7 SDCLK5

CKE0 CKE2

CKE1 CKE3

VCC3

33

A[0]

117

A[1]

34

A[2]

118

A[3]

35

A[4]

119

A[5]

36

A[6]

120

A[7]

37

A[8]

121

A[9]

38

A[10]/AP

123

A[11]

126

A[12]

122

BA[0]

39

BA[1]

132

A[13]

28

DQM[0]

29

DQM[1]

46

DQM[2]

47

DQM[3]

112

DQM[4]

113

DQM[5]

130

DQM[6]

131

DQM[7]

105

CB[4]

21

CB[0]

22

CB[1]

106

CB[5]

52

CB[2]

53

CB[3]

136

CB[6]

137

CB[7]

115

SRAS#

111

SCAS#

30

S#[0]

114

S#[1]

45

S#[2]

129

S#[3]

27

WE0#

48

WE2#

42

CK[0]

125

CK[1]

79

CK[2]

163

CK[3]

128

CKE[0]

63

CKE[1]

83

SCL

82

SDA

SA[0]

SA[1]

SA[2]

WP/NC

NC

NC

NC

NC/OE#0

NC/OE#2

NCNCNC

616280

NC

108

addr =

1010000b

VSS

VSS

1

12

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

43647896116

107

85

68

543223

VSS

VSS

165

166

167

81

24

25

50

31

44

127

REOE/NC

VSS

VSS

138

148

DQ[0]

DQ[1]

DQ[2]

DQ[3]

DQ[4]

DQ[5]

DQ[6]

DQ[7]

DQ[8]

DQ[9]

DQ[10]

DQ[11]

DQ[12]

DQ[13]

DQ[14]

DQ[15]

DQ[16]

DQ[17]

DQ[18]

DQ[19]

DQ[20]

DQ[21]

DQ[22]

DQ[23]

DQ[24]

DQ[25]

DQ[26]

DQ[27]

DQ[28]

DQ[29]

DQ[30]

DQ[31]

DQ[32]

DQ[33]

DQ[34]

DQ[35]

DQ[36]

DQ[37]

DQ[38]

DQ[39]

DQ[40]

DQ[41]

DQ[42]

DQ[43]

DQ[44]

DQ[45]

DQ[46]

DQ[47]

DQ[48]

DQ[49]

DQ[50]

DQ[51]

DQ[52]

DQ[53]

DQ[54]

DQ[55]

DQ[56]

DQ[57]

DQ[58]

DQ[59]

DQ[60]

DQ[61]

DQ[62]

DQ[63]

VSS

152

147

MD0

2

MD1

3

4

MD2

MD3

5

MD7

7

MD5

8

MD6

9

10

MD4

164

NC

MD8

11

MD9

13

MD10

14

15

MD11

MD12

16

MD13

17

MD14

19

MD15

20

51

NC

MD16

55

MD17

56

MD18

57

MD19

58

60

MD20

MD21

65

MD22

66

MD23

67

146

NC

69

MD24

MD25

70

MD26

71

MD27

72

MD28

74

75

MD29

76

MD31

77

145

NC

MD32

86

87

MD33

MD34

88

MD35

89

MD36

91

MD37

92

93

MD38

MD39

94

135

NC

MD40

95

MD41

97

98

MD42

MD43

99

MD44

100

MD45

101

MD46

103

104

MD47

134

NC

MD48

139

MD49

140

MD50

141

142

MD51

MD52

144

MD53

149

MD54

150

MD55

151

109

NC

MD56

153

MD57

154

MD58

155

MD59

156

158

MD60

MD61

159

MD62

160

MD63

161

VSS

VSS

DIMM

162

VCCM

CSA#2

CSA#3

CSB#2

CSB#3

VCCM VCCM

168

157

143

133

124

110

1029084735949414026186

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

33

A[0]

117

A[1]

34

A[2]

118

A[3]

35

A[4]

119

A[5]

36

A[6]

120

A[7]

37

A[8]

121

A[9]

38

A[10]/AP

123

A[11]

126

A[12]

122

BA[0]

39

BA[1]

132

A[13]

28

DQM[0]

29

DQM[1]

46

DQM[2]

47

DQM[3]

112

DQM[4]

113

DQM[5]

130

DQM[6]

131

DQM[7]

21

CB[0]

22

CB[1]

52

CB[2]

53

CB[3]

105

CB[4]

106

CB[5]

136

CB[6]

137

CB[7]

115

SRAS#

111

SCAS#

30

S#[0]

114

S#[1]

45

S#[2]

129

S#[3]

27

WE0#

48

WE2#

42

CK[0]

125

CK[1]

79

CK[2]

163

CK[3]

128

CKE[0]

63

CKE[1]

83

SCL

82

SDA

SA[0]

SA[1]

SA[2]

WP/NC

NC

NC

NC

NC/OE#0

NC/OE#2

NCNCNC

616280

NC

108

VSS

1

12

addr =

1010001b

VSS

VSS

VSS

VSS

VSS

VSS

VSS

43647896116

68

543223

165

166

167

81

24

25

50

31

44

REOE/NC

DQ[0]

DQ[1]

DQ[2]

DQ[3]

DQ[4]

DQ[5]

DQ[6]

DQ[7]

NC

DQ[8]

DQ[9]

DQ[10]

DQ[11]

DQ[12]

DQ[13]

DQ[14]

DQ[15]

NC

DQ[16]

DQ[17]

DQ[18]

DQ[19]

DQ[20]

DQ[21]

DQ[22]

DQ[23]

NC

DQ[24]

DQ[25]

DQ[26]

DQ[27]

DQ[28]

DQ[29]

DQ[30]

DQ[31]

NC

DQ[32]

DQ[33]

DQ[34]

DQ[35]

DQ[36]

DQ[37]

DQ[38]

DQ[39]

NC

DQ[40]

DQ[41]

DQ[42]

DQ[43]

DQ[44]

DQ[45]

DQ[46]

DQ[47]

NC

DQ[48]

DQ[49]

DQ[50]

DQ[51]

DQ[52]

DQ[53]

DQ[54]

DQ[55]

NC

DQ[56]

DQ[57]

DQ[58]

DQ[59]

DQ[60]

DQ[61]

DQ[62]

DQ[63]

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

138

152

162

148

127

107

85

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

R56

DIMM2

8.2K

REOE

147

MD0

2

MD1

3

4

MD2

MD3

5

MD7

7

MD5

8

MD6

9

10

MD4

164

MD8

11

MD9

13

MD10

14

15

MD11

MD12

16

17

19

20

51

55

56

57

58

60

65

66

67

146

69

70

71

72

74

75

76

77

145

86

87

88

89

91

92

93

94

135

95

97

98

99

100

101

103

104

134

139

140

141

142

144

149

150

151

109

153

154

155

156

158

159

160

161

DIMM

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DIMM DECOUPLING

VCCM

Closed to DIMM1,2 socket

CKE1

CKE3

CKE2

CKE0

Micro Star Restricted Secret

DDR DIMM 1 & 2

MS-6721

Last Revision Date:

Thursday, October 03, 2002

Sheet

10 27

CB76

0.1u

CB54

0.1u

CB31

0.1u

CB60

0.1u

CB10

0.1u

CB35

0.1u

RN19

1 2

3 4

5 6

7 8

8P4R-470

of

VCCM

Rev

0A

REFCLK23

CD IN

JCD1

CD-D1x4-BK-SBTJ

SPDIFO

12

12

R200

C181

105P

C187

10p

47K

VDD3

12

C192

0.1u

R231 33

R233 22

CDL1

CDR1

12

R213

47K

CP40

VDD3

VCC3

R237

10K

C190 103P

1

2

3

4

XTALIN

R236

10K

R206

CDL CDLX

R201

CDGND CDGNDX

R194

CDR CDRX

1 2

1 2

R238 X_3.3/0805

AC_RST#13

AC_SDIN013

AC_SDOUT13,14

AC_SYNC13

AC_BITCLK13

4.7K12

4.7K12

4.7K12

12

R199

CDGND1

47K

R239 1K

4847464544424140394338

U14

1

NC

NC

DVDD1

9

DVDD2

4

DVSS1

7

DVSS2

2

XTL_IN

3

XTL_OUT

ALC 101

11

RESET#

8

SDATA_IN

5

SDATA_OUT

10

SYNC

6

BIT_CLK

12

PC_BEEP

PHONE

AUXL

1314151617181920212223

C171

12

105P/0805

C170

12

105P/0805

C169

12

105P/0805

TEST6

AUXR

TEST5

TEST4

TEST1

VIDEOL

VIDEOR

AVSS2

DACOUTR

CDL

CDGND

+5VR

TEST2

DACOUTL

CDR

C195

4.7U/0805

37

36

LOUTR

35

MONO

AVDD2

LOUTL

34

NC

33

NC

32

VRDA

31

VRAD

30

AFILT2

29

AFILT1

28

NC

27

VREF

25

AVDD1

26

AVSS1

MIC1

MIC2

LINL

LINR

ALC101

24

LINEIN_R

LINEIN_L LINEIN_LC

C168

MIC_I

1 2

105P/0805

VREFOUT

1 2

C166

MIC_I_C

12

C176

0.1u

C162

103P

+5VR

105P/0805

105P/0805

VREFOUT

LINE_ROUT

LINE_LOUT

+

EC18

ELS10/16-B

LINEIN_RC

12

R215

47K

R167 4.7K

R214 1K

EC23 ELS10/16-B

+

EC22 ELS10/16-B

+

C177

0.1u

1 2

R204

12

R205

R216

47K

LINE OUT

AUDIO1-4

23

22

21

20

30

AUDIO_GAME

R249

FB3

1 2

301S/0805

FB4

1 2

301S/0805

R247

1K

1K

12

C205

102p

SPEAKER_R

SPEAKER_L

12

C212

102p

LINE_NEXT_R

LINE_NEXT_L

12

C135

102p

12

C136

102p

Front Audio Pin Header

12

12

C185

C182

C134

0.1u

1 2

4.7K1 2

4.7K1 2C167

MIC_IN

12

C139

102p

102p

12

C138

102p

27

26

25

24

29

102p

12

C137

102p

AUDIO1-2

AUDIO_GAME

C188

X_105P

C191

X_105P

AUDIO1-3

19

18

17

16

28

AUDIO_GAME

SPEAKER_R LINE_NEXT_R

SPEAKER_L LINE_NEXT_L

SPEAKER_R

SPEAKER_L

JAUD1

MIC_IN

1 2

3 4

6

5

7

109

D2x5-1:8-BK

LINE_NEXT_R

R248 X_0

LINE_NEXT_L

R246 X_0

DECOUPLING CAPACITOR

LINE_NEXT_R

LINE_NEXT_L

SPEAKER_R

SPEAKER_L

MIC_IN

For EMI

C210

102P

12

C214

102P

+5VR

C211

0.1u

C206

102P

12

12

C213

C215

102P

102P

12

R202 X_2.2K

+5VR

R203

X_2.2K

External MIC power

GAME PORT

CP34

1 2

L41

F3

X_121S/1206 R146 2.2K

C127

0.1u

9

10

11

12

13

14

15

12

12

C113

C110

103P

103P

12

C104

103P

12

C101

102P

12

C108

103P

C111

5600p

C106

5600p

C132

0.1u

C102

5600p

1

2

3

4

5

6

7

8

AUDIO1-1

AUDIO_GAME

C123

C116

5600p

1 2

1.5A-S

0.1u

VCC5

GP4

GP4

GP2

GP2

GP1

GP5 RXD 21

R136 2.2K

GP1

R127 2.2K

GP5

12

C98

102P

GP4

GP5

GP6

GP7

RXD

TXD

R133 2.2K

R121 2.2K

R131 2.2K

R119 2.2K

R123 2.2K

R144 2.2K

R126 2.2K

R104 2.2K

R109 2.2K

GP6

GP0

TXD

GP3

GP7

RXD

VCC5

GP6 21

GP0 21

TXD 21

GP3 21

GP7 21

SPDIF CONNECTOR

For ALC202A

VCC5

JSP1

1

SPDIFO

2

3

X_D1x3-BK

ALC101 AC97 CODEC

VCC5

X_0.1uC147

X_0.1uC194

X_0.1uC89

FOR EMI

AUDIO CODE REGULATORS

R245

3.3_1206

12

C201

CP42

1 2

C164 X_0.1u

CP19

1 2

C120 X_0.1u

Title

Micro Star Restricted Secret

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

0.1u

21

O

AC' 97 CODEC & AUDIO Connectors

12

C199

0.1u

TOP VIEW

I3G

MS-6721

Last Revision Date:

Sheet

VR1

L78L05-TO92-100mA

3 1

VIN VOUT

GND

2

Thursday, October 03, 2002

11 27

of

+5VR+12VR+12V

12

C202

105P/0805

CP3912

Rev

0A

VCC1_8

R208

150

R210

150

INTD#

INTB#

INTC#

INTA#

VCC3

RN33

12

34

56

78

8P4R-8.2K

PREQ#216

PREQ#116

PREQ#016

PGNT#216

PGNT#116

PGNT#016

C/BE#[0..3]16

INTA#8,16

INTB#16

INTC#16

INTD#16

FRAME#16

IRDY#16

TRDY#16

STOP#16

SERR#16

DEVSEL#16

PLOCK#16

96XPCLK3

PCIRST#24

ZCLK13

ZSTB08

ZSTB-08

ZSTB18

ZSTB-18

ZUREQ8

ZDREQ8

CB108

0.1u

INTA#

INTB#

INTC# ICHRDYB

INTD# IDEREQB

FRAME# CBLIDB

IRDY#

TRDY# IDEIOR-B

STOP# IDEIOW-B

SERR#

PAR IDESAB2

PAR16

DEVSEL# IDESAB1

PLOCK# IDESAB0

96XPCLK IDECS-B1

PCIRST# IDECS-B0

ZCLK1 IDEDA4

ZSTB0 IDEDA6

ZSTB-0 IDEDA7

ZSTB1 IDEDA9

ZSTB-1 IDEDA10

ZUREQ IDEDA13

ZDREQ IDEDA14

SZVREF IDEDB12

AD[0..31]16

PREQ#2

PREQ#1

PREQ#0

PGNT#2

PGNT#1 IDACK-A

PGNT#0

C/BE#3 IDESAA1

C/BE#2 IDESAA0

C/BE#1

C/BE#0 IDECS-A1

R261 33

SVDDZCMP IDEDB0

SZCMP_N IDEDB1

SZCMP_P IDEDB3

SVSSZCMP IDEDB4

SZ1XAVDD IDEDB7

SZ1XAVSS IDEDB8

SZ4XAVDD IDEDB10

SZ4XAVSS IDEDB11

SZVREF IDEDB13

AD[0..31]

F1

PREQ#4

F2

PREQ#3

E1

PREQ#2

H5

PREQ#1

F3

PREQ#0

H3

PGNT#4

G1

PGNT#3

G2

PGNT#2

G3

PGNT#1

H4

PGNT#0

K3

C/BE#3

M4

C/BE#2

P1

C/BE#1

R4

C/BE#0

E3

INT#A

F4

INT#B

E2

INT#C

G4

INT#D

M3

FRAME#

M1

IRDY#

M2

TRDY#

N4

STOP#

M5

SERR#

N3

PAR

N1

DEVSEL#

N2

PLOCK#

Y2

PCICLK

C3

PCIRST#

V20

ZCLK

N19

ZSTB0

N20

ZSTB0#

K20

ZSTB1

K19

ZSTB1#

N16

ZUREQ

N17

ZDREQ

R19

VDDZCMP

N18

ZCMP_N

R18

ZCMP_P

P18

VSSZCMP

U20

Z1XAVDD

U19

Z1XAVSS

T20

Z4XAVDD

T19

Z4XAVSS

R20

VZREF

P20

ZVSSREF

AD31 ZAD0

AD30 ZAD1

AD29 ZAD2

AD28 ZAD3

AD27 ZAD4

AD26 ZAD5

AD25 ZAD6

AD24 ZAD7

AD23 ZAD8

AD22 ZAD9

AD21 ZAD10

AD20 ZAD11

AD19 ZAD12

AD18 ZAD13

AD17 ZAD14

AD16 ZAD15

AD15

AD14

AD13

AD12

AD11

AD10

AD9

AD8

J5J4H2H1J3K4J2J1K5K2L3K1L1L4L5L2N5P2P3P4R2R3R1T1P5T2U1U2T3R5U3

AD9

AD31

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

AD13

AD12

AD11

AD10

AD8

PCI

962L-1

HyperZip

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

M18

M19

M17

M16

M20

L16

L20

L18

K18

ZAD15

J20

K17

K16

H20

J18

H19

H18

AD7

AD6

AD5

AD4

AD3

AD7

AD6

AD5

AD4

AD3

IDE

AD2

AD1

AD0

V1

AD2

AD1

U15A

AD0

IDEAVDD

IDEAVSS

ICHRDYA

IDREQA

IIRQA

CBLIDA

IIOR#A

IIOW#A

IDACK#A

IDSAA2

IDSAA1

IDSAA0

IDECSA#1

IDECSA#0

ICHRDYB

IDREQB

IIRQB

CBLIDB

IIOR#B

IIOW#B

IDACK#B

IDSAB2

IDSAB1

IDSAB0

IDECSB#1

IDECSB#0

IDA10

IDA11

IDA12

IDA13

IDA14

IDA15

IDB10

IDB11

IDB12

IDB13

IDB14

IDB15

Y3

Y4

W10

V10

Y11

U12

V11

Y9

Y10

T11

U11

W11

T12

V12

W17

Y17

T16

U17

T14

W16

V16

Y18

T15

V17

U16

W18

U10

IDA0

V9

IDA1

W8

IDA2

T9

IDA3

Y7

IDA4

V7

IDA5

Y6

IDA6

Y5

IDA7

W6

IDA8

U8

IDA9

W7

V8

U9

Y8

T10

W9

Y16

IDB0

V15

IDB1

U14

IDB2

W14

IDB3

V13

IDB4

T13

IDB5

Y13

IDB6

Y12

IDB7

W12

IDB8

W13

IDB9

U13

Y14

V14

W15

Y15

U15

SIS962L

IDESAA2

IDECS-A0

IDEDA0

IDEDA1

IDEDA2

IDEDA3

IDEDA5

IDEDA8

IDEDA11

IDEDA12

IDEDA15

IDEDB2

IDEDB5

IDEDB6

IDEDB9

IDEDB14

IDEDB15

CB127

0.01u

IDESAA[0..2]

IDECS-A[0..1]

IDESAB[0..2]

IDECS-B[0..1]

CP43

1 2

X_COPPER_0

CB126

0.1u

ICHRDYA

IDEREQA

IDEIRQA

CBLIDA

IDEIOR-A

IDEIOW-A

IDECS-A[0..1] 18

IDEIRQB

IDACK-B

IDECS-B[0..1] 18

IDEDA[0..15] 18

IDEDB[0..15] 18

VCC1_8

CB129

0.1u

ICHRDYA 18

IDEREQA 18

IDEIRQA 18

CBLIDA 18

IDEIOR-A 18

IDEIOW-A 18

IDACK-A 18

IDESAA[0..2] 18

ICHRDYB 18

IDEREQB 18

IDEIRQB 18

CBLIDB 18

IDEIOR-B 18

IDEIOW-B 18

IDACK-B 18

IDESAB[0..2] 18

C156

X_10u_0805

CP47

1 2

X_COPPER_0

CP44

1 2

X_COPPER_0

ZAD[0..15]8

COST DOWN

SZ1XAVDD

C160

0.1u

SZ1XAVSS

Analog Power supplies of Transzip function for 962 Chip.

CP45

1 2

X_COPPER_0

CP48

1 2

X_COPPER_0

C159

0.1u

COST DOWN

SZ4XAVDD

SZ4XAVSS

VCC1_8VCC3 VCC3

CP38

1 2

X_COPPER_0

CP46

1 2

X_COPPER_0

C157

0.1u

COST DOWN

R207 56

R209 56

SVDDZCMP

SZCMP_N

SZCMP_P

SVSSZCMP

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

Micro Star Restricted Secret

SIS 962 PART 1

MS-6721

Last Revision Date:

Sheet

Rev

Thursday, October 03, 2002

12 27

of

0A

U15B

MIICLK25M

A8

HINIT#4

A20M#4

SMI#4

INTR4

NMI4

IGNNE#4

FERR#4

STPCLK#4

CPUSLP#4

APICCLK3

LAD[0..3]21

LFRAME#21

LDRQ#21

SIRQ21

PWRGD8,23,24

SMBDAT3,10,24

SMBCLK3,10,24

AC_SDIN011

AC_SDOUT11,14