Page 1

5

戶服務

smd.db-x7.ru

4

3

2

1

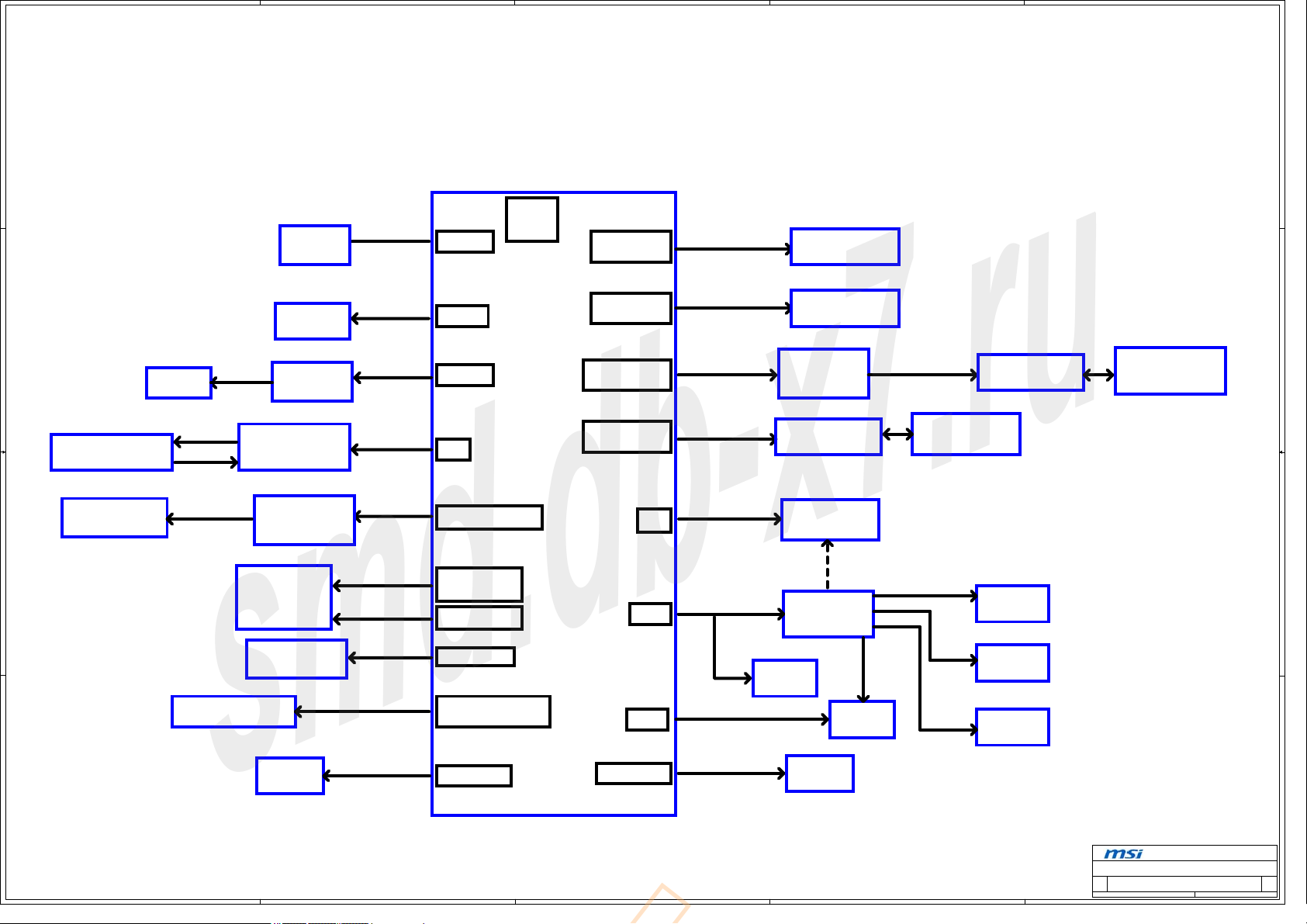

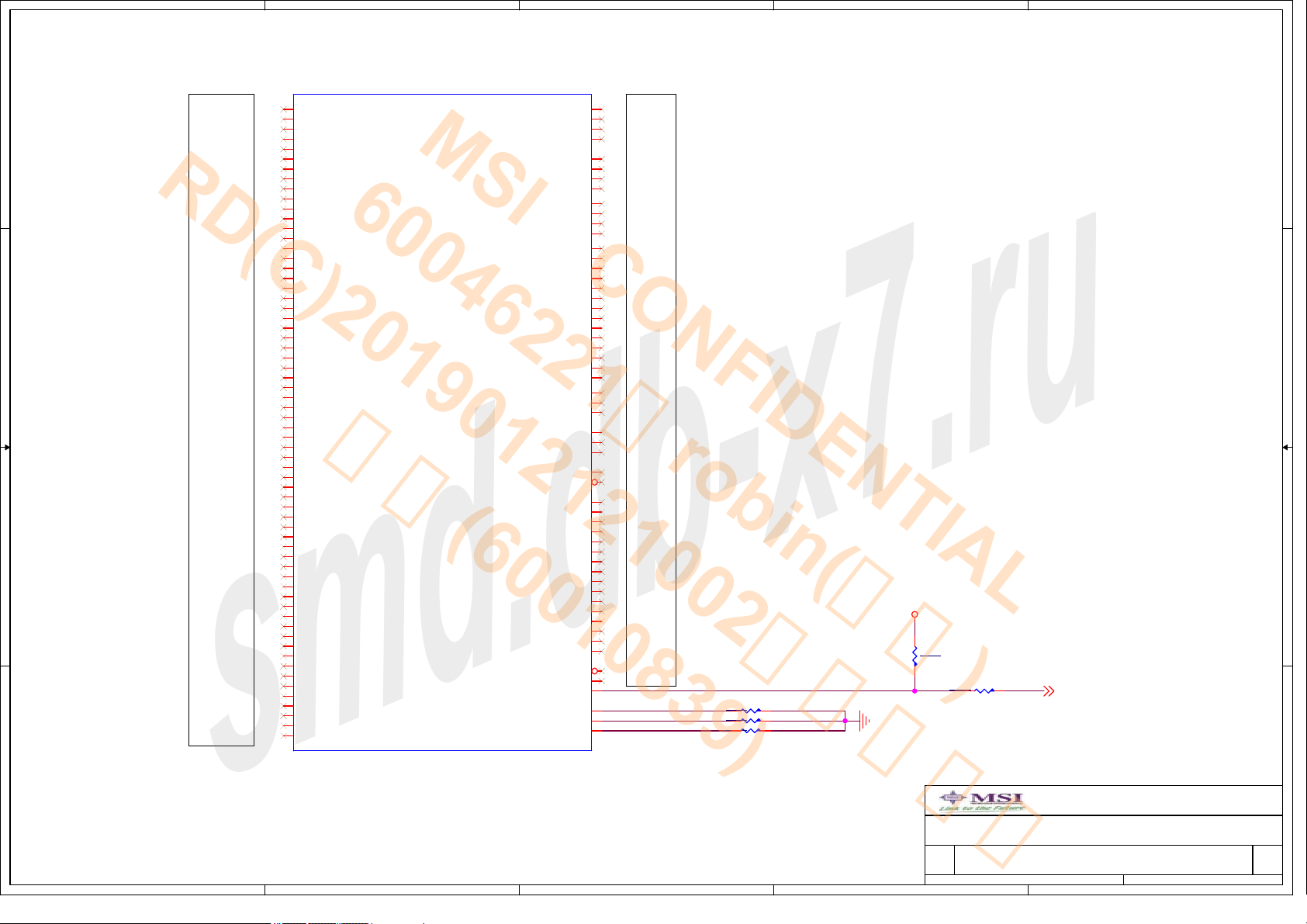

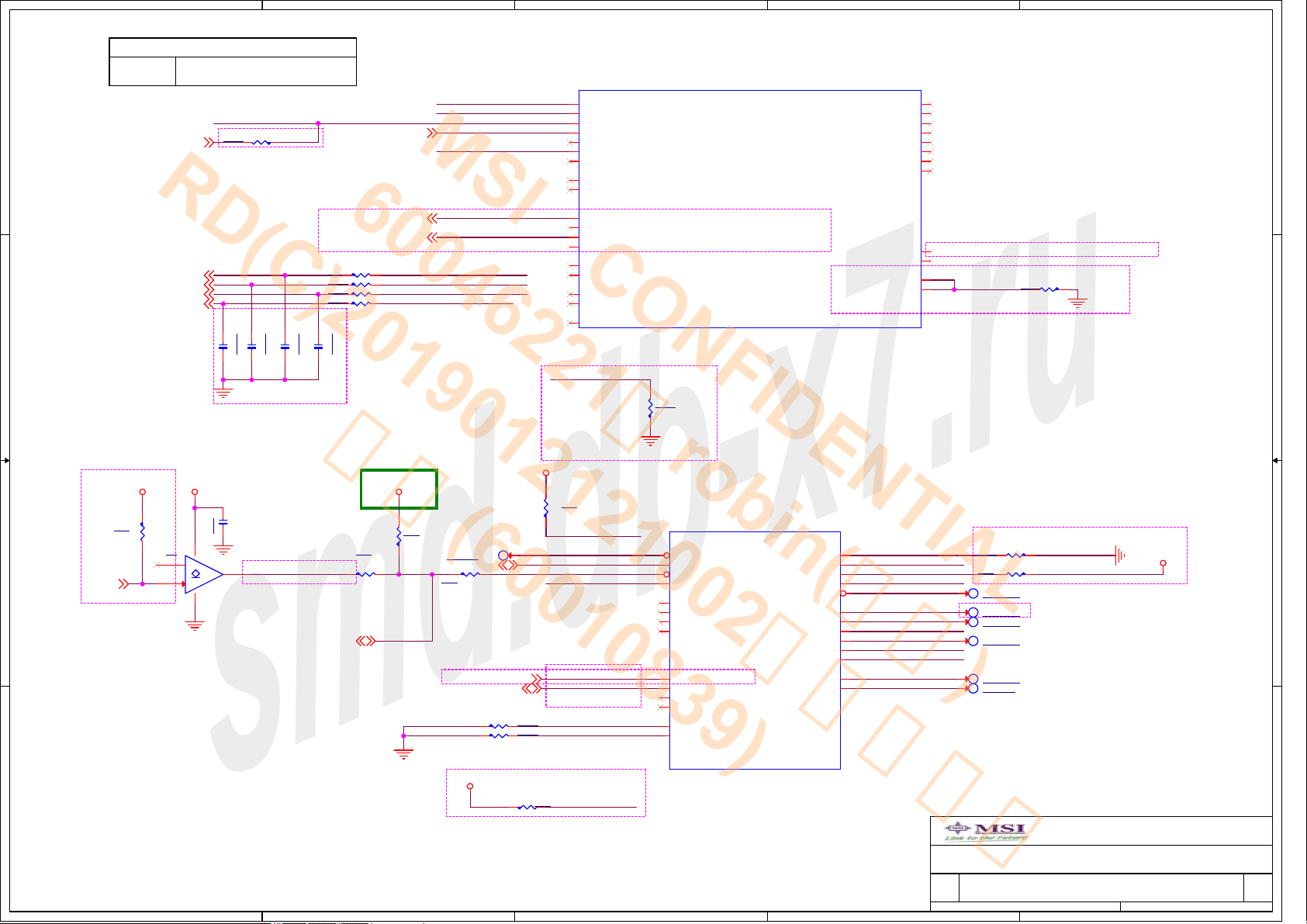

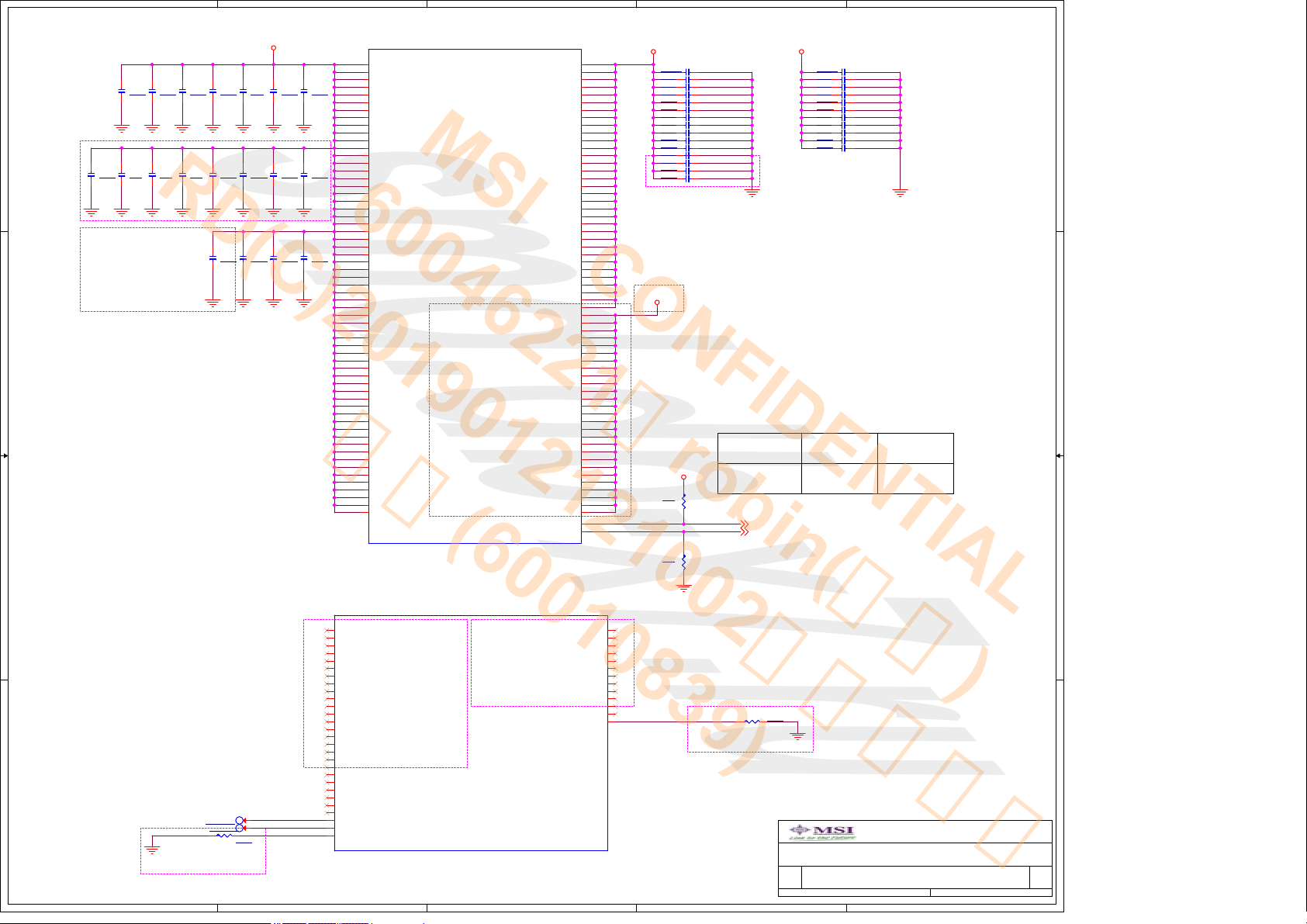

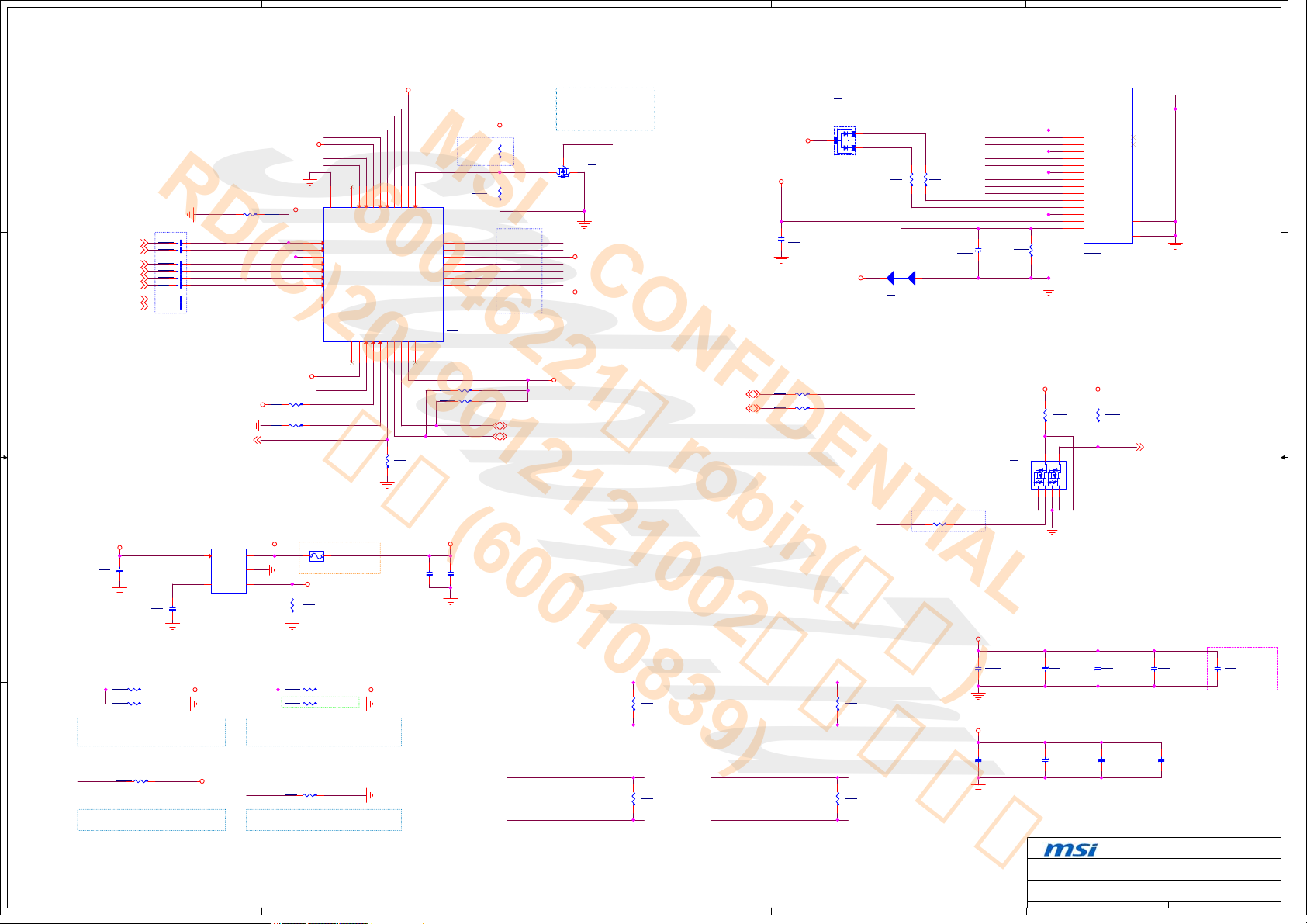

WhiskeyLake - U Processor Platform

D D

VER : B

MS-14B3KP02113

Whiskey Lake - U

(BGA1528)

4 Core

16G DDR4

SODIMM

Page 6

eDP CON

C C

HDMI CON

Page 17

Audio Combo JACK

2G GDDR5

8Gb(256Mx32bit) * 2

B B

Page 21

Page 35~36

M.2 KEY-M Combo SSD

TMDS

HP-OUT

MIC-IN

Frame Buffer

AUDIO CODEC

Realtek ALC298Q-CG

M.2 KEY-E WLAN

INTEL 9260

CNVi

CardReader

Realtek RTS5170

Page 19

Page 16

Level shift

SN75DP139

Page 17

Page 21

GPU

NVIDIA N17S-G2

Page 33~42

Page 20

Page 22

PCI-E Gen3/SATA Gen3 PCI-E Port 13,14,15,16

Channel A

DDR4

2400 MHZ

eDp

TMDS

HDA

PCIE Gen3

PCIE Gen2/USB2

CNVi

USB2

DDR CH A

eDP Port

DDI Port 1

HDA

PCIE Port 9,10,11,12

PCIE Port 7

USB 2.0 Port 10

CNVi

USB 2.0 Port 5

SATA Port 2

GT2

USB 3.0 Port 3

USB 2.0 Port 1

USB 3.0 Port 4

USB 2.0 Port 2

USB 3.0 Port 1,2

USB 2.0 Port 3

USB 3.0 Port 5,6

USB 2.0 Port 4

ME

LPC

SMBus

USB3.1 Gen1/USB2

USB3.1 Gen1/USB2

USB3.1 Gen1/USB2

USB3.1 Gen1/USB2

SPI

LPC

TPM

SLB9665

SMbus

USB3-Type-A Port1

USB3-Type-A Port2

USB3 Re-Driver*2

TUSB1002A

Page 25

USB3-Type-C Port4

Page 28

BIOS/EC ROM

W25Q128JVSIQ-HF

KBC

ENE KB9028GC

Page 23

Page 7

SPI/Share ROM

Page 18

Click PAD

Page 24

Page 24

USB3.1 Gen1/USB2 USB3-Type-C Port3

Type-C PD Controller

TI TPS25810

PS2

Page 29

Page 28

Keyboard

Page 18

FAN

Page 30

LED

Page 31

Page 27

Type-C Controller

TI TPS25810

Page 27

A A

5

Camera

Page 31

USB2

USB 2.0 Port 7

Page 03~05, 07~15

4

USB 2.0 Port 6

3

USB2

Fingerprint

Page 29

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Size Document Number Re v

Size Document Number Re v

Size Document Number Re v

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

MS-14B3

MS-14B3

MS-14B3

1

0A

0A

0A

of

157Friday, November 16, 2018

of

157Friday, November 16, 2018

of

157Friday, November 16, 2018

Page 2

A

戶服務

smd.db-x7.ru

B

C

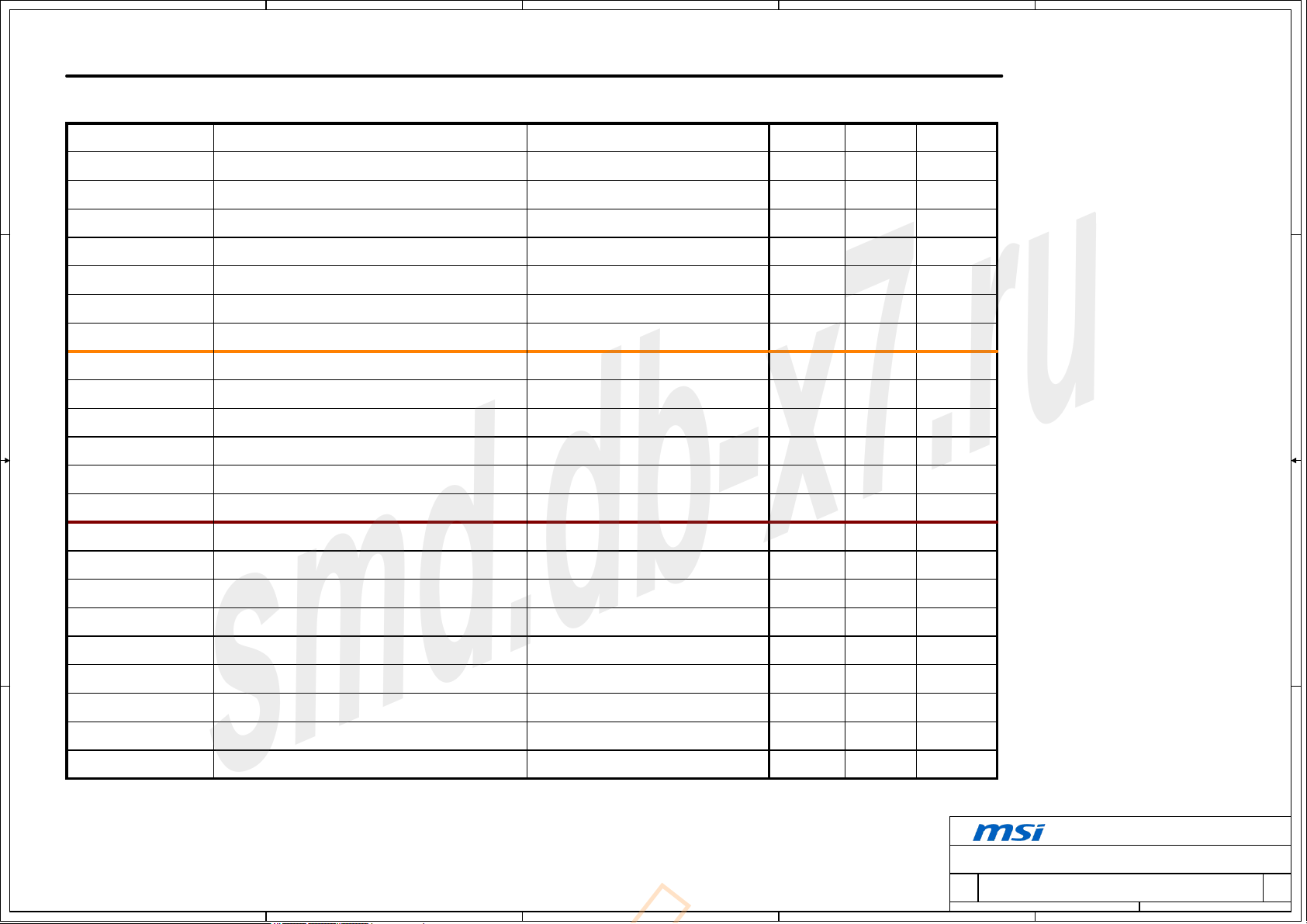

SCHEMATIC ANNOTATIONS AND BOARD INFORMATION

D

E

Voltage Rails

1 1

Voltage Description Control Signal

PWR_SRC

+5VALW 5.0V always on power rail

+3VALW

+5VSUS

+3VSUS

+1_8VSUS

2 2

+1_05VSUS

+2_5VMEM_VPP

+VCCST 1.05V power rail CPU (off in S4-S5)

+VCCPLL 1.05V power rail CPU (off in S4-S5) +VCCST

+1_2VDIMM 1.2V power rail DDR (off in S4-S5)

+VDDQC

+VCCPLL_OC +1_2VDIMM1.2V power rail CPU (off in S4-S5)

+5VRUN

AC ADAPTER OR BATTERY IN

3.3V always on power rail

5.0V power rail

3.3V power rail

1.8V power rail

1.05V power rail

2.5V power rail DDR (off in S4-S5)

5.0V switched power rail (off in S3-S5)

PWR_SRC

PWR_SRC

SUS_ON

SUS_ON

3V5VSUSPWRGD

1_8VSUSPWRGD

DIMM_ON_VPP

DIMM_ON_VPP

DIMM_ON_VDDQ

+1_2VDIMM1.2V power rail CPU DRAM (off in S4-S5)

RUND

POWER STATES

SLP_S3#SLP_S5# SLP_S4#

H

L

LL L

LL L

LL L

LL L

LL L

H

H

H

H

H

H

H

L

L

LL

LL

LL

LL

LL

H

HH

L

L

L

3 3

+3VRUN

+1_8VRUN

+VCC_IO

+VCCSTG

+0_6VTT_RUN

+VCC_SA 0.55V to 1.15V Voltage for Processor

+VCC_CORE

+VCC_GT

3.3V switched power rail (off in S3-S5 / M0)

1.8V power rail AUDIO (off in S3-S5)

1.05V rail for Processor & PCH (off in S3-S5)

1.05V power rail CPU (off in S3-S5)

0.6V DDR Termination voltage (off in S3-S5)

0.55V to 1.5V Voltage for Processor

0.55V to 1.52V Core Voltage for Processor

RUND

RUND

RUND

+VCC_IO

DDR_VTT_CTRL

VR_ON

VR_ON

VR_ON

H

H

HH

HH

H

H

HH

HH

HH

HH

L

L

L

L

L

L

L

L

4 4

Note: WHEN AC MODE, System turn on then +*VSUS will always keep high

S4( Suspend to Disk)

S3( Suspend to RAM)

S0( Full ON)

A

B

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

PLATFORM

PLATFORM

PLATFORM

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

MS-14B3

MS-14B3

MS-14B3

Date : Sheet

Date : Sheet

C

Date : Sheet

D

MICRO-STAR INT'L CO.,LTD.

of

257Friday, November 16, 2018

of

257Friday, November 16, 2018

of

257Friday, November 16, 2018

E

0A

0A

0A

Page 3

A

戶服務

smd.db-x7.ru

B

C

D

E

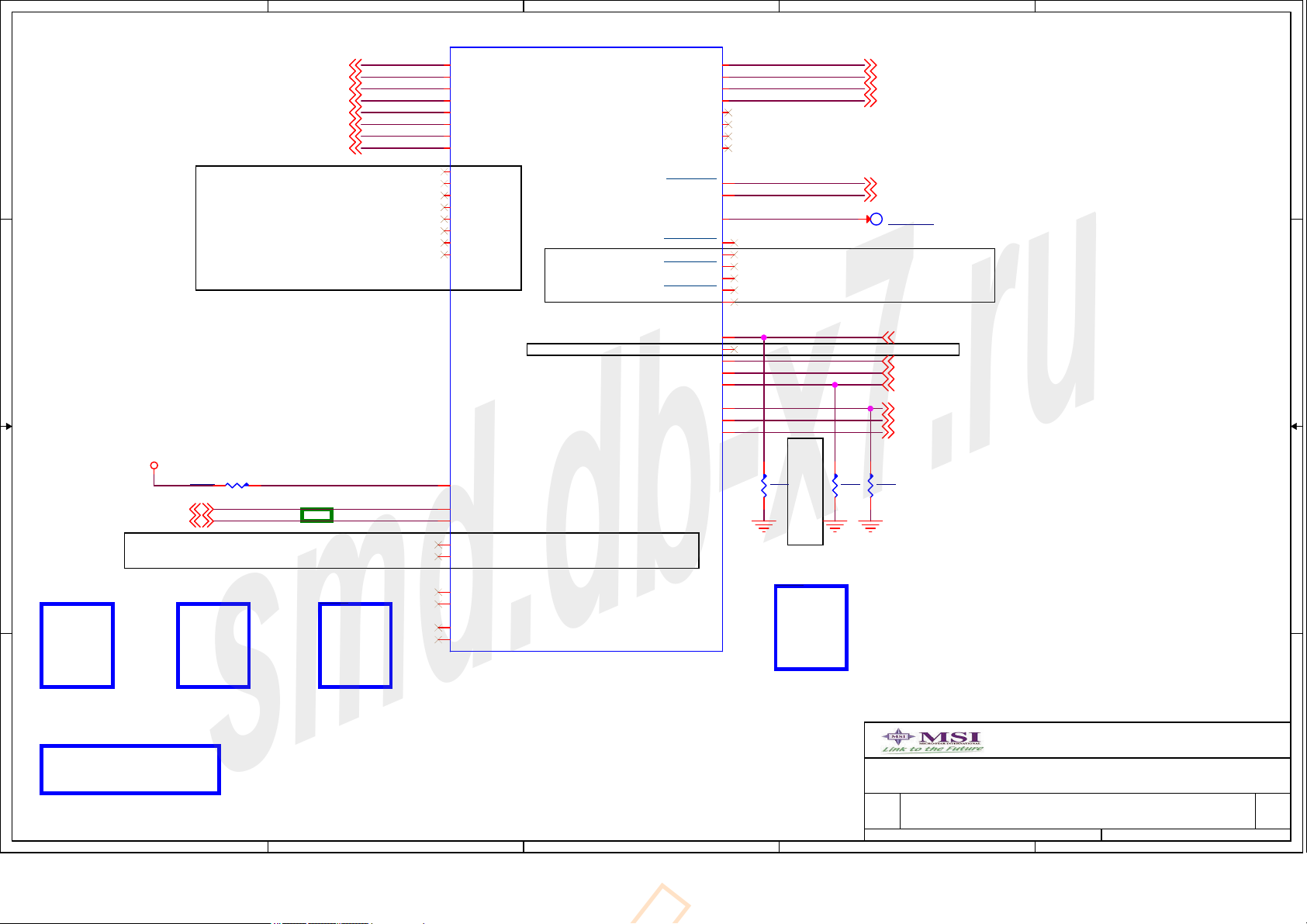

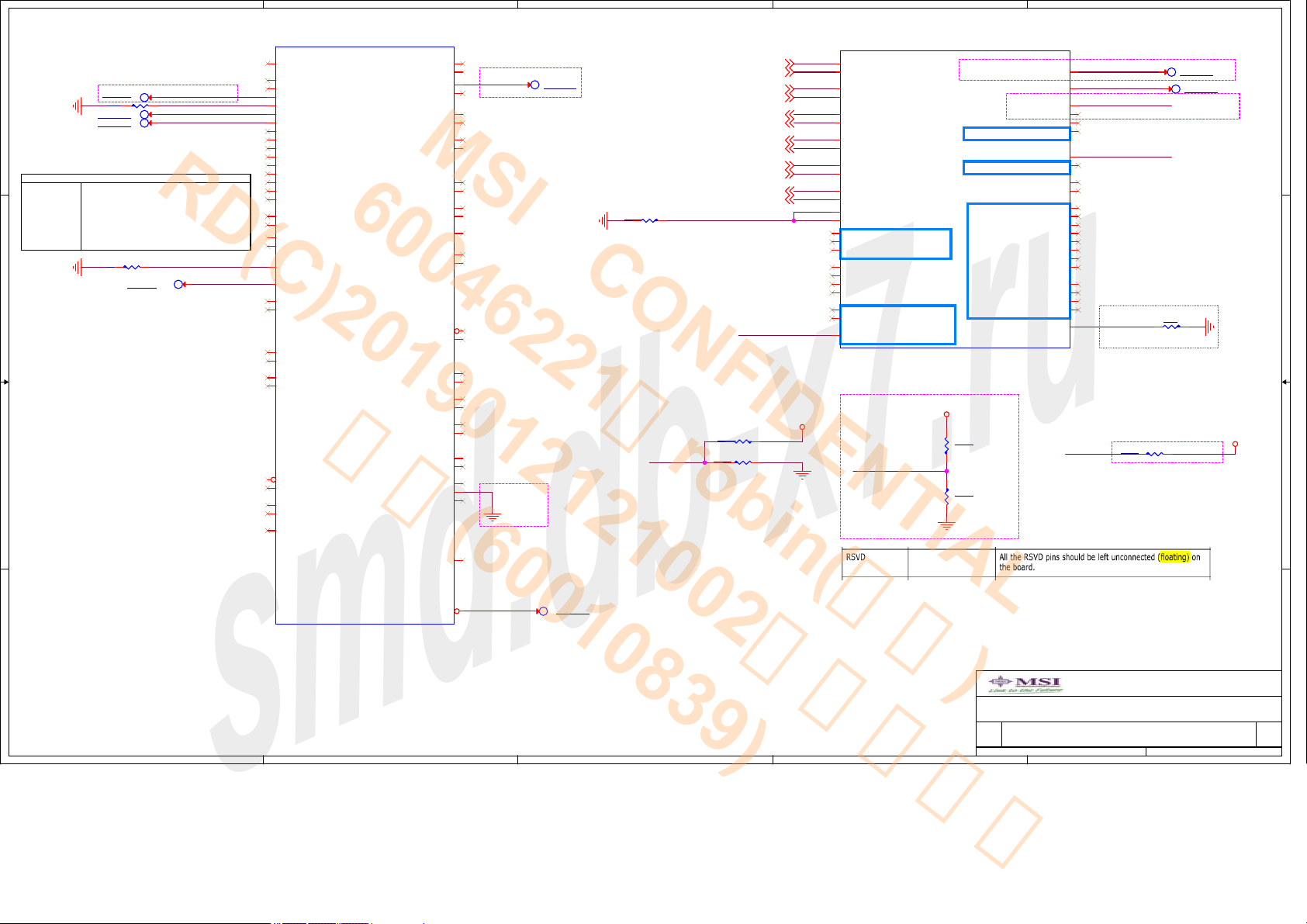

Reference 16S1

CPU1A

AL5

HDMI1_TX2_DN<17>

HDMI1_TX2_DP<17>

HDMI1_TX1_DN<17>

4 4

HDMI

DDI1

3 3

+VCC_IO

R359 24.9R1%0402

DDI1_CTRL_CLK<17>

Port B

2 2

CPU2

CPU

X_WHL-U_i5-8265U

OAC-13G3001-I06

CPU4

1 1

DDI1_CTRL_DATA<17>

Remove DDI2 #2018.08.28

CPU3

CPU

X_WHL-U_i7-8565U

OAD-13G3001-I06

HDMI1_TX1_DP<17>

HDMI1_TX0_DN<17>

HDMI1_TX0_DP<17>

HDMI1_CLK_DN<17>

HDMI1_CLK_DP<17>

Remove DDI2 #2018.08.28

Pull up on level shift page

CPU5

X_WHL-U_i3-8145U

OAB-13M1001-I06

DISP_RCOMP

CPU

DDI1_TXN_0

AL6

DDI1_TXP_0

AJ5

DDI1_TXN_1

AJ6

DDI1_TXP_1

AF6

DDI1_TXN_2

AF5

DDI1_TXP_2

AE5

DDI1_TXN_3

AE6

DDI1_TXP_3

AC4

DDI2_TXN_0

AC3

DDI2_TXP_0

AC1

DDI2_TXN_1

AC2

DDI2_TXP_1

AE4

DDI2_TXN_2

AE3

DDI2_TXP_2

AE1

DDI2_TXN_3

AE2

DDI2_TXP_3

Port C

GPP_E13/DDPB_HPD0/DISP_MISC0

GPP_E14/DDPC_HPD1/DISP_MISC1

GPP_E15/DPPD_HPD2/DISP_MISC2

GPP_E16/DPPE_HPD3/DISP_MISC3

GPP_E17/EDP_HPD/DISP_MISC4

AM6

DISP_RCOMP

CC8

GPP_E18/DPPB_CTRLCLK/CNV_BT_HOST_WAKE#

CC9

GPP_E19/DPPB_CTRLDATA

CH4

GPP_E20/DPPC_CTRLCLK

CH3

GPP_E21/DPPC_CTRLDATA

CP4

GPP_E22/DPPD_CTRLCLK

CN4

GPP_E23/DPPD_CTRLDATA

CR26

GPP_H16/DDPF_CTRLCLK

CP26

GPP_H17/DDPF_CTRLDATA

WHL-i7-8565U

A0D-8565U05-I06

1 of 20

Port B

Port C

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

EDP_TXN_2

EDP_TXP_2

EDP_TXN_3

EDP_TXP_3

EDP_AUX

EDP_AUX_P

DISP_UTILS

DDI1_AUX

DDI1_AUX_P

DDI2_AUX

DDI2_AUX_P

DDI3_AUX

DDI3_AUX_P

EDP_BKLTEN

EDP_VDDEN

EDP_BKLTCTL

CPU

INTERPOSER

X_WHISKEY LAKE,CPU INTERPOSER

OS1-16S1001-I06

A

B

C

EDP_TX0_DN

AG4

EDP_TX0_DP

AG3

EDP_TX1_DN

AG2

EDP_TX1_DP

AG1

AJ4

AJ3

AJ2

AJ1

EDP_AUX_DN

AH4

EDP_AUX_DP

AH3

EDP_DISP_UTIL

AM7

AC7

AC6

AD4

AD3

AG7

AG6

CN6

CM6

CP7

CP6

CM7

CK11

CG11

CH11

R64

100KR0402

Remove DP_HDP Pull-Down #2018.08.28

CPU6

CPU

X_WHL-U_i7-8565U

A0D-8565U05-I06

EDP_TX0_DN <16>

EDP_TX0_DP <16>

EDP_TX1_DN <16>

EDP_TX1_DP <16>

EDP_AUX_DN <16>

EDP_AUX_DP <16>

TPJNC47

Remove DDI2 #2018.08.08

HDMI_HPD <17>

KBSMI# <18>

KBSCI# <18>

EDP_HPD <16>

EDP_BKLT_EN <18>

EDP_VDDEN <16>

EDP_BKLTCTL <16>

R74

R98

100KR0402

100KR0402

Title

Title

Title

Whiskey lake U(EDP,DDI)

Whiskey lake U(EDP,DDI)

Size

Size

Size

Date: Sheet

Date: Sheet

Date: Sheet

Whiskey lake U(EDP,DDI)

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

D

Port A

eDP

DDI0

Internal pull-down with 130k ohm

Remove DP_HDP #2018.08.28

KBSMI#/SCI#

Follow MS-N1131

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MS-14B3

MS-14B3

MS-14B3

0A

0A

0A

of

of

of

357Friday, November 16, 2018

357Friday, November 16, 2018

357Friday, November 16, 2018

E

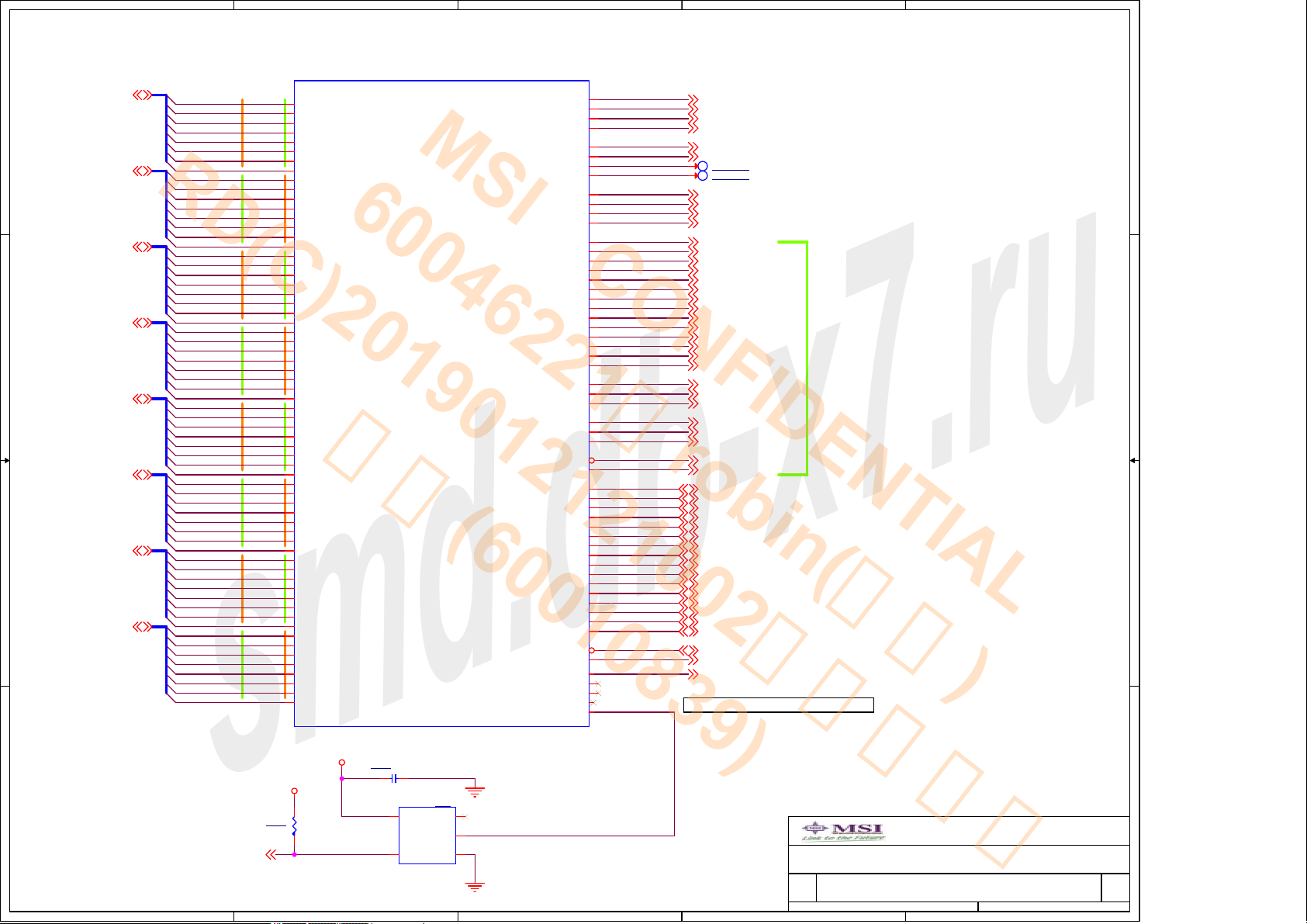

Page 4

A

MSI CONFIDENTIAL

60046221 robin(周斌)

RD(C)2019012121002客戶服務部

孫飛(60010839)

smd.db-x7.ru

B

C

D

E

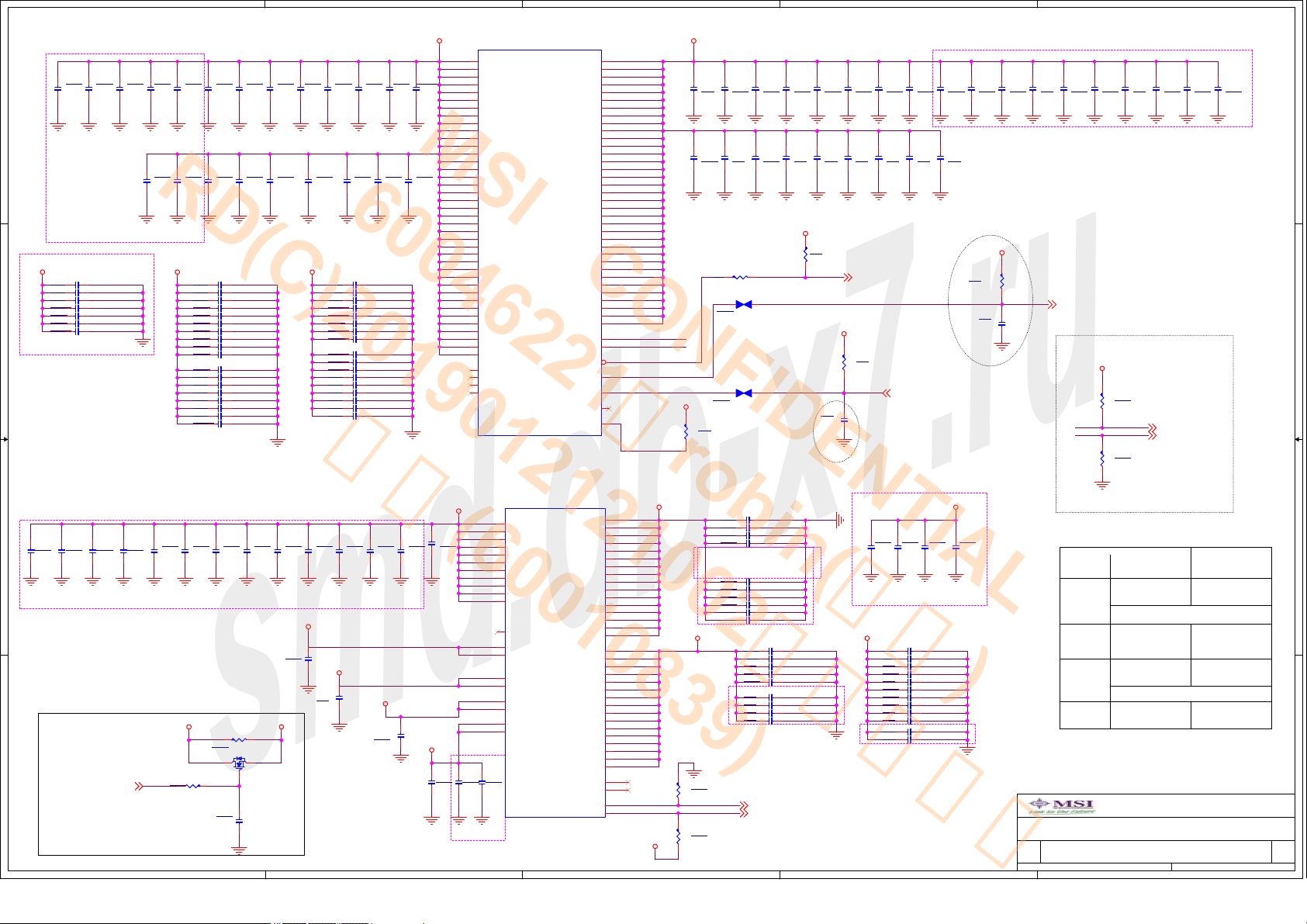

SODIMM_A

CPU1B

M_A_DQ_0_[0:7]<6>

4 4

M_A_DQ_1_[0:7]<6>

M_A_DQ_2_[0:7]<6>

M_A_DQ_3_[0:7]<6>

3 3

M_A_DQ_4_[0:7]<6>

M_A_DQ_5_[0:7]<6>

M_A_DQ_6_[0:7]<6>

2 2

M_A_DQ_7_[0:7]<6>

1 1

A

M_A_DQ_0_0

M_A_DQ_0_1

M_A_DQ_0_2

M_A_DQ_0_3

M_A_DQ_0_4

M_A_DQ_0_5

M_A_DQ_0_6

M_A_DQ_0_7

M_A_DQ_1_0

M_A_DQ_1_1

M_A_DQ_1_2

M_A_DQ_1_3

M_A_DQ_1_4

M_A_DQ_1_5

M_A_DQ_1_6

M_A_DQ_1_7

M_A_DQ_2_0

M_A_DQ_2_1

M_A_DQ_2_2

M_A_DQ_2_3

M_A_DQ_2_4

M_A_DQ_2_5

M_A_DQ_2_6

M_A_DQ_2_7

M_A_DQ_3_0

M_A_DQ_3_1

M_A_DQ_3_2

M_A_DQ_3_3

M_A_DQ_3_4

M_A_DQ_3_5

M_A_DQ_3_6

M_A_DQ_3_7

M_A_DQ_4_0

M_A_DQ_4_1

M_A_DQ_4_2

M_A_DQ_4_3

M_A_DQ_4_4

M_A_DQ_4_5

M_A_DQ_4_6

M_A_DQ_4_7

M_A_DQ_5_0

M_A_DQ_5_1

M_A_DQ_5_2

M_A_DQ_5_3

M_A_DQ_5_4

M_A_DQ_5_5

M_A_DQ_5_6

M_A_DQ_5_7

M_A_DQ_6_0

M_A_DQ_6_1

M_A_DQ_6_2

M_A_DQ_6_3

M_A_DQ_6_4

M_A_DQ_6_5

M_A_DQ_6_6

M_A_DQ_6_7

M_A_DQ_7_0

M_A_DQ_7_1

M_A_DQ_7_2

M_A_DQ_7_3

M_A_DQ_7_4

M_A_DQ_7_5

M_A_DQ_7_6

M_A_DQ_7_7

DDR_VTT_CTRL<45>

A26

DDR0_DQ_0/DDR0_DQ_0

D26

DDR0_DQ_1/DDR0_DQ_1

D28

DDR0_DQ_2/DDR0_DQ_2

C28

DDR0_DQ_3/DDR0_DQ_3

B26

DDR0_DQ_4/DDR0_DQ_4

C26

B28

A28

B30

D30

B33

D32

A30

C30

B32

C32

H37

H34

K34

K35

H36

H35

K36

K37

N36

N34

R37

R34

N37

N35

R36

R35

AN35

AN34

AR35

AR34

AN37

AN36

AR36

AR37

AU35

AU34

AW35

AW34

AU37

AU36

AW36

AW37

BA35

BA34

BC35

BC34

BA37

BA36

BC36

BC37

BE35

BE34

BG35

BG34

BE37

BE36

BG36

BG37

+3VRUN

R196

220KR0402-1

DDR0_DQ_5/DDR0_DQ_5

DDR0_DQ_6/DDR0_DQ_6

DDR0_DQ_7/DDR0_DQ_7

DDR0_DQ_8/DDR0_DQ_8

DDR0_DQ_9/DDR0_DQ_9

DDR0_DQ_10/DDR0_DQ_10

DDR0_DQ_11/DDR0_DQ_11

DDR0_DQ_12/DDR0_DQ_12

DDR0_DQ_13/DDR0_DQ_13

DDR0_DQ_14/DDR0_DQ_14

DDR0_DQ_15/DDR0_DQ_15

DDR0_DQ_16/DDR0_DQ_32

DDR0_DQ_17/DDR0_DQ_33

DDR0_DQ_18/DDR0_DQ_34

DDR0_DQ_19/DDR0_DQ_35

DDR0_DQ_20/DDR0_DQ_36

DDR0_DQ_21/DDR0_DQ_37

DDR0_DQ_22/DDR0_DQ_38

DDR0_DQ_23/DDR0_DQ_39

DDR0_DQ_24/DDR0_DQ_40

DDR0_DQ_25/DDR0_DQ_41

DDR0_DQ_26/DDR0_DQ_42

DDR0_DQ_27/DDR0_DQ_43

DDR0_DQ_28/DDR0_DQ_44

DDR0_DQ_29/DDR0_DQ_45

DDR0_DQ_30/DDR0_DQ_46

DDR0_DQ_31/DDR0_DQ_47

DDR0_DQ_32/DDR1_DQ_0

DDR0_DQ_33/DDR1_DQ_1

DDR0_DQ_34/DDR1_DQ_2

DDR0_DQ_35/DDR1_DQ_3

DDR0_DQ_36/DDR1_DQ_4

DDR0_DQ_37/DDR1_DQ_5

DDR0_DQ_38/DDR1_DQ_6

DDR0_DQ_39/DDR1_DQ_7

DDR0_DQ_40/DDR1_DQ_8

DDR0_DQ_41/DDR1_DQ_9

DDR0_DQ_42/DDR1_DQ_10

DDR0_DQ_43/DDR1_DQ_11

DDR0_DQ_44/DDR1_DQ_12

DDR0_DQ_45/DDR1_DQ_13

DDR0_DQ_46/DDR1_DQ_14

DDR0_DQ_47/DDR1_DQ_15

DDR0_DQ_48/DDR1_DQ_32

DDR0_DQ_49/DDR1_DQ_33

DDR0_DQ_50/DDR1_DQ_34

DDR0_DQ_51/DDR1_DQ_35

DDR0_DQ_52/DDR1_DQ_36

DDR0_DQ_53/DDR1_DQ_37

DDR0_DQ_54/DDR1_DQ_38

DDR0_DQ_55/DDR1_DQ_39

DDR0_DQ_56/DDR1_DQ_40

DDR0_DQ_57/DDR1_DQ_41

DDR0_DQ_58/DDR1_DQ_42

DDR0_DQ_59/DDR1_DQ_43

DDR0_DQ_60/DDR1_DQ_44

DDR0_DQ_61/DDR1_DQ_45

DDR0_DQ_62/DDR1_DQ_46

DDR0_DQ_63/DDR1_DQ_47

WHL-i7-8565U

A0D-8565U05-I06

+1_2VDIMM

B

2 of 20

C147

C0.1u25X50402

5

VCC

4

Y

DDR0_CKN_0/DDR0_CKN_0

DDR0_CKP_0/DDR0_CKP_0

DDR0_CKN_1/DDR0_CKN_1

DDR0_CKP_1/DDR0_CKP_1

DDR0_CKE_0/DDR0_CKE_0

DDR0_CKE_1/DDR0_CKE_1

DDR0_CKE_2/NC

DDR0_CKE_3/NC

DDR0_CS#_0/DDR0_CS#_0

DDR0_CS#_1/DDR0_CS#_1

DDR0_ODT_0/DDR0_ODT_0

NC/DDR0_ODT_1

DDR0_CAB_9/DDR0_MA_0

DDR0_CAB_8/DDR0_MA_1

DDR0_CAB_5/DDR0_MA_2

NC/DDR0_MA_3

NC/DDR0_MA_4

DDR0_CAA_0/DDR0_MA_5

DDR0_CAA_2/DDR0_MA_6

DDR0_CAA_4/DDR0_MA_7

DDR0_CAA_3/DDR0_MA_8

DDR0_CAA_1/DDR0_MA_9

DDR0_CAB_7/DDR0_MA_10

DDR0_CAA_7/DDR0_MA_11

DDR0_CAA_6/DDR0_MA_12

DDR0_CAB_0/DDR0_MA_13

DDR0_CAB_2/DDR0_MA_14

DDR0_CAB_1/DDR0_MA_15

DDR0_CAB_3/DDR0_MA_16

DDR0_CAB_4/DDR0_BA_0

DDR0_CAB_6/DDR0_BA_1

DDR0_CAA_5/DDR0_BG_0

DDR0_CAA_8/DDR0_ACT#

DDR0_CAA_9/DDR0_BG_1

DDR0_DQSN_0/DDR0_DQSN_0

DDR0_DQSP_0/DDR0_DQSP_0

DDR0_DQSN_1/DDR0_DQSN_1

DDR0_DQSP_1/DDR0_DQSP_1

DDR0_DQSN_2/DDR0_DQSN_4

DDR0_DQSP_2/DDR0_DQSP_4

DDR0_DQSN_3/DDR0_DQSN_5

DDR0_DQSP_3/DDR0_DQSP_5

DDR0_DQSN_4/DDR1_DQSN_0

DDR0_DQSP_4/DDR1_DQSP_0

DDR0_DQSN_5/DDR1_DQSN_1

DDR0_DQSP_5/DDR1_DQSP_1

DDR0_DQSN_6/DDR1_DQSN_4

DDR0_DQSP_6/DDR1_DQSP_4

DDR0_DQSN_7/DDR1_DQSN_5

DDR0_DQSP_7/DDR1_DQSP_5

NC/DDR0_ALERT#

DDR_VREF_CA

DDR0_VREF_DQ_0

DDR0_VREF_DQ_1

DDR1_VREF_DQ

U14

1

GND

NC

2

A

3

DDR_PG_CTRL

SN74AUP1G07DCKR_SC70-5-RH

NC/DDR0_PAR

DDR_VTT_CTL

V32

V31

T32

T31

U36

U37

U34

U35

AE32

AF32

AE31

AF31

AC37

AC36

AC34

AC35

AA35

AB35

AA37

AA36

AB34

W36

Y31

W34

AA34

AC32

AC31

AB32

Y32

W32

AB31

V34

V35

W35

C27

D27

D31

C31

J35

J34

P34

P35

AP35

AP34

AV34

AV35

BB35

BB34

BF34

BF35

W37

W31

F36

D35

D37

E36

C35

C

M_A_CLK_DDRN0 <6>

M_A_CLK_DDRP0 <6>

M_A_CLK_DDRN1 <6>

M_A_CLK_DDRP1 <6>

M_A_CKE0 <6>

M_A_CKE1 <6>

TPJNC59

TPJNC60

M_A_CSN0 <6>

M_A_CSN1 <6>

M_A_ODT0 <6>

M_A_ODT1 <6>

M_A_A0 <6>

M_A_A1 <6>

M_A_A2 <6>

M_A_A3 <6>

M_A_A4 <6>

M_A_A5 <6>

M_A_A6 <6>

M_A_A7 <6>

M_A_A8 <6>

M_A_A9 <6>

M_A_A10 <6>

M_A_A11 <6>

M_A_A12 <6>

M_A_A13 <6>

M_A_A14_WEN <6>

M_A_A15_CASN <6>

M_A_A16_RASN <6>

M_A_BA0 <6>

M_A_BA1 <6>

M_A_BG0 <6>

M_A_ACTN <6>

M_A_BG1 <6>

M_A_DQS_DN0 <6>

M_A_DQS_DP0 <6>

M_A_DQS_DN1 <6>

M_A_DQS_DP1 <6>

M_A_DQS_DN2 <6>

M_A_DQS_DP2 <6>

M_A_DQS_DN3 <6>

M_A_DQS_DP3 <6>

M_A_DQS_DN4 <6>

M_A_DQS_DP4 <6>

M_A_DQS_DN5 <6>

M_A_DQS_DP5 <6>

M_A_DQS_DN6 <6>

M_A_DQS_DP6 <6>

M_A_DQS_DN7 <6>

M_A_DQS_DP7 <6>

DDR0_A_ALERTN <6>

DDR0_A_PARITY <6>

+VREF_DDR_CA <6>

CLK enable

CTRL

CLK

CMD

Strobe

Alert

CMD

Remove DDR1_VREF_DQ #2018.08.28

14B3 only supprot DDR0

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Whiskey lake (DDR4)CHA

Whiskey lake (DDR4)CHA

Whiskey lake (DDR4)CHA

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

Date : Sheet

Date : Sheet

Date : Sheet

D

MS-14B3

MS-14B3

MS-14B3

MICRO-STAR INT'L CO.,LTD.

457Friday, November 16, 2018

457Friday, November 16, 2018

457Friday, November 16, 2018

E

0A

0A

0A

of

of

of

Page 5

A

MSI CONFIDENTIAL

60046221 robin(周斌)

RD(C)2019012121002客戶服務部

孫飛(60010839)

smd.db-x7.ru

B

C

D

E

SODIMM_B

CPU1C

J22

DDR1_DQ_0/DDR0_DQ_16

H25

4 4

3 3

2 2

1 1

A

DDR1_DQ_1/DDR0_DQ_17

G22

DDR1_DQ_2/DDR0_DQ_18

H22

DDR1_DQ_3/DDR0_DQ_19

F25

J25

G25

F22

D22

C22

C24

D24

A22

B22

A24

B24

G31

G32

H29

H28

G28

G29

H31

H32

L31

L32

N29

N28

L28

L29

N31

N32

AJ29

AJ30

AM32

AM31

AM30

AM29

AJ31

AJ32

AR31

AR32

AV30

AV29

AR30

AR29

AV32

AV31

BA32

BA31

BD31

BD32

BA30

BA29

BD29

BD30

BG31

BG32

BK32

BK31

BG29

BG30

BK30

BK29

DDR1_DQ_4/DDR0_DQ_20

DDR1_DQ_5/DDR0_DQ_21

DDR1_DQ_6/DDR0_DQ_22

DDR1_DQ_7/DDR0_DQ_23

DDR1_DQ_8/DDR0_DQ_24

DDR1_DQ_9/DDR0_DQ_25

DDR1_DQ_10/DDR0_DQ_26

DDR1_DQ_11/DDR0_DQ_27

DDR1_DQ_12/DDR0_DQ_28

DDR1_DQ_13/DDR0_DQ_29

DDR1_DQ_14/DDR0_DQ_30

DDR1_DQ_15/DDR0_DQ_31

DDR1_DQ_16/DDR0_DQ_48

DDR1_DQ_17/DDR0_DQ_49

DDR1_DQ_18/DDR0_DQ_50

DDR1_DQ_19/DDR0_DQ_51

DDR1_DQ_20/DDR0_DQ_52

DDR1_DQ_21/DDR0_DQ_53

DDR1_DQ_22/DDR0_DQ_54

DDR1_DQ_23/DDR0_DQ_55

DDR1_DQ_24/DDR0_DQ_56

DDR1_DQ_25/DDR0_DQ_57

DDR1_DQ_26/DDR0_DQ_58

DDR1_DQ_27/DDR0_DQ_59

DDR1_DQ_28/DDR0_DQ_60

DDR1_DQ_29/DDR0_DQ_61

DDR1_DQ_30/DDR0_DQ_62

DDR1_DQ_31/DDR0_DQ_63

DDR1_DQ_32/DDR1_DQ_16

DDR1_DQ_33/DDR1_DQ_17

DDR1_DQ_34/DDR1_DQ_18

DDR1_DQ_35/DDR1_DQ_19

DDR1_DQ_36/DDR1_DQ_20

DDR1_DQ_37/DDR1_DQ_21

DDR1_DQ_38/DDR1_DQ_22

DDR1_DQ_39/DDR1_DQ_23

DDR1_DQ_40/DDR1_DQ_24

DDR1_DQ_41/DDR1_DQ_25

DDR1_DQ_42/DDR1_DQ_26

DDR1_DQ_43/DDR1_DQ_27

DDR1_DQ_44/DDR1_DQ_28

DDR1_DQ_45/DDR1_DQ_29

DDR1_DQ_46/DDR1_DQ_30

DDR1_DQ_47/DDR1_DQ_31

DDR1_DQ_48/DDR1_DQ_48

DDR1_DQ_49/DDR1_DQ_49

DDR1_DQ_50/DDR1_DQ_50

DDR1_DQ_51/DDR1_DQ_51

DDR1_DQ_52/DDR1_DQ_52

DDR1_DQ_53/DDR1_DQ_53

DDR1_DQ_54/DDR1_DQ_54

DDR1_DQ_55/DDR1_DQ_55

DDR1_DQ_56/DDR1_DQ_56

DDR1_DQ_57/DDR1_DQ_57

DDR1_DQ_58/DDR1_DQ_58

DDR1_DQ_59/DDR1_DQ_59

DDR1_DQ_60/DDR1_DQ_60

DDR1_DQ_61/DDR1_DQ_61

DDR1_DQ_62/DDR1_DQ_62

DDR1_DQ_63/DDR1_DQ_63

WHL-i7-8565U

A0D-8565U05-I06

3 of 20

B

DDR1_CKN_0/DDR1_CKN_0

DDR1_CKP_0/DDR1_CKP_0

DDR1_CKN_1/DDR1_CKN_1

DDR1_CKP_1/DDR1_CKP_1

DDR1_CKE_0/DDR1_CKE_0

DDR1_CKE_1/DDR1_CKE_1

DDR1_CKE_2/NC

DDR1_CKE_3/NC

DDR1_CS#_0/DDR1_CS#_0

DDR1_CS#_1/DDR1_CS#_1

DDR1_ODT_0/DDR1_ODT_0

NC/DDR1_ODT_1

DDR1_CAB_9/DDR1_MA_0

DDR1_CAB_8/DDR1_MA_1

DDR1_CAB_5/DDR1_MA_2

NC/DDR1_MA_3

NC/DDR1_MA_4

DDR1_CAA_0/DDR1_MA_5

DDR1_CAA_2/DDR1_MA_6

DDR1_CAA_4/DDR1_MA_7

DDR1_CAA_3/DDR1_MA_8

DDR1_CAA_1/DDR1_MA_9

DDR1_CAB_7/DDR1_MA_10

DDR1_CAA_7/DDR1_MA_11

DDR1_CAA_6/DDR1_MA_12

DDR1_CAB_0/DDR1_MA_13

DDR1_CAB_2/DDR1_MA_14

DDR1_CAB_1/DDR1_MA_15

DDR1_CAB_3/DDR1_MA_16

DDR1_CAB_4/DDR1_BA_0

DDR1_CAB_6/DDR1_BA_1

DDR1_CAA_5/DDR1_BG_0

DDR1_CAA_9/DDR1_BG_1

DDR1_CAA_8/DDR1_ACT#

DDR1_DQSN_0/DDR0_DQSN_2

DDR1_DQSP_0/DDR0_DQSP_2

DDR1_DQSN_1/DDR0_DQSN_3

DDR1_DQSP_1/DDR0_DQSP_3

DDR1_DQSN_2/DDR0_DQSN_6

DDR1_DQSP_2/DDR0_DQSP_6

DDR1_DQSN_3/DDR0_DQSN_7

DDR1_DQSP_3/DDR0_DQSP_7

DDR1_DQSN_4/DDR1_DQSN_2

DDR1_DQSP_4/DDR1_DQSP_2

DDR1_DQSN_5/DDR1_DQSN_3

DDR1_DQSP_5/DDR1_DQSP_3

DDR1_DQSN_6/DDR1_DQSN_6

DDR1_DQSP_6/DDR1_DQSP_6

DDR1_DQSN_7/DDR1_DQSN_7

DDR1_DQSP_7/DDR1_DQSP_7

NC/DDR1_ALERT#

NC/DDR1_PAR

DRAM_RESET#

DDR_RCOMP_0

DDR_RCOMP_1

DDR_RCOMP_2

AF28

AF29

AE28

AE29

T28

T29

V28

V29

AL37

AL35

AL36

AL34

AG36

AG35

AF34

AG37

AE35

AF35

AE37

AC29

AE36

AB29

AG34

AC28

AB28

AK35

AJ35

AK34

AJ34

AJ37

AJ36

W29

Y28

W28

H24

G24

C23

D23

G30

H30

L30

N30

AL31

AL30

AU31

AU30

BC31

BC30

BH31

BH30

Y29

AE34

BU31

BN28

BN27

BN29

DDR_RCOMP_0

DDR_RCOMP_1

DDR_RCOMP_2

C

Remove DDR1 #2018.08.28

14B3 only supprot DIMMA

+1_2VDIMM

R207

470R1%0402

DDR4_DRAMRST#

R417 121R1%0402

R407 80.6R1%0402

R428 100R1%0402

Width 15 mils, Spacing 20, < 500 mils

D

R208 0R1%0402

Title

Title

Title

Whiskey lake (DDR4)CHB

Whiskey lake (DDR4)CHB

Whiskey lake (DDR4)CHB

Size

Size

Size

Document Number R e v

Document Number R e v

Document Number R e v

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MS-14B3

MS-14B3

MS-14B3

DDR4_DRAMRST#_R <6>

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

557Friday, November 16, 2018

557Friday, November 16, 2018

557Friday, November 16, 2018

E

0A

0A

0A

of

of

of

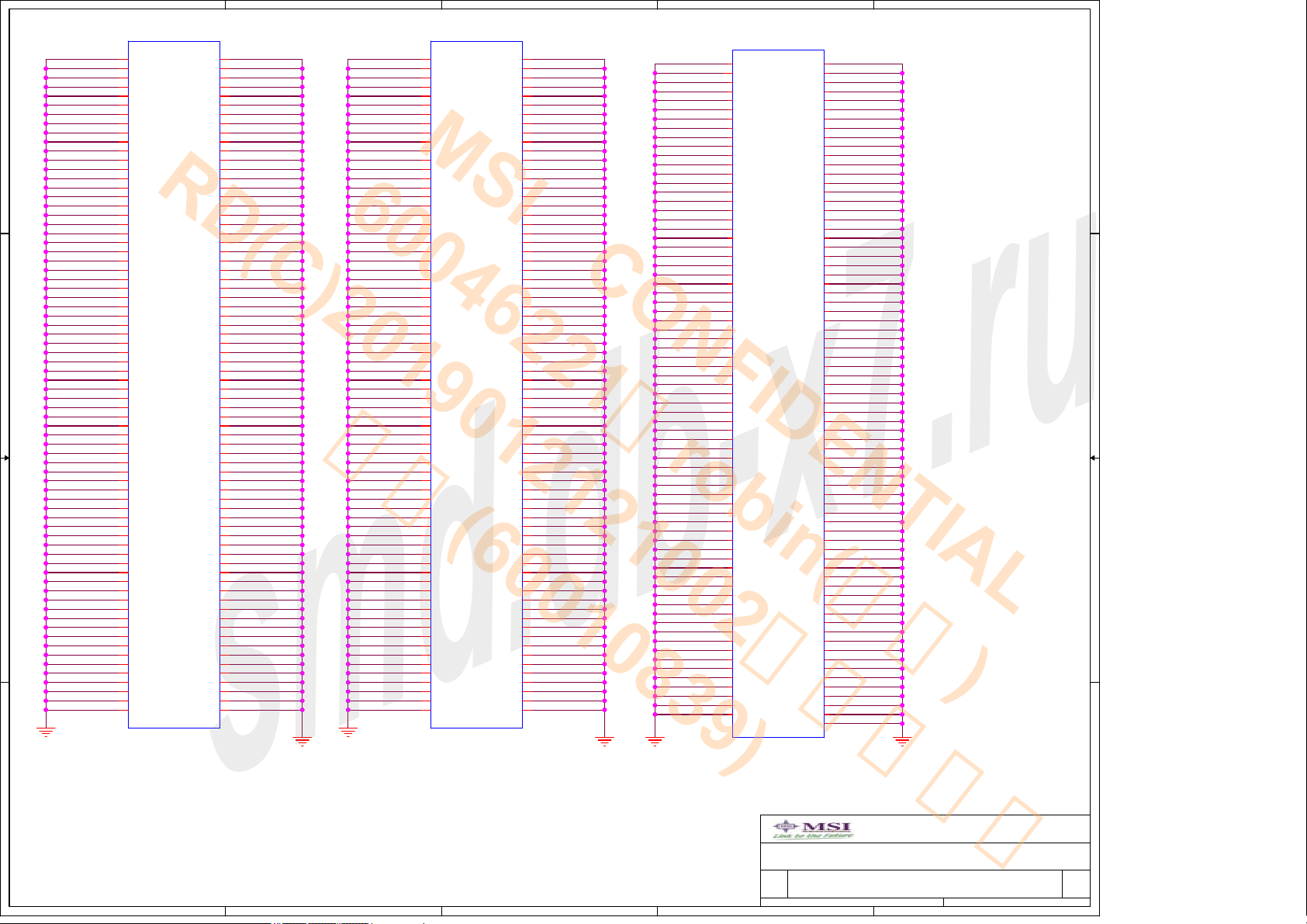

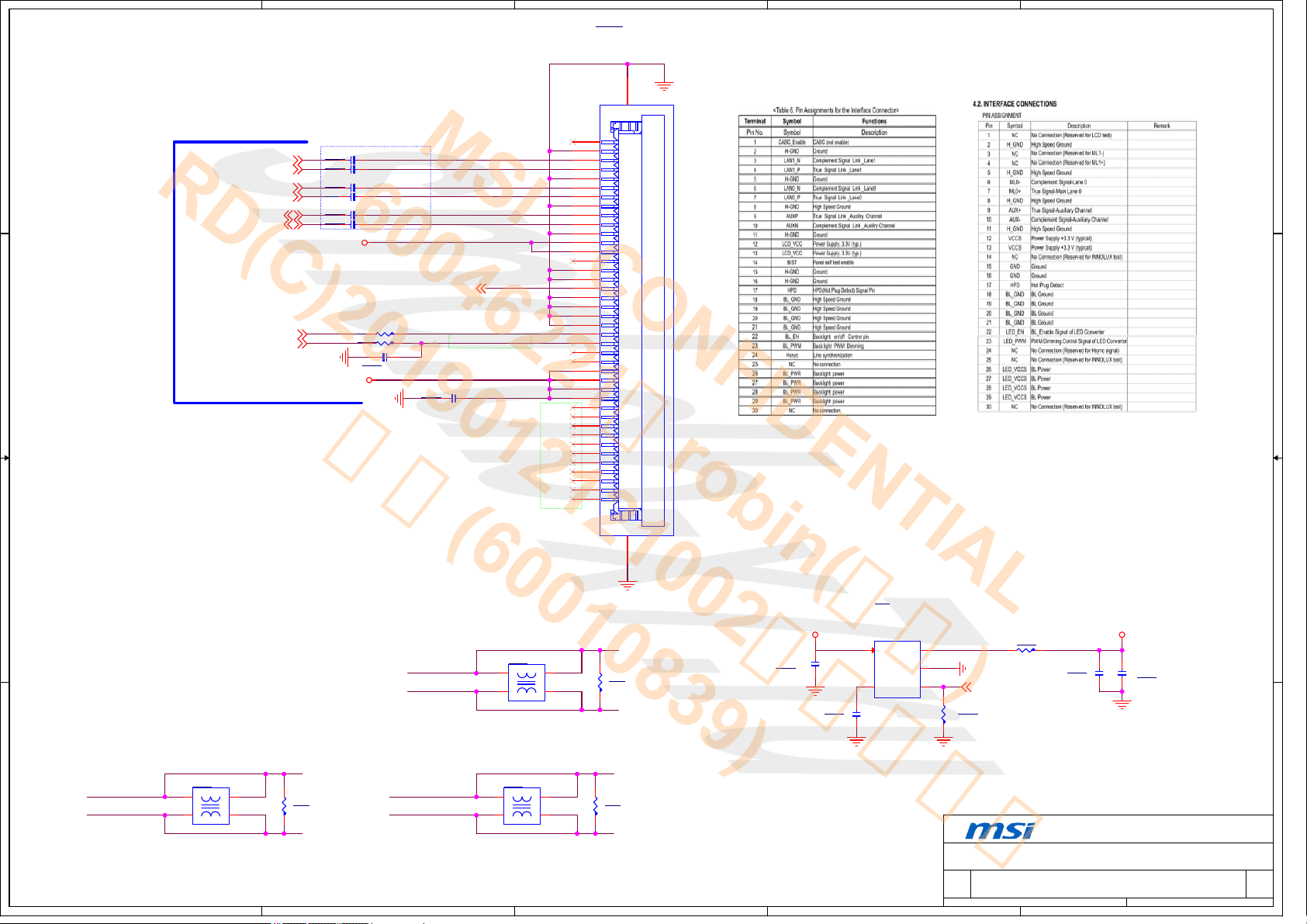

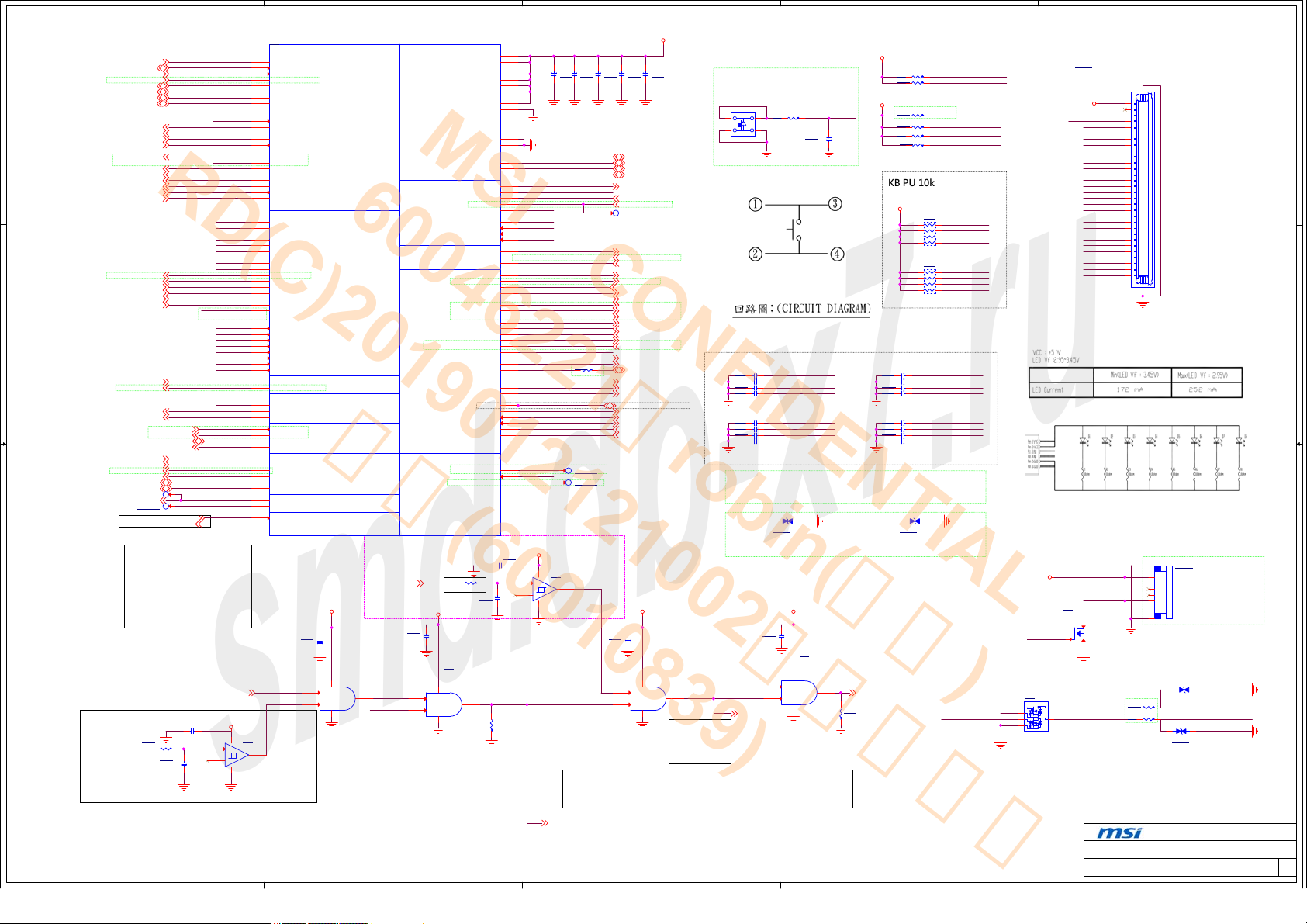

Page 6

SODIMM_A

MSI CONFIDENTIAL

60046221 robin(周斌)

RD(C)2019012121002客戶服務部

孫飛(60010839)

smd.db-x7.ru

5

DDR4 SODIMM Interleave (IL)

4

Follow 14B1 to change location for placement #2018.08.22

3

2

1

VDDQ

M_A_DQ_0_[0:7]<4>

D D

M_A_DQ_1_[0:7]<4>

M_A_DQ_2_[0:7]<4>

M_A_DQ_3_[0:7]<4>

M_A_DQ_4_[0:7]<4>

C C

M_A_DQ_5_[0:7]<4>

M_A_DQ_6_[0:7]<4>

M_A_DQ_7_[0:7]<4>

B B

A A

M_A_DQ_0_4

M_A_DQ_0_2

M_A_DQ_0_3

M_A_DQ_0_1

M_A_DQ_0_0

M_A_DQ_0_5

M_A_DQ_0_6

M_A_DQ_0_7

M_A_DQ_1_5

M_A_DQ_1_2

M_A_DQ_1_1

M_A_DQ_1_7

M_A_DQ_1_4

M_A_DQ_1_0

M_A_DQ_1_3

M_A_DQ_1_6

M_A_DQ_2_5

M_A_DQ_2_4

M_A_DQ_2_6

M_A_DQ_2_3

M_A_DQ_2_0

M_A_DQ_2_1

M_A_DQ_2_2

M_A_DQ_2_7

M_A_DQ_3_4

M_A_DQ_3_5

M_A_DQ_3_6

M_A_DQ_3_7

M_A_DQ_3_1

M_A_DQ_3_0

M_A_DQ_3_2

M_A_DQ_3_3

M_A_DQ_4_5

M_A_DQ_4_1

M_A_DQ_4_3

M_A_DQ_4_2

M_A_DQ_4_0

M_A_DQ_4_4

M_A_DQ_4_6

M_A_DQ_4_7

M_A_DQ_5_1

M_A_DQ_5_0

M_A_DQ_5_6

M_A_DQ_5_7

M_A_DQ_5_3

M_A_DQ_5_5

M_A_DQ_5_2

M_A_DQ_5_4

M_A_DQ_6_0

M_A_DQ_6_1

M_A_DQ_6_6

M_A_DQ_6_3

M_A_DQ_6_5

M_A_DQ_6_4

M_A_DQ_6_2

M_A_DQ_6_7

M_A_DQ_7_7

M_A_DQ_7_5

M_A_DQ_7_4

M_A_DQ_7_3

M_A_DQ_7_1

M_A_DQ_7_6

M_A_DQ_7_2

M_A_DQ_7_0

M_A_BG0<4>

M_A_BG1<4>

Width 20 mils, Spacing 20

+VREF_DDR_CA<4>

5

SOCKET1A

8

DQ0

7

DQ1

20

DQ2

21

DQ3

4

DQ4

3

DQ5

16

DQ6

17

DQ7

28

DQ8

29

DQ9

41

DQ10

42

DQ11

24

DQ12

25

DQ13

38

DQ14

37

DQ15

50

DQ16

49

DQ17

62

DQ18

63

DQ19

46

DQ20

45

DQ21

58

DQ22

59

DQ23

70

DQ24

71

DQ25

83

DQ26

84

DQ27

66

DQ28

67

DQ29

79

DQ30

80

DQ31

174

DQ32

173

DQ33

187

DQ34

186

DQ35

170

DQ36

169

DQ37

183

DQ38

182

DQ39

195

DQ40

194

DQ41

207

DQ42

208

DQ43

191

DQ44

190

DQ45

203

DQ46

204

DQ47

216

DQ48

215

DQ49

228

DQ50

229

DQ51

211

DQ52

212

DQ53

224

DQ54

225

DQ55

237

DQ56

236

DQ57

249

DQ58

250

DQ59

232

DQ60

233

DQ61

245

DQ62

246

DQ63

115

BG0

113

BG1

DDR4SODIMM-260PS_BLACK-HF-20

N13-2600220-L41

DDR4_SODIMM260P_H4_5

C140

C0.022u25X0402

R170

24.9R1%0402

GND

144

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14/WE#

A15/CAS#

A16/RAS#

BA0

BA1

CS0#

CS1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

SCL

SDA

ODT0

ODT1

DM0#/DBIO#

DM1#/DBI1#

DM2#/DBI2#

DM3#/DBI3#

DM4#/DBI4#

DM5#/DBI5#

DM6#/DBI6#

DM7#/DBI7#

DBI8#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

DQS8#

SA0

SA1

RFU

M_A_A0 <4>

133

M_A_A1 <4>

132

M_A_A2 <4>

131

M_A_A3 <4>

128

M_A_A4 <4>

126

M_A_A5 <4>

127

M_A_A6 <4>

122

M_A_A7 <4>

125

M_A_A8 <4>

121

M_A_A9 <4>

146

M_A_A10 <4>

120

M_A_A11 <4>

119

M_A_A12 <4>

158

M_A_A13 <4>

151

M_A_A14_WEN <4>

156

M_A_A15_CASN <4>

152

M_A_A16_RASN <4>

150

M_A_BA0 <4>

145

M_A_BA1 <4>

149

M_A_CSN0 <4>

157

M_A_CSN1 <4>

137

M_A_CLK_DDRP0 <4>

139

138

140

109

110

253

254

155

161

12

33

54

75

178

199

220

241

96

13

34

55

76

179

200

221

242

97

11

32

53

74

177

198

219

240

95

256

260

166

SA0_DIMA0_0_0

SA1_DIMA0_0_0

SA2_DIMA0_0_0

M_A_CLK_DDRN0 <4>

M_A_CLK_DDRP1 <4>

M_A_CLK_DDRN1 <4>

M_A_CKE0 <4>

M_A_CKE1 <4>

SMBCLK_DIMM_Q <7,29>

SMBDATA_DIMM_Q <7,29>

M_A_ODT0 <4>

M_A_ODT1 <4>

+1_2VDIMM

M_A_DQS_DP0 <4>

M_A_DQS_DP1 <4>

M_A_DQS_DP2 <4>

M_A_DQS_DP3 <4>

M_A_DQS_DP4 <4>

M_A_DQS_DP5 <4>

M_A_DQS_DP6 <4>

M_A_DQS_DP7 <4>

M_A_DQS_DN0 <4>

M_A_DQS_DN1 <4>

M_A_DQS_DN2 <4>

M_A_DQS_DN3 <4>

M_A_DQS_DN4 <4>

M_A_DQS_DN5 <4>

M_A_DQS_DN6 <4>

M_A_DQS_DN7 <4>

1 2

TPJNC64 X_0402

1 2

TPJNC63 X_0402

1 2

TPJNC65 X_0402

GND

M_A_DQS_DP8

M_A_DQS_DN8

+2_5VMEM_VPP

Width 20 mils, Spacing 20

Close SODIMM

+0_6VTT_RUN

+1_2VDIMM

R494

240R1%0402

+1_2VDIMM

R493

240R1%0402

GND

GND

GND

2A

1A

+VREF_DDR_CA_R

C647X_C10u10X5-HF

C643C1u25X50402-HF

750mA

A0 ( 0 0 0 )

+1_2VDIMM

R177

GND

1KR1%0402

R182

1KR1%0402

4

R176 2R1%0402

X_C0.1u25X50402-HF

+VREF_DDR_CA_R

C143

GND

SOCKET1B

111

VDD-1

112

VDD-2

117

VDD-3

118

VDD-4

123

VDD-5

124

VDD-6

129

VDD-7

130

VDD-8

135

VDD-9

136

VDD-10

141

VDD-11

142

VDD-12

147

VDD-13

148

VDD-14

153

VDD-15

154

159

160

163

257

259

164

258

167

168

171

172

175

176

180

181

184

185

188

189

192

193

196

197

201

202

205

206

209

210

213

214

217

218

222

223

226

227

230

231

234

235

238

239

243

244

247

248

251

252

261

262

GND GND

C1/CS3#/NC10

VDD-16

VDD-17

VDD-18

VDD-19

VPP-1

VPP-2

VREF_CA

VTT

VSS-53

VSS-54

VSS-55

VSS-56

VSS-57

VSS-58

VSS-59

VSS-60

VSS-61

VSS-62

VSS-63

VSS-64

VSS-65

VSS-66

VSS-67

VSS-68

VSS-69

VSS-70

VSS-71

VSS-72

VSS-73

VSS-74

VSS-75

VSS-76

VSS-77

VSS-78

VSS-79

VSS-80

VSS-81

VSS-82

VSS-83

VSS-84

VSS-85

VSS-86

VSS-87

VSS-88

VSS-89

VSS-90

VSS-91

VSS-92

VSS-93

VSS-94

261

262

MEC1

MEC2

MEC1

MEC2

DDR4SODIMM-260PS_BLACK-HF-20

N13-2600220-L41

DDR4_SODIMM260P_H4_5

3

VDDSPD

CB0/NC4

CB1/NC3

CB2/NC6

CB3/NC8

CB4/NC2

CB5/NC1

CB6/NC5

CB7/NC7

C0/CS2#/NC9

RESET#

ACT#

ALERT#

EVENT#

Parity

VSS-1

VSS-2

VSS-3

VSS-4

VSS-5

VSS-6

VSS-7

VSS-8

VSS-9

VSS-10

VSS-11

VSS-12

VSS-13

VSS-14

VSS-15

VSS-16

VSS-17

VSS-18

VSS-19

VSS-20

VSS-21

VSS-22

VSS-23

VSS-24

VSS-25

VSS-26

VSS-27

VSS-28

VSS-29

VSS-30

VSS-31

VSS-32

VSS-33

VSS-34

VSS-35

VSS-36

VSS-37

VSS-38

VSS-39

VSS-40

VSS-41

VSS-42

VSS-43

VSS-44

VSS-45

VSS-46

VSS-47

VSS-48

VSS-49

VSS-50

VSS-51

VSS-52

255

92

91

101

105

DIMM ECC check bits

88

87

100

104

162

165

108

114

116

134

Delete. 20170920

143

1

2

5

6

9

10

14

15

18

19

22

23

26

27

30

31

35

36

39

40

43

44

47

48

51

52

56

57

60

61

64

65

68

69

72

73

77

78

81

82

85

86

89

90

93

94

98

99

102

103

106

107

Close to VDD pin

+3VRUN+1_2VDIMM

< 200 mils

C639 X_C0.1u25X50402-HF

DDR4_DRAMRST#_R <5>

M_A_ACTN <4>

DDR0_A_ALERTN <4>

DDR0_A_PARITY <4>

GND

VTT

+0_6VTT_RUN

VDDSPD

+1_2VDIMM

C615 C1u25X50402-HF

C609 C1u25X50402-HF

C605 C1u25X50402-HF

C600 C1u25X50402-HF

C616 C1u25X50402-HF

C613 C1u25X50402-HF

C607 C1u25X50402-HF

C633 C1u25X50402-HF

C638 C1u25X50402-HF

C637 C1u25X50402-HF

C606 C1u25X50402-HF

C640 C1u25X50402-HF

C626 C1u25X50402-HF

C614 C1u25X50402-HF

C630 C1u25X50402-HF

C612 C1u25X50402-HF

C617 C10u10X5-HF

C629 C10u10X5-HF

C598 C10u10X5-HF

C628 C10u10X5-HF

C634 C10u10X5-HF

C621 C10u10X5-HF

C608 C10u10X5-HF

C641 C10u10X5-HF

C636 C10u10X5-HF

C620 C10u10X5-HF

C625 C10u10X5-HF

C627 C10u10X5-HF

C632 C10u10X5-HF

C601 C10u10X5-HF

C597 C10u10X5-HF

C599 C10u10X5-HF

+

1 2

C284 C330u2SO-HF-3

VPP

+2_5VMEM_VPP

C610 C1u25X50402-HF

C618 C1u25X50402-HF

C611 C10u10X5-HF

C619 C10u10X5-HF

GND

C271 C1u25X50402-HF

C272 C1u25X50402-HF

C270 C1u25X50402-HF

C273 C1u25X50402-HF

C278 C10u25X50805-HF C11-1067614-W08

C277 C10u25X50805-HF C11-1067614-W08

+3VRUN

C596 C0.1u25X50402-HF

C602 C2.2u10X5-HF

2

Place VTT plane to close SODIMM

Placehoder Place VTT plane to close SODIMM

GND

Place close to DRAM

GND

1 placehoder

GND

DRAM Side

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

DDR4_SODIMM_A

DDR4_SODIMM_A

DDR4_SODIMM_A

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

MS-14B3

MS-14B3

MS-14B3

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

1

0A

0A

0A

of

657Friday, November 16, 2018

of

657Friday, November 16, 2018

of

657Friday, November 16, 2018

Page 7

+3VRUN

MSI CONFIDENTIAL

60046221 robin(周斌)

RD(C)2019012121002客戶服務部

孫飛(60010839)

smd.db-x7.ru

R431 10KR1%0402

R125 10KR1%0402

R416 10KR1%0402

Remove CLKOUT #2018.08.28

1 1

Add CLK for WLAN #2018.08.28

WLAN

CLKOUT_PCIEN_WLAN<20>

CLKOUT_PCIEP_WLAN<20>

PCIE_CLK_WLAN_REQ#<20>

GPU

COMBO SSD

CLKOUT_PCIEN_SSD<19>

CLKOUT_PCIEP_SSD<19>

PCIE_CLK_SSD_REQ#<19>

SUS

2 2

SMBCLK_DIMM

SMBDATA_DIMM

A

PCIE_CLK_SSD_REQ#

GPU_CLKREQ#

PCIE_CLK_WLAN_REQ#

Add WLAN REQ# for WLAN #2018.08.28

PCIE_CLK_WLAN_REQ#

GFX_REFCLK#<33>

GFX_REFCLK<33>

GPU_CLKREQ#<33>

Vgs(th) = 0.5, 1.2, 1.5V

ID = 0.2A

GPU_CLKREQ#

PCIE_CLK_SSD_REQ#

Q16

NN-BSS138DW-7-F_SOT363-6-RH

D03-138DW19-D07

SOT_363

S1

D1

G1

S2

G2

D2

AW2

CLKOUT_PCIE_N0

AY3

CLKOUT_PCIE_P0

CF32

GPP_B5/SRCCLKREQ0#

BC1

CLKOUT_PCIE_N1

BC2

CLKOUT_PCIE_P1

CE32

GPP_B6/SRCCLKREQ1#

BD3

CLKOUT_PCIE_N2

BC3

CLKOUT_PCIE_P2

CF30

GPP_B7/SRCCLKREQ2#

BH3

CLKOUT_PCIE_N3

BH4

CLKOUT_PCIE_P3

CE31

GPP_B8/SRCCLKREQ3#

BA1

CLKOUT_PCIE_N4

BA2

CLKOUT_PCIE_P_4

CE30

GPP_B9/SRCCLKREQ4#

BE1

CLKOUT_PCIE_N5

BE2

CLKOUT_PCIE_P5

CF31

GPP_B10/SRCCLKREQ5#

SMBCLK_DIMM_Q

SMBDATA_DIMM_Q

C114 C0.1u25X50402-HF

+3VRUN

100Mhz

CPU1J

WHL-i7-8565U

A0D-8565U05-I06

10 of 20

RUN

SMBCLK_DIMM_Q <6,29>

SMBDATA_DIMM_Q <6,29>

GND

+3VSUS+3VSUS+3VSUS +3VSUS+3VSUS

R157

100KR0402

0B. Remove BIOS ROM socket & place BIOS ROM M31-2512893-W03 #2018.11.09

3 3

EC11

X_C10p50N0402

Add CS Pin PU

R139

10KR0402

SPI_CS0#

SPI_MISO SPI_HOLD#_B

SPI_CLK

SPI_MISO

SPI_MOSI

SPI_WP#

SPI_HOLD#_B

1

2

3

4

SPI resistance form 15ohm change to 49.9ohm

R149 49.9R1%0402

R171 49.9R1%0402

R174 49.9R1%0402

R156 49.9R1%0402

R153 49.9R1%0402

+3VRUN

R479

10KR0402

4 4

SERIRQ<18,23>

C118 C0.1u25X50402

U12

CS

DO(IO1)

WP(IO2)

GND

W25Q128JVSIQ-HF

M31-2512893-W03

ROM from 8M change to 16MB

SPI_MISO<18>

VCC

HOLD(IO3)

CLK

DI(IO0)

SPI_CLK_R

SPI_MISO_R

SPI_MOSI_R

SPI_WP#_R

SPI_HOLD#_B_R

SPI_CS0#

SPI_CLK<18>

SPI_CS0#<18>

SPI_MOSI<18>

SPI_CLK

SPI_CS0#

SPI_MISO

SPI_MOSI

KBRST#<18>

R154

8

7

SPI_CLKSPI_WP#

6

SPI_MOSI

5

100KR0402

SPI_CLK_R

For glitch free implementation requirements

CPU1E

CH37

SPI0_CLK

CF37

SPI0_MISO

CF36

SPI0_MOSI

CF34

SPI0_IO2

CG34

SPI0_IO3

CG36

SPI0_CS0#

CG35

SPI0_CS1#

CH34

SPI0_CS2#

CF20

GPP_D1/SPI1_CLK/BK1/SBK1

CG22

GPP_D2/SPI1_MISO_IO1/BK2/SBK2

CF22

GPP_D3/SPI1_MOSI_IO0/BK3/SBK3

CG23

GPP_D21/SPI1_IO2

CH23

GPP_D22/SPI1_IO3

CG20

GPP_D0/SPI1_CS0#/BK0/SBK0

CH7

CL_CLK

CH8

CL_DATA

CH9

CL_RST#

BV29

GPP_A0/RCIN#/TIME_SYNC1

BV28

GPP_A6/SERIRQ

WHL-i7-8565U

A0D-8565U05-I06

B

Debug port

CLKOUT_ITP#

XTAL_IN

XTAL_OUT

RTCX1

RTCX2

SRTCRST#

RTCRST#

5 of 20

AU1

CLKOUT_ITP

AU2

Add SUSCLK_WLAN to M.2 WLAN #2018.08.28

BT32

SUSCLK

XTAL24_IN

CK3

XTAL24_OUT

CK2

XCLK_BIASREF

CJ1

CLKIN_LCP

CM3

RTC_X1

BN31

RTC_X2

BN32

SRTC_RST_N

BR37

RTC_RST_N

BR34

C567

+3VALW

R248

1.5KR0402

R243

X_45.3KR1%0402

GND

GPP_B23/SML1ALERT#/PCHHOT#

GPP_A1/LAD0/ESPI_IO0

GPP_A2/LAD1/ESPI_IO1

GPP_A3/LAD2/ESPI_IO2

GPP_A4/LAD3/ESPI_IO3

GPP_A5/LFRAME#/ESPI_CS#

GPP_A14/SUS_STAT#/ESPI_RESET#

GPP_A9/CLKOUT_LPC0/ESPI_CLK

GPP_A10/CLKOUT_LPC1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

GPD8/SUSCLK

XCLK_BIASREF

CLKIN_XTAL

Strap Pin requireStrap Pin require

R175

100KR0402

R145 100KR0402

TPJNC8

TPJNC4

SUSCLK_WLAN <20>

R48 60.4R1%0402

CLKIN_LCP <20>

C581

C1u25X50402-HF

C1u25X50402-HF

+3VALW_R

S-BAT54C_SOT23

1KR1%0402

Remove SMBCLK_DIMM & SMBDATA_DIMM off-page #2018.08.28

GPP_C0/SMBCLK

GPP_C1/SMBDATA

GPP_C2/SMBALERT#

GPP_C3/SML0CLK

GPP_C4/SML0DATA

GPP_C5/SML0ALERT#

GPP_C6/SML1CLK

GPP_C7/SML1DATA

GPP_A8/CLKRUN#

EC_CLKRUN#

Add 0 ohm

Close to PCH

R51 0R0402

R55 0R0402

XCLK_BIASREF change form PU to 60.4 ohm PD

Add CNVi function

R46720KR1%0402

R45120KR1%0402

0B. Change C580 & C584 from 4.7pF to 3.9pF(C11-39A1822-W08) by Vender matching report #2018.11.12

Follow 16S1 0B add discharge circuit on

SRTC_RST & RTC_RST #2018.09.13

R512 & R246 place on CPU side and close ball out

SRTC_RST_N

RTC_RST_N

Y

+RTC_D

Z

D5

R247

GND

X

CK14

CH15

CJ15

CH14

CF15

CG15

CN15

CM15

CC34

CA29

BY29

BY27

BV27

CA28

CA27

BV32

BV30

BY30

S-BAS40WS_SOD323-RH

D01-BAS4000-P15

DIODE_SOD323

+RTC_R

+RTC

1

2

6 5

CON7

BH1X2#S-1.25PITCH_BLACK-HF

N32-10200Q0-A81

SD_53261_0210_2P

SMBCLK_DIMM

SMBDATA_DIMM

SMBALERT#

SML0_CLK

SML0_DATA

SML0ALERT#

SMB_CLK_R

SMB_DATA_R

SML1ALERT#

Follow PDG resistor can be up to 22 ohm

LPC_AD0_R

LPC_AD1_R

LPC_AD2_R

LPC_AD3_R

LPC_FRAME#_R

SUS_STAT#

CLKOUT_PCI0

CLKOUT_BLF

EC_CLKRUN# <18>

R190 8.2KR0402

C

Resistor form 1M ohm to 200K ohm

XTAL24_IN_R

R52

200KR1%0402

XTAL24_OUT_R

RTCVCC

Follow PDG change BIAS R from 10M 5% to 10M 1% #2018.08.23

D4

R463

10MR1%0402

2018.05.30 Update Crystal 24M component (<30 ohm)

R512 0R0402

R246 0R0402

R253 X_0R0402

NOT used

SML0ALERT# (eSPI/LPC):This

signal has a weak internal

pull-down.

0 = LPC is selected for EC (Default) ;

1 = eSPI is selected for EC

R472 22R0402

R475 22R0402

R457 22R0402

R480 22R0402

R460 22R0402

R185 22R1%0402

R465 22R1%0402

+3VRUN

C60

C12p50N0402

34

Y1

24MHZ12p_S-HF-8

D04-3904000-SC6

1 2

C62

C12p50N0402

12

Y3

32.768KHZ7p_S-HF-2

D04-0307000-C11

OSC_3_2X1_5_1

Vgs(th) = 0.5, 1.2, 1.5V

ID = 0.2A

Q30

NN-BSS138DW-7-F_SOT363-6-RH

D03-138DW19-D07

SOT_363

D1

D2

RTCVCC

BAT1

BCR1220H2

D06-0105701-K26

EC12

S1

G1

S2

G2

GND

C174

C1u25X5-HF

GND

Follow 14B1

SML1ALERT# :

This signal has an internal pull-down.

0 = Disable IntelR DCI-OOB (Default)

1 = Enable IntelR DCI-OOB

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

TPJNC50

CLK_PCI_KBC <18>

EC42

C580C3.9p50N0402

C584C3.9p50N0402

GND

GND

R240

100KR1%0402

LPC_AD0 <18,23>

LPC_AD1 <18,23>

LPC_AD2 <18,23>

LPC_AD3 <18,23>

LPC_FRAME# <18,23>

CLK_PCI_TPM

EC_RTC_RST <18>

CLK_PCI_TPM <23>

D

+3VRUN

SMBCLK_DIMM_Q

SMBDATA_DIMM_Q

SMBCLK_DIMM

SMBDATA_DIMM

SMBALERT#

SML1ALERT#

SML0ALERT#

SML0_CLK

SML0_DATA

SMB_CLK_R

SMB_DATA_R

SMBCLK_DIMM_Q

SMBDATA_DIMM_Q

SMBCLK_DIMM

SMBDATA_DIMM

SML0ALERT#

CLKIN_LCP

close to SOC

2018.05.29 Change CLKIN_LCP PD resistor to PCH side

R129 2.2KR1%0402

R114 2.2KR1%0402

R103 2.2KR0402

R118 2.2KR0402

R113 X_4.7KR0402

R447 X_4.7KR0402

R89 X_4.7KR0402

RN1 8P4R-2.2KR0402

1

3

5

7

EC9 X_C100p50N0402

EC7 X_C100p50N0402

EC6 X_C100p50N0402

EC8 X_C100p50N0402

R90 X_20KR1%0402

R59 10KR0402

LPC_FRAME#

LPC_AD3

LPC_AD2

LPC_AD1

LPC_AD0

Follow PDG(P.294) reserve capacitor to GND for EMI issue #2018.08.15

+3VSUS

2

4

6

8

EC43

EC40

EC44

EC45

X_C10p50N0402

X_C10p50N0402

X_C10p50N0402

X_C10p50N0402

E

Reference 16S1

EC41

Can be up to 27pF

X_C10p50N0402

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

X_C10p50N0402

X_C10p50N0402

A

B

C

D

Title

Title

Title

Whiskey lake U (RTC;LPC;CLOCK)

Whiskey lake U (RTC;LPC;CLOCK)

Whiskey lake U (RTC;LPC;CLOCK)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-14B3

MS-14B3

MS-14B3

E

0A

0A

0A

of

of

of

757Friday, November 16, 2018

757Friday, November 16, 2018

757Friday, November 16, 2018

Page 8

follow 13H1 reserve MB ID[0:3] #2018.08.10

MSI CONFIDENTIAL

60046221 robin(周斌)

RD(C)2019012121002客戶服務部

孫飛(60010839)

smd.db-x7.ru

MB_ID0

MB_ID1

MB_ID2

MB_ID3

MB_ID0

MB_ID1

MB_ID2

MB_ID3

1 1

CNVI_BRI_RSP<20>

CNVI_RGI_DT<20>

CNVI_BRI_DT<20>

CNVI_RGI_RSP<20>

Follow MOW Table 5-1 change R7042 & R7034 from 75 to 33ohm #2018.08.29

GPU

Change netname to GPIO1_GC6_FB_EN #2018.08.28

2 2

A

R411 X_10KR0402

R456 X_10KR0402

R423 X_10KR0402

R430 X_10KR0402

R412 10KR0402

R441 10KR0402

R422 10KR0402

R429 10KR0402

GPIO2_GPU_EVENT_PCH<40>

GPIO1_GC6_FB_EN<40,41>

DGPU_PWRGD<18,33,41>

DGPU_HOLD_RST#<40>

DGPU_PWR_EN<41>

+3VRUN

TPJNC53

R438 33R0402

R437 33R0402

Remove USB-SMI# #2018.08.28

I2C_DATA_TP

I2C_CLK_TP

Remove TP_INT# #2018.08.28

Active HI

R435 100KR1%0402

GND

R126 100KR1%0402

GND

MB_ID2

PIRQA#

MB_ID3

MB_ID0

MB_ID1

CNVI_RGI_DT_R

CNVI_BRI_DT_R

TPJNC52

TPJNC20

CC27

CC32

CE28

CE27

CE29

CA31

CA32

PME#

CC29

CC30

CA30

CK20

CG19

CJ20

CH19

CR12

CP12

CN12

CM12

CM11

CN11

CK12

CJ12

CF27

CF29

CH27

CH28

CJ30

3.3V

CJ31

Follow 14B1 reserve R657 for CFG_UMA sku. #2018.08.10

Remove level shift

B

C

D

Reference 16S1

CPU1F

GPP_B15/GSPI0_CS0#

GPP_A7/PIRQA#/GSPI0_CS1#

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_B19/GSPI1_CS0#

GPP_A11/PME#/GSPI1_CS1#/SD_VDD2_PWR_EN#

GPP_B20/GSPI1_CLK

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_F5/CNV_BRI_RSP

GPP_F6/CNV_RGI_DT

GPP_F4/CNV_BRI_DT

GPP_F7/CNV_RGI_RSP

GPP_C20/UART2_RXD

GPP_C21/UART2_TXD

GPP_C22/UART2_RTS#

GPP_C23/UART2_CTS#

GPP_C16/I2C0_SDA

GPP_C17/I2C0_SCL

GPP_C18/I2C1_SDA

GPP_C19/I2C1_SCL

GPP_H4/I2C2_SDA

GPP_H5/I2C2_SCL

GPP_H6/I2C3_SDA

GPP_H7/I2C3_SCL

GPP_H8/I2C4_SDA

GPP_H9/I2C4_SCL

WHL-i7-8565U

A0D-8565U05-I06

1.8V

SMI# / NMI

6 of 20

NN-BSS138DW-7-F_SOT363-6-RH

D03-138DW19-D07

SUS

I2C_CLK_TP

I2C_DATA_TP

D1

D2

Vgs(th) = 0.5V,1.2V,1.5V

GPP_A12/ISH_GP6/BM_BUSY#/SX_EXIT_HOLDOFF#

SOT_363

GPP_D9/ISH_SPI_CS#/GSPI2_CS0#

GPP_D10/ISH_SPI_CLK/GSPI2_CLK

GPP_D11/ISH_SPI_MISO/GSPI2_MISO

GPP_D12/ISH_SPI_MOSI/GSPI2_MOSI

GPP_D15/ISH_UART0_RTS#/GSPI2_CS1#

GPP_D16/ISH_UART0_CTS#/SML0BALERT#

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_C14/UART1_RTS#/ISH_UART1_RTS#

GPP_C15/UART1_CTS#/ISH_UART1_CTS#

Q11

S1

G1

S2

G2

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_H10/I2C5_SDA/ISH_I2C2_SDA

GPP_H11/I2C5_SCL/ISH_I2C2_SCL

GPP_D13/ISH_UART0_RXD

GPP_D14/ISH_UART0_TXD

GPP_A18/ISH_GP0

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

RUN

I2C_CLK_TP_Q

I2C_DATA_TP_Q

+3VRUN

I2C_CLK_TP_Q <29>

I2C_DATA_TP_Q <29>

C87 C0.1u25X50402-HF

CN22

GPP_D10

CR22

CM22

GPP_D12

CP22

Follow PDG DCI OOB implementation

CK22

CH20

CH22

CJ22

GPP_H10

CJ27

GPP_H11

CJ29

CM24

CN23

CM23

CR24

CG12

CH12

CF12

CG14

BW35

BW34

CA37

CA36

CA35

CA34

BW37

GND

TPJNC16

TPJNC22

TPJNC51

2018.06.14 PCIE_WAKE# signal follow CRB Pull up 8.2k ohm

2018.06.14 Del PM_SLP_S0# and EXT_PWR_GATE# pull up resistor

Becasue function pin is output pin and isn`t be used

Change R7051 from 10k to 4.7k #2018.08.24

SOC Internal Pull Down 15k~40k ohm

2018.06.13 Del SUSPWRDNACK pull up resistor for PDG suggest

I2C_CLK_TP

I2C_DATA_TP

Remove USB-SMI# & TP_INT# PU #2018.08.28

GPP_D12

I2C_CLK_TP_Q

I2C_DATA_TP_Q

Remove USB-SMI# & TP_INT# PU #2018.08.28

I2C_CLK_TP_Q

I2C_DATA_TP_Q

Remove USB-SMI# & TP_INT# Cap to GND #2018.08.28

CNVI_BRI_RSP

CNVI_RGI_RSP

DT resistance close to module

RSP resistance close to SOC

For glitch free implementation requirements

PCIE_WAKE#

AC_PRESENT

PM_BATLOW#

EC_PWRBTN#

PIRQA#

RSMRST#

PCH_PWROK

AC_PRESENT

For glitch free implementation requirements

PM_SLP_S3#

PM_SLP_S4#

R78 2.2KR0402

R73 2.2KR0402

R96 100KR0402

R67 2.2KR0402

R66 2.2KR0402

EC5 X_C100p50N0402

EC4 X_C100p50N0402

+1_8VSUS

R400 X_20KR0402-2

R391 X_20KR0402-2

R464 8.2KR0402

R454 4.7KR0402

R462 8.2KR0402

R217 X_10KR0402

R425 10KR0402

R459 10KR0402

R478 10KR0402

R455 X_100KR0402

R200 100KR0402

R184 100KR0402

E

+3VSUS

+3VRUN

GND

+3VSUS

+3VRUN

CPU1K

PLT_RST#

3 3

+3VSUS

C163C0.1u25X50402

U16

74HC1G08GW_TSSOP5-HF

BUF_PLT_RST#<18,19,23,40>

R198

100KR0402

Follow 14B1 add WLAN_RST to GPU #2018.08.28

4 4

WLAN_RST#<20>

R218

100KR1%0402

GND

GND

C165C0.1u25X50402-HF

4

Y

A

53

VCC

4

Y

GND

+3VSUS

53

VCC

1

A

2

B

GND

U17

NL17SZ08DFT2G_SC70-5-HF

T70-7SZ0870-O05

GND

SC70_5

Follow 14B1 add SUS_PWR_ACK# #2018.08.28

1

A

2

B

R204

61.9KR1%0402-RH

For glitch free implementation requirements

EC_WLAN_RST# <18>

R75 10KR0402

+3VRUN

RSMRST#<18>

TPJNC3

SYS_PWROK<18>

PCH_PWROK<18>

TPJNC30

SUS_PWR_ACK<18>

WLAN_WAKE#<20>

Follow 14B1 add WLAN_WAKE#

#2018.08.28

DSWROK can be tied to RSMRST# for platforms

that dose not support the Deep Sx state.

DSW_PWROK

SYS_RESET#_JNC

PROCPWRGD

VCCST_PWRGD

R76 0R0402

R471 0R0402

DSW_PWROK

SUS_PWR_ACK

R468 0R0402

R458 0R0402

B

PCIE_WAKE#

RSMRST#

EC_ALLSYSPG<18,48>

BJ35

GPP_B13/PLTRST#

CN10

SYS_RESET#

BR36

RSMRST#

AR2

PROCPWRGD

BJ2

VCCST_PWRGOOD

CR10

SYS_PWROK

BP31

PCH_PWROK

BP30

DSW_PWROK

BV34

GPP_A13/SUSWARN#/SUSPWRDACK

BY32

GPP_A15/SUSACK#

BU30

WAKE#

BU32

GPD2/LAN_WAKE#

BU34

GPD11/LANPHYPC

WHL-i7-8565U

A0D-8565U05-I06

+3VSUS +VCCST

U3

1

AY

2

GPP_B11/EXT_PWR_GATE#

11 of 20

C45

53

VCC

GND

74AHC1G07GW_SOT353-RH

R38

1KR0402

C0.1u25X50402

VCCST_PWRGD_R

4

2018.06.13 VCCST_PWRGD of signal add series resistor to follow PDG suggest

C

GPP_B12/SLP_S0#

GPD4/SLP_S3#

GPD5/SLP_S4#

GPD10/SLP_S5#

SLP_SUS#

SLP_LAN#

GPD9/SPL_WLAN#

GPD6/SLP_A#

GPD3/PWRBTN#

GPD1/ACPRESENT

GPD0/BATLOW#

INTRUDER#

GPP_B2/VRALERT#

INPUT3VSEL

R42 60.4R1%0402

Remove SLP_S0# function, 14B3 did not support #2018.08.09

PM_SLP_S0#

BJ37

PM_SLP_S3#

BU36

PM_SLP_S4#

BU27

PM_SLP_S5#_R

BT29

BU29

BT31

BT30

BU37

EC_PWRBTN#

BU28

AC_PRESENT

BU35

PM_BATLOW#

BV36

SM_INTRUDER_N

BR35

EXT_PWR_GATE#

CC37

CC36

BT27

INPUT3VSEL

2018/01/30 3V Select Strap

Low ->3.3V +-5%

High -> 3.0V +-5%

VCCST_PWRGD

TPJNC29

R439 0R0402

Follow 13H1 add SLP_S5# to EC #2018.08.28

Change PM_PWRBTN# to EC_PWRBTN# #2018.08.28

EC_PWRBTN# <18>

AC_PRESENT <18>

TPJNC57

R4661MR0402

D

PM_SLP_S3# <18,46>

PM_SLP_S4# <18,45,47>

PM_SLP_S5# <18>

+3VSUS

RTCVCC

R469

X_4.7KR0402

R470

4.7KR0402

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Whiskey lake U (LPSS;ISH;I2C)

Whiskey lake U (LPSS;ISH;I2C)

Whiskey lake U (LPSS;ISH;I2C)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-14B3

MS-14B3

MS-14B3

E

857Friday, November 16, 2018

857Friday, November 16, 2018

857Friday, November 16, 2018

0A

0A

0A

of

of

of

Page 9

A

MSI CONFIDENTIAL

60046221 robin(周斌)

RD(C)2019012121002客戶服務部

孫飛(60010839)

smd.db-x7.ru

B

C

D

E

Flash Descriptor Security Override

+3VSUS

U5

1

AY

2

Low = Disable

High = Enable

HDA_SDOUT_PCH

R201 1KR0402

from 4.7K change to 1K for PDG

Follow 14B1 change HDA R/C value for SA #2018.08.15

EC15

EC33

X_C2p50N0402

Cap close to PCH

EC13

X_C2p50N0402

X_C2p50N0402

HDA_SDIN_PCH<21>

CNVI_RF_RESET<20>

MODEN_CLKREQ<20>

R192 33R0402

R197 33R0402

R195 10R1%0402

R179 22R0402

EC14

X_C10p50N0402

+VCCSTG+3VRUN

C56

53

VCC

C0.1u25X50402

EC_PROCHOT#_OD

4

74AHC1G07GW_SOT353-RH

GND

2018.05.25 add EC_PROCHOT#_OD signal

2016/04/14 add dumping

resistor for nec request

IMVP_PROCHOT#<44,48>

R50

100R0402

HDA_SYNC_PCH

HDA_BIT_CLK_PCH

HDA_RST#_PCH

Add CNVi function

CNVI_RF_RESET

HDA_SYNC_PCH

HDA_BIT_CLK_PCH

HDA_SDOUT_PCH

HDA_RST#_PCH

Add CNVI_RF_RESET pull down resistor position from module side to PCH side #2018.08.24

+VCCST

PDG 561280 Page 243

R39

1KR0402

TPJNC5

H_PECI<18>

R54 499R1%0402

2018.06.11 Change SCI wake up function pin from GPP_C2 to GP P_E3

SCI_WAKE_UP#<18>

ACPI_RadioSW<18>

R41549.9R1%0402

R40649.9R1%0402

CPU1G

BN34

HDA_SYNC/I2S0_SFRM

BN37

HDA_BCLK/I2S0_SCLK

BN36

HDA_SDO/I2S0_TXD

BN35

HDA_SDI0/I2S0_RXD

BL36

HDA_SDI1/I2S1_RXD/SNDW1_DATA

BL35

HDA_RST#/I2S1_SCLK/SNDW1_CLK

CK23

GPP_D23/I2S_MCLK

BL37

I2S1_SFRM/SNDW2_CLK

BL34

I2S1_TXD/SNDW2_DATA

CJ32

GPP_H1/I2S2_SFRM/CNV_BT_I2S_BCLK/CNV_RF_RESET#

CH32

GPP_H0/I2S2_SCLK/CNV_BT_I2S_SCLK

CH29

GPP_H2/I2S2_TXD/CNV_BT_I2S_SDI/MODEM_CLKREQ

CH30

GPP_H3/I2S2_RXD/CNV_BT_I2S_SDO

CP24

GPP_D19/DMIC_CLK0/SNDW4_CLK

CN24

GPP_D20/DMIC_DATA0/SNDW4_DATA

CK25

GPP_D17/DMIC_CLK1/SNDW3_CLK

CJ25

GPP_D18/DMIC_DATA1/SNDW3_DATA

CF35

GPP_B14/SPKR

WHL-i7-8565U

A0D-8565U05-I06

CNVI_RF_RESET

R35

1KR0402

THERMTRIP#

H_CATERR#

H_PROCHOT#_R

THERMTRIP#

SCI_WAKE_UP#

Del ASM1142 cap

PROC_POPIRCOMP

PCH_OPIRCOMP

close to SOC

R215

75KR1%0402

GND

AA4

AR1

Y4

BJ1

U1

U2

U3

U4

CE9

CN3

CB34

CC35

BP27

BW25

7 of 20

CPU1D

CATERR#

PECI

PROCHOT#

THRMTRIP#

BPM#_0

BPM#_1

BPM#_2

BPM#_3

GPP_E3/CPU_GP0

GPP_E7/CPU_GP1

GPP_B3/CPU_GP2

GPP_B4/CPU_GP3

PROC_POPIRCOMP

PCH_OPIRCOMP

GPP_G0/SD_CMD

GPP_G1/SD_DATA0

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD#

GPP_G6/SD_CLK

GPP_G7/SD_WP

GPP_A17/SD_VDD1_PWR_EN#/ISH_GP7

GPP_A16/SD_1P8_SEL

PROC_TCK

PROC_TDI

PROC_TDO

PROC_TMS

PROC_TRST#

PCH_TCK

PCH_TDI

PCH_TDO

PCH_TMS

PCH_TRST#

PCH_JTAGX

PROC_PREQ#

PROC_PRDY#

SD_1P8_RCOMP

SD_3P3_RCOMP

JTAG_TCK_JNC

T6

JTAG_TDI_JNC

U6

JTAG_TDO_JNC

Y5

JTAG_TMS_JNC

T5

JTAG_TRST#_JNC

AB6

PCH_JTAG_TCK

W6

JTAG_TDI_JNC

U5

JTAG_TDO_JNC

W5

JTAG_TMS_JNC

P5

JTAG_TRST#_JNC

Y6

JTAG_TCK_JNC

P6

PROC_PREQ#

W2

PROC_PRDY#

W1

2016/04/22 It deleted S0ix signal is

not support CS mode for nec request

CH36

CL35

CL36

CM35

CN35

CH35

CK36

CK34

2018.06.11 Remove Sensor INT function pin

BW36

BY31

CK33

SD_RCOMP

CM34

SD_RCOMP can combine with a resistor

2018.06.04 Follow PDG 575412 Figure 13-6 for DCI debug

R445 200R1%0402

R360 51R1%0402

R40 51R1%0402

TPJNC45

TPJNC46

TPJNC13

TPJNC14

TPJNC11

TPJNC9

2018.06.14 PCH_JTAG_TCK signal add Test Point

HDA_SDO

1 1

FLASH_SECURITY<18>

HDA_SYNC<21>

HDA_BIT_CLK<21>

HDA_SDOUT<21>

HDA_RST#<21>

2 2

0B. Change R195 form 22R to 10R (R11-0100T12-W08) and unstuff EC14 for SA #2018.11.09

R49

10KR0402

3 3

EC_PROCHOT#<18>

Reference 16S1

+VCCSTG

4 4

A

B

+3VSUS

SCI_WAKE_UP#

R9210KR0402

C

4 of 20

WHL-i7-8565U

A0D-8565U05-I06

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Whiskey lake U(HDA;MISC,JTAG)

Whiskey lake U(HDA;MISC,JTAG)

Whiskey lake U(HDA;MISC,JTAG)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

Date : Sheet

Date : Sheet

Date : Sheet

D

MS-14B3

MS-14B3

MS-14B3

MICRO-STAR INT'L CO.,LTD.

0A

0A

0A

of

of

of

957Friday, November 16, 2018

957Friday, November 16, 2018

957Friday, November 16, 2018

E

Page 10

A

MSI CONFIDENTIAL

60046221 robin(周斌)

RD(C)2019012121002客戶服務部

孫飛(60010839)

smd.db-x7.ru

AC coupling capacitors on motherboard are recommended to be placed

closer to either the connector or processor side.

Avoid placing AC caps at the center of the motherboard.

1 1

Change to 14B3 configuration #2018.08.28

USB3_RXN_TYPEC3<28>

USB3_RXP_TYPEC3<28>

USB3_TXN_TYPEC3<28>

Port5,6 : USB3.1 TypeC Port4

Port7 : M.2 WLAN

USB3_TXP_TYPEC3<28>

USB3_RXN_TYPEC4<28>

USB3_RXP_TYPEC4<28>

USB3_TXN_TYPEC4<28>

USB3_TXP_TYPEC4<28>

PCIE_RXN_WLAN<20>

PCIE_RXP_WLAN<20>

PCIE_TXN_WLAN<20>

PCIE_TXP_WLAN<20>

PCIE9_RXN<33>

2 2

Port9~12: PCI-E 1 x 4 GPU

3 3

Port13~16/SATA2 : PCI-E SSD

4 4

Reference 16S1

A

PCIE9_RXP<33>

PCIE9_TXN<33>

PCIE9_TXP<33>

PCIE10_RXN<33>

PCIE10_RXP<33>

PCIE10_TXN<33>

PCIE10_TXP<33>

PCIE11_RXN<33>

PCIE11_RXP<33>

PCIE11_TXN<33>

PCIE11_TXP<33>

PCIE12_RXN<33>

PCIE12_RXP<33>

PCIE12_TXN<33>

PCIE12_TXP<33>

PCIE_RXN_SSD1<19>

PCIE_RXP_SSD1<19>

PCIE_TXN_SSD1<19>

PCIE_TXP_SSD1<19>

PCIE_RXN_SSD2<19>

PCIE_RXP_SSD2<19>

PCIE_TXN_SSD2<19>

PCIE_TXP_SSD2<19>

PCIE_RXN_SSD3<19>

PCIE_RXP_SSD3<19>

PCIE_TXN_SSD3<19>

PCIE_TXP_SSD3<19>

PCIE_SATA_RXN_SSD<19>

PCIE_SATA_RXP_SSD<19>

PCIE_SATA_TXN_SSD<19>

PCIE_SATA_TXP_SSD<19>

4 mils min (breakout) 12-15 mils (trace)

At least 12 mils to any adjacent high speed I/O.

R370 100R1%0402

B

PCIE_RCOMPN

PCIE_RCOMPP

B

CPU1H

BW9

PCIE5_RXN/USB31_5_RXN

BW8

PCIE5_RXP/USB31_5_RXP

BW4

PCIE5_TXN/USB31_5_TXN

BW3

PCIE5_TXP/USB31_5_TXP

BU6

PCIE6_RXN/USB31_6_RXN

BU5

PCIE6_RXP/USB31_6_RXP

BU4

PCIE6_TXN/USB31_6_TXN

BU3

PCIE6_TXP/USB31_6_TXP

BT7

PCIE7_RXN

BT6

PCIE7_RXP

BU2

PCIE7_TXN

BU1

PCIE7_TXP

BU9

PCIE8_RXN

BU8

PCIE8_RXP

BT4

PCIE8_TXN

BT3

PCIE8_TXP

BP5

PCIE9_RXN

BP6

PCIE9_RXP

BR2

PCIE9_TXN

BR1

PCIE9_TXP

BN6

PCIE10_RXN

BN5

PCIE10_RXP

BR4

PCIE10_TXN

BR3

PCIE10_TXP

BN10

PCIE11_RXN/SATA0_RXN

BN8

PCIE11_RXP/SATA0_RXP

BN4

PCIE11_TXN/SATA0_TXN

BN3

PCIE11_TXP/SATA0_TXP

BL6

PCIE12_RXN/SATA1A_RXN

BL5

PCIE12_RXP/SATA1A_RXP

BN2

PCIE12_TXN/SATA1A_TXN

BN1

PCIE12_TXP/SATA1A_TXP

BK6

PCIE13_RXN

BK5

PCIE13_RXP

BM4

PCIE13_TXN

BM3

PCIE13_TXP

BJ6

PCIE14_RXN

BJ5

PCIE14_RXP

BL2

PCIE14_TXN

BL1

PCIE14_TXP

BG5

PCIE15_RXN/SATA1B_RXN

BG6

PCIE15_RXP/SATA1B_RXP

BL4

PCIE15_TXN/SATA1B_TXN

BL3

PCIE15_TXP/SATA1B_TXP

BE5

PCIE16_RXN/SATA2_RXN

BE6

PCIE16_RXP/SATA2_RXP

BJ4

PCIE16_TXN/SATA2_TXN

BJ3

PCIE16_TXP/SATA2_TXP

CE6

PCIE_RCOMP

CE5

PCIE_RCOMP_P

CR28

GPP_H12/M2_SKT2_CFG0

CP28

GPP_H13/M2_SKT2_CFG1

CN28

GPP_H14/M2_SKT2_CFG2

CM28

GPP_H15/M2_SKT2_CFG3

WHL-i7-8565U

A0D-8565U05-I06

PCIE1_RXN/USB31_1_RXN

PCIE1_RXP/USB31_1_RXP

PCIE1_TXN/USB31_1_TXN

PCIE1_TXP/USB31_1_TXP

PCIE2_RXN/USB31_2_RXN/SSIC_1_RXN

PCIE2_RXP/USB31_2_RXP/SSIC_1_RXP

PCIE2_TXN/USB31_2_TXN/SSIC_1_TXN

PCIE2_TXP/USB31_2_TXP/SSIC_1_TXP

PCIE3_RXN/USB31_3_RXN

PCIE3_RXP/USB31_3_RXP

PCIE3_TXN/USB31_3_TXN

PCIE3_TXP/USB31_3_TXP

PCIE4_RXN/USB31_4_RXN

PCIE4_RXP/USB31_4_RXP

PCIE4_TXN/USB31_4_TXN

PCIE4_TXP/USB31_4_TXP

USB2N_1

USB2P_1

USB2N_2

USB2P_2

USB2N_3

USB2P_3

USB2N_4

USB2P_4

USB2N_5

USB2P_5

USB2N_6

USB2P_6

USB2N_7

USB2P_7

USB2N_8

USB2P_8

USB2N_9

USB2P_9

USB2N_10

USB2P_10

USB2_COMP

GPP_E9/USB2_OC0#/GP_BSSB_CLK

8 of 20

USB_VBUSSENSE

GPP_E10/USB2_OC1#/GP_BSSB_DI

GPP_E11/USB2_OC2#

GPP_E12/USB2_OC3#

GPP_E4/DEVSLP0

GPP_E5/DEVSLP1

GPP_E6/DEVSLP2

GPP_E0/SATAXPCIE0/SATAGP0

GPP_E1/SATAXPCIE1/SATAGP1

GPP_E2/SATAXPCIE2/SATAGP2

GPP_E8/SATALED#/SPI1_CS1#

RSVD_1/FS_RESET#/RSVD_1

USB_ID

C

CB5

CB6

CA4

CA3

BY8

BY9

CA2

CA1

BY7

BY6

BY4

BY3

BW6

BW5

BW2

BW1

CE3

CE4

CE1

CE2

CG3

CG4

CD3

CD4

CG5

CG6

CC1

CC2

CG8

CG9

CB8

CB9

CH5

CH6

CC3

CC4

CC5

CE8

CC6

CK6

CK5

CK8

CK9

CP8

CR8

CM8

CN8

CM10

CP10

CN7

AR3

C

Change USB3.1 port1/2/3/4 order for layout #2018.09.04

USB3_RXN_TYPEC1 <25>

USB3_RXP_TYPEC1 <25>

USB3_TXN_TYPEC1 <25>

USB3_TXP_TYPEC1 <25>

USB3_RXN_TYPEC2 <25>

USB3_RXP_TYPEC2 <25>

USB3_TXN_TYPEC2 <25>

USB3_TXP_TYPEC2 <25>

USB3_RXN_TYPEA1 <24>

USB3_RXP_TYPEA1 <24>

USB3_TXN_TYPEA1 <24>

USB3_TXP_TYPEA1 <24>

USB3_RXN_TYPEA2 <24>

USB3_RXP_TYPEA2 <24>

USB3_TXN_TYPEA2 <24>

USB3_TXP_TYPEA2 <24>

USB2N_TYPEA1 <24>

USB2P_TYPEA1 <24>

USB2N_TYPEA2 <24>

USB2P_TYPEA2 <24>

USB2N_TYPEC1 <27>

USB2P_TYPEC1 <27>

USB2N_TYPEC2 <28>

USB2P_TYPEC2 <28>

USB2N_CardReader <22>

USB2P_CardReader <22>

USB2N_FP <29>

USB2P_FP <29>

USB2N_CAMERA <31>

USB2P_CAMERA <31>

USB2N_BT <20>

USB2_RCOMP

USB2_VBUSSENSE

USB2_OC0#

USB2_OC1#

USB2_OC2#

Remove DEVSLP0 #2018.08.28

USB2P_BT <20>

R356 113R1%0402

R381 1KR0402

R68 0R1%0402 R69 10KR1%0402

R72 0R1%0402

R81 0R1%0402

R84 0R1%0402 R83 10KR1%0402

DEVSLP2_SSD <19>

SSD_CFG <19>

SATAXPCIE0 -> SATA Port 0

SATAXPCIE1 -> SATA Port 1

SATAXPCIE2 -> SATA Port 2

OC0# <24>

OC1# <24>

OC2# <27>

OC3# <28>

Note.

The OC0# is USB3 Port 1, USB2 Port 1

The OC1# is USB3 Port 2, USB2 Port 2

The OC2# is USB3 Port 3,4, USB2 Port 3

The OC3# is USB3 Port 5,6, USB2 Port 4

D

Port3,4 : USB3.1 TypeC Port3

Port1 : USB3.1 TypeA Port1

Port2 : USB3.1 TypeA Port2

Port1 : USB3.1 TypeA Port1

Port2 : USB3.1 TypeA Port2

Port3 : USB3.1 TypeC Port3

Port4 : USB3.1 TypeC Port4

Port5 : Card reader

Port6 : Finger printer

Port7 : Camera

Port10: M.2 BT

USB2_OC0#

USB2_OC1#

USB2_OC2#

Follow 14B1 add OC[0:3]# funciton #2018.08.28

USB2_OC3#USB2_OC3#

D

R71 10KR1%0402

R80 10KR1%0402

+3VSUS

Title

Title

Title

Whiskey lake U(PCIE;USB;SATA)

Whiskey lake U(PCIE;USB;SATA)

Whiskey lake U(PCIE;USB;SATA)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

E

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MS-14B3

MS-14B3

MS-14B3

E

0A

0A

0A

of

10 57Friday, November 16, 2018

of

10 57Friday, November 16, 2018

of

10 57Friday, November 16, 2018

Page 11

A

MSI CONFIDENTIAL

60046221 robin(周斌)

RD(C)2019012121002客戶服務部

孫飛(60010839)

smd.db-x7.ru

CPU1Q

T4

AB5

CG2

CG1

BV24

BV25

R4

T3

R3

J4

M4

J3

M3

R2

N2

R1

N1

J2

L2

J1

L1

L3

N3

L4

N4

W4

H4

H3

2018.06.04 ADD TP for DCI

TPJNC7

1 1

CFG4

2 2

R47 1KR0402

TPJNC10

TPJNC12

CFG4 - Display Port Presence

1:Disabled; No Physical Display Port

attached to Embedded Display Port (NC in

DG)

0:Enabled; An external Display Port

device is connected to the Embedded

Display Port

(Pull down to GND through a 1K ± 5 % resistor)

R363 49.9R1%0402

TPJNC6

CFG3

CFG4

CFG5

CFG6

CFG_RCOMP

ITP_PMODE

WHL QS/CFL/WHL_ES1_CNL U

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_18

CFG_17

CFG_19

CFG_RCOMP

ITP_PMODE

RSVD_8

RSVD_9

RSVD_10

RSVD_11

RSVD_12

RSVD_13

RSVD_TP_3/RSVD/RSVD_TP_3

RSVD_TP_4/RSVD/RSVD_TP_4

RSVD_TP_8/RSVD/RSVD_TP_8

RSVD_TP_9/RSVD/RSVD_TP_9

RSVD_TP_10/RSVD/RSVD_TP_10

RSVD_TP_11/RSVD/RSVD_TP_11

RSVD_TP_13/RSVD/RSVD_TP_13

RSVD_TP_1/RSVD/RSVD_TP_1

IST_TRIG_0/RSVD/IST_TRIG_0

3 3

BK36

RSVD_18

BK35

RSVD_17

W3

RSVD_4

AM4

RSVD_5

AM3

RSVD_TP_7/RSVD/RSVD_TP_7

IST_TRIG_1/RSVD/IST_TRIG_1

RSVD_TP_2/RSVD/RSVD_TP_2

B

RSVD_TP_5

RSVD_TP_6

IST_TRIG

RSVD_TP_12

TP_3

TP_4

RSVD_14

RSVD_15

RSVD_16

RSVD_2

RSVD_3

RSVD_6

RSVD_7

IST_TP_0/RSVD/IST_TP_0

IST_TP_1/RSVD/IST_TP_1

TP_2

VSS_1/TP/VSS_1

TP_1

F37

F34

CP36

CN36

BJ36

BJ34

BK34

BR18

BT9

BT8

BP8

BP9

CR4

CP3

CR3

AT3

AU3

AN1

AN2

AN4

AN3

AL2

AL1

AL4

AL3

BP34

BP36

BP35

CR35

ADD TP

IST_TRIG

BP36 : VSS

C

CNVI_WR_D0N<20>

GPP_H21

CNVI_WR_D0P<20>

CNVI_WR_D1N<20>

CNVI_WR_D1P<20>

CNVI_WT_D0N<20>

CNVI_WT_D0P<20>

CNVI_WT_D1N<20>

CNVI_WT_D1P<20>

CNVI_WR_CLK_DN<20>

CNVI_WR_CLK_DP<20>

CNVI_WT_CLK_DN<20>

CNVI_WT_CLK_DP<20>

CNV_WT_RCOMP

A4WP_PRESENT

R452 4.7KR0402

R453 X_20KR1%0402

+3VSUS

TPJNC27

R138 150R1%0402

2018.07.05 LTE datasheet suggest the M.2_LTE_DEV_EN signal pull to OD pin

GPP_H21

This signal has a weak internal pull-down.

An external pull-up is required on this strap since 38.4

MHz XTAL is not supported on the PCH.

0 = 38.4 XTAL frequency selected. (Default)

1 = 24MHz XTAL frequency selected.

GND

D

CPU1I

CR30

CNV_WR_D0N

CP30

CNV_WR_D0P

CM30

CNV_WR_D1N

CN30

CNV_WR_D1P

CN32

CNV_WT_D0N

CM32

CNV_WT_D0P

CP33

CNV_WT_D1N

CN33

CNV_WT_D1P

CN31

CNV_WR_CLKN

CP31

CNV_WR_CLKP

CP34

CNV_WT_CLKN

CN34

CNV_WT_CLKP

CP32

CNV_WT_RCOMP_1

CR32

CNV_WT_RCOMP_2

CP20

GPP_F0/CNV_PA_BLANKING

CK19

GPP_F1

CG17

GPP_F2

CR14

GPP_C8/UART0_RXD

CP14

GPP_C9/UART0_TXD

CN14

GPP_C10/UART0_RTS#

CM14

GPP_C11/UART0_CTS#

CJ17

GPP_F8/CNV_MFUART2_RXD

CH17

GPP_F9/CNV_MFUART2_TXD

CF17

GPP_F23/A4WP_PRESENT

WHL-i7-8565U

A0D-8565U05-I06

0 = 3.3V supply is 3.3V +-5%

1 = 3.3V supply is 3.0V +-5%

This strap should only be used for specific targeted 1S battery systems.

A4WP_PRESENT

9 of 20

+1_8VSUS

CPU_C10_GATE# for VCCIO low power mode control s ignal

High : normal

Low : low power mode

CPU_C10_GATE#

GPP_H21

GPP_H22

GPP_H23

GPP_F10

GPD7

GPP_F3

CN27

TIMESYNC_0

CM27

GPP_H21

CF25

CN26

CM26

CK17

BV35

GPD7

CN20

CG25

Pin : CG25.CH25 RVP for Camera I2C

CH25

CR20

CM20

CN19

CM19

CN18

CR18

CP18

CM18

CM16

CP16

CR16

CN16

EMMC_RCOMP

CK15

GPD7

GPP_H18/CPU_C10_GATE#

GPP_H19/TIMESYNC_0

GPP_D4/IMGCLKOUT0/BK4/SBK4

GPP_H20/IMGCLKOUT1

GPP_F12/EMMC_DATA0

1.8V

GPP_F13/EMMC_DATA1

GPP_F14/EMMC_DATA2

GPP_F15/EMMC_DATA3

GPP_F16/EMMC_DATA4

GPP_F17/EMMC_DATA5

GPP_F18/EMMC_DATA6

GPP_F19/EMMC_DATA7

GPP_F20/EMMC_RCLK

GPP_F21/EMMC_CLK

GPP_F11/EMMC_CMD

GPP_F22/EMMC_RESET#

EMMC_RCOMP

R101

X_100KR0402

R102

100KR0402

E

Follow 13H1 add TP #2018.08.28

TPJNC23

TPJNC24

CNVi Strap Pin

R87

200R1%0402

Strap Pin require

R461 100KR0402

+3VSUS

E1

SKTOCC#

20 of 20

WHL-i7-8565U

A0D-8565U05-I06

4 4

SKTOCC#JNC

Reference 16S1

A

B

TPJNC15

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Titl e

Titl e

Titl e

Whiskey lake U (CFG;CSI;RSVD)

Whiskey lake U (CFG;CSI;RSVD)

Whiskey lake U (CFG;CSI;RSVD)

Size

Size

Size

Document Number Re v

Document Number Re v

Document Number Re v

Custom

Custom

Custom

Date: Sheet

Date: Sheet

C

D

Date: Sheet

MS-14B3

MS-14B3

MS-14B3

MICRO-STAR INT'L CO.,LTD.

of

of

of

11 57Friday, November 16, 2018

11 57Friday, November 16, 2018

11 57Friday, November 16, 2018

E

0A

0A

0A

Page 12

A

MSI CONFIDENTIAL

60046221 robin(周斌)

RD(C)2019012121002客戶服務部

孫飛(60010839)

smd.db-x7.ru

Reference 16S1

C399

C457

1 1

C10u6.3X50402

C10u6.3X50402

C326

C354

C10u6.3X50402

C400

22x10 uf 0402

C472

C10u6.3X50402

C10u6.3X50402

C398

C402

C328

C349

C10u6.3X50402

C10u6.3X50402

C490

ZRB15XR60J106ME12D

C394

C397

C10u6.3X50402

C360

C401

C10u6.3X50402

C10u6.3X50402

C371

C10u6.3X50402

C10u6.3X50402

+VCC_CORE

C6P38 C1u6.3X50201

C6P26 C1u6.3X50201

C6P15 C1u6.3X50201

C6P31 C1u6.3X50201

C6P3 C1u6.3X50201

C6P5 C1u6.3X50201

2 2

C6P32 C1u6.3X50201

2018.06.11 Refer to PDG 575412 Table 11-2

+VCC_CORE

C10u6.3X50402

42x1uf 0201

C5P10 C1u6.3X50201

C5P4 C1u6.3X50201

C5P6 C1u6.3X50201

C5P2 C1u6.3X50201

C5P9 C1u6.3X50201

C5P3 C1u6.3X50201

C5P7 C1u6.3X50201

C5P8 C1u6.3X50201

C5P5 C1u6.3X50201

C5P1 C1u6.3X50201

C6P6 C1u6.3X50201

C6P42 C1u6.3X50201

C6P44 C1u6.3X50201

C6P18 C1u6.3X50201

C6P16 C1u6.3X50201

C6P36 C1u6.3X50201

C6P27 C1u6.3X50201

C6P22 C1u6.3X50201

C10u6.3X50402

C10u6.3X50402

+VCC_CORE

C10u6.3X50402

C6P10 C1u6.3X50201

C6P25 C1u6.3X50201

C6P40 C1u6.3X50201

C6P37 C1u6.3X50201

C6P11 C1u6.3X50201

C6P9 C1u6.3X50201

C6P41 C1u6.3X50201

C6P43 C1u6.3X50201

C6P45 C1u6.3X50201

C6P35 C1u6.3X50201

C6P28 C1u6.3X50201

C6P12 C1u6.3X50201

C6P23 C1u6.3X50201

C6P17 C1u6.3X50201

C6P24 C1u6.3X50201

C6P14 C1u6.3X50201

C6P39 C1u6.3X50201