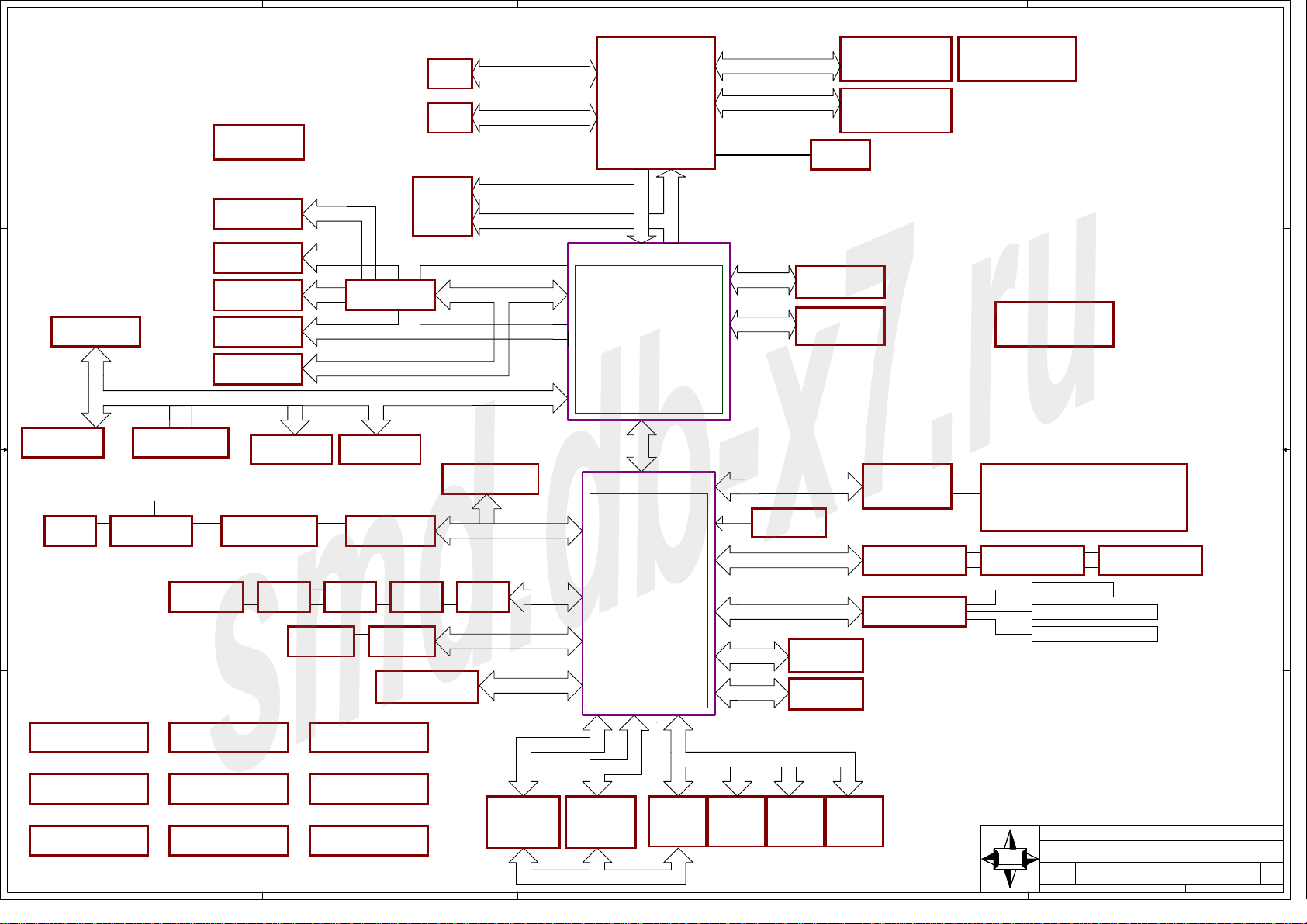

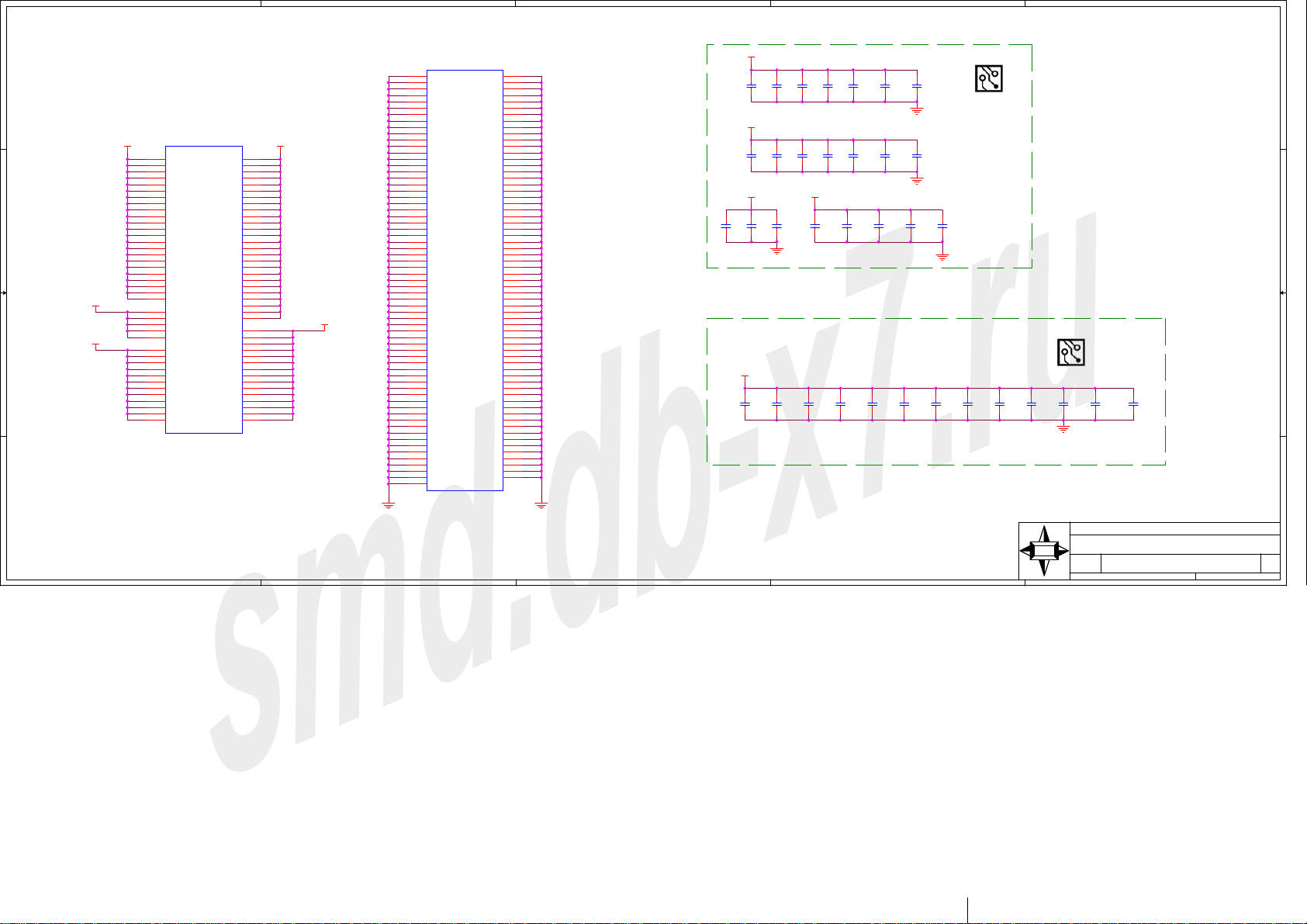

Page 1

5

smd.db-x7.ru

PRELIMINARY

D D

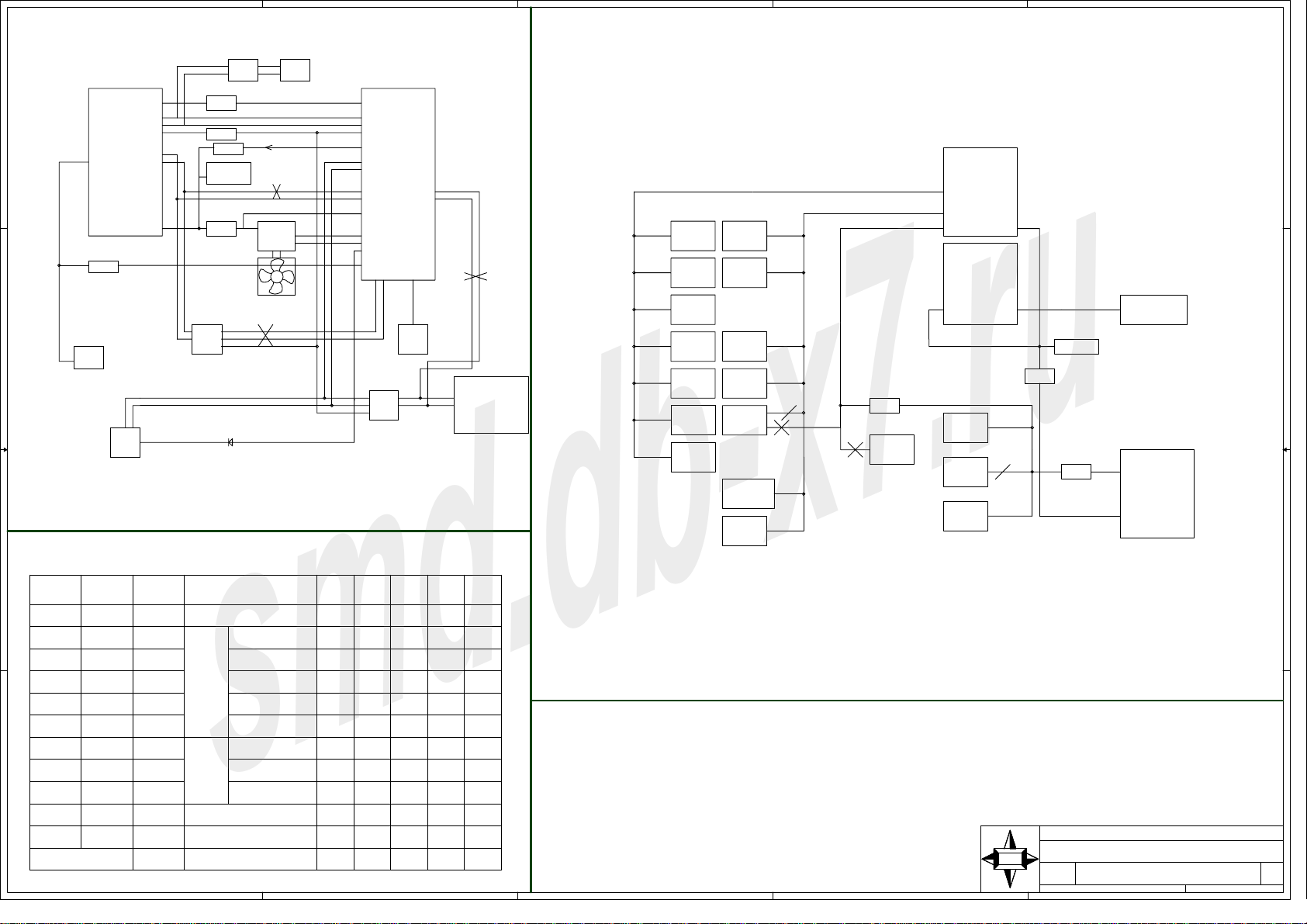

EXTERNAL CLOCK GENERATOR

ICS9LPRS478

DISPLAY PORT

2,3,4

20

37,38

4

3

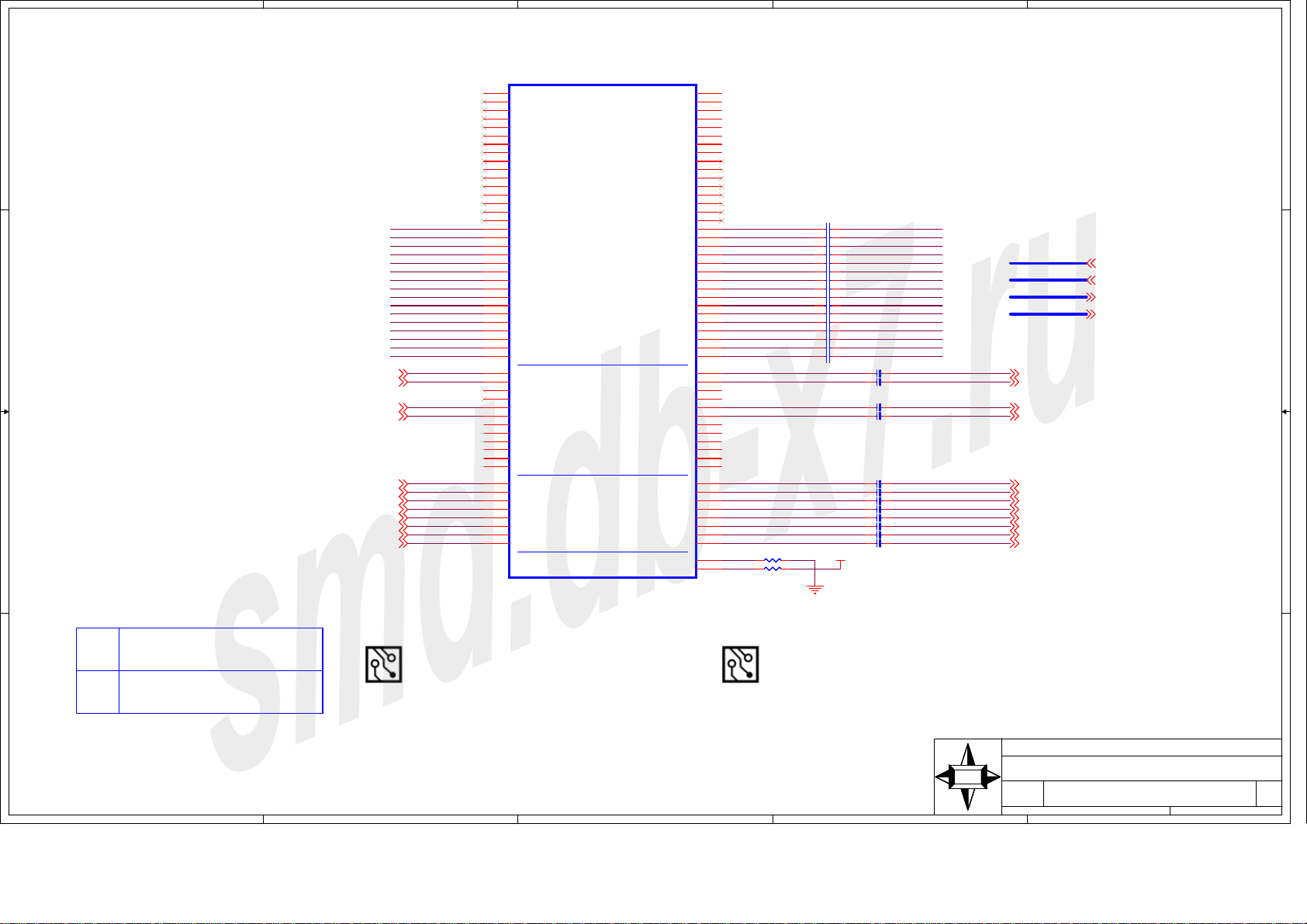

GUAM S1G4 SCHEMATIC DESIGN

DDR III, 1333MT/S

HDT

SCAN

HT Debug

Header

16

16

21

AMD S1G4 CPU

14,15,16,17

IN

OUT

HyperTransport

16x16

Channel A

Channel B

LINK0

UNBUFFERED DDR3

NEAR SODIMM

UNBUFFERED DDR3

FAR SODIMM

SB-TSI

16

2

18,19

18,19

Optional CPU

Temperature sensor

16

1

MXM 3.0

x2 PCIE

GPP4&5

MINIPCIE

46

Finger Print

Reader

USB1.1-0

LVDS MUX

33

CRT MUX

PCIE x8

50

MINIPCIE

49

USB#1USB#2

45

GB ETHERNET PHY

(Optional)

X8 PCIE MUX

GPP INTERFACE

USB#0

46

USB1.1

RGMII

47

48

USB 2.0

RS880M

HyperTransport LINK0 CPU I/F

DX10 IGP

LVDS/TVOUT/TMDS

DISPLAY PORT X2

Side Port Memory

1 X16 PCIE I/F

1 X4 PCIE I/F WITH SB

6 X1 PCIE I/F

21,22,23,24,25

PCIE

X4

SB800

USB2.0 (14)+1.1(2)

SATA III (6 PORTS)

4 X1 PCIE GEN2 I/F

INT. CLK GEN.

GB MAC

HW MONITOR

PCI/PCI BDGE

INT. RTC

26,27,28,29

EC

HD AUDIO

LPC I/F

SPI I/F

ACPI 1.1

Side port

I2C I/F

HW MONITOR I/F

SPI I/F

I2C I/F

LVDS CON

eDP CON

51

SD Reader

VGA CON

LASSO CON

GPP PCIE INTERFACE

Express Card

44

C C

B B

IEEE 1394

MINI PCIE

SIM card

socket

44

48

PCIE ETHERNET

MINIPCIE

USB12

49

35

37

36

36

USB3.0

Controller

USB#3

39

50

46 46

Bluetooth

USB1.1-1

45

FRAME BUFFER

DRR3 512MBIT

BOOTSTRAPS

ROM(NB)

HD AUDIO I/F

CIR

SATA III I/F

45

SPI ROM

BOOTSTRAPS

ROM (SB)

24

24

AZALIA CODEC

42,43

Mobile 2.5" HDD eSATAMobile ODD

HW MONITOR

28

30

41

28

Ambient Light Sensor

Headphone & SPDIF

Jack

Digital MIC Array

Header x2

43

42

41

CPU FAN

CPU Tempreture Sensor

VOLTAGE MONITOR

52

MIC In Jack

Speaker Headr x2

43

43

41

BATTERY CHAGER

A A

SYSTEM MAIN POWER

VCCNB&VLDT

Power

7

13

12

5

CPU CORE/NB POWER

1V8 &1V1DUAL

POWER

DISCHARGE CIRCUIT

CPU MEMORY POWER

8

59

1V5 &1V5DUAL

POWER

RESET,FAN

& ENABLES

10

9

11

55

4

SCANNED

MATRIX

KEYBOARD

PS2

TOUCH PAD

53 53

SMSC1100

EC

3

52

DEBUG

POSTCARD

LPC

57

LPC ROM

LPC header

TPM1.2

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

54

54

MSI

MSI

MSI

2

MICRO-STAR INT'L CO.,LTD

MS-168x

MS-168x

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Tuesday, March 23, 2010

Tuesday, March 23, 2010

Tuesday, March 23, 2010

MS-168x

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

1

Sheet ofDate:

152

Sheet ofDate:

152

Sheet ofDate:

152

0A

0A

0A

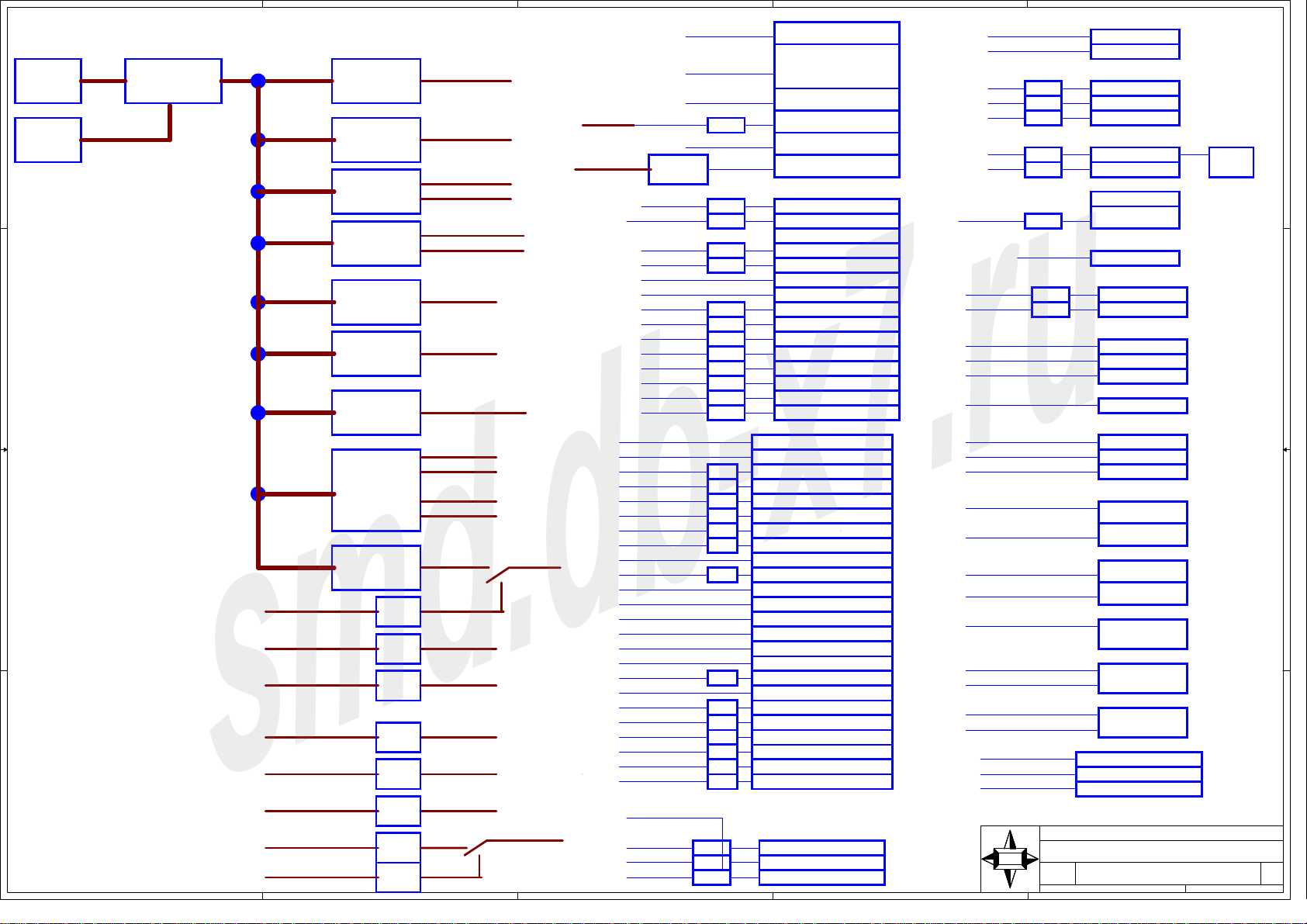

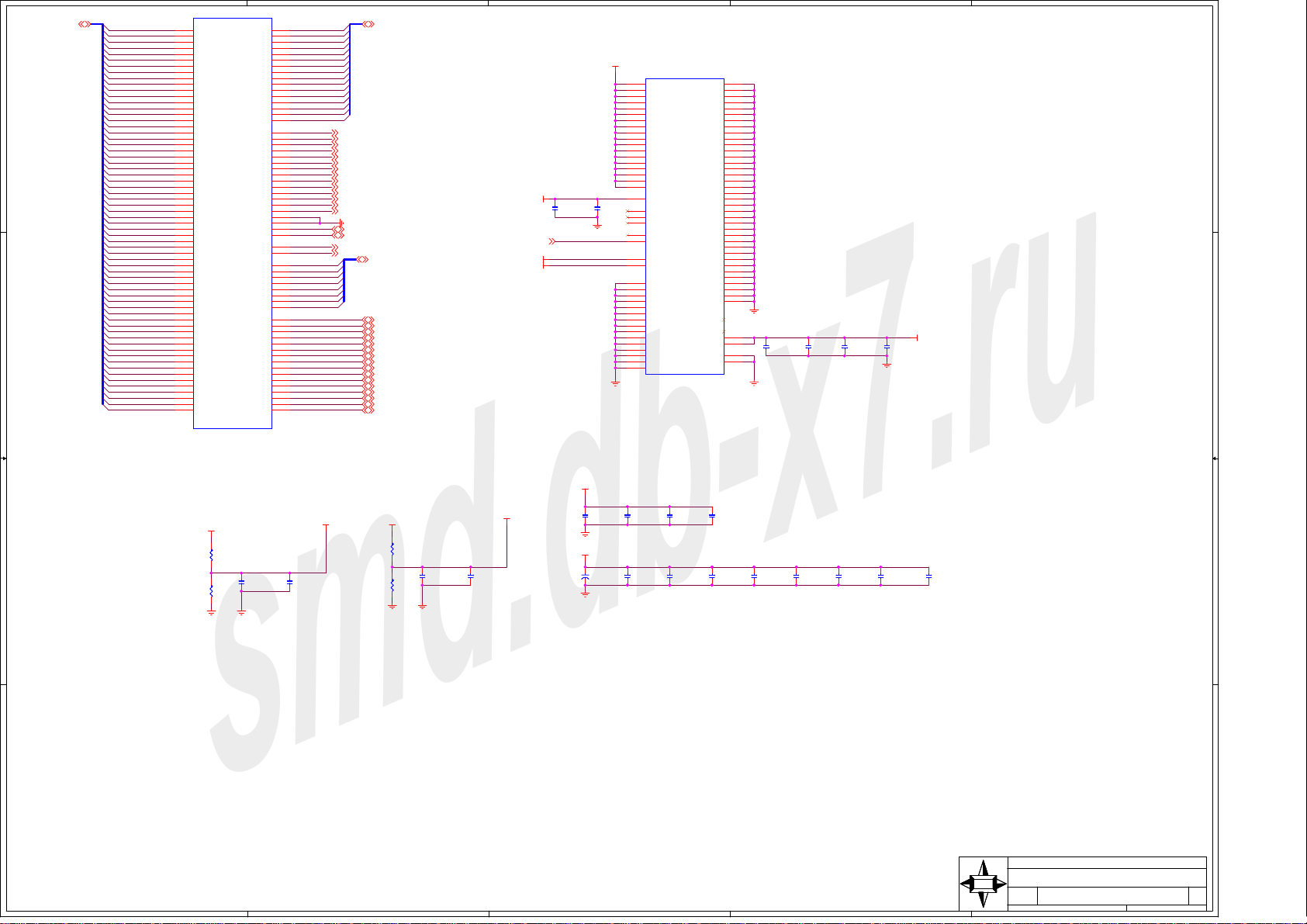

Page 2

5

smd.db-x7.ru

4

3

2

1

D D

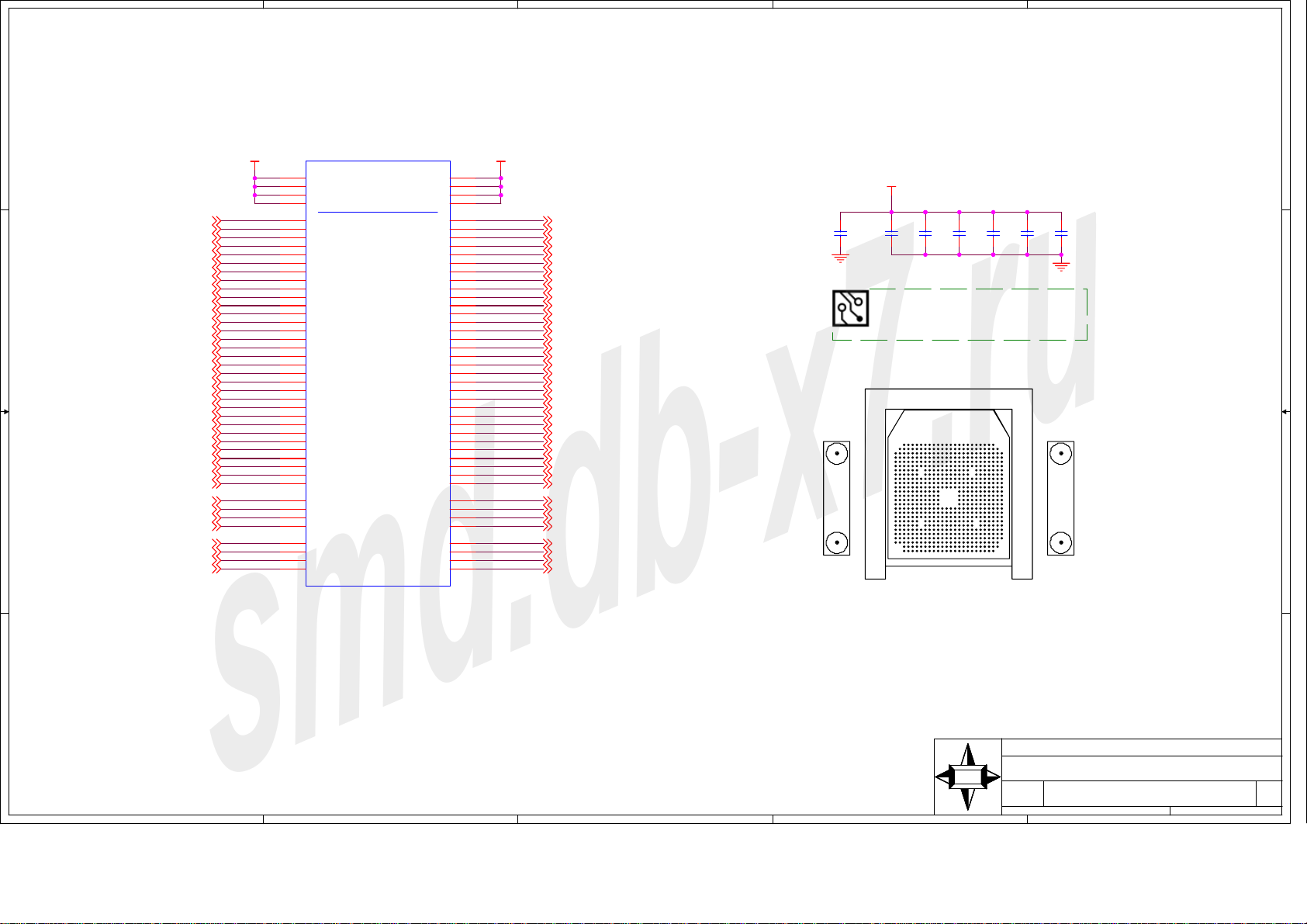

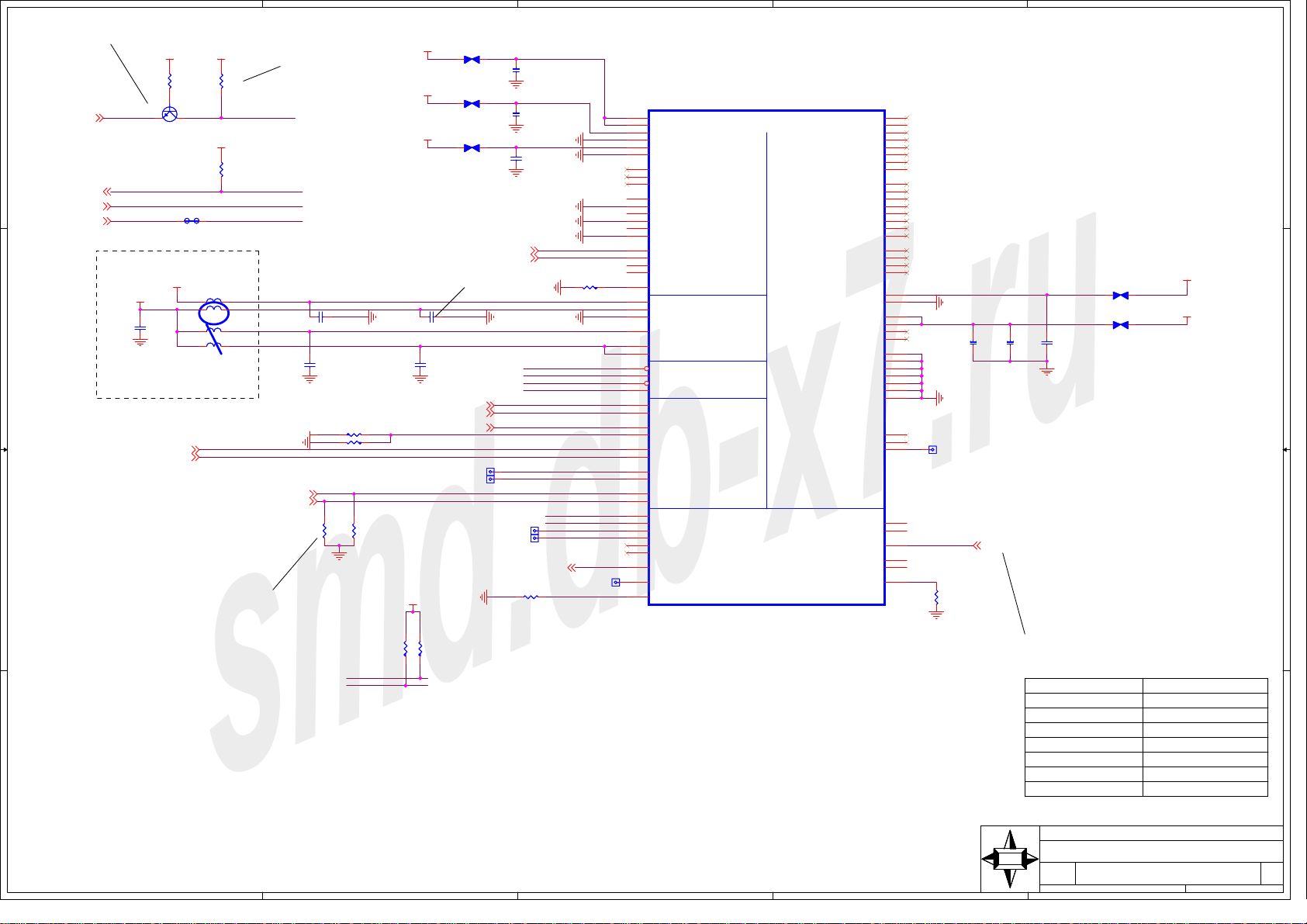

P01 : BLOCK DIAGRAM

P02 : TABLE OF CONTENTS

P03 : POWER DELIVERY CHART

P04 : POWER SEQUENCE CHART

P05 : CLOCK DISTRIBUTION

P06 : MISC TABLES

P07 : BATTERY CHARGER

P08 : CPU CORE PWR

P09 : CPU MEM PWR

C C

P10 : 1V1DUAL / 1V1 /18V /3V3 /5V

P11 : 1V5 / 1V5DUAL

P12 : NBCORE / VLDT

P13 : SYSTEM POWER

P14 : S1G4 HT I/F

P15 : S1G4 DDRIII MEMORY I/F

P16 : S1G4 CTRL / DEBUG

P17 : S1G4 PWR / GND

P18 : DDR3 SODIMMS A/B CHANNLE

P19 : DDR3 SODIMMS DECOUPLING

P20 : EXTERNAL CLOCK GEN

P21 : RS880M HT I/F

B B

P22 : RS880M PCIE I/F

P23 : RS880M SYSTEM

P24 : RS880M SPMEM/STRAPS

P25 : RS880M POWER

P26 : SB8X0 PCIE/PCI/CPU/LPC/CLK

P27 : SB8X0 GPIO/USB/AZ/RGMII

P28 : SB8X0 SATA/IDE/HWM/SPI

P29 : SB8X0 POWER / DECOUPLING

P30 : SB8X0 STRAPS

P31 : PCIE SWITCH

TABLE OF CONTENTS

P32 : MXM PWR / MISC

P33 : MXM 3.0 EDGE

P34 : LVDS / CRT SWITCH

P35 : LVDS CON / BACKLIGHT

P36 : CRT / LASSO CONN

P37 : EDP / DPD

P38 : DPB / DPC

P39 : USB3.0 (1)

P40 : USB3.0 (2)

P41 : SATA CONN / DEBUG

P42 : HD AUDIO CODEC

P43 : HD AUDIO CONN

P44 : 1394 / SD READER

P45 : FP / BT / CIR

P46 : USB2.0 PORTS

P47 : LAN PHY (B50610)

P48 : MINI PCIE SLOT 0, 3

P49 : MINI PCIE SLOT 1, 2

P50 : X4 GPP / PCIE EXPRESS CARD

P51 : LOM (57760)

P52 : KBC - SMSC1100L

P53 : KBCBIOS / KBD /MOUSE

P54 : CONFIG ROM / LPC ROM / TPM

P55 : RESET / FAN / LED / PWRGD

P56 : ACPI CONN

P57 : DEBUG - POST LEDS

P58 : DUAL RAIL ENABLE

P59 : DISCHARGE CIRCUIT

P60 : SB800 A11 PU RES

P61 : CHANGE HISTROY

P62 : POWER ON SEQUENCE CHART

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-168x

MS-168x

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Tuesday, March 23, 2010

Tuesday, March 23, 2010

5

4

3

2

Tuesday, March 23, 2010

MS-168x

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

1

Sheet ofDate:

252

Sheet ofDate:

252

Sheet ofDate:

252

0A

0A

0A

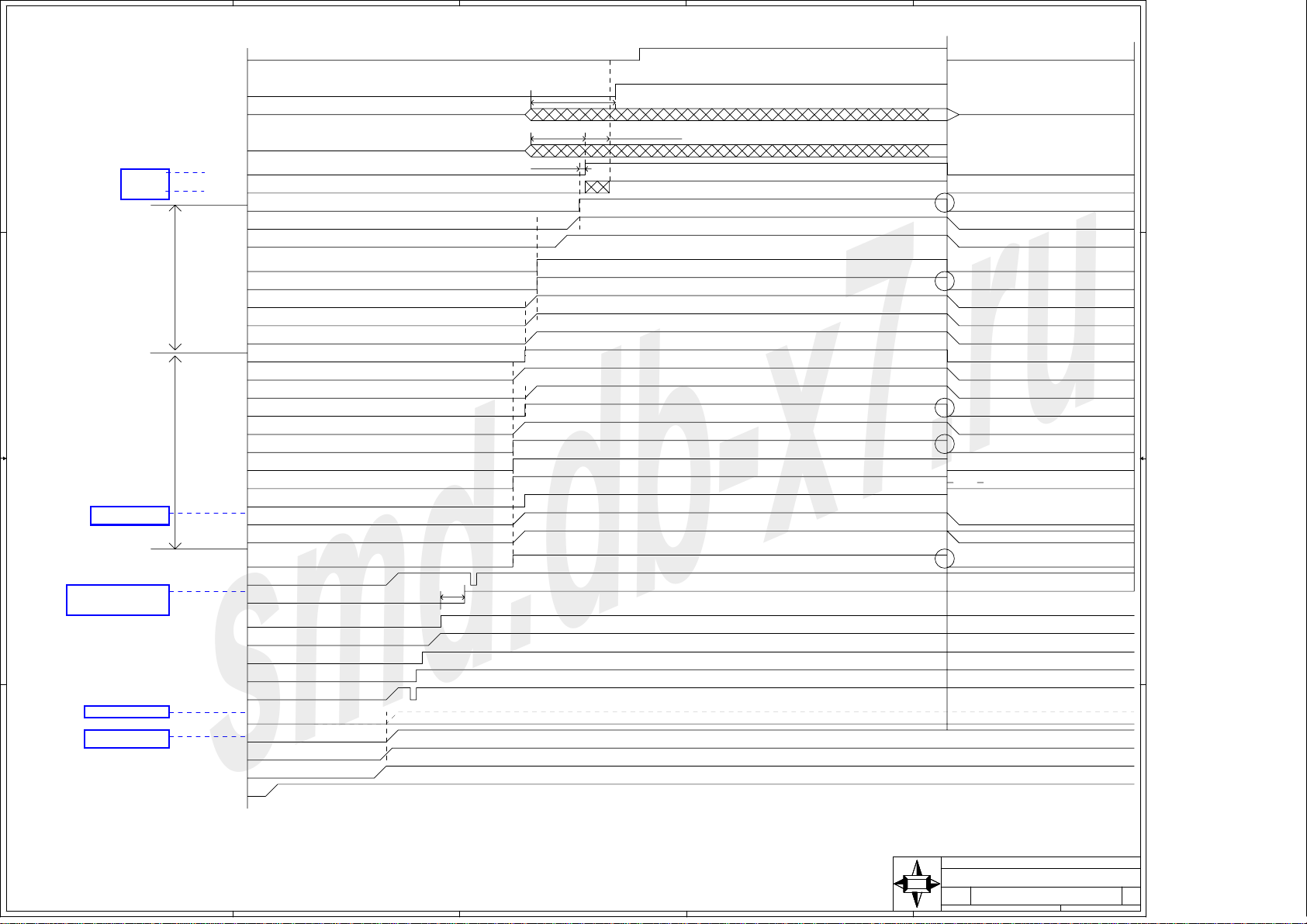

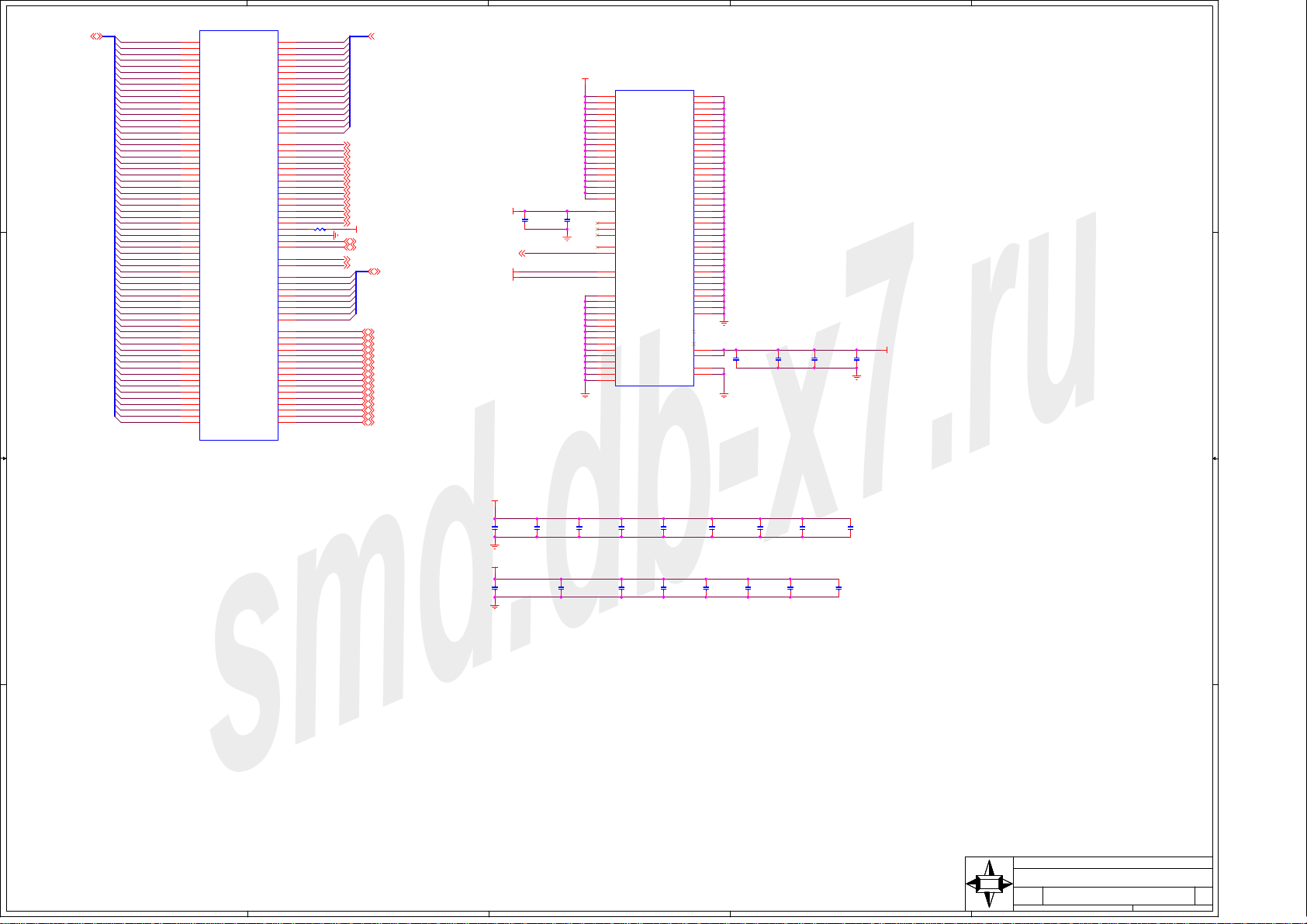

Page 3

5

smd.db-x7.ru

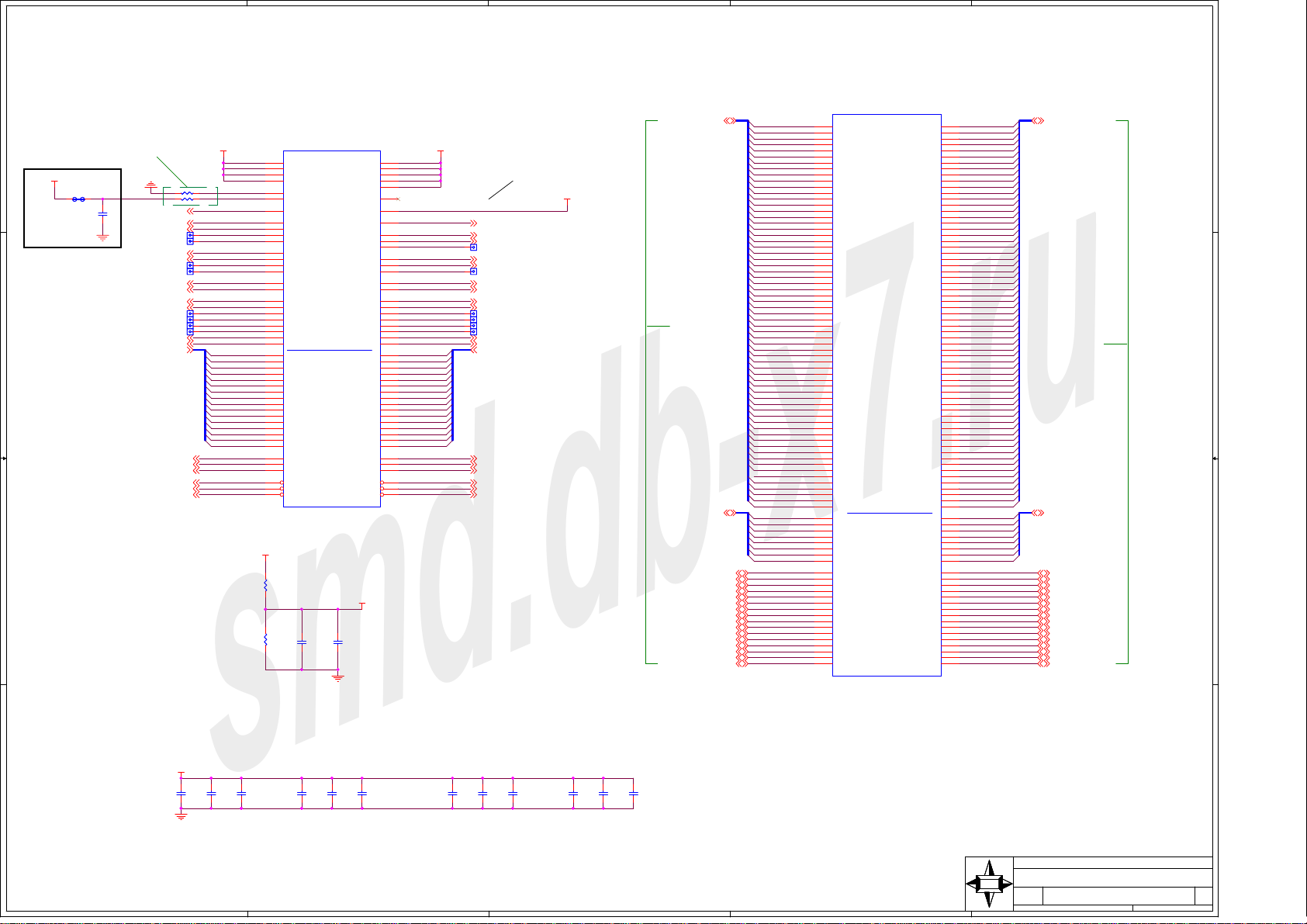

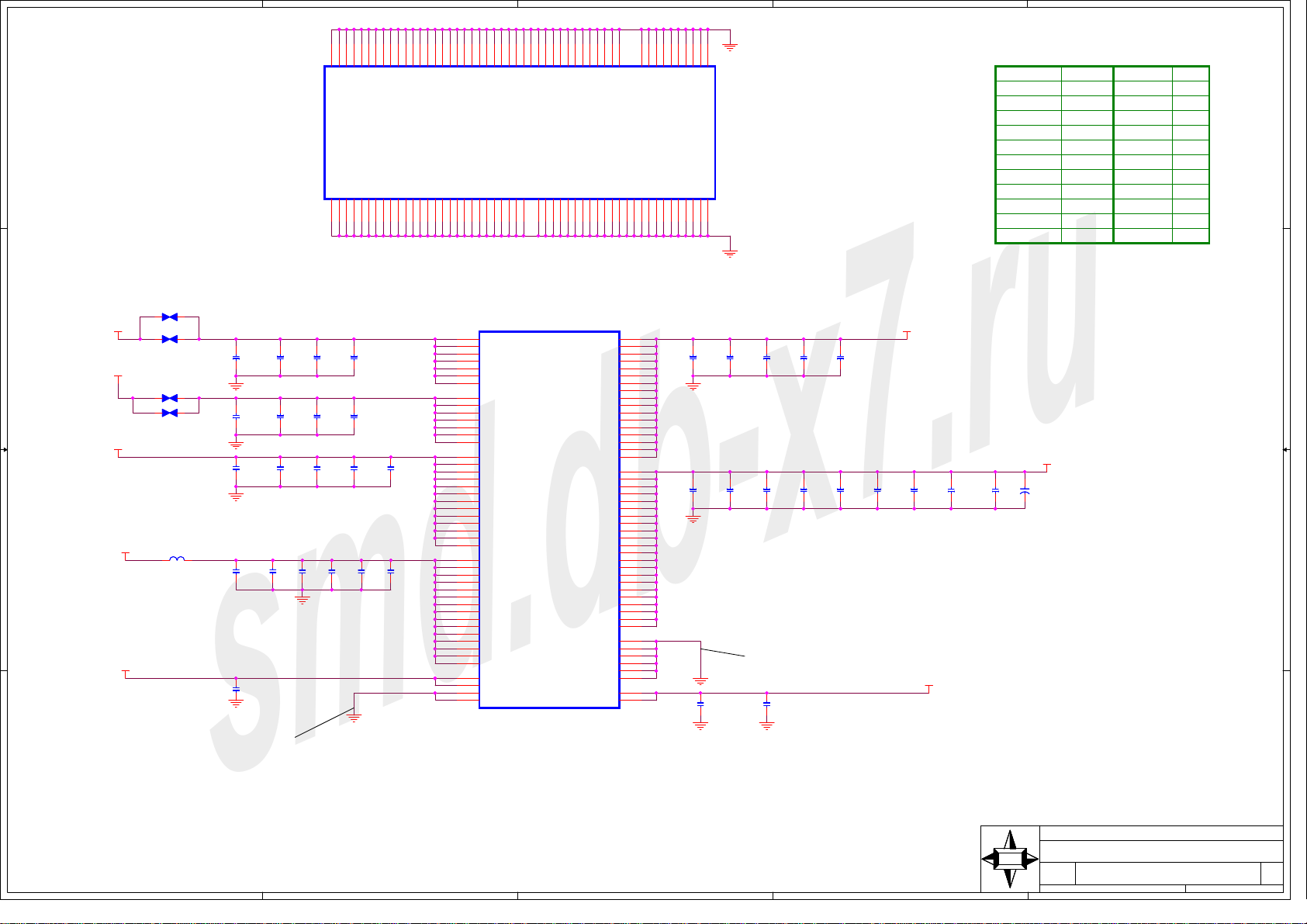

BATTERY

11.1V 62WHr

D D

AC ADAPTOR

15-16V 90W

C C

B B

A A

5

BATTERY

CHARGER

MAX1535

+VIN

CPU_VDDIO_SUS

+5VDUAL

+3.3VDUAL

+1.1V DUAL

+1.1V

+3.3VDUAL

+1.5V

4

CPU core

PWM

MAX17009

CPU core

PWM

MAX8792

DDR3 PWM

LDO VTT

MAX8632

+1V~1.2V SW

+1.1V SW

MAX8775

+1.2V SW

MAX8716-1/2

+1.8V SW

MAX8716-2/2

SW

OZ9956

+5V SW

+3V SW

+5V LDO

+3V LDO

MAX1533

SW

MAX1714

SWITCH

SWITCH

SWITCH

2.5V LDO

SWITCH

1.0V LDO

1.5V LDO

SWITCH

4

CPU_VDD_RUN@38A

CPU_VDDNB_RUN@4A

CPU_VDDIO_SUS@9A

MEM_VTT@1.5A

VLDT (1.1V/1.2V)

+VCC_NB_RUN

+1.1VDUAL@10A

+1.8V@3.3A

VDD_LED_BL_RUN

+3.3VALW

+5VALW

+3.3VDUAL@8A

+5VDUAL@8A

+1.5V@5A

+5V

+3.3V

CPU_VDDA_RUN +3.3V

+1.1V

+1.0V

S3,S4,S5

S0

+1.5V

+1.5VDUAL

3

+5V

VLDT

+1.1V

+1.1V

+1.8V

+1.1V

+3.3V

+1.8V

+1.1V

+3.3V

+1.1V

+3.3V

+3.3VDUAL

+1.1VDUAL

+1.1V

+1.1V

VDDIO_GBE_S/2

+3.3VDUAL

+1.1VDUAL

PHY_VDDIO_DUAL

+3.3VDUAL

+1.1VDUAL

+1.1VDUAL

AZ_VDDIO_DUAL

+1.1VDUAL

+3.3V

+1.1V

+3.3VDUAL

+3.3VDUAL

+3.3VDUAL

MXM_EN

+3.3V

+5V

+VIN

3

VLDT

AOZ1024

PWM

+VCC_NB

+3.3V

+1.8V

+1.5V

+1.5V

+3.3V

+1.8V

+3.3V

+1.8V

CPU_VDDA_RUN

CPU_VDD_RUN

CPU_VDDNB_RUN

BEAD

CPU_VDDIO_SUS

VDDR

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

AMD SB800

VDDIO_33_PCIGP 3.3V 0.020A

VDDIO_18_FC 1.8V 0.050A

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

SW

SW

Sensor

Resistor

VDDAN_11_PCIE 1.1V 1A

VDDPL_33_PCIE 3.3V 0.030A

VDDAN_11_SATA 1.1V 0.8A

VDDPL_33_SATA 3.3V 0.020A

VDDAN_33_USB_S 3.3V 0.2A

VDDAN_11_USB_S 1.2V 0.2A

VDDCR_11 1.1V 0.5A

VDDAN_11_CLK 1.1V 0.4A

VDDIO_33_GBE_S 3.3V

VDDCR_11_GBE_S 1.1V

AMD S1G4

VCCA 2.5V

VDD CORE

1.375-1.500V 36A

VDDNB CORE

0.9V 4A

VLDT 1.2V TPDA

VDD MEM TPDA

VDDR 1.5A

RS880M

VDDHTTX 1.2V 0.68A

VDDHTRX+HT 1.1V 0.68A

VDDPCIE 1.1V 1.1A

VDDA18 1.8V 0.64A

VDDC 1.0V-1.1V 7.6A

VDDG33 3.3V 0.06A

VDDG18 1.8V 0.005A

VDD18_MEM 1.8V 0.005A

VDD_MEM 1.8V 0.23A

AVDD 3.3V 0.125A

VDDLT18 0.22A

VDDLT33 0A

PLLs 1.8V 0.1A

PLLs 1.1/1.2V 0.23A

VDDRF_GBE_S

VDDIO_GBE_S 3.3V

VDDIO_33_S 3.3V

VDDCR_11_S 1.1V

VDDCD_11_USB 1.1V

VDDIO_AZ_S 3.3V OR 1.5V

VDDCR_11_USB_S 1.1V

VDDPL_33_SYS 3.3V SYS PLL

VDDPL_11_SYS 1.1 V SYS PLL

VDDPL_33_USB_S 3.3 V USB PLL

VDDAN_33_S 3.3V HWM

VDDXL_33_S 3.3V

MXM HE 3.0

MXM_VDD_3.3V 1A

MXM_VDD_5V 2.5A

MXM_VDD_MAIN upto 10A

2

CPU_VDDIO_SUS

MEM_VTT

BEAD

+1.5V

BEAD

+3.3V

+1.1V

BEAD

+1.5V

BEAD

+3.3V

BEAD

DDRiII SODIMMX2--SYSTEM

VDD MEM 4A

VTT_MEM 0.5A

CLOCK GEN

1.2V 0.2A

3.3V

1.1V 0.5A

HD CODEC

1.5V CORE 0.3A

3V ANALOG 0.1A

1

AUDIO

OP

GBIT ETHERNET

+3.3VDUAL

+3.3V

+5V

+5V

VDD_LED_BL_RUN

+VIN

+5VDUAL

+1.5V

+3.3V

+3.3VDUAL

+1.5V

+3.3VDUAL

+3.3V

+5V

+5V

+3.3V

+1.0V

+3.3V

+1.8V

+3.3VDUAL

2

BEAD

+3.3VDUAL

SW

BEAD

+VIN

+3.3V

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

3.3V 0.5A

SMSC1100--EC

3.3V 0.5A

LCD PANEL

3.3V 1.5A

5V 0.5A

BACK LIGHT

+5V

LED_BL

+VDD_MAIN

USB X2 FR

5VDual

EXPRESS CARD

1.5V (S0, S1) 0.7A

3.3V (S0, S1) 1.3A

3.3V (S3, S5) 0.3A

MINI PCIE SLOT0,1,2

1.5V (S0, S1) 0.5A

each

3.3V (S3, S5) 2.75A

each

SATA HD0,1

3.3V (S0, S1) TBD

5V (S3, S5) TBD

SATA ODD

5V (S0, S1) TBD

uPD720200

3.3V (S0, S1) TBD

1.0V (S0, S1) TBD

OZ8888

3.3V (S0, S1) 0.5A

1.8V (S0, S1) 0.5A

Desktop x1 PCIE

+12V

+3.3V

+3.3Vaux

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-168x

MS-168x

MS-168x

POWER DELIVERT

POWER DELIVERT

Tuesday, March 23, 2010

Tuesday, March 23, 2010

Tuesday, March 23, 2010

POWER DELIVERT

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

1

0A

0A

352

352

352

0A

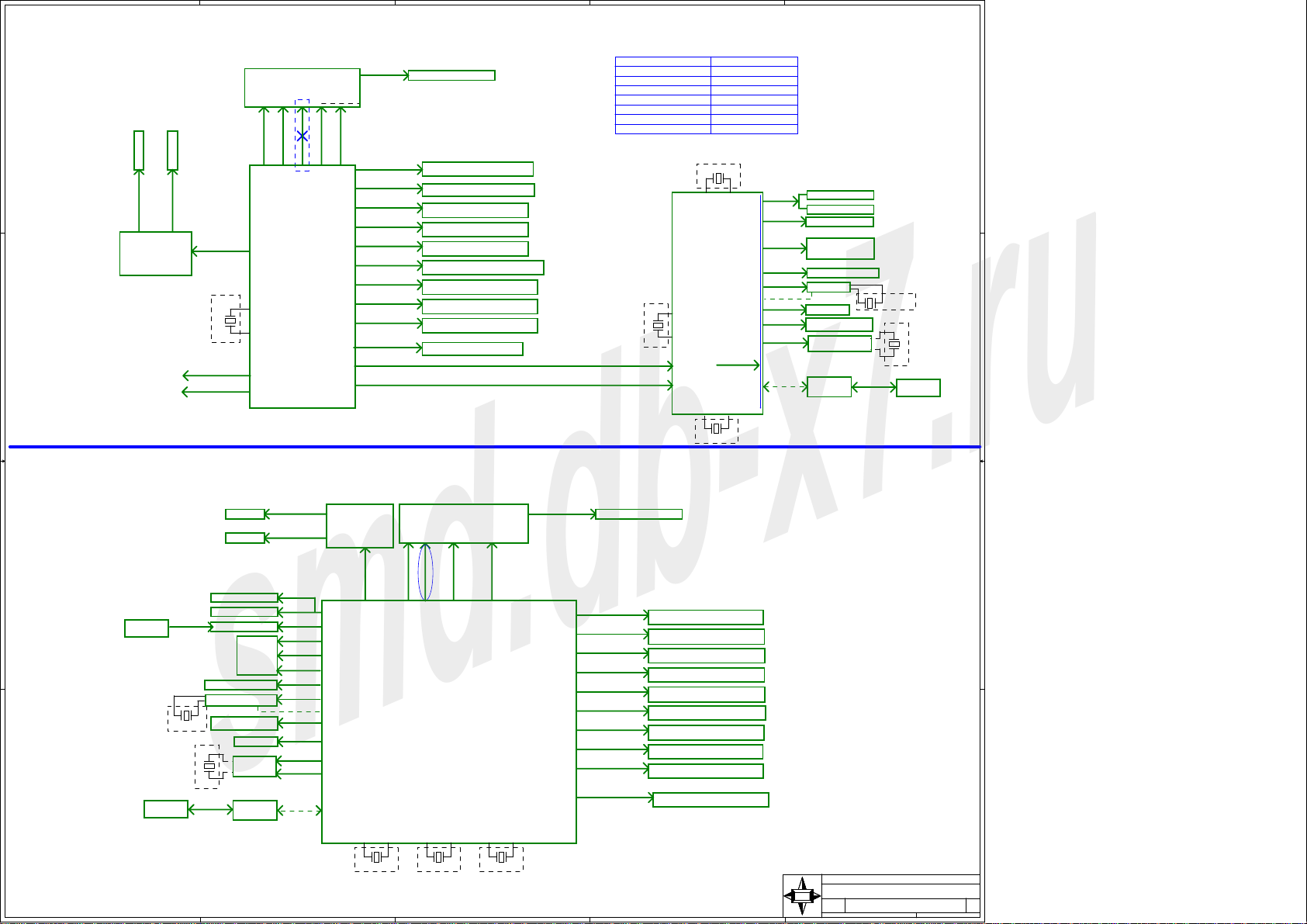

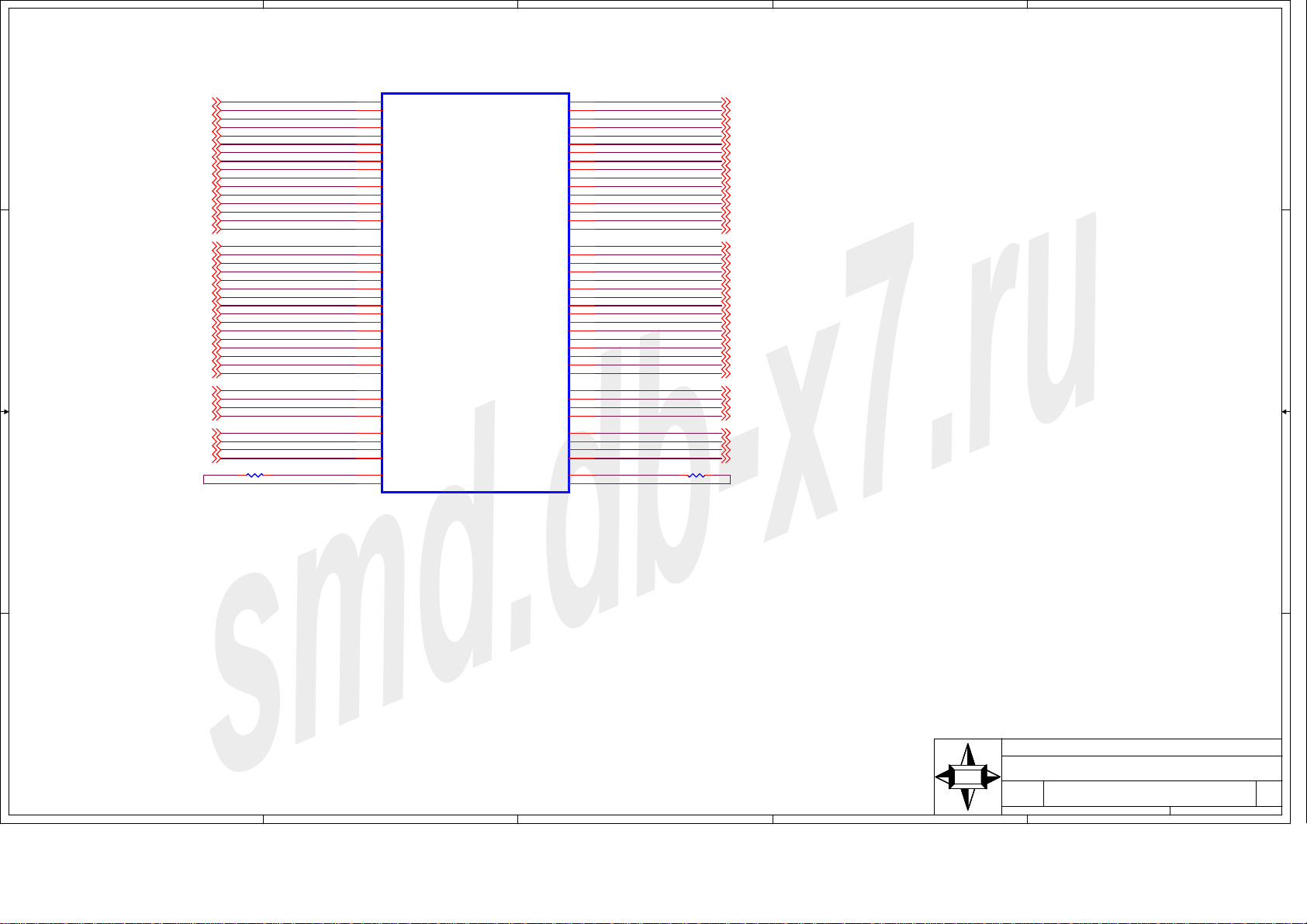

Page 4

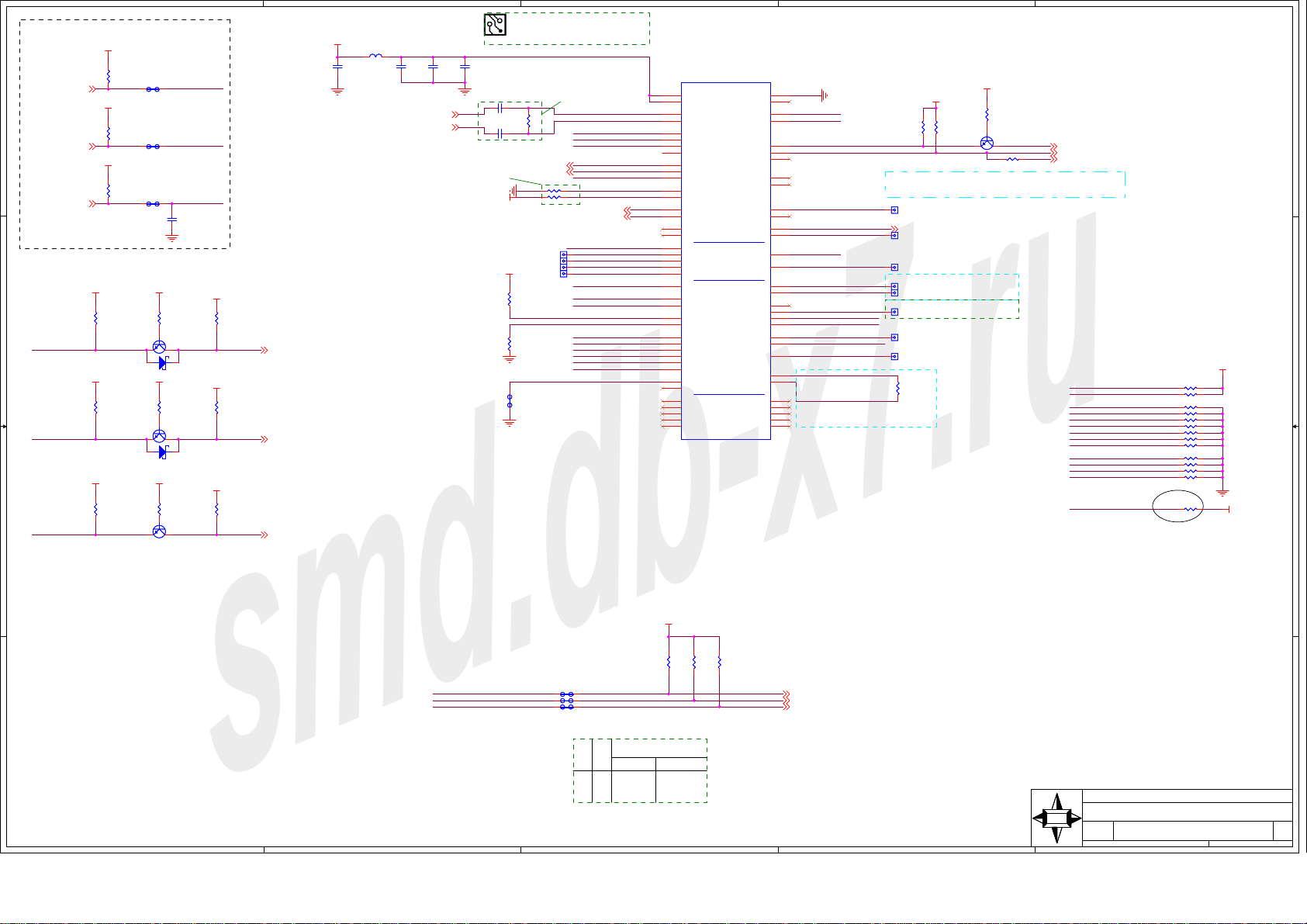

Power on Sequence required:

smd.db-x7.ru

SB800:

1, +3.3VDUAL ramp before +1.1VDUAL

2, +3.3V ramp before +1.8v

3, +1.8V ramp before +1.1v

4, +3.3v ramp before +1.1v

5, +3.3VALW_R ramping down time > 300us

6, 50uS <= All power rails except +3.3VALW_R <= 40mS

7, 100uS <= +3.3VALW_R <= 40mS

RS880:

1, 0 <(+3.3V) - (+1.8v) < 2.1

D D

2, +1.8V ramp before +1.1v

3. +1.1V ramp before VCC_NB

C C

B B

CPU_THM/SB/SB_SCL1/2

SB_KB/SPI/LPC ROM PWRS

A A

5

SB OUTPUT

SB INPUT

CPU MEM CTL &

DDR3 SODIMM PWRS

KBC is ready

KBC is powered by

A_VBAT & +3.3VALW

CPU_LDT_RST#

(SB TO CPU)

CPU_PWROK

(SB TO CPU)

CPU_CLKP/N running

NB_PWRGD

NB_PWRGD_IN

+1.2V_PWRGD

VCC_NB

+1.1V

VRM_PWRGD

CPU_VDDR

CPU_VDD_RUN

CPU_VDDNB_RUN

VDDA_PWRGD

+2.5V_LDO

(CPU_VDDA_2.5_RUN)

1V8_PWRGD

GROUP A GROUP B

+5V/+3.3V

RUN_EN_HIGH

RUN_EN_LOW

VDD_BOOST_LOW

SLP_S3#

VDRAM_PWRGD

MEM_VTT

MEM_VREF

CPU_VDDIO_SUS

SLP_S5#

PWR_BTN#_EC

V3V5DUAL_PWRGD

1V1DUAL_PWRGD

SYSTEM_DUAL_PG_DELAY

RSMRST#

DUAL RAILS

VDD_DUAL_EN

VDD_DUAL_EN_EC

PWR_BTN#_HW

PWR_BTN#_SB

AC_OK

(ACIN detect)

+5VALW/+3.3VALW

LDO:5.4V

(from DCIN)

+VIN/+12V_HD

A_VBAT

1)+1.5V SWITCH TO +1.5VDUAL 2)LASSO_PWRON 3)LPCPD# for TPM 4) TO SB&KBCSB_PWRGD

+VLDT

+1.5V

+1.8V

VTT only will be shut down in S3 mode, and VTT for DDR3 SODIMM only.

4

RC=0

Power button from EC to SB

20mS

delay

+5VDUAL/+3.3VDUAL/+1.5VDUAL/+1.1VDUAL

When IMC, always on at all time( always PWR)

Power button pressed

AC not present scenario = LOW AC present= high

Battery inserted/AC IN

3

Req.

>1 mS

>1 mS Req.

running

>1 mS Req.

RC=~22ms

RC=~4.7ms

VRM_PWRGD AND 1V8_PWRGD

RC=0

RC=0

RC=0

VCC_NB(all NB power) valid before NB_PWRGD.

+1.2V_PWRGD

VCC_NB should not ramp before 1.1v

SLP_S3#

SYS_RST#

1V1DUAL_PWRGD

1V5_PWRGD/DNI

KBC_GPIO77/DNI

2

to S3

1

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-168x

MS-168x

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Tuesday, March 23, 2010

Tuesday, March 23, 2010

5

4

3

2

Tuesday, March 23, 2010

MS-168x

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

1

Sheet ofDate:

452

Sheet ofDate:

452

Sheet ofDate:

452

0A

0A

0A

Page 5

5

smd.db-x7.ru

4

3

2

1

EXTERNAL CLOCK MODE

SPM_CLK

SIDE PORT MEMORY CHIP

NB_OSC

100MHZ

14.318MHZ

xxxMHZ

GFX_CLKP/N

100MHZ

PCIE_DT_CLKP/N

100MHZ

PCIE_1394_CLKP/N

100MHZ

PCIE_PE0_CLKP/N

100MHZ

PCIE_PE1_CLKP/N

100MHZ

PCIE_EXPCARD_CLKP/N

100MHZ

PCIE_PE2_CLKP/N

100MHZ

PCIE_LAN_CLKP/N

100MHZ

PCIE_USB30_CLKP/N

100MHZ

PCIE_PE3_CLKP/N

100MHZ

CLK_REQ in CLK GEN

PCIE GFX SLOT (RS880M, 16 LANES)

EXT_MXM_CLKREQ#

PCIE GPP SLOT (RS880M, 2 LANES)

EXT_PCIE_DT_CLKREQ#

PCIE GPP I/F (RS880M, 1 LANE)

EXT_PCIE_1394_CLKREQ#

MINIPCIE SLOT (RS880M, 1 LANE)

EXT_PCIE_PE0_CLKREQ#

MINIPCIE SLOT (SB800, 1 LANE)

EXT_PCIE_PE1_CLKREQ#

PCIE NEW CARD SLOT (SB800, 1 LANE)

EXT_PCIE_EXPCARD_CLKREQ#

MINIPCIE SLOT (SB800, 1 LANE)

EXT_PCIE_PE2_CLKREQ#

PCIE GPP I/F (RS880M, 1 LANE)

EXT_PCIE_LAN_CLKREQ#

PCIE GPP I/F (RS880M, 1 LANE)

EXT_PCIE_USB30_CLKREQ#

MINIPCIE SLOT (SB800, 1 LANE)

EXT_PCIE_PE3_CLKREQ#

PORT3:WLAN

MXM SLOT

PCIe x4 SLOT

1394:OZ888GS0L3N

PORT0:WLAN

PORT1:WWAN

EXPRESS CARD

PORT2:WUSB

BCM57760A0KMLG

USB3.0:uPD720200F

AMD NORTHBRIDGE

RS880M

A-LINK

GPP_REFCLK

D D

100MHZ

100MHZ

100MHZ

GPP REF_CLK

A_SODIMM

B_SODIMM

MEM_MB_CLK1_P/N

MEM_MB_CLK2_P/N

MEM_MA_CLK1_P/N

MEM_MA_CLK2_P/N

KBC_OSC

SB_OSC

CPU_CLKP/N

200MHZ

DNI

AMD

SIG4 CPU

C C

NBLINK_RCLKP/N

EXTERNAL

CLOCK GENERATOR

14.31818MHz

HT_REFCLKP/N

NB_GFX_REFCLKP/N

NB CLOCK INPUT TABLE

NB CLOCKS

HT_REFCLKP

HT_REFCLKN

REFCLK_P

REFCLK_N

GFX_REFCLK

GPP_REFCLK

GPPSB_REFCLK 100M DIFF

* RS880M can be used as clock buffer to output two PCIE referecence clocks

By deault, chip will configured as input mode, BIOS can program it to output mode.

AMD SB800

EXT CLK MODE

FOR SATA

25M Hz

SATA_X1

DNI

SATA_X2

SBSRC_CLKP/N

CLK_48M_USB

100MHZ

48MHZ

PCIE_RCLKP/N

USBCLK

25M Hz

25M_X1

14M_25M_48M_OSC

32.768K Hz

RS880M

100M DIFF

100M DIFF

14M SE (1.1V)

vref

100M DIFF(IN/OUT)*

NC or 100M DIFF OUTPUT

PCICLK0

25M_X2

PCICLK1

PCICLK2

PCICLK3

PCICLK4

LPCCLK0

LPCCLK1

RTCCLK

AZ_BITCLK

SPI_CLK

GBE_RXCLK

GBE_TXCLK

PCI_CLK0

33MHZ

SMSC_CLK

33MHZ

PCI_CLK2

PCI_CLK3

PCI_CLK4

33MHZ

LPC_CLK0

33MHZ

LPC_CLK1

33MHZ

AZ_BIT_CLK

24MHZ

SPI_CLK

xxHZ

SB_25MHz_PHY

GBE_TX/RXCLK

IMC_IM_CLK

SPCI MICTOR

PSOT CODE LED

KBC1100L

STRAPS SETTING,

UNUSED CLOCKS

LPC BIOS & HEADER

LPC TPM

HD AUDIO

SPI ROM & HEADER

GBE PHY

MOUSE

TOUCH PAD

IM_CLK

32.768K Hz

25M Hz

KBC1100L

INTERNAL CLOCK MODE

MEM_MA_CLK1_P/N

MEM_MA_CLK2_P/N

A_SODIMM

MEM_MB_CLK1_P/N

MEM_MB_CLK2_P/N

B_SODIMM

B B

SPCI MICTOR

OSCILLATOR

14.318MHZ

32.768K Hz

PSOT CODE LED

KBC1100L

LPC BIOS & HEADER

LPC TPM

SPI ROM & HEADER

25M Hz

STRAPS

SETTING,

UNUSED

CLOCKS

HD AUDIO

GBE PHY

A A

5

KBC1100L

IM_CLK

MOUSE

TOUCH PAD

33MHZ

PCI_CLK0

SMSC_CLK

33MHZ

PCI_CLK2

33MHZ

PCI_CLK3

33MHZ

PCI_CLK4

33MHZ

LPC_CLK0

33MHZ

LPC_CLK1

33MHZ

SPI_CLK

xxHZ

AZ_BIT_CLK

24MHZ

SB_25MHz_PHY

25MHZ

GBE_RXCLK

GBE_TXCLK

IMC_IM_CLK

4

AMD

SIG4 CPU

200MHZ

CPU_CLKP/N

PCICLK0

PCICLK1

PCICLK2

CPU_HT_CLKP/N

PCICLK3

PCICLK4

LPCCLK0

LPCCLK1

RTCCLK

SPI_CLK

AZ_BITCLK

14M_25M_48M_OSC

GBE_RXCLK

GBE_TXCLK

PS2M_CLK

FOR MASTER FOR RTC FOR SATA

25M Hz

AMD NORTHBRIDGE

RS880M

REFCLKP/N

A-LINK

100MHZ

100MHZ

100MHZ

NB_REFCLK_P/N

SB_NBLINK_RCLKP/N

NB_GFX_REFCLKP/N

PCIE_RCLKP/N

GPP_CLK6P/N

NB_DISP_CLKP/N

AMD SB800

CLOCK GENERATOR

32.768K Hz

GPP_REFCLK

HT_REFCLKP/N

NB_HT_CLKP/N

25M Hz

3

100MHZ

DNI

SPM_CLK

xxxMHZ

SLT_GFX_CLKP/N

GPP_CLK5P/N

GPP_CLK8P/N

GPP_CLK1P/N

GPP_CLK4P/N

GPP_CLK0P/N

GPP_CLK2P/N

GPP_CLK3P/N

GPP_CLK7P/N

GPP_CLK6P/N

SIDE PORT MEMORY CHIP

GFX_CLKP/N

100MHZ

PCIE_DT_CLKP/N

100MHZ

PCIE_1394_CLKP/N

100MHZ

PCIE_PE0_CLKP/N

100MHZ

PCIE_PE1_CLKP/N

100MHZ

PCIE_EXPCARD_CLKP/N

100MHZ

PCIE_PE2_CLKP/N

100MHZ

PCIE_LAN_CLKP/N

100MHZ

PCIE_USB30_CLKP/N

100MHZ

PCIE_PE3_CLKP/N

100MHZ

PCIE GFX SLOT (RS880M, 16 LANES)

CLK_REQG# in SB

PCIE GPP SLOT (RS880M, 2 LANES)

CLK_REQ5 in SB

PCIE GPP I/F (RS880M, 1 LANE)

CLK_REQ8 in SB

MINIPCIE SLOT (RS880M, 1 LANE)

CLK_REQ1 in SB

MINIPCIE SLOT (SB800, 1 LANE)

CLK_REQ4 in SB

PCIE NEW CARD SLOT (SB800,1 LANE)

CLK_REQ0 in SB

MINIPCIE SLOT (SB800, 1 LANE)

CLK_REQ2 in SB

PCIE GPP I/F (RS880M, 1 LANE)

CLK_REQ3 in SB

PCIE GPP I/F (RS880M, 1 LANE)

CLK_REQ7 in SB

MINIPCIE SLOT (SB800, 1 LANE)

CLK_REQ6 in SB

2

MXM SLOT

PCIe x4 SLOT

1394:OZ888GS0L3N

PORT0:WLAN

PORT1:WWAN

EXPRESS CARD

PORT2:WUSB

BCM57760A0KMLG

USB3.0:uPD720200F

PORT3:WLAN

MSI

MSI

MSI

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-168x

MS-168x

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

CLOCK BLOCK

CLOCK BLOCK

CLOCK BLOCK

Tuesday, March 23, 2010

Tuesday, March 23, 2010

Tuesday, March 23, 2010

MS-168x

1

Sheet ofDate:

552

Sheet ofDate:

552

Sheet ofDate:

552

0A

0A

0A

Page 6

5

smd.db-x7.ru

Thermal Systems

(Emergency Shutdown, Throttling, Fan Control)

4

3

2

1

translate1.5V TSI 3.3V TSI

THERMTRIP_L

D D

MEMHOT_L

ALERT_L

THERMDC

THERMDA

SID

SIC

AMD

translate

translate

translate

VRM Power

VRM_HOT#

S1G4

PROCHOT_L

translate

ADM

C C

SO-DIMM

EVENT

MXM

THERM#

SDA

SCL

1032

Thermal disaster prevention is implemented by PROCHOT_L and THERMTRIP_L with hardware

non-system dependant functions. Fan speed control will only be implemented

by SB TSI software based implementation

B B

Global

System

State

A A

G2

G2/G3

Power State / Voltage Rail Activity Summary

Processor

Sleep

State

G0

G0

G0

G0

G0

G0

G1

G1

G2

S5 LOW

G3

Power

State

S0

S0

S0

S0

S0

S0

S1

S3

S4

S5

C0

C0

C1

C2

C3

c4

OFF

OFF

OFF

OFF

OFF

OFF

5

Running

Running

Sleeping

Description

P-state transitions

Powered on suspend

Suspend to diskON

Soft-off

Battery IN

Mechanical off

KBC

SMSC

NON-POP

OVERRIDE#translate

PWM

TACH

4-PIN CPU FAN

NON-POP

under OS control

Halt

Stop grant,

caches snoopable

TBD

TBD

Suspend to RAM

G7

THERMTRIP#

SDA3

(S5-S0)

SCL3

T7

(S0)

TALERT#

Y9

FANOUT2

AMD

W18

SDA0AA18

SB800

SCL0

B6

TEMPIN0

C6

TEMP_COMM

F24

PROCHOT#

M8

FANOUT0

P5

FANIN0

TEMPIN3

J4

GEVENT4#

SCL2

SDA2

Place under DDR

TEMP

SENSOR

(Q600)

ADM

1032

RTC ALW DUAL

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

ON

4

TEMPIN1

TEMP_COMM

TEMPIN2

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

OFF

A6

C6

THERMDC

THERMDA

SUS RUN

ON

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

OFF

OFF

NON-POP

AMD

RS880

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

OFF

OFF

OFF

SMBus Block Diagram

(S5-S0)

DUAL_SMB1

BCM57760

LAN

U1300

mini

PCI Exp x1 SO-DIMM

J3700

mini

PCI Exp x1

J3703

mini

PCI Exp x1

J3711

mini

PCI Exp x1

J3712

GPP Slot

J3701

Exp Card

J2500

Group Name Description

INT: Stuff when use internal clock generator

EXT: Stuff when use external clock generator

DNI: DO NOT INSTALL

KBC: Stuff when use external KBC

IMC: Stuff when use internal EC

A11:Resistors marked with "A11" is only for SB800A11 ONLY.

3

DDR 2

SO-DIMM

J400

DDR 2

J401

CLK. Gen.

ICS9LPRS470

U800

MXM

J3600

CONFIG ROM

U1001

LCP Debug Header

J1000

ADM1032

Diode Reader

U204

POP

NOPOP

NOPOP

SDATA1

SCLK1

SDATA0

SCLK0

SDATA2

SCLK2

NOPOP

CPU Thermal

Sensor

ADM1032

AMD

SB800

(master)

SDA1

(S5-S0)

SCL1

ASF Only

SDA0

(S0)

SCL0

SDA2

SCL2

(S5-S0)

(S5-S0)

1.8V

SDA3

SCL3

AMD

S1G4

SVC

CPU Core PWR PWM

SVD

(S5-S0)

I2C1A_DAT

I2C1A_CLK

I2C1B_DAT

I2C1B_CLK

KBC1100L

MS-168x

MS-168x

MS-168x

SMBUS BLOCK

SMBUS BLOCK

SMBUS BLOCK

MAX17009

U2800

SMSC

U103

(master)

1

(S5-S0)

(S5-S0)

Sheet ofDate:

652

Sheet ofDate:

652

Sheet ofDate:

652

0A

0A

0A

100R

(S3-S0)

SVC

SVD

J106

translate

POP

BAT_DAT

BAT_CLK

MSI

MSI

MSI

POP

3.3V SB-TSI

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Tuesday, March 23, 2010

Tuesday, March 23, 2010

Tuesday, March 23, 2010

SIC

SID

TL2560

SDA

light sensor

SCL

U3201

smart

battery

J2700

MAX1535

battery charger

U2700

2

Page 7

5

smd.db-x7.ru

4

3

2

1

D D

U20A

+1.1VRUN

HT_NB_CPU_CAD_H013

HT_NB_CPU_CAD_L013

HT_NB_CPU_CAD_H113

HT_NB_CPU_CAD_L113

HT_NB_CPU_CAD_H213

HT_NB_CPU_CAD_L213

HT_NB_CPU_CAD_H313

HT_NB_CPU_CAD_L313

HT_NB_CPU_CAD_H413

HT_NB_CPU_CAD_L413

C C

B B

HT_NB_CPU_CAD_H513

HT_NB_CPU_CAD_L513

HT_NB_CPU_CAD_H613

HT_NB_CPU_CAD_L613

HT_NB_CPU_CAD_H713

HT_NB_CPU_CAD_L713

HT_NB_CPU_CAD_H813

HT_NB_CPU_CAD_L813

HT_NB_CPU_CAD_H913

HT_NB_CPU_CAD_L913

HT_NB_CPU_CAD_H1013

HT_NB_CPU_CAD_L1013

HT_NB_CPU_CAD_H1113

HT_NB_CPU_CAD_L1113

HT_NB_CPU_CAD_H1213

HT_NB_CPU_CAD_L1213

HT_NB_CPU_CAD_H1313

HT_NB_CPU_CAD_L1313

HT_NB_CPU_CAD_H1413

HT_NB_CPU_CAD_L1413

HT_NB_CPU_CAD_H1513

HT_NB_CPU_CAD_L1513

HT_NB_CPU_CLK_H013

HT_NB_CPU_CLK_L013

HT_NB_CPU_CLK_H113

HT_NB_CPU_CLK_L113

HT_NB_CPU_CTL_H013

HT_NB_CPU_CTL_L013

HT_NB_CPU_CTL_H113

HT_NB_CPU_CTL_L113

U20A

D1

VLDT_A0

D2

VLDT_A1

D3

VLDT_A2

D4

VLDT_A3

E3

L0_CADIN_H0

E2

L0_CADIN_L0

E1

L0_CADIN_H1

F1

L0_CADIN_L1

G3

L0_CADIN_H2

G2

L0_CADIN_L2

G1

L0_CADIN_H3

H1

L0_CADIN_L3

J1

L0_CADIN_H4

K1

L0_CADIN_L4

L3

L0_CADIN_H5

L2

L0_CADIN_L5

L1

L0_CADIN_H6

M1

L0_CADIN_L6

N3

L0_CADIN_H7

N2

L0_CADIN_L7

E5

L0_CADIN_H8

F5

L0_CADIN_L8

F3

L0_CADIN_H9

F4

L0_CADIN_L9

G5

L0_CADIN_H10

H5

L0_CADIN_L10

H3

L0_CADIN_H11

H4

L0_CADIN_L11

K3

L0_CADIN_H12

K4

L0_CADIN_L12

L5

L0_CADIN_H13

M5

L0_CADIN_L13

M3

L0_CADIN_H14

M4

L0_CADIN_L14

N5

L0_CADIN_H15

P5

L0_CADIN_L15

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

SOCKET_638_PIN

SOCKET_638_PIN

HT LINK

HT LINK

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

+1.1VRUN

HT_CPU_NB_CAD_H0 13

HT_CPU_NB_CAD_L0 13

HT_CPU_NB_CAD_H1 13

HT_CPU_NB_CAD_L1 13

HT_CPU_NB_CAD_H2 13

HT_CPU_NB_CAD_L2 13

HT_CPU_NB_CAD_H3 13

HT_CPU_NB_CAD_L3 13

HT_CPU_NB_CAD_H4 13

HT_CPU_NB_CAD_L4 13

HT_CPU_NB_CAD_H5 13

HT_CPU_NB_CAD_L5 13

HT_CPU_NB_CAD_H6 13

HT_CPU_NB_CAD_L6 13

HT_CPU_NB_CAD_H7 13

HT_CPU_NB_CAD_L7 13

HT_CPU_NB_CAD_H8 13

HT_CPU_NB_CAD_L8 13

HT_CPU_NB_CAD_H9 13

HT_CPU_NB_CAD_L9 13

HT_CPU_NB_CAD_H10 13

HT_CPU_NB_CAD_L10 13

HT_CPU_NB_CAD_H11 13

HT_CPU_NB_CAD_L11 13

HT_CPU_NB_CAD_H12 13

HT_CPU_NB_CAD_L12 13

HT_CPU_NB_CAD_H13 13

HT_CPU_NB_CAD_L13 13

HT_CPU_NB_CAD_H14 13

HT_CPU_NB_CAD_L14 13

HT_CPU_NB_CAD_H15 13

HT_CPU_NB_CAD_L15 13

HT_CPU_NB_CLK_H0 13

HT_CPU_NB_CLK_L0 13

HT_CPU_NB_CLK_H1 13

HT_CPU_NB_CLK_L1 13

HT_CPU_NB_CTL_H0 13

HT_CPU_NB_CTL_L0 13

HT_CPU_NB_CTL_H1 13

HT_CPU_NB_CTL_L1 13

+1.1VRUN

[DG] VLDT total CAP >30uF

*

C352

C352

4.7uF

4.7uF

C361

C361

4.7uF

4.7uF

C360

C360

22uF

22uF

C353

C353

0.22uF

0.22uF

C342

C342

0.22uF

0.22uF

C341

C341

180pF

180pF

Place close to socket

* If VLDT is connected only on one side,

one 4.7uF cap should be added to

the island side

[ChckList] Can change 22u*1/4.7u*2 to 10u*3

K26

J26

F26

G26

H26

D26

E26

G25

C25

F25

B25

K25

H25

E25

D25

J25

G24

A24

C24

F24

K24

H24

E24

B24

D24

J24

C23

G23

F23

H23

K23

A23

E23

J23

B23

D23

H22

F22

A22

K22

E22

J22

C22

G22

B22

D22

D21

H21

J21

F21

A21

K21

E21

C21

G21

B21

A20

F20

K20

E20

C20

J20

H20

B20

D20

A19

E19

H19

F19

K19

D19

C19

B19

A18

F18

G18

E18

H18

K18

D18

J18

C18

B18

G17

K17

H17

E17

F17

A17

J17

B17

D17

C17

K16

B16B3H16

E16

F16

A16

J16

D16

C16

G16

K15

A15

E15

D15

C15

G15

B15

F15

G14

J14

K14

E14

H14

A14

F14

D14

B14

C14

B13

K13

D13

J13

E13

H13

A13

F13

G13

C13

F12

C12

K12

E12

D12

H12

A12

G12

J12

B12

F11

H11

G11 AD11

C11

K11

D11

E11

J11

A11

B11 AB11

J10

G10

K10

F10

C10

D10

H10

B10

A10

E10

C9

K9

D9

J9

H9

F9

A9

E9

G9

B9

K8

H8

F8

D8

A8

C8

J8

B8

E8

B7

H7

K7

C7

D7

A7

F7

E7

J7

J6

G6

H6

D6

C6

K6

A6

B6

F6

E6

J5

K5

H5

D5

G5

A5

B5

C5

E5

H4

A4

D4

C4

B4

J4

F4

E4

K4

J3 W3

F3

E3

H3

A3

G3

C3

D2

H2

E2

C2

J2

G2

K2

F2

D1

E1

F1

H1

J1

C1

K1

G1

A1

BGA638_50_26SQ_S1G3_OEM

AB26

L26

Y26

U26

R26

N26

V26

M26C26

AA26

T26

P26

W26

AB25

U25

P25

L25

R25

AA25

Y25

N25

V25

T25

M25

W25

M24

AB24

P24

W24

L24

U24

N24

R24

V24

Y24

AA24

T24

M23

W23

U23

L23

R23

V23P23

T23

N23

AA23

AB23

Y23

U22

W22

L22

P22

V22

N22

AA22

T22

R22

Y22

M22

AB22

U21

W21

V21

P21

N21

L21

T21

AA21

R21

Y21

M21

AB21

N20

R20

AA20

V20

M20

U20

Y20

P20

AB20

L20

T20

U19N19

AA19

Y19

V19J19 P19

R19

M19

L19

AB19

P18

AA18

V18

U18

N18

W18

L18

Y18

R18

T18

M18

AB18

T17

P17

U17

W17

N17

L17

AA17

Y17

R17

V17

M17

AB17

T16

L16

AA16

R16

N16

M16

W16

V16

U16

Y16

P16

AB16

L15

AA15

Y15

W15

AB15J15

T15

U15

V15

T14

U14

L14

Y14

AB14

W14

V14

AA14

U13

AA13

L13

W13

Y13

V13

T13

AB13

T12

Y12

AA12

U12

W12

V12

L12

AB12

P11

T11

L11 AE11

AA11

U11

M11

N11

V11

R11

W11

Y11

L10

P10 AA10

U10

M10

Y10

W10

N10

R10

V10

T10 AE10

AB10

R9

L9

U9W8W9

N9 P9

V9

Y9

T9

M9

AA9

AB9

R8

L8

U8N8

M8

AA8

T8

V8

P8

AB8

L7

U7

N7

M7

P7

V7R6AA7

AB7

R7

T7

W7

N6

W6

P6

V6

M6

U6

AA6

Y6

L6

T6

AB6

W5

AA5

P5

R5

M5

V5

U5

Y5

N5K3F5

L5

AB5

T5

W4

N4

AA4

V4

M4

P4G4

R4

U4

L4

Y4

AB4

T4

L3

V3D3

AA3

Y3

P3

R3

T3

U3

M3

N3

AB3

R2 V2

U2

T2

P2

Y2

W2

AB2

M2

AA2

N2

L2

Y1

L1

M1

T1

V1

AA1

P1

W1

N1

AB1

U1

R1

AD26

AC26

AE25

AD25

AC25

AD24

AE24

AC24

AF24

AD23

AE23

AC23

AF23

AD22

AE22

AC22

AF22

AF21

AC21

AD21

AE21

AE20

AC20

AD20

AF20

AE19

AD19

AF19T19

AC19

AC18

AF18

AD18

AE18

AF17

AD17

AC17

AE17

AF16

AD16

AE16

AC16

AF15

AD15

AE15H15

AC15

AD14

AF14

AC14

AE14

AD13

AF13

AE13

AC13

AD12

AF12

AE12

AC12

AC11

AF11

AD10

AC10

AF10

AE9

AC9

AD9

AF9

AC8

AE8

AD8

AF8

AD7

AC7

AE7

AF7

AD6

AC6

AF6

AE6

AE5

AC5

AD5

AF5

AF4

AE4

AD4

AC4

AC3

AE3

AD3

AD2

AC2

AE2

AC1

AD1

C338

C338

180pF

180pF

[CheckList] If the I/O device does not support the CTLIN1 pair, pull up 51ohm

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-168x

MS-168x

MSI

MSI

5

4

3

2

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

B

B

B

Monday, April 12, 2010

Monday, April 12, 2010

Monday, April 12, 2010

MS-168x

SIG4 HT I/F

SIG4 HT I/F

SIG4 HT I/F

0A

0A

0A

Sheet ofDate:

752

Sheet ofDate:

752

Sheet ofDate:

1

752

Page 8

A

smd.db-x7.ru

B

C

D

E

Processor Memory Interface

U20C

U20C

MEM:DATA

4 4

U20B

PLACE THEM CLOSE TO

CPU WITHIN 1"

CPU_VDDIO_SUS

R290R290

C586

C586

10uF

10uF

Updated on Rev2.0

If remove R/C?

3 3

2 2

R294 39.2RR294 39.2R

R292 39.2RR292 39.2R

MEM_MA_RST#11

MEM_MA0_ODT011

MEM_MA0_ODT111

MEM_MA0_CS#011

MEM_MA0_CS#111

MEM_MA_CKE011

MEM_MA_CKE111

MEM_MA_CLK1_P11

MEM_MA_CLK1_N11

MEM_MA_CLK2_P11

MEM_MA_CLK2_N11

MEM_MA_ADD[0..15]11

MEM_MA_BANK011

MEM_MA_BANK111

MEM_MA_BANK211

MEM_MA_RAS#11

MEM_MA_CAS#11

MEM_MA_WE#11

TP20TP20

TP25TP25

TP27TP27

TP26TP26

TP28TP28

TP32TP32

TP17TP17

TP19TP19

MEM_MA1_ODT0

MEM_MA1_ODT1

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

M_ZP

M_ZN

CPU_VDDIO_SUS

AD10

AE10

AA16

AF10

D10

C10

B10

H16

T19

V22

U21

V19

T20

U19

U20

V20

N19

N20

E16

F16

Y16

P19

P20

N21

M20

N22

M19

M22

L20

M24

L21

L19

K22

R21

L22

K20

V24

K24

K19

R20

R23

R19

T22

T24

VDDR1

VDDR2

VDDR3

VDDR4

MEMZP

MEMZN

MA_RESET_L

MA0_ODT0

MA0_ODT1

MA1_ODT0

MA1_ODT1

MA0_CS_L0

MA0_CS_L1

MA1_CS_L0

MA1_CS_L1

J22

MA_CKE0

J20

MA_CKE1

MA_CLK_H5

MA_CLK_L5

MA_CLK_H1

MA_CLK_L1

MA_CLK_H7

MA_CLK_L7

MA_CLK_H4

MA_CLK_L4

MA_ADD0

MA_ADD1

MA_ADD2

MA_ADD3

MA_ADD4

MA_ADD5

MA_ADD6

MA_ADD7

MA_ADD8

MA_ADD9

MA_ADD10

MA_ADD11

MA_ADD12

MA_ADD13

MA_ADD14

MA_ADD15

MA_BANK0

MA_BANK1

J21

MA_BANK2

MA_RAS_L

MA_CAS_L

MA_WE_L

SOCKET_638_PIN

SOCKET_638_PIN

R137

R137

1.00K

1.00K

R139

R139

1.00K

1.00K

U20B

MEM:CMD/CTRL/CLK

MEM:CMD/CTRL/CLK

VDDR_SENSE

MB_RESET_L

MB0_CS_L0

MB0_CS_L1

MB1_CS_L0

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

CPU_M_VREF_SUS

C254

C254

C252

C252

1nF

1nF

10nF

10nF

VDDR5

VDDR6

VDDR7

VDDR8

VDDR9

MEMVREF

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB_CKE0

MB_CKE1

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

PLACE CLOSE TO CPU

W10

AC10

AB10

AA10

A10

Y10

W17

B18

W26

W23

Y26

V26

W25

U22

J25

H26

P22

R22

A17

A18

AF18

AF17

R26

R25

P24

N24

P26

N23

N26

L23

N25

L24

M26

K26

T26

L26

L25

W24

J23

J24

R24

U26

J26

U25

U24

U23

sensing point for

op-amp feedback

routed near CPU

VDDR--1.05V

CPU_VDDRCPU_VDDR

MEM_MB1_ODT0

MEM_MB1_CS1

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_RST# 12

MEM_MB0_ODT0 12

MEM_MB0_ODT1 12

TP15TP15

MEM_MB0_CS#0 12

MEM_MB0_CS#1 12

TP16TP16

MEM_MB_CKE0 12

MEM_MB_CKE1 12

MEM_MB_CLK1_P 12

MEM_MB_CLK1_N 12

TP33TP33

TP34TP34

TP66TP66

TP67TP67

MEM_MB_CLK2_P 12

MEM_MB_CLK2_N 12

MEM_MB_ADD[0..15] 12

MEM_MB_BANK0 12

MEM_MB_BANK1 12

MEM_MB_BANK2 12

MEM_MB_RAS# 12

MEM_MB_CAS# 12

MEM_MB_WE# 12

CPU_M_VREF_SUS

MEM_MB_DATA[0..63]12

To reverse SODIMM socket

MEM_MB_DM[0..7]12

MEM_MB_DQS0_P12

MEM_MB_DQS0_N12

MEM_MB_DQS1_P12

MEM_MB_DQS1_N12

MEM_MB_DQS2_P12

MEM_MB_DQS2_N12

MEM_MB_DQS3_P12

MEM_MB_DQS3_N12

MEM_MB_DQS4_P12

MEM_MB_DQS4_N12

MEM_MB_DQS5_P12

MEM_MB_DQS5_N12

MEM_MB_DQS6_P12

MEM_MB_DQS6_N12

MEM_MB_DQS7_P12

MEM_MB_DQS7_N12

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

AE14

AF14

AF11

AD11

AB26

AE22

AC16

AD12

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

Y11

A12

B16

A22

E25

C12

B12

D16

C16

A24

A23

F26

E26

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

SOCKET_638_PIN

SOCKET_638_PIN

MEM:DATA

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DATA[0..63] 11

To normal SODIMM socket

MEM_MA_DM[0..7] 11

MEM_MA_DQS0_P 11

MEM_MA_DQS0_N 11

MEM_MA_DQS1_P 11

MEM_MA_DQS1_N 11

MEM_MA_DQS2_P 11

MEM_MA_DQS2_N 11

MEM_MA_DQS3_P 11

MEM_MA_DQS3_N 11

MEM_MA_DQS4_P 11

MEM_MA_DQS4_N 11

MEM_MA_DQS5_P 11

MEM_MA_DQS5_N 11

MEM_MA_DQS6_P 11

MEM_MA_DQS6_N 11

MEM_MA_DQS7_P 11

MEM_MA_DQS7_N 11

CPU_VDDR

C582

C582

4.7uF

1 1

4.7uF

C303

C303

4.7uF

4.7uF

C266

C266

4.7uF

4.7uF

Place close to socket

C270

C270

C267

220nF

220nF

C267

X_220nF

X_220nF

C584

C584

220nF

220nF

C283

C283

1nF

1nF

C583

C583

1nF

1nF

C257

C257

1nF

1nF

C275

C275

180pF

180pF

C284

C284

180pF

180pF

C258

C258

X_180pF

X_180pF

[ChckList] VDDR:0.22u*4/1n*4/180p*4/4.7u*4

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-168x

MS-168x

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

C

C

C

Tuesday, March 30, 2010

Tuesday, March 30, 2010

A

B

C

D

Tuesday, March 30, 2010

MS-168x

SIG4 MEMORY

SIG4 MEMORY

SIG4 MEMORY

E

Sheet ofDate:

852

Sheet ofDate:

852

Sheet ofDate:

852

0A

0A

0A

Page 9

5

smd.db-x7.ru

[DG] BEAD: R<40mΩ(about 35), I>500mA

Keep net PWRGD, LDT_STOP#, LDT_RST# no stub

+1.5VRUN

R145

R145

300R

CPU_PWRGD18

D D

CPU_LDT_STOP#15,18

CPU_LDT_RST#18

CPU_VDDIO_SUS

C C

CPU_SID

CPU_VDDIO_SUS

CPU_SIC

CPU_VDDIO_SUS

CPU_ALERT

B B

THERMDA/THERMDC is not used;

CPU thermal control is based on TSI by default.

+1.5VRUN

+1.5VRUN

R1981KR198

1K

R1971KR197

1K

R1801KR180

1K

300R

R138

R138

300R

300R

R141

R141

300R

300R

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

R147R147

R134R134

R140R140

R199

R199

2.2K

2.2K

Q19

Q19

B

B

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

C

C

E

E

A C

D13 BAS40WSD13 BAS40WS

R195

R195

2.2K

2.2K

Q18

Q18

B

B

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

C

C

E

E

A C

D14 BAS40WSD14 BAS40WS

R184

R184

10K

10K

Q17

Q17

B

B

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

C

C

E

E

PWRGD

LDT_STOP#

LDT_RST#

C246

C246

X_180pF

X_180pF

[ChckList] VDDA:100u*1/4.7u*1/0.22u0603*1/3300p0603*1

+VDDA

C282

C282

22uF

22uF

[CheckList} VDD1_FB_H/L NC if not use

+3.3VSUS

4.7K

4.7K

R190

R190

SMB_THRMCPU_DATA 30

+3.3VSUS

4.7K

4.7K

R189

R189

SMB_THRMCPU_CLK 30

+3.3VSUS

4.7K

4.7K

R185

R185

SMBALERT# 19,30

4

L15 26R_600mAL15 26R_600mA

C326

C326

4.7UF

4.7UF

200MHz

CPU_LDT_REQ# is NOT needed by S1G4

place them to CPU within 1.5"

CPU_CLKP34

CPU_CLKN34

C314

C314

220nF

220nF

CPU_SVC_R

CPU_SVD_R

PWRGD

3

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

R296

R296

169R

169R

CPU_SIC19

CPU_SID19

R174 44.2RR174 44.2R

R175 44.2RR175 44.2R

CPU_VDD0_RUN_FB_H47

CPU_VDD0_RUN_FB_L47

TP41TP41

TP68TP68

TP69TP69

TP70TP70

CPU_VDDA_RUN

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

LDT_RST#

PWRGD

LDT_STOP#

CPU_SIC

CPU_SID

CPU_ALERT

CPU_HTREF0

CPU_HTREF1

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST23_TSTUPD

CPU_TEST18_PLLTEST1

CPU_TEST19_PLLTEST0

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST27_SINGLECHAIN

CPU_TEST9_ANALOGIN

F8

F9

A9

A8

B7

A7

F10

C6

AF4

AF5

AE6

R6

P6

F6

E6

Y6

AB6

G10

AA9

AC9

AD9

AF9

AD7

H10

G9

E9

E8

AB8

AF7

AE7

AE8

AC8

AF8

C2

AA6

A3

A5

B3

B5

C1

U20D

U20D

VDDA1

VDDA2

CLKIN_H

CLKIN_L

RESET_L

PWROK

LDTSTOP_L

LDTREQ_L

SIC

SID

ALERT_L

HT_REF0

HT_REF1

VDD0_FB_H

VDD0_FB_L

VDD1_FB_H

VDD1_FB_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST23

TEST18

TEST19

TEST25_H

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

TEST9

TEST6

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

SOCKET_638_PIN

SOCKET_638_PIN

RSVD11

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

DBREQ_L

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

M11

VSS

W18

A6

SVC

A4

SVD

AF6

AC7

AA8

W7

W8

W9

Y9

H6

G6

E10

AE9

TDO

J7

H8

D7

E7

F7

C7

C3

K8

C4

C9

C8

H18

H19

AA7

D5

C5

C328

C328

3.3NF

3.3NF

Keep trace from resisor to CPU within 0.6"

keep trace from caps to CPU within 1.2"

C596 3.9NFC596 3.9NF

C597 3.9NFC597 3.9NF

+1.1VRUN

CPU_VDDIO_SUS

R291

R291

510R

510R

R293

R293

510R

510R

R191R191

RSVD/TEST6/7/8/10/28--NC

TEST14/15/16/17--Test Point

TEST23/25--Test Point

TEST12/18~24--Pull down 1Kohn to VSS

TEST27 pull-up 1Kohm to VDDIO

TEST25_H pull-up 510ohm to VDDIO

TEST25_L pull-down 510ohm to VSS

TEST9 is tied to VSS

There is a (±1%) differential termination between TEST29_L and TEST29_H

CPU_DBRDY not need pull down in checklist

+1.5VRUN

10K

10K

10K

R164R164

R201R201

R150R150

10K

R166

R166

PWRGD pull-up in 2 times (R187 and R163)?

R202

R202

R149 X_2.2KR149 X_2.2K

2

CPU_SVC_R

CPU_SVD_R

CPU_THERMTRIP#_VDDIO

CPU_VDDIO_SUS

R1771KR177

1K

S1G4 does not support MEMHOT_L

TP40TP40

CPU_VDDNB_RUN_FB_H 47

CPU_DBREQ#

CPU_TDO

CPU_TEST28_H_PLLCHRZ_P

CPU_TEST28_L_PLLCHRZ_N

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST7_ANALOG_T

CPU_TEST10_ANALOGOUT

CPU_TEST8_DIG_T

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

TP44TP44

TP71TP71

TP43TP43

TP42TP42

TP45TP45

TP47TP47

TP46TP46

R167

R167

80.6R

80.6R

Route as 80ohm, diff

R184's value is TBD.

TEST23--R358 NC in ref schematic?

CPU_SVC 47

CPU_SVD 47

CPU_PWRGD_SVID_REG 47

CPU_VDDIO_SUS

R171

R171

10K

10K

Q16

R170

R170

300R

300R

Thermdc and Thermda should be routed away to VRM,

crystal, etc. Customer should follow the MBDG.

However, Guam is using TSI so this does not applies to Guam.

Q16

B

B

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

C

C

E

E

R165 X_0RR165 X_0R

CPU_THERMTRIP# 19

CPU_PROCHOT# 18

VRD_PROCHOT# 47

[CheckList] VDDIO_FB_H/L NC if not use

route as differential

as short as possible

testpoint under package

For debug only

CPU_DBREQ#

CPU_TEST27_SINGLECHAIN

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST18_PLLTEST1

CPU_TEST19_PLLTEST0

CPU_TEST23_TSTUPD

CPU_DBRDY

CPU_TEST10_ANALOGOUT

R147, R152 is installed ONLY when SCAN is enabled

R215, R185 internal ONLY

R162 is TBD

[DateSheet] Internal Termination:Systems that do not require use of

these pins can rely on the internal termination to pull the signals

to the proper inactive state. When these pins are used, they must

not be driven with open-drain outputs,otherwise additional

termination is required

[DateSheet] Internal pull_up 870~1250 ohm:

SSA[2;0], TCK, TMS, TRST_L, TDI, DBREQ_L, PLATFORM_TYPE, TEST27

[DateSheet] Internal pull_down 870~1250 ohm:

TEST12, TEST[20:24]

Internal pull_up 870~1250 ohm:

SSA[2;0], TCK, TMS, TRST_L, TDI, DBREQ_L, PLATFORM_TYPE, TEST27

1

CPU_VDDIO_SUS

R156 300RR156 300R

R303 1KR303 1K

R306 1KR306 1K

R307 1KR307 1K

R308 1KR308 1K

R304 1KR304 1K

R305 1KR305 1K

R176 X_300RR176 X_300R

R160 X_300RR160 X_300R

R159 1KR159 1K

R135 1KR135 1K

R173 1KR173 1K

R163 X_300RR163 X_300R

R161 X_300RR161 X_300R

+1.1VRUN

A A

5

4

BOOT VOLTAGE(VDD)

SVC

SVD

0 0 1.1 1.1

0 1 1.0 1.2

1 0 0.9 1.0

1 1 0.8 0.8

(CPUVRM_PRO#

= VCC/GND)

(CPUVRM_PRO#

= OPEN)

VID OVERIDE TABLE (VDD)

3

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-168x

MS-168x

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Wednesday, May 05, 2010

Wednesday, May 05, 2010

2

Wednesday, May 05, 2010

MS-168x

SIG4 CTRL and DEBEG

SIG4 CTRL and DEBEG

SIG4 CTRL and DEBEG

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

1

0A

0A

0A

952

952

952

Page 10

5

smd.db-x7.ru

4

3

2

1

U20F

U20F

AA4

D D

U20E

CPU_VDD_RUN

C C

CPU_VDDNB_RUN

CPU_VDDIO_SUS

B B

A A

G4

H2

J9

J11

J13

J15

K6

K10

K12

K14

L4

L7

L9

L11

L13

L15

M2

M6

M8

M10

N7

N9

N11

K16

M16

P16

T16

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

U20E

VDD_1

VDD_2

VDD_3

VDD_4

VDD_5

VDD_6

VDD_7

VDD_8

VDD_9

VDD_10

VDD_11

VDD_12

VDD_13

VDD_14

VDD_15

VDD_16

VDD_17

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

VDD_23

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

SOCKET_638_PIN

SOCKET_638_PIN

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

VDDIO13

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

VDD_32

VDD_33

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

VDD_42

VDD_43

VDD_44

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

P18

CPU_VDD_RUN

CPU_VDDIO_SUS

AA11

AA13

AA15

AA17

AA19

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AB2

AB7

AB9

AD6

AD8

B4

B6

B8

B9

B11

B13

B15

B17

B19

B21

B23

B25

D6

D8

D9

D11

D13

D15

D17

D19

D21

D23

D25

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

H21

H23

J4

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

SOCKET_638_PIN

SOCKET_638_PIN

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

CPU_VDD_RUN

CPU_VDD_RUN

CPU_VDDNB_RUN

[ChckList] VDD:22u*8/0.22u*2/0.01u0603*2/180p*2

[ChckList] VDDNB:22u*3

CPU_VDDIO_SUS

[ChckList] VDDIO:22u*2/0.22u*6/0.1u0603*2/0.01u0603*1/180p*1/4.7u*4

PROCESSOR POWER AND GROUND

5

4

3

BOTTOM SIDE DECOUPLING

C262

C249

C249

22uF

22uF

C311

C311

22uF

22uF

C272

C272

22uF

22uF

C248

C248

22uF

22uF

C261

C261

C293

C293

22uF

22uF

22uF

22uF

C310

C310

C273

C273

22uF

22uF

22uF

22uF

CPU_VDDIO_SUS

C247

C247

22uF

22uF

C251

C251

22uF

22uF

C262

22uF

22uF

C294

C294

22uF

22uF

C250

C250

22uF

22uF

C298

C298

220nF

220nF

C315

C315

220nF

220nF

C543

C543

220nF

220nF

C330

C330

10nF

10nF

C337

C337

10nF

10nF

C201

C201

220nF

220nF

C263

C263

180pF

180pF

C286

C286

180pF

180pF

C212

C212

180pF

180pF

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

C164

C209

C209

4.7uF

4.7uF

C159

C159

4.7uF

4.7uF

C213

C213

4.7uF

4.7uF

C214

C214

4.7uF

4.7uF

C208

C208

220nF

220nF

C164

C141

X_220nF

X_220nF

C141

220nF

220nF

C210

C210

220nF

220nF

2

C157

C157

X_100nF

X_100nF

C222

C222

10nF

10nF

MSI

MSI

MSI

C123

C123

C207

C207

180pF

180pF

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Wednesday, May 05, 2010

Wednesday, May 05, 2010

Wednesday, May 05, 2010

C142

C142

X_180pF

X_180pF

100nF

100nF

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-168x

MS-168x

MS-168x

SIG4 POWER and GND

SIG4 POWER and GND

SIG4 POWER and GND

Sheet ofDate:

10 52

Sheet ofDate:

10 52

Sheet ofDate:

1

10 52

0A

0A

0A

Page 11

5

smd.db-x7.ru

MEM_MA_DATA[0..63]8

D D

C C

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

DIMM2A

DIMM2A

5

DQ0

7

DQ1

15

DQ2

17

DQ3

4

DQ4

6

DQ5

16

DQ6

18

DQ7

21

DQ8

23

DQ9

33

DQ10

35

DQ11

22

DQ12

24

DQ13

34

DQ14

36

DQ15

39

DQ16

41

DQ17

51

DQ18

53

DQ19

40

DQ20

42

DQ21

50

DQ22

52

DQ23

57

DQ24

59

DQ25

67

DQ26

69

DQ27

56

DQ28

58

DQ29

68

DQ30

70

DQ31

129

DQ32

131

DQ33

141

DQ34

143

DQ35

130

DQ36

132

DQ37

140

DQ38

142

DQ39

147

DQ40

149

DQ41

157

DQ42

159

DQ43

146

DQ44

148

DQ45

158

DQ46

160

DQ47

163

DQ48

165

DQ49

175

DQ50

177

DQ51

164

DQ52

166

DQ53

174

DQ54

176

DQ55

181

DQ56

183

DQ57

191

DQ58

193

DQ59

180

DQ60

182

DQ61

192

DQ62

194

DQ63

DDR3SODIMM-204PS_BLACK-HF-3

DDR3SODIMM-204PS_BLACK-HF-3

A10/AP

A12/BC#

CK0#

CK1#

CKE0

CKE1

CAS#

RAS#

ODT0

ODT1

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

MEM_MA_ADD0

98

A0

MEM_MA_ADD1

97

A1

MEM_MA_ADD2

96

A2

MEM_MA_ADD3

95

A3

MEM_MA_ADD4

92

A4

MEM_MA_ADD5

91

A5

MEM_MA_ADD6

90

A6

MEM_MA_ADD7

86

A7

MEM_MA_ADD8

89

A8

MEM_MA_ADD9

85

A9

MEM_MA_ADD10

107

MEM_MA_ADD11

84

A11

MEM_MA_ADD12

83

MEM_MA_ADD13

119

A13

MEM_MA_ADD14

80

A14

MEM_MA_ADD15

78

A15

109

BA0

108

BA1

79

BA2

114

S0#

121

S1#

101

CK0

103

102

CK1

104

73

74

115

110

113

WE#

197

SA0

201

SA1

202

SCL

200

SDA

116

120

MEM_MA_DM0

11

DM0

MEM_MA_DM1

28

DM1

MEM_MA_DM2

46

DM2

MEM_MA_DM3

63

DM3

MEM_MA_DM4

136

DM4

MEM_MA_DM5

153

DM5

MEM_MA_DM6

170

DM6

MEM_MA_DM7

187

DM7

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

4

MEM_MA_ADD[0..15] 8

MEM_MA_BANK0 8

MEM_MA_BANK1 8

MEM_MA_BANK2 8

MEM_MA0_CS#0 8

MEM_MA0_CS#1 8

MEM_MA_CLK1_P 8

MEM_MA_CLK1_N 8

MEM_MA_CLK2_P 8

MEM_MA_CLK2_N 8

MEM_MA_CKE0 8

MEM_MA_CKE1 8

MEM_MA_CAS# 8

MEM_MA_RAS# 8

MEM_MA_WE# 8

SCLK0 12,19,34

SDATA0 12,19,34

MEM_MA0_ODT0 8

MEM_MA0_ODT1 8

MEM_MA_DM[0..7] 8

MEM_MA_DQS0_P 8

MEM_MA_DQS1_P 8

MEM_MA_DQS2_P 8

MEM_MA_DQS3_P 8

MEM_MA_DQS4_P 8

MEM_MA_DQS5_P 8

MEM_MA_DQS6_P 8

MEM_MA_DQS7_P 8

MEM_MA_DQS0_N 8

MEM_MA_DQS1_N 8

MEM_MA_DQS2_N 8

MEM_MA_DQS3_N 8

MEM_MA_DQS4_N 8

MEM_MA_DQS5_N 8

MEM_MA_DQS6_N 8

MEM_MA_DQS7_N 8

+3.3VRUN

MEM_MA_RST#8

MEM_M_VREF_SUS

MEM_M_VREFCA

C202

C202

C0.1u10X0402

C0.1u10X0402

3

CPU_VDDIO_SUS

C203

C203

X_C2.2u6.3X5

X_C2.2u6.3X5

DIMM2B

DIMM2B

75

VDD