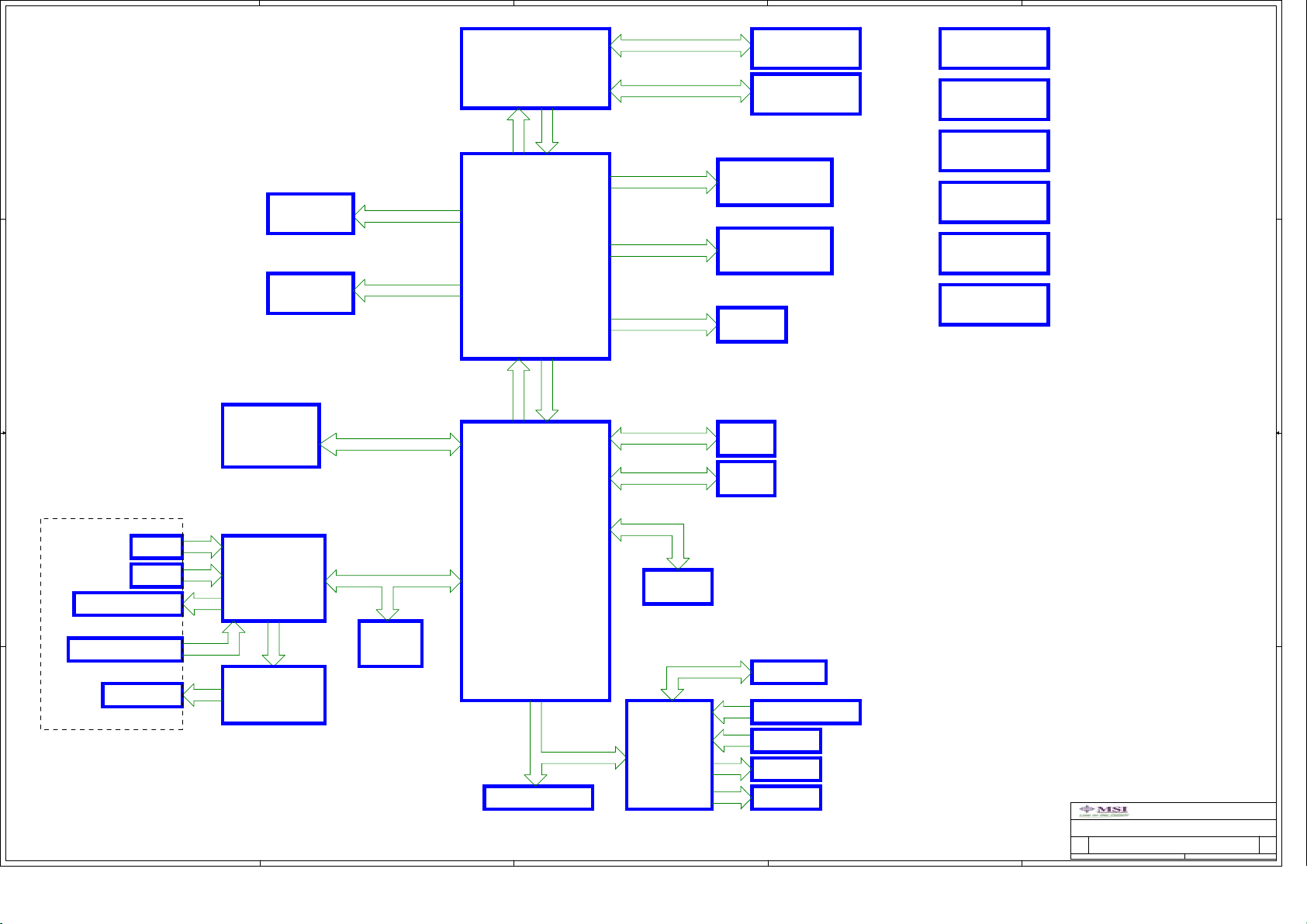

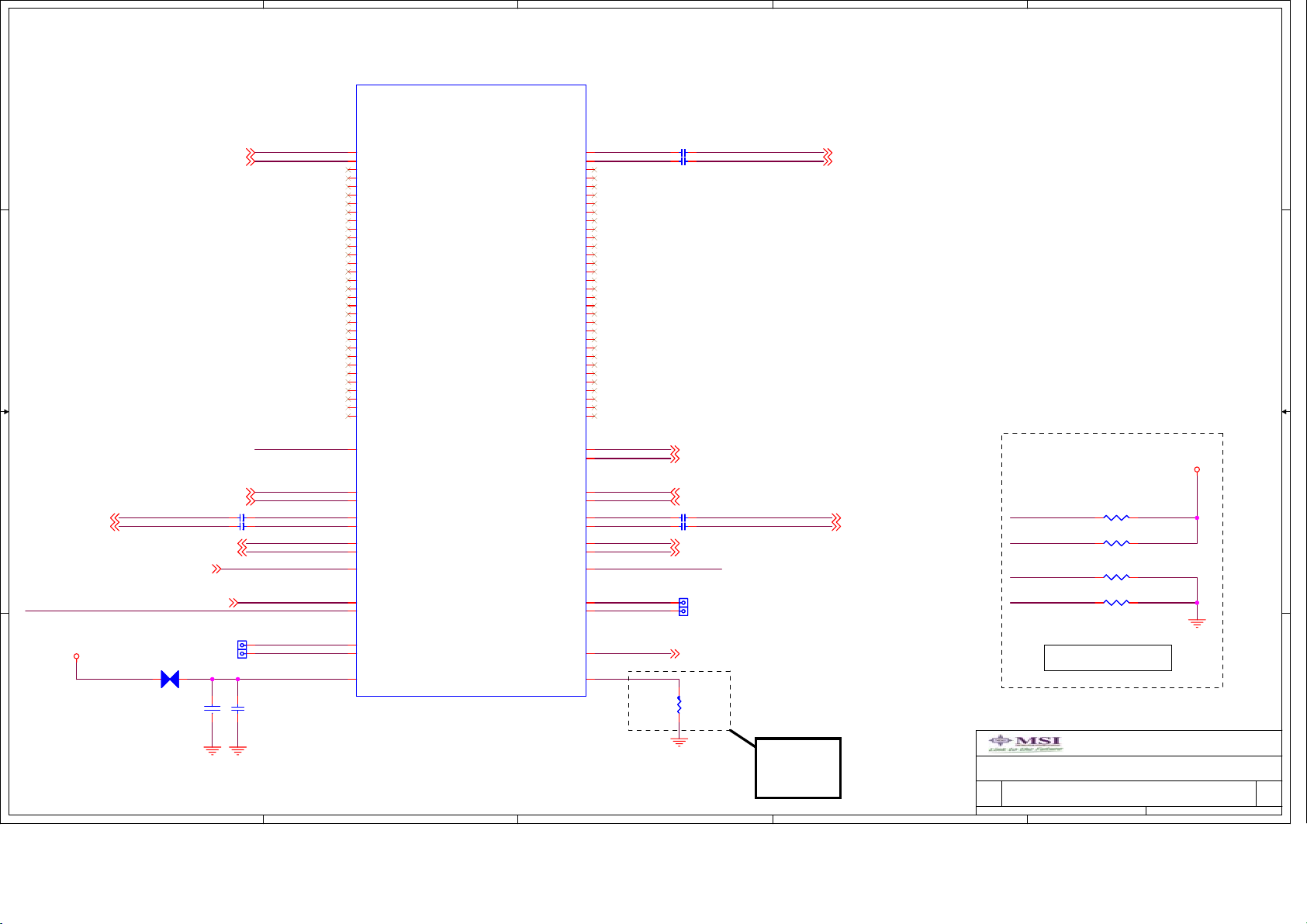

Page 1

5

4

3

2

1

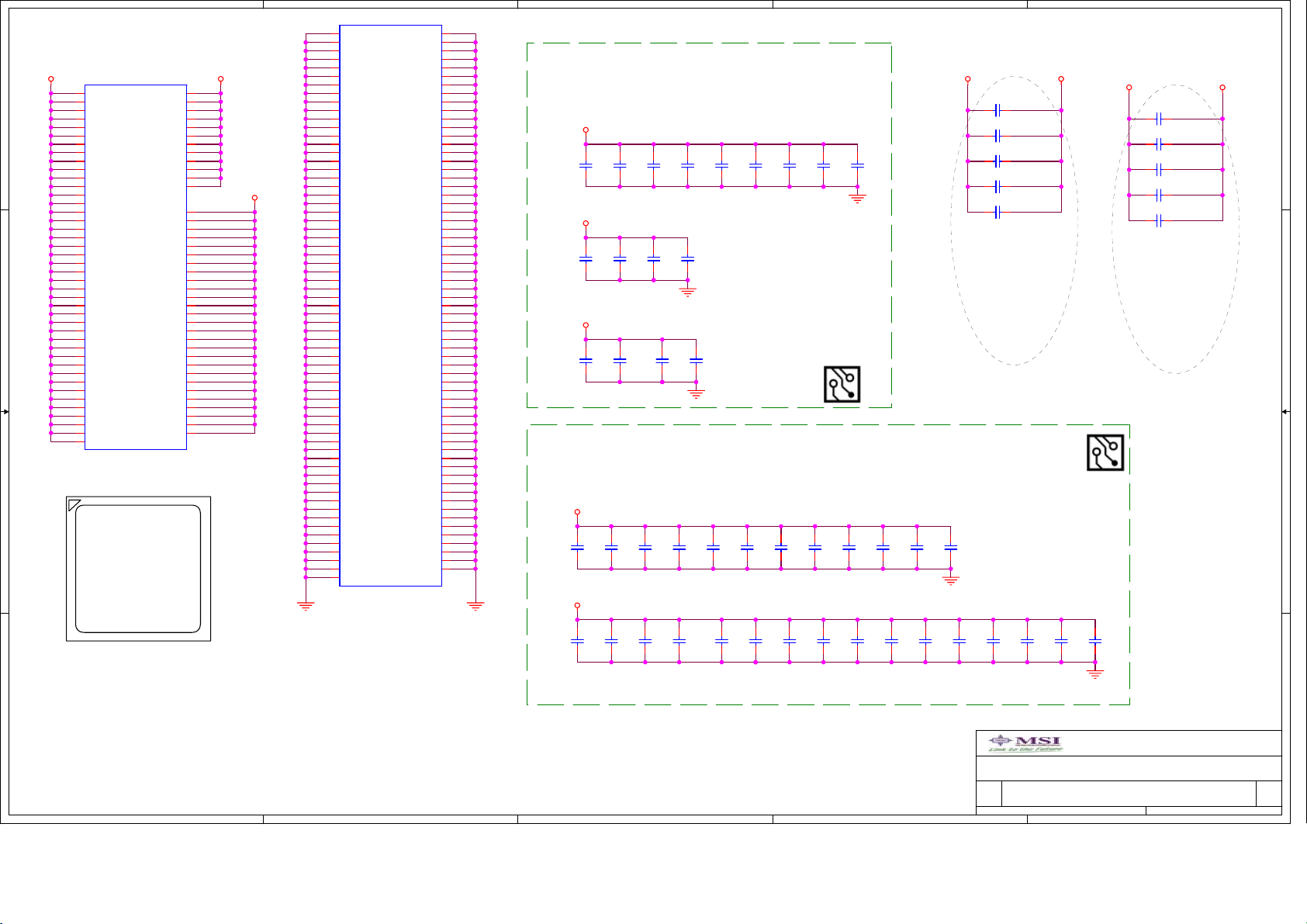

MS-14141 Ver : 0.A

D D

LVDS

Page 21

CRT

Page 21

C C

LVDS Transmitter

CRT_RGB

Processor

AMD S1

638 pin uFCPGA 638 socket

Page 2,3,4,5

16 X 16 Bit

HyperTransport Link

North Bridge

nVIDIA C51MV

Page 8,9,10,11,12

HyperTransport Link

DDR2 400 / 533 / 667 MHz

PCI Express

PCI Express

PCI Express

DDR2 Sodimm 0

DDR2 Sodimm 1

Optional

TV Tunner OR 3G card

Mini PCIE

Page 24

WLAN

Mini PCIE

New Card

Page 24

Page 23

Page 6 Page 29

Page 6

Battery select

Page 28

DRAM Power

Battery Charger

Page 32

System Power

Page 31

North Bridge Power

Page 30

CPU Power

Page 33

LAN PHY

RTL 8201CL

Page 22

MII TNTERFACE

South Bridge

nVIDIA MCP51M

SATA Bus

Primary IDE Bus

HDD

Page 25

ODD

Page 25

B B

Line Out

MIC In

LINE In

Audio Codec

Realtek ALC883

Page 21

Azalia Interface

USB 1.1 / 2.0

USB 0,1,2,3

Page 26

USB Connectors

MDC

Internal Microphone

Audio AMP

Internal SPK

Page 19

A A

5

APA 2031

Page 22

Page 28

4

Page 13,14,15,16,17

LPC

LPC Debug Port

KBC

ene KB3910

Page 20

3

X-Bus

BIOS ROM

Internal Keyboard

Touch Pad

Smart Fan

SYSTEM LED

Page 23

Page 23

For CPU & System

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

Block diagram

Block diagram

Block diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-14141

MS-14141

MS-14141

1

0.A

0.A

0.A

of

of

of

137Tuesday, September 26, 2006

137Tuesday, September 26, 2006

137Tuesday, September 26, 2006

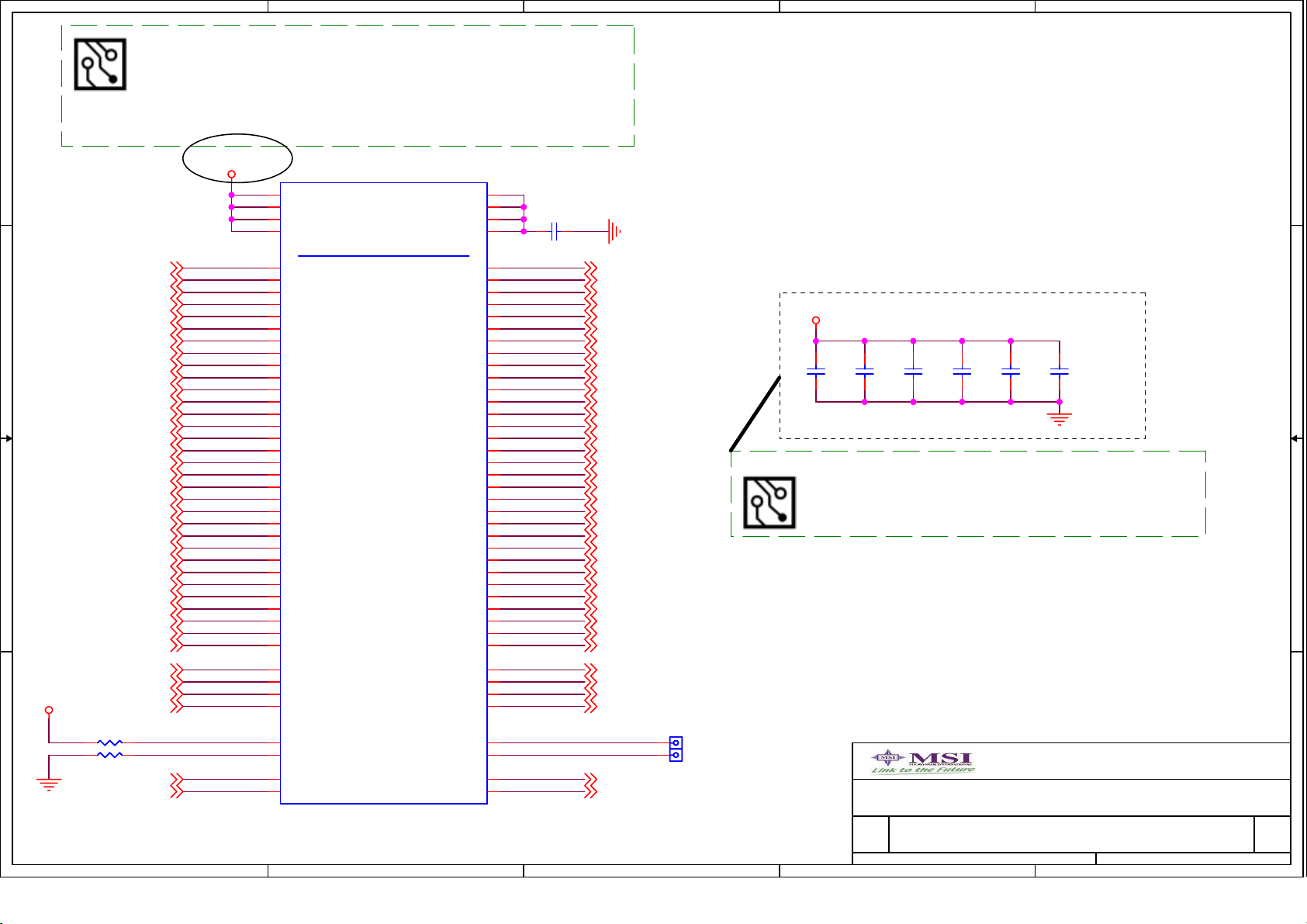

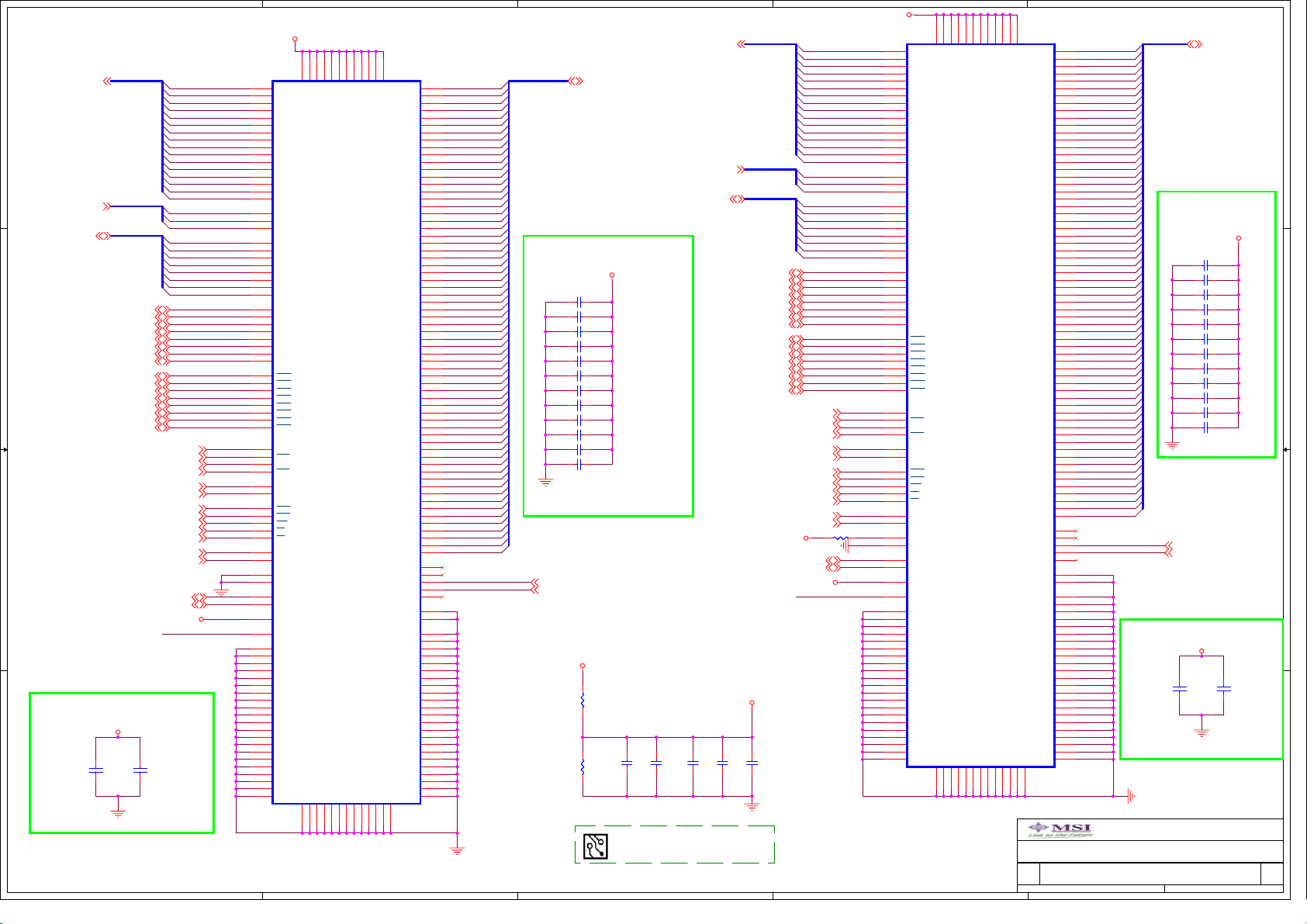

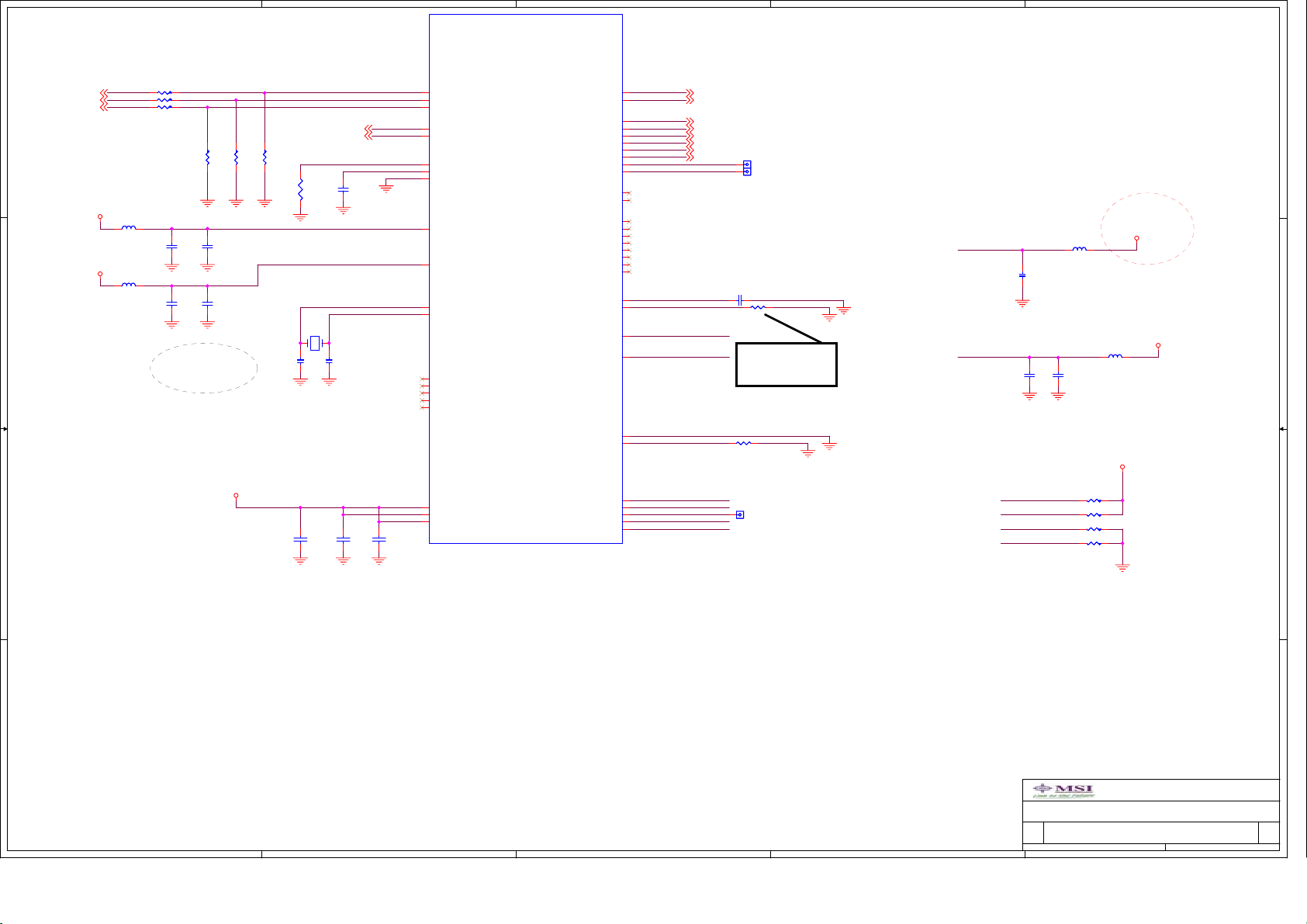

Page 2

5

4

3

2

1

PROCESSOR HYPERTRANSPORT INTERFACE

VLDT_Ax AND VLDT_Bx ARE CONNECTED TO THE LDT_RUN POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

D D

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

+VLDT

D4

VLDT_A3

D3

VLDT_A2

D2

VLDT_A1

D1

VLDT_A0

HT_CADIN15_P8

HT_CADIN15_N8

HT_CADIN14_P8

HT_CADIN14_N8

HT_CADIN13_P8

+VLDT

HT_CADIN13_N8

HT_CADIN12_P8

HT_CADIN12_N8

HT_CADIN11_P8

HT_CADIN11_N8

HT_CADIN10_P8

HT_CADIN10_N8

HT_CADIN9_P8

HT_CADIN9_N8

HT_CADIN8_P8

HT_CADIN8_N8

HT_CADIN7_P8

HT_CADIN7_N8

HT_CADIN6_P8

HT_CADIN6_N8

HT_CADIN5_P8

HT_CADIN5_N8

HT_CADIN4_P8

HT_CADIN4_N8

HT_CADIN3_P8

HT_CADIN3_N8

HT_CADIN2_P8

HT_CADIN2_N8

HT_CADIN1_P8

HT_CADIN1_N8

HT_CADIN0_P8

HT_CADIN0_N8

HT_CLKIN1_P8

HT_CLKIN1_N8

HT_CLKIN0_P8

HT_CLKIN0_N8

C C

B B

N5

L0_CADIN_H15

P5

L0_CADIN_L15

M3

L0_CADIN_H14

M4

L0_CADIN_L14

L5

L0_CADIN_H13

M5

L0_CADIN_L13

K3

L0_CADIN_H12

K4

L0_CADIN_L12

H3

L0_CADIN_H11

H4

L0_CADIN_L11

G5

L0_CADIN_H10

H5

L0_CADIN_L10

F3

L0_CADIN_H9

F4

L0_CADIN_L9

E5

L0_CADIN_H8

F5

L0_CADIN_L8

N3

L0_CADIN_H7

N2

L0_CADIN_L7

L1

L0_CADIN_H6

M1

L0_CADIN_L6

L3

L0_CADIN_H5

L2

L0_CADIN_L5

J1

L0_CADIN_H4

K1

L0_CADIN_L4

G1

L0_CADIN_H3

H1

L0_CADIN_L3

G3

L0_CADIN_H2

G2

L0_CADIN_L2

E1

L0_CADIN_H1

F1

L0_CADIN_L1

E3

L0_CADIN_H0

E2

L0_CADIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

U13AU13A

VLDT_B3

VLDT_B2

VLDT_B1

VLDT_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

AE5

AE4

AE3

AE2

T4

T3

V5

U5

V4

V3

Y5

W5

AB5

AA5

AB4

AB3

AD5

AC5

AD4

AD3

T1

R1

U2

U3

V1

U1

W2

W3

AA2

AA3

AB1

AA1

AC2

AC3

AD1

AC1

Y4

Y3

Y1

W1

4.7U_0805

4.7U_0805

C318

C318

HT_CADOUT15_P 8

HT_CADOUT15_N 8

HT_CADOUT14_P 8

HT_CADOUT14_N 8

HT_CADOUT13_P 8

HT_CADOUT13_N 8

HT_CADOUT12_P 8

HT_CADOUT12_N 8

HT_CADOUT11_P 8

HT_CADOUT11_N 8

HT_CADOUT10_P 8

HT_CADOUT10_N 8

HT_CADOUT9_P 8

HT_CADOUT9_N 8

HT_CADOUT8_P 8

HT_CADOUT8_N 8

HT_CADOUT7_P 8

HT_CADOUT7_N 8

HT_CADOUT6_P 8

HT_CADOUT6_N 8

HT_CADOUT5_P 8

HT_CADOUT5_N 8

HT_CADOUT4_P 8

HT_CADOUT4_N 8

HT_CADOUT3_P 8

HT_CADOUT3_N 8

HT_CADOUT2_P 8

HT_CADOUT2_N 8

HT_CADOUT1_P 8

HT_CADOUT1_N 8

HT_CADOUT0_P 8

HT_CADOUT0_N 8

HT_CLKOUT1_P 8

HT_CLKOUT1_N 8

HT_CLKOUT0_P 8

HT_CLKOUT0_N 8

C309

C309

4.7U_0805

4.7U_0805

+VLDT

C312

C312

4.7U_0805

4.7U_0805

C313

C313

0.22u_0603

0.22u_0603

0.01U25X0402

0.01U25X0402

C314

C314

0.22u_0603

0.22u_0603

C85

C85

C315

C315

0.01U25X0402

0.01U25X0402

LAYOUT: Place bypass cap on topside of board

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

TO OTHER HT POWER PINS

PLACE CLOSE TO VLDT0 POWER PINS

R32 51_0402R32 51_0402

A A

R31 51_0402R31 51_0402

HT_CTLIN0_P8

HT_CTLIN0_N8

HT_CTLIN1_P

HT_CTLIN1_N

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

Athlon 64 S1 Processor Socket

5

4

HT_CPU_CTLOUT1_P

T5

HT_CPU_CTLOUT1_N

R5

R2

R3

TP5TP5

TP4TP4

HT_CTLOUT0_P 8

HT_CTLOUT0_N 8

3

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

AMD S1 HT I/F

AMD S1 HT I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

AMD S1 HT I/F

Custom

Custom

Custom

MS-14141

MS-14141

MS-14141

2

of

of

of

237Tuesday, September 26, 2006

237Tuesday, September 26, 2006

237Tuesday, September 26, 2006

1

0.A

0.A

0.A

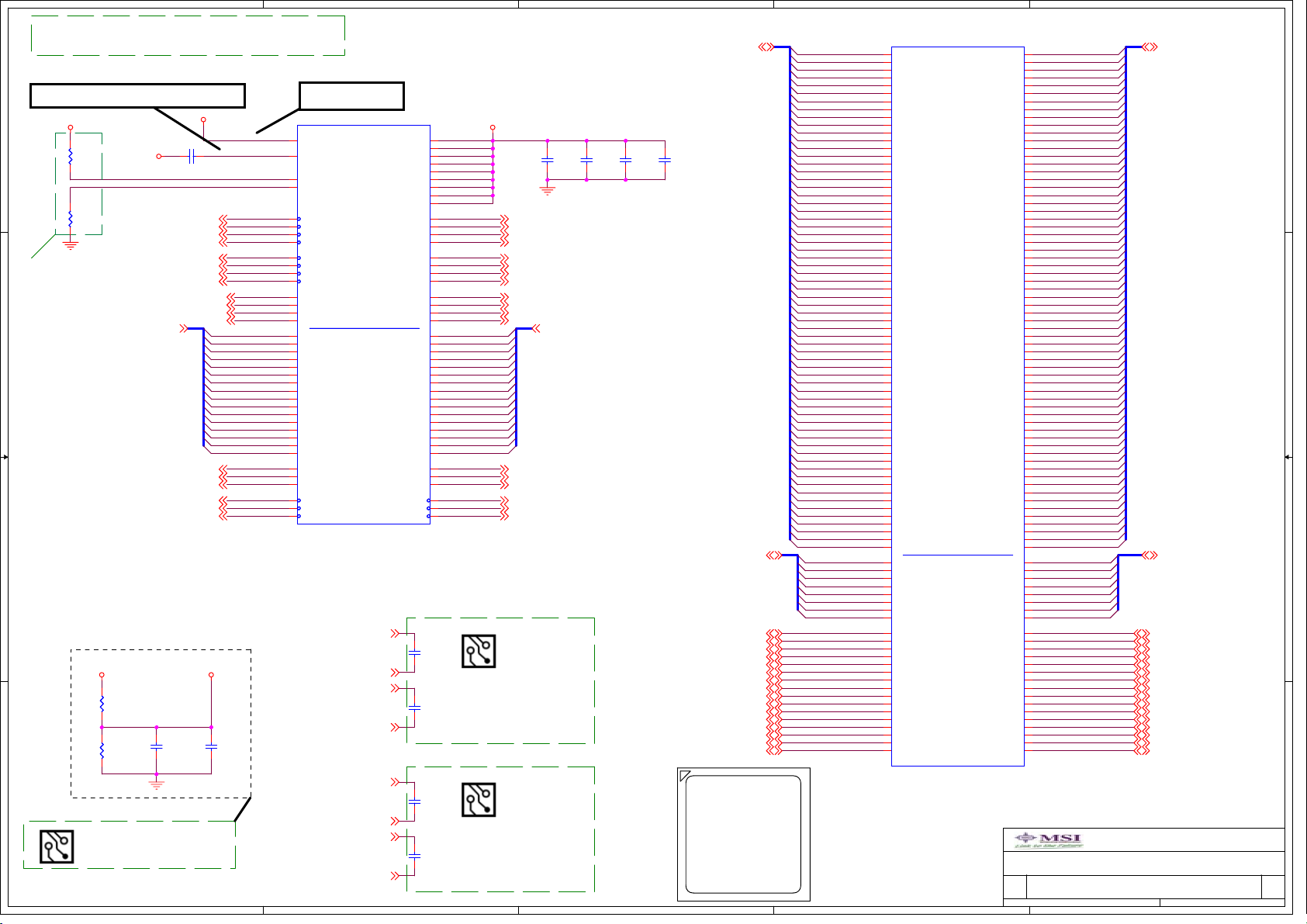

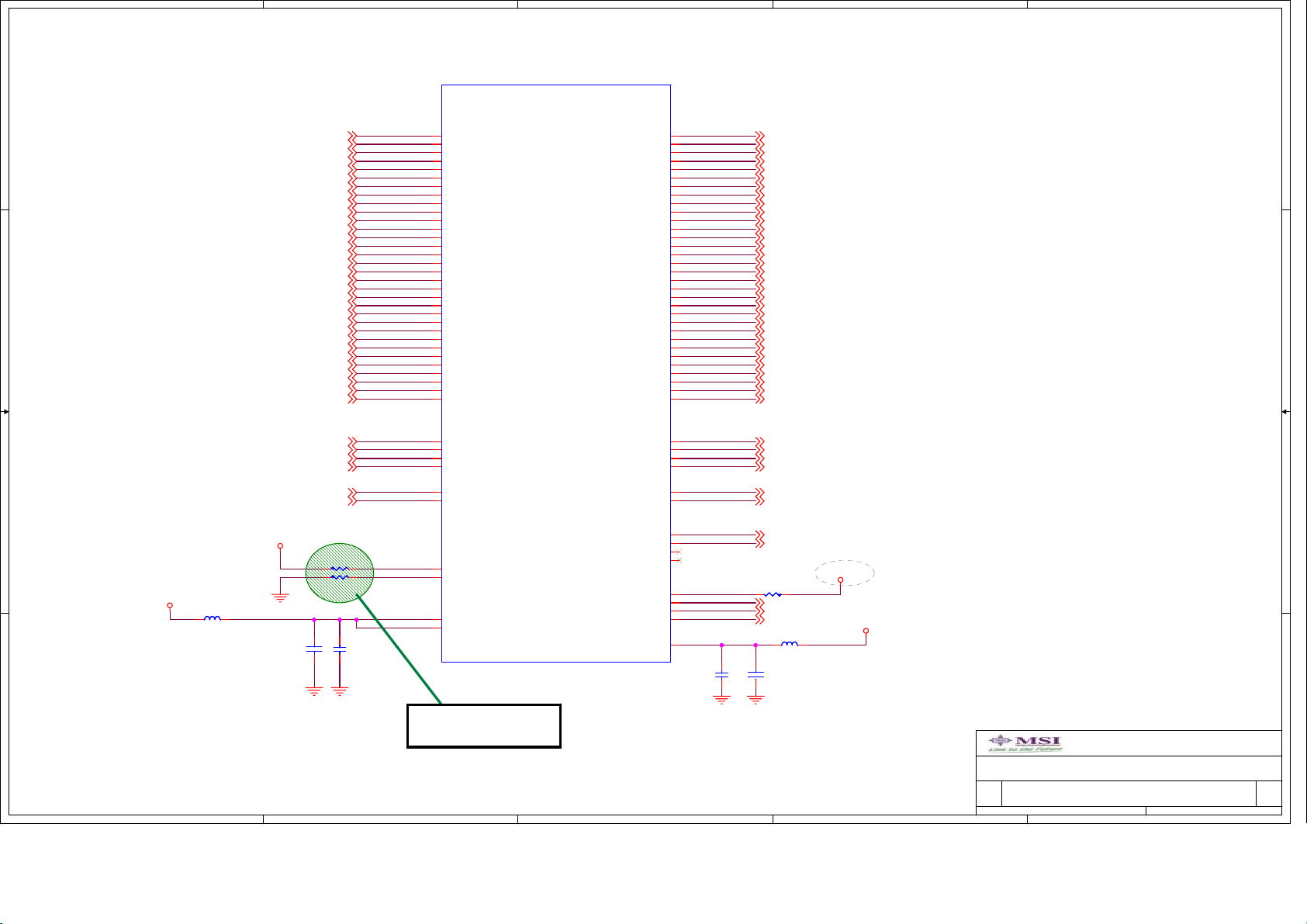

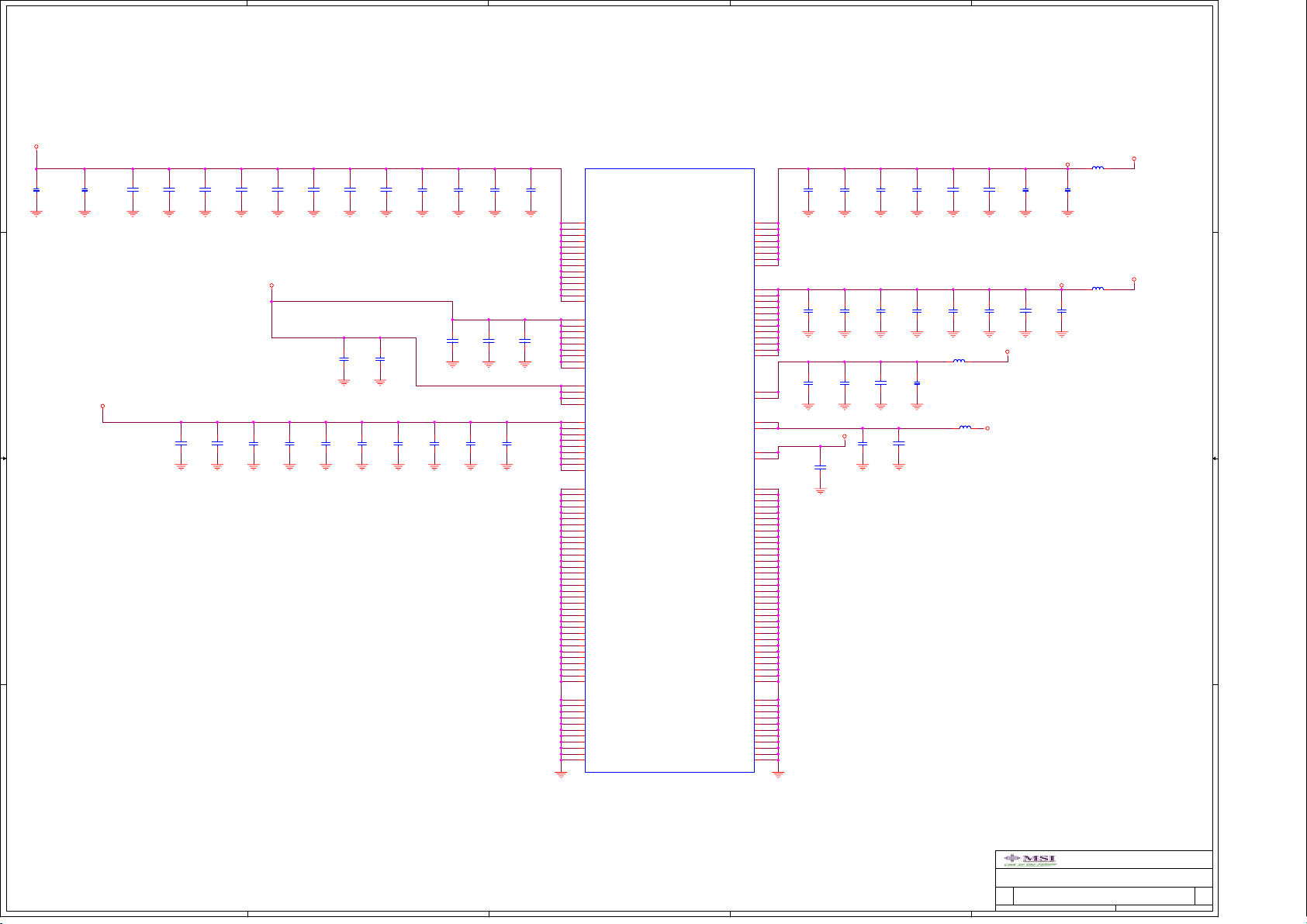

Page 3

5

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

VTT_SENSE

should be routed as a 10-mil trace with 10 mils spacing.

CPU_VDDIO_SUS

D D

CPU_VTT_SUS

R197

R197

39.2_0402 1%

39.2_0402 1%

R198

R198

39.2_0402 1%

39.2_0402 1%

PLACE THEM CLOSE TO

CPU WITHIN 1"

MEM_MA_ADD[15..0]6,7

C C

B B

CPU_VDDIO_SUS CPU_M_VREF_SUS

A A

VDD_VREF_SUS_CPU

R51

R51

1K_0402 1%

1K_0402 1%

R52

R52

1K_0402 1%

1K_0402 1%

CPU_M_VREF_SUS

CPU_M_VREF_SUS

SNS_+0.9VTT

C93 1n_0402C93 1n_0402

M_ZN

M_ZP

MEM_MA0_CS#36,7 MEM_MA0_CLK2_P 6

MEM_MA0_CS#26,7

MEM_MA0_CS#16,7

MEM_MA0_CS#06,7

MEM_MB0_CS#36,7

MEM_MB0_CS#26,7

MEM_MB0_CS#16,7

MEM_MB0_CS#06,7

MEM_MB_CKE16,7

MEM_MB_CKE06,7

MEM_MA_CKE16,7

MEM_MA_CKE06,7

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_BANK26,7

MEM_MA_BANK16,7 MEM_MB_BANK1 6,7

MEM_MA_BANK06,7

MEM_MA_RAS#6,7

MEM_MA_CAS#6,7

MEM_MA_WE#6,7

0922 by

harry

C125

C125

1n_0402

1n_0402

C118

C118

1n_0402

1n_0402

15MIL trace, 20MIL space,

shorter than 1"

W17

MEMVREF

Y10

VTT_SENSE

AE10

MEMZN

AF10

MEMZP

V19

MA0_CS_L3

J22

MA0_CS_L2

V22

MA0_CS_L1

T19

MA0_CS_L0

Y26

MB0_CS_L3

J24

MB0_CS_L2

W24

MB0_CS_L1

U23

MB0_CS_L0

H26

MB_CKE1

J23

MB_CKE0

J20

MA_CKE1

J21

MA_CKE0

K19

MA_ADD15

K20

MA_ADD14

V24

MA_ADD13

K24

MA_ADD12

L20

MA_ADD11

R19

MA_ADD10

L19

MA_ADD9

L22

MA_ADD8

L21

MA_ADD7

M19

MA_ADD6

M20

MA_ADD5

M24

MA_ADD4

M22

MA_ADD3

N22

MA_ADD2

N21

MA_ADD1

R21

MA_ADD0

K22

MA_BANK2

R20

MA_BANK1

T22

MA_BANK0

T20

MA_RAS_L

U20

MA_CAS_L

U21

MA_WE_L

MEM_MB0_CLK2_P6

MEM_MB0_CLK2_N6

MEM_MB0_CLK1_P6

MEM_MB0_CLK1_N6

MEM_MA0_CLK2_P6

MEM_MA0_CLK2_N6

MEM_MA0_CLK1_P6

DDR II: CMD/CTRL/CLK

DDR II: CMD/CTRL/CLK

Athlon 64 S1

Processor

Socket

LAYOUT:PLACE CLOSE TO CPU

MEM_MA0_CLK1_N6

5

U13B

U13B

4

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

MA0_CLK_H2

MA0_CLK_L2

MA0_CLK_H1

MA0_CLK_L1

MB0_CLK_H2

MB0_CLK_L2

MB0_CLK_H1

MB0_CLK_L1

MB0_ODT1

MB0_ODT0

MA0_ODT1

MA0_ODT0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_BANK2

MB_BANK1

MB_BANK0

MB_RAS_L

MB_CAS_L

MB_WE_L

4

CPU_VTT_SUS

D10

C10

B10

AD10

W10

AC10

AB10

AA10

A10

Y16

AA16

E16

F16

AF18

AF17

A17

A18

W23

W26

V20

U19

MEM_MB_ADD15

J25

MEM_MB_ADD14

J26

MEM_MB_ADD13

W25

MEM_MB_ADD12

L23

MEM_MB_ADD11

L25

MEM_MB_ADD10

U25

MEM_MB_ADD9

L24

MEM_MB_ADD8

M26

MEM_MB_ADD7

L26

MEM_MB_ADD6

N23

MEM_MB_ADD5

N24

MEM_MB_ADD4

N25

MEM_MB_ADD3

N26

MEM_MB_ADD2

P24

MEM_MB_ADD1

P26

MEM_MB_ADD0

T24

K26

T26

U26

U24

V26

U22

C324

C324

0.1u_0402

0.1u_0402

MEM_MA0_CLK2_N 6

MEM_MA0_CLK1_P 6

MEM_MA0_CLK1_N 6

MEM_MB0_CLK2_P 6

MEM_MB0_CLK2_N 6

MEM_MB0_CLK1_P 6

MEM_MB0_CLK1_N 6

MEM_MB0_ODT1 6,7

MEM_MB0_ODT0 6,7

MEM_MA0_ODT1 6,7

MEM_MA0_ODT0 6,7

MEM_MB_BANK2 6,7

MEM_MB_BANK0 6,7

MEM_MB_RAS# 6,7

MEM_MB_CAS# 6,7

MEM_MB_WE# 6,7

Differential CTT termination

C320

C320

1.5p_0402

1.5p_0402

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

C121

C121

1.5p_0402

1.5p_0402

Differential CTT termination

C119

C119

1.5p_0402

1.5p_0402

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

C120

C120

1.5p_0402

1.5p_0402

CI25

CI25

0.1u_0402_NC

0.1u_0402_NC

EMI

MEM_MB_ADD[15..0] 6,7

3

CI41

CI41

0.1u_0402_NC

0.1u_0402_NC

AF1

3

MEM_MB_DATA[63..0]6

CI24

CI24

0.1u_0402_NC

0.1u_0402_NC

A1

MEM_MB_DM[7..0]6

MEM_MB_DQS7_P6

MEM_MB_DQS7_N6

MEM_MB_DQS6_P6

MEM_MB_DQS6_N6

MEM_MB_DQS5_P6

MEM_MB_DQS5_N6

MEM_MB_DQS4_P6

MEM_MB_DQS4_N6

MEM_MB_DQS3_P6

MEM_MB_DQS3_N6

MEM_MB_DQS2_P6

MEM_MB_DQS2_N6

MEM_MB_DQS1_P6

MEM_MB_DQS1_N6

MEM_MB_DQS0_N6

Athlon 64 S1g1

uPGA638

Top View

2

Processor DDR2 Memory Interface

U13C

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30 MEM_MA_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26 MEM_MA_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21 MEM_MA_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DM7

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AD11

AF11

AF14

AE14

Y11

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

AD12

AC16

AE22

AB26

E25

A22

B16

A12

AF12

AE12

AE16

AD16

AF21

AF22

AC25

AC26

F26

E26

A24

A23

D16

C16

C12

B12

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

A26

U13C

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

DDR: DATA

DDR: DATA

Athlon 64 S1

Processor

Socket

2

AA12

AB12

AA14

AB14

W11

Y12

AD13

AB13

AD15

AB15

AB17

Y17

Y14

W14

W16

AD17

Y18

AD19

AD21

AB21

AB18

AA18

AA20

Y20

AA22

Y22

W21

W22

AA21

AB22

AB24

Y24

H22

H20

E22

E21

J19

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

Y13

MA_DM7

AB16

MA_DM6

Y19

MA_DM5

AC24

MA_DM4

F24

MA_DM3

E19

MA_DM2

C15

MA_DM1

E12

MA_DM0

W12

W13

Y15

W15

AB19

AB20

AD23

AC23

G22

G21

C22

C21

G16

G15

G13

H13

Title

Title

Title

AMD S1 DDRII MEMORY I/F

AMD S1 DDRII MEMORY I/F

AMD S1 DDRII MEMORY I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet of

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_DM7

MEM_MA_DM6MEM_MB_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MS-14141

MS-14141

MS-14141

1

MEM_MA_DATA[63..0] 6

MEM_MA_DM[7..0] 6

MEM_MA_DQS7_P 6

MEM_MA_DQS7_N 6

MEM_MA_DQS6_P 6

MEM_MA_DQS6_N 6

MEM_MA_DQS5_P 6

MEM_MA_DQS5_N 6

MEM_MA_DQS4_P 6

MEM_MA_DQS4_N 6

MEM_MA_DQS3_P 6

MEM_MA_DQS3_N 6

MEM_MA_DQS2_P 6

MEM_MA_DQS2_N 6

MEM_MA_DQS1_P 6

MEM_MA_DQS1_N 6

MEM_MA_DQS0_P 6MEM_MB_DQS0_P6

MEM_MA_DQS0_N 6

337Tuesday, September 26, 2006

337Tuesday, September 26, 2006

337Tuesday, September 26, 2006

1

0.A

0.A

0.A

of

of

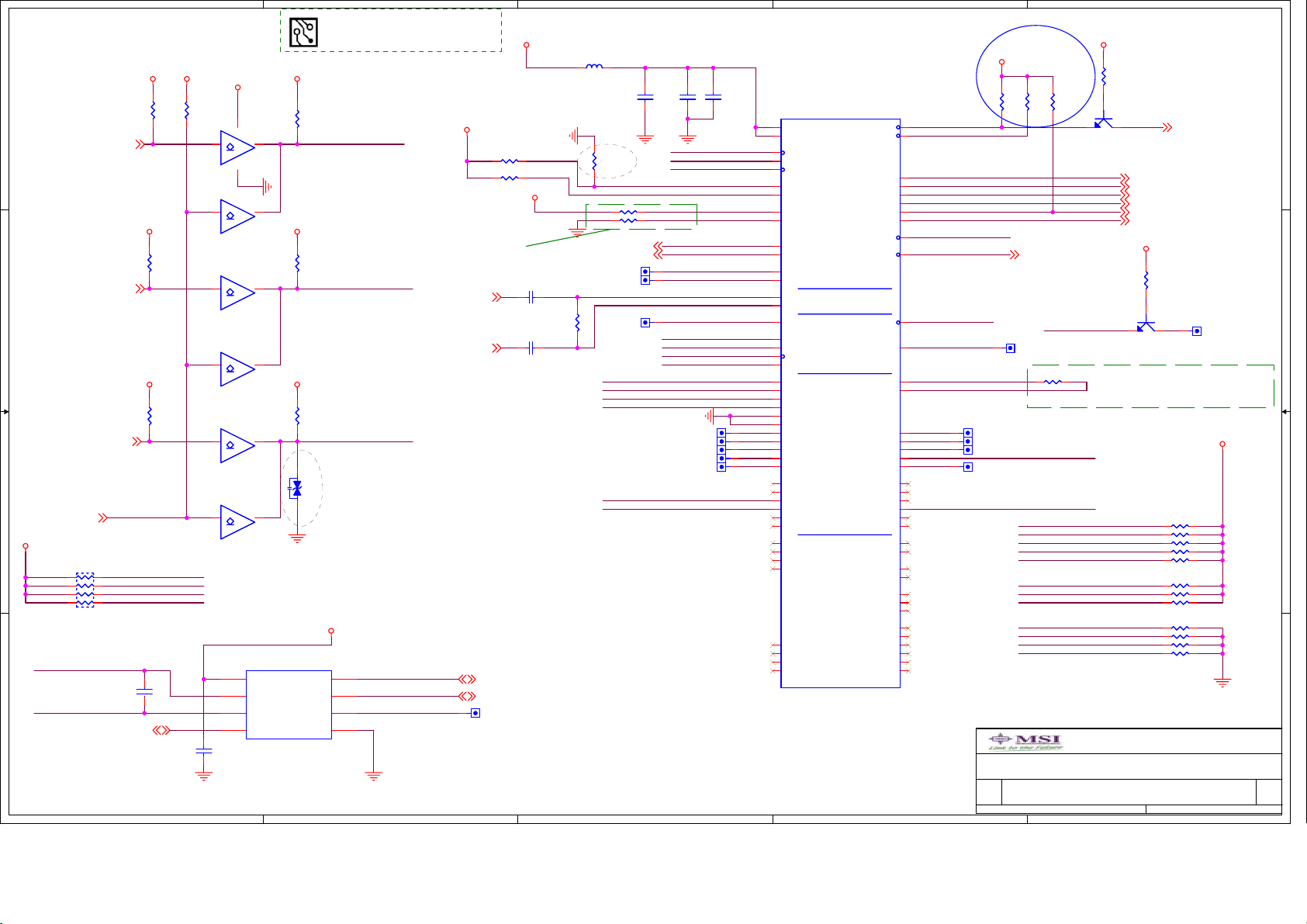

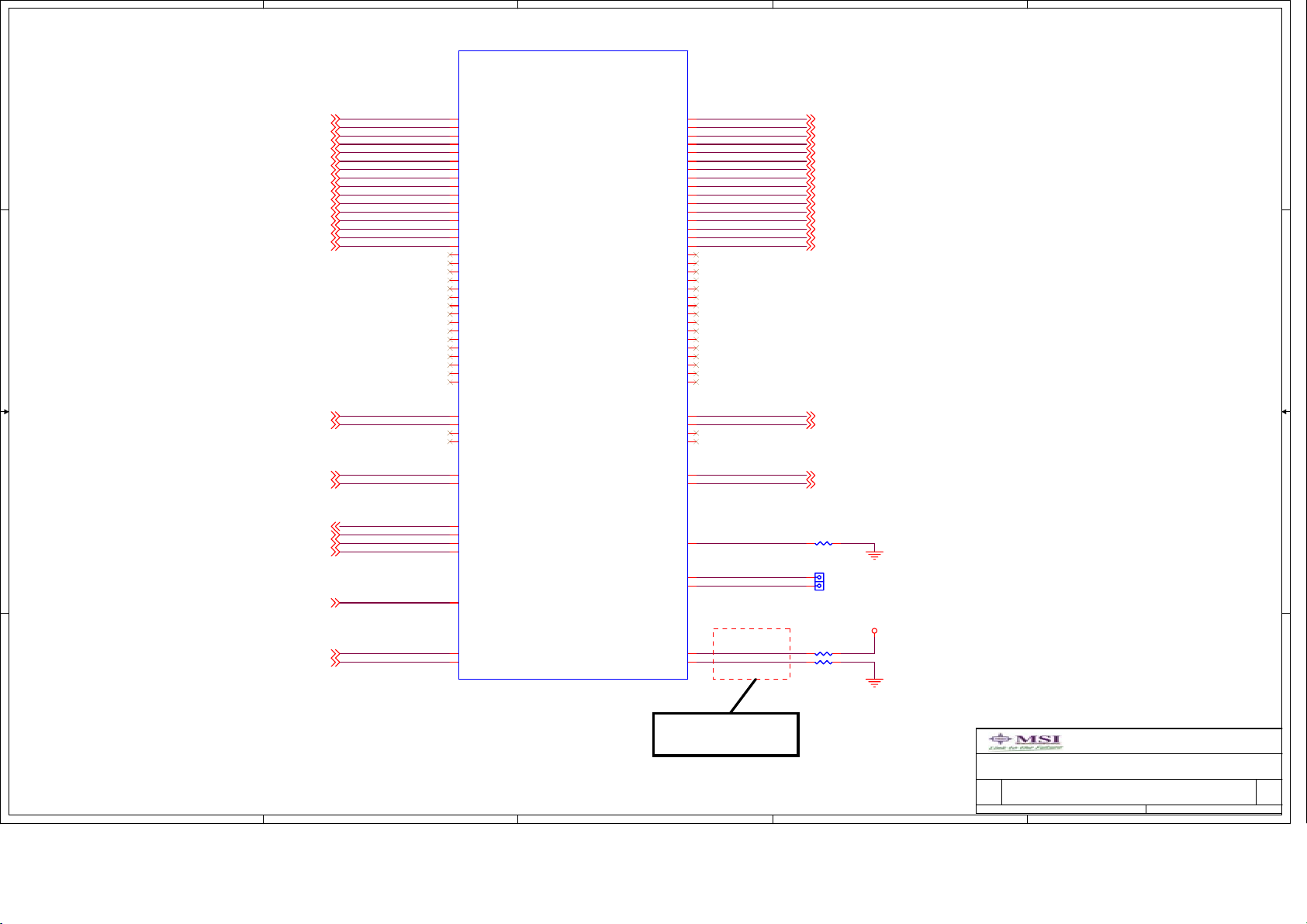

Page 4

5

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

+2.5VRUN

+3VRUN

+3VSUS

4.7KR0402

R181

R181

CPU_CRIT#

C86

C86

0.1u_0402

0.1u_0402

4.7KR0402

DNI

DNI

U12A

U12A

1 2

74LCX07(Open Drain)

74LCX07(Open Drain)

U12B

U12B

3 4

74LCX07(Open Drain)

74LCX07(Open Drain)

U12C

U12C

5 6

74LCX07(Open Drain)

74LCX07(Open Drain)

U12D

U12D

13 12

74LCX07(Open Drain)

74LCX07(Open Drain)

U12E

U12E

11 10

74LCX07(Open Drain)

74LCX07(Open Drain)

U12F

U12F

9 8

74LCX07(Open Drain)

74LCX07(Open Drain)

R177

D D

HTCPU_PWRGD8

R177

1K_0402 1%

1K_0402 1%

De-Glitching Circuit

1/21 Change to OD gate

+2.5VRUN

R179

R179

1K_0402 1%

1K_0402 1%

HTCPU_STOP#8

C C

+2.5VRUN

R183

R183

1K_0402 1%

1K_0402 1%

HTCPU_RST#8

B B

+3VALW

A A

VLDT_PG15,30

RN1

RN1

8P4R-10KR0402

8P4R-10KR0402

CPU_CRIT#

1

2

ALERT#

3

4

SMB_THRMCPU_DATA

5

6

SMB_THRMCPU_CLK

7

8

Cap close to

thermal

sensor

CPU_TEST4_THERMDA

2200P50X0402

2200P50X0402

CPU_TEST5_THERMDC

CPU_CRIT#27

C88

C88

5

CPU_VDDIO_SUS

R178

14

7

U4

U4

1

VDD

2

D+

3

D-

4

T_CRIT_A#

LM86CIMMXNOPB_MSOP8-RH

LM86CIMMXNOPB_MSOP8-RH

R178

300_0402

300_0402

CPU_VDDIO_SUS

R182

R182

300_0402

300_0402

CPU_VDDIO_SUS

R184

R184

300_0402

300_0402

ED1

ED1

ESD-DIODE_NC

ESD-DIODE_NC

1 2

03/21 for EMI

+3VALW

SMBCLK

SMBDATA

ALERT#

GND

Close to CPU socket

CPU_VDDA_2.5_RUN

CPU_ALL_PWROK

3/9 Delete 0 ohm

8

7

6

5

4

CPU_LDTSTOP#

CPU_HT_RESET#

SMB_THRMCPU_CLK

SMB_THRMCPU_DATA

ALERT#

4

+2.5VRUN

CPU_VDDIO_SUS

R189 300_0402_NCR189 300_0402_NC

R187 300_0402R187 300_0402

+VLDT

place them to CPU within

1"(5mil trace 10mil space)

CPU_CLK_P8

CPU_CLK_N8

C316 3.9nC316 3.9n

169_0402 1%

169_0402 1%

C317 3.9nC317 3.9n

SMB_THRMCPU_CLK 20

SMB_THRMCPU_DATA 20

TP6TP6

R185

R185

L14

L14

CPU_VDD_RUN_FB_H33

CPU_VDD_RUN_FB_L33

300L600mA

300L600mA

3

ATHLON Control and Debug

VDDA_L

C96

3.9n

3.9n

CPU_SIC_R

CPU_SID_R

TP17TP17

TP14TP14

CPU_CLKIN_SC_P

TP23TP23

3

C96

CPU_HT_RESET#

CPU_ALL_PWROK

CPU_LDTSTOP#

CPU_VDD_RUN_FB_H

CPU_VDD_RUN_FB_L

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

C89

C89

4.7U_0805

4.7U_0805

R186

R186

300_0402

300_0402

R35 44.2_0603 1%R35 44.2_0603 1%

R38 44.2_0603 1%R38 44.2_0603 1%

CPU_CLKIN_SC_N

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

CPU_TEST5_THERMDC

CPU_TEST4_THERMDA

TP11TP11

TP15TP15

TP16TP16

TP10TP10

TP12TP12

C92

C92

0.22u_0603

0.22u_0603

CPU_HTREF1

CPU_HTREF0

F10

AF4

AF5

G10

AA9

AC9

AD9

AF9

H10

AA7

AC8

AA6

AB6

P20

P19

N20

N19

R26

R25

P22

R22

F8

F9

B7

A7

P6

R6

F6

E6

W9

Y9

A9

A8

E9

E8

G9

C2

D7

E7

F7

C7

C3

W7

W8

Y6

VDDA2

VDDA1

RESET_L

PWROK

LDTSTOP_L

SIC

SID

HT_REF1

HT_REF0

VDD_FB_H

VDD_FB_L

VDDIO_FB_H

VDDIO_FB_L

CLKIN_H

CLKIN_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

THERMDC

THERMDA

TEST3

TEST2

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

AMD NPT S1 SOCKET

Processor Socket

U13D

U13D

THERMTRIP_L

PROCHOT_L

CPU_PRESENT_L

DBREQ_L

JTAC

JTAC

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

MISC

MISC

VID5

VID4

VID3

VID2

VID1

VID0

PSI_L

TDO

TEST8

RSVD8

RSVD9

2

220_0402

220_0402

CPU_THERMTRIP#

AF6

CPU_PROCHOT#_1.8

AC7

CPU_VID5

A5

CPU_VID4

C6

CPU_VID3

A6

CPU_VID2

A4

CPU_VID1

C5

CPU_VID0

B5

CPU_PRESENT#

AC6

CPU_PSI#

A3

CPU_DBREQ#

E10

AE9

C9

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

H16

B18

B3

C1

H6

G6

D5

R24

W18

R23

AA8

H18

H19

2

CPU_TDO

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

1

0824

CPU_VDDIO_SUS

R190

R190

R191

R191

220_0402

220_0402

CPU_PSI# 33

TP21TP21

TP8TP8

TP7TP7

TP13TP13

CPU_TEST21_SCANEN

TP9TP9

CPU_TEST26_BURNIN#

CPU_DBREQ#

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

CPU_TEST26_BURNIN#

CPU_PRESENT#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST21_SCANEN

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST18_PLLTEST1

Title

Title

Title

AMD S1 CTRL

AMD S1 CTRL

AMD S1 CTRL

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

MS-14141

MS-14141

Date: Sheet

Date: Sheet

Date: Sheet

MS-14141

+1.8VRUN

R194

R194

10K

R192

R192

300_0402

300_0402

CPU_PROCHOT#_1.8

R37 80.6_0603 1%R37 80.6_0603 1%

10K

B

E C

Q8

Q8

PMBS3904

PMBS3904

E C

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

PLACE IT CLOSE TO CPU WITHIN 1"

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

CPU_THERMTRIP_D# 13

CPU_VID5 33

CPU_VID4 33

CPU_VID3 33

CPU_VID2 33

CPU_VID1 33

CPU_VID0 33

+1.8VRUN

R193

R193

10K_NC

10K_NC

B

Q9

Q9

SMBT3904_NC

SMBT3904_NC

R47 510_0402_NCR47 510_0402_NC

R45 510_0402_NCR45 510_0402_NC

R43 510_0402_NCR43 510_0402_NC

R196 510_0402_NCR196 510_0402_NC

R195 510_0402_NCR195 510_0402_NC

R188 300_0402R188 300_0402

R39 1K_0402 1%R39 1K_0402 1%

R44 510_0402R44 510_0402

R42 300_0402R42 300_0402

R36 510_0402R36 510_0402

R46 300_0402R46 300_0402

R50 300_0402R50 300_0402

1

TP56TP56

CPU_VDDIO_SUS

437Tuesday, September 26, 2006

437Tuesday, September 26, 2006

437Tuesday, September 26, 2006

of

of

of

0.A

0.A

0.A

Page 5

5

AA4

AA11

AA13

AA15

CPU_VDD_RUN CPU_VDD_RUN

AC4

AD2

J11

J13

K10

K12

K14

L11

L13

M10

N11

P10

R11

T10

T12

T14

U11

U13

V10

G4

H2

J9

K6

L4

L7

L9

M2

M6

M8

N7

N9

P8

R4

R7

R9

T2

T6

T8

U7

U9

V6

V8

D D

C C

A1

B B

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

U13E

U13E

POWER

POWER

Athlon 64 S1

Processor Socket

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

V12

V14

W4

Y2

J15

K16

L15

M16

P16

T16

U15

V16

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

CPU_VDDIO_SUS

A26

Athlon 64 S1g1

uPGA638

AA17

AA19

AB2

AB7

AB9

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD6

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

B11

B13

B15

B17

B19

B21

B23

B25

D11

D13

D15

D17

D19

D21

D23

D25

F11

F13

F15

F17

F19

F21

F23

F25

H21

H23

B4

B6

B8

B9

D6

D8

D9

E4

F2

H7

H9

J4

Top View

AF1

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

4

U13F

U13F

GROUND

GROUND

Athlon 64 S1

Processor

Socket

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

M11

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

3

2

BOTTOMSIDE DECOUPLING

CPU_VDD_RUN

C97

C97

22UF_0805

22UF_0805

CPU_VDD_RUN

CPU_VDDIO_SUS

C132

C132

22UF_0805_NC

22UF_0805_NC

0.22u_0603

0.22u_0603

C84

C84

C98

C98

22UF_0805

22UF_0805

C91

C91

0.22u_0603

0.22u_0603

C126

C126

22UF_0805

22UF_0805

22UF_0805

22UF_0805

C109

C109

22UF_0805

22UF_0805

0.01U25X0402

0.01U25X0402

C87

C87

0.22u_0603

0.22u_0603

C122

C122

C110

C106

C106

22UF_0805_NC

22UF_0805_NC

C90

C90

0.01U25X0402

0.01U25X0402

C127

C127

0.22u_0603

0.22u_0603

C99

C99

22UF_0805_NC

22UF_0805_NC

C100

C100

22UF_0805

22UF_0805

22UF_0805_NC

22UF_0805_NC

C108

C108

22UF_0805

22UF_0805

C107

C107

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

CPU_VDDIO_SUS

0.22u_0603

C239

C239

4.7U_0805

4.7U_0805

CPU_VTT_SUS

C326

C326

4.7U_0805

4.7U_0805

C131

C131

4.7U_0805

4.7U_0805

C325

C325

4.7U_0805

4.7U_0805

4.7U_0805

4.7U_0805

C123

C123

4.7U_0805

4.7U_0805

C323

C323

C145

C145

4.7U_0805

4.7U_0805

C322

C322

4.7U_0805

4.7U_0805

0.22u_0603

0.22u_0603

C237

C237

0.22u_0603

0.22u_0603

C330

C330

C130

C130

0.22u_0603

0.22u_0603

C329

C329

0.22u_0603

0.22u_0603

0.22u_0603

C240

C240

0.22u_0603

0.22u_0603

0.22u_0603

0.22u_0603

C331

C331

C128

C128

0.01U25X0402

0.01U25X0402

C328

C328

0.22u_0603

0.22u_0603

0.01U25X0402

0.01U25X0402

C117

C117

1n_0402

1n_0402

C94

C94

C115

C115

C142

C142

1n_0402

1n_0402

CPU_VTT_SUS CPU_VDDIO_SUS

10n_0402_NC

10n_0402_NC

CE172

CE172

10n_0402_NC

10n_0402_NC

CE160

CE160

CE125 0.1u_0402_NCCE125 0.1u_0402_NC

CE139 0.1u_0402_NCCE139 0.1u_0402_NC

CE109 0.1u_0402_NCCE109 0.1u_0402_NC

FOR EMI FOR EMI

0.01U25X0402

0.01U25X0402

C124

C124

C116

C116

0.01U25X0402

0.01U25X0402

1n_0402

1n_0402

C111

C111

C105

C105

1n_0402

1n_0402

0.01U25X0402

0.01U25X0402

C170

C170

0.01U25X0402

0.01U25X0402

C319

C319

0.01U25X0402

0.01U25X0402

C321

C321

0.01U25X0402

0.01U25X0402

C101

C101

1

CPU_VDDIO_SUSCPU_VDD_RUN

CE86 0.1u_0402_NCCE86 0.1u_0402_NC

CE85 0.1u_0402_NCCE85 0.1u_0402_NCC110

CE84 0.1u_0402_NCCE84 0.1u_0402_NC

CE82 0.1u_0402_NCCE82 0.1u_0402_NC

CE83 0.1u_0402_NCCE83 0.1u_0402_NC

A A

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

AMD S1 Power & Ground

AMD S1 Power & Ground

AMD S1 Power & Ground

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

MS-14141

MS-14141

5

PROCESSOR POWER AND GROUND

4

3

2

Date: Sheet

Date: Sheet

Date: Sheet

MS-14141

MICRO-STAR INT'L CO.,LTD.

537Tuesday, September 26, 2006

537Tuesday, September 26, 2006

537Tuesday, September 26, 2006

of

of

1

of

0.A

0.A

0.A

Page 6

5

CPU_VDDIO_SUS

MEM_MA_ADD[15..0]3,7

D D

MEM_MA_BANK[2..0]3,7

MEM_MA_DM[7..0]3

MEM_MA_DQS0_P3

MEM_MA_DQS1_P3

MEM_MA_DQS2_P3

MEM_MA_DQS3_P3

C231

C231

MEM_MA_DQS4_P3

MEM_MA_DQS5_P3

MEM_MA_DQS6_P3

MEM_MA_DQS7_P3

MEM_MA_DQS0_N3

MEM_MA_DQS1_N3

MEM_MA_DQS2_N3

MEM_MA_DQS3_N3

MEM_MA_DQS4_N3

MEM_MA_DQS5_N3

MEM_MA_DQS6_N3

MEM_MA_DQS7_N3

MEM_MA0_CLK1_P3

MEM_MA0_CLK2_P3

CPU_VDDIO_SUS

C C

B B

47UF_1206

47UF_1206

A A

MEM_MA0_CLK1_N3

MEM_MA0_CLK2_N3

MEM_MA0_CS#03,7

MEM_MA0_CS#13,7

C235

C235

5

MEM_MA_CKE03,7

MEM_MA_CKE13,7

MEM_MA_RAS#3,7

MEM_MA_CAS#3,7

MEM_MA_WE#3,7

MEM_MA0_ODT03,7

MEM_MA0_ODT13,7

47UF_1206

47UF_1206

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

SDATA014

SCLK014

+3VRUN

MEM_M_VREF_SUS

SDATA0

SCLK0

102

A0

101

A1

99

98

97

94

92

93

91

90

89

86

84

85

10

26

52

67

13

31

51

70

11

29

49

68

30

32

79

80

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

1

2

3

8

9

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14/NC

A15/NC

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

SO-DIMM

SO-DIMM

59

100

105

116

107

106

130

147

170

185

131

148

169

188

129

146

167

186

164

166

108

113

109

110

115

114

119

198

200

195

197

199

103

111

104

112

117

118

VDD8

VDD7

VDD9

VDD10

(RVS)

(RVS)

VSS31

VSS30

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

128

127

122

121

4

VDD11

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC/TEST

VSS100

VSS101

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

132

4

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

NC1

NC2

NC3

NC4

J15

J15

DDR2_SO-DIMM_STD1

DDR2_SO-DIMM_STD1

MEM_MA_DATA0

5

MEM_MA_DATA1

7

MEM_MA_DATA2

17

MEM_MA_DATA3

19

MEM_MA_DATA4

4

MEM_MA_DATA5

6

MEM_MA_DATA6

14

MEM_MA_DATA7

16

MEM_MA_DATA8MEM_MA_ADD8

23

MEM_MA_DATA9

25

MEM_MA_DATA10

35

MEM_MA_DATA11

37

MEM_MA_DATA12

20

MEM_MA_DATA13

22

MEM_MA_DATA14

36

MEM_MA_DATA15

38

MEM_MA_DATA16

43

MEM_MA_DATA17

45

MEM_MA_DATA18

55

MEM_MA_DATA19

57

MEM_MA_DATA20

44

MEM_MA_DATA21

46

MEM_MA_DATA22

56

MEM_MA_DATA23

58

MEM_MA_DATA24

61

MEM_MA_DATA25

63

MEM_MA_DATA26

73

MEM_MA_DATA27

75

MEM_MA_DATA28

62

MEM_MA_DATA29

64

MEM_MA_DATA30

74

MEM_MA_DATA31

76

MEM_MA_DATA32

123

MEM_MA_DATA33

125

MEM_MA_DATA34

135

MEM_MA_DATA35

137

MEM_MA_DATA36

124

MEM_MA_DATA37

126

MEM_MA_DATA38

134

MEM_MA_DATA39

136

MEM_MA_DATA40

141

MEM_MA_DATA41

143

MEM_MA_DATA42

151

MEM_MA_DATA43

153

MEM_MA_DATA44

140

MEM_MA_DATA45

142

MEM_MA_DATA46

152

MEM_MA_DATA47

154

MEM_MA_DATA48

157

MEM_MA_DATA49

159

MEM_MA_DATA50

173

MEM_MA_DATA51

175

MEM_MA_DATA52

158

MEM_MA_DATA53

160

MEM_MA_DATA54

174

MEM_MA_DATA55

176

MEM_MA_DATA56

179

MEM_MA_DATA57

181

MEM_MA_DATA58

189

MEM_MA_DATA59

191

MEM_MA_DATA60

180

MEM_MA_DATA61

182

MEM_MA_DATA62

192

MEM_MA_DATA63

194

50

69

83

120

163

201

202

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

C365 0.1u_0402C365 0.1u_0402

C362 0.1u_0402C362 0.1u_0402

C357 0.1u_0402C357 0.1u_0402

C387 0.1u_0402C387 0.1u_0402

C356 0.1u_0402C356 0.1u_0402

C363 0.1u_0402C363 0.1u_0402

C364 0.1u_0402C364 0.1u_0402

C366 0.1u_0402C366 0.1u_0402

C353 0.1u_0402C353 0.1u_0402

C367 0.1u_0402C367 0.1u_0402

C114 0.1u_0402C114 0.1u_0402

C358 0.1u_0402C358 0.1u_0402

MEM_MA0_CS#2 3,7

MEM_MA0_CS#3 3,7

CPU_VDDIO_SUS

1% 0922 by harry

3

MEM_MB_ADD[15..0]3,7

MEM_MA_DATA[63..0] 3

MEM_MB_BANK[2..0]3,7

MEM_MB_DM[7..0]3

CPU_VDDIO_SUS

MEM_VREF_SUS

R223

R223

1K_0402 1%

1K_0402 1%

1n_0402

1n_0402

C360

C360

C144

C144

R222

R222

1n_0402

1n_0402

1K_0402 1%

1K_0402 1%

LAYOUT: PLACE CLOSE TO DIMMs

3

C361

C361

0.1u_0402

0.1u_0402

MEM_MB_DQS0_P3

MEM_MB_DQS1_P3

MEM_MB_DQS2_P3

MEM_MB_DQS3_P3

MEM_MB_DQS4_P3

MEM_MB_DQS5_P3

MEM_MB_DQS6_P3

MEM_MB_DQS7_P3

MEM_MB_DQS0_N3

MEM_MB_DQS1_N3

MEM_MB_DQS2_N3

MEM_MB_DQS3_N3

MEM_MB_DQS4_N3

MEM_MB_DQS5_N3

MEM_MB_DQS6_N3

MEM_MB_DQS7_N3

MEM_MB0_CLK1_P3

MEM_MB0_CLK1_N3

MEM_MB0_CLK2_P3

MEM_MB0_CLK2_N3

MEM_MB0_CS#03,7

MEM_MB0_CS#13,7

MEM_M_VREF_SUS

1n_0402

1n_0402

C171

C171

C339

C339

1n_0402

1n_0402

MEM_MB_CKE03,7

MEM_MB_CKE13,7

MEM_MB_RAS#3,7

MEM_MB_CAS#3,7

MEM_MB_WE#3,7

MEM_MB0_ODT03,7

MEM_MB0_ODT13,7

+3VRUN

SDATA014

SCLK014

MEM_M_VREF_SUS

CPU_VDDIO_SUS

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

R247 4.7KR0402R247 4.7KR0402

SDATA0

SCLK0

+3VRUN

2

103

111

104

112

117

118

J16

J16

MEM_MB_DATA0

102

A0

101

A1

99

98

97

94

92

93

91

90

89

86

84

85

10

26

52

67

13

31

51

70

11

29

49

68

30

32

79

80

1

2

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

2

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14/NC

A15/NC

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VDD081VDD182VDD287VDD388VDD495VDD596VDD6

59

100

105

116

107

106

130

147

170

185

131

148

169

188

129

146

167

186

164

166

108

113

109

110

115

114

119

198

200

195

197

199

VDD8

VDD7

VDD9

SO-DIMM(RVS)

SO-DIMM(RVS)

VSS30

VSS29

VSS2878VSS2777VSS2672VSS2571VSS2466VSS2365VSS2260VSS21

127

122

121

5

DQ0

MEM_MB_DATA1

7

DQ1

MEM_MB_DATA2

17

DQ2

VDD10

VDD11

NC/TEST

VSS100

VSS101

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

132

128

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MEM_MB_DATA3

19

DQ3

MEM_MB_DATA4

4

DQ4

MEM_MB_DATA5

6

DQ5

MEM_MB_DATA6

14

DQ6

MEM_MB_DATA7

16

DQ7

MEM_MB_DATA8

23

DQ8

MEM_MB_DATA9

25

DQ9

MEM_MB_DATA10

35

DQ10

MEM_MB_DATA11

37

DQ11

MEM_MB_DATA12

20

DQ12

MEM_MB_DATA13

22

DQ13

MEM_MB_DATA14

36

DQ14

MEM_MB_DATA15

38

DQ15

MEM_MB_DATA16

43

DQ16

MEM_MB_DATA17

45

DQ17

MEM_MB_DATA18

55

DQ18

MEM_MB_DATA19

57

DQ19

MEM_MB_DATA20

44

DQ20

MEM_MB_DATA21

46

DQ21

MEM_MB_DATA22

56

DQ22

MEM_MB_DATA23

58

DQ23

MEM_MB_DATA24

61

DQ24

MEM_MB_DATA25

63

DQ25

MEM_MB_DATA26

73

DQ26

MEM_MB_DATA27

75

DQ27

MEM_MB_DATA28

62

DQ28

MEM_MB_DATA29

64

DQ29

MEM_MB_DATA30

74

DQ30

MEM_MB_DATA31

76

DQ31

MEM_MB_DATA32

123

DQ32

MEM_MB_DATA33

125

DQ33

MEM_MB_DATA34

135

DQ34

MEM_MB_DATA35

137

DQ35

MEM_MB_DATA36

124

DQ36

MEM_MB_DATA37

126

DQ37

MEM_MB_DATA38

134

DQ38

MEM_MB_DATA39

136

DQ39

MEM_MB_DATA40

141

DQ40

MEM_MB_DATA41

143

DQ41

MEM_MB_DATA42

151

DQ42

MEM_MB_DATA43

153

DQ43

MEM_MB_DATA44

140

DQ44

MEM_MB_DATA45

142

DQ45

MEM_MB_DATA46

152

DQ46

MEM_MB_DATA47

154

DQ47

MEM_MB_DATA48

157

DQ48

MEM_MB_DATA49

159

DQ49

MEM_MB_DATA50

173

DQ50

MEM_MB_DATA51

175

DQ51

MEM_MB_DATA52

158

DQ52

MEM_MB_DATA53

160

DQ53

MEM_MB_DATA54

174

DQ54

MEM_MB_DATA55

176

DQ55

MEM_MB_DATA56

179

DQ56

MEM_MB_DATA57

181

DQ57

MEM_MB_DATA58

189

DQ58

MEM_MB_DATA59

191

DQ59

MEM_MB_DATA60

180

DQ60

MEM_MB_DATA61

182

DQ61

MEM_MB_DATA62

192

DQ62

MEM_MB_DATA63

194

DQ63

50

NC1

69

NC2

83

NC3

120

NC4

163

203

204

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

DDR2-STD

DDR2-STD

DDR2 SODIMMS: A/B CHANNEL

DDR2 SODIMMS: A/B CHANNEL

DDR2 SODIMMS: A/B CHANNEL

MS-14141

MS-14141

MS-14141

1

MEM_MB_DATA[63..0] 3

CPU_VDDIO_SUS

C385 0.1u_0402C385 0.1u_0402

C354 0.1u_0402C354 0.1u_0402

C384 0.1u_0402C384 0.1u_0402

C337 0.1u_0402C337 0.1u_0402

C335 0.1u_0402C335 0.1u_0402

C338 0.1u_0402C338 0.1u_0402

C334 0.1u_0402C334 0.1u_0402

C388 0.1u_0402C388 0.1u_0402

C386 0.1u_0402C386 0.1u_0402

C383 0.1u_0402C383 0.1u_0402

C355 0.1u_0402C355 0.1u_0402

C336 0.1u_0402C336 0.1u_0402

MEM_MB0_CS#2 3,7

MEM_MB0_CS#3 3,7

CPU_VDDIO_SUS

C236

C236

47UF_1206

47UF_1206

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

1

C201

C201

47UF_1206

47UF_1206

637Tuesday, September 26, 2006

637Tuesday, September 26, 2006

637Tuesday, September 26, 2006

of

of

of

0.A

0.A

0.A

Page 7

5

MEM_MA_ADD[15..0]3,6

D D

MEM_MA_BANK[2..0]3,6

C C

MEM_MB_ADD[15..0]3,6

B B

MEM_MB_BANK[2..0]3,6

A A

MEM_MA_ADD[15..0]

MEM_MA_BANK[2..0]

MEM_MA_CAS#3,6

MEM_MA_WE#3,6

MEM_MA_RAS#3,6

MEM_MA0_CS#03,6

MEM_MA0_CS#13,6

MEM_MA0_CS#23,6

MEM_MA0_CS#33,6

MEM_MA0_ODT03,6

MEM_MA0_ODT13,6

MEM_MA_CKE13,6

MEM_MA_CKE03,6

MEM_MB_ADD[15..0]

MEM_MB_BANK[2..0]

MEM_MB_CAS#3,6

MEM_MB_WE#3,6

MEM_MB_RAS#3,6

MEM_MB0_CS#03,6

MEM_MB0_CS#13,6

MEM_MB0_CS#23,6

MEM_MB0_CS#33,6

MEM_MB0_ODT03,6

MEM_MB0_ODT13,6

MEM_MB_CKE13,6

MEM_MB_CKE03,6

5

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CAS#

MEM_MA_WE#

MEM_MA_RAS#

MEM_MA0_CS#0

MEM_MA0_CS#1

MEM_MA0_CS#2

MEM_MA0_CS#3

MEM_MA0_ODT0

MEM_MA0_ODT1

MEM_MA_CKE1

MEM_MA_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0 MEM_MB_ADD15

MEM_MB_CAS#

MEM_MB_WE#

MEM_MB_RAS#

MEM_MB0_CS#0

MEM_MB0_CS#1

MEM_MB0_CS#2

MEM_MB0_CS#3

MEM_MB0_ODT0

MEM_MB0_ODT1

MEM_MB_CKE1

MEM_MB_CKE0

4

MEM_MA_CKE0

MEM_MA_BANK2

MEM_MA_ADD12

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD3

MEM_MA_ADD5

MEM_MA_ADD2

MEM_MA_BANK0

MEM_MA_ADD10

MEM_MA_WE#

MEM_MA_CAS#

MEM_MA_ADD13

MEM_MA0_CS#3

MEM_MA0_ODT1

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA0_CS#2

MEM_MA_CKE1

MEM_MA_ADD6

MEM_MA_ADD4

MEM_MA_ADD7

MEM_MA_ADD11

MEM_MA_BANK1

MEM_MA_RAS#

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA0_CS#1

MEM_MA0_ODT0

MEM_MA0_CS#0

MEM_MB_CKE0

MEM_MB_BANK2

MEM_MB0_CS#2

MEM_MB_ADD12

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD11

MEM_MB_ADD3

MEM_MB_ADD5

MEM_MB_ADD1

MEM_MB_WE#

MEM_MB_ADD10

MEM_MB0_CS#3

MEM_MB_ADD13

MEM_MB0_ODT1

MEM_MB0_ODT0

MEM_MB_ADD7

MEM_MB_ADD14

MEM_MB_CKE1

MEM_MB_ADD0

MEM_MB_ADD2

MEM_MB_ADD6

MEM_MB_ADD4

MEM_MB0_CS#0

MEM_MB_RAS#

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_CAS#

MEM_MB0_CS#1

4

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

3

2

1

EMI

1

MEM_MA_ADD6

CI20

CI20

10p_0402_NC

10p_0402_NC

MEM_MA_ADD13

CI12

CI12

10p_0402_NC

10p_0402_NC

MEM_MB_ADD4

CI66

CI66

10p_0402_NC

10p_0402_NC

MEM_MB_ADD11

CI64

CI64

10p_0402_NC

10p_0402_NC

MEM_MA_BANK2

CI48

CI48

10p_0402_NC

10p_0402_NC

MEM_MB_CKE1

CI57

CI57

10p_0402_NC

10p_0402_NC

MEM_MA0_CS#0

CI18

CI18

10p_0402_NC

10p_0402_NC

MEM_MB0_CS#3

CI71

CI71

10p_0402_NC

10p_0402_NC

737Tuesday, September 26, 2006

737Tuesday, September 26, 2006

737Tuesday, September 26, 2006

of

of

of

0.A

0.A

0.A

MEM_MA_ADD5

CI51

CI51

10p_0402_NC

10p_0402_NC

CI49

CI49

10p_0402_NC

10p_0402_NC

MEM_MB_ADD3MEM_MB_ADD0

CI35

CI35

10p_0402_NC

10p_0402_NC

MEM_MB_ADD10

CI27

CI27

10p_0402_NC

10p_0402_NC

MEM_MA_BANK1

CI23

CI23

10p_0402_NC

10p_0402_NC

MEM_MB_CKE0

CI26

CI26

10p_0402_NC

10p_0402_NC

MEM_MB_RAS#

CI60

CI60

10p_0402_NC

10p_0402_NC

MEM_MB0_CS#2

CI40

CI40

10p_0402_NC

10p_0402_NC

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

2

MEM_MA_ADD2

CI11

CI11

10p_0402_NC

10p_0402_NC

MEM_MA_ADD9

CI54

CI54

10p_0402_NC

10p_0402_NC

CI67

CI67

10p_0402_NC

10p_0402_NC

MEM_MB_ADD7

CI59

CI59

10p_0402_NC

10p_0402_NC

MEM_MB_ADD14

CI63

CI63

10p_0402_NC

10p_0402_NC

MEM_MB_BANK2

CI39

CI39

10p_0402_NC

10p_0402_NC

MEM_MA_RAS#

CI14

CI14

10p_0402_NC

10p_0402_NC

MEM_MA0_CS#3

CI10

CI10

10p_0402_NC

10p_0402_NC

MEM_MB0_ODT0

CI61

CI61

10p_0402_NC

10p_0402_NC

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

MEM_MA_ADD3

CI53

CI53

10p_0402_NC

10p_0402_NC

MEM_MA_ADD10

CI43

CI43

10p_0402_NC

10p_0402_NC

MEM_MB_ADD1MEM_MA_ADD14

CI32

CI32

10p_0402_NC

10p_0402_NC

MEM_MB_ADD8

CI36

CI36

10p_0402_NC

10p_0402_NC

MEM_MB_ADD15

CI58

CI58

10p_0402_NC

10p_0402_NC

MEM_MA_CKE0

CI47

CI47

10p_0402_NC

10p_0402_NC

CI28

CI28

10p_0402_NC

10p_0402_NC

CI69

CI69

10p_0402_NC

10p_0402_NC

MEM_MB0_ODT1

CI37

CI37

10p_0402_NC

10p_0402_NC

DDR2 SODIMMS TERMINATIONS

DDR2 SODIMMS TERMINATIONS

DDR2 SODIMMS TERMINATIONS

Custom

Custom

Custom

MEM_MA_ADD4

CI19

CI19

10p_0402_NC

10p_0402_NC

MEM_MA_ADD11MEM_MA_ADD8MEM_MA_ADD7 MEM_MA_ADD12

CI22

CI22

10p_0402_NC

10p_0402_NC

MEM_MB_ADD2MEM_MA_ADD15

CI62

CI62

10p_0402_NC

10p_0402_NC

MEM_MB_ADD9

CI30

CI30

10p_0402_NC

10p_0402_NC

MEM_MA_BANK0

CI56

CI56

10p_0402_NC

10p_0402_NC

MEM_MA_CKE1

CI9

CI9

10p_0402_NC

10p_0402_NC

MEM_MB_WE#

CI31

CI31

10p_0402_NC

10p_0402_NC

MEM_MB0_CS#1

CI29

CI29

10p_0402_NC

10p_0402_NC

MS-14141

MS-14141

MS-14141

CPU_VTT_SUS

RN3

RN3

RN2

RN2

RN4

RN4

RN5

RN5

RN8

RN8

RN9

RN9

RN10

RN10

RN11

RN11

CPU_VTT_SUS

RN15

RN15

RN14

RN14

RN13

RN13

RN20

RN20

RN17

RN17

RN18

RN18

RN19

RN19

RN12

RN12

C159 0.1u_0402_NCC159 0.1u_0402_NC

C162 0.1u_0402C162 0.1u_0402

C175 0.1u_0402_NCC175 0.1u_0402_NC

C160 0.1u_0402C160 0.1u_0402

C173 0.1u_0402_NCC173 0.1u_0402_NC

C157 0.1u_0402C157 0.1u_0402

C172 0.1u_0402_NCC172 0.1u_0402_NC

C155 0.1u_0402C155 0.1u_0402

C134 0.1u_0402_NCC134 0.1u_0402_NC

C135 0.1u_0402C135 0.1u_0402

C141 0.1u_0402_NCC141 0.1u_0402_NC

C136 0.1u_0402C136 0.1u_0402

C137 0.1u_0402_NCC137 0.1u_0402_NC

C138 0.1u_0402C138 0.1u_0402

C139 0.1u_0402_NCC139 0.1u_0402_NC

C140 0.1u_0402C140 0.1u_0402

C214 0.1u_0402_NCC214 0.1u_0402_NC

C216 0.1u_0402C216 0.1u_0402

C217 0.1u_0402_NCC217 0.1u_0402_NC

C218 0.1u_0402C218 0.1u_0402

C219 0.1u_0402_NCC219 0.1u_0402_NC

C220 0.1u_0402C220 0.1u_0402

C221 0.1u_0402_NCC221 0.1u_0402_NC

C222 0.1u_0402C222 0.1u_0402

C156 0.1u_0402_NCC156 0.1u_0402_NC

C182 0.1u_0402C182 0.1u_0402

C158 0.1u_0402_NCC158 0.1u_0402_NC

C183 0.1u_0402C183 0.1u_0402

C174 0.1u_0402_NCC174 0.1u_0402_NC

C161 0.1u_0402C161 0.1u_0402

C176 0.1u_0402_NCC176 0.1u_0402_NC

C215 0.1u_0402C215 0.1u_0402

3

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

MEM_MA_ADD0

CI21

CI21

10p_0402_NC

10p_0402_NC

CI13

CI13

10p_0402_NC

10p_0402_NC

CI16

CI16

10p_0402_NC

10p_0402_NC

MEM_MB_ADD5

CI34

CI34

10p_0402_NC

10p_0402_NC

MEM_MB_ADD12

CI33

CI33

10p_0402_NC

10p_0402_NC

MEM_MB_BANK0

CI38

CI38

10p_0402_NC

10p_0402_NC

MEM_MA_CAS# MEM_MB_CAS#

CI55

CI55

10p_0402_NC

10p_0402_NC

MEM_MA0_CS#1 MEM_MB0_CS#0

CI45

CI45

10p_0402_NC

10p_0402_NC

MEM_MA0_ODT0

CI17

CI17

10p_0402_NC

10p_0402_NC

MEM_MA_ADD1

CI42

CI42

10p_0402_NC

10p_0402_NC

CI50

CI50

10p_0402_NC

10p_0402_NC

CI15

CI15

10p_0402_NC

10p_0402_NC

MEM_MB_ADD6

CI65

CI65

10p_0402_NC

10p_0402_NC

MEM_MB_ADD13

CI70

CI70

10p_0402_NC

10p_0402_NC

MEM_MB_BANK1

CI68

CI68

10p_0402_NC

10p_0402_NC

MEM_MA_WE#

CI44

CI44

10p_0402_NC

10p_0402_NC

MEM_MA0_CS#2

CI52

CI52

10p_0402_NC

10p_0402_NC

MEM_MA0_ODT1

CI46

CI46

10p_0402_NC

10p_0402_NC

Page 8

5

D D

HT_CADOUT0_P2

HT_CADOUT0_N2

HT_CADOUT1_P2

HT_CADOUT1_N2

HT_CADOUT2_P2

HT_CADOUT2_N2

HT_CADOUT3_P2

HT_CADOUT3_N2

HT_CADOUT4_P2

HT_CADOUT4_N2

HT_CADOUT5_P2

HT_CADOUT5_N2

HT_CADOUT6_P2

HT_CADOUT6_N2

HT_CADOUT7_P2

HT_CADOUT7_N2

HT_CADOUT8_P2

HT_CADOUT8_N2

HT_CADOUT9_P2

HT_CADOUT9_N2

C C

HT_CADOUT10_P2

HT_CADOUT10_N2

HT_CADOUT11_P2

HT_CADOUT11_N2

HT_CADOUT12_P2

HT_CADOUT12_N2

HT_CADOUT13_P2

HT_CADOUT13_N2

HT_CADOUT14_P2

HT_CADOUT14_N2

HT_CADOUT15_P2

HT_CADOUT15_N2

4

U11A

U11A

C51MV

C51MV

CPU-HT

Y23

HT_CPU_RXD0_P

Y22

HT_CPU_RXD0_N

W24

HT_CPU_RXD1_P

W23

HT_CPU_RXD1_N

V24

HT_CPU_RXD2_P

V23

HT_CPU_RXD2_N

U22

HT_CPU_RXD3_P

U21

HT_CPU_RXD3_N

R24

HT_CPU_RXD4_P

R23

HT_CPU_RXD4_N

P24

HT_CPU_RXD5_P

P23

HT_CPU_RXD5_N

P22

HT_CPU_RXD6_P

P21

HT_CPU_RXD6_N

N22

HT_CPU_RXD7_P

N21

HT_CPU_RXD7_N

Y21

HT_CPU_RXD8_P

Y20

HT_CPU_RXD8_N

V21

HT_CPU_RXD9_P

W20

HT_CPU_RXD9_N

W21

HT_CPU_RXD10_P

W22

HT_CPU_RXD10_N

T21

HT_CPU_RXD11_P

U20

HT_CPU_RXD11_N

R18

HT_CPU_RXD12_P

R19

HT_CPU_RXD12_N

P16

HT_CPU_RXD13_P

P17

HT_CPU_RXD13_N

N20

HT_CPU_RXD14_P

N19

HT_CPU_RXD14_N

M17

HT_CPU_RXD15_P

N18

HT_CPU_RXD15_N

CPU-HT

HT_CPU_TXD10_N

HT_CPU_TXD11_P

HT_CPU_TXD11_N

HT_CPU_TXD12_P

HT_CPU_TXD12_N

HT_CPU_TXD13_P

HT_CPU_TXD13_N

HT_CPU_TXD14_P

HT_CPU_TXD14_N

HT_CPU_TXD15_P

HT_CPU_TXD15_N

3

PART 1 OF 5

PART 1 OF 5

HT_CPU_TXD0_P

HT_CPU_TXD0_N

HT_CPU_TXD1_P

HT_CPU_TXD1_N

HT_CPU_TXD2_P

HT_CPU_TXD2_N

HT_CPU_TXD3_P

HT_CPU_TXD3_N

HT_CPU_TXD4_P

HT_CPU_TXD4_N

HT_CPU_TXD5_P

HT_CPU_TXD5_N

HT_CPU_TXD6_P

HT_CPU_TXD6_N

HT_CPU_TXD7_P

HT_CPU_TXD7_N

HT_CPU_TXD8_P

HT_CPU_TXD8_N

HT_CPU_TXD9_P

HT_CPU_TXD9_N

HT_CPU_TXD10_P

C23

C24

D23

D24

E22

E23

F23

F24

H22

H23

J21

J22

K21

K22

K23

K24

D21

D22

F19

E20

F21

E21

G20

G19

J19

J18

L17

K17

L20

K19

L18

L19

HT_CADIN0_P 2

HT_CADIN0_N 2

HT_CADIN1_P 2

HT_CADIN1_N 2

HT_CADIN2_P 2

HT_CADIN2_N 2

HT_CADIN3_P 2

HT_CADIN3_N 2

HT_CADIN4_P 2

HT_CADIN4_N 2

HT_CADIN5_P 2

HT_CADIN5_N 2

HT_CADIN6_P 2

HT_CADIN6_N 2

HT_CADIN7_P 2

HT_CADIN7_N 2

HT_CADIN8_P 2

HT_CADIN8_N 2

HT_CADIN9_P 2

HT_CADIN9_N 2

HT_CADIN10_P 2

HT_CADIN10_N 2

HT_CADIN11_P 2

HT_CADIN11_N 2

HT_CADIN12_P 2

HT_CADIN12_N 2

HT_CADIN13_P 2

HT_CADIN13_N 2

HT_CADIN14_P 2

HT_CADIN14_N 2

HT_CADIN15_P 2

HT_CADIN15_N 2

2

1

HT_CLKOUT0_P2

HT_CLKOUT0_N2

HT_CLKOUT1_P2

HT_CLKOUT1_N2

HT_CTLOUT0_P2

+VLDT

+1.2VPLL_HT

1U10X

1U10X

C76

C76

HT_CTLOUT0_N2

R27150_0402 1% R27150_0402 1%

R28150_0402 1% R28150_0402 1%

C70

C70

0.1u_0402

0.1u_0402

B B

+1.2VRUN

A A

5

L11

L11

220L3A

220L3A

T23

HT_CPU_RX_CLK0_P

T22

HT_CPU_RX_CLK0_N

R21

HT_CPU_RX_CLK1_P

R20

HT_CPU_RX_CLK1_N

M23

HT_CPU_RXCTL_P

M22

HT_CPU_RXCTL_N

W19

HT_CPU_CAL_1P2V

Y19

HT_CPU_CAL_GND

N16

+1.2V_PLLHTCPU

T13

+1.2V_PLLHTMCP

nVIDIA_C51MV

nVIDIA_C51MV

Place within 500 mils of ball,

route 5/10

4

HT_CPU_TX_CLK0_P

HT_CPU_TX_CLK0_N

HT_CPU_TX_CLK1_P

HT_CPU_TX_CLK1_N

HT_CPU_TXCTL_P

HT_CPU_TXCTL_N

CLKOUT_PRI_200MHZ_P

CLKOUT_PRI_200MHZ_N

CLKOUT_SEC_200MHZ_P

CLKOUT_SEC_200MHZ_N

HT_CPU_REQ#

HT_CPU_STOP#

HT_CPU_RESET#

HT_CPU_PWRGD

+2.5V_PLLHTCPU

4.7U_0805_NC

4.7U_0805_NC

3

G23

G24

G22

G21

L23

L24

B24

B23

A22

B21

F18

G18

D20

E19

L16

C64

C64

HTCPU_REQ#

HT_CLKIN0_P 2

HT_CLKIN0_N 2

HT_CLKIN1_P 2

HT_CLKIN1_N 2

HT_CTLIN0_P 2

HT_CTLIN0_N 2

CPU_CLK_P 4

CPU_CLK_N 4

R2522K_0402 R2522K_0402

HTCPU_STOP# 4

HTCPU_RST# 4

HTCPU_PWRGD 4

L10

L10

220L3A

220L3A

C65

C65

1UF_0402

1UF_0402

+2.5VRUN

+2.5VRUN

3/9 Modify

2

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

Title

Title

Title

C51MV/D HT CPU

C51MV/D HT CPU

C51MV/D HT CPU

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

B

B

B

MS-14141

MS-14141

Date: Sheet

Date: Sheet

Date: Sheet

MS-14141

MICRO-STAR INT'L CO.,LTD.

837Tuesday, September 26, 2006

837Tuesday, September 26, 2006

837Tuesday, September 26, 2006

of

of

1

of

0.A

0.A

0.A

Page 9

5

D D

C C

HT_MCP_RX0_P13

HT_MCP_RX0_N13

HT_MCP_RX1_P13

HT_MCP_RX1_N13

HT_MCP_RX2_P13

HT_MCP_RX2_N13

HT_MCP_RX3_P13

HT_MCP_RX3_N13

HT_MCP_RX4_P13

HT_MCP_RX4_N13

HT_MCP_RX5_P13

HT_MCP_RX5_N13

HT_MCP_RX6_P13

HT_MCP_RX6_N13

HT_MCP_RX7_P13

HT_MCP_RX7_N13

4

U11B

U11B

C51MV

C51MV

MCP-HT

AD6

AC6

AC7

AB7

AA8

AB8

AA9

AB9

AD10

AC10

AD11

AC11

AC12

AB12

AC13

AB13

AA6

AA7

Y10

W10

AA11

Y12

V11

W11

W12

V13

Y6

W7

Y7

Y8

V9

W9

HT_MCP_RXD0_P

HT_MCP_RXD0_N

HT_MCP_RXD1_P

HT_MCP_RXD1_N

HT_MCP_RXD2_P

HT_MCP_RXD2_N

HT_MCP_RXD3_P

HT_MCP_RXD3_N

HT_MCP_RXD4_P

HT_MCP_RXD4_N

HT_MCP_RXD5_P

HT_MCP_RXD5_N

HT_MCP_RXD6_P

HT_MCP_RXD6_N

HT_MCP_RXD7_P

HT_MCP_RXD7_N

HT_MCP_RXD8_P

HT_MCP_RXD8_N

HT_MCP_RXD9_P

HT_MCP_RXD9_N

HT_MCP_RXD10_P

HT_MCP_RXD10_N

HT_MCP_RXD11_P

HT_MCP_RXD11_N

HT_MCP_RXD12_P

HT_MCP_RXD12_N

HT_MCP_RXD13_P

HT_MCP_RXD13_N

HT_MCP_RXD14_P

HT_MCP_RXD14_N

HT_MCP_RXD15_P

HT_MCP_RXD15_N

MCP-HT

3

PART 2 OF 5

PART 2 OF 5

HT_MCP_TXD0_P

HT_MCP_TXD0_N

HT_MCP_TXD1_P

HT_MCP_TXD1_N

HT_MCP_TXD2_P

HT_MCP_TXD2_N

HT_MCP_TXD3_P

HT_MCP_TXD3_N

HT_MCP_TXD4_P

HT_MCP_TXD4_N

HT_MCP_TXD5_P

HT_MCP_TXD5_N

HT_MCP_TXD6_P

HT_MCP_TXD6_N

HT_MCP_TXD7_P

HT_MCP_TXD7_N

HT_MCP_TXD8_P

HT_MCP_TXD8_N

HT_MCP_TXD9_P

HT_MCP_TXD9_N

HT_MCP_TXD10_P

HT_MCP_TXD10_N

HT_MCP_TXD11_P

HT_MCP_TXD11_N

HT_MCP_TXD12_P

HT_MCP_TXD12_N

HT_MCP_TXD13_P

HT_MCP_TXD13_N

HT_MCP_TXD14_P

HT_MCP_TXD14_N

HT_MCP_TXD15_P

HT_MCP_TXD15_N

AC24

AC23

AD23

AD22

AC22

AC21

AC20

AD20

AB18

AC18

AA17

AB17

AB16

AB15

AC16

AD16

AB21

AB22

AB20

AA20

AB19

AA19

W18

V17

W15

V15

AA15

Y15

Y14

W14

W13

Y13

HT_MCP_TX0_P 13

HT_MCP_TX0_N 13

HT_MCP_TX1_P 13

HT_MCP_TX1_N 13

HT_MCP_TX2_P 13

HT_MCP_TX2_N 13

HT_MCP_TX3_P 13

HT_MCP_TX3_N 13

HT_MCP_TX4_P 13

HT_MCP_TX4_N 13

HT_MCP_TX5_P 13

HT_MCP_TX5_N 13

HT_MCP_TX6_P 13

HT_MCP_TX6_N 13

HT_MCP_TX7_P 13

HT_MCP_TX7_N 13

2

1

HT_MCP_RX_CLK0_P13

HT_MCP_RX_CLK0_N13

HT_MCP_RX_CTL_P13

HT_MCP_RX_CTL_N13

B B

A A

5