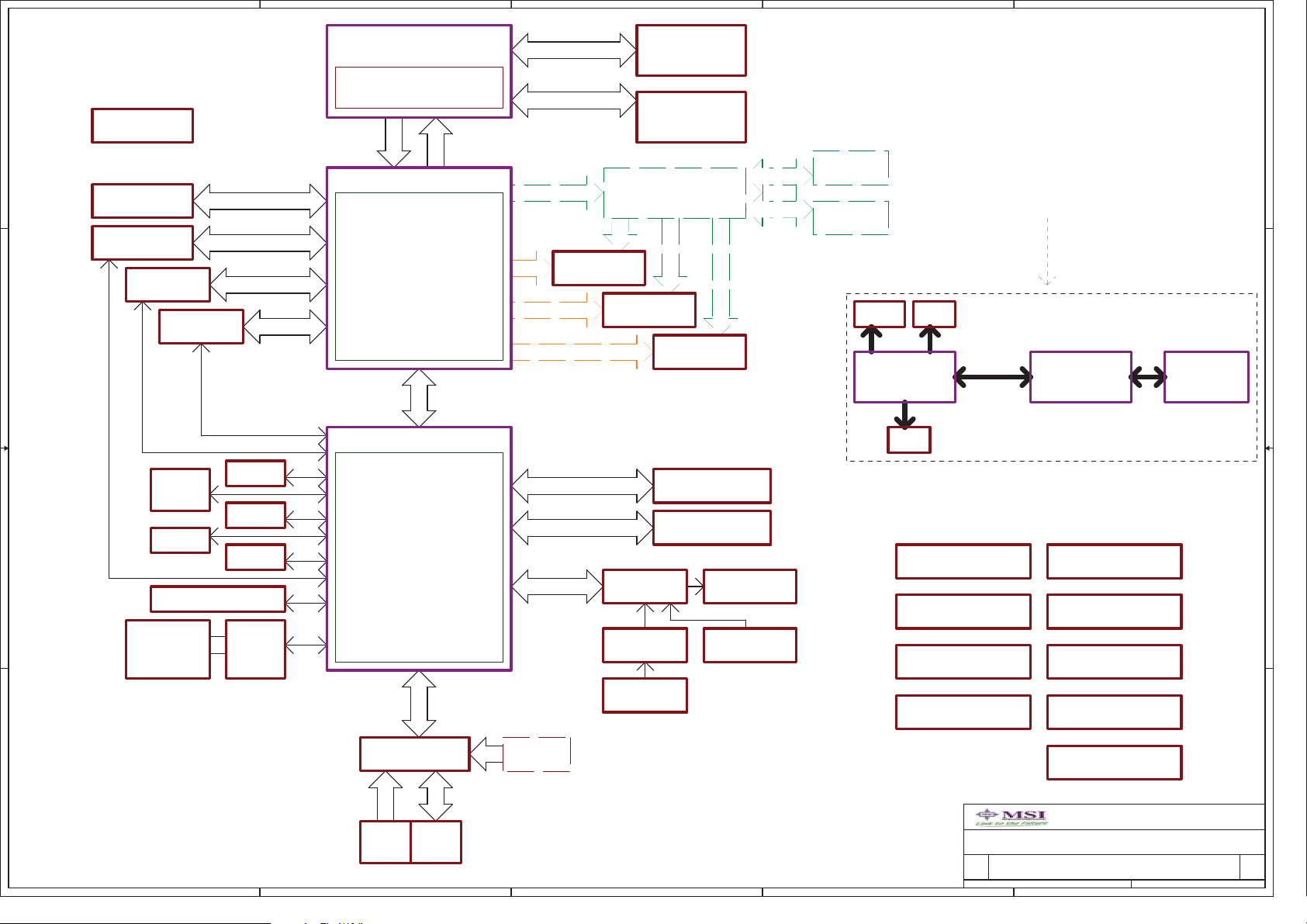

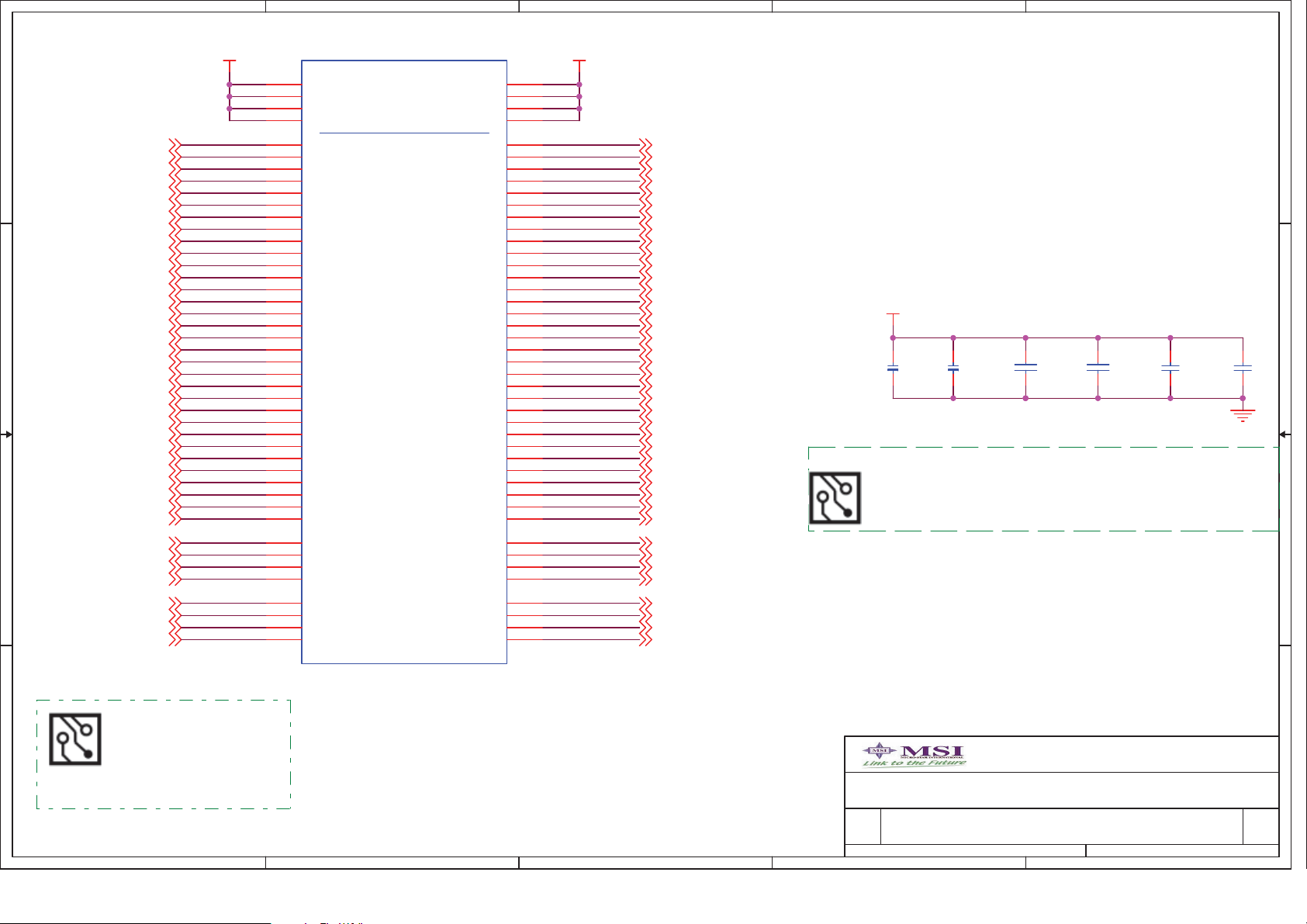

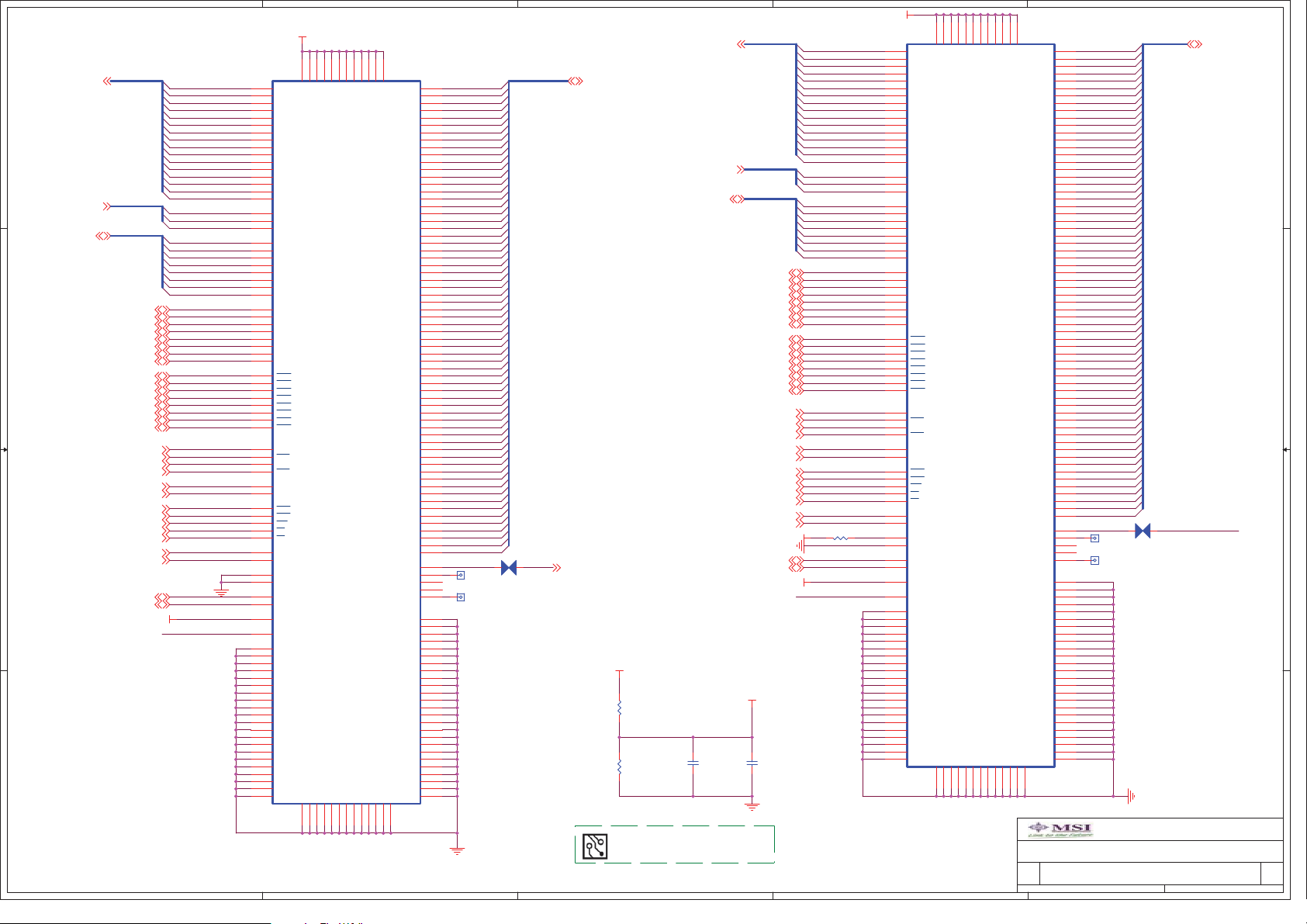

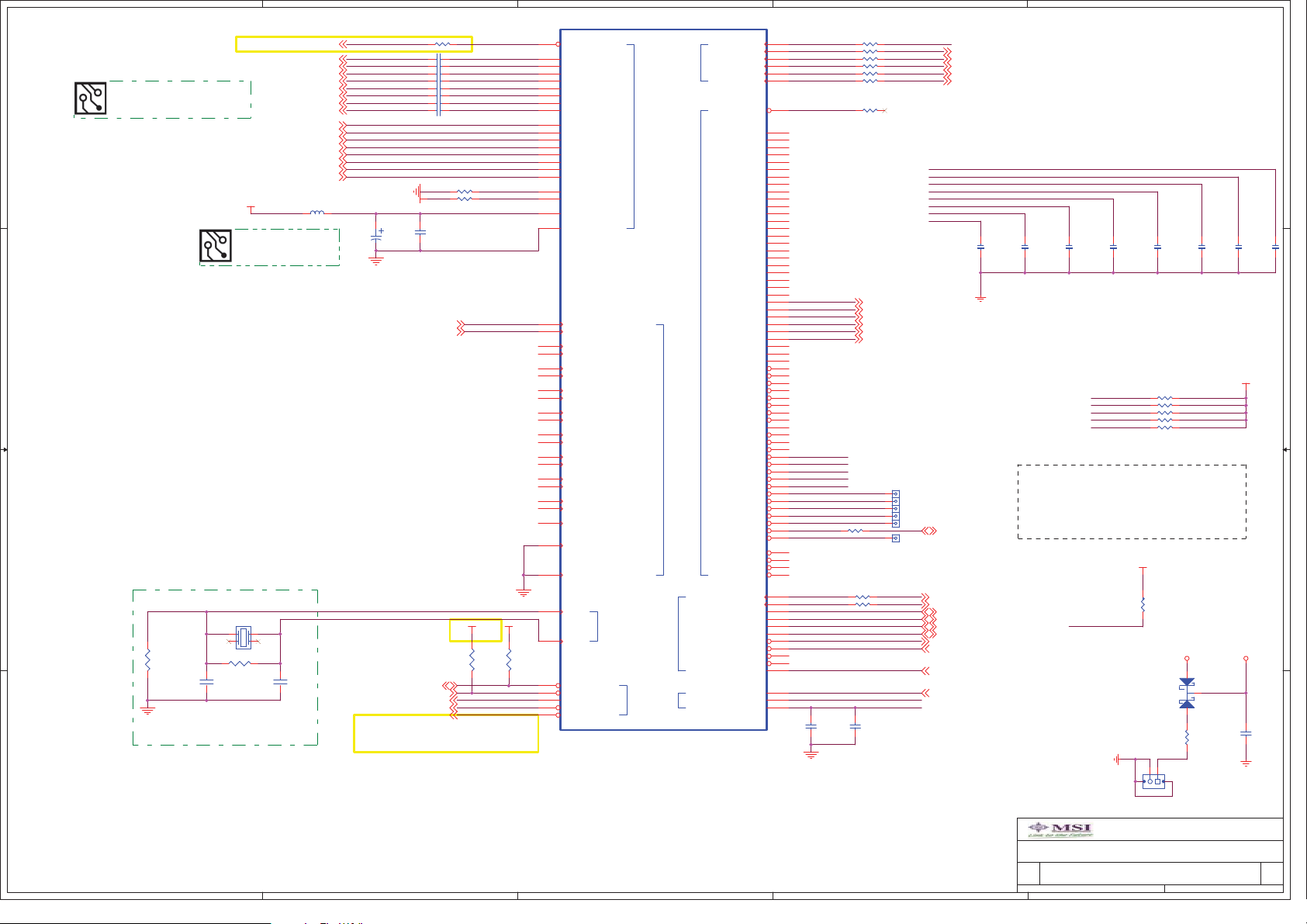

MSI MS-13331, EX310 Schematics

5

FWU

4

3

2

1

AMD S1G2

EXTERNAL CLOCK GENERATOR

D D

C C

CS9LPRS472

RTL8111B

PCIE ETHERNET

Express CARD

USB7

16

33

31

USB1

38

MINI-PCIE

PCIE I/F

PCIE I/F

USB0

38

PCIE I/FMINI-PCIE

PCIE I/F

PROCESSOR

638-Pin uFCPGA 638

CPU REV 11

HT3 2600Mhz

5.2GT/s

16x16

OUT

ATI NB - RS780M

HyperTransport LINK3 CPU I/F

DX10 IGP

LVDS/TVOUT/TMDS

1 X16 PCIE GFX I/F

1 X4 A-Link II-E I/F WITH SB

6 X1 PCIE GPP I/F

11,12,13,14,15

5,6,7,8

IN

A-LINK II

PCIE1.1

1X4 Lanes

2.5Gbps/L

DDRII 800MT/S

DDRII 800MT/S

X16 PEIE I/F

VGA CON

CRT

LVDS

TMDS

ATI SB - SB700

USB2

USB3

FINGER

PRINT

36

36

USB5

USBCONN2

B B

BLUETOOTH

3in1

CONNECTOR

30

A A

36

CAMERA

36

USB4

USBCONN1

36

USB6

USBCONN3

USB8

36

USB9

RTS5158

CARD

READER

30

USB 2.0 (12 PORTS)

SATA II (6 PORTS)

ATA 66/100/133

SMBus 2.0

SPI I/F

LPC I/F

ACPI 2.0

INT RTC

HW MONITOR

PCI/PCI BDGE

17, 18, 19, 20, 21

LPC BUS

ENE3954

KBC ENE3945

SATA 1.5/2.5/3Gbps

UP TO SATAII

SATA 1.5/2.5/3Gbps

HD AUDIO I/F

CIR

39

(DNI)

36

UNBUFFERED

DDR2 NEAR

SODIMM

200-PIN DDR2 SODIMM

UNBUFFERED

DDR2 FAR

SODIMM

200-PIN DDR2 SODIMM

9,10

9,10

ATI VGA - M82S

22,23,24,25,26,28,29

CRT

40

LVDS CON

ALC888

HD CODEC EARPHONE

FM2010

DSP

ARRAY

MICROPHONE

LVDS

40

HDMI

SATA H.D.D. CONN.

SATA O.D.D. CONN.

32

32

TMDS

41

JACK

MICROPHONE

JACK

667M

667M

37

37

GDDRIII

27

Option Orange for MS13321 & MS12241

Option Green for MS13331 & MS12251

GDDRIII

27

HDMI LVDS

ATI NB RS780M

3534

35

Option below for Cross File Circuit

ATI VGA M82S

VGA

CPU&RS780 HT VLDT

POWER

CPU CORE POWER

CPU MEMORY POWER

SYSTEM MAIN POWER

RS780 CORE POWER

47 44

SB700 & PCIE POWER

47

M82S & GDDR III

POWER

46

BATTERY CHAGER

43

DISCHARGE CIRCUIT

GDDRIII

X2

44

45

50

43

PS2

SPI I/F

KBD

MOUSE

5

SPI

ROM

39 39

4

3

2

Title

BLOCK DIAGRAM

Size Document Number Rev

Custom

Date: Sheet

MS-13331

MICRO-STAR INT'L CO.,LTD.

155Tuesday, December 11, 2007

1

of

0B

http://laptop-motherboard-schematic.blogspot.com/

5

4

3

2

1

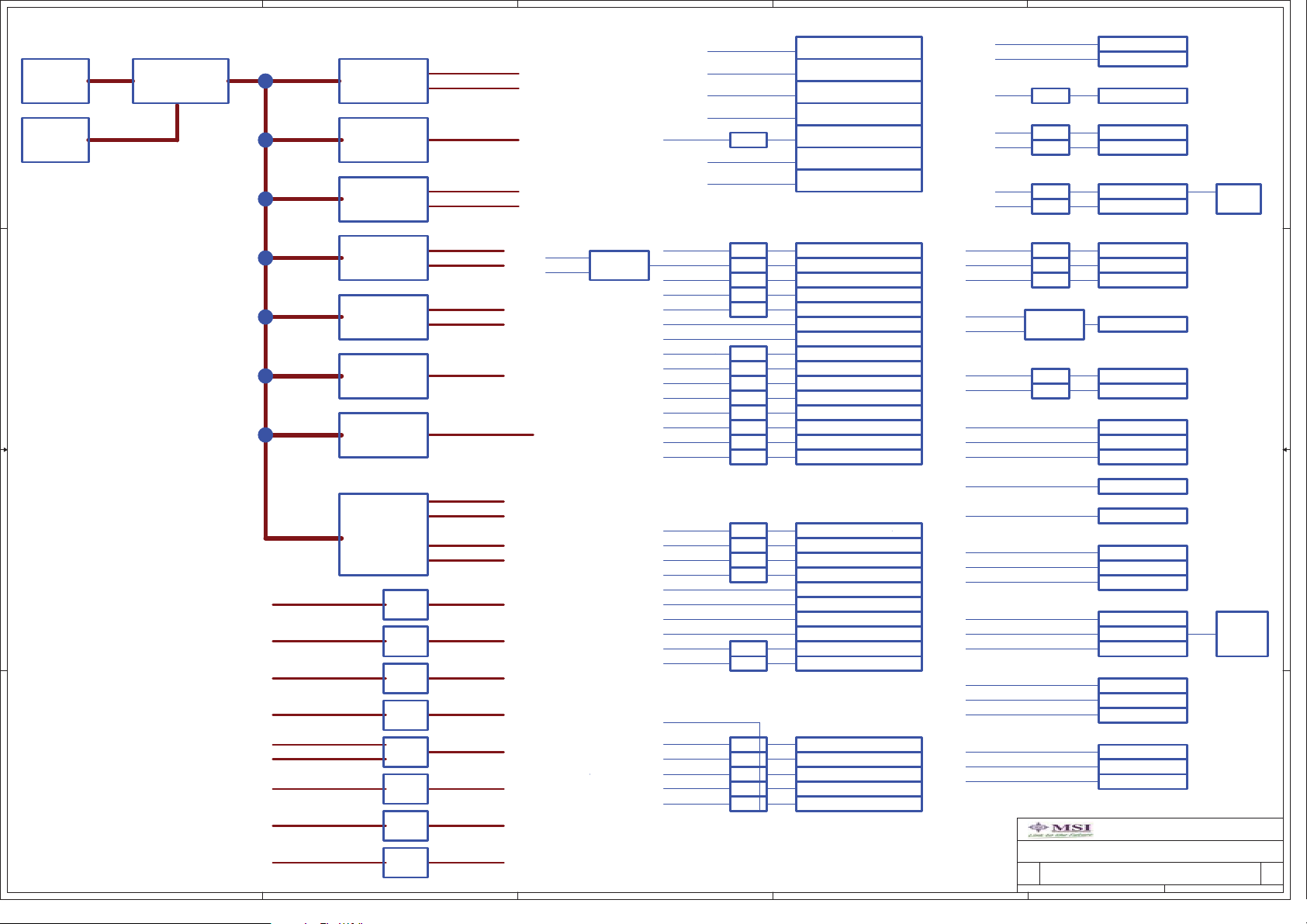

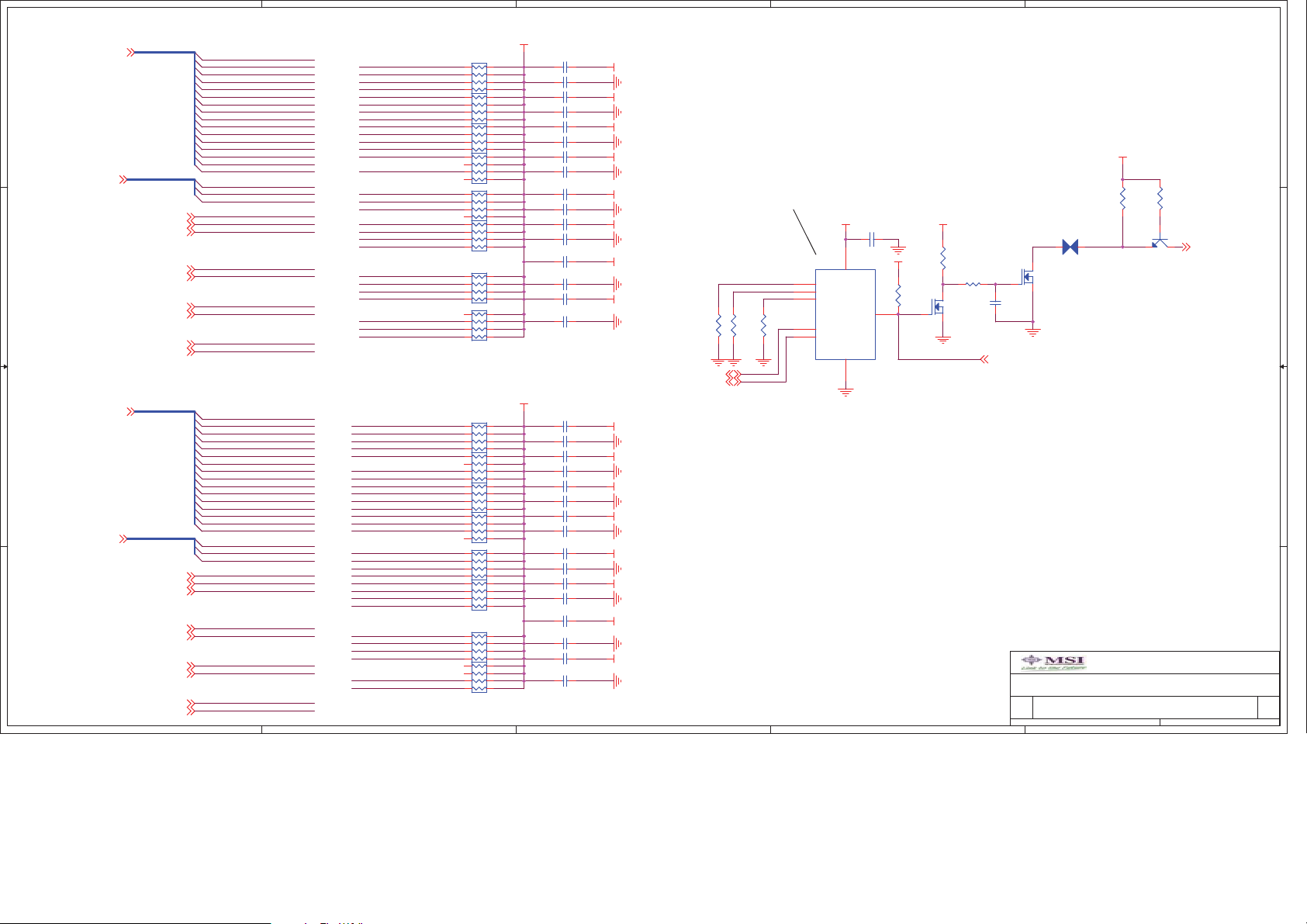

CPU_VDDA_RUN

+1.2V

+VCC_NB

+3.3V

+1.8V

+1.8V

+1.8V

+3.3V

+1.8V

+3.3V

+1.8V

CPU_VDD0_RUN

CPU_VDD1_RUN

CPU_VDDNB_RUN

BEAD

CPU_VDDIO_SUS

CPU_VTT_SUS

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

BATTERY

11.1V

54WHr

D D

AC ADAPTOR

15-16V 90W

BATTERY

CHARGER

MAX1533

+VIN

CPU core

PWM

MAX17009

CPU core

PWM

MAX8792

DDR2 PWM

LDO VTT

MAX8632

+1.2V SW

+1V~+1.2V SW

MAX8717

CPU_VDD0_RUN

CPU_VDD1_RUN

CPU_VDDNB_RUN

CPU_VDDIO_SUS

CPU_VTT_SUS

+VCC_NB

+1.2V

+1.2V

+1.1V

Jumper

RS740/RS780

+1.2V

NB_VDD_MUX

NB_VDD_MUX

NB_VDD_MUX

+1.5V SW

+1.1V SW

C C

MAX8717

+2.5V SW

MAX1714

SW

OZ9956

+1.5V

+1.1V

+2.5VDUAL

VDD_LED_BL_RUN

+1.8V

NB_VDD_MUX

AMD S1G2

VCCA 2.5V

VDD0 CORE

0.375-1.500V

VDD1 CORE

18A

1.375-1.500V

VDDNB CORE

18A

1.375-1.500V

TPDA

VLDT 1.2V TPDA

VDD MEM TPDA

VTT_MEM TPDA

RS780

VDDHTTX 1.2V 0.5A

VDDHTRX 1.1V 0.45A

VDDHT 1.1V 0.6A

VDDPCIE 1.1V 0.7A

VDDA18 1.8V 0.25A

VDDC 1.0V-1.1V 7A

VDDG33 3.3V 0.03A

VDDG18 1.8V 0.005A

VDD18_MEM 1.8V 0.005A

VDD_MEM 1.8V 0.15A

AVDD 3.3V 0.135A

VDDLT18 0.08A

VDDLT33 0.22A

PLLs 1.8V 0.1A

PLLs 1.1/1.2V 0.15A

CPU_VDDIO_SUS

CPU_VTT_SUS

+1.8V

BEAD

+1.2V

BEAD

+3.3V

BEAD

+3.3V

BEAD

+5V

BEAD

+1.2VDUAL

+2.5VDUAL

+3.3VDUAL

+3.3VDUAL

+3.3VALW

+3.3V

+5V

BEAD

BEAD

BEAD

Jumper

RS740/RS780

SW

BEAD

+5V

VDD_LED_BL_RUN

+VIN

+5VDUAL

+3.3VALW

+5V SW

+3V SW

+5V LDO

+3V LDO

B B

+5VDUAL

+3.3VDUAL

+2.5VDUAL

MAX1533

SWITCH

SWITCH

SWITCH

+5VALW

+3.3VDUAL

+5VDUAL

+5V

+3.3V

+2.5V

+1.2V

+1.2V

+1.2V

+1.2V

VDD33_18

+1.2V

+1.2VDUAL

+3.3VDUAL

+3.3VDUAL

+1.2VDUAL

VDD33_18

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

SB SB700

PCIE IO 0.8A

PCIE PVDD 80mA

ATA I/O 0.2A

ATA PLL 0.01A

3.3V OR 1.8v I/O 0.45A

SB CORE 0.6A

1.2V S5 PW 0.22A

3.3V S5 PW 0.01A

USB I/O 0.2A

USB CORE 0.2A

+5VDUAL

+1.5V

+3.3V

+3.3VDUAL

+1.5V

+3.3V

+3.3VDUAL

+1.5V

+3.3V

+2.5VDUAL

+1.2V_S5

+1.2V

A A

CPU_VDDIO_SUS

+3.3V

+3.3VDUAL

5

http://laptop-motherboard-schematic.blogspot.com/

LDO

SWITCH

SWITCH

2.5V LDO

1.2V LDO

4

+1.2V_S5

+1.2VDUAL

+1.8V

CPU_VDDA_RUN

+1.2VDUAL

3

MXM_EN

+1.8V

+2.5V

+3.3V

+5V

+VIN

SW

SW

SW

SW

SW

MXM HE

MXM_VDD_1.8V

MXM_VDD_2.5V

MXM_VDD_3.3V

MXM_VDD_5V

MXM_VDD_MAIN

2

+3.3VDUAL

+1.5V

+3.3V

+3.3VDUAL

Title

POWER DELIVERY CHART

Size Document Number Rev

Custom

Date: Sheet

DDRII SODIMMX2--SYSTEM

VDD MEM 4A

VTT_MEM 0.5A

DDRII SIDE PORT MEMORY

VDD MEM

CLOCK GEN

1.2V 0.2A

3.3V 0.5A

HD CODEC

3.3V CORE 0.3A

5V ANALOG 0.1A

GBIT ENTHENET

1.2V 0.5A

2.5V 0.5A

3.3V 0.5A

SMSC1100--EC

3.3V 0.5A

LCD PANEL

3.3V 1.5A

5V 0.5A

BACK LIGHT

+5V

LED_BL

+VDD_MAIN

USB X2 FR

5VDual

USB X7 FR

5VDual

EXPRESS CARD

1.5V (S0, S1) 0.7A

3.3V (S0, S1) 1.3A

3.3V (S3, S5) 0.3A

MINI PCIE SLOT1

1.5V (S0, S1) 0.7A

3.3V (S0, S1) 1.3A

3.3V (S3, S5) 0.3A

MINI PCIE SLOT2

1.5V (S0, S1) 0.7A

3.3V (S0, S1) 1.3A

3.3V (S3, S5) 0.3A

MINI PCIE SLOT2

1.5V (S0, S1) 0.7A

3.3V (S0, S1) 1.3A

3.3V (S3, S5) 0.3A

MICRO-STAR INT'L CO.,LTD.

MS-13331

1

AUDIO

OP

SIM

0B

of

255Tuesday, December 11, 2007

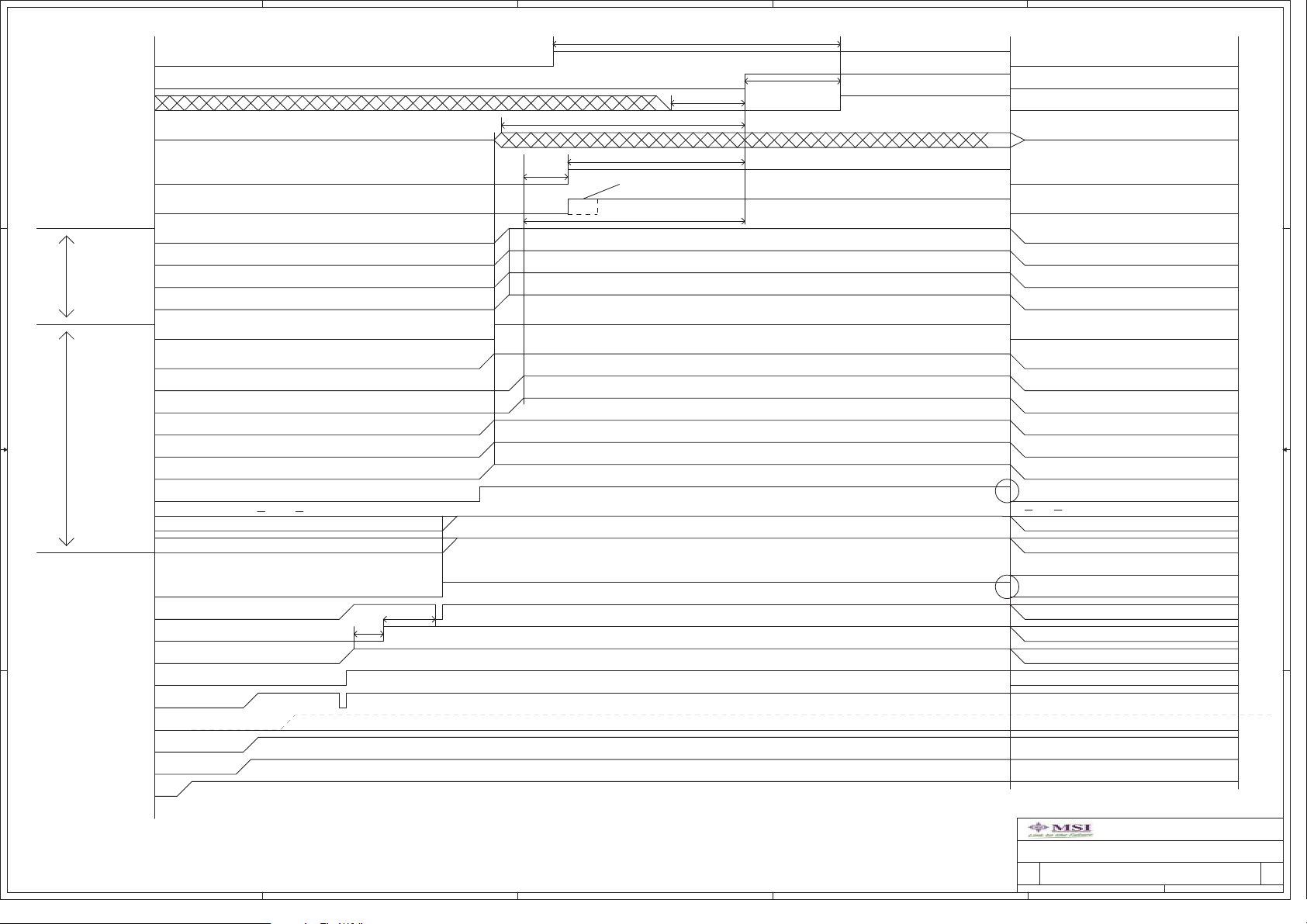

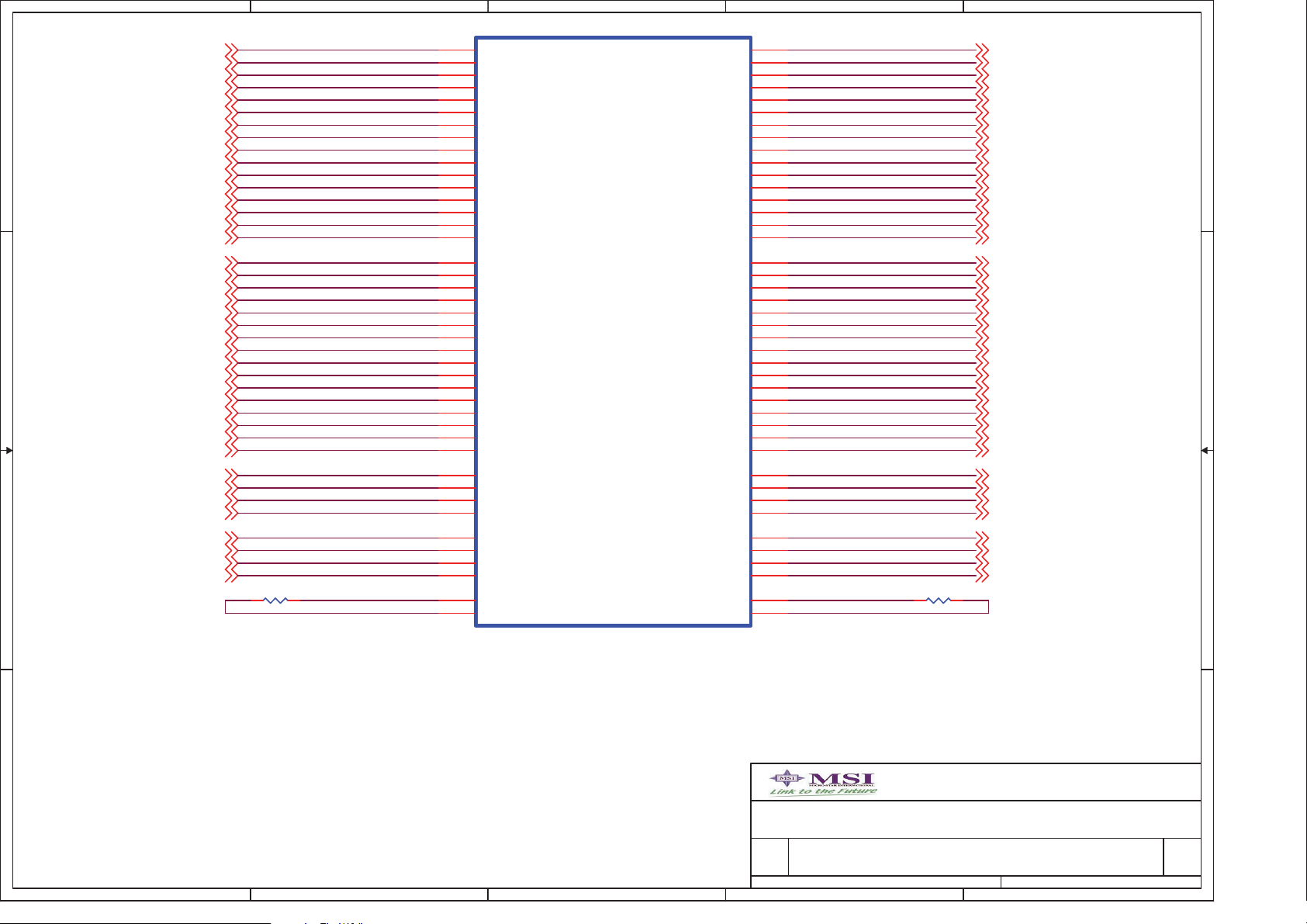

5

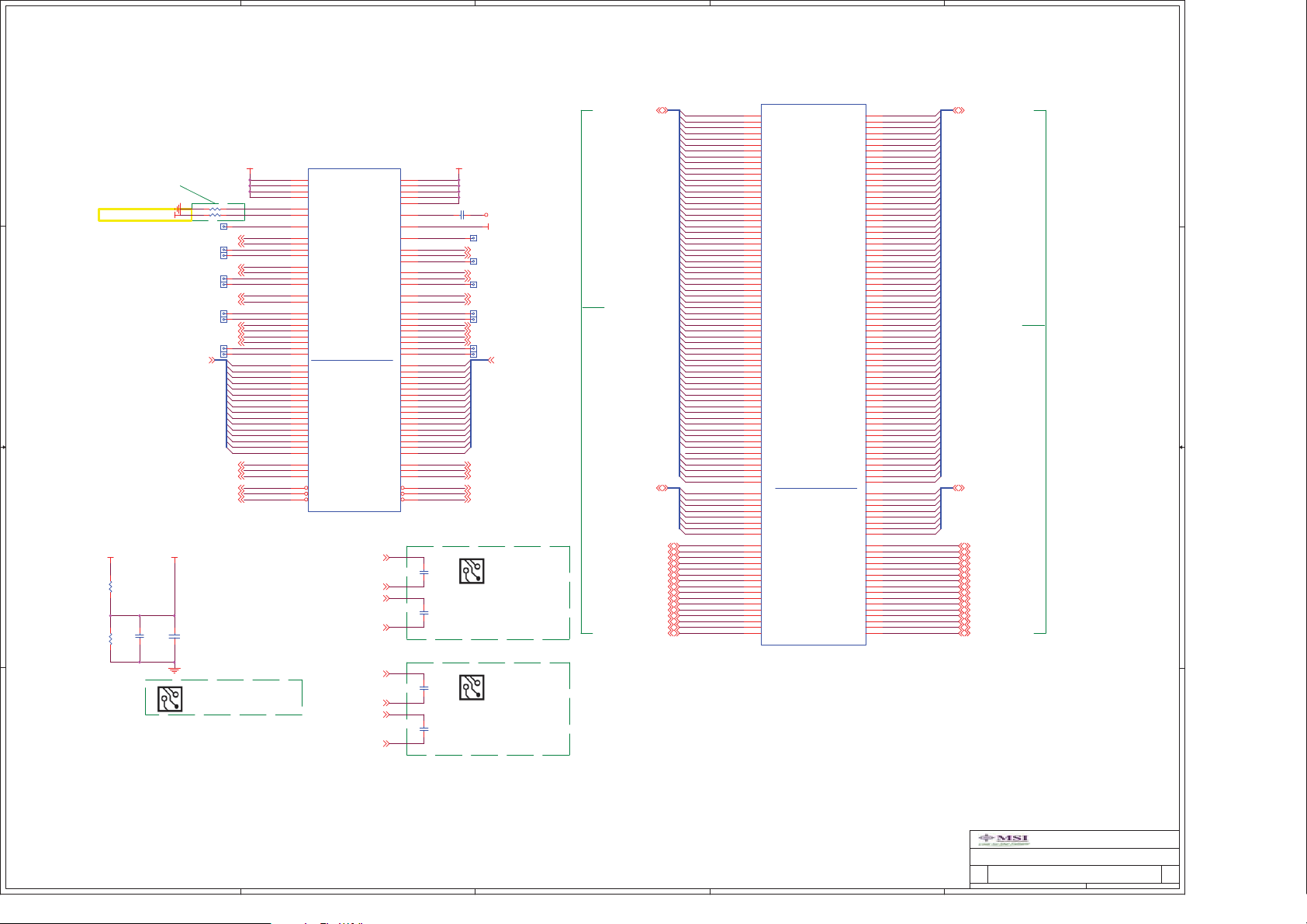

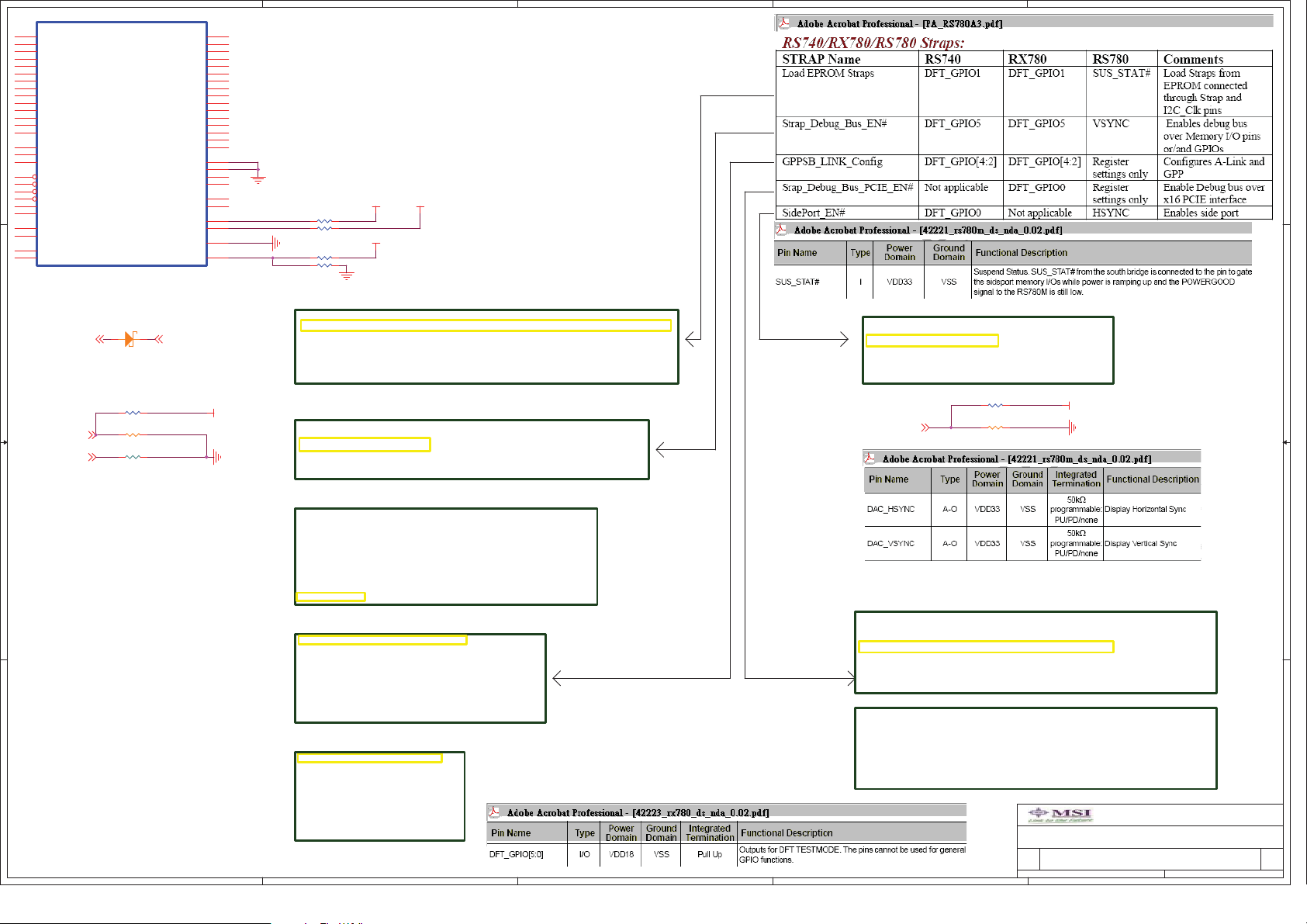

CPU_LDTSTOP#

CPU_PWROK

CPU_RESET#

D D

CPU_CLKIN

Southbridge

PWR_GOOD

Northbridge

POWERGOOD

CPU_VLDT_RUN

CPU_VDDNB_RUN

CPU_VDD1_RUN

CPU_VDD0_RUN

4

15 mS delay

3

>1 mS

Req.

running

48 mS chipset delay

If use Internal Clk Gen

NB_PWRGD is

asserted by SB700

>1 mS

Req.

>1 mS

>1 mS

Req.

Req.

>1 uS

Req.

2

1

GROUP B

C C

B B

A A

CPU_VDDA_PG

CPU_VDDA_RUN

VDD_NB_CORE_RUN

GROUP A

SLP_S3_L

CPU_VTT_SUS

CPU_VDDIO_SUS

SLP_S5#

PWR_BTN#_SB

RSM_RST_L

DUAL RAILS

VDD_DUAL_EN

PWR_BTN#_HW

AC_OK

+3.3VALW/+5VALW

A_VBAT

+1.2V

+1.8V

+5V

+3.3V

+VIN

from S3

Battery inserted/AC IN

power button

locked out

20mS

delay

5VDUAL/3.3VDUAL/2.5VDUAL/1.2VDUAL

Power button pressed

AC not present scenar i o = LO W AC present= high

to S3

stays active if AC present

stays active if AC present

stays active if AC present

stays active if AC present

waiting for power button

Title

POWER SEQUENCE CHART

Size Document Number Rev

Custom

5

http://laptop-motherboard-schematic.blogspot.com/

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-13331

1

0B

of

355Tuesday, December 11, 2007

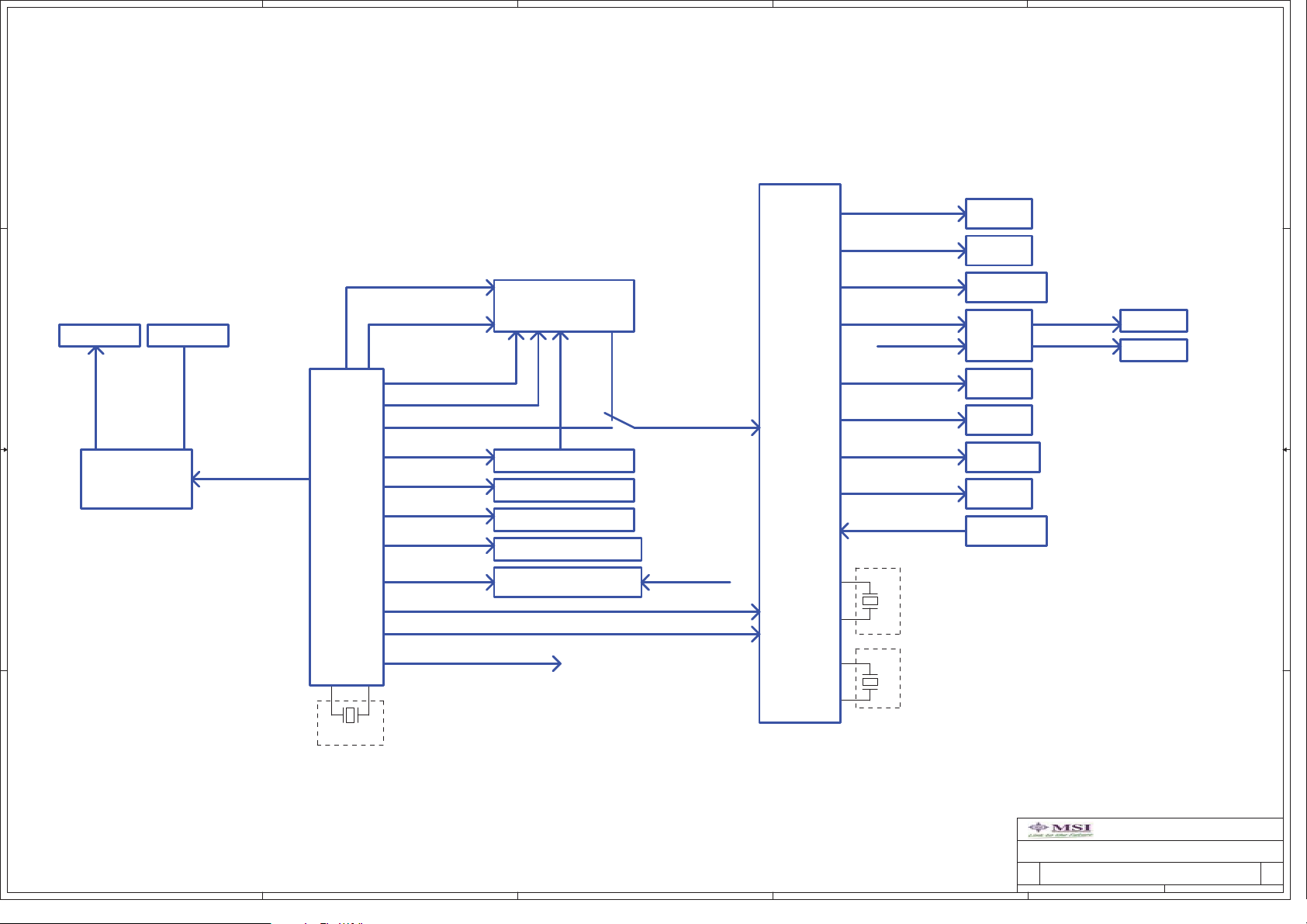

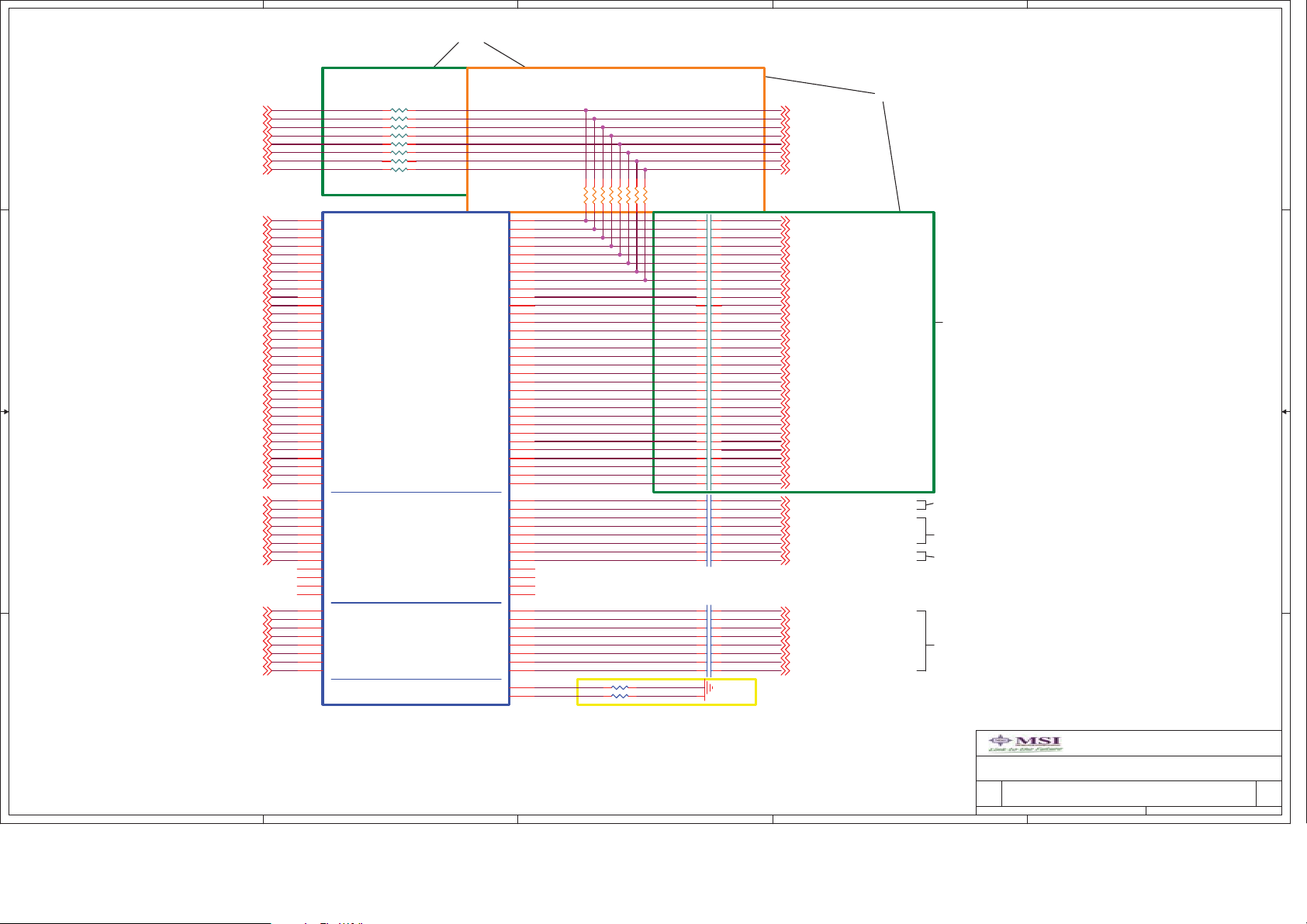

5

D D

4

3

2

1

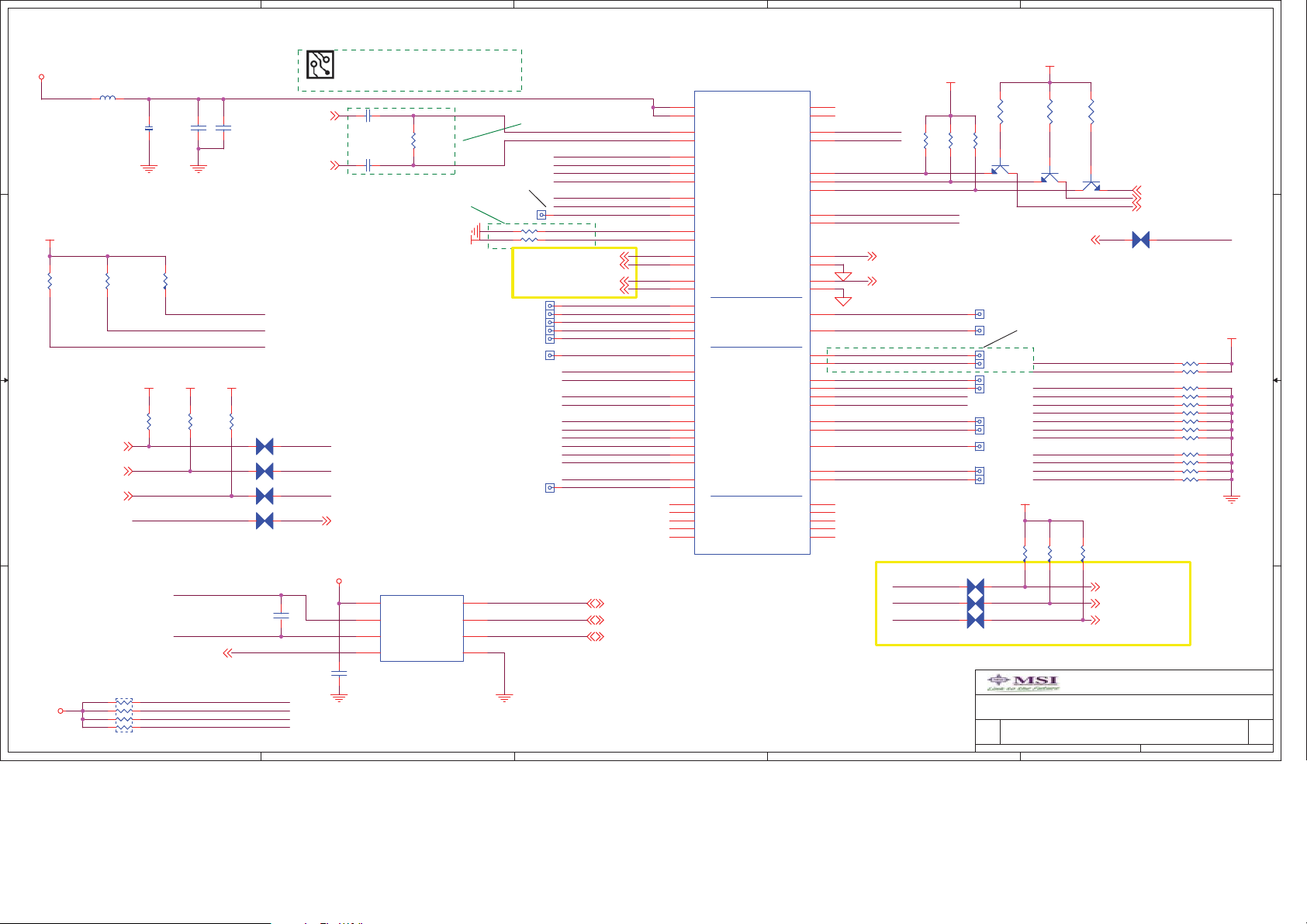

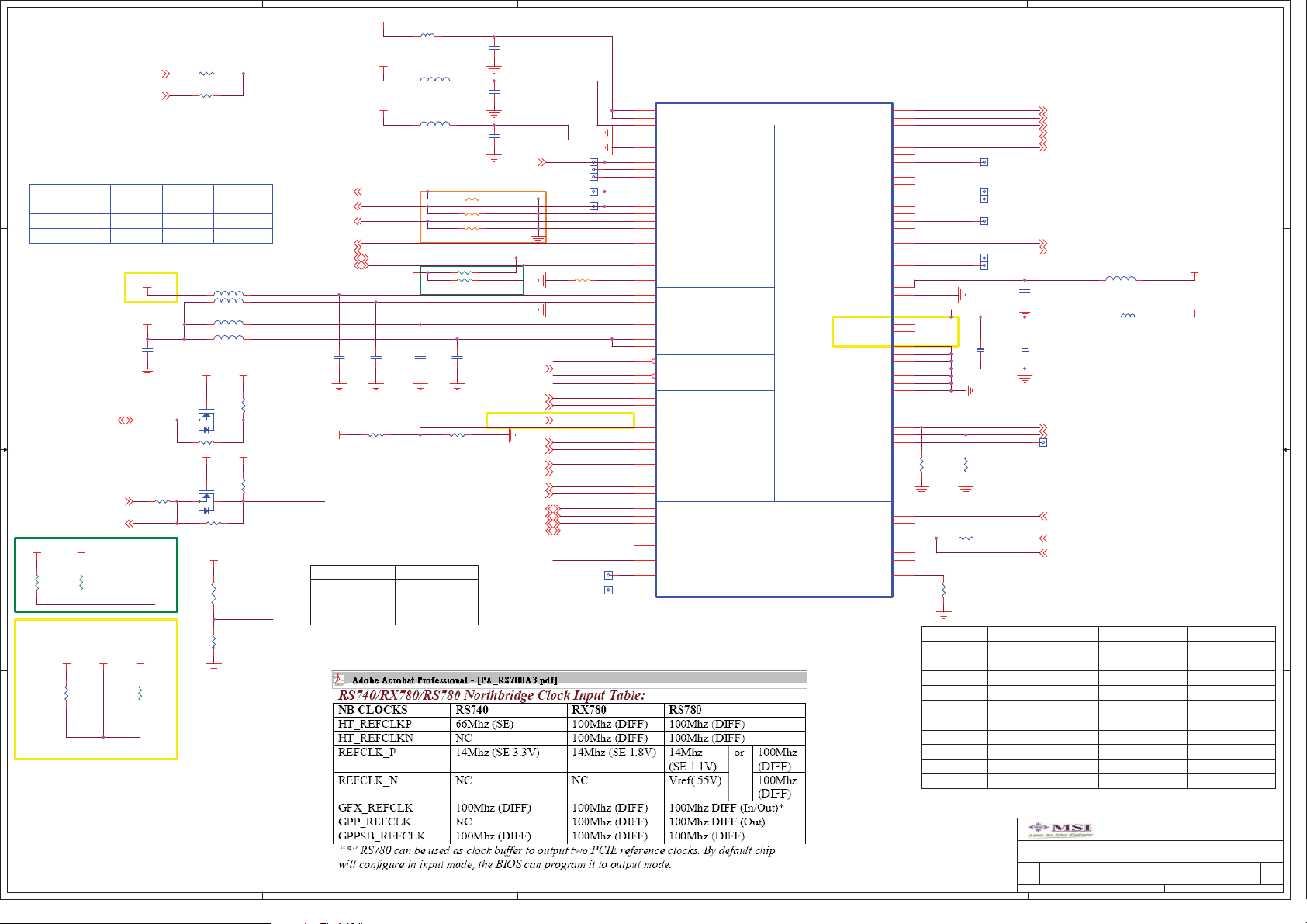

PCI CLK0

33MHZ

PCI CLK1

33MHZ

HTREFCLK

66MHZ

NB-OSC

C C

B B

NEAR SO-DIMM REV SO-DIMM

2 PAIR MEM CLK

ATHLON64 S1 CPU

2 PAIR MEM CLK

1 PAIR CPU CLK

LGA638 PACKAGE

EXTERNAL

CLK GEN.

200MHZ

14.318MHZ

NB PCIE CLK

100MHZ

SB PCIE CLK

100MHZ

SB-OSCIN

14.318MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

PCIE CLK

100MHZ

SUPER IO CLK

48MHZ

ATI NB - RS780M

TVCLKIN

TVCLKIN

PCIE GFX SLOT - 16 LANES

PCIE GPP SLOT 1 - 1 LANE

PCIE GPP SLOT 2 - 1 LANE

PCI EXPRESS CARD - 1 LANE

GIGABIT ETHERNET - 1 LANE

SB-OSCIN

14.318MHZ

SB-OSCIN

14.318MHZ

25MHZ OSC INPUT

PCIE CLK

100MHZ

USB CLK

48MHZ

ATI SB

SB700

AZALIA_BITCLK

PCI CLK2

33MHZ

PCI CLK3

33MHZ

SUPER IO CLK

48MHZ

PCI CLK4

33MHZ

PCI CLK5

33MHZ

PCI CLK6

33MHZ

PCI CLK7

33MHZ

25M Hz

PCI SLOT0

PCI SLOT1

MINI PCI SLOT

SUPER IO

IT8712F

LPC SLOT

LPC BIOS

DEBUG POST

PCI SLOT2

AZALIA CODEC

KB_CLK

MS_CLK

KEYBOARD

MOUSE

32.768K Hz

14.31818MHz

A A

Title

CLOCK DISTRIBUTION

Size Document Number Rev

Custom

5

http://laptop-motherboard-schematic.blogspot.com/

4

3

2

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-13331

1

0B

of

455Tuesday, December 11, 2007

5

4

3

2

1

+VLDT +VLDT

D D

HT_NB_CPU_CAD_H011

HT_NB_CPU_CAD_L011

HT_NB_CPU_CAD_H111

HT_NB_CPU_CAD_L111

HT_NB_CPU_CAD_H211

HT_NB_CPU_CAD_L211

HT_NB_CPU_CAD_H311

HT_NB_CPU_CAD_L311

HT_NB_CPU_CAD_H411

HT_NB_CPU_CAD_L411

HT_NB_CPU_CAD_H511

HT_NB_CPU_CAD_L511

HT_NB_CPU_CAD_H611

HT_NB_CPU_CAD_L611

HT_NB_CPU_CAD_H711

HT_NB_CPU_CAD_L711

C C

HT_NB_CPU_CAD_H811

HT_NB_CPU_CAD_L811

HT_NB_CPU_CAD_H911

HT_NB_CPU_CAD_L911

HT_NB_CPU_CAD_H1011

HT_NB_CPU_CAD_L1011

HT_NB_CPU_CAD_H1111

HT_NB_CPU_CAD_L1111

HT_NB_CPU_CAD_H1211

HT_NB_CPU_CAD_L1211

HT_NB_CPU_CAD_H1311

HT_NB_CPU_CAD_L1311

HT_NB_CPU_CAD_H1411

HT_NB_CPU_CAD_L1411

HT_NB_CPU_CAD_H1511

HT_NB_CPU_CAD_L1511

HT_NB_CPU_CLK_H011

B B

HT_NB_CPU_CLK_L011

HT_NB_CPU_CLK_H111

HT_NB_CPU_CLK_L111

HT_NB_CPU_CTL_H011

HT_NB_CPU_CTL_L011

HT_NB_CPU_CTL_H111

HT_NB_CPU_CTL_L111

U21A

D1

VLDT_A0

D2

VLDT_A1

D3

VLDT_A2

D4

VLDT_A3

E3

L0_CADIN_H0

E2

L0_CADIN_L0

E1

L0_CADIN_H1

F1

L0_CADIN_L1

G3

L0_CADIN_H2

G2

L0_CADIN_L2

G1

L0_CADIN_H3

H1

L0_CADIN_L3

J1

L0_CADIN_H4

K1

L0_CADIN_L4

L3

L0_CADIN_H5

L2

L0_CADIN_L5

L1

L0_CADIN_H6

M1

L0_CADIN_L6

N3

L0_CADIN_H7

N2

L0_CADIN_L7

E5

L0_CADIN_H8

F5

L0_CADIN_L8

F3

L0_CADIN_H9

F4

L0_CADIN_L9

G5

L0_CADIN_H10

H5

L0_CADIN_L10

H3

L0_CADIN_H11

H4

L0_CADIN_L11

K3

L0_CADIN_H12

K4

L0_CADIN_L12

L5

L0_CADIN_H13

M5

L0_CADIN_L13

M3

L0_CADIN_H14

M4

L0_CADIN_L14

N5

L0_CADIN_H15

P5

L0_CADIN_L15

J3

L0_CLKIN_H0

J2

L0_CLKIN_L0

J5

L0_CLKIN_H1

K5

L0_CLKIN_L1

N1

L0_CTLIN_H0

P1

L0_CTLIN_L0

P3

L0_CTLIN_H1

P4

L0_CTLIN_L1

HT LINK

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H15

L0_CADOUT_L15

VLDT_B0

VLDT_B1

VLDT_B2

VLDT_B3

L0_CADOUT_H0

L0_CADOUT_L0

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H9

L0_CADOUT_L9

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

AE2

AE3

AE4

AE5

AD1

AC1

AC2

AC3

AB1

AA1

AA2

AA3

W2

W3

V1

U1

U2

U3

T1

R1

AD4

AD3

AD5

AC5

AB4

AB3

AB5

AA5

Y5

W5

V4

V3

V5

U5

T4

T3

Y1

W1

Y4

Y3

R2

R3

T5

R5

* If VLDT is connected only on one side,

one 4.7uF cap should be added to

the island side

HT_CPU_NB_CAD_H0 11

HT_CPU_NB_CAD_L0 11

HT_CPU_NB_CAD_H1 11

HT_CPU_NB_CAD_L1 11

HT_CPU_NB_CAD_H2 11

HT_CPU_NB_CAD_L2 11

HT_CPU_NB_CAD_H3 11

HT_CPU_NB_CAD_L3 11

HT_CPU_NB_CAD_H4 11

HT_CPU_NB_CAD_L4 11

HT_CPU_NB_CAD_H5 11

HT_CPU_NB_CAD_L5 11

HT_CPU_NB_CAD_H6 11

HT_CPU_NB_CAD_L6 11

HT_CPU_NB_CAD_H7 11

HT_CPU_NB_CAD_L7 11

HT_CPU_NB_CAD_H8 11

HT_CPU_NB_CAD_L8 11

HT_CPU_NB_CAD_H9 11

HT_CPU_NB_CAD_L9 11

HT_CPU_NB_CAD_H10 11

HT_CPU_NB_CAD_L10 11

HT_CPU_NB_CAD_H11 11

HT_CPU_NB_CAD_L11 11

HT_CPU_NB_CAD_H12 11

HT_CPU_NB_CAD_L12 11

HT_CPU_NB_CAD_H13 11

HT_CPU_NB_CAD_L13 11

HT_CPU_NB_CAD_H14 11

HT_CPU_NB_CAD_L14 11

HT_CPU_NB_CAD_H15 11

HT_CPU_NB_CAD_L15 11

HT_CPU_NB_CLK_H0 11

HT_CPU_NB_CLK_L0 11

HT_CPU_NB_CLK_H1 11

HT_CPU_NB_CLK_L1 11

HT_CPU_NB_CTL_H0 11

HT_CPU_NB_CTL_L0 11

HT_CPU_NB_CTL_H1 11

HT_CPU_NB_CTL_L1 11

+VLDT

C194

4.7U6.3X

C0603

LAYOUT: Place bypass cap on topside of board

AMD check list 4-24~4-27

C199

4.7U6.3X

C0603

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

TO OTHER HT POWER PINS

PLACE CLOSE TO VLDT0 POWER PINS

C188

X

0.22U10X

C0402

C197

0.22U10X

C0402

C189

180P50N

C0402

C196

X

180P50N

C0402

SOCKET_638_PIN

BGA638P

N12-6380010-F02

NO STUB

A A

Only for RS740

5

4

3

Title

SOCKET S1G2 HT I/F

Size Document Number Rev

Custom

Date: Sheet

MS-13331

2

MICRO-STAR INT'L CO.,LTD.

of

555Tuesday, December 11, 2007

1

0B

http://laptop-motherboard-schematic.blogspot.com/

A

B

C

D

E

Processor Memory Interface

U21C

4 4

PLACE THEM CLOSE TO

CPU WITHIN 1"

R307 39.2R_1%R0603

MEM_MA_ADD[0..15]9,10

C138

1000P50X

C0402

R308 39.2R_1%R0603

C147

X

0.1U10X

C0402

CPU_VDDIO_SUS

3 3

2 2

CPU_VDDIO_SUS CPU_M_VREF_SUS

VDD_VREF_SUS_CPU

R77

1K_1%

R0402

R76

1K_1%

R0402

CPU_VTT_SUS

M_ZP

M_ZN

MEM_MA_RESET#

TP21

MEM_MA0_ODT09,10

MEM_MA0_ODT19,10

MEM_MA1_ODT0

TP12

MEM_MA1_ODT1

TP18

MEM_MA0_CS#09,10

MEM_MA0_CS#19,10

MEM_MA1_CS#0

MEM_MA1_CS#1

TP14

TP16

MEM_MA_CKE09,10

MEM_MA_CKE19,10

TP19

TP13

MEM_MA_CLK1_P9

MEM_MA_CLK1_N9

MEM_MA_CLK7_P9

MEM_MA_CLK7_N9

MEM_MA_BANK09,10

MEM_MA_BANK19,10

MEM_MA_BANK29,10

MEM_MA_CLK4_P

MEM_MA_CLK4_N

TP15

TP17

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_RAS#9,10

MEM_MA_CAS#9,10

MEM_MA_WE#9,10

LAYOUT:PLACE CLOSE TO CPU

U21B

D10

VTT1

MEM:CMD/CTRL/CLK

C10

VTT2

B10

VTT3

AD10

VTT4

AF10

MEMZP

AE10 Y10

MEMZN VTT_SENSE

H16

RSVD_M1

T19

MA0_ODT0

V22

MA0_ODT1

U21

MA1_ODT0

V19

MA1_ODT1

T20

MA0_CS_L0

U20

MA1_CS_L0

V20

MA1_CS_L1

J22

MA_CKE0

J20

MA_CKE1

N19

MA_CLK_H5

N20

MA_CLK_L5

E16

MA_CLK_H1

F16

MA_CLK_L1

Y16

MA_CLK_H7

AA16

MA_CLK_L7

P19

MA_CLK_H4

P20

MA_CLK_L4

N21

MA_ADD0

M20

MA_ADD1

N22

MA_ADD2

M19

MA_ADD3

M22

MA_ADD4

L20

MA_ADD5

M24

MA_ADD6

L21

MA_ADD7

L19

MA_ADD8

K22

MA_ADD9

R21

MA_ADD10

L22

MA_ADD11

K20

MA_ADD12

V24

MA_ADD13

K24

MA_ADD14

K19

MA_ADD15

R20

MA_BANK0

R23

MA_BANK1

J21

MA_BANK2

R19

MA_RAS_L

T22

MA_CAS_L

T24

MA_WE_L

SOCKET_638_PIN

BGA638P

N12-6380010-F02

MEM_MA_CLK7_P9

MEM_MA_CLK7_N9

MEM_MA_CLK1_P9

MEM_MA_CLK1_N9

AMD check list 2-1

MEM_MB_CLK7_P9

MEM_MB_CLK7_N9

MEM_MB_CLK1_P9

MEM_MB_CLK1_N9

VTT5

VTT6

VTT7

VTT8

VTT9

MEMVREF

RSVD_M2

MB0_ODT0

MB0_ODT1

MB1_ODT0

MB0_CS_L0MA0_CS_L1

MB0_CS_L1

MB1_CS_L0

MB_CKE0

MB_CKE1

MB_CLK_H5

MB_CLK_L5

MB_CLK_H1

MB_CLK_L1

MB_CLK_H7

MB_CLK_L7

MB_CLK_H4

MB_CLK_L4

MB_ADD0

MB_ADD1

MB_ADD2

MB_ADD3

MB_ADD4

MB_ADD5

MB_ADD6

MB_ADD7

MB_ADD8

MB_ADD9

MB_ADD10

MB_ADD11

MB_ADD12

MB_ADD13

MB_ADD14

MB_ADD15

MB_BANK0

MB_BANK1

MB_BANK2

MB_RAS_L

MB_CAS_L

MB_WE_L

W10

AC10

AB10

AA10

A10

SNS_+0.9VTT

W17

MEM_MB_RESET#

B18

W26

W23

MEM_MB1_ODT0

Y26

V26U19

W25

MEM_MB1_CS#0

U22

J25

H26

MEM_MB_CLK5_H

P22

MEM_MB_CLK5_L

R22

A17

A18

AF18

AF17

MEM_MB_CLK4_N

R26

MEM_MB_CLK4_N

R25

MEM_MB_ADD0

P24

MEM_MB_ADD1

N24

MEM_MB_ADD2

P26

MEM_MB_ADD3

N23

MEM_MB_ADD4

N26

MEM_MB_ADD5

L23

MEM_MB_ADD6

N25

MEM_MB_ADD7

L24

MEM_MB_ADD8

M26

MEM_MB_ADD9

K26

MEM_MB_ADD10

T26

MEM_MB_ADD11

L26

MEM_MB_ADD12

L25

MEM_MB_ADD13

W24

MEM_MB_ADD14

J23

MEM_MB_ADD15

J24

R24

U26

J26

U25

U24

U23

CPU_VTT_SUS

C165

X

CPU_VTT_SUS

1000P50X

C0402

TP20

MEM_MB0_ODT0 9,10

MEM_MB0_ODT1 9,10

TP6

MEM_MB0_CS#0 9,10

MEM_MB0_CS#1 9,10

TP9

MEM_MB_CKE0 9,10

MEM_MB_CKE1 9,10

TP11

TP10

MEM_MB_CLK1_P 9

MEM_MB_CLK1_N 9

MEM_MB_CLK7_P 9

MEM_MB_CLK7_N 9

TP8

TP7

MEM_MB_BANK0 9,10

MEM_MB_BANK1 9,10

MEM_MB_BANK2 9,10

MEM_MB_RAS# 9,10

MEM_MB_CAS# 9,10

MEM_MB_WE# 9,10

C150

1.5P50N

C0402

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

C143

1.5P50N

C0402

C140

1.5P50N

C0402

PLACE CLOSE TO PROCESSOR

WITHIN 1.5 INCH

C141

1.5P50N

C0402

CPU_M_VREF_SUS

MEM_MB_ADD[0..15] 9,10

MEM_MB_DATA[0..63]9

To reverse SODIMM

socket

MEM_MB_DM[0..7]9

MEM_MB_DQS0_P9

MEM_MB_DQS0_N9

MEM_MB_DQS1_P9

MEM_MB_DQS1_N9 MEM_MA_DQS1_N 9

MEM_MB_DQS2_P9

MEM_MB_DQS2_N9

MEM_MB_DQS3_P9

MEM_MB_DQS3_N9

MEM_MB_DQS4_P9

MEM_MB_DQS4_N9

MEM_MB_DQS5_P9

MEM_MB_DQS5_N9

MEM_MB_DQS6_P9

MEM_MB_DQS6_N9

MEM_MB_DQS7_P9

MEM_MB_DQS7_N9

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

AA24

AA23

AD24

AE24

AA26

AA25

AD26

AE25

AC22

AD22

AE20

AF20

AF24

AF23

AC20

AD20

AD18

AE18

AC14

AD14

AF19

AC18

AF16

AF15

AF13

AC12

AB11

AE14

AF14

AF11

AD11

AB26

AE22

AC16

AD12

AC25

AC26

AF21

AF22

AE16

AD16

AF12

AE12

C11

A11

A14

B14

G11

E11

D12

A13

A15

A16

A19

A20

C14

D14

C18

D18

D20

A21

D24

C25

B20

C20

B24

C24

E23

E24

G25

G26

C26

D26

G23

G24

Y11

A12

B16

A22

E25

C12

B12

D16

C16

A24

A23

F26

E26

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA24

MB_DATA25

MB_DATA26

MB_DATA27

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

MB_DM0

MB_DM1

MB_DM2

MB_DM3

MB_DM4

MB_DM5

MB_DM6

MB_DM7

MB_DQS_H0

MB_DQS_L0

MB_DQS_H1

MB_DQS_L1

MB_DQS_H2

MB_DQS_L2

MB_DQS_H3

MB_DQS_L3

MB_DQS_H4

MB_DQS_L4

MB_DQS_H5

MB_DQS_L5

MB_DQS_H6

MB_DQS_L6

MB_DQS_H7

MB_DQS_L7

SOCKET_638_PIN

BGA638P

N12-6380010-F02

MEM:DATA

MA_DATA0

MA_DATA1

MA_DATA2

MA_DATA3

MA_DATA4

MA_DATA5

MA_DATA6

MA_DATA7

MA_DATA8

MA_DATA9

MA_DATA10

MA_DATA11

MA_DATA12

MA_DATA13

MA_DATA14

MA_DATA15

MA_DATA16

MA_DATA17

MA_DATA18

MA_DATA19

MA_DATA20

MA_DATA21

MA_DATA22

MA_DATA23

MA_DATA24

MA_DATA25

MA_DATA26

MA_DATA27

MA_DATA28

MA_DATA29

MA_DATA30

MA_DATA31

MA_DATA32

MA_DATA33

MA_DATA34

MA_DATA35

MA_DATA36

MA_DATA37

MA_DATA38

MA_DATA39

MA_DATA40

MA_DATA41

MA_DATA42

MA_DATA43

MA_DATA44

MA_DATA45

MA_DATA46

MA_DATA47

MA_DATA48

MA_DATA49

MA_DATA50

MA_DATA51

MA_DATA52

MA_DATA53

MA_DATA54

MA_DATA55

MA_DATA56

MA_DATA57

MA_DATA58

MA_DATA59

MA_DATA60

MA_DATA61

MA_DATA62

MA_DATA63

MA_DM0

MA_DM1

MA_DM2

MA_DM3

MA_DM4

MA_DM5

MA_DM6

MA_DM7

MA_DQS_H0

MA_DQS_L0

MA_DQS_H1

MA_DQS_L1

MA_DQS_H2

MA_DQS_L2

MA_DQS_H3

MA_DQS_L3

MA_DQS_H4

MA_DQS_L4

MA_DQS_H5

MA_DQS_L5

MA_DQS_H6

MA_DQS_L6

MA_DQS_H7

MA_DQS_L7

G12

F12

H14

G14

H11

H12

C13

E13

H15

E15

E17

H17

E14

F14

C17

G17

G18

C19

D22

E20

E18

F18

B22

C23

F20

F22

H24

J19

E21

E22

H20

H22

Y24

AB24

AB22

AA21

W22

W21

Y22

AA22

Y20

AA20

AA18

AB18

AB21

AD21

AD19

Y18

AD17

W16

W14

Y14

Y17

AB17

AB15

AD15

AB13

AD13

Y12

W11

AB14

AA14

AB12

AA12

E12

C15

E19

F24

AC24

Y19

AB16

Y13

G13

H13

G16

G15

C22

C21

G22

G21

AD23

AC23

AB19

AB20

Y15

W15

W12

W13

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

A_DATA7

MEM_M

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19MEM_MB_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41MEM_MB_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DATA[0..63] 9

To normal SODIMM

MEM_MA_DM[0..7] 9

MEM_MA_DQS0_P 9

MEM_MA_DQS0_N 9

MEM_MA_DQS1_P 9

MEM_MA_DQS2_P 9

MEM_MA_DQS2_N 9

MEM_MA_DQS3_P 9

MEM_MA_DQS3_N 9

MEM_MA_DQS4_P 9

MEM_MA_DQS4_N 9

MEM_MA_DQS5_P 9

MEM_MA_DQS5_N 9

MEM_MA_DQS6_P 9

MEM_MA_DQS6_N 9

MEM_MA_DQS7_P 9

MEM_MA_DQS7_N 9

socket

1 1

Title

SOCKET S1G2 DDR2 MEMORY I/F

Size Document Number Rev

C

A

B

C

D

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-13331

E

655Tuesday, December 11, 2007

0B

of

http://laptop-motherboard-schematic.blogspot.com/

5

4

3

2

1

CPU_VDDA_2.5_RUN

maximun

+VDDA

D D

CPU_VDDIO_SUS

C C

B B

A A

+3VSUS

40 ohm

AMD check list 4-22

L1110L1000m_50L0402

C176

4.7U6.3X

C0603

R103

390R

R0402

CPU_PWRGD17

CPU_LDT_STOP#13,17

CPU_LDT_RST#13,17

R110

390R

R0402

+1.8VRUN +1.8VRUN

R339

300R

R0402

CPU_LDT_REQ#_CPU

RN18 8P4R-10K RN0402_MSI

1

2

3

4

5

6

7

8

5

VDDA 2.5V ==> Max Current 250mA

C173

3300P50X

C0402

R94

1K

R0402

+1.8VRUN

R106

300R

R0402

T_CRIT_CPU#48

T_CRIT_CPU#

SMB_THRMCPU_CLK

SMB_THRMCPU_DATA

CPU_THRM_ALERT-

C175

0.22U10X

C0402

CPU_ALERT

CPU_SIC

CPU_SID

R340

300R

R0402

JNC44 NC_0402_6

JNC27 NC_0402_6

JNC45 NC_0402_6

JNC46 NC_0402_6

Cap close to

thermal

sensor

CPU_THERMDA

C158

2200P50X

CPU_THERMDC

C0402

CPU_CLKP16

CPU_CLKN16

PWRGD

LDT_STOP#

LDT_RST#

C200

0.1U10X

C0402

LAYOUT: ROUTE VDDA TRACE APPROX.

50 mils WIDE (USE 2x25 mil TRACES TO

EXIT BALL FIELD) AND 500 mils LONG.

Keep trace from resisor to CPU within 0.6"

C542 3900P50X

C0603

R318

169R_1%

C543 3900P50X

C0603

If unused, the ALERT_L pin is left unconnected

R0402

keep trace from caps to CPU within 1.2"

place them to CPU within 1.5"

+VLDT

PWM PWM

CPU_LDT_REQ# 13

+3VSUS

U10

D+

DT_CRIT_A#

4

SMBCLKVDD

SMBDATA

ALERT#

GND

2

3

4

LM86CIMMXNOPB_MSOP8-RH

MSOP8_T

Close to CPU socket

81

7

6

5

CPU_VDDA_RUN

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

LDT_RST#

PWRGD

LDT_STOP#

CPU_LDT_REQ#_CPU

CPU_SIC

CPU_SID

CPU_ALERT

TP33

R112 44.2R 1%R0603

R116 44.2R 1%R0603

CPU_VDD0_RUN_FB_H47

CPU_VDD0_RUN_FB_L47

CPU_VDD1_RUN_FB_H47

CPU_VDD1_RUN_FB_L47

CPU_DBRDY

CPU_TMS

TP22

CPU_TCK

TP27

CPU_TRST#

TP26

CPU_TDI

TP25

TP65

CPU_TEST23_TSTUPD

TP31

CPU_TEST18_PLLTEST0

CPU_TEST19_PLLTEST1

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST27_SINGLECHAIN

CPU_TEST9_ANALOGIN

CPU_TEST6_DIECRACKMON

TP32

SMB_THRMCPU_CLK

SMB_THRMCPU_DAT A

F8

F9

A9

A8

B7

A7

F10

C6

AF4

AF5

CPU_HTREF0

CPU_HTREF1

SMB_THRMCPU_CLK 39

SMB_THRMCPU_DATA 39

CPU_THRM_ALERT- 18,39

AE6

R6

P6

F6

E6

Y6

AB6

G10

AA9

AC9

AD9

AF9

AD7

H10

G9

E9

E8

AB8

AF7

AE7

AE8

AC8

AF8

C2

AA6

A3

A5

B3

B5

C1

3

U21D

VDDA1

VDDA2

CLKIN_H

CLKIN_L

RESET_L

PWROK

LDTSTOP_L

LDTREQ_L

SIC

SID

ALERT_L

HT_REF0

HT_REF1

VDD0_FB_H

VDD0_FB_L

VDD1_FB_H

VDD1_FB_L

DBRDY

TMS

TCK

TRST_L

TDI

TEST23

TEST18

TEST19

TEST25_H

TEST25_L

TEST21

TEST20

TEST24

TEST22

TEST12

TEST27

TEST9

TEST6

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

SOCKET_638_PIN

BGA638P

N12-6380010-F02

KEY1

KEY2

SVC

SVD

THERMTRIP_L

PROCHOT_L

MEMHOT_L

THERMDC

THERMDA

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

DBREQ_L

TDO

TEST28_H

TEST28_L

TEST17

TEST16

TEST15

TEST14

TEST7

TEST10

TEST8

TEST29_H

TEST29_L

RSVD10

RSVD9

RSVD8

RSVD7

RSVD6

M11

W18

CPU_SVC_R

A6

CPU_SVD_R

A4

CPU_THERMTRIP#_1.8V

AF6

CPU_PROCHOT#_1.8V

AC7

CPU_MEMHOT#_1.8V

AA8

CPU_THERMDC

W7

CPU_THERMDA

W8

W9

Y9

H6

G6

E10

AE9

J7

H8

D7

E7

F7

C7

C3

K8

C4

C9

C8

H18

H19

AA7

D5

C5

VDDIO 46

CPU_VDDNB_RUN_FB_H 47

CPU_DBREQ#

CPU_TDO

CPU_TEST28_H_PLLCHRZ_P

CPU_TEST28_L_PLLCHRZ_N

CPU_TEST17_BP3

CPU_TEST16_BP2

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST7_ANALOG_T

CPU_TEST10_ANALOGOUT

CPU_TEST8_DIG_T

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST29_L_FBCLKOUT_N

CPU_SVC_R

CPU_SVD_R

PWRGD

2

CPU_VDDIO_SUS

R78

300R

R0402

R0402

R83

R80

300R

300R

R0402

JNC30 NC_0402_6

JNC42 NC_0402_6

JNC29 NC_0402_6

CPU_VDDIO_SUS

R79

10K

R0402

Q11

B

SMBT3904

SOT23EBC_T

E C

VRD_PROCHOT#47

TP23

route as differential

TP64

as short as possible

testpoint under package

TP35

TP30

TP66

TP34

TP37

TP29

TP36

TP28

TP24

CPU_VDDIO_SUS

R102

1K

R0402

Q10

SMBT3904

B

SOT23EBC_T

E C

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST27_SINGLECHAIN

CPU_TEST21_SCANEN

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST19_PLLTEST1

CPU_TEST18_PLLTEST0

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST9_ANALOGIN

CPU_PWRGD Pull up to 1.8VRun

R82

R81

10K

10K

R0402

R0402

Q12

SMBT3904

SOT23EBC_T

B

EC

JNC26 NC_0402_6

R101

R312

X

2.2K

1K

R0402

R0402

CPU_SVC 47

CPU_SVD 47

CPU_PWRGD_SVID_REG 47

CPU_MEMHOT# 10,18

CPU_PROCHOT# 17

CPU_THERMTRIP# 18

CPU_PROCHOT#_1.8V

CPU_VDDIO_SUS

R311 510R R0402

R90 300R R0402

R105 300R R0402

R92 300R R0402

R93 300R R0402

R91 300R R0402

R109 300R R0402

R113 300R R0402

R327 300R R0402

R108 300R R0402

R95 300R R0402

R313 510R R0402

R338 0R R0402

PWM

MICRO-STAR INT'L CO.,LTD.

Title

SOCKET S1G2 CTRL

Size Document Number Rev

Custom

Date: Sheet

MS-13331

of

755Tuesday, December 11, 2007

1

0B

http://laptop-motherboard-schematic.blogspot.com/

5

D D

C C

B B

CPU_VDD0_RUN

CPU_VDDNB_RUN

CPU_VDDIO_SUS

U21E

G4

VDD0_1

H2

VDD0_2

J9

VDD0_3

J11

VDD0_4

J13

VDD0_5

J15

VDD0_6

K6

VDD0_7

K10

VDD0_8

K12

VDD0_9

K14

VDD0_10

L4

VDD0_11

L7

VDD0_12

L9

VDD0_13

L11

VDD0_14

L13

VDD0_15

L15

VDD0_16

M2

VDD0_17

M6

VDD0_18

M8

VDD0_19

M10

VDD0_20

N7

VDD0_21

N9

VDD0_22

N11

VDD0_23

K16

VDDNB_1

M16

VDDNB_2

P16

VDDNB_3

T16

VDDNB_4

V16

VDDNB_5

H25

VDDIO1

J17

VDDIO2

K18

VDDIO3

K21

VDDIO4

K23

VDDIO5

K25

VDDIO6

L17

VDDIO7

M18

VDDIO8

M21

VDDIO9

M23

VDDIO10

M25

VDDIO11

N17 P18

VDDIO12 VDDIO13

SOCKET_638_PIN

BGA638P

N12-6380010-F02

VDD1_1

VDD1_2

VDD1_3

VDD1_4

VDD1_5

VDD1_6

VDD1_7

VDD1_8

VDD1_9

VDD1_10

VDD1_11

VDD1_12

VDD1_13

VDD1_14

VDD1_15

VDD1_16

VDD1_17

VDD1_18

VDD1_19

VDD1_20

VDD1_21

VDD1_22

VDD1_23

VDD1_24

VDD1_25

VDD1_26

VDDIO27

VDDIO26

VDDIO25

VDDIO24

VDDIO23

VDDIO22

VDDIO21

VDDIO20

VDDIO19

VDDIO18

VDDIO17

VDDIO16

VDDIO15

VDDIO14

P8

P10

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

W4

Y2

AC4

AD2

Y25

V25

V23

V21

V18

U17

T25

T23

T21

T18

R17

P25

P23

P21

CPU_VDDIO_SUS

4

U21F

AA4

AA11

AA13

AA15

AA17

AA19

AB2

AB7

AB9

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD6

AD8

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

B4

B6

B8

B9

B11

B13

B15

B17

B19

B21

B23

B25

D6

D8

D9

D11

D13

D15

D17

D19

D21

D23

D25

E4

F2

F11

F13

F15

F17

F19

F21

F23

F25

H7

H9

H21

H23

J4

SOCKET_638_PIN

BGA638P

N12-6380010-F02

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

CPU_VTT_SUS

J6

J8

J10

J12

J14

J16

J18

K2

K7

K9

K11

K13

K15

K17

L6

L8

L10

L12

L14

L16

L18

M7

M9

AC6

M17

N4

N8

N10

N16

N18

P2

P7

P9

P11

P17

R8

R10

R16

R18

T7

T9

T11

T13

T15

T17

U4

U6

U8

U10

U12

U14

U16

U18

V2

V7

V9

V11

V13

V15

V17

W6

Y21

Y23

N6

3

2

1

BOTTOMSIDE DECOUPLING

CPU_VDD0_RUNCPU_VDD1_RUN

C152

22U6.3X

C0805_67

CPU_VDD1_RUN

C157

22U6.3X

C0805_67

CPU_VDDNB_RUN

C149

22U6.3X

C0805_67

C155

22U6.3X

C0805_67

C169

22U6.3X

C0805_67

C144

22U6.3X

C0805_67

C172

22U6.3X

C0805_67

C156

22U6.3X

C0805_67

C185

22U6.3X

C0805_67

C170

22U6.3X

C0805_67

C166

0.22U10X

C0402

C181

0.22U10X

C0402

C154

10N16X

C0402

C187

10N16X

C0402

C151

180P50N

C0402

C153

180P50N

C0402

DECOUPLING BETWEEN PROCESSOR AND DIMMs

PLACE CLOSE TO PROCESSOR AS POSSIBLE

CPU_VDDIO_SUS

C139

C142

4.7U6.3X

C0603

C148

4.7U6.3X

C0603

4.7U6.3X

C0603

CPU_VDDIO_SUS

C146

22U6.3X

C0805_67

C130

C133

4.7U6.3X

0.22U10X

C0603

C0402

AMD Check list 4-1~4-5

C129

22U6.3X

C0805_67

C136

0.22U10X

C0402

C131

0.22U10X

C0402

C137

0.22U10X

C0402

C145

0.22U10X

C0402

C134

0.22U10X

C0402

C520

10N16X

C0402

C525

10N16X

C0402

C515

180P50N

C0402

C517

180P50N

C0402

C12

C82

C38

C81

4.7U6.3X

C0603

4.7U6.3X

C0603

3

4.7U6.3X

PROCESSOR POWER AND GROUND

A A

5

4

C0603

4.7U6.3X

C0603

C4

0.22U10X

C0402

C5

0.22U10X

C0402

C36

0.22U10X

C0402

AMD check list 4-6~4-8,4-11

C67

0.22U10X

C0402

C161

1000P50X

C0402

2

C162

1000P50X

C0402

C128

C163

C167

C168

C164

1000P50X

180P50N

1000P50X

C0402

C0402

Title

SOCKET S1G2 PWR & GND

Size Document Number Rev

Custom

Date: Sheet

MS-13331

180P50N

C0402

C0402

MICRO-STAR INT'L CO.,LTD.

1

180P50N

C0402

C160

180P50N

C0402

855Tuesday, December 11, 2007

of

0B

http://laptop-motherboard-schematic.blogspot.com/

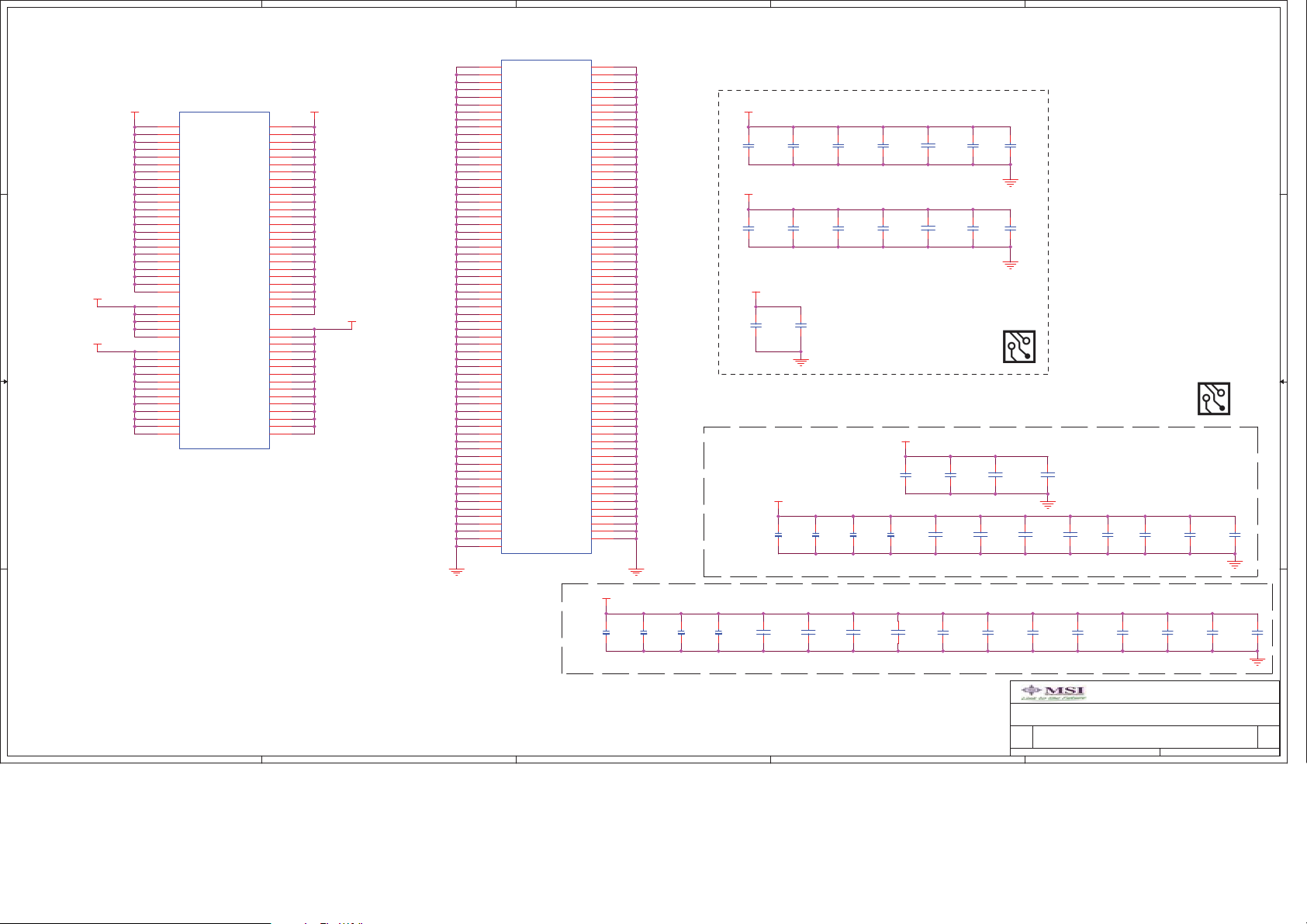

5

CPU_VDDIO_SUS

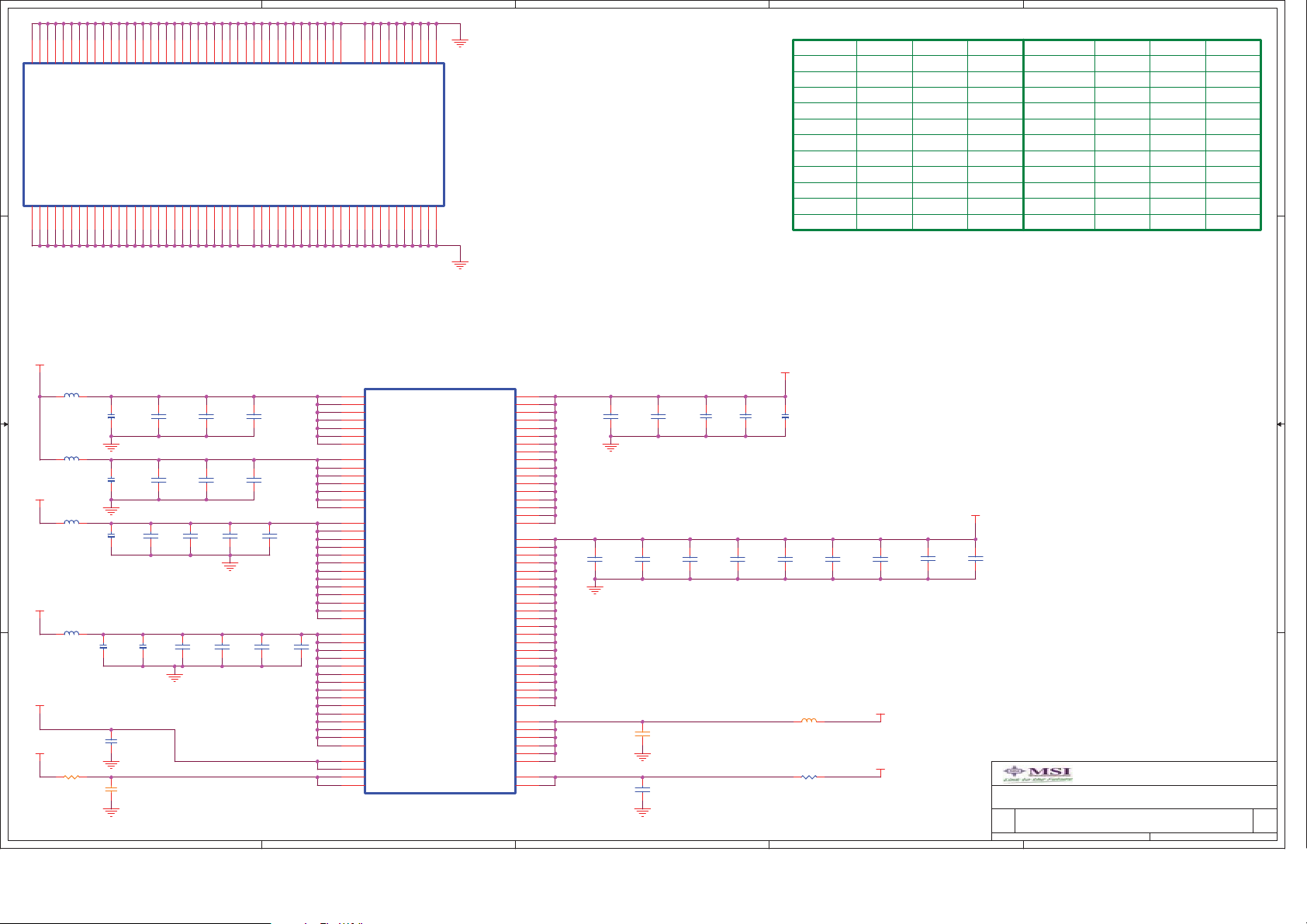

MEM_MA_ADD[0..15]6,10

D D

MEM_MA_BANK[2..0]6,10

MEM_MA_DM[0..7]6

MEM_MA_DQS0_P6

MEM_MA_DQS1_P6

MEM_MA_DQS2_P6

MEM_MA_DQS3_P6

C C

B B

A A

MEM_MA_DQS4_P6

MEM_MA_DQS5_P6

MEM_MA_DQS6_P6

MEM_MA_DQS7_P6

MEM_MA_DQS0_N6

MEM_MA_DQS1_N6

MEM_MA_DQS2_N6

MEM_MA_DQS3_N6

MEM_MA_DQS4_N6

MEM_MA_DQS5_N6

MEM_MA_DQS6_N6

MEM_MA_DQS7_N6

MEM_MA_CLK1_P6

MEM_MA_CLK1_N6

MEM_MA_CLK7_P6

MEM_MA_CLK7_N6

MEM_MA_CKE06,10

MEM_MA_CKE16,10

MEM_MA_RAS#6,10

MEM_MA_CAS#6,10

MEM_MA_WE#6,10

MEM_MA0_CS#06,10

MEM_MA0_CS#16,10

MEM_MA0_ODT06,10

MEM_MA0_ODT16,10

SDATA010,16,18,32

SCLK010,16,18,32

+3VRUN

5

MEM_MA_ADD0

EM_MA_ADD1

M

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_M_VREF_SUS

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10

90

A11

89

A12

116

A13

86

A14/NC

84

A15/NC

107

BA0

106

BA1

85

BA2

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS0

29

DQS1

49

DQS2

68

DQS3

129

DQS4

146

DQS5

167

DQS6

186

DQS7

30

CK0

32

CK0

164

CK1

166

CK1

79

CKE0

80

CKE1

108

RAS

113

CAS

109

WE

110

S0

115

S1

114

ODT0

119

ODT1

198

SA0

200

SA1

195

SDA

197

SCL

199

VDDspd

1

VREF

2

VSS0

3

VSS1

8

VSS2

9

VSS3

12

VSS4

15

VSS5

18

VSS6

21

VSS7

24

VSS8

27

VSS9

28

VSS10

33

VSS11

34

VSS12

39

VSS13

40

VSS14

41

VSS15

42

VSS16

47

VSS17

48

VSS18

53

VSS19

54

VSS20

818287889596103

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

SO-DIMM

VSS26

VSS25

VSS24

VSS23

VSS22

VSS21

DDR2_SODIMM_RVS_H=5.2mm

DDR_SODIMM200P_5_2H

http://laptop-motherboard-schematic.blogspot.com/

4

111

104

112

117

118

VDD6

VDD8

VDD7

VDD9

VDD10

VDD11

NC/TEST

(RVS)

VSS57

VSS58

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

VSS29

VSS28

VSS27

132

128

127

122

1217877727166656059

4

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

J65

MEM_MA_DATA0

5

MEM_MA_DATA1

7

MEM_MA_DATA2

17

MEM_MA_DATA3

19

MEM_MA_DATA4

4

MEM_MA_DATA5

6

MEM_MA_DATA6

14

MEM_MA_DATA7

16

MEM_MA_DATA8MEM_MA_ADD8

23

MEM_MA_DATA9

25

MEM_MA_DATA10

35

MEM_MA_DATA11

37

MEM_MA_DATA12

20

MEM_MA_DATA13

22

MEM_MA_DATA14

36

MEM_MA_DATA15

38

MEM_MA_DATA16

43

MEM_MA_DATA17

45

MEM_MA_DATA18

55

MEM_MA_DATA19

57

MEM_MA_DATA20

44

MEM_MA_DATA21

46

MEM_MA_DATA22

56

MEM_MA_DATA23

58

MEM_MA_DATA24

61

MEM_MA_DATA25

63

MEM_MA_DATA26

73

MEM_MA_DATA27

75

MEM_MA_DATA28

62

MEM_MA_DATA29

64

MEM_MA_DATA30

74

MEM_MA_DATA31

76

MEM_MA_DATA32

123

MEM_MA_DATA33

125

MEM_MA_DATA34

135

MEM_MA_DATA35

137

MEM_MA_DATA36

124

MEM_MA_DATA37

126

MEM_MA_DATA38

134

MEM_MA_DATA39

136

MEM_MA_DATA40

141

MEM_MA_DATA41

143

MEM_MA_DATA42

151

MEM_MA_DATA43

153

MEM_MA_DATA44

140

MEM_MA_DATA45

142

MEM_MA_DATA46

152

MEM_MA_DATA47

154

MEM_MA_DATA48

157

MEM_MA_DATA49

159

MEM_MA_DATA50

173

MEM_MA_DATA51

175

MEM_MA_DATA52

158

MEM_MA_DATA53

160

MEM_MA_DATA54

174

MEM_MA_DATA55

176

MEM_MA_DATA56

179

MEM_MA_DATA57

181

MEM_MA_DATA58

189

MEM_MA_DATA59

191

MEM_MA_DATA60

180

MEM_MA_DATA61

182

MEM_MA_DATA62

192

MEM_MA_DATA63

194

MEMHOTDIMM0#

50

69

83

120

163

201

202

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

TP62

TP63

JNC10

NC_0402_6

MEM_MA_DATA[0..63] 6

MEMHOT_SODIMM# 10

CPU_VDDIO_SUS

LAYOUT: PLACE CLOSE TO DIMMs

3

MEM_MB_ADD[0..15]6,10

MEM_MB_BANK[2..0]6,10

MEM_MB_DM[0..7]6

MEM_VREF_SUS

R25

1K_1%

R0402

R35

1K_1%

R0402

3

C27

0.1U10X

C0402

MEM_MB_DQS0_P6

MEM_MB_DQS1_P6

MEM_MB_DQS2_P6

MEM_MB_DQS3_P6

MEM_MB_DQS4_P6

MEM_MB_DQS5_P6

MEM_MB_DQS6_P6

MEM_MB_DQS7_P6

MEM_MB_DQS0_N6

MEM_MB_DQS1_N6

MEM_MB_DQS2_N6

MEM_MB_DQS3_N6

MEM_MB_DQS4_N6

MEM_MB_DQS5_N6

MEM_MB_DQS6_N6

MEM_MB_DQS7_N6

MEM_MB_CLK1_P6

MEM_MB_CLK1_N6

MEM_MB_CLK7_P6

MEM_MB_CLK7_N6

MEM_MB_CKE06,10

MEM_MB_CKE16,10

MEM_MB_RAS#6,10

MEM_MB_CAS#6,10

MEM_MB_WE#6,10

MEM_MB0_CS#06,10

MEM_MB0_CS#16,10

MEM_MB0_ODT06,10

MEM_MB0_ODT16,10

SDATA010,16,18,32

SCLK010,16,18,32

MEM_M_VREF_SUS

C63

1000P50X

C0402

+3VRUN

+3VRUN

MEM_M_VREF_SUS

CPU_VDDIO_SUS

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

R291 4.7KR0402

2

818287889596103

102

A0

101

A1

VDD0

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14/NC

A15/NC

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

CK0

CK0

CK1

CK1

CKE0

CKE1

RAS

CAS

WE

S0

S1

ODT0

ODT1

SA0

SA1

SDA

SCL

VDDspd

VREF

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VDD1

VSS22

VSS21

100

99

98

97

94

92

93

91

105

90

89

116

86

84

107

106

85

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

30

32

164

166

79

80

108

113

109

110

115

114

119

198

200

195

197

199

1

2

3

8

9

12

15

18

21

24

27

28

33

34

39

40

41

42

47

48

53

54

2

111

104

112

117

118

J64

DQ0

VDD2

VDD3

VSS24

VSS23

VDD4

VDD5

VSS26

VSS25

VDD6

VSS27

DQ1

VDD8

VDD7

VDD9

DQ2

VDD10

VDD11

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NC1

NC2

NC3

NC4

NC/TEST

VSS57

VSS58

VSS56

SO-DIMM(RVS)

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

VSS29

VSS28

DDR2_SODIMM_RVS_H=9.2mm

132

128

127

122

1217877727166656059

DDR_SODIMM200P_9_2H

Title

DDR2 SODIMMS A/B CHANNEL

Size Document Number Rev

Custom

Date: Sheet

MEM_MB_DATA0

5

MEM_MB_DATA1

7

MEM_MB_DATA2

17

MEM_MB_DATA3

19

MEM_MB_DATA4

4

MEM_MB_DATA5

6

MEM_MB_DATA6

14

MEM_MB_DATA7

16

MEM_MB_DATA8

23

MEM_MB_DATA9

25

MEM_MB_DATA10

35

MEM_MB_DATA11

37

MEM_MB_DATA12

20

MEM_MB_DATA13

22

MEM_MB_DATA14

36

MEM_MB_DATA15

38

MEM_MB_DATA16

43

MEM_MB_DATA17

45

MEM_MB_DATA18

55

MEM_MB_DATA19

57

MEM_MB_DATA20

44

MEM_MB_DATA21

46

MEM_MB_DATA22

56

MEM_MB_DATA23

58

MEM_MB_DATA24

61

MEM_MB_DATA25

63

MEM_MB_DATA26

73

MEM_MB_DATA27

75

MEM_MB_DATA28

62

MEM_MB_DATA29

64

MEM_MB_DATA30

74

MEM_MB_DATA31

76

MEM_MB_DATA32

123

MEM_MB_DATA33

125

MEM_MB_DATA34

135

MEM_MB_DATA35

137

MEM_MB_DATA36

124

MEM_MB_DATA37

126

MEM_MB_DATA38

134

MEM_MB_DATA39

136

MEM_MB_DATA40

141

MEM_MB_DATA41

143

MEM_MB_DATA42

151

MEM_MB_DATA43

153

MEM_MB_DATA44

140

MEM_MB_DATA45

142

MEM_MB_DATA46

152

MEM_MB_DATA47

154

MEM_MB_DATA48

157

MEM_MB_DATA49

159

MEM_MB_DATA50

173

MEM_MB_DATA51

175

MEM_MB_DATA52

158

MEM_MB_DATA53

160

MEM_MB_DATA54

174

MEM_MB_DATA55

176

MEM_MB_DATA56

179

MEM_MB_DATA57

181

MEM_MB_DATA58

189

MEM_MB_DATA59

191

MEM_MB_DATA60

180

MEM_MB_DATA61

182

MEM_MB_DATA62

192

MEM_MB_DATA63

194

MEMHOTDIMM1#

50

69

83

120

163

201

202

196

193

190

187

184

183

178

177

172

171

168

165

162

161

156

155

150

149

145

144

139

138

133

MS-13331

TP61

TP60

1

MEM_MB_DATA[0..63] 6

MEMHOT_SODIMM#

JNC41 NC_0402_6

MICRO-STAR INT'L CO.,LTD.

of

955Tuesday, December 11, 2007

1

0B

<

V

i

MEM_MA_ADD[0..15]6,9

D D

MEM_MA_BANK[2..0]6,9

C C

MEM_MB_ADD[0..15]6,9

B B

MEM_MB_BANK[2..0]6,9

A A

5

MEM_MA_ADD[0..15]

MEM_MA_BANK[2..0]

MEM_MA_CAS#6,9

MEM_MA_WE#6,9

MEM_MA_RAS#6,9

MEM_MA0_CS#06,9

MEM_MA0_CS#16,9

MEM_MA0_ODT06,9

MEM_MA0_ODT16,9

MEM_MA_CKE16,9

MEM_MA_CKE06,9

MEM_MB_ADD[0..15]

MEM_MB_BANK[2..0]

MEM_MB_CAS#6,9

MEM_MB_WE#6,9

MEM_MB_RAS#6,9

MEM_MB0_CS#06,9

MEM_MB0_CS#16,9

MEM_MB0_ODT06,9

MEM_MB0_ODT16,9

MEM_MB_CKE16,9

MEM_MB_CKE06,9

5

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CAS#

MEM_MA_WE#

MEM_MA_RAS#

MEM_MA0_CS#0

MEM_MA0_CS#1

MEM_MA0_ODT0

MEM_MA0_ODT1

MEM_MA_CKE1

MEM_MA_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_CAS#

MEM_MB_WE#

MEM_MB_RAS#

MEM_MB0_CS#0

MEM_MB0_CS#1

MEM_MB0_ODT0

MEM_MB0_ODT1

MEM_MB_CKE1

MEM_MB_CKE0

4

8P4R-47R RN0402_MSI

8P4R-47R RN0402_MSI

8P4R-47R RN0402_MSI

8P4R-47R RN0402_MSI

8P4R-47R RN0402_MSI

8P4R-47R RN0402_MSI

MEM_MA_CKE0

MEM_MA_BANK2

MEM_MA_ADD9

MEM_MA_ADD12

MEM_MA_ADD8

MEM_MA_ADD3

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_BANK0

MEM_MA_RAS#

MEM_MA_WE#

MEM_MA_CAS#

MEM_MA0_ODT1

MEM_MA0_CS#1

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_CKE1

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD11

MEM_MA_ADD5

8P4R-47R RN0402_MSI

8P4R-47R RN0402_MSI

MEM_MA_BANK1

MEM_MA_ADD10

MEM_MA_ADD0

MEM_MA_ADD4

MEM_MA0_ODT0

MEM_MA_ADD13

MEM_MA0_CS#0

MEM_MB_CKE0

MEM_MB_BANK2

MEM_MB_ADD9

MEM_MB_ADD12

MEM_MB_ADD8

MEM_MB_ADD1

MEM_MB_ADD3

MEM_MB_ADD10

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_RAS#

B_WE#

MEM_M

MEM_MB0_ODT1

MEM_MB_ADD13

MEM_MB_ADD11

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_CKE1

MEM_MB_ADD6

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD7

MEM_MB0_CS#1

MEM_MB_CAS#

MEM_MB_ADD2

MEM_MB_ADD0

MEM_MB0_CS#0

MEM_MB0_ODT0

4

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

8P4R-47R RN0402_MSI

8P4R-47R RN0402_MSI

8P4R-47R RN0402_MSI

8P4R-47R RN0402_MSI

8P4R-47R RN0402_MSI

8P4R-47R RN0402_MSI

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

1

3

5

7

8P4R-47R RN0402_MSI

1

3

5

7

1

3

5

7

8P4R-47R RN0402_MSI

CPU_VTT_SUS

RN14

2

4

6

8

RN16

2

4

6

8

RN15

2

4

6

8

RN13

2

4

6

8

RN12

2

4

6

8

RN11

2

4

6

8

RN10

2

4

6

8

RN9

2

4

6

8

CPU_VTT_SUS

RN8

2

4

6

8

RN7

2

4

6

8

RN6

2

4

6

8

RN5

2

4

6

8

RN4

2

4

6

8

RN3

2

4

6

8

RN2

2

4

6

8

RN1

2

4

6

8

C37 0.1U10X

C0402

C69 0.1U10X

C0402

C71 0.1U10X

C0402

C68 0.1U10X

C0402

C70 0.1U10X

C0402

C66 0.1U10X

C0402

C65 0.1U10X

C0402

C64 0.1U10X

C0402

C52 0.1U10X

C0402

C54 0.1U10X

C0402

C50 0.1U10X

C0402

C53 0.1U10X

C0402

C48 0.1U10X

C0402

C47 0.1U10X

C0402

C51 0.1U10X

C0402

C49 0.1U10X

C0402

C39 0.1U10X

C0402

C35 0.1U10X

C0402

C34 0.1U10X

C0402

C33 0.1U10X

C0402

C32 0.1U10X

C0402

C31 0.1U10X

C0402

C30 0.1U10X

C0402

C29 0.1U10X

C0402

C11 0.1U10X

C0402

C3 0.1U10X

C0402

C10 0.1U10X

C0402

C9 0.1U10X

C0402

C8 0.1U10X

C0402

C7 0.1U10X

C0402

C2 0.1U10X

C0402

C6 0.1U10X

C0402

3

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

CPU_VDDIO_SUS

3

SMBus Address

48h 7-bit

90h 8-bit

R99

X

10K

R0402

SDATA09,16,18,32

SCLK09,16,18,32

2

D0F-LM75C02-N04

+3VRUN

X

10K

R0402

R119

G

+3VRUN+3VRUN

DS

X

N-2N7002

SOT23SGD_T

C171

X

0.1U10X

C0402

7

A0

6

A1

5

R98

R0402

A2

1

SDA

2

SCL

O.S

GND VCC

U11

X

4 8

LM75

SOIC8

D0F-0100402-N04

3

R97

X

X

10K

10K

R0402

OVERTEMP SENSOR SO-DIMM REGION

Overtemperature Output Assertion Default Setting 80 C

Overtemperature Output Deassertion Default Setting 75 C

2

Q18

X

10K

R0402

X

33R

R0402

X

1U6.3Y

C0402

1

+3VRUN

R100

X

10K

R0402

R118

R114

C179

JNC28 NC_0402_6

DS

Q16

X

N-2N7002

SOT23SGD_T

G

MEMHOT_SODIMM# 9

Title

DDR2 SODIMMS TERMINATIONS

Size Document Number Rev

Custom

Date: Sheet

MICRO-STAR INT'L CO.,LTD.

MS-13331

B

E C

1

R104

X

10K

R0402

Q14

X

SMBT3904

SOT23EBC_T

CPU_MEMHOT# 7,18

10 55Tuesday, December 11, 2007

of

0B

http://laptop-motherboard-schematic.blogspot.com/

5

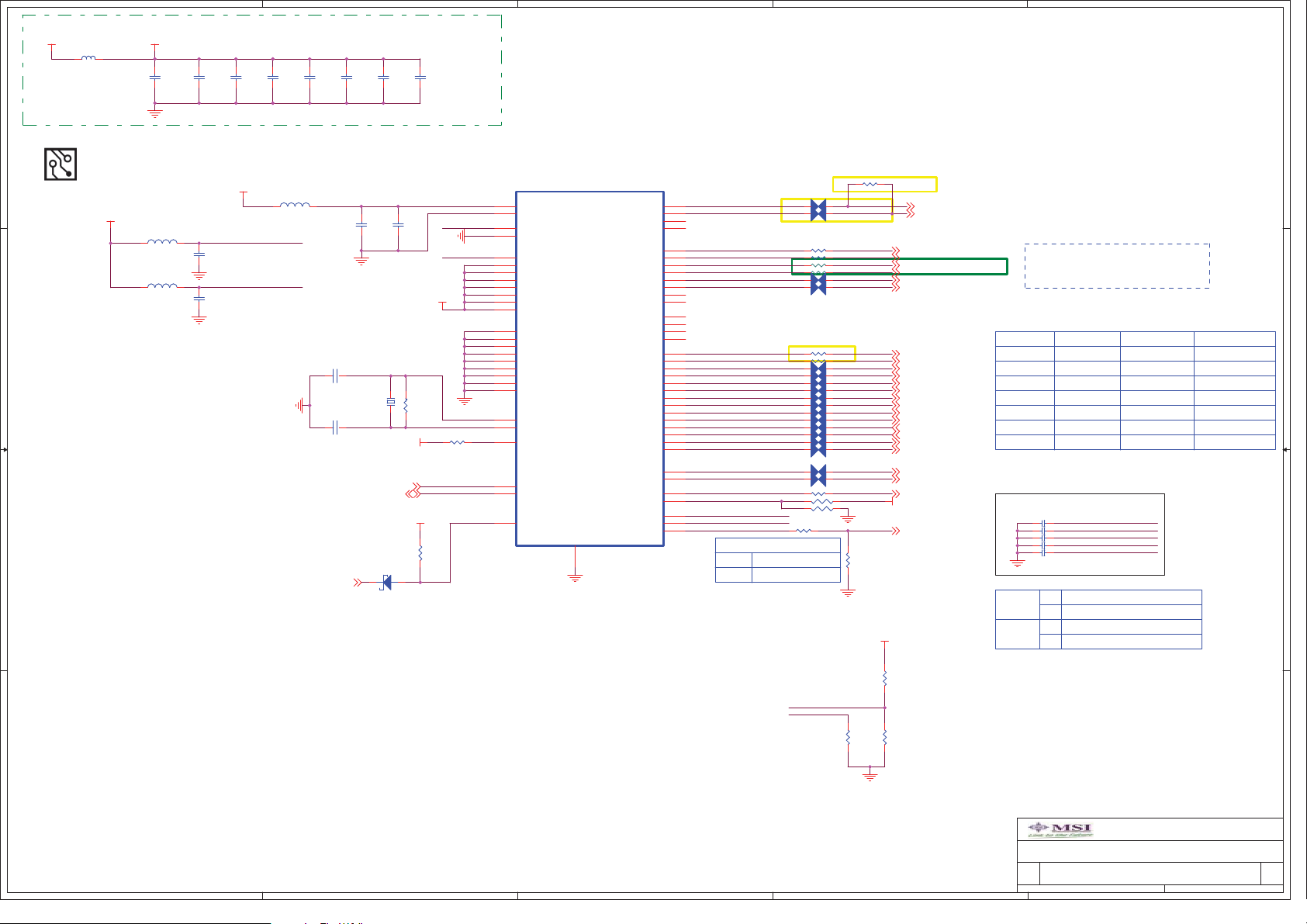

HT_CPU_NB_CAD_H05

HT_CPU_NB_CAD_L05 HT_NB_CPU_CAD_L0 5

HT_CPU_NB_CAD_H15

HT_CPU_NB_CAD_L15

HT_CPU_NB_CAD_H25

HT_CPU_NB_CAD_L25

D D

C C

B B

HT_CPU_NB_CAD_H35

HT_CPU_NB_CAD_L35

HT_CPU_NB_CAD_H45

HT_CPU_NB_CAD_L45

HT_CPU_NB_CAD_H55

HT_CPU_NB_CAD_L55

HT_CPU_NB_CAD_H65

HT_CPU_NB_CAD_H75

HT_CPU_NB_CAD_L75 HT_NB_CPU_CAD_L7 5

HT_CPU_NB_CAD_H85

HT_CPU_NB_CAD_L85

HT_CPU_NB_CAD_H95

HT_CPU_NB_CAD_H105

HT_CPU_NB_CAD_L105

HT_CPU_NB_CAD_H115

HT_CPU_NB_CAD_L115

HT_CPU_NB_CAD_H125

HT_CPU_NB_CAD_L125

HT_CPU_NB_CAD_H135

HT_CPU_NB_CAD_L135

HT_CPU_NB_CAD_H145

HT_CPU_NB_CAD_L145

HT_CPU_NB_CAD_H155

HT_CPU_NB_CAD_L155

HT_CPU_NB_CLK_H05

HT_CPU_NB_CLK_L05

HT_CPU_NB_CLK_H15

HT_CPU_NB_CLK_L15

HT_CPU_NB_CTL_H05

HT_CPU_NB_CTL_L05

HT_CPU_NB_CTL_H15

HT_CPU_NB_CTL_L15

R344 301R 1%

R0402

4

HT_RXCALP

HT_RXCALN

U23A

Y25

HT_RXCAD0P

Y24

HT_RXCAD0N

V22

HT_RXCAD1P

V23

HT_RXCAD1N

V25

HT_RXCAD2P

V24

HT_RXCAD2N

U24

HT_RXCAD3P

U25

HT_RXCAD3N

T25

HT_RXCAD4P

T24

HT_RXCAD4N

P22

HT_RXCAD5P

P23

HT_RXCAD5N

P25

HT_RXCAD6P

P24

HT_RXCAD6N

N24

HT_RXCAD7P

N25

HT_RXCAD7N

AC24

HT_RXCAD8P

AC25

HT_RXCAD8N

AB25

HT_RXCAD9P

AB24

HT_RXCAD9N

AA24

HT_RXCAD10P

AA25

HT_RXCAD10N

Y22

HT_RXCAD11P

Y23

HT_RXCAD11N

W21

HT_RXCAD12P

W20

HT_RXCAD12N

V21

HT_RXCAD13P

V20

HT_RXCAD13N

U20

HT_RXCAD14P

U21

HT_RXCAD14N

U19

HT_RXCAD15P

U18

HT_RXCAD15N

T22

HT_RXCLK0P

T23

HT_RXCLK0N

AB23

HT_RXCLK1P

AA22

HT_RXCLK1N

M22

HT_RXCTL0P

M23

HT_RXCTL0N

R21

HT_RXCTL1P

R20

HT_RXCTL1N

C23

HT_RXCALP

A24

HT_RXCALN

RS780M_A12

FCBGA528_SMDR14_TEST

B01-RS78025-A08

3

PART 1 OF 6

HYPER TRANSPORT CPU

I/F

HT_TXCAD0P

HT_TXCAD0N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD15P

HT_TXCAD15N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCTL0P

HT_TXCTL0N

HT_TXCTL1P

HT_TXCTL1N

HT_TXCALP

HT_TXCALN

D24

D25

E24

E25

F24

F25

F23

F22

H23

H22

J25

J24

K24

K25

K23

K22

F21

G21

G20

H21

J20

J21

J18

K17

L19

J19

M19

L18

M21

P21

P18

M18

H24

H25

L21

L20

M24

M25

P19

R18

B24

B25

2

HT_TXCALP

HT_TXCALN

1

HT_NB_CPU_CAD_H0 5

HT_NB_CPU_CAD_H1 5

HT_NB_CPU_CAD_L1 5

HT_NB_CPU_CAD_H2 5

HT_NB_CPU_CAD_L2 5

HT_NB_CPU_CAD_H3 5

HT_NB_CPU_CAD_L3 5

HT_NB_CPU_CAD_H4 5

HT_NB_CPU_CAD_L4 5

HT_NB_CPU_CAD_H5 5

HT_NB_CPU_CAD_L5 5

HT_NB_CPU_CAD_H6 5

HT_NB_CPU_CAD_L6 5HT_CPU_NB_CAD_L65

HT_NB_CPU_CAD_H7 5

HT_NB_CPU_CAD_H8 5

HT_NB_CPU_CAD_L8 5

HT_NB_CPU_CAD_H9 5

HT_NB_CPU_CAD_L9 5HT_CPU_NB_CAD_L95

HT_NB_CPU_CAD_H10 5

HT_NB_CPU_CAD_L10 5

HT_NB_CPU_CAD_H11 5

HT_NB_CPU_CAD_L11 5

HT_NB_CPU_CAD_H12 5

HT_NB_CPU_CAD_L12 5

HT_NB_CPU_CAD_H13 5

HT_NB_CPU_CAD_L13 5

HT_NB_CPU_CAD_H14 5

HT_NB_CPU_CAD_L14 5

HT_NB_CPU_CAD_H15 5

HT_NB_CPU_CAD_L15 5

HT_NB_CPU_CLK_H0 5

HT_NB_CPU_CLK_L0 5

HT_NB_CPU_CLK_H1 5

HT_NB_CPU_CLK_L1 5

HT_NB_CPU_CTL_H0 5

HT_NB_CPU_CTL_L0 5

HT_NB_CPU_CTL_H1 5

HT_NB_CPU_CTL_L1 5

R342 301R 1%

R0402

A A

Title

MICRO-STAR INT'L CO.,LTD.

RX/RS780 HT LINK I/F

Size Document Number Rev

A

5

4

http://laptop-motherboard-schematic.blogspot.com/

3

Date: Sheet

MS-13331

2

11 55Tuesday, December 11, 2007

of

1

0B

5

4

Close

3

2

1

MS1333 MS1332

D D

C C

B B

A A

M82S_HDMI_TX2P_DPB3N23

M82S_HDMI_TX2M_DPB3P23

M82S_HDMI_TX1P_DPB2N23

M82S_HDMI_TX1M_DPB2P23

M82S_HDMI_TX0P_DPB1N23

M82S_HDMI_TX0M_DPB1P23

M82S_HDMI_TXCP_DPB0N23

M82S_HDMI_TXCM_DPB0P23

U23B

PCIE_NB_RX0P22

PCIE_NB_RX0N22

PCIE_NB_RX1P22

PCIE_NB_RX1N22

PCIE_NB_RX2P22

PCIE_NB_RX2N22

PCIE_NB_RX3P22

PCIE_NB_RX3N22

PCIE_NB_RX4P22

PCIE_NB_RX4N22

PCIE_NB_RX5P22

PCIE_NB_RX5N22

PCIE_NB_RX6P22

PCIE_NB_RX6N22

PCIE_NB_RX7P22

PCIE_NB_RX7N22

PCIE_NB_RX8P22

PCIE_NB_RX8N22

PCIE_NB_RX9P22

PCIE_NB_RX9N22

PCIE_NB_RX10P22

PCIE_NB_RX10N22

PCIE_NB_RX11P22

PCIE_NB_RX11N22

PCIE_NB_RX12P22

PCIE_NB_RX12N22

PCIE_NB_RX13P22

PCIE_NB_RX13N22

PCIE_NB_RX14P22

PCIE_NB_RX14N22

PCIE_NB_RX15P22

PCIE_NB_RX15N22

PCIE_EXPCARD_NB_RXP31

PCIE_EXPCARD_NB_RXN31

PCIE_PE1_NB_RXP38

PCIE_PE1_NB_RXN38

PCIE_PE2_NB_RXP38

PCIE_PE2_NB_RXN38

PCIE_LAN_NB_RXP33

PCIE_LAN_NB_RXN33

PCIE_SB_NB_RX0P17

PCIE_SB_NB_RX0N17

PCIE_SB_NB_RX1P17

PCIE_SB_NB_RX1N17

PCIE_SB_NB_RX2P17

PCIE_SB_NB_RX2N17

PCIE_SB_NB_RX3P17

PCIE_SB_NB_RX3N17

D4

GFX_RX0P

C4

GFX_RX0N

A3

GFX_RX1P

B3

GFX_RX1N

C2

GFX_RX2P

C1

GFX_RX2N

E5

GFX_RX3P

F5

GFX_RX3N

G5

GFX_RX4P

G6

GFX_RX4N

H5

GFX_RX5P

H6

GFX_RX5N

J6

GFX_RX6P

J5

GFX_RX6N

J7

GFX_RX7P

J8

GFX_RX7N

L5

GFX_RX8P

L6

GFX_RX8N

M8

GFX_RX9P

L8

GFX_RX9N

P7

GFX_RX10P

M7

GFX_RX10N

P5

GFX_RX11P

M5

GFX_RX11N

R8

GFX_RX12P

P8

GFX_RX12N

R6

GFX_RX13P

R5

GFX_RX13N

P4

GFX_RX14P

P3

GFX_RX14N

T4

GFX_RX15P

T3

GFX_RX15N

AE3

GPP_RX0P

AD4

GPP_RX0N

AE2

GPP_RX1P

AD3

GPP_RX1N

AD1

GPP_RX2P

AD2

GPP_RX2N

V5

GPP_RX3P

W6

GPP_RX3N

U5

GPP_RX4P

U6

GPP_RX4N

U8

GPP_RX5P

U7

GPP_RX5N

AA8

SB_RX0P

Y8

SB_RX0N

AA7

SB_RX1P

Y7

SB_RX1N

AA5

SB_RX2P

AA6

SB_RX2N

W5

SB_RX3P

Y5

SB_RX3N

RS780M_A12

FCBGA528_SMDR14_TEST

B01-RS78025-A08

R414 0R R0402

R412 0R R0402

R418 0R R0402

R416 0R R0402

R421 0R R0402

R425 0R R0402

R431 0R R0402

R428 0R R0402

PART 2 OF 6

PCIE I/F

GFX

PCIE I/F GPP

PCIE I/F SB

PCE_CALRP(PCE_BCALRP)

PCE_CALRN(PCE_BCALRN)

R413

X

0R

R0402

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

GPP_TX4P

GPP_TX4N

GPP_TX5P

GPP_TX5N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

SB_TX2P

SB_TX2N

SB_TX3P

SB_TX3N

R411

X

0R

R0402

A5

B5

A4

B4

C3

B2

D1

D2

E2

E1

F4

F3

F1

F2

H4

H3

H1

H2

J2

J1

K4

K3

K1

K2

M4

M3

M1

M2

N2

N1

P1

P2

AC1

AC2

AB4

AB3

AA2

AA1

Y1

Y2

Y4

Y3

V1

V2