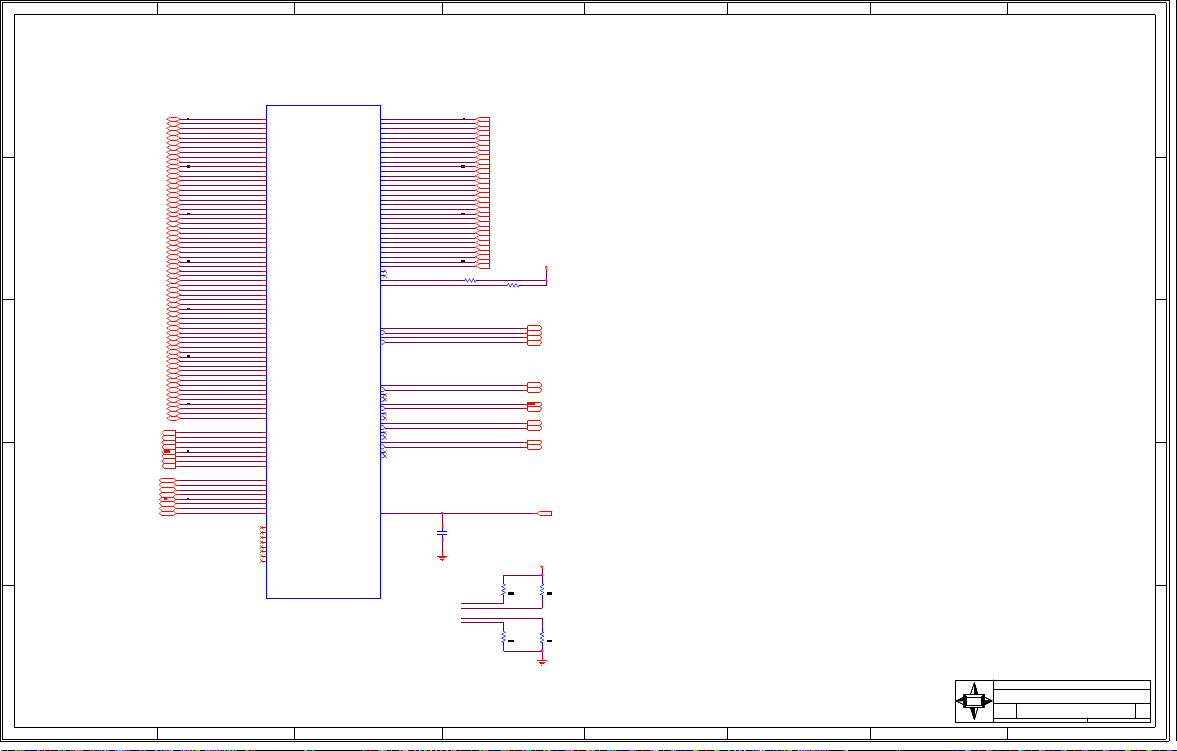

MSI GeForce GTX 960 GAMING 2G Schematics REV1.0

A B

D

HGFEC

PG301 A02

1

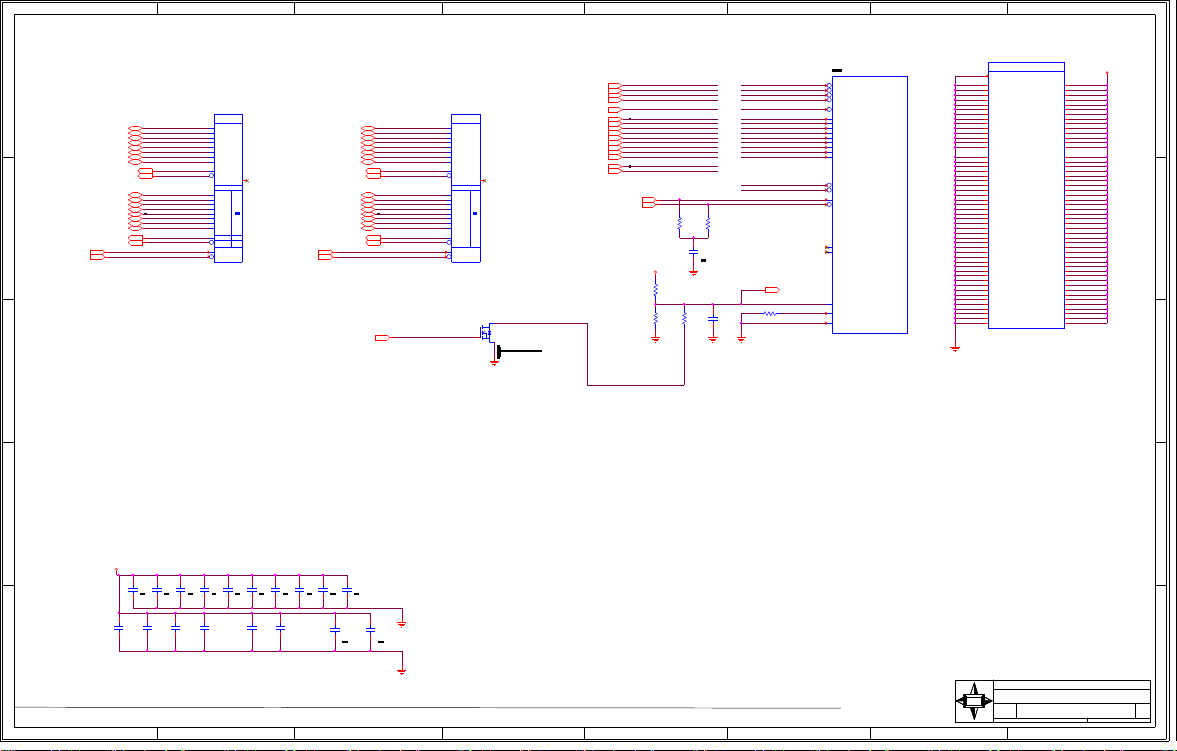

Comanche 192b GDDR5, <150W, 2-way SLI

Tall DVI-I + DP + DP + DP/HDMI + DP

TABLE OF CONTENTS

Page

Description

Page

1

Table of Contents

2

Block Diagram

3

PCI Express

4

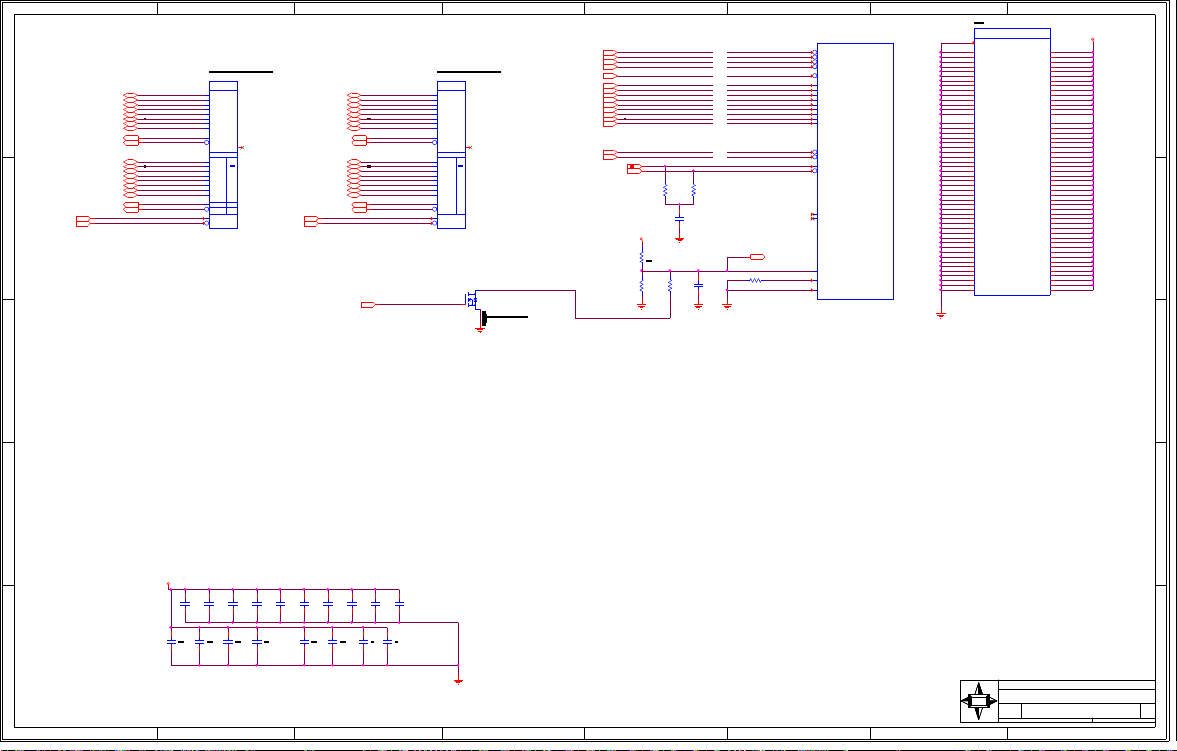

MEMORY: GPU Partition A/B

5

2

3

4

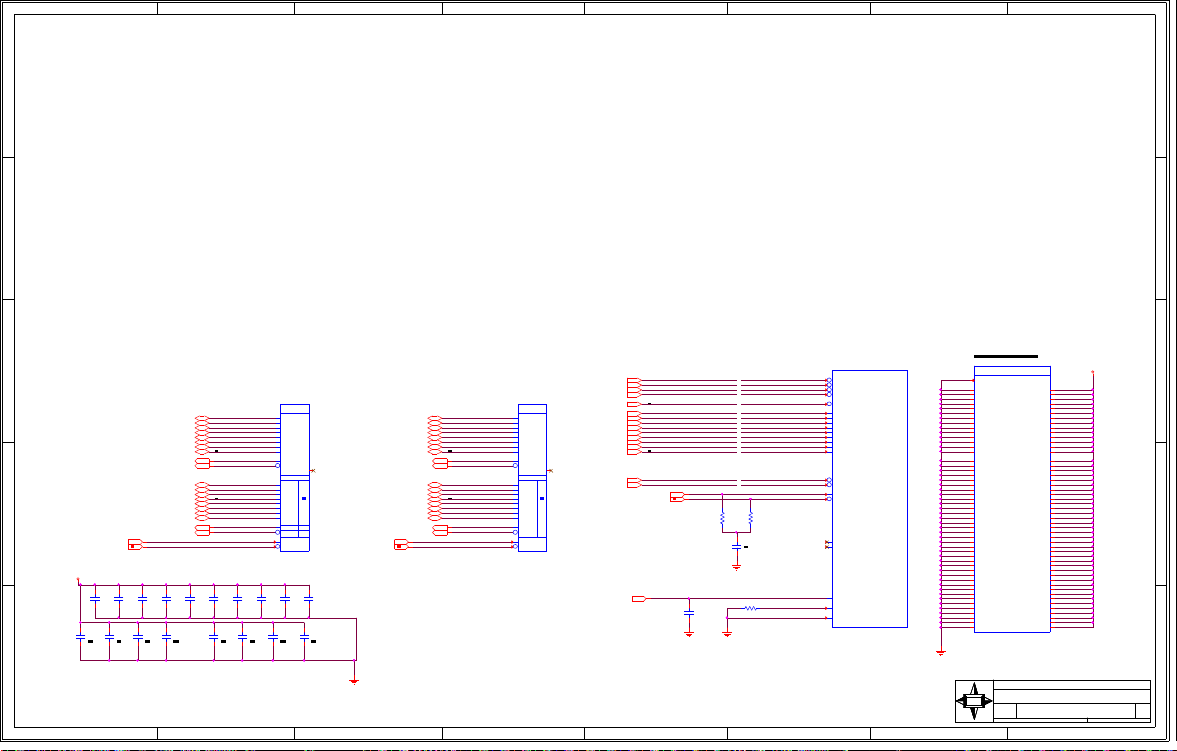

MEMORY: FBA[31:0]

6

MEMORY: FBA[63:32]

7

MEMORY: FBB[31:0]

8

MEMORY: FBB[63:32]

9

MEMORY: GPU Partition C

10

MEMORY: FBC[31:0]

11

MEMORY: FBC[63:32]

12

GPU PWR and GND

13

GPU Decoupling

14

DACA Interface

15

IFPAB DVI-I-DL

16

IFPEF with IFPE DP

17

IFPF DP

18

IFPC HDMI/DP

19

IFPD DP

20

MIOA

21

MISC1: Fan, Thermal, JTAG, GPIO

22

MISC2: ROM, XTAL, Straps

23

PS: 5V, PEX_VDD, VID_PLL

24

PS: FBVDD/Q

25

PS: NVVDD Controller OVR4 option

Description

PS: NVVDD Phase 1,2

26

PS: NVVDD Phase 3,4

27

[RESERVED]

28

29

PS: NVVDD OVR2+1 option

PS: Inputs, Filtering, and Monitoring

30

31

PS: Sequence and Shutdown

32

LEDs

PS: IOVDD Regulator

33

34

MECH: Bracket/Thermal

Note:

1 page:4-11 修改net name,加<>

2 page:8 增加跨頁符號

3 page:15 修改DVI footprint

4 page:16/17/19 修改DP footprint

5 page:18 修改HDMI footprint

6 page:26/27 修改output chike footprint

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICAT IONS, REFERENCE SP ECIFICATIONS, REFERENCE BOARDS, FILES, DRAWI NGS, DIAGNOSTICS, LIST S AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEP ARATEL Y, 'MATERIALS') ARE BE ING PROVIDED 'AS IS'. THE MAT ERIALS MAY

CONTAINK NOWNA ND UNKNOWN VIOLATIONS OR DEVIA TIONS OFI NDUSTRY ST ANDARDS AND SP ECIFICATIONS. NVIDIA MAKESNO WARRA NTIES, E XPRESSE D, IMPLIED, STAT UTORY OR OTHERWISE WITH RESPECT TOT HE MATERIALS OROTHERWIS E, AND EXP RESSLY DISCLA IMS ALL

IMPLIED WARRANTIES INCLUDING, WIT HOUT LIMITATION, T HE WARRANT IES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNE SS FOR A PARTICULA R PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, T RADE PRACT ICE, OR INDUSTRY ST ANDARDS.

A B D F

ASSEMBLY

PAGE DETAIL

BASE LEVEL GENE RIC SCHEMATIC ONLY

Table of Contents

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

MS-V320

MS-V320

MSI

MSI

MSI

EC

G

MS-V320

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

01_Table of Cont ents

01_Table of Cont ents

01_Table of Cont ents

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

Sheet ofDate:

1 34

Sheet ofDate:

1 34

Sheet ofDate:

1 34

5

10

10

10

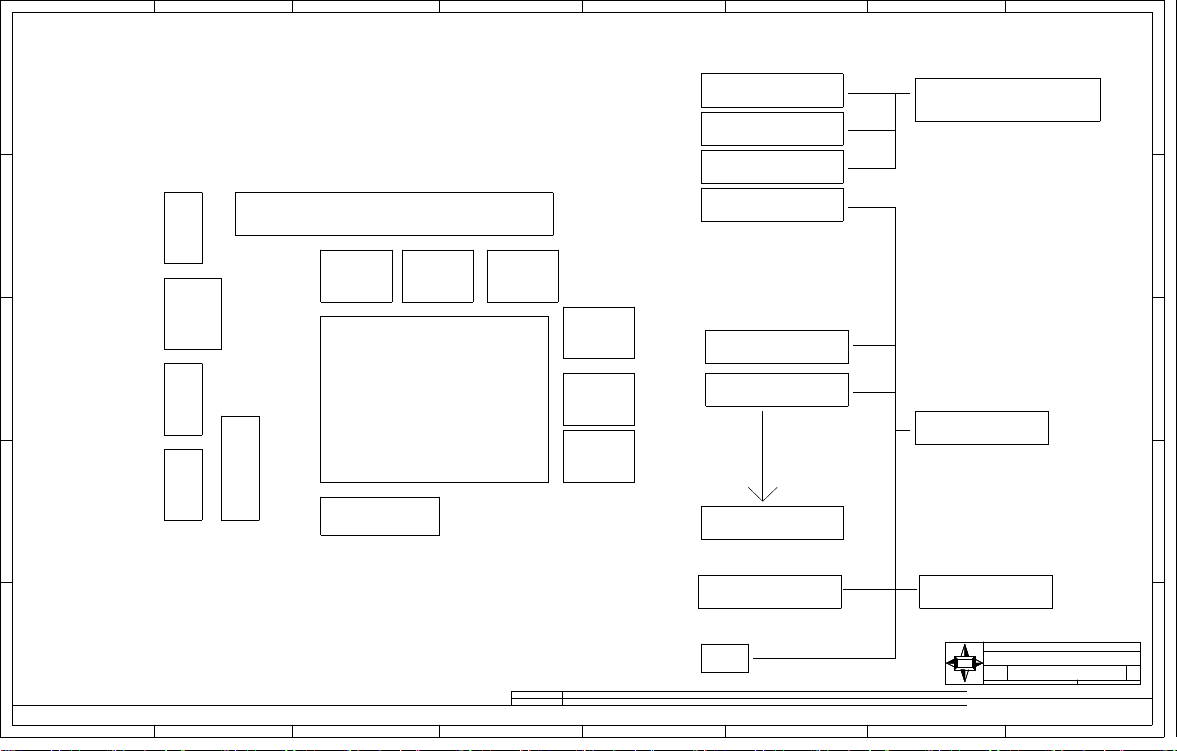

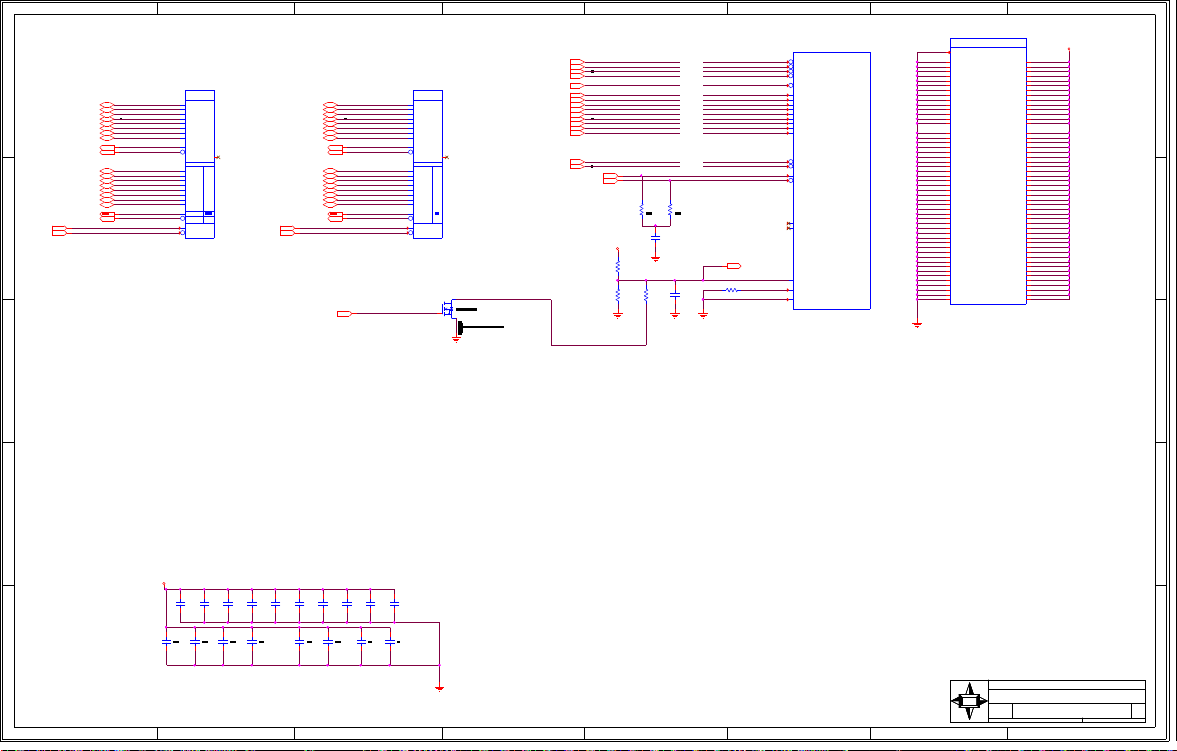

Block Diagram

A B C D E F G H

1

SLI/

2

3

DP

HDMI/

QD:FRAME LOCK

DP

C

MEM MEM MEM B

LO

C

HI

DP

DVI-I

DP

4

5

ALL NVIDIA DESIGN SPECIFICAT IONS, REFERENCE SP ECIFICATIONS, REFERENCE BOARDS, FILES, DRAWI NGS, DIAGNOSTICS, LIST S AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEP ARATEL Y, 'MATERIALS') ARE BE ING PROVIDED 'AS IS'. THE MAT ERIALS MAY

CONTAINK NOWNA ND UNKNOWN VIOLATIONS OR DEVIA TIONS OFI NDUSTRY ST ANDARDS AND SP ECIFICATIONS. NVIDIA MAKESNO WARRA NTIES, E XPRESSE D, IMPLIED, STAT UTORY OR OTHERWISE WITH RESPECT TOT HE MATERIALS OROTHERWIS E, AND EXP RESSLY DISCLA IMS ALL

IMPLIED WARRANTIES INCLUDING, WIT HOUT LIMITATION, T HE WARRANT IES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNE SS FOR A PARTICULA R PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, T RADE PRACT ICE, OR INDUSTRY ST ANDARDS.

QD:STEREO

QUADRO OPTIONS SHOWN IN YELLOW

and prefix "QD:"

C E

LO

ASSEMBLY

PAGE DETAIL

B

MEM

HI

A

MEM

LO

MEM A

HI

BASE LEVEL GENE RIC SCHEMATIC ONLY

Block Diagram

Power Supply

NVVDD-PH4

Power Supply

NVVDD-PH3

Power Supply

NVVDD-PH2

Power Supply

NVVDD-PH1

Power Supply

5V Linear

Power Supply

FBVDD/FBVDD Q

PEX_VDD

LDO

VID_PLL

LDO

Fan

EXT_12V 2x3 PWR 1

1

(NORTH)

2

3

PEX_12V Finger

4

PEX_3V3 Finger

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

MS-V320

MS-V320

MSI

MSI

MSI

FDBA

G

MS-V320

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

02_Block Diagram

02_Block Diagram

02_Block Diagram

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

2 34

2 34

2 34

5

10

10

10

A B C D E F G H

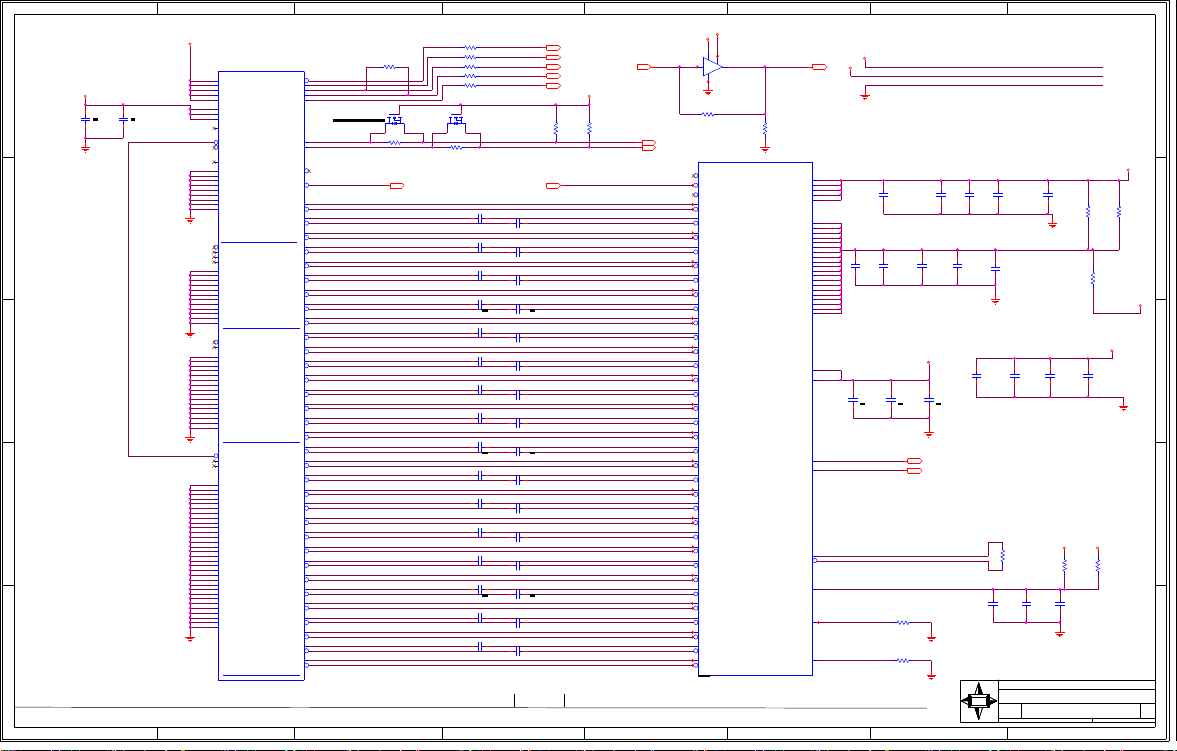

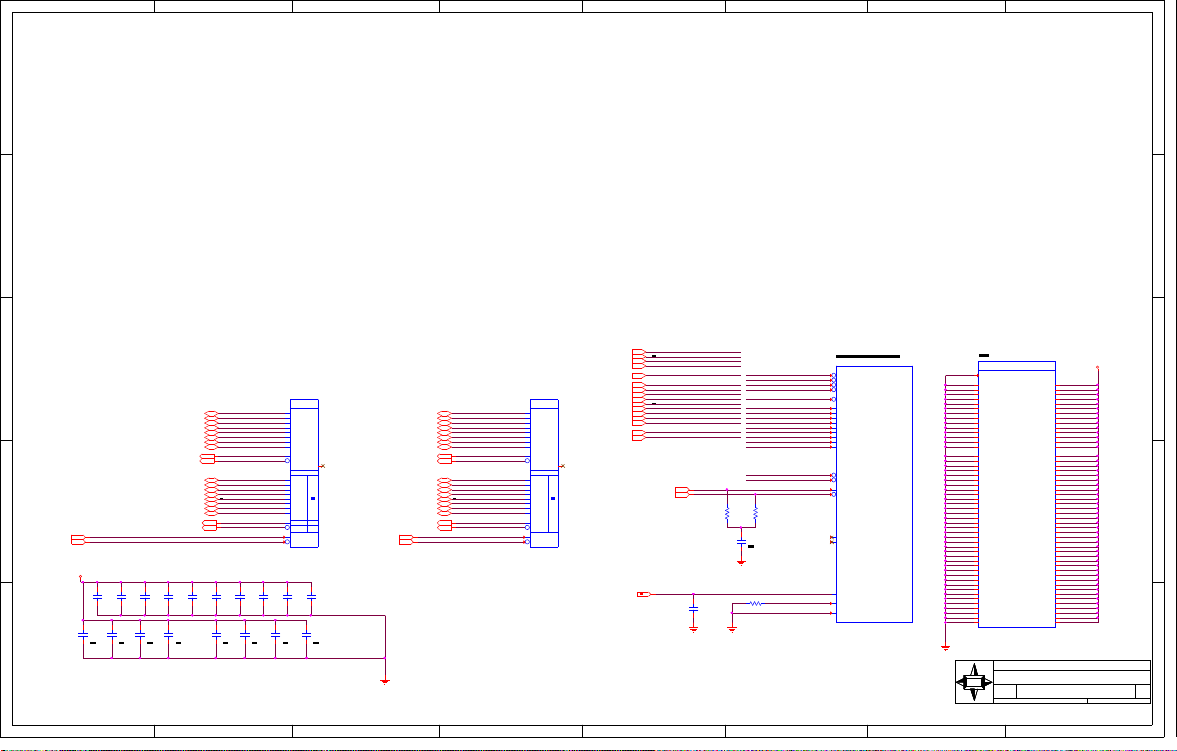

PCI Express

1

2

3

4

5

ALLNV IDIA DESIGN SPECIFICAT IONS, REFERENCE SP ECIFICATIONS, REFERENCE BOARDS,FILES , DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEP ARATEL Y, 'MATERIALS') ARE BE INGP ROVIDED 'AS IS'. THE MAT ERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIA TIONS OF INDUSTRY ST ANDARDS AND SP ECIFICATIONS. NVIDIA MAKES NO WARRANTIE S, EXPRE SSED, IMPLIED, ST ATUT ORY OR OTHERWISE WIT H RESPECT TO THE MAT ERIALS OR OTHERWIS E, AND EXP RESSLY DISCLA IMS ALL

IMPLIED WARRANTIES INCLUDING, WIT HOUT LIMITATION, T HE WARRANT IES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNE SS FOR A PARTICULA R PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, T RADE PRACT ICE, OR INDUSTRY ST ANDARDS.

3V3

XXXV32010

12

12

4.7uF

20%

X5R

0603

COMMON

C817

C822

GND

12V

NONPH Y-X16

NONPHY-X16

CON_X1 6

COMMON

@electro_mechanic.c on_pc i_expr ess( sym_1 ):page3_ i662

B1

+12V

B2

+12V

A2

+12V

A3

+12V

B3

PEX_PRSNT*

+12V/RSVD

B8

+3V3

A9

+3V3

A10

+3V3

B10

+3V3AUX

A1

PRSNT1

B17

PRSNT2

B12

RSVD

B4

GND

A4

GND

B7

GND

A12

GND

B13

GND

A15

GND

B16

GND

B18

GND

A18

GND

GND

END OF X1

B31

PRSNT2

A19

RSVD

B30

RSVD

A32

RSVD

A20

GND

B21

GND

B22

GND

A23

GND

A24

GND

B25

GND

B26

GND

A27

GND

A28

GND

B29

GND

A31

GND

B32

GND

END OF X4

B48

GND

PRSNT2

A33

RSVD

A34

GND

B35

GND

B36

GND

A37

GND

A38

GND

B39

GND

B40

GND

A41

GND

A42

GND

B43

GND

B44

GND

A45

GND

A46

GND

B47

GND

B49

GND

A49

GND

END OF X8

GND

B81

PRSNT2

A50

RSVD

B82

RSVD

A51

GND

B52

GND

B53

GND

A54

GND

A55

GND

B56

GND

B57

GND

A58

GND

A59

GND

B60

GND

B61

GND

A62

GND

A63

GND

B64

GND

B65

GND

A66

GND

A67

GND

B68

GND

B69

GND

A70

GND

A71

GND

B72

GND

B73

GND

A74

GND

A75

GND

B76

GND

B77

GND

A78

GND

A79

GND

B80

GND

A82

GND

GND

XXXV32010

0.1uF

10%

X7R

0402

COMMON

END OF X16

XXXV32010

CN2

TRST* JTA G1

TCLK JT AG2

TDI JTA G3

TDO JTAG4

TMS JTAG5

B9

A5

A6

A7

A8

B5

SMCLK

B6

SMDAT

B11

WAKE

A11

PERST

A13

REFCLK

A14

REFCLK

A16

PERP0

A17

PERN0

B14

PETP0

B15

PETN0

A21

PERP1

A22

PERN1

B19

PETP1

B20

PETN1

A25

PERP2

A26

PERN2

B23

PETP2

B24

PETN2

A29

PERP3

A30

PERN3

B27

PETP3

B28

PETN3

A35

PERP4

A36

PERN4

B33

PETP4

B34

PETN4

A39

PERP5

A40

PERN5

B37

PETP5

B38

PETN5

A43

PERP6

A44

PERN6

B41

PETP6

B42

PETN6

A47

PERP7

A48

PERN7

B45

PETP7

B46

PETN7

A52

PERP8

A53

PERN8

B50

PETP8

B51

PETN8

A56

PERP9

A57

PERN9

B54

PETP9

B55

PETN9

A60

PERP10

A61

PERN10

B58

PETP10

B59

PETN10

A64

PERP11

A65

PERN11

B62

PETP11

B63

PETN11

A68

PERP12

A69

PERN12

B66

PETP12

B67

PETN12

A72

PERP13

A73

PERN13

B70

PETP13

B71

PETN13

A76

PERP14

A77

PERN14

B74

PETP14

B75

PETN14

A80

PERP15

A81

PERN15

B78

PETP15

B79

PETN15

1 2

COMMON

PEX_TRST*

PEX_TCLK

PEX_TDI

PEX_TDO

PEX_TMS

XXXV32010

COMMON

SOT363

PEX_SMCLK

PEX_SMDAT

PEX_RST*

PEX_REFCLK

PEX_REFCLK PEXGEN3_SIGNALS

PEX_REFCLK*

PEX_TXX0

PEX_TXX0*

PEX_TXX0 PEXGEN3_SIGNALS

PEX_RX0

PEX_RX0*

PEX_TXX1

PEX_TXX1*

PEX_RX1

PEX_RX1 PEXGEN3_SIGNALS

PEX_RX1*

PEX_RX1 PEXGEN3_SIGNALS

PEX_TXX2

PEX_TXX2 PEXGEN3_SIGNALS

PEX_TXX2*

PEX_TXX2 PEXGEN3_SIGNALS

PEX_RX2

PEX_RX2*

PEX_RX2 PEXGEN3_SIGNALS

PEX_TXX3

PEX_TXX3*

PEX_RX3

PEX_RX3 PEXGEN3_SIGNALS

PEX_RX3*

PEX_TXX4

PEX_TXX4*

PEX_RX4

PEX_RX4 PEXGEN3_SIGNALS

PEX_RX4*

PEX_RX4 PEXGEN3_SIGNALS

PEX_TXX5

PEX_TXX5*

PEX_RX5

PEX_RX5 PEXGEN3_SIGNALS

PEX_RX5*

PEX_RX5 PEXGEN3_SIGNALS

PEX_TXX6

PEX_TXX6*

PEX_RX6

PEX_RX6 PEXGEN3_SIGNALS

PEX_RX6*

PEX_RX6 PEXGEN3_SIGNALS

PEX_TXX7

PEX_TXX7 PEXGEN3_SIGNALS

PEX_TXX7*

PEX_TXX7 PEXGEN3_SIGNALS

PEX_RX7

PEX_RX7 PEXGEN3_SIGNALS

PEX_RX7*

PEX_RX7 PEXGEN3_SIGNALS

PEX_TXX8

PEX_TXX8*

PEX_RX8

PEX_RX8 PEXGEN3_SIGNALS

PEX_RX8*

PEX_RX8 PEXGEN3_SIGNALS

PEX_TXX9

PEX_TXX9*

PEX_RX9

PEX_RX9 PEXGEN3_SIGNALS

PEX_RX9*

PEX_RX9 PEXGEN3_SIGNALS

PEX_TXX10

PEX_TXX10*

PEX_RX10

PEX_RX10 PEXGEN3_SIGNALS

PEX_RX10*

PEX_RX10 PEXGEN3_SIGNALS

PEX_TXX11

PEX_TXX11*

PEX_RX11

PEX_RX11 PEXGEN3_SIGNALS

PEX_RX11*

PEX_RX11 PEXGEN3_SIGNALS

PEX_TXX12

PEX_TXX12 PEXGEN3_SIGNALS

PEX_TXX12*

PEX_TXX12 PEXGEN3_SIGNALS

PEX_RX12

PEX_RX12 PEXGEN3_SIGNALS

PEX_RX12*

PEX_RX12 PEXGEN3_SIGNALS

PEX_TXX13

PEX_TXX13 PEXGEN3_SIGNALS

PEX_TXX13*

PEX_TXX13 PEXGEN3_SIGNALS

PEX_RX13

PEX_RX13 PEXGEN3_SIGNALS

PEX_RX13*

PEX_RX13 PEXGEN3_SIGNALS

PEX_TXX14

PEX_TXX14 PEXGEN3_SIGNALS

PEX_TXX14*

PEX_TXX14 PEXGEN3_SIGNALS

PEX_RX14

PEX_RX14 PEXGEN3_SIGNALS

PEX_RX14*

PEX_RX14 PEXGEN3_SIGNALS

PEX_TXX15

PEX_TXX15 PEXGEN3_SIGNALS

PEX_TXX15*

PEX_TXX15 PEXGEN3_SIGNALS

PEX_RX15

PEX_RX15 PEXGEN3_SIGNALS

PEX_RX15*

PEX_RX15 PEXGEN3_SIGNALS

C E

VVVV32010

0ohm

0402

R118

G

2

S

D

6

0ohm

1 2

Q518

DNI0402

XXXV32010

R162

OUT 3

XXXV32010

@discrete.q_fet_n_enh(s ym_2) :page3_i898

COMMON

SOT363

1

PEXGEN3_SIGNALSPEX_REFCLK

PEXGEN3_SIGNALSPEX_TXX0

PEXGEN3_SIGNALSPEX_RX0

PEXGEN3_SIGNALSPEX_RX0

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALSPEX_RX2

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALSPEX_RX3

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

XXXV32010

XXXV32010

XXXV32010

XXXV32010

XXXV32010

D

3

Q518

1 2

0402 DNI

XXXV32010

R148

1 2

1 2

R688

1 2

R724

0402

1 2

R704

0402

1 2

R705

0402

R706

G

5

S

4

0ohm

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

1 2

X5R

1 2

0402 6.3V

X5R

1 2

X5R

1 2

0402 6.3V

X5R

1 2

0402 6.3V

X5R

1 2

0402

X5R

1 2

0402 6.3V

X5R

1 2

0402 6.3V

X5R

1 2

0402 6.3V

X5R

1 2

0402

X5R

1 2

0402

X5R

1 2

0402

X5R

1 2

0402

X5R

1 2

0402 6.3V

X5R

1 2

0402 6.3V

X5R

1 2

0402

X5R

NV3V3

U502

3V3_F

0ohm

JTAG_TRST*

JTAG_TCLK

JTAG_TDI

JTAG_TDO

JTAG_TMS

1 2

0402

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

1 2

0402 6.3V

VVVV32010

C801

VVVV32010

C790

VVVV32010

C783

VVVV32010

C777

VVVV32010

C767

VVVV32010

C781

VVVV32010

C778

VVVV32010

C771

VVVV32010

C768

VVVV32010

C765

VVVV32010

C678

VVVV32010

C652

VVVV32010

C632

VVVV32010

C601

VVVV32010

C581

VVVV32010

C570

ASSEMBLY

PAGE DETAIL

0.22uF

10%

6.3V

X5R

0.22uF

10%

X5R

0.22uF

10%

X5R

0.22uF

X5R

0.22uF

10%

X5R

0.22uF

10%

X5R

0.22uF

10%

X5R

0.22uF

10%

X5R

0.22uF

X5R

0.22uF

10%

X5R

0.22uF

10%

X5R

0.22uF

10%

X5R

0.22uF

10%

X5R

0.22uF

X5R

0.22uF

10%

X5R

0.22uF

10%

X5R

OUT 21

OUT 21

OUT 21

OUT 21

OUT 21

XXXV32010

100k

5 %

0402

COMMON

R1642

IN3,20,32

PEX_TX0

PEX_TX0*

COMMON

PEX_TX1

PEX_TX1*

COMMON

PEX_TX2

PEX_TX2*

COMMON

PEX_TX3

PEX_TX3*

COMMON

PEX_TX4

PEX_TX4*

COMMON

PEX_TX5

PEX_TX5*

COMMON

PEX_TX6

PEX_TX6*

COMMON

PEX_TX7

PEX_TX7*

COMMON

PEX_TX8

PEX_TX8*

COMMON

PEX_TX9

PEX_TX9*

COMMON

PEX_TX10

PEX_TX10*

COMMON

PEX_TX11

PEX_TX11*

COMMON

PEX_TX12

PEX_TX12*

COMMON

PEX_TX13

PEX_TX13*

COMMON

PEX_TX14

PEX_TX14*

COMMON

PEX_TX15

PEX_TX15*

COMMON

BASE LEVEL GENE RIC SCHEMATIC ONLY

PCI Express

PEX_RST*

IN3 OUT 3,20,32

NV3V3

XXXV32010

100k

5 %

0402

COMMON

I2CS_SCL

OUT 21

I2CS_SDA

OUT 21

R1643

PEX_RST_BUF*

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

PEXGEN3_SIGNALS

COMMON0402

0ohm

COMMON0402

0ohm

COMMON

0ohm

COMMON

0ohm

COMMON

0.22uF

6.3V0402

10%

VVVV32010

C804

0.22uF

10%

VVVV32010

C795

0.22uF

6.3V0402

10%

VVVV32010

C787

0.22uF

VVVV32010

C779

0.22uF

10%

VVVV32010

C769

0.22uF

6.3V

10%

VVVV32010

C782

0.22uF

10%

VVVV32010

C780

0.22uF

10%

VVVV32010

C776

0.22uF

VVVV32010

C770

0.22uF

6.3V

10%

VVVV32010

C766

0.22uF

6.3V

10%

VVVV32010

C684

0.22uF

6.3V

10%

VVVV32010

C659

0.22uF

6.3V

10%

VVVV32010

C639

0.22uF

VVVV32010

C609

0.22uF

10%

VVVV32010

C584

0.22uF

6.3V

10%

VVVV32010

C574

@logic.u_buf_3_state(sy m_10):page 3_i876

SC70_5

5

COMMON

1

VCC

XXXV32010

OE

A

Y

2

4

GND

3

GND

R672

0ohm

1 2

COMMON0402

VVVV32010

U_GPU_GB2B_ 192 _BG A142 8-T EST_G M206 _G PU_GM2 06- INT-A1- GM2 06- INT-A1

BGA1428

@digital.u_gpu_gb2b_192( sym_1 ):page3_i8 64

BGA1428

COMMON

1/18 PCI_EXPRESS

BA15

PEX_WAKE

BB19

PEX_RST

BB18

PEX_CLKREQ

AW17

PEX_REFCLK

AY17

PEX_REFCLK

AU19

PEX_TX0

AV19

PEX_TX0

BA19

PEX_RX0

AY19

PEX_RX0

AW20

PEX_TX1

AV20

PEX_TX1

AY21

PEX_RX1

BA21

PEX_RX1

AV21

PEX_TX2

AU21

PEX_TX2

BB21

PEX_RX2

BB22

PEX_RX2

AU22

PEX_TX3

AV22

PEX_TX3

BA22

PEX_RX3

AY22

PEX_RX3

AV23

PEX_TX4

AW23

PEX_TX4

AY24

PEX_RX4

BA24

PEX_RX4

AV24

PEX_TX5

AU24

PEX_TX5

BB24

PEX_RX5

BB25

PEX_RX5

AU25

PEX_TX6

AV25

PEX_TX6

BA25

PEX_RX6

AY25

PEX_RX6

AW26

PEX_TX7

AV26

PEX_TX7

AY27

PEX_RX7

BA27

PEX_RX7

AV27

PEX_TX8

AU27

PEX_TX8

BB27

PEX_RX8

BB28

PEX_RX8

AU28

PEX_TX9

AV28

PEX_TX9

BA28

PEX_RX9

AY28

PEX_RX9

AW29

PEX_TX10

AV29

PEX_TX10

AY30

PEX_RX10

BA30

PEX_RX10

AV30

PEX_TX11

AU30

PEX_TX11

BB30

PEX_RX11

BB31

PEX_RX11

AU31

PEX_TX12

AV31

PEX_TX12

BA31

PEX_RX12

AY31

PEX_RX12

AW32

PEX_TX13

AV32

PEX_TX13

AY33

PEX_RX13

BA33

PEX_RX13

AV33

PEX_TX14

AU33

PEX_TX14

BB33

PEX_RX14

BB34

PEX_RX14

AU34

PEX_TX15

AV34

PEX_TX15

BA34

PEX_RX15

AY34

PEX_RX15

VVVV32010

G1

PEX_RST_BUF*

GND

R675

XXXV32010

5 %

0402

DNI

PEX_TST CLK_OUT

PEX_TST CLK_OUT

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_PLL_HVDD

PEX_SVDD_3V3

NVVDD_SENSE

GND_SENSE

PEX_PLLVDD

TESTMODE

PEX_TERMP

MIN_WIDTHNET

0.500

5.5A

0.500

3.0A

C751

C132

12

12

VVVV32010

VVVV32010

22uF

22uF

6.3V

20%

X5R

0805

COMMON

C721

VVVV32010

12

1uF

6.3V

10%

X5R

0402

COMMON

GND

C133

12

VVVV32010

22uF

6.3V

20%

X5R

0805

COMMON

nv_res

6.3V

R1668

20%

VVVV32010

X5R

0ohm

0805

COMMON

0.05 ohm

0805

COMMON

GND

nv_res

R1669

XXXV32010

0ohm

0.05 ohm

0805

COMMON

C136

C750

12

12

VVVV32010

VVVV32010

22uF

22uF

6.3V

6.3V

20%

20%

X5R

X5R

0805

0805

COMMON

COMMON

1

PEX_VDD

nv_res

R1670

VVVV32010

0ohm

0.05 ohm

0805

COMMON

2

IOVDD

PEX_VDD

3

GND

C743

12

VVVV32010

4.7uF

6.3V

20%

X5R

0603

COMMON

C722

12

VVVV32010

0.1uF

16V

10%

X7R

0402

COMMON

IOVDD

C679

12

VVVV32010

4.7uF

6.3V

X5R

0603

COMMON

GND

OUT 25,29

OUT 25,29

VOLTAGE MAX_CURRENT

12V

3.3V

C741

12

VVVV32010

22uF

6.3V

20%

X5R

0805

COMMON

C732

12

VVVV32010

0.1uF

16V

10%

X7R

0402

COMMON

C137

12

VVVV32010

4.7uF

6.3V

20%

X5R

0603

COMMON

12V

12V

3V3

3V3

GND 0.4008.5A0V

GND

AP29

AP30

AR27

AR28

AR29

AP17

AP18

AP19

AP20

AP21

AP22

AP23

AP24

AP25

AP26

AP27

AP28

AR19

AR20

AR21

AR22

AR23

AR24

AR25

AR26

AT22

AT28

AT42

AT41

NVVDD_SENSE

GND_SENSE

12

VVVV32010

C672

12

VVVV32010

C762

12

VVVV32010

1uF

6.3V

10%

X5R

0402

COMMON

GPU_PEX_IOVDDQ 0.400

C723

C724

12

VVVV32010

1uF

1uF

6.3V

6.3V

10%

10%

X5R

X5R

0402

0402

COMMON

COMMON

C729

12

VVVV32010

0.1uF

4.7uF

16V

6.3V

X7R

X5R

0402

0603

COMMON

COMMON

4

PEX_VDD IOVDD

R635

PEX_PLL_CLK_OUT

BB36

BA36

AT25

AT21

AW35

FDBA

PEX_PLL_CLK_OUT*

GPU_TESTMODE

PEX_TERMP

PEX_PLL_CLK PEXGEN3_SIGNALS

PEX_PLL_CLK PEXGEN3_SIGNALS

PEX_PLLVDD

1 2

0402

5 %

VVVV32010

R637

1 2

0402

1 %

VVVV32010

R629

10k

COMMON

GND

2.49k

COMMON

GND

G

200ohm

5 %

0402

COMMON

VVVV32010

C759

12

VVVV32010

0.1uF

16V

10%

X7R

0402

COMMON

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

R664

0ohm

VVVV32010

0402

COMMON

C731

C761

12

12

VVVV32010

VVVV32010

1uF

4.7uF

6.3V

6.3V

10%

20%

X5R

X5R

0402

0603

COMMON

COMMON

GND

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

MS-V320

MS-V320

MS-V320

03_PCI Express

03_PCI Express

03_PCI Express

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

R663

0ohm

XXXV32010

0402

COMMON

5

10

10

10

Sheet ofDate:

3 34

Sheet ofDate:

3 34

Sheet ofDate:

3 34

H

A B C D E F G H

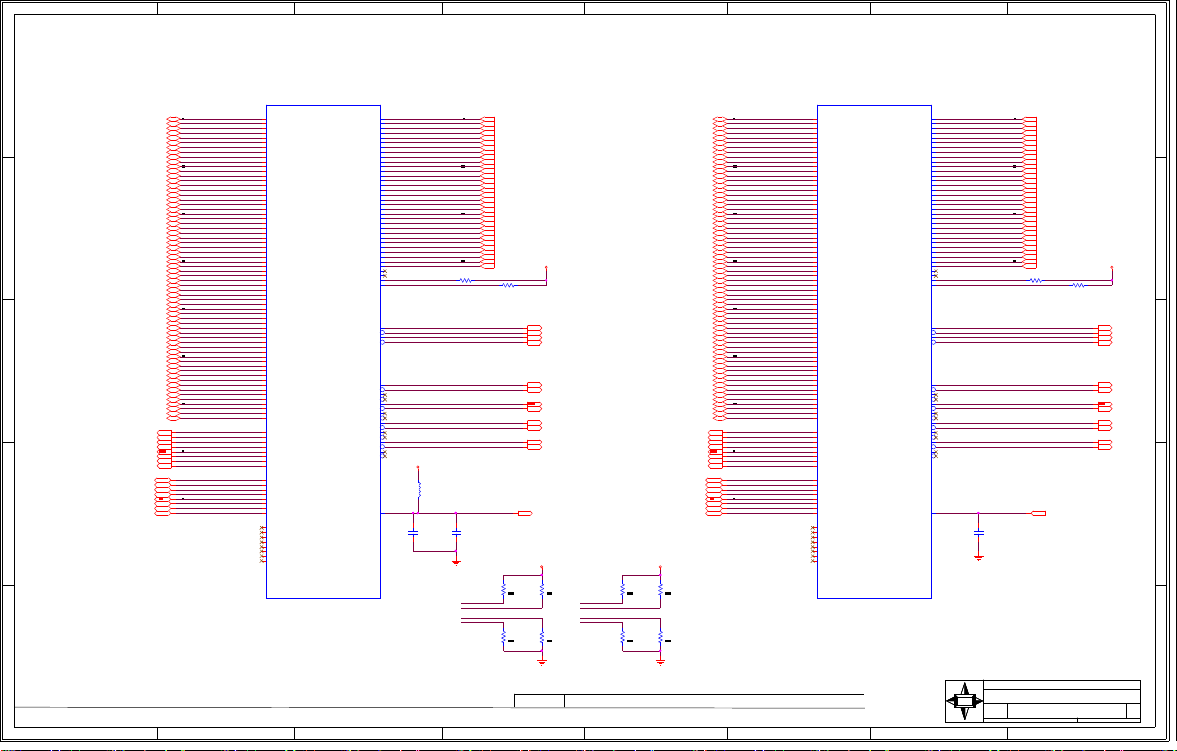

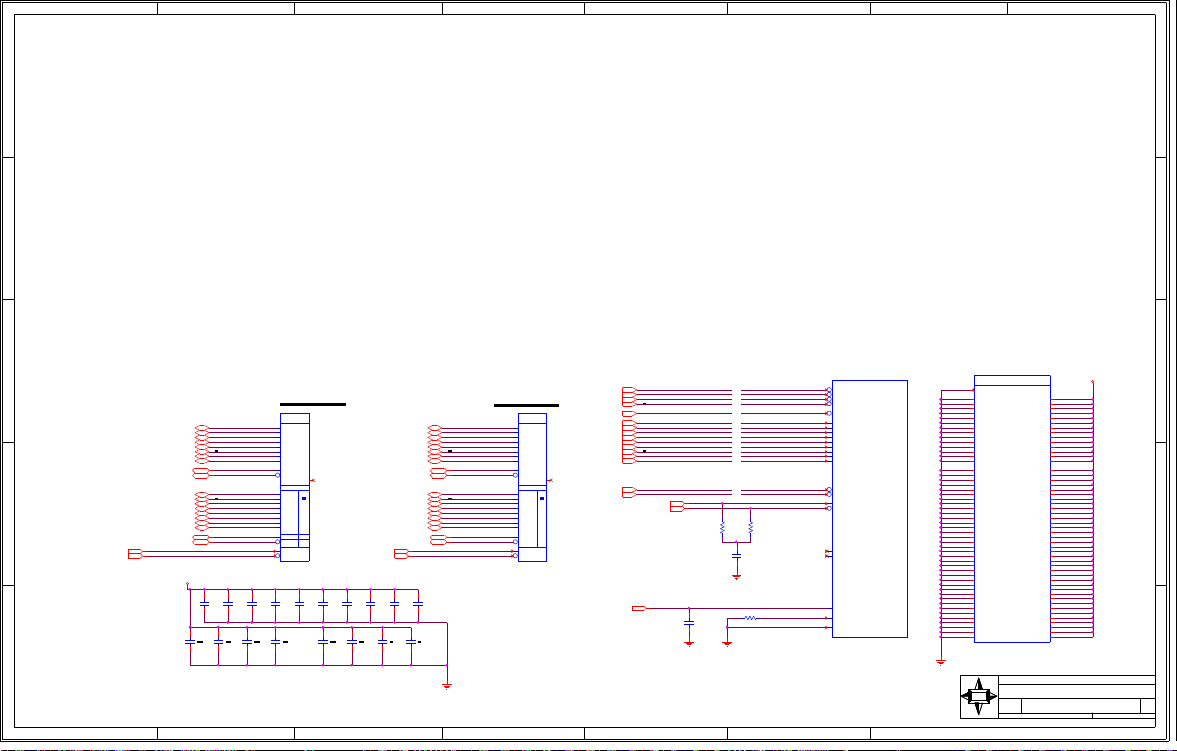

MEMORY: GPU Partition A/B

1

5

Fba_D<0>

5

Fba_D<1>

5

Fba_D<2>

5

Fba_D<3>

5

Fba_D<4>

5

Fba_D<5>

5

Fba_D<6>

5

Fba_D<7>

5

Fba_D<8>

5

Fba_D<9>

5

Fba_D<10>

5

Fba_D<11>

5

Fba_D<12>

5

Fba_D<13>

5

Fba_D<14>

5

Fba_D<15>

5

Fba_D<16>

5

Fba_D<17>

5

Fba_D<18>

5

Fba_D<19>

5

Fba_D<20>

5

Fba_D<21>

5

2

3

Fba_D<22>

5

Fba_D<23>

5

Fba_D<24>

5

Fba_D<25>

5

Fba_D<26>

5

Fba_D<27>

5

Fba_D<28>

5

Fba_D<29>

5

Fba_D<30>

5

Fba_D<31>

6

Fba_D<32>

6

Fba_D<33>

6

Fba_D<34>

6

Fba_D<35>

6

Fba_D<36>

6

Fba_D<37>

6

Fba_D<38>

6

Fba_D<39>

6

Fba_D<40>

6

Fba_D<41>

6

Fba_D<42>

6

Fba_D<43>

6

Fba_D<44>

6

Fba_D<45>

6

Fba_D<46>

6

Fba_D<47>

6

Fba_D<48>

6

Fba_D<49>

6

Fba_D<50>

6

Fba_D<51>

6

Fba_D<52>

6

Fba_D<53>

6

Fba_D<54>

6

Fba_D<55>

6

Fba_D<56>

6

Fba_D<57>

6

Fba_D<58>

6

Fba_D<59>

6

Fba_D<60>

6

Fba_D<61>

6

Fba_D<62>

6

Fba_D<63>

6

4

5

ALL NVIDIA DESIGN SPECIFICAT IONS, REFERENCE SP ECIFICATIONS, REFERENCE BOARDS, FILES, DRAWI NGS, DIAGNOSTICS, LIST S AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEP ARATEL Y, 'MATERIALS') ARE BE ING PROVIDED 'AS IS'. THE MAT ERIALS MAY

CONTAINK NOWNA ND UNKNOWN VIOLATIONS OR DEVIA TIONS OFI NDUSTRY ST ANDARDS AND SP ECIFICATIONS. NVIDIA MAKESNO WARRA NTIES, E XPRESSE D, IMPLIED, STAT UTORY OR OTHERWISE WITH RESPECT TOT HE MATERIALS OROTHERWIS E, AND EXP RESSLY DISCLA IMS ALL

IMPLIED WARRANTIES INCLUDING, WIT HOUT LIMITATION, T HE WARRANT IES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNE SS FOR A PARTICULA R PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, T RADE PRACT ICE, OR INDUSTRY ST ANDARDS.

6

FBA_D<0>

FBA_D<1>

1

FBA_D<2>

2

FBA_D<3>

3

FBA_D<4>

4

FBA_D<5>

5

FBA_D<6>

6

FBA_D<7>

7

FBA_D<8>

8

FBA_D<9>

9

FBA_D<10>

FBA_D<11>

11

FBA_D<12>

12

FBA_D<13>

13

FBA_D<14>

14

FBA_D<15>

15

FBA_D<16>

16

FBA_D<17>

17

FBA_D<18>

18

FBA_D<19>

19

FBA_D<20>

FBA_D<21>

21

FBA_D<22>

22

FBA_D<23>

23

FBA_D<24>

24

FBA_D<25>

25

FBA_D<26>

26

FBA_D<27>

27

FBA_D<28>

28

FBA_D<29>

29

FBA_D<30>

FBA_D<31>

31

FBA_D<32>

32

FBA_D<33>

33

FBA_D<34>

34

FBA_D<35>

35

FBA_D<36>

36

FBA_D<37>

37

FBA_D<38>

38

FBA_D<39>

39

FBA_D<40>

FBA_D<41>

41

FBA_D<42>

42

FBA_D<43>

43

FBA_D<44>

44

FBA_D<45>

45

FBA_D<46>

46

FBA_D<47>

47

FBA_D<48>

48

FBA_D<49>

49

FBA_D<50>

FBA_D<51>

51

FBA_D<52>

52

FBA_D<53>

53

FBA_D<54>

54

FBA_D<55>

55

FBA_D<56>

56

FBA_D<57>

57

FBA_D<58>

58

FBA_D<59>

59

FBA_D<60>

FBA_D<61>

61

FBA_D<62>

62

FBA_D<63>

63

FBA_DBI<0>

0

OUT5

FBA_DBI<1>

1

OUT5

FBA_DBI<2>

2

OUT5

FBA_DBI<3>

3

OUT5

FBA_DBI<4>

FBA_DBI<5>

5

OUT6

FBA_DBI<6>

6

OUT6

FBA_DBI<7>

7

OUT6

FBA_EDC<0>

0

BI5

FBA_EDC<1>

1

BI5

FBA_EDC<2>

2

BI5

FBA_EDC<3>

3

BI5

FBA_EDC<4>

FBA_EDC<5>

5

BI6

FBA_EDC<6>

6

BI6

FBA_EDC<7>

7

BI6

U_GPU_GB2B_ 192 _BG A142 8-T EST_G M206 _G PU_GM2 06- INT-A1- GM2 06- INT-A1

G1B

@digital.u_gpu_gb2b_192( sym_2 ):page4_i1 905

BGA1428

COMMON

2/18 FBA

H38

FBA_D0

J39

FBA_D1

J38

FBA_D2

J37

FBA_D3

L36

FBA_D4

K38

FBA_D5

M39

FBA_D6

K39

FBA_D7

M42

FBA_D8

L40

FBA_D9

M41

FBA_D10

M40

FBA_D11

J42

FBA_D12

J41

FBA_D13

H40

FBA_D14

J40

FBA_D15

N40

FBA_D16

N41

FBA_D17

N42

FBA_D18

P40

FBA_D19

T40

FBA_D20

T42

FBA_D21

U40

FBA_D22

T41

FBA_D23

T38

FBA_D24

T37

FBA_D25

T39

FBA_D26

U36

FBA_D27

P36

FBA_D28

R39

FBA_D29

R38

FBA_D30

N39

FBA_D31

AT40

FBA_D32

AP39

FBA_D33

AR38

FBA_D34

AP38

FBA_D35

AN37

FBA_D36

AL37

FBA_D37

AN39

FBA_D38

AN38

FBA_D39

AL40

FBA_D40

AL41

FBA_D41

AL42

FBA_D42

AM40

FBA_D43

AP40

FBA_D44

AP42

FBA_D45

AR40

FBA_D46

AP41

FBA_D47

AK37

FBA_D48

AK39

FBA_D49

AK38

FBA_D50

AH39

FBA_D51

AF36

FBA_D52

AG37

FBA_D53

AG39

FBA_D54

AG38

FBA_D55

AF38

FBA_D56

AG41

FBA_D57

AG40

FBA_D58

AG42

FBA_D59

AJ40

FBA_D60

AK40

FBA_D61

AK42

FBA_D62

AK41

FBA_D63

K36

FBA_DQM0

K42

FBA_DQM1

R42

FBA_DQM2

R37

FBA_DQM3

AP37

FBA_DQM4

AN42

FBA_DQM5

AJ36

FBA_DQM6

AH42

FBA_DQM7

J36

FBA_DQS_WP0

K41

FBA_DQS_WP1

R41

FBA_DQS_WP2

T35

FBA_DQS_WP3

AN36

FBA_DQS_WP4

AN41

FBA_DQS_WP5

AH38

FBA_DQS_WP6

AH41

FBA_DQS_WP7

J35

FBA_DQS_RN0

K40

FBA_DQS_RN1

R40

FBA_DQS_RN2

R36

FBA_DQS_RN3

AM36

FBA_DQS_RN4

AN40

FBA_DQS_RN5

AH37

FBA_DQS_RN6

AH40

FBA_DQS_RN7

VVVV32010

FBA_CMD<0>

W38

FBA_CMD0

FBA_CMD<1>

W37

FBA_CMD1

Y40

FBA_CMD2

Y38

FBA_CMD3

AC40

FBA_CMD4

Y36

FBA_CMD5

V36

FBA_CMD6

W42

FBA_CMD7

W41

FBA_CMD8

W40

FBA_CMD9

V35

FBA_CMD10

W39

FBA_CMD11

V40

FBA_CMD12

V39

FBA_CMD13

V38

FBA_CMD14

V37

FBA_CMD15

AE38

FBA_CMD16

AE37

FBA_CMD17

AE36

FBA_CMD18

AD39

FBA_CMD19

AE35

FBA_CMD20

AD38

FBA_CMD21

AE41

FBA_CMD22

AE42

FBA_CMD23

AD37

FBA_CMD24

AC38

FBA_CMD25

AC36

FBA_CMD26

W35

FBA_CMD27

AE40

FBA_CMD28

AD42

FBA_CMD29

AD41

FBA_CMD30

AD40

FBA_CMD31

AE34

FBA_CMD32

AF34

FBA_CMD33

AC35

FBA_CMD34

AD35

FBA_CMD35

V41

FBA_CLK0

V42

FBA_CLK0

AF40

FBA_CLK1

AF39

FBA_CLK1

M37

FBA_WCK01

M38

FBA_WCK01

M36

FBA_WCKB01

L35

FBA_WCKB01

N37

FBA_WCK23

N38

FBA_WCK23

P35

FBA_WCKB23

N36

FBA_WCKB23

AK36

FBA_WCK45

AJ35

FBA_WCK45

AH36

FBA_WCKB45

AG35

FBA_WCKB45

AL38

FBA_WCK67

AL39

FBA_WCK67

AM35

FBA_WCKB67

AL36

FBA_WCKB67

AG34

FBA_PLL_AVDD

C E

1

FBA_CMD<2>

2

FBA_CMD<3>

3

FBA_CMD<4>

4

FBA_CMD<5>

5

FBA_CMD<6>

6

FBA_CMD<7>

7

FBA_CMD<8>

8

FBA_CMD<9>

9

FBA_CMD<10>

FBA_CMD<11>

11

FBA_CMD<12>

12

FBA_CMD<13>

13

FBA_CMD<14>

14

FBA_CMD<15>

15

FBA_CMD<16>

16

FBA_CMD<17>

17

FBA_CMD<18>

18

FBA_CMD<19>

19

FBA_CMD<20>

FBA_CMD<21>

21

FBA_CMD<22>

22

FBA_CMD<23>

23

FBA_CMD<24>

24

FBA_CMD<25>

25

FBA_CMD<26>

26

FBA_CMD<27>

27

FBA_CMD<28>

28

FBA_CMD<29>

29

FBA_CMD<30>

FBA_CMD<31>

31

R580

FBA_DEBUG0

1 2

FBA_DEBUG1

0402

1 %

XXXV32010

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBA_WCK01

FBA_WCK01*

FBA_WCK23

FBA_WCK23*

FBA_WCK45

FBA_WCK45*

FBA_WCK67

FBA_WCK67*

IOVDD

LB501

30ohm

COMMON

BEAD_060 3

VVVV32010

FB_PLLVDD FB_PLLVDD

VVVV32010

C593

12

C633

12

0.1uF

22uF

16V

6.3V

10%

20%

X7R

X5R

0402

0805

COMMON

COMMON

VVVV32010

GND

CKE*

FBA_CMD<30>

FBA_CMD<14>

FBA_CMD<29>

FBA_CMD<13>

U_GPU_GB2B_ 192 _BG A142 8-T EST_G M206 _G PU_GM2 06- INT-A1- GM2 06- INT-A1

G1C

@digital.u_gpu_gb2b_192( sym_3 ):page4_i1 906

BGA1428

COMMON

5

FBA_CMD<0>

5

FBA_CMD<1>

FBA_CMD<2>

FBA_CMD<3>

FBA_CMD<4>

FBA_CMD<5>

FBA_CMD<6>

FBA_CMD<7>

FBA_CMD<8>

FBA_CMD<9>

FBA_CMD<10>

FBA_CMD<11>

FBA_CMD<12>

FBA_CMD<13>

FBA_CMD<14>

FBA_CMD<15>

FBA_CMD<16>

FBA_CMD<17>

FBA_CMD<18>

FBA_CMD<19>

FBA_CMD<20>

FBA_CMD<21>

FBA_CMD<22>

FBA_CMD<23>

FBA_CMD<24>

FBA_CMD<25>

FBA_CMD<26>

FBA_CMD<27>

FBA_CMD<28>

FBA_CMD<29>

FBA_CMD<30>

FBA_CMD<31>

60.4ohm

R583

1 2

DNI

0402

1 %

XXXV32010

FB_CLK

FB_CLK

FB_CLK

FB_CLK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

R614

10k

5 %

COMMON

VVVV32010

VVVV32010

R564

10k

5 %

COMMON

5

5

5

5

5

5

5

5

5

5

5

5

5

5

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

FBVDDQ

6

60.4ohm

DNI

OUT 5

OUT 5

OUT 6

OUT 6

OUT 5

OUT 5

OUT 5

OUT 6

OUT 6

OUT 6

OUT 6

OUT 4,9,15

FBVDDQ

R561

10k

5 %

COMMON

VVVV32010

VVVV32010

R621

10k

5 %

COMMON

GND

ASSEMBLY

PAGE DETAIL

GDDR5_BGA170_MIRROR

CMD0 CS*

CMD1 A3_BA3

CMD2 A2_BA0

CMD3 A4_BA2

CMD4 A5_BA1

CMD5 WE*

CMD6 A7_A8

CMD7 A6_A11

CMD8 ABI*

CMD9 A12_RFU

CMD10 A0_A10

CMD11 A1_A9

CMD12 RAS*

CMD13 RST*

CMD14 CKE*

CMD15 CAS*

CMD32

CMD34 DBG0 DBG0

CMD16 CS*

CMD17 A3_BA3

CMD18 A2_BA0

CMD19 A4_BA2

CMD20 A5_BA1

CMD21 W E*

CMD22 A7_A8

CMD23 A6_A11

CMD24 ABI *

CMD25 A12_RFU

CMD26 A0_A10

CMD27 A1_A9

CMD28 RAS*

CMD29 RST*

CMD30 CKE*

CMD31 CAS*

CMD33

CMD35 DBG1 DBG1

5

CKE*

FBB_CMD<30>

FBB_CMD<14>

FBB_CMD<29>

FBB_CMD<13>

RST*RST*

BASE LEVEL GENE RIC SCHEMATIC ONLY

MEMORY: GPU Partition A/B

0..31 32..63

7

Fbb_D<0>

7

Fbb_D<1>

7

Fbb_D<2>

7

Fbb_D<3>

7

Fbb_D<4>

7

Fbb_D<5>

7

Fbb_D<6>

7

Fbb_D<7>

7

Fbb_D<8>

7

Fbb_D<9>

7

Fbb_D<10>

7

Fbb_D<11>

7

Fbb_D<12>

7

Fbb_D<13>

7

Fbb_D<14>

7

Fbb_D<15>

7

Fbb_D<16>

7

Fbb_D<17>

7

Fbb_D<18>

7

Fbb_D<19>

7

Fbb_D<20>

7

Fbb_D<21>

7

Fbb_D<22>

7

Fbb_D<23>

7

Fbb_D<24>

7

Fbb_D<25>

7

Fbb_D<26>

7

Fbb_D<27>

7

Fbb_D<28>

7

Fbb_D<29>

7

Fbb_D<30>

7

Fbb_D<31>

8

Fbb_D<32>

8

Fbb_D<33>

8

Fbb_D<34>

8

Fbb_D<35>

8

Fbb_D<36>

8

Fbb_D<37>

8

Fbb_D<38>

8

Fbb_D<39>

8

Fbb_D<40>

8

Fbb_D<41>

8

Fbb_D<42>

8

Fbb_D<43>

8

Fbb_D<44>

8

Fbb_D<45>

8

Fbb_D<46>

8

Fbb_D<47>

8

Fbb_D<48>

8

Fbb_D<49>

8

Fbb_D<50>

8

Fbb_D<51>

8

Fbb_D<52>

8

Fbb_D<53>

8

Fbb_D<54>

8

Fbb_D<55>

8

Fbb_D<56>

8

Fbb_D<57>

8

Fbb_D<58>

8

Fbb_D<59>

8

Fbb_D<60>

8

Fbb_D<61>

8

Fbb_D<62>

8

Fbb_D<63>

8

8

FBVDDQ

R552

R550

10k

10k

5 %

5 %

COMMON

COMMON

VVVV32010

VVVV32010

VVVV32010

VVVV32010

R551

R553

10k

10k

5 %

5 %

COMMON

COMMON

GND

FBB_D<0>

FBB_D<1>

1

FBB_D<2>

2

FBB_D<3>

3

FBB_D<4>

4

FBB_D<5>

5

FBB_D<6>

6

FBB_D<7>

7

FBB_D<8>

8

FBB_D<9>

9

FBB_D<10>

FBB_D<11>

11

FBB_D<12>

12

FBB_D<13>

13

FBB_D<14>

14

FBB_D<15>

15

FBB_D<16>

16

FBB_D<17>

17

FBB_D<18>

18

FBB_D<19>

19

FBB_D<20>

FBB_D<21>

21

FBB_D<22>

22

FBB_D<23>

23

FBB_D<24>

24

FBB_D<25>

25

FBB_D<26>

26

FBB_D<27>

27

FBB_D<28>

28

FBB_D<29>

29

FBB_D<30>

FBB_D<31>

31

FBB_D<32>

32

FBB_D<33>

33

FBB_D<34>

34

FBB_D<35>

35

FBB_D<36>

36

FBB_D<37>

37

FBB_D<38>

38

FBB_D<39>

39

FBB_D<40>

FBB_D<41>

41

FBB_D<42>

42

FBB_D<43>

43

FBB_D<44>

44

FBB_D<45>

45

FBB_D<46>

46

FBB_D<47>

47

FBB_D<48>

48

FBB_D<49>

49

FBB_D<50>

FBB_D<51>

51

FBB_D<52>

52

FBB_D<53>

53

FBB_D<54>

54

FBB_D<55>

55

FBB_D<56>

56

FBB_D<57>

57

FBB_D<58>

58

FBB_D<59>

59

FBB_D<60>

FBB_D<61>

61

FBB_D<62>

62

FBB_D<63>

63

FBB_DBI<0>

0

OUT7

FBB_DBI<1>

1

OUT7

FBB_DBI<2>

2

OUT7

FBB_DBI<3>

3

OUT7

FBB_DBI<4>

FBB_DBI<5>

5

OUT8

FBB_DBI<6>

6

OUT8

FBB_DBI<7>

7

OUT8

FBB_EDC<0>

0

BI7

FBB_EDC<1>

1

BI7

FBB_EDC<2>

2

BI7

FBB_EDC<3>

3

BI7

FBB_EDC<4>

FBB_EDC<5>

5

BI8

FBB_EDC<6>

6

BI8

FBB_EDC<7>

7

BI8

3/18 FBB

F15

FBB_D0

D15

FBB_D1

E15

FBB_D2

G15

FBB_D3

E16

FBB_D4

D16

FBB_D5

D18

FBB_D6

E18

FBB_D7

C18

FBB_D8

C17

FBB_D9

A18

FBB_D10

B18

FBB_D11

C15

FBB_D12

A15

FBB_D13

C14

FBB_D14

B15

FBB_D15

D19

FBB_D16

E19

FBB_D17

F19

FBB_D18

D21

FBB_D19

G23

FBB_D20

F22

FBB_D21

E22

FBB_D22

D22

FBB_D23

C23

FBB_D24

B22

FBB_D25

C22

FBB_D26

A22

FBB_D27

B21

FBB_D28

C19

FBB_D29

A19

FBB_D30

B19

FBB_D31

G41

FBB_D32

F42

FBB_D33

G42

FBB_D34

F41

FBB_D35

C41

FBB_D36

D42

FBB_D37

C39

FBB_D38

C40

FBB_D39

G35

FBB_D40

F37

FBB_D41

D36

FBB_D42

D37

FBB_D43

E37

FBB_D44

E39

FBB_D45

G37

FBB_D46

F38

FBB_D47

A36

FBB_D48

C35

FBB_D49

C36

FBB_D50

B36

FBB_D51

A34

FBB_D52

A33

FBB_D53

C33

FBB_D54

B33

FBB_D55

F35

FBB_D56

G34

FBB_D57

E36

FBB_D58

A37

FBB_D59

F34

FBB_D60

E33

FBB_D61

F33

FBB_D62

G32

FBB_D63

F16

FBB_DQM0

A16

FBB_DQM1

H22

FBB_DQM2

A21

FBB_DQM3

D40

FBB_DQM4

D41

FBB_DQM5

E34

FBB_DQM6

D34

FBB_DQM7

G16

FBB_DQS_WP0

B16

FBB_DQS_WP1

E21

FBB_DQS_WP2

C21

FBB_DQS_WP3

F40

FBB_DQS_WP4

D38

FBB_DQS_WP5

C34

FBB_DQS_WP6

B37

FBB_DQS_WP7

H15

FBB_DQS_RN0

C16

FBB_DQS_RN1

F21

FBB_DQS_RN2

C20

FBB_DQS_RN3

E40

FBB_DQS_RN4

D39

FBB_DQS_RN5

B34

FBB_DQS_RN6

C37

FBB_DQS_RN7

VVVV32010

FDBA

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD28

FBB_CMD29

FBB_CMD30

FBB_CMD31

FBB_CMD32

FBB_CMD33

FBB_CMD34

FBB_CMD35

FBB_WCK01

FBB_WCK01

FBB_WCKB01

FBB_WCKB01

FBB_WCK23

FBB_WCK23

FBB_WCKB23

FBB_WCKB23

FBB_WCK45

FBB_WCK45

FBB_WCKB45

FBB_WCKB45

FBB_WCK67

FBB_WCK67

FBB_WCKB67

FBB_WCKB67

FBB_PLL_AVDD

FBB_CLK0

FBB_CLK0

FBB_CLK1

FBB_CLK1

FBB_CMD<0>

D24

FBB_CMD<1>

E24

F24

H24

C24

A25

B25

C25

D25

G24

F25

E25

C26

C29

C30

B30

B31

G26

E26

C31

A31

A30

G31

D30

F30

E30

E29

H25

G29

D31

E31

F31

H29

H26

H30

H31

B24

A24

D32

C32

H20

G19

G18

H17

G17

F18

G20

G21

C38

B39

G36

H35

A39

B40

H36

H37

H23

G

1

FBB_CMD<2>

2

FBB_CMD<3>

3

FBB_CMD<4>

4

FBB_CMD<5>

5

FBB_CMD<6>

6

FBB_CMD<7>

7

FBB_CMD<8>

8

FBB_CMD<9>

9

FBB_CMD<10>

FBB_CMD<11>

11

FBB_CMD<12>

12

FBB_CMD<13>

13

FBB_CMD<14>

14

FBB_CMD<15>

15

FBB_CMD<16>

16

FBB_CMD<17>

17

FBB_CMD<18>

18

FBB_CMD<19>

19

FBB_CMD<20>

FBB_CMD<21>

21

FBB_CMD<22>

22

FBB_CMD<23>

23

FBB_CMD<24>

24

FBB_CMD<25>

25

FBB_CMD<26>

26

FBB_CMD<27>

27

FBB_CMD<28>

28

FBB_CMD<29>

29

FBB_CMD<30>

FBB_CMD<31>

31

FBB_DEBUG0

FBB_DEBUG1

FBB_CLK0

FBB_CLK0*

FBB_CLK1

FBB_CLK1*

FBB_WCK01

FBB_WCK01*

FBB_WCK23

FBB_WCK23*

FBB_WCK45

FBB_WCK45*

FBB_WCK67

FBB_WCK67*

MSI

MSI

MSI

R562

1 2

0402

C704

12

0.1uF

16V

10%

X7R

0402

COMMON

VVVV32010

GND

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

04_MEMORY_ GPU Partition A_B

04_MEMORY_ GPU Partition A_B

04_MEMORY_ GPU Partition A_B

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

Fbb_Cmd<0>

Fbb_Cmd<1>

Fbb_Cmd<2>

Fbb_Cmd<3>

Fbb_Cmd<4>

Fbb_Cmd<5>

Fbb_Cmd<6>

Fbb_Cmd<7>

Fbb_Cmd<8>

Fbb_Cmd<9>

Fbb_Cmd<10>

Fbb_Cmd<11>

Fbb_Cmd<12>

Fbb_Cmd<13>

Fbb_Cmd<14>

Fbb_Cmd<15>

Fbb_Cmd<16>

Fbb_Cmd<17>

Fbb_Cmd<18>

Fbb_Cmd<19>

Fbb_Cmd<20>

Fbb_Cmd<21>

Fbb_Cmd<22>

Fbb_Cmd<23>

Fbb_Cmd<24>

Fbb_Cmd<25>

Fbb_Cmd<26>

Fbb_Cmd<27>

Fbb_Cmd<28>

Fbb_Cmd<29>

Fbb_Cmd<30>

Fbb_Cmd<31>

60.4ohm

DNI

1 %

XXXV32010

FB_CLK

FB_CLK

FB_CLK

FB_CLK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

FB_WCK

IN 4,9,15

MS-V320

MS-V320

MS-V320

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

7

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

8

R566 60.4ohm

1 2

0402

1 %

XXXV32010

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

DNI

OUT 7

OUT 7

OUT 8

OUT 8

OUT 7

OUT 7

OUT 7

OUT 8

OUT 8

OUT 8

OUT 8

FBVDDQ

4 34

4 34

4 34

1

2

3

7

4

10

10

10

A B C D E F G H

MEMORY: FBA Partition 31..0

1

4

4

4

4

4

4

4

4

4

4

4

4

4

4

2

3

4

4

M2C

@memory.u_mem_sd_ddr5 _x32( sym_6 ):page5_ i558

BGA170

M2B

@memory.u_mem_sd_ddr5 _x32( sym_5 ):page5_ i556

COMMON

G3

RAS

L3

CAS

L12

WE

G12

CS

J4

ABI

H4

A0_A10

H5

A1_A9

H11

A2_BA0

H10

A3_BA3

K11

A4_BA2

K10

A5_BA1

K5

A6_A11

K4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

J14

VREFC

FBA_ZQ_1

121ohm

J13

ZQ

COMMON0402

J10

SEN

VVVV32010

C578

10nF

16V

10%

0402

COMMON

VVVV32010

VVVV32010

R565

40.2ohm

1 %

0402

COMMON

0.350 0.140A

12

C573

10nF

6.3V

10%

X5R

0402

COMMON

VVVV32010

GND GND

FBA_VREFC

1.05V

FBA_CMD<12>

FBA_CMD<15>

FBA_CMD<5>

FBA_CMD<0>

FBA_CMD<8>

FBA_CMD<10>

FBA_CMD<11>

FBA_CMD<2>

FBA_CMD<1>

FBA_CMD<3>

FBA_CMD<4>

FBA_CMD<7>

FBA_CMD<6>

FBA_CMD<9>

FBA_CMD<13>

FBA_CMD<14>

R204

1 2

VVVV32010

OUT 6

1 %

FBA_CMD<3>

3

FBA_CMD<3>

FBA_CMD<0>

FBA_CMD<10>

FBA_CMD<15>

FBA_CMD<7>

FBA_CMD<5>

FBA_CMD<4>

FBA_CMD<13>

FBA_CMD<14>

FBA_CMD<12>

FBA_CMD<11>

FBA_CMD<8>

FBA_CMD<9>

FBA_CMD<6>

FBA_CMD<2>

FBA_CMD<1>

0.350 1.05V

FBA_VREF_Q

FBA_D<16>

FBA_D<17>

FBA_D<18>

FBA_D<19>

FBA_D<20>

FBA_D<21>

FBA_D<22>

FBA_D<23>

FBA_D<24>

FBA_D<25>

FBA_D<26>

FBA_D<27>

FBA_D<28>

FBA_D<29>

FBA_D<30>

FBA_D<31>

GPIO10_FBVREF_SEL

VVVV32010

M2A

@memory.u_mem_sd_ddr5 _x32( sym_3 ):page5_ i507

BGA170

COMMON

NORMAL

V11

DQ16

V13

DQ17

T11

DQ18

T13

DQ19

N11

DQ20

N13

DQ21

M11

DQ22

M13

DQ23

R13

EDC2

P13

DBI2

VREFD

x32

V4

DQ24

V2

DQ25

T4

DQ26

T2

DQ27

N4

DQ28

N2

DQ29

M4

DQ30

M2

DQ31

R2

EDC3

P2

DBI3

P4

WCK23

P5

WCK23

Use low VGSth part for Pascal

AO3420

1G1D1 S

x16

NC

NC

NC

NC

NC

NC

NC

NC

NC

G

1

V10

VVVV32010

3

D

Q515

@discrete.q_fet_n_enh(s ym_2) :page5_i506

SOT23_1 G1D 1S

COMMON

S

2

GND

M2D

@memory.u_mem_sd_ddr5 _x32( sym_1 ):page5_ i468

BGA170

COMMON

NORMAL

FBA_D<0>

A4

FBA_WCK01

FBA_WCK01*

FBA_D<1>

FBA_D<2>

FBA_D<3>

FBA_D<4>

FBA_D<5>

FBA_D<6>

FBA_D<7>

FBA_EDC<0>

FBA_DBI<0>

FBA_D<8>

FBA_D<9>

FBA_D<10>

FBA_D<11>

FBA_D<12>

FBA_D<13>

FBA_D<14>

FBA_D<15>

DQ0

A2

DQ1

B4

DQ2

B2

DQ3

E4

DQ4

E2

DQ5

F4

DQ6

F2

DQ7

C2

EDC0

D2

DBI0

A10

VREFD

x16

x32

A11

DQ8

NC

A13

DQ9

NC

B11

DQ10

NC

B13

DQ11

NC

E11

DQ12

E13

DQ13

NC

F11

DQ14

NC

F13

DQ15

NC

C13

EDC1

GND

D13

DBI1

NC

D4

WCK01

D5

WCK01

VVVV32010

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

16

Fba_D<16>

17

Fba_D<17>

18

Fba_D<18>

19

Fba_D<19>

20

Fba_D<20>

21

Fba_D<21>

22

Fba_D<22>

23

Fba_D<23>

FBA_EDC<2>

OUT4

FBA_DBI<2>

OUT4

24

Fba_D<24>

25

Fba_D<25>

26

Fba_D<26>

27

Fba_D<27>

Fba_D<28>

29

Fba_D<29>

30

Fba_D<30>

31

Fba_D<31>

FBA_EDC<3>

OUT4

FBA_DBI<3>

OUT4

IN4

IN4

FBA_WCK23

FBA_WCK23*

IN7,10,21

0

Fba_D<0>

1

Fba_D<1>

2

Fba_D<2>

3

Fba_D<3>

4

Fba_D<4>

5

Fba_D<5>

6

Fba_D<6>

7

Fba_D<7>

OUT4

OUT4

8

Fba_D<8>

9

Fba_D<9>

10

Fba_D<10>

11

Fba_D<11>

Fba_D<12>

13

Fba_D<13>

14

Fba_D<14>

15

Fba_D<15>

FBA_EDC<1>

OUT4

FBA_DBI<1>

OUT4

IN4

IN4

4

FBA_CMD<0>

0

4

FBA_CMD<10>

10

4

FBA_CMD<15>

15

4

FBA_CMD<7>

7

4

FBA_CMD<5>

4

FBA_CMD<4>

4

4

FBA_CMD<13>

13

4

FBA_CMD<14>

14

4

FBA_CMD<12>

12

4

FBA_CMD<11>

11

4

FBA_CMD<8>

8

4

FBA_CMD<9>

9

4

FBA_CMD<6>

6

4

FBA_CMD<2>

4

FBA_CMD<1>

1

4

FBA_CLK0

IN4

FBA_CLK0*

IN4

VVVV32010

R563

40.2ohm

1 %

0402

COMMON

FBA_CLK0_CM

12

FBVDDQ

VVVV32010

GND

R659

549ohm

1 %

0402

COMMON

R181

R658

1.33k

931ohm

1 %

1 %

0402

0402

COMMON

COMMON

VVVV32010

VVVV32010

GND

COMMON

Normal

J1

MF_VSS/SOE*

add 1k to VSS

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

VVVV32010

GND

FBVDDQ

C10

VDD

C5

VDD

D11

VDD

G1

VDD

G11

VDD

G14

VDD

G4

VDD

L1

VDD

L11

VDD

L14

VDD

L4

VDD

P11

VDD

R10

VDD

R5

VDD

B1

VDDQ

B12

VDDQ

B14

VDDQ

B3

VDDQ

D1

VDDQ

D12

VDDQ

D14

VDDQ

D3

VDDQ

E10

VDDQ

E5

VDDQ

F1

VDDQ

F12

VDDQ

F14

VDDQ

F3

VDDQ

G13

VDDQ

G2

VDDQ

H12

VDDQ

H3

VDDQ

K12

VDDQ

K3

VDDQ

L13

VDDQ

L2

VDDQ

M1

VDDQ

M12

VDDQ

M14

VDDQ

M3

VDDQ

N10

VDDQ

N5

VDDQ

P1

VDDQ

P12

VDDQ

P14

VDDQ

P3

VDDQ

T1

VDDQ

T12

VDDQ

T14

VDDQ

T3

VDDQ

1

2

3

4

FBVDDQ

C147

12

C140

12

C742

12

C694

12

C738

12

C693

12

C181

12

C739

12

C712

12

C703

1uF

1uF

1uF

1uF

1uF

6.3V

6.3V

6.3V

X5R

X5R

X5R

0402

0402

0402

COMMON

COMMON

COMMON

VVVV32010

VVVV32010

VVVV32010

C621

12

C159

12

C554

12

4.7uF

4.7uF

4.7uF

6.3V

6.3V

6.3V

20%

20%

20%

X5R

X5R

X5R

0603

0603

0603

COMMON

COMMON

5

ALL NVIDIA DESIGN SPECIFICAT IONS, REFERENCE SP ECIFICATIONS, REFERENCE BOARDS, FILES, DRAWI NGS, DIAGNOSTICS, LIST S AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEP ARATEL Y, 'MATERIALS') ARE BE ING PROVIDED 'AS IS'. THE MAT ERIALS MAY

CONTAINK NOWNA ND UNKNOWN VIOLATIONS OR DEVIA TIONS OFI NDUSTRY ST ANDARDS AND SP ECIFICATIONS. NVIDIA MAKESNO WARRA NTIES, E XPRESSE D, IMPLIED, STAT UTORY OR OTHERWISE WITH RESPECT TOT HE MATERIALS OROTHERWIS E, AND EXP RESSLY DISCLA IMS ALL

IMPLIED WARRANTIES INCLUDING, WIT HOUT LIMITATION, T HE WARRANT IES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNE SS FOR A PARTICULA R PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, T RADE PRACT ICE, OR INDUSTRY ST ANDARDS.

VVVV32010

COMMON

VVVV32010

VVVV32010

1uF

6.3V

6.3V

6.3V

X5R

X5R

X5R

0402

0402

0402

COMMON

COMMON

COMMON

VVVV32010

VVVV32010

VVVV32010

C158

12

C162

12

4.7uF

10uF

6.3V

6.3V

20%

20%

X5R

X5R

0603

0805

COMMON

COMMON

VVVV32010

VVVV32010

12

1uF

1uF

1uF

1uF

6.3V

6.3V

6.3V

6.3V

X5R

X5R

X5R

X5R

0402

0402

0402

0402

COMMON

COMMON

COMMON

COMMON

VVVV32010

VVVV32010

VVVV32010

VVVV32010

C550

12

10uF

6.3V

20%

X5R

0805

COMMON

VVVV32010

C173

12

C176

12

47uF

47uF

GND

4V

4V

20%

20%

X5R

X5R

COMMON

COMMON

VVVV32010

VVVV32010

GND

C E

4

5

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

MS-V320

MS-V320

MSI

MSI

MSI

FDBA

G

MS-V320

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

05_MEMORY_ FBA[ 31_0]

05_MEMORY_ FBA[ 31_0]

05_MEMORY_ FBA[ 31_0]

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

Sheet ofDate:

5 34

Sheet ofDate:

5 34

Sheet ofDate:

5 34

H

10

10

10

A B C D E F G H

MEMORY: FBA Partition 63..32

1

2

3

4

4

4

4

4

4

4

4

4

4

4

4

4

FBA_WCK45

FBA_WCK45*

12

4

4

4

VVVV32010

VVVV32010

C567

12

C566

C646

12

1uF

1uF

1uF

6.3V

6.3V

6.3V

10%

10%

10%

X5R

X5R

X5R

0402

0402

0402

COMMON

COMMON

COMMON

C754

12

C130

12

4.7uF

4.7uF

6.3V

6.3V

20%

20%

0603

0603

COMMON

COMMON

VVVV32010

VVVV32010

4

IN4

IN4

FBVDDQ

VVVV32010

C665

12

4.7uF

6.3V

20%

5

ALL NVIDIA DESIGN SPECIFICAT IONS, REFERENCE SP ECIFICATIONS, REFERENCE BOARDS, FILES, DRAWI NGS, DIAGNOSTICS, LIST S AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEP ARATEL Y, 'MATERIALS') ARE BE ING PROVIDED 'AS IS'. THE MAT ERIALS MAY

CONTAINK NOWNA ND UNKNOWN VIOLATIONS OR DEVIA TIONS OFI NDUSTRY ST ANDARDS AND SP ECIFICATIONS. NVIDIA MAKESNO WARRA NTIES, E XPRESSE D, IMPLIED, STAT UTORY OR OTHERWISE WITH RESPECT TOT HE MATERIALS OROTHERWIS E, AND EXP RESSLY DISCLA IMS ALL

IMPLIED WARRANTIES INCLUDING, WIT HOUT LIMITATION, T HE WARRANT IES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNE SS FOR A PARTICULA R PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, T RADE PRACT ICE, OR INDUSTRY ST ANDARDS.

0603

COMMON

VVVV32010

32

Fba_D<32>

33

Fba_D<33>

34

Fba_D<34>

35

Fba_D<35>

36

Fba_D<36>

37

Fba_D<37>

38

Fba_D<38>

39

Fba_D<39>

FBA_EDC<4>

OUT4

FBA_DBI<4>

OUT4

40

Fba_D<40>

41

Fba_D<41>

42

Fba_D<42>

43

Fba_D<43>

Fba_D<44>

45

Fba_D<45>

46

Fba_D<46>

47

Fba_D<47>

FBA_EDC<5>

OUT4

FBA_DBI<5>

OUT4

VVVV32010

VVVV32010

VVVV32010

C182

12

C595

12

C619

12

1uF

1uF

1uF

6.3V

6.3V

6.3V

10%

10%

10%

X5R

X5R

X5R

0402

0402

0402

COMMON

COMMON

COMMON

C674

12

C129

12

4.7uF

10uF

6.3V

6.3V

20%

20%

0603

0805

COMMON

COMMON

VVVV32010

VVVV32010

M503D

@memory.u_mem_sd_ddr5 _x32( sym_1 ):page6_ i380

BGA170

COMMON

NORMAL

FBA_D<32>

A4

DQ0

A2

FBA_D<33>

DQ1

FBA_D<34>

B4

DQ2

FBA_D<35>

B2

DQ3

FBA_D<36>

E4

DQ4

FBA_D<37>

E2

DQ5

FBA_D<38>

F4

DQ6

FBA_D<39>

F2

DQ7

C2

EDC0

D2

DBI0

A10

VREFD

x16

x32

FBA_D<40>

A11

DQ8

FBA_D<41>

FBA_D<42>

FBA_D<43>

FBA_D<44>

FBA_D<45>

FBA_D<46>

FBA_D<47>

VVVV32010

C154

12

1uF

6.3V

10%

X5R

0402

COMMON

12

NC

A13

DQ9

NC

B11

DQ10

NC

B13

DQ11

NC

E11

DQ12

E13

DQ13

NC

F11

DQ14

NC

F13

DQ15

NC

C13

EDC1

GND

D13

DBI1

NC

D4

WCK01

D5

WCK01

VVVV32010

VVVV32010

VVVV32010

VVVV32010

C150

12

C620

12

C151

12

1uF

1uF

1uF

6.3V

6.3V

6.3V

10%

10%

10%

X5R

X5R

X5R

0402

0402

0402

COMMON

COMMON

COMMON

C569

12

C653

C145

12

10uF

6.3V

20%

0805

COMMON

VVVV32010

47uF

47uF

4V

4V

20%

20%

0805

0805

COMMON

COMMON

VVVV32010

VVVV32010

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

GND

C E

48

Fba_D<48>

49

Fba_D<49>

50

Fba_D<50>

51

Fba_D<51>

52

Fba_D<52>

53

Fba_D<53>

54

Fba_D<54>

55

Fba_D<55>

FBA_EDC<6>

OUT4

FBA_DBI<6>

OUT4

56

Fba_D<56>

57

Fba_D<57>

58

Fba_D<58>

59

Fba_D<59>

Fba_D<60>

61

Fba_D<61>

62

Fba_D<62>

63

Fba_D<63>

FBA_EDC<7>

OUT4

FBA_DBI<7>

OUT4

FBA_WCK67

IN4

FBA_WCK67*

IN4

FBA_D<48>

FBA_D<49>

FBA_D<50>

FBA_D<51>

FBA_D<52>

FBA_D<53>

FBA_D<54>

FBA_D<55>

FBA_D<56>

FBA_D<57>

FBA_D<58>

FBA_D<59>

FBA_D<60>

FBA_D<61>

FBA_D<62>

FBA_D<63>

M503A

@memory.u_mem_sd_ddr5 _x32( sym_3 ):page6_ i420

BGA170

COMMON

NORMAL

V11

DQ16

V13

DQ17

T11

DQ18

T13

DQ19

N11

DQ20

N13

DQ21

M11

DQ22

M13

DQ23

R13

EDC2

P13

DBI2

VREFD

x16

x32

V4

DQ24

NC

V2

DQ25

NC

T4

DQ26

NC

T2

DQ27

NC

N4

DQ28

N2

DQ29

NC

M4

DQ30

NC

M2

DQ31

NC

R2

EDC3

NC

P2

DBI3

NC

P4

WCK23

P5

WCK23

VVVV32010

1

2

FBA_CMD<19>

19

FBA_CMD<19>

FBA_CMD<16>

FBA_CMD<26>

FBA_CMD<31>

FBA_CMD<23>

FBA_CMD<21>

FBA_CMD<20>

FBA_CMD<29>

FBA_CMD<30>

FBA_CMD<28>

FBA_CMD<27>

FBA_CMD<24>

FBA_CMD<25>

FBA_CMD<22>

FBA_CMD<18>

FBA_CMD<17>

V10

5

4

FBA_CMD<16>

4

FBA_CMD<26>

26

4

FBA_CMD<31>

31

4

FBA_CMD<23>

23

4

FBA_CMD<21>

21

4

FBA_CMD<20>

20

4

FBA_CMD<29>

29

4

FBA_CMD<30>

30

4

FBA_CMD<28>

4

FBA_CMD<27>

27

4

FBA_CMD<24>

24

4

FBA_CMD<25>

25

4

FBA_CMD<22>

22

4

FBA_CMD<18>

18

4

FBA_CMD<17>

17

4

FBA_CLK1

IN4

FBA_CLK1*

IN4

C713

12

10nF

6.3V

10%

X5R

0402

COMMON

VVVV32010

GND GND

FBA_CMD<28>

FBA_CMD<31>

FBA_CMD<21>

FBA_CMD<16>

FBA_CMD<24>

FBA_CMD<26>

FBA_CMD<27>

FBA_CMD<18>

FBA_CMD<17>

FBA_CMD<19>

FBA_CMD<20>

FBA_CMD<23>

FBA_CMD<22>

FBA_CMD<25>

FBA_CMD<29>

FBA_CMD<30>

R609

R600

40.2ohm

40.2ohm

1 %

1 %

VVVV32010

0402

0402

COMMON

COMMON

FBA_CLK1_CM

VVVV32010

C726

12

10nF

16V

X7R

0402

COMMON

VVVV32010

GND

R619

121ohm

1 2

COMMON

0402

1 %

VVVV32010

FBA_ZQ_2_B

FBA_VREFC

M503B

BGA170

COMMON

G3

RAS

L3

CAS

L12

WE

G12

CS

J4

ABI

H4

A0_A10

H5

A1_A9

H11

A2_BA0

H10

A3_BA3

K11

A4_BA2

K10

A5_BA1

K5

A6_A11

K4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

J14

VREFC

J13

ZQ

J10

SEN

VVVV32010

FDBA

M503C

@memory.u_mem_sd_ddr5 _x32( sym_6 ):page6_ i479

COMMON

Normal

J1

MF_VSS/SOE*

add 1k to VSS

B10

VSS

B5

VSS

D10

VSS

G10

VSS

G5

VSS

H1

VSS

H14

VSS

K1

VSS

K14

VSS

L10

VSS

L5

VSS

P10

VSS

T10

VSS

T5

VSS

A1

VSSQ

A12

VSSQ

A14

VSSQ

A3

VSSQ

C1

VSSQ

C11

VSSQ

C12

VSSQ

C14

VSSQ

C3

VSSQ

C4

VSSQ

E1

VSSQ

E12

VSSQ

E14

VSSQ

E3

VSSQ

F10

VSSQ

F5

VSSQ

H13

VSSQ

H2

VSSQ

K13

VSSQ

K2

VSSQ

M10

VSSQ

M5

VSSQ

N1

VSSQ

N12

VSSQ

N14

VSSQ

N3

VSSQ

R1

VSSQ

R11

VSSQ

R12

VSSQ

R14

VSSQ

R3

VSSQ

R4

VSSQ

V1

VSSQ

V12

VSSQ

V14

VSSQ

V3

VSSQ

VVVV32010

GND

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

Wednesday, November 12, 201 4

G

FBVDDQ

C10

VDD

C5

VDD

D11

VDD

G1

VDD

G11

VDD

G14

VDD

G4

VDD

L1

VDD

L11

VDD

L14

VDD

L4

VDD

P11

VDD

R10

VDD

R5

VDD

B1

VDDQ

B12

VDDQ

B14

VDDQ

B3

VDDQ

D1

VDDQ

D12

VDDQ

D14

VDDQ

D3

VDDQ

E10

VDDQ

E5

VDDQ

F1

VDDQ

F12

VDDQ

F14

VDDQ

F3

VDDQ

G13

VDDQ

G2

VDDQ

H12

VDDQ

H3

VDDQ

K12

VDDQ

K3

VDDQ

L13

VDDQ

L2

VDDQ

M1

VDDQ

M12

VDDQ

M14

VDDQ

M3

VDDQ

N10

VDDQ

N5

VDDQ

P1

VDDQ

P12

VDDQ

P14

VDDQ

P3

VDDQ

T1

VDDQ

T12

VDDQ

T14

VDDQ

T3

VDDQ

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

MIC RO-STA R INT 'L CO .,LTD

MS-V320

MS-V320

MS-V320

06_MEMORY_ FBA[ 63_32]

06_MEMORY_ FBA[ 63_32]

06_MEMORY_ FBA[ 63_32]

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

6 34

6 34

6 34

3

4

5

10

10

10

A B C D E F G H

MEMORY: FBB Partition 31..0

1

2

3

4

Fbb_D<0>

4

Fbb_D<1>

4

Fbb_D<2>

4

Fbb_D<3>

4

Fbb_D<4>

4

Fbb_D<5>

4

Fbb_D<6>

4

Fbb_D<7>

4

Fbb_D<8>

4

Fbb_D<9>

4

Fbb_D<10>

4

Fbb_D<11>

4

Fbb_D<12>

4

Fbb_D<13>

4

Fbb_D<14>

4

Fbb_D<15>

IN4

IN4

M3C

@memory.u_mem_sd_ddr5 _x32( sym_6 ):page7_ i570

M3B

@memory.u_mem_sd_ddr5 _x32( sym_5 ):page7_ i567

BGA170

COMMON

G3

RAS

L3

CAS

L12

WE

G12

CS

J4

ABI

H4

A0_A10

H5

A1_A9

H11

A2_BA0

H10

A3_BA3

K11

A4_BA2

K10

A5_BA1

K5

A6_A11

K4

A7_A8

J5

RFU_A12

J2

RESET

J3

CKE

J12

CLK

J11

CLK

A5

NC_RFU_A5

V5

NC_RFU_V5

J14

VREFC

FBB_ZQ_1

J13

ZQ

COMMON

J10

SEN

VVVV32010

C510

10nF

16V

10%

X7R

0402

COMMON

VVVV32010

GND GND

VVVV32010

R533

40.2ohm

1 %

0402

COMMON

0.350 0.140A

C509

12

10nF

6.3V

10%

X5R

0402

COMMON

VVVV32010

FBB_VREFC

1.05V

FBB_CMD<12>

FBB_CMD<15>

FBB_CMD<5>

FBB_CMD<0>

FBB_CMD<8>

FBB_CMD<10>

FBB_CMD<11>

FBB_CMD<2>

FBB_CMD<1>

FBB_CMD<3>

FBB_CMD<4>

FBB_CMD<7>

FBB_CMD<6>

FBB_CMD<9>

FBB_CMD<13>

FBB_CMD<14>

R216 121ohm

1 2

0402

VVVV32010

OUT 8

1 %

Fbb_Cmd<3>

4

Fbb_Cmd<0>

4

Fbb_Cmd<10>

M3D

BGA170

COMMON

NORMAL

FBB_D<0>

A4

0

1

2

3

4

6

7

FBB_EDC<0>

OUT4

FBB_DBI<0>

OUT4

8

10

11

12

13

14

15

FBB_EDC<1>

OUT4

FBB_DBI<1>

OUT4

FBB_WCK01

FBB_WCK01*

DQ0

FBB_D<1>

A2

DQ1

FBB_D<2>

B4

DQ2

FBB_D<3>

B2

DQ3

FBB_D<4>

E4

DQ4

FBB_D<5>

E2

DQ5

FBB_D<6>

F4

DQ6

FBB_D<7>

F2

DQ7

C2

EDC0

D2

DBI0

VREFD

x16

x32

FBB_D<8>

A11

DQ8

FBB_D<9>

FBB_D<10>

FBB_D<11>

FBB_D<12>

FBB_D<13>

FBB_D<14>

FBB_D<15>

NC

A13

DQ9

B11

DQ10

NC

B13

DQ11

NC

E11

DQ12

NC

E13

DQ13

NC

F11

DQ14

NC

F13

DQ15

NC

C13

EDC1

GND

D13

DBI1

NC

D4

WCK01

D5

WCK01

VVVV32010

4

4

4

4

4

4

4

4

A10

4

4

4

4

4

4

4

4

IN4

IN4

Fbb_D<16>

Fbb_D<17>

Fbb_D<18>

Fbb_D<19>

Fbb_D<20>

Fbb_D<21>

Fbb_D<22>

Fbb_D<23>

Fbb_D<24>

Fbb_D<25>

Fbb_D<26>

Fbb_D<27>

Fbb_D<28>

Fbb_D<29>

Fbb_D<30>

Fbb_D<31>

16

17

18

19

20

22

23

FBB_EDC<2>

OUT4

FBB_DBI<2>

OUT4

24

26

27

28

29

30

31

FBB_EDC<3>

OUT4

FBB_DBI<3>

OUT4