Motorola MTB20N20E Datasheet

1

Motorola TMOS Power MOSFET Transistor Device Data

" !

N–Channel Enhancement–Mode Silicon Gate

The D2PAK package has the capability of housing a larger die

than any existing surface mount package which allows it to be used

in applications that require the use of surface mount components

with higher power and lower R

DS(on)

capabilities. This advanced

TMOS E –FET i s designed t o withstand h igh e nergy i n the

avalanche and commutation modes. The new energy efficient

design also offers a drain–to–source diode with a fast recovery

time. Designed for low voltage, high speed switching applications in

power supplies, converters and PWM motor controls, these

devices are particularly well suited for bridge circuits where diode

speed and commutating safe operating areas are critical and offer

additional safety margin against unexpected voltage transients.

• Avalanche Energy Specified

• Source–to–Drain Diode Recovery Time Comparable to a

Discrete Fast Recovery Diode

• Diode is Characterized for Use in Bridge Circuits

• I

DSS

and V

DS(on)

Specified at Elevated Temperature

• Short Heatsink Tab Manufactured — Not Sheared

• Specially Designed Leadframe for Maximum Power Dissipation

• Available in 24 mm 13–inch/800 Unit Tape & Reel, Add T4

Suffix to Part Number

MAXIMUM RATINGS

(TC = 25°C unless otherwise noted)

Rating Symbol Value Unit

Drain–Source Voltage V

DSS

200 Vdc

Drain–Gate Voltage (RGS = 1.0 MΩ) V

DGR

200 Vdc

Gate–Source Voltage — Continuous

Gate–Source Voltage — Non–Repetitive (tp ≤ 10 ms)

V

GS

V

GSM

± 20

± 40

Vdc

Vpk

Drain Current — Continuous

Drain Current — Continuous @ 100°C

Drain Current — Single Pulse (tp ≤ 10 µs)

I

D

I

D

I

DM

20

12

60

Adc

Apk

Total Power Dissipation

Derate above 25°C

Total Power Dissipation @ TA = 25°C, when mounted with the minimum recommended pad size

P

D

125

1.0

2.5

Watts

W/°C

Watts

Operating and Storage Temperature Range TJ, T

stg

– 55 to 150 °C

Single Pulse Drain–to–Source Avalanche Energy — Starting TJ = 25°C

(VDD = 25 Vdc, VGS = 10 Vdc, IL = 20 Apk, L = 3.0 mH, RG = 25 Ω)

E

AS

600 mJ

Thermal Resistance — Junction to Case

Thermal Resistance — Junction to Ambient

Thermal Resistance — Junction to Ambient, when mounted with the minimum recommended pad size

R

θJC

R

θJA

R

θJA

1.0

62.5

50

°C/W

Maximum Lead Temperature for Soldering Purposes, 1/8″ from case for 10 seconds T

L

260 °C

Designer’s Data for “Worst Case” Conditions — The Designer’s Data Sheet permits the design of most circuits entirely from the information presented. SOA Limit

curves — representing boundaries on device characteristics — are given to facilitate “worst case” design.

E–FET and Designer’s are trademarks of Motorola, Inc. TMOS is a registered trademark of Motorola, Inc.

Thermal Clad is a trademark of the Bergquist Company.

Preferred devices are Motorola recommended choices for future use and best overall value.

REV 2

Order this document

by MTB20N20E/D

SEMICONDUCTOR TECHNICAL DATA

TMOS POWER FET

20 AMPERES

200 VOLTS

R

DS(on)

= 0.16 OHM

Motorola Preferred Device

CASE 418B–02, Style 2

D2PAK

D

S

G

Motorola, Inc. 1995

MTB20N20E

2

Motorola TMOS Power MOSFET Transistor Device Data

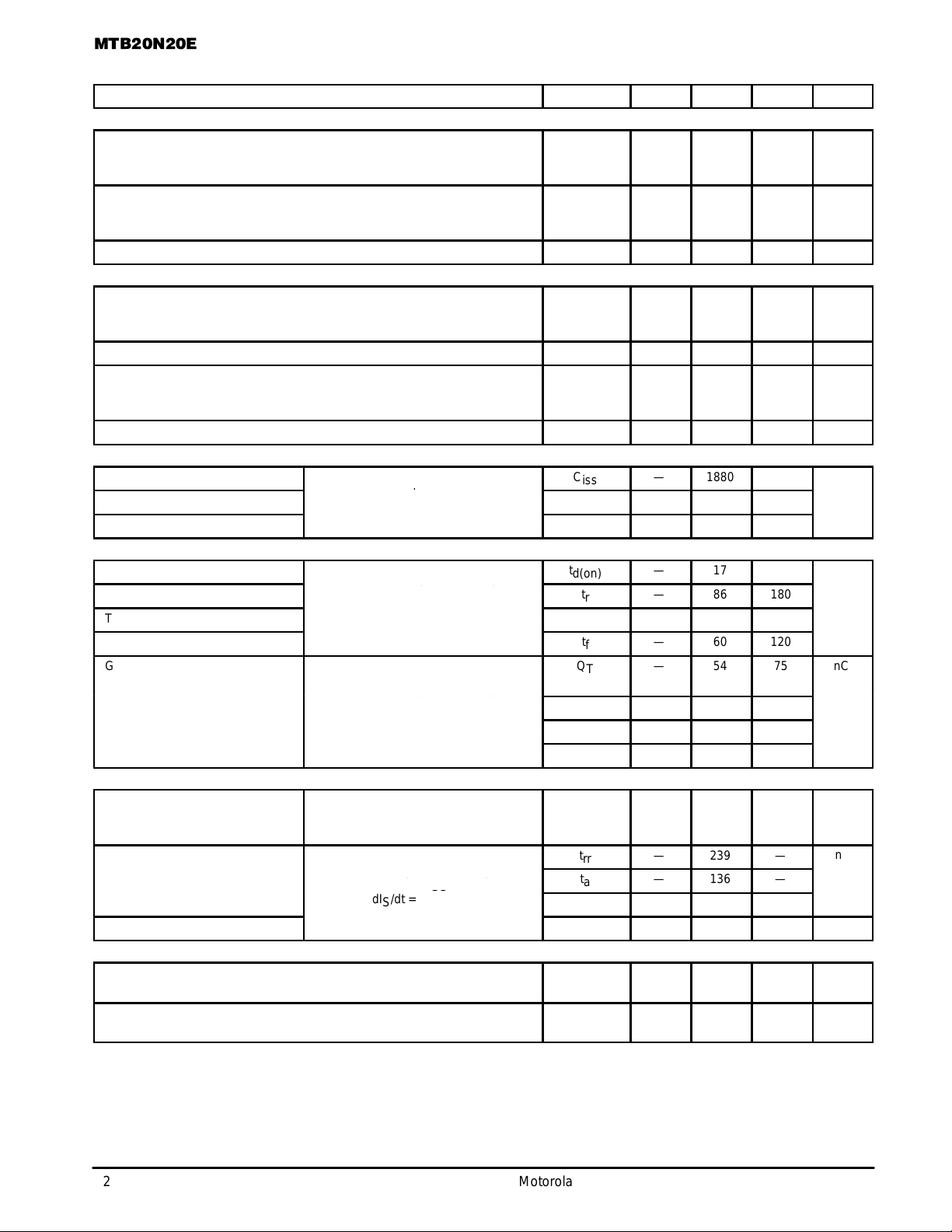

ELECTRICAL CHARACTERISTICS

(TJ = 25°C unless otherwise noted)

Characteristic Symbol Min Typ Max Unit

OFF CHARACTERISTICS

Drain–Source Breakdown Voltage

(VGS = 0 Vdc, ID = 250 µAdc)

Temperature Coefficient (Positive)

V

(BR)DSS

200

—

—

263

—

—

Vdc

mV/°C

Zero Gate Voltage Drain Current

(VDS = 200 Vdc, VGS = 0 Vdc)

(VDS = 200 Vdc, VGS = 0 Vdc, TJ = 125°C)

I

DSS

—

—

—

—

10

100

µAdc

Gate–Body Leakage Current (VGS = ± 20 Vdc, VDS = 0) I

GSS

— — 100 nAdc

ON CHARACTERISTICS (1)

Gate Threshold Voltage

(VDS = VGS, ID = 250 µAdc)

Temperature Coefficient (Negative)

V

GS(th)

2.0

—

—

7.0

4.0

—

Vdc

mV/°C

Static Drain–Source On–Resistance (VGS = 10 Vdc, ID = 10 Adc) R

DS(on)

— 0.12 0.16 Ohm

Drain–Source On–Voltage (VGS = 10 Vdc)

(ID = 20 Adc)

(ID = 10 Adc, TJ = 125°C)

V

DS(on)

—

—

—

—

3.84

3.36

Vdc

Forward Transconductance (VDS = 13 Vdc, ID = 10 Adc) g

FS

8.0 11 — mhos

DYNAMIC CHARACTERISTICS

Input Capacitance

C

iss

— 1880 2700 pF

Output Capacitance

(VDS = 25 Vdc, VGS = 0 Vdc,

f = 1.0 MHz)

C

oss

— 378 535

Reverse Transfer Capacitance

f = 1.0 MHz)

C

rss

— 68 100

SWITCHING CHARACTERISTICS (2)

Turn–On Delay Time

t

d(on)

— 17 40 ns

Rise Time

t

r

— 86 180

Turn–Off Delay Time

VGS = 10 Vdc,

RG = 9.1 Ω)

t

d(off)

— 50 100

Fall Time

G

= 9.1 Ω)

t

f

— 60 120

Gate Charge

(See Figure 8)

Q

T

— 54 75 nC

Q

1

— 12 —

VGS = 10 Vdc)

Q

2

— 24 —

Q

3

— 22 —

SOURCE–DRAIN DIODE CHARACTERISTICS

Forward On–Voltage (1)

(IS = 20 Adc, VGS = 0 Vdc)

(IS = 20 Adc, VGS = 0 Vdc, TJ = 125°C)

V

SD

—

—

1.0

0.82

1.35

—

Vdc

t

rr

— 239 —

(See Figure 14)

S

= 20 Adc, VGS = 0 Vdc,

t

a

— 136 —

(IS = 20 Adc, VGS = 0 Vdc,

dIS/dt = 100 A/µs)

t

b

— 103 —

Reverse Recovery Stored Charge Q

RR

— 2.09 — µC

INTERNAL PACKAGE INDUCTANCE

Internal Drain Inductance

(Measured from the drain lead 0.25″ from package to center of die)

L

D

— 4.5 — nH

Internal Source Inductance

(Measured from the source lead 0.25″ from package to source bond pad)

L

S

— 7.5 — nH

(1) Pulse Test: Pulse Width ≤ 300 µs, Duty Cycle ≤ 2%.

(2) Switching characteristics are independent of operating junction temperature.

Reverse Recovery Time

(VDD = 100 Vdc, ID = 20 Adc,

(VDS = 160 Vdc, ID = 20 Adc,

(I

ns

MTB20N20E

3

Motorola TMOS Power MOSFET Transistor Device Data

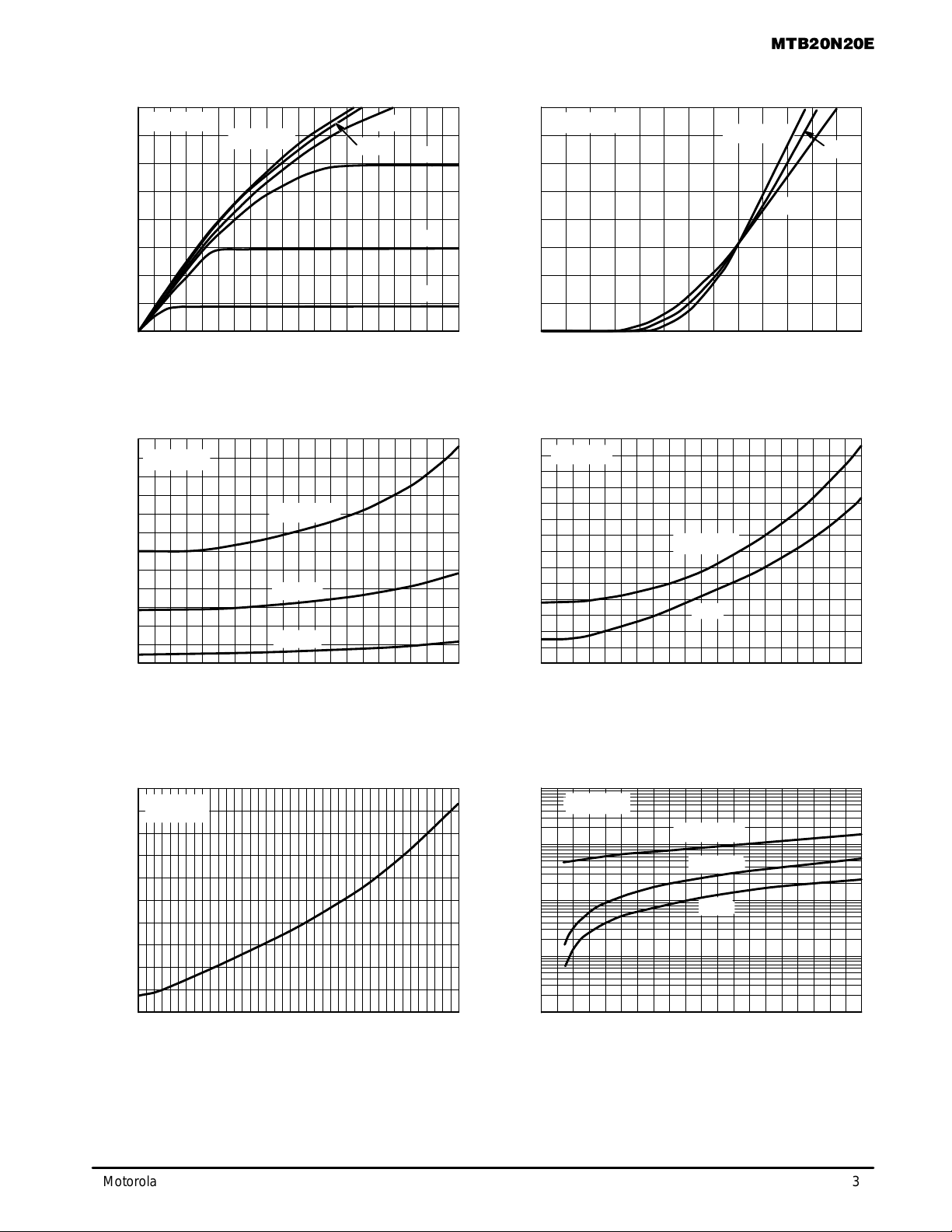

TYPICAL ELECTRICAL CHARACTERISTICS

R

DS(on)

, DRAIN–TO–SOURCE RESISTANCE

(NORMALIZED)

R

DS(on)

, DRAIN–TO–SOURCE RESISTANCE (OHMS)

R

DS(on)

, DRAIN–TO–SOURCE RESISTANCE (OHMS)

0 1 3 5 7 9

0

10

20

30

40

VDS, DRAIN–TO–SOURCE VOLTAGE (VOLTS)

Figure 1. On–Region Characteristics

I

D

, DRAIN CURRENT (AMPS)

2.0 8.5

0

10

20

30

40

I

D

, DRAIN CURRENT (AMPS)

VGS, GATE–TO–SOURCE VOLTAGE (VOLTS)

Figure 2. Transfer Characteristics

0 4 16 24 36 40

0.05

0.10

0.25

0.30

0.35

0 4 12 20 32 40

0.10

0.11

0.13

0.15

0.17

ID, DRAIN CURRENT (AMPS)

Figure 3. On–Resistance versus Drain Current

and Temperature

ID, DRAIN CURRENT (AMPS)

Figure 4. On–Resistance versus Drain Current

and Gate Voltage

–50

0.4

1.2

1.6

2.0

2.4

0 200

1

10

100

1000

10000

TJ, JUNCTION TEMPERATURE (

°

C)

Figure 5. On–Resistance Variation with

Temperature

VDS, DRAIN–TO–SOURCE VOLTAGE (VOLTS)

Figure 6. Drain–To–Source Leakage

Current versus Voltage

I

DSS

, LEAKAGE (nA)

VGS = 10 V

ID = 10 A

–25 0 25 50 75 100 125 150

TJ = 25°C

VGS = 10 V

VDS ≥ 10 V

TJ = –55°C

25°C

100°C

TJ = 25°C

VGS = 0 V

VGS = 10 V

2 4 6 8 10

9 V

6 V

7 V

8 V

35

25

15

5

2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 6.5 7.0 7.5 8.0

TJ = 100°C

25°C

–55°C

0.15

0.20

8 12 20 28 32

0.16

0.14

0.12

8 16 24 28 36

0.8

25°C

100°C

50 100 150

TJ = 125°C

VGS = 10 V

15 V

5 V

Loading...

Loading...