Page 1

MPC750UMAD/AD

1/1999

Rev. 1

ª

Errata to

MPC750 RISC Microprocessor UserÕs

Manual

This errata describes corrections to the MPC750 RISC Microprocessor

UserÕs Manual

described in

convenience, the section number and page number of the errata item in the

userÕs manual are provided.

To locate any published updates for this document, refer to the world-wide

web at http://www.mot.com/powerpc.

Section/Page Changes

2.1.1, 2-7 The implementation note for the decrementer register

2.1.2.2, 2-12 In Table 2-4, replace the description of HID0[DBP]

. These corrections also apply to the MPC740, which is

MPC750 RISC Microprocessor UserÕs Manual . For

(DEC) should read as follows:

In the MPC750 the decrementer register is decremented

and the time base is incremented at a speed that is

one-fourth the speed of the bus clock.

(bit 1), with the following:

This document contains information on a new product under development by Motorola and IBM. Motorola and IBM reserve the right to

discontinue this product without notice.

Motorola Inc., 1999. All rights reserved.

©

change or

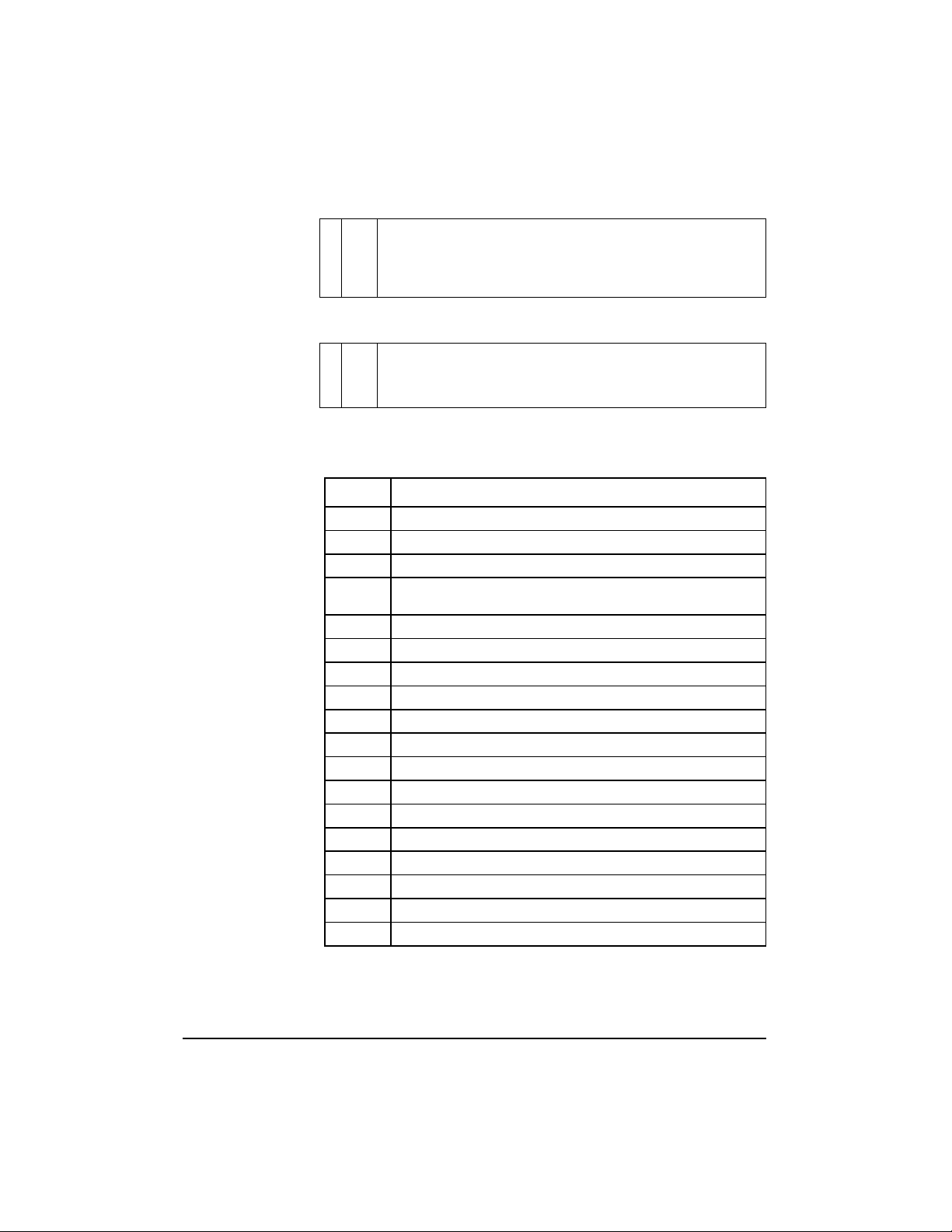

Page 2

2

1 DBP Disable 60x bus address and data parity generation.

0 The system generates address and data parity.

1 Parity generation is disabled and parity signals are driven to 0 during bus

operations. When parity generation is disabled, all parity checking should

also be disabled and parity signals need not be connected.

Replace the description of HID0[BTIC] (bit 26), with the following:

26 BTIC BTIC enable. Used to enable use of the 64-entry branch instruction cache.

0 The BTIC contents are invalidated and the BTIC behaves as if it were

empty. New entries cannot be added until the BTIC is enabled.

1 The BTIC is enabled and new entries can be added.

2.1.2.4.5, 2-18 Replace Table 2-11 with the following:

Table 2-11. PMC2 EventsÑMMCR0[26Ð31] Select Encodings

Encoding Description

00 0000 Register holds current value.

00 0001 Counts processor cycles.

00 0010 Counts completed instructions. Does not include folded branches.

00 0011 Counts transitions from 0 to 1 of TBL bits speciÞed through

00 0100 Counts instructions dispatched. 0, 1, or 2 instructions per cycle.

00 0101 Counts L1 instruction cache misses.

00 0110 Counts ITLB misses.

00 0111 Counts L2 instruction misses.

00 1000 Counts branches predicted or resolved not taken.

00 1001 Counts MSR[PR] bit toggles.

00 1010 Counts times reserved load operations completed.

00 1011 Counts completed load and store instructions.

00 1100 Counts snoops to the L1 and the L2.

00 1101 Counts L1 cast-outs to the L2.

00 1110 Counts completed system unit instructions.

00 1111 Counts instruction fetch misses in the L1.

01 0000 Counts branches allowing out-of-order execution that resolved correctly.

All others Reserved.

MMRC0[RTCSELECT]. 00 = 47, 01 = 51, 10 = 55, 11 = 63.

4.5.11, 4-20 Remove Table 4-10, ÒTrace ExceptionÑSRR1 Settings.Ó This

interrupt is implemented as deÞned by the OEA. Remove the

Table 4-10 and the introductory text.

Errata to MPC750 UserÕs Manual MOTOROLA

Page 3

5.1.7, 5-18 Table 5-4, delete the second row in table ( lwarx or stwcx. with W = 1).

7.2.5.2.1, 7-14 For ARTRY, change ÒTiming Comments,Ó ÒNegation,Ó Þrst paragraph,

last sentence to the following:

First the buffer goes to high impedance for a minimum of one-half

processor cycle (dependent on the clock mode), then it is driven

negated for one-half bus cycle before returning to high impedance.

9.1.2, 9-5 In Table 9-1, replace the description of L2CR[L2DO] (bit 9), with the

following:

9 L2DO L2 data-only. Setting this bit inhibits the caching of instructions in the L2

cache. All accesses from the L1 instruction cache are treated as

cache-inhibited by the L2 cache (bypass L2 cache, no L2 tag look-up

performed).

11.2.1.5, 11-7 Replace Table 11-6 with the following:

Table 11-16. PMC2 EventsÑMMCR0[26Ð31] Select Encodings

Encoding Description

00 0000 Register holds current value.

00 0001 Counts processor cycles.

00 0010 Counts completed instructions. Does not include folded branches.

00 0011 Counts transitions from 0 to 1 of TBL bits speciÞed through

00 0100 Counts instructions dispatched. 0, 1, or 2 instructions per cycle.

00 0101 Counts L1 instruction cache misses.

00 0110 Counts ITLB misses.

00 0111 Counts L2 instruction misses.

00 1000 Counts branches predicted or resolved not taken.

00 1001 Counts MSR[PR] bit toggles.

00 1010 Counts times reserved load operations completed.

00 1011 Counts completed load and store instructions.

00 1100 Counts snoops to the L1 and the L2.

00 1101 Counts L1 cast-outs to the L2.

00 1110 Counts completed system unit instructions.

00 1111 Counts instruction fetch misses in the L1.

01 0000 Counts branches allowing out-of-order execution that resolved correctly.

All others Reserved.

MMRC0[RTCSELECT]. 00 = 47, 01 = 51, 10 = 55, 11 = 63.

MOTOROLA

Errata to MPC750 UserÕs Manual 3

Page 4

The PowerPC name is a registered trademark and the PowerPC logotype is a trademark of International Business Machines Corporation used by Motorola

under license from International Business Machines Corporation.

Mfax is a trademark of Motorola, Inc.

Information in this document is provided solely to enable system and software implementers to use PowerPC microprocessors. There are no express or implied

copyright licenses granted hereunder to design or fabricate PowerPC integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee

regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or

circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. ÒTypicalÓ parameters can and do vary in

different applications. All operating parameters, including ÒTypicalsÓ must be validated for each customer application by customerÕs technical experts. Motorola

does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components

in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure

of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such

unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless

against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola Literature Distribution Centers :

USA/EUROPE: Motorola Literature Distribution; P.O. Box 5405; Denver, Colorado 80217; Tel.: 1-800-441-2447 or 1-303-675-2140;

World Wide Web Address: http://ldc.nmd.com/

JAPAN : Nippon Motorola Ltd SPD, Strategic Planning Office 4-32-1, Nishi- Gotanda Shinagawa-ku, Tokyo 141, Japan Tel.: 81-3-5487-8488

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd Silicon Harbour Centre 2, Dai King Street Tai Po Industrial Estate Tai Po, New Territories, Hong Kong

Mfaxª : RMFAX0@email.sps.mot.com; TOUCHTONE 1-602-244-6609; US & Canada ONLY (800) 774-1848;

World Wide Web Address

INTERNET : http://motorola.com/sps

Technical Information : Motorola Inc. SPS Customer Support Center; 1-800-521-6274; electronic mail address: crc@wmkmail.sps.mot.com.

Document Comments : FAX (512) 895-2638, Attn: RISC Applications Engineering.

World Wide Web Addresses : http://www.mot.com/PowerPC

: http://sps.motorola.com/mfax

http://www.mot.com/netcomm

MPC750UMAD/AD

Loading...

Loading...