1

Motorola TMOS Power MOSFET Transistor Device Data

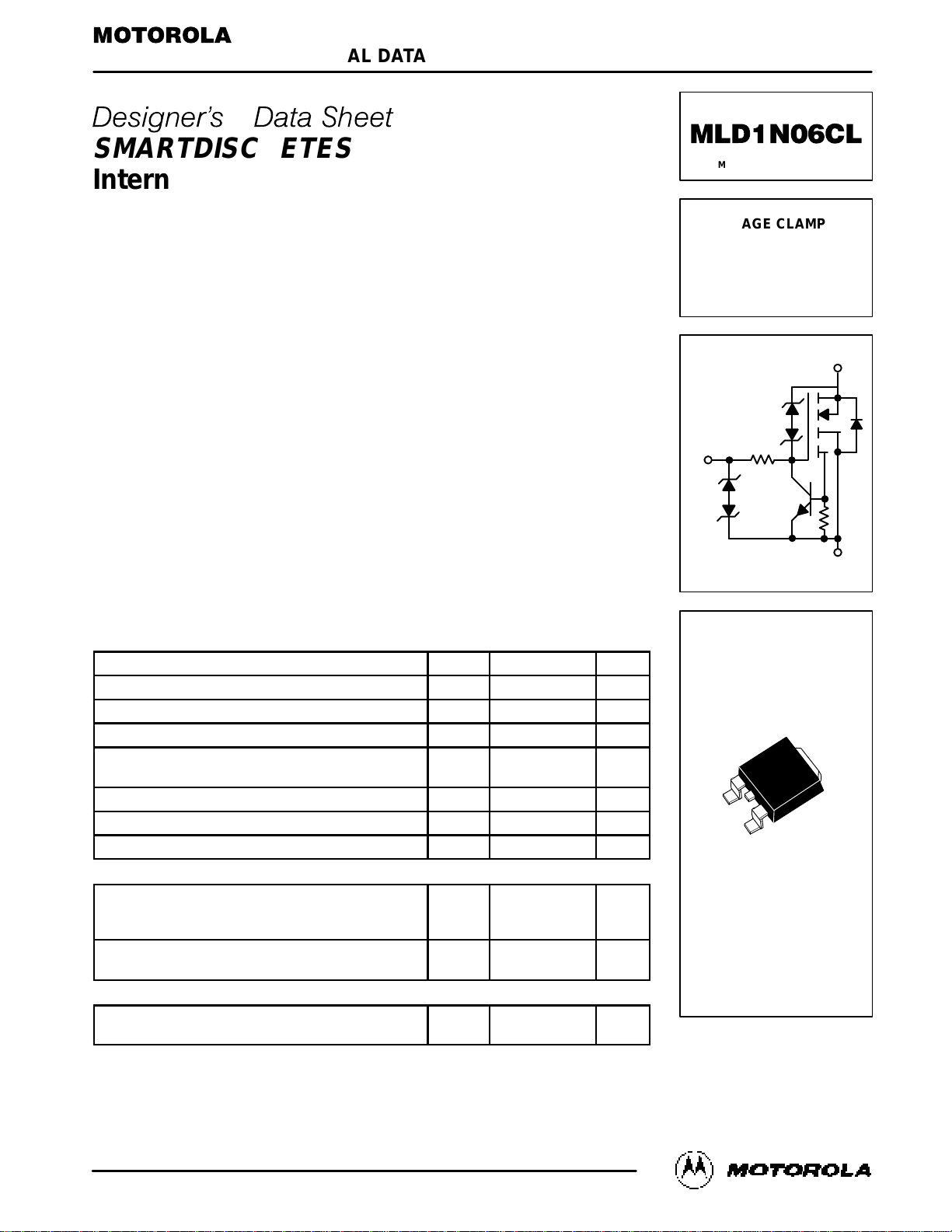

SMARTDISCRETES

Internally Clamped, Current Limited

N–Channel Logic Level Power MOSFET

The MLD1N06CL is designed for applications that require a rugged power switching

device with short circuit protection that can be directly interfaced to a microcontrol unit

(MCU). Ideal applications include automotive fuel injector driver, incandescent lamp

driver or other applications where a high in–rush current or a shorted load condition could

occur.

This logic level power MOSFET features current limiting for short circuit protection,

integrated Gate–Source clamping for ESD protection and integral Gate–Drain clamping

for over–voltage protection and Sensefet technology for low on–resistance. No additional

gate series resistance is required when interfacing to the output of a MCU, but a 40 kΩ

gate pulldown resistor is recommended to avoid a floating gate condition.

The internal Gate–Source and Gate–Drain clamps allow the device to be applied

without use of external transient suppression components. The Gate–Source clamp

protects the MOSFET input from e lectrostatic v oltage s tress up t o 2.0 kV. The

Gate–Drain clamp protects the MOSFET drain from the avalanche stress that occurs

with inductive loads. Their unique design provides voltage clamping that is essentially

independent of operating temperature.

The MLD1N06CL is fabricated using Motorola’s SMARTDISCRETES technology which

combines the advantages of a power MOSFET output device with the on–chip protective

circuitry that can be obtained from a standard MOSFET process. This approach offers an

economical means of providing protection to power MOSFETs from harsh automotive and

industrial environments. SMARTDISCRETES devices are specified over a wide temperature range from –50°C to 150°C.

MAXIMUM RATINGS

(TJ = 25°C unless otherwise noted)

Rating

Symbol Value Unit

Drain–to–Source Voltage V

DSS

Clamped Vdc

Drain–to–Gate Voltage (RGS = 1.0 MΩ) V

DGR

Clamped Vdc

Gate–to–Source Voltage — Continuous V

GS

±10 Vdc

Drain Current — Continuous

— Single Pulse

I

D

I

DM

Self–limited

1.8

Adc

Apk

Total Power Dissipation P

D

40 Watts

Operating and Storage Temperature Range TJ, T

stg

–50 to 150 °C

Electrostatic Discharge Voltage (Human Model) ESD 2.0 kV

THERMAL CHARACTERISTICS

Thermal Resistance — Junction to Case

— Junction to Ambient

— Junction to Ambient (1)

R

θJC

R

θJA

R

θJA

3.12

100

71.4

°C/W

Maximum Lead Temperature for Soldering Purposes,

1/8″ from case for 5 sec.

T

L

260 °C

UNCLAMPED DRAIN–TO–SOURCE AVALANCHE CHARACTERISTICS

Single Pulse Drain–to–Source Avalanche Energy

Starting TJ = 25°C

E

AS

80 mJ

(1) When surface mounted to an FR4 board using the minimum recommended pad size.

SMARTDISCRETES is a trademark of Motorola, Inc.

Designer’s Data for “Worst Case” Conditions —The Designer’s Data Sheet permits the design of most circuits entirely from the information presented. SOA Limit

curves — representing boundaries on device characteristics — are given to facilitate “worst case” design.

Preferred devices are Motorola recommended choices for future use and best overall value.

Order this document

by MLD1N06CL/D

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

MLD1N06CL

Motorola Preferred Device

VOLTAGE CLAMPED

CURRENT LIMITING

MOSFET

62 VOLTS (CLAMPED)

R

DS(on)

= 0.75 OHMS

CASE 369A–13, Style 2

DPAK Surface Mount

D

G

S

R1

R2

Motorola, Inc. 1996

MLD1N06CL

2

Motorola TMOS Power MOSFET Transistor Device Data

ELECTRICAL CHARACTERISTICS

(TC = 25°C unless otherwise noted)

Characteristic

Symbol Min Typ Max Unit

OFF CHARACTERISTICS

Drain–to–Source Breakdown Voltage (Internally Clamped)

(ID = 20 mAdc, VGS = 0 Vdc)

(ID = 20 mAdc, VGS = 0 Vdc, TJ = 150°C)

V

(BR)DSS

59

59

62

62

65

65

Vdc

Zero Gate Voltage Drain Current

(VDS = 45 Vdc, VGS = 0 Vdc)

(VDS = 45 Vdc, VGS = 0 Vdc, TJ = 150°C)

I

DSS

—

—

0.6

6.0

5.0

20

µAdc

Gate–Source Leakage Current

(VG = 5.0 Vdc, VDS = 0 Vdc)

(VG = 5.0 Vdc, VDS = 0 Vdc, TJ = 150°C)

I

GSS

—

—

0.5

1.0

5.0

20

µAdc

ON CHARACTERISTICS(1)

Gate Threshold Voltage

(ID = 250 µAdc, VDS = VGS)

(ID = 250 µAdc, VDS = VGS, TJ = 150°C)

V

GS(th)

1.0

0.6

1.5

—

2.0

1.6

Vdc

Static Drain–to–Source On–Resistance

(ID = 1.0 Adc, VGS = 4.0 Vdc)

(ID = 1.0 Adc, VGS = 5.0 Vdc)

(ID = 1.0 Adc, VGS = 4.0 Vdc, TJ = 150°C)

(ID = 1.0 Adc, VGS = 5.0 Vdc, TJ = 150°C)

R

DS(on)

—

—

—

—

0.63

0.59

1.1

1.0

0.75

0.75

1.9

1.8

Ohms

Static Source–to–Drain Diode Voltage (IS = 1.0 Adc, VGS = 0 Vdc) V

SD

— 1.1 1.5 Vdc

Static Drain Current Limit

(VGS = 5.0 Vdc, VDS = 10 Vdc)

(VGS = 5.0 Vdc, VDS = 10 Vdc, TJ = 150°C)

I

D(lim)

2.0

1.1

2.3

1.3

2.75

1.8

Adc

Forward Transconductance (ID = 1.0 Adc, VDS = 10 Vdc) g

FS

1.0 1.4 — mhos

RESISTIVE SWITCHING CHARACTERISTICS(2)

Turn–On Delay Time

t

d(on)

— 1.2 2.0

Rise Time

DD

= 25 Vdc, ID = 1.0 Adc,

t

r

— 4.0 6.0

Turn–Off Delay Time

(VDD = 25 Vdc, ID = 1.0 Adc,

V

GS(on)

= 5.0 Vdc, RGS = 50 Ohms)

t

d(off)

— 4.0 6.0

Fall Time t

f

— 3.0 5.0

INTERNAL PACKAGE INDUCTANCE

Internal Drain Inductance

(Measured from drain lead 0.25” from package to center of die)

L

D

— 4.5 —

nH

Internal Source Inductance

(Measured from the source lead 0.25” from package to source bond pad)

L

S

— 7.5 —

nH

(1) Pulse Test: Pulse Width ≤ 300 µs, Duty Cycle ≤ 2%.

(2) Switching characteristics are independent of operating junction temperature.

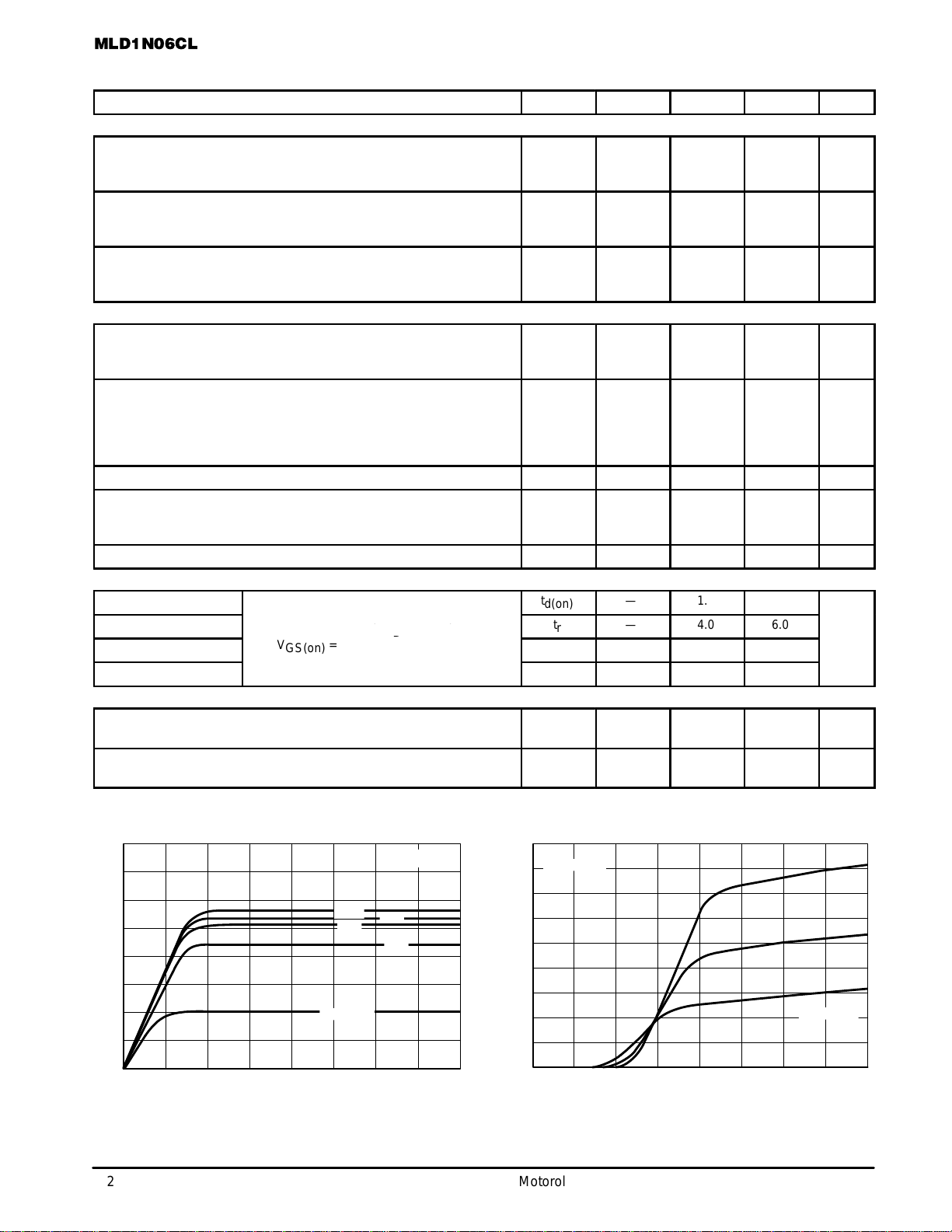

2 4 6 8

4

1

0

3

2

VDS, DRAIN–TO–SOURCE VOLTAGE (VOLTS)

10 V

8 V

4 V

VGS = 3 V

0

, DRAIN CURRENT (AMPS)I

D

6 V

–50°C

0 2 4 6 8

4

1

0

3

2

VGS, GATE–TO–SOURCE VOLTAGE (VOLTS)

, DRAIN CURRENT (AMPS)I

D

25°C

VDS ≥ 7.5 V

TJ = 150°C

TJ = 25°C

(V

ns

Figure 1. Output Characteristics Figure 2. Transfer Function