Motorola MCM69L736AZP9.5, MCM69L736AZP7.5R, MCM69L736AZP8.5, MCM69L736AZP8.5R, MCM69L736AZP10.5R Datasheet

...

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Advance Information

4M Late Write HSTL

The MCM69L736A/818A is a 4M synchronous late write fast static RAM

designed to provide high performance in secondary cache and ATM switch,

Telecom, and other high speed memory applications. The MCM69L818A

(organized as 256K words by 18 bits) and the MCM69L736A (organized as 128K

words by 36 bits) are fabricated in Motorola’s high performance silicon gate

BiCMOS technology .

The differential clock (CK) inputs control the timing of read/write operations of

the RAM. At the rising edge of CK, all addresses, write enables, and synchronous

selects are registered. An internal buffer and special logic enable the memory to

accept write data on the rising edge of CK a cycle after address and control

signals. Read data is available at the falling edge of CK.

The RAM uses HSTL inputs and outputs. The adjustable input trip–point (V

and output voltage (V

optimizing system performance.

The synchronous write and byte enables allow writing to individual bytes or the

entire word.

The impedance of the output buffers is programmable, allowing the outputs to

match the impedance of the circuit traces which reduces signal reflections.

• Byte Write Control

• Single 3.3 V +10%, – 5% Operation

• HSTL — I/O (JEDEC Standard JESD8–6 Class I)

• HSTL — User Selectable Input Trip–Point

• HSTL — Compatible Programmable Impedance Output Drivers

• Register to Latch Synchronous Operation

• Asynchronous Output Enable

• Boundary Scan (JTAG) IEEE 1149.1 Compatible

• Differential Clock Inputs

• Optional x18 or x36 Organization

• MCM69L736A/818A–7.5 = 7.5 ns

MCM69L736A/818A–8.5 = 8.5 ns

MCM69L736A/818A–9.5 = 9.5 ns

MCM69L736A/818A–10.5 = 10.5 ns

• 1 19 Bump, 50 mil (1.27 mm) Pitch, 14 mm x 22 mm Plastic Ball Grid Array

(PBGA) Package

) gives the system designer greater flexibility in

DDQ

ref

Order this document

by MCM69L736A/D

MCM69L736A

MCM69L818A

ZP PACKAGE

PBGA

CASE 999–01

)

This document contains information on a new product. Specifications and information herein are subject to change without notice.

4/3/97

Motorola, Inc. 1997

MOTOROLA FAST SRAM

MCM69L736A•MCM69L818A

1

FUNCTIONAL BLOCK DIAGRAM

SA

SW

SBx

CK

SS

ADDRESS

REGISTERS

SW

REGISTERS

G

SS

REGISTERS

MEMORY

ARRAY

CONTROL

LOGIC

DATA IN

REGISTER

DQ

DATA OUT

LATCH

PIN ASSIGNMENTS

TOP VIEW

MCM69L736A

6543217

MCM69L818A

6543217

A

V

SA SA SA SA

DDQ

B

NC NC SA NC

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

SA SA SA SA

NC

DQc DQc VSSZQ DQb

DQc

DQc

V

DQc V

DDQ

DQcDQc

DQc

DQc VSSNC DQb

V

V

V

V

DD

DDQ

DQd DQd V

DQd V

DDQ

DQdDQd

DQd DQd V

SA SA

NC

NC

NC SA SA NC

DDQ

NC

SA

V

DD

V

SS

V

G

V

DD

CK V

CK

SW

SA

V

DD

SA

TCK

SS

V

SS

SBb

V

SS

V

ref

SS

V

SS

V

SS

V

SS

V

SS

TDO

SS

SS

V

ref

SS

SBdDQdDQd

SS

SS

SS

V

DD

TDITMS

NC

DQbSSV

DQb

DQbNCSBc

V

DD

DQa

DQaSBa

DQa

DQaSAV

DQa

NC

V

V

V

V

V

DDQ

NC

NC

DQb

DQb

DDQ

DQb

DQb

DDQ

DQa

DQa

DDQ

DQa

DQa

NC

ZZ

DDQ

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

SA SA SA SA

V

DDQ

NC NC SA NC

SA SA SA SA

NC

DQb NC VSSZQ DQa

DQbNC

V

NC V

DDQ

DQbNC

DQb

NC VSSNC DQa

V

V

V

V

DD

DDQ

NC DQb VSSCK V

NCDQb

DQb V

DDQ

NCDQb

NC DQb VSSSA

SA SA

NC

SA SA SA SA

NC

DDQ

NC

NC

SA

V

DD

V

SS

V

NCSSV

G

V

DD

CK

SW

V

DD

NC

TCK

SS

V

SS

V

SS

V

SS

V

ref

SS

V

SS

V

SS

V

SS

V

SS

TDO

DQa

NCNCSBb

V

NC

DQaSBa

NC

DQaSAV

NC

NC

SS

SS

V

ref

V

SS

SS

SS

V

DD

TDITMS

DD

V

V

V

V

V

DDQ

NC

NC

NC

DQa

DDQ

DQa

NC

DDQ

DQa

NC

DDQ

NC

DQa

NC

ZZ

DDQ

MCM69L736A•MCM69L818A

2

MOTOROLA FAST SRAM

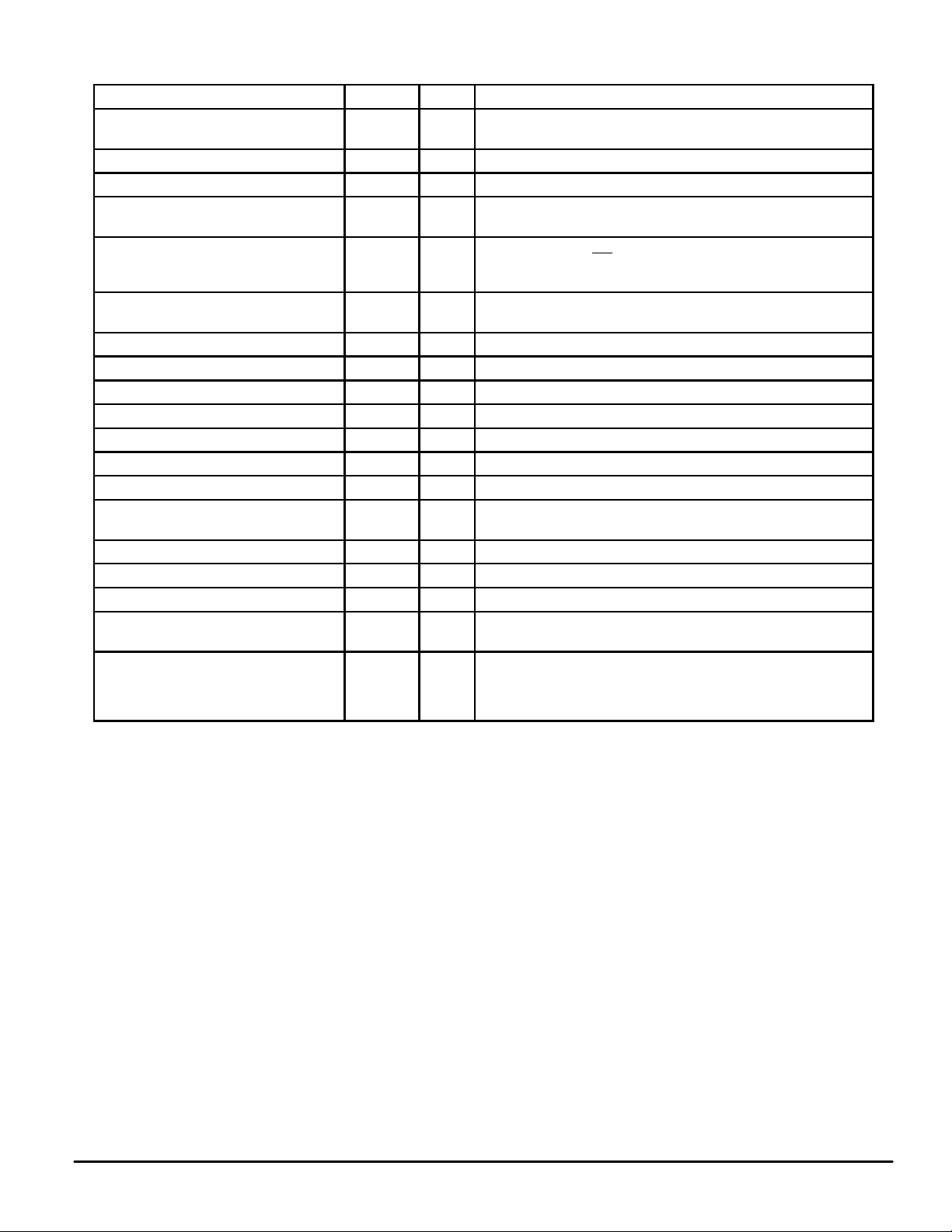

MCM69L736A PIN DESCRIPTIONS

PBGA Pin Locations Symbol Type Description

2A, 3A, 5A, 6A, 3B, 5B, 2C, 3C,

5C, 6C, 4N, 4P, 2R, 6R, 3T, 4T, 5T

4K CK Input Address, data in, and control input register clock. Active high.

4L CK Input Address, data in, and control input register clock. Active low.

4M SW Input Synchronous Write: Registered on the rising clock edge, active low.

5L, 5G, 3G, 3L

(a), (b), (c), (d)

4E SS Input Synchronous Chip Enable: Registered on the rising clock edge, active

4F G Input Output Enable: Asynchronous pin, active low.

2U TMS Input T est Mode Select (JTAG).

3U TDI Input Test Data In (JT AG).

4U TCK Input Test Clock (JTAG).

5U TDO Output Test Data Out (JTAG).

4D ZQ Input Programmable Output Impedance: Programming pin.

7T ZZ Input Reserved for future use. Must be grounded.

(a) 6K, 7K, 6L, 7L, 6M, 6N, 7N, 6P, 7P

(b) 6D, 7D, 6E, 7E, 6F, 6G, 7G, 6H, 7H

(c) 1D, 2D, 1E, 2E, 2F, 1G, 2G, 1H, 2H

(d) 1K, 2K, 1L, 2L, 2M, 1N, 2N, 1P, 2P

3J, 5J V

4C, 2J, 4J, 6J, 4R, 3R V

1A, 7A, 1F, 7F, 1J, 7J, 1M, 7M, 1U, 7U V

3D, 5D, 3E, 5E, 3F, 5F, 3H, 5H,

3K, 5K, 3M, 5M, 3N, 5N, 3P, 5P, 5R

4A, 1B, 2B, 4B, 6B, 7B, 1C, 7C,

4G, 4H, 1R, 7R, 1T, 2T, 6T, 6U

SA Input Synchronous Address Inputs: Registered on the rising clock edge.

Writes all enabled bytes.

SBx Input Synchronous Byte Write Enable: Enables writes to byte x in

DQx I/O Synchronous Data I/O.

ref

DD

DDQ

V

SS

NC — No Connection: There is no connection to the chip.

Supply Input Reference: Provides reference voltage for input buffers.

Supply Core Power Supply.

Supply Output Power Supply: Provides operating power for output buffers.

Supply Ground.

conjunction with the SW

low.

low.

input. Has no effect on read cycles, active

MOTOROLA FAST SRAM

MCM69L736A•MCM69L818A

3

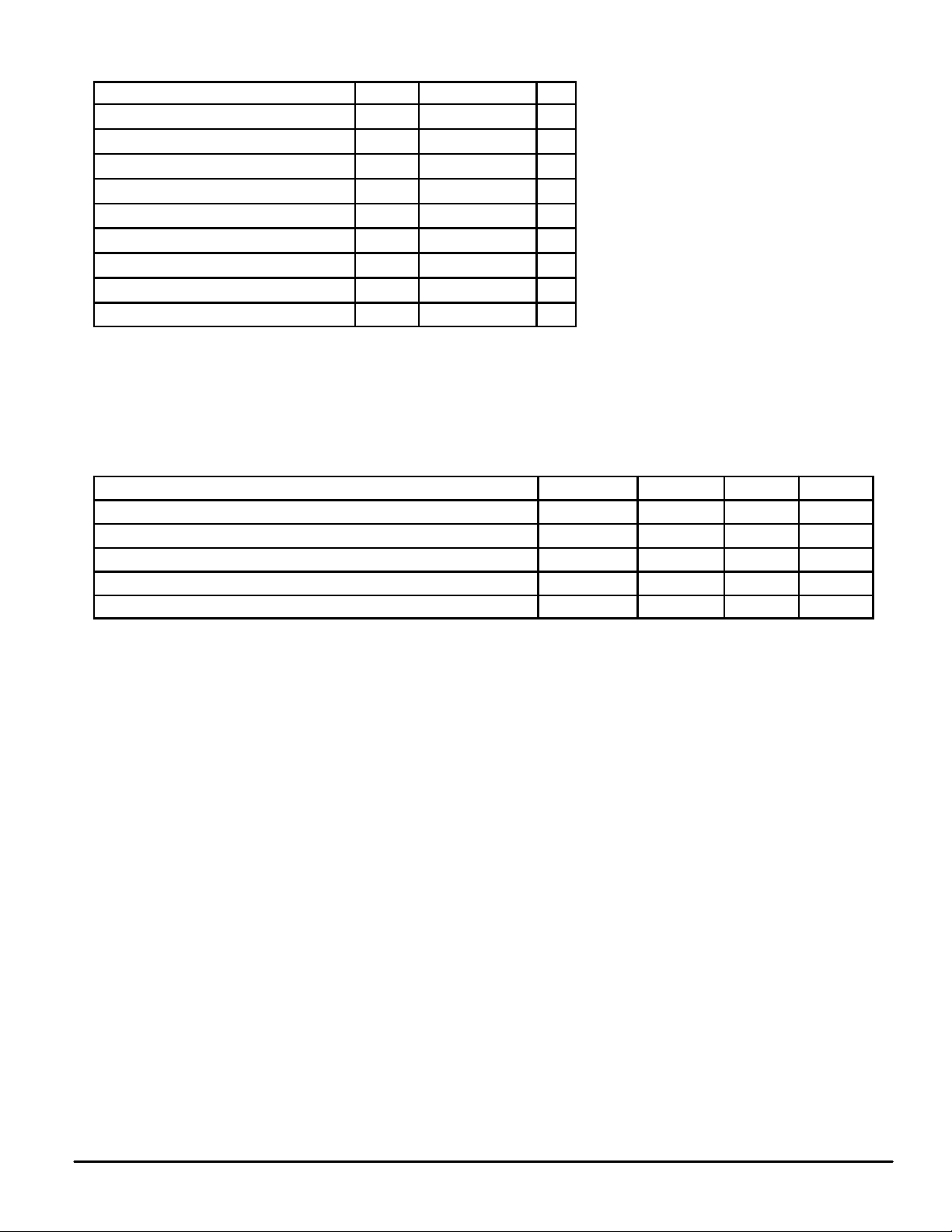

MCM69L818A PIN DESCRIPTIONS

PBGA Pin Locations Symbol

2A, 3A, 5A, 6A, 3B, 5B, 2C, 3C, 5C,

6C, 4N, 4P, 2R, 6R, 2T, 3T, 5T, 6T

4K CK Input Address, data in, and control input register clock. Active high.

4L CK Input Address, data in, and control input register clock. Active low.

4M SW Input Synchronous Write: Registered on the rising clock edge, active low.

5L, 3G

(a), (b)

4E SS Input Synchronous Chip Enable: Registered on the rising clock edge, active

2U TMS Input T est Mode Select (JTAG).

3U TDI Input Test Data In (JT AG).

4U TCK Input Test Clock (JTAG).

5U TDO Output Test Data Out (JTAG).

4D ZQ Input Programmable Output Impedance: Programming pin.

4F G Input Output Enable: Asynchronous pin, active low.

7T ZZ Input Reserved for future use. Must be grounded.

(a) 6D, 7E, 6F, 7G, 6H, 7K, 6L, 6N, 7P

(b) 1D, 2E, 2G, 1H, 2K, 1L, 2M, 1N, 2P

3J, 5J V

4C, 2J, 4J, 6J, 4R, 3R V

1A, 7A, 1F, 7F, 1J, 7J, 1M, 7M, 1U, 7U V

3D, 5D, 3E, 5E, 3F, 5F, 5G, 3H, 5H,

3K, 5K, 3L, 3M, 5M, 3N, 5N, 3P, 5P, 5R

4A, 1B, 2B, 4B, 6B, 7B, 1C, 7C,

2D, 7D, 1E, 6E, 2F, 1G, 4G, 6G,

2H, 4H, 7H, 1K, 6K, 2L, 7L, 6M, 2N,

7N, 1P, 6P, 1R, 7R, 1T, 4T, 6U

Type Description

SA Input Synchronous Address Inputs: Registered on the rising clock edge.

Writes all enabled bytes.

SBx Input Synchronous Byte Write Enable: Enables writes to byte x in

DQx I/O Synchronous Data I/O.

ref

DD

DDQ

V

SS

NC — No Connection: There is no connection to the chip.

Supply Input Reference: Provides reference voltage for input buffers.

Supply Core Power Supply.

Supply Output Power Supply: Provides operating power for output buffers.

Supply Ground.

conjunction with the SW

low.

low.

input. Has no effect on read cycles, active

MCM69L736A•MCM69L818A

4

MOTOROLA FAST SRAM

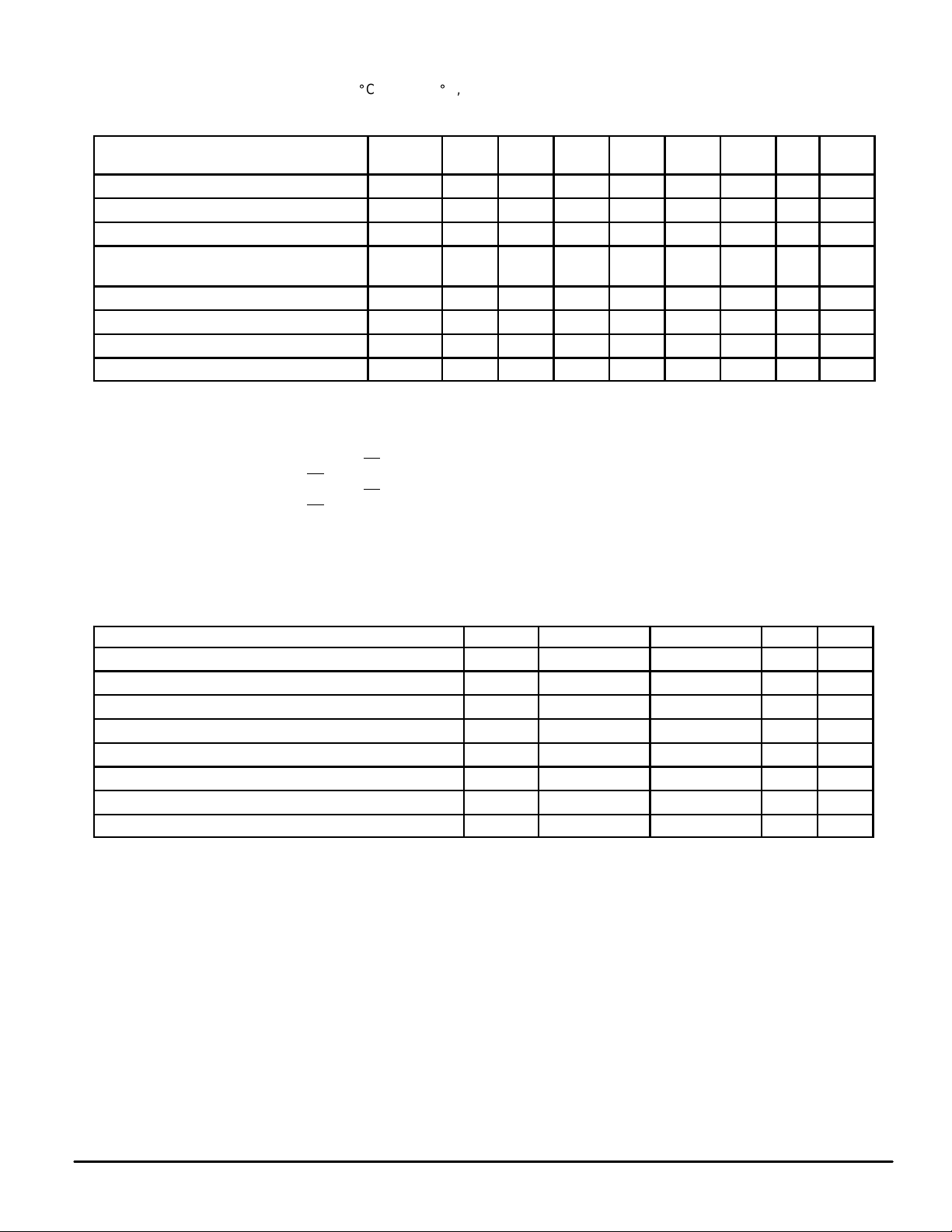

ABSOLUTE MAXIMUM RATINGS (Voltages Referenced to V

Rating

Core Supply Voltage V

Output Supply Voltage V

Voltage On Any Pin V

Input Current (per I/O) I

Output Current (per I/O) I

Power Dissipation (See Note 2) P

Operating Temperature T

Temperature Under Bias T

Storage Temperature T

NOTES:

1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are

exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended

periods of time could affect device reliability.

2. Power dissipation capability will be dependent upon package characteristics and use

environment. See enclosed thermal impedance data.

Symbol Value Unit

DD

DDQ

bias

– 0.5 to VDD + 0.5 V

– 0.5 to VDD + 0.5 V

in

in

out

D

A

stg

, See Note 1)

SS

– 0.5 to + 4.6 V

± 50 mA

± 70 mA

— W

0 to + 70 °C

–10 to + 85 °C

– 55 to + 125 °C

This device contains circuitry to protect the

inputs against damage due to high static voltages or electric fields; however, it is advised

that normal precautions be taken to avoid

application of any voltage higher than maximum rated voltages to this high–impedance

circuit.

This BiCMOS memory circuit has been

designed to meet the dc and ac specifications

shown in the tables, after thermal equilibrium

has been established.

This device contains circuitry that will ensure

the output devices are in High–Z at power up.

PBGA PACKAGE THERMAL CHARACTERISTICS

Rating Symbol Max Unit Notes

Junction to Ambient (Still Air) R

Junction to Ambient (@200 ft/min) Single Layer Board R

Junction to Ambient (@200 ft/min) Four Layer Board R

Junction to Board (Bottom) R

Junction to Case (Top) R

NOTES:

1. Junction temperature is a function of on–chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient

temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

2. Per SEMI G38–87.

3. Indicates the average thermal resistance between the die and the printed circuit board.

4. Indicates the average thermal resistance between the die and the case top surfac e as measured by the cold plate method (MIL SPEC–883

Method 1012.1).

θJA

θJA

θJA

θJB

θJC

53 °C/W 1, 2

38 °C/W 1, 2

22 °C/W

14 °C/W 3

5 °C/W 4

MOTOROLA FAST SRAM

MCM69L736A•MCM69L818A

5

DC OPERA TING CONDITIONS AND CHARACTERISTICS

(0_C ≤ TA ≤ 70_C, Unless Otherwise Noted)

RECOMMENDED OPERATING CONDITIONS

Parameter

Input Reference DC Voltage V

Core Power Supply Voltage V

Output Driver Supply Voltage V

Active Power Supply Current (x18)

Quiescent Active Power Supply Current) I

Active Standby Power Supply Current I

Quiescent Standby Power Supply Current I

Sleep Mode Power Supply Current I

NOTES:

1. All data sheet parameters specified to full range of VDD unless otherwise noted. All voltages are referenced to voltage applied to VSS bumps.

2. Supply voltage applied to VDD connections.

3. Supply voltage applied to V

4. All power supply currents measured with outputs open or deselected.

5. VDD = VDD (max), t

6. VDD = VDD (max), t

7. VDD = VDD (max), t

8. VDD = VDD (max), t

9. VDD = VDD (Max), t

10. 200 mV ≥ Vin ≥ V

11. Although considerable latitude in the selection of the nominal dc value (i.e., rms value) of V

superimposed on V

DDQ

DDQ

= t

KHKH

= dc, SS

KHKH

= t

KHKH

= dc, SS

KHKH

= dc, registered inactive, ZZ high.

KHKH

– 200 mV.

may not exceed 5% of the dc component of V

ref

(x36)

connections.

(min), SS

KHKH

registered active.

(min), SS

KHKH

registered inactive, ZZ low.

(See Notes 1 through 4)

Typical

Symbol Min

(dc) 0.6 — — — — 1.1 V 11

ref

DD

DDQ

I

DD1

DD2

SB1

SB2

SB3

registered active, 50% read cycles.

registered inactive.

3.15 — — — — 3.6 V

1.4 — — — — 1.6 V

—

—

— 190 190 190 190 250 mA 6, 10

— 160 160 160 160 250 mA 7

— 140 140 140 140 230 mA 8, 10

— TBD TBD TBD TBD TBD mA 9, 10

–7.5

ref

300

390

.

Typical

–8.5

290

380

Typical

–9.5

ref

Typical

–10.5

270

360

is supported, the peak to peak ac component

260

350

Max Unit Notes

450

560

mA 5

DC INPUT CHARACTERISTICS

Parameter Symbol Min Max Unit Notes

DC Input Logic High VIH (dc) V

DC Input Logic Low VIL (dc) – 0.3 V

Input Reference DC Voltage V

Input Leakage Current I

Clock Input Signal Voltage V

Clock Input Differential V oltage V

Clock Input Common Mode Voltage Range (See Figure 3) VCM (dc) 0.68 1.1 V 5

Clock Input Crossing Point Voltage Range V

NOTES:

1. Inputs may undershoot to – 0.5 V (peak) for up to 20% t

2. Although considerable latitude in the selection of the nominal dc value (i.e., rms value) of V

superimposed on V

3. 0 V ≤ Vin ≤ V

4. Minimum instantaneous differential input voltage required for differential input clock operation.

5. Maximum rejectable common mode input voltage variation.

DDQ

may not exceed 5% of the dc component of V

ref

for all pins.

KHKH

(dc) 0.6 1.1 V 2

ref

lkg(1)

in

(dc) 0.1 VDD + 0.6 V 4

DIF

X

(e.g., 2 ns at a clock cycle time of 10 ns).

.

ref

+ 0.1 VDD + 0.3 V

ref

– 0.1 V 1

ref

— ± 5 µA 3

– 0.3 VDD + 0.3 V

0.68 1.1 V

is supported, the peak–to–peak ac component

ref

MCM69L736A•MCM69L818A

6

MOTOROLA FAST SRAM

Loading...

Loading...