Motorola MCM32P865, MCM32N864, MCM32N865, MCM32P864 Datasheet

MCM32N864•MCM32N865•MCM32P864•MCM32P865

1

MOTOROLA FAST SRAM

Advance Information

256KB Secondary Cache Module

With Tag and Optional Dirty for

486 Processor Systems

These 256K Byte cache modules offer dual asynchronous 32K x 32 banks of

memory. There is a 16K x 8 tag memory for main memory cacheability up to 64

Megabytes. The MCM32N865 and MCM32P865 include a 16K x 1 common I/O

dirty bit for writeback cache capability. The modules are designed to support

common 486 chipsets which utilize chip enable (CEx) byte control and bank write

enable (CWEx

). The MCM32N864 and MCM32N865 operate at 5 V while the

MCM32P864 and MCM32P865 operate at 3.3 V power. PD pins are provided for

cache size identification at system startup

• 64MB of Cacheable Memory

• Low Profile Edge Connector: Burndy Part Number: CELP2X56SC3Z48

• All Inputs and Outputs are TTL Compatible

• Three State Outputs

• Fast Module Cycle Time: Up to External Processor Bus Speed of 33 MHz

• Cache Bank Write, Byte Chip Enable, Bank Output Enable

• Decoupling Capacitors are Used for Each Fast Static RAM

• High Quality Multi–Layer FR4 PWB With Separate Power and Ground Planes

• 5 V and 3.3 V Power Supplies are Supported

This document contains information on a new product. Specifications and information herein are subject to change without notice.

Order this document

by MCM32N864/D

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

MCM32N864

MCM32N865

MCM32P864

MCM32P865

56

46

45

1

112–LEAD

CARD EDGE

CASE 1112–01

TOP VIEW

REV 1

6/95

Motorola, Inc. 1995

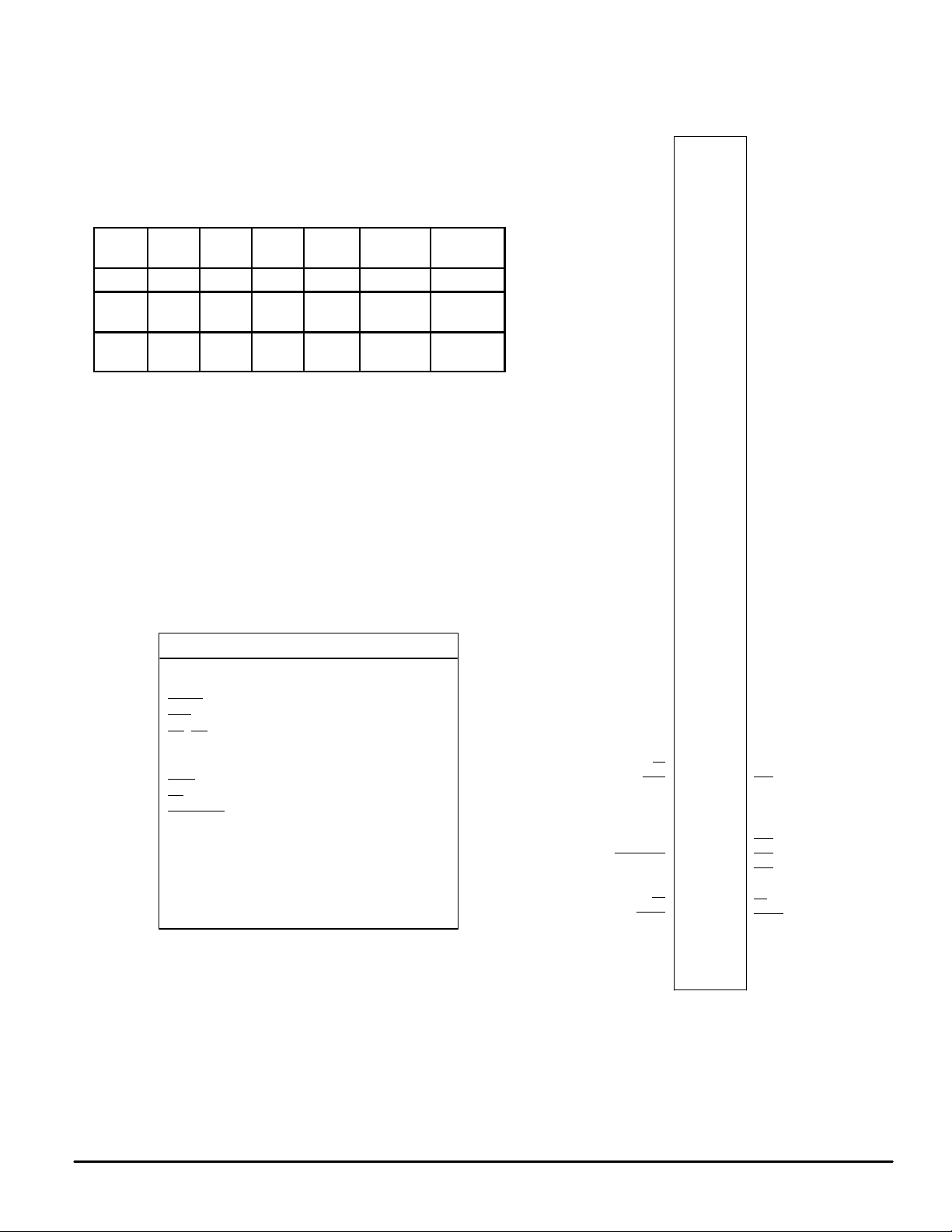

PIN ASSIGNMENT

CACHE MODULE

112 PIN CARDEDGE

TOP VIEW

V

SS

DQ0

DQ2

DQ4

DQ6

VCC5

NC

DQ8

DQ10

DQ12

V

SS

DQ14

DQ16

DQ18

DQ20

VCC5

DQ22

NC

DQ24

DQ26

V

SS

DQ28

DQ30

CA3B

CA3A

VCC5

A4

A6

A8

A10

A12

A14

A16

NC

V

SS

NC

TDQ0

TDQ2

TDQ4

V

SS

TDQ6

NC

TE

TWE

VCC5

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

V

SS

DQ1

DQ3

DQ5

DQ7

VCC3

NC

DQ9

DQ11

DQ13

V

SS

DQ15

DQ17

DQ19

DQ21

VCC3

DQ23

NC

DQ25

DQ27

V

SS

DQ29

DQ31

NC

NC

VCC3

A5

A7

A9

A11

A13

A15

A17

NC

V

SS

NC

TDQ1

TDQ3

TDQ5

V

SS

TDQ7

DIRTY*

NC

CE0

VCC3

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

V

SS

G1

CWE1

PD1

PD3

NC

V

SS

46

47

48

49

50

51

52

53

54

55

56

102

103

104

105

106

107

108

109

110

111

112

V

SS

NC

*DIRTYWE

NC

VCC5

G0

CWE0

PD0

PD2

NC

V

SS

CE1

CE2

CE3

VCC3

PIN NAMES

A4 – A17 Address Inputs. . . . . . . . . . . . . . . . . . . . . .

CA3A, CA3B Bank Address Inputs. . . . . . . . . . . . . .

CWEx

Bank Write Enable. . . . . . . . . . . . . . . . . . . . .

CEx

Byte Chip Enable. . . . . . . . . . . . . . . . . . . . . . . .

G0

, G1 Bank Output Enable. . . . . . . . . . . . . . . . . . .

DQ0 – DQ31 Cache Data Input/Output. . . . . . . . . .

TDQ0 – TDQ8 Tag Data Input/Output. . . . . . . . . . .

TWE

Tag Write Enable. . . . . . . . . . . . . . . . . . . . . . . .

TE

Tag Chip Enable. . . . . . . . . . . . . . . . . . . . . . . . . .

DIRTYWE

Dirty Write Enable. . . . . . . . . . . . . . . . . .

DIRTY Dirty Input/Output. . . . . . . . . . . . . . . . . . . . . .

PD0 – PD3 Presence Detect. . . . . . . . . . . . . . . . . .

NC No Connect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VCC5 +5 V Power Supply. . . . . . . . . . . . . . . . . . . . .

VCC3 +3.3 V Power Supply. . . . . . . . . . . . . . . . . . .

V

SS

Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

* No Connect for MCM32N864 and MCM32P864

MCM32N864•MCM32N865•MCM32P864•MCM32P865

2

MOTOROLA FAST SRAM

PD3 PD2 PD1 PD0

Cache

Size

Dirty Module

NC NC NC NC — — No Module

NC GND NC NC 256KB No 32N864

32P864

GND GND NC NC 256KB Yes 32N865

32P865

Loading...

Loading...