Motorola MCM32A932SG33, MCM32A964SG33, MCM32A764SG33, MCM32A832SG33, MCM32A732SG33 Datasheet

...

MCM32A732/764•MCM32A832/864•MCM32A932/964

1

MOTOROLA FAST SRAM

Advance Information

128KB/256KB Secondary Cache

Module

With Tag, Valid, and Dirty for i486

Processor Systems

This family of cache modules is well suited to provide the secondary cache for

the Intel 82420 PCI chipset. This family provides the 128K Byte and 256K Byte

cache sizes with valid, dirty and a choice of 7, 8, or 9 tag bits. The tag/valid bits

have 12 ns access times for zero wait states at 33 MHz clock speeds. The PD

pins map into the configuration register of the 82420 for auto–configuration of the

cache controller during system startup.

• Low Profile Edge Connector: Burndy Part Number: CELP2X56SC3Z48

• Single 5 V ± 10% Power Supply

• All Inputs and Outputs are TTL Compatible

• Three State Outputs

• Fast Module Cycle Time: Up to External Processor Bus Speed of 33 MHz

• Cache Byte Write, Bank Chip Enable, Bank Output Enable

• Decoupling Capacitors are Used for Each Fast Static RAM

• High Quality Multi–Layer FR4 PWB With Separate Power and Ground Planes

BurstRAM is a registered trademark of Motorola.

I486 is a registered trademark Intel Corp.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

Order this document

by MCM32A732/D

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

MCM32A732

MCM32A832

MCM32A932

MCM32A764

MCM32A864

MCM32A964

56

46

45

1

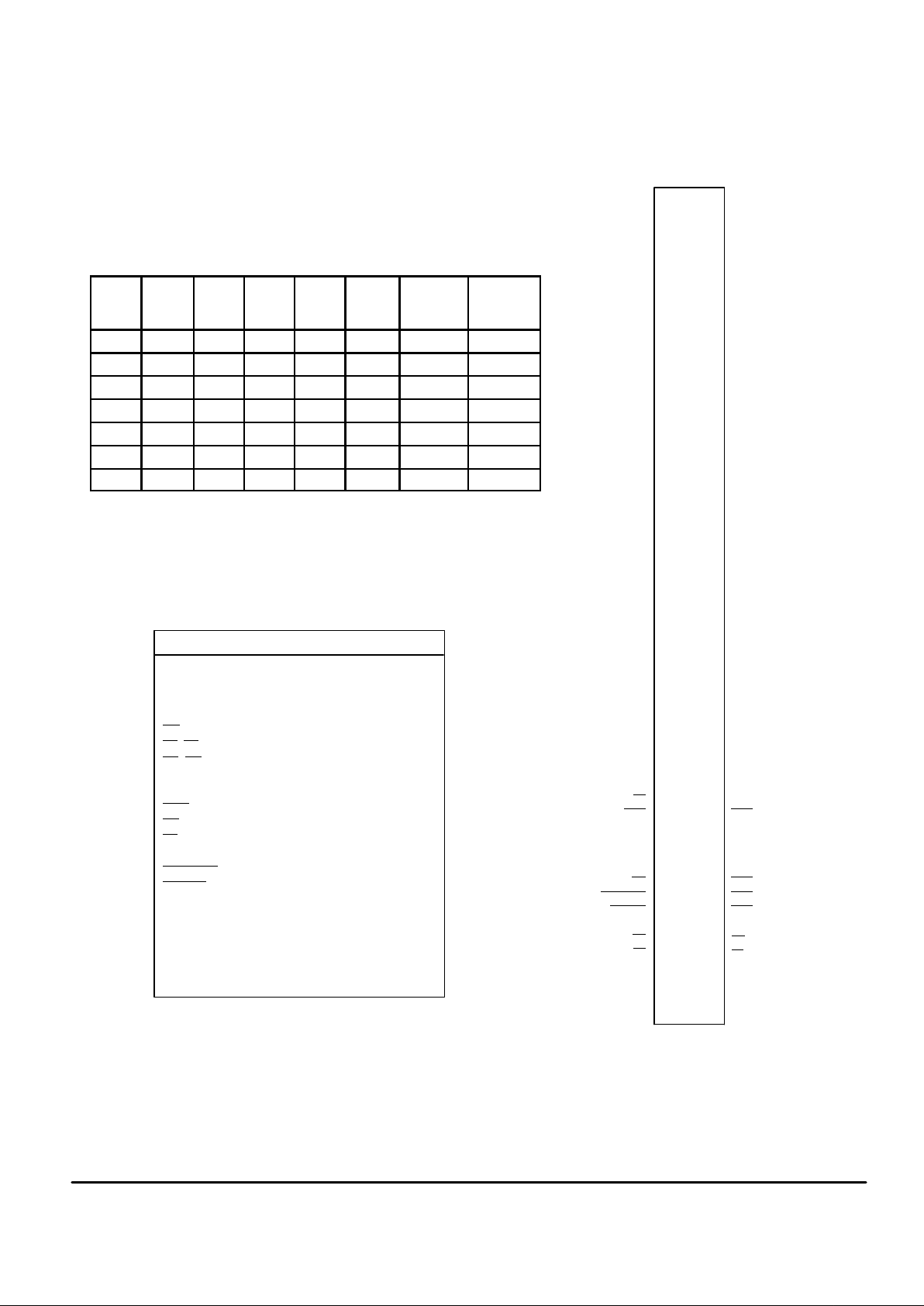

112–LEAD

CARD EDGE

CASE 1112–01

TOP VIEW

REV 1

6/95

Motorola, Inc. 1994

PIN ASSIGNMENT

CACHE MODULE

112–LEAD CARDEDGE

TOP VIEW

V

SS

DQ0

DQ2

DQ4

DQ6

V

CC

NC

DQ8

DQ10

DQ12

V

SS

DQ14

DQ16

DQ18

DQ20

V

CC

DQ22

NC

DQ24

DQ26

V

SS

DQ28

DQ30

LA2

LA3

V

CC

A4

A6

A8

A10

A12

A14

A16

NC

V

SS

DIRTYD

TDQ0

TDQ2

TDQ4

V

SS

TDQ6

VALID

TE

TWE

V

CC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

V

SS

DQ1

DQ3

DQ5

DQ7

V

CC

NC

DQ9

DQ11

DQ13

V

SS

DQ15

DQ17

DQ19

DQ21

V

CC

DQ23

NC

DQ25

DQ27

V

SS

DQ29

DQ31

HA2

HA3

V

CC

A5

A7

A9

A11

A13

A15

NC

NC

V

SS

DIRTYQ

TDQ1

TDQ3

TDQ5

V

SS

TDQ7*

TDQ8**

ALE

WE0

V

CC

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

V

SS

G1

E1

PD1

PD3

NC

V

SS

46

47

48

49

50

51

52

53

54

55

56

102

103

104

105

106

107

108

109

110

111

112

V

SS

TG

DIRTYWE

DIRTYE

V

CC

G0

E0

PD0

PD2

PD4

V

SS

WE1

WE2

WE3

V

CC

PIN NAMES

A4 – A19 Address Inputs. . . . . . . . . . . . . . . . . . . . . .

HCA2, HCA3 Upper Bank Address Inputs. . . . . . .

LCA2, LCA3 Lower Bank Address Inputs. . . . . . . .

ALE Address Latch Enable. . . . . . . . . . . . . . . . . . . .

Wx

Byte Write Enable. . . . . . . . . . . . . . . . . . . . . . . .

E0

, E1 Bank Chip Enable. . . . . . . . . . . . . . . . . . . . .

G0

, G1 Bank Output Enable. . . . . . . . . . . . . . . . . . .

DQ0 – DQ31 Cache Data Input/Output. . . . . . . . . .

TDQ0 – TDQ8 Tag Data Input/Output. . . . . . . . . . .

TWE

Tag Write Enable. . . . . . . . . . . . . . . . . . . . . . . .

TG

Tag Output Enable. . . . . . . . . . . . . . . . . . . . . . . .

TE

Tag Chip Enable. . . . . . . . . . . . . . . . . . . . . . . . . .

VALID Valid Bit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DIRTYWE Dirty Write Enable. . . . . . . . . . . . . . . . . .

DIRTYE

Dirty Chip Enable. . . . . . . . . . . . . . . . . . . . .

DIRTYD Dirty Data Input. . . . . . . . . . . . . . . . . . . . . .

DIRTYQ Dirty Data Output. . . . . . . . . . . . . . . . . . . . .

PD0 – PD4 Presence Detect. . . . . . . . . . . . . . . . . .

NC No Connect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

V

CC

+5 V Power Supply. . . . . . . . . . . . . . . . . . . . . .

V

SS

Ground. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

* No Connect for 32A864, 32A832

** No Connect for 32A764, 32A864, 32A732, 32A832

MCM32A732/764•MCM32A832/864•MCM32A932/964

2

MOTOROLA FAST SRAM

PD4 PD3 PD2 PD1 PD0

Cache

Size

Main

Memory

Max

Module

NC NC NC NC NC — — No Module

V

CC

V

CC

NC NC V

CC

128KB 16MB 32A732

V

CC

NC NC NC V

CC

128KB 32MB 32A832

V

CC

NC V

CC

NC V

CC

128KB 64MB 32A932

V

CC

V

CC

NC V

CC

NC 256KB 32MB 32A764

V

CC

NC NC V

CC

NC 256KB 64MB 32A864

V

CC

NC V

CC

V

CC

NC 256KB 128MB 32A964

MCM32A732/764•MCM32A832/864•MCM32A932/964

3

MOTOROLA FAST SRAM

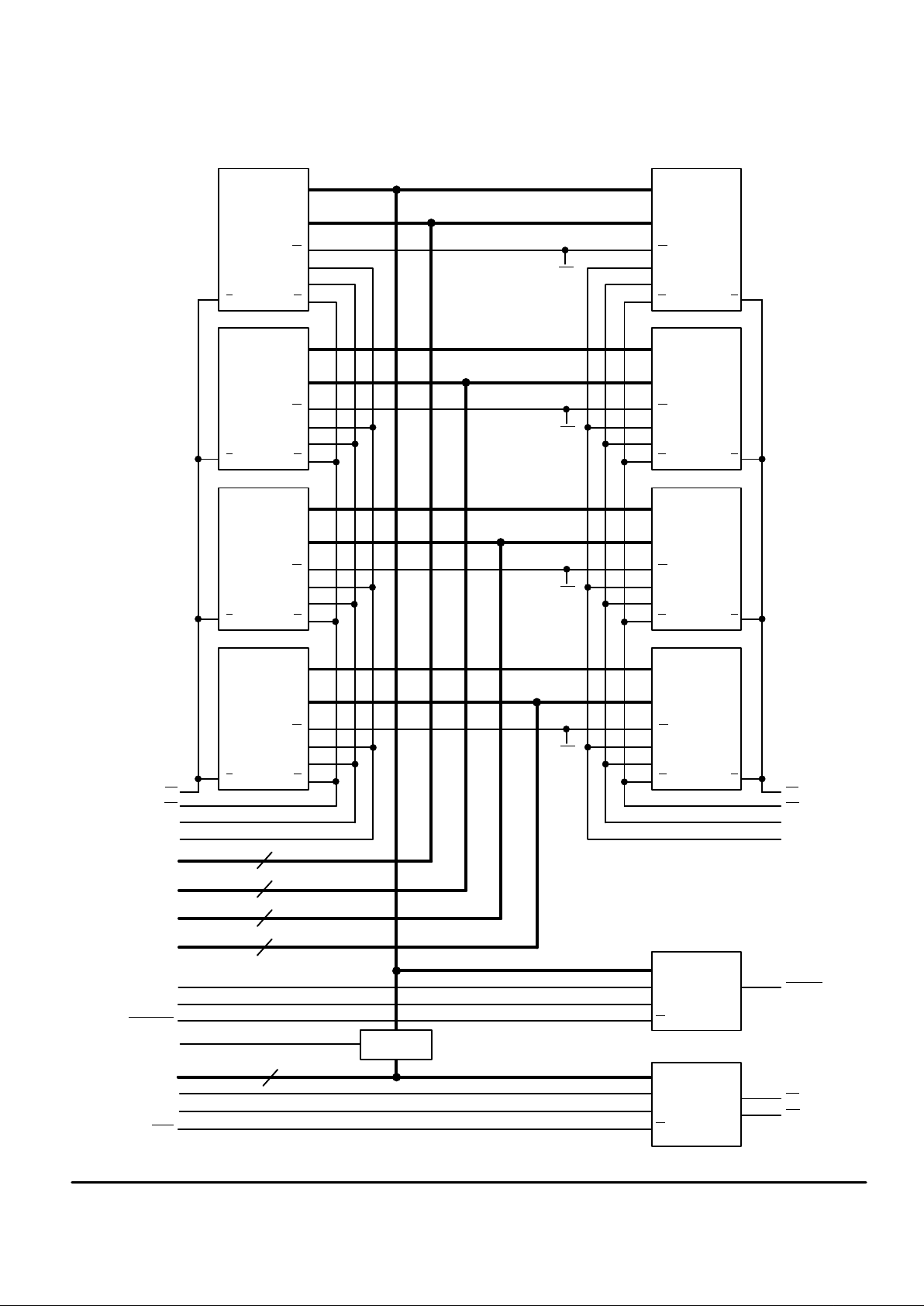

486 256KB CACHE MODULE BLOCK DIAGRAM

WITH 9 TAG BITS

A2 – A14 A2 – A14

DQ0 – DQ7 DQ0 – DQ7

W

A1

G

A0

E

32K x 8

W

A1

G

A0

E

32K x 8

W0

A2 – A14 A2 – A14

DQ0 – DQ7 DQ0 – DQ7

W

A1

G

A0

E

32K x 8

W

A1

G

A0

E

32K x 8

W1

A2 – A14 A2 – A14

DQ0 – DQ7 DQ0 – DQ7

W

A1

G

A0

E

32K x 8

W

A1

G

A0

E

32K x 8

W2

A2 – A14 A2 – A14

DQ0 – DQ7 DQ0 – DQ7

W

A1

G

A0

E

32K x 8

W

A1

G

A0

E

32K x 8

W3

E1

HCA3

G1

HCA2

E0

LCA3

G0

LCA2

DQ0 – DQ7

DQ8 – DQ15

DQ16 – DQ23

DQ24 – DQ31

DIRTYQ

DIRTYD

DIRTYWE

A0 – A13

D

in

D

out

W

16K x 1

74F373

ALE

DIRTYE

A0 – A13

DQ9

DQ0 – DQ8

W

16K x 10

TE

TG

TWE

TDQ0 – TDQ8

VALID

A4 – A17

8

8

8

8

14

MCM32A732/764•MCM32A832/864•MCM32A932/964

4

MOTOROLA FAST SRAM

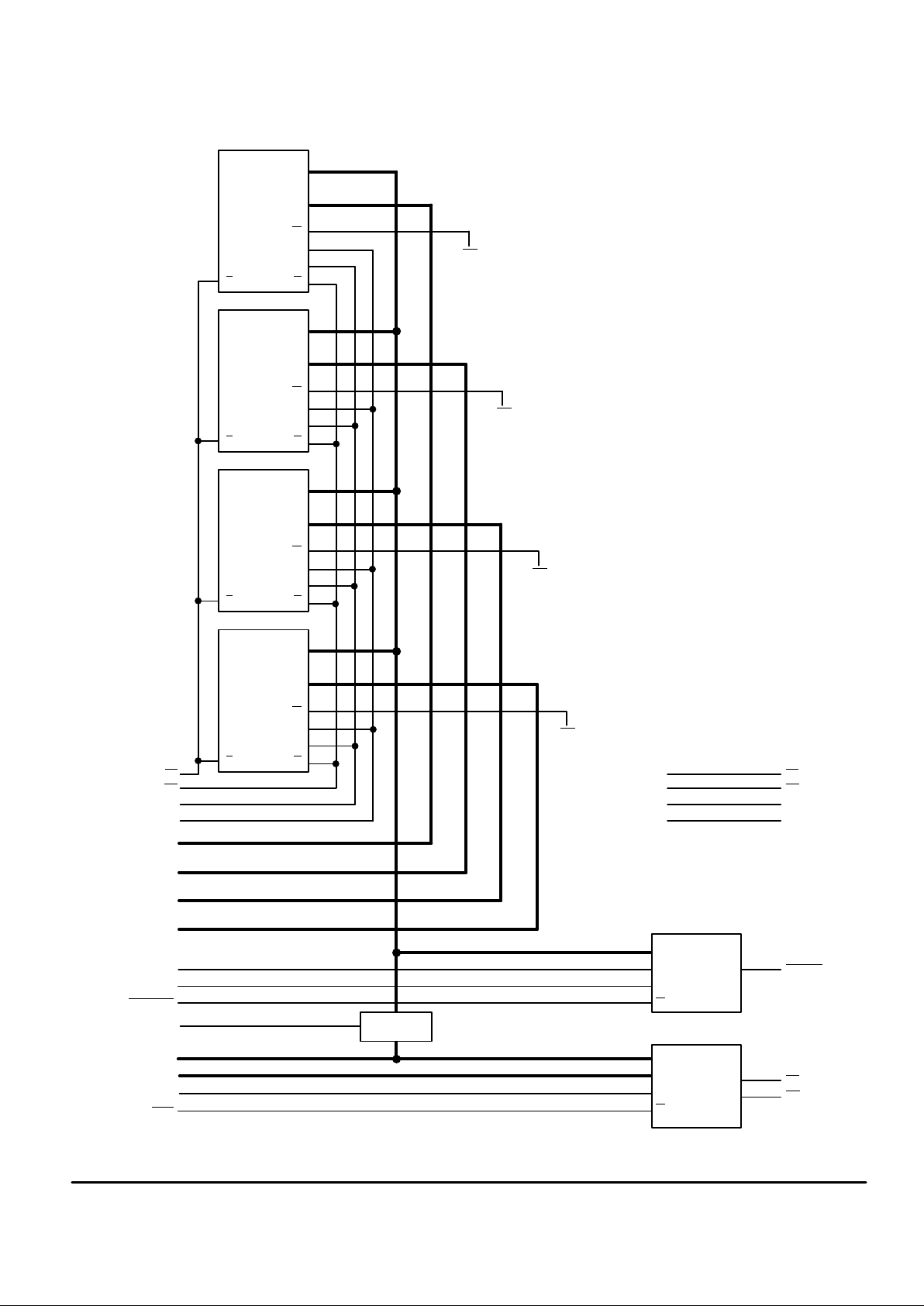

486 128KB CACHE MODULE BLOCK DIAGRAM

WITH 9 TAG BITS

A2 – A14

DQ0 – DQ7

W

A1

G

A0

E

32K x 8

W0

A2 – A14

DQ0 – DQ7

W

A1

G

A0

E

32K x 8

W1

A2 – A14

DQ0 – DQ7

W

A1

G

A0

E

32K x 8

W2

A2 – A14

DQ0 – DQ7

W

A1

G

A0

E

32K x 8

W3

E1

HCA3

G1

HCA2

E0

LCA3

G0

LCA2

DQ0 – DQ7

DQ8 – DQ15

DQ16 – DQ23

DQ24 – DQ31

DIRTYQ

DIRTYD

DIRTYWE

A0 – A12

D

in

D

out

W

8K x 1

74F373

ALE

DIRTYE

A0 – A12

DQ9

DQ0 – DQ8

W

8K x 10

TE

TG

TWE

TDQ0 – TDQ8

VALID

A4 – A17

NC

NC

NC

NC

Loading...

Loading...