MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Advance Information

ATM Cell Processor

The ATM Cell Processor (MC92501) is an Asynchronous Transfer Mode (ATM)

layer device composed of dedicated high-performance ingress and egress cell

processors combined with UTOPIA Level 2-compliant physical (PHY) and switch

interface ports (see Block Diagram). The MC92501 is a second generation ATM

cell processor in MotorolaÕs 92500 series. This document provides information

on the new features offered by the second generation ATM cell processor. This

document, combined with MC92500/D, provides the complete speciÞcation for

the ATM cell processor.

New Features of the MC92501:

¥ Implements ATM Layer Functions for Broadband ISDN According to ATM

Forum UNI 4.0 and TM 4.0 SpeciÞcations, ITU Recommendations, and

Bellcore Recommendations

¥ Provides ABR Relative Rate Marking and EFCI Marking According to TM 4.0

¥ Selective Discard CLP = 1 (or CLP = 0+1) Flow on Selected Connections

¥ UTOPIA Level 2 PHY Interface and UTOPIA ATM Layer Interface

¥ Supports Both Partial Packet Discard (PPD) and Early Packet Discard (EPD)

¥ Change ABR RM Cell Priority

¥ Support for CLP Transparency

Order this document

by MC92501/D

MC92501

GC SUFFIX

GTBGA

CASE 1208

ORDERING INFORMATION

MC92501GC GTBGA

Existing MC92500 Features:

¥ Full-Duplex Operation at Data Rates up to 155 Mbit/sec

¥ Performs Internal VPI and VCI Address Compression for up to 64K VCs

¥ CLP-Aware Peak, Average, and Burst-Length Policing with Programmable

Tag/Drop Action Per Policer

¥ Supports up to 16 Physical Links Using Dedicated Ingress/Egress MultiPHY

Control Signals

¥ Each Physical Link Can Be ConÞgured as Either a UNI or NNI Port

¥ Supports Multicast, Multiport Address Translation

¥ Maintains Both Virtual Connection and Physical Link Counters on Both

Ingress and Egress Cell Flows

¥ Provides a Flexible 32-Bit External Memory Port for Context Management

¥ Automated AIS, RDI, CC, and Loopback Functions with Performance

Monitoring Block Test on All 64K Connections

¥ Programmable 32-Bit Microprocessor Interface Supporting Big-Endian or

Little-Endian Bus Formats

¥ Bidirectional UPC or NPC Design with up to Four Leaky Buckets Per

Connection

¥ Supports a Programmable Number of Additional Switch Overhead

Parameters Allowing Adaptation to Any Switch Routing Header Format

¥ Provides Per-Link Cell Counters in Both Directions

This document contains information on a new product. SpeciÞcations and information herein are subject to change without notice.

REV 1.2

2/98 TN98020500

© Motorola, Inc. 1998

MOTOROLA

MC92501

1

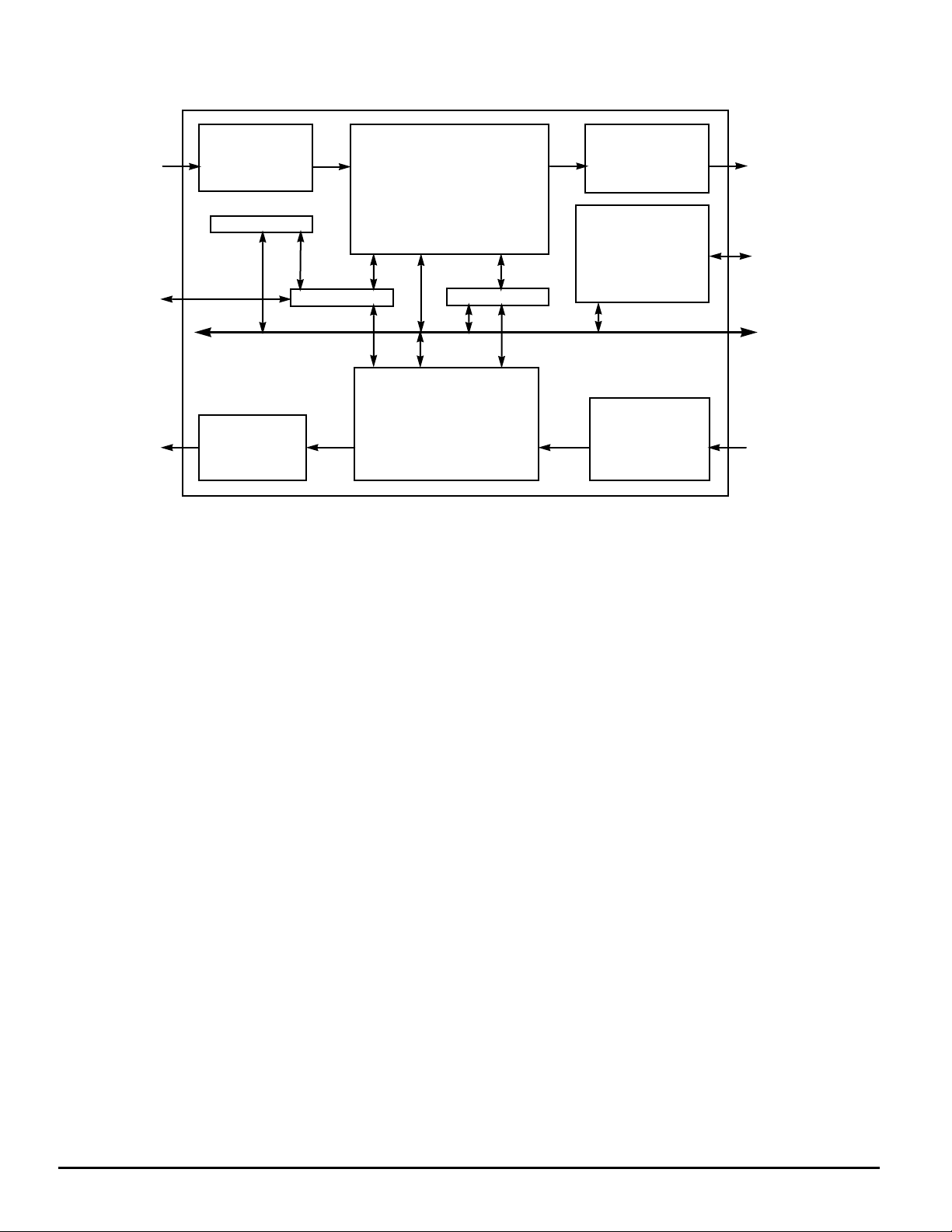

REPRESENTATIVE BLOCK DIAGRAM

UTOPIA IF

EXTERNAL

MEMORY IF

UTOPIA IF

INGRESS PHY IF

CRC Check (OAM)

MultiPHY Support

INTERNAL SCAN

EGRESS PHY IF

CRC Gen (OAM)

MultiPHY Support

Microprocessor Cell Insertion/Extraction

EXT MEMORY IF

Microprocessor Cell Insertion/Extraction

INGRESS CELL PROCESSOR

VP and VC Address Translation

NPC/UPC

Cell Counting

OAM Operations

Add Switch Parameters

FMC GENERATION

EGRESS CELL PROCESSOR

Multicast Translation

Cell Counting

OAM Operations

Address Translation

INGRESS SWITCH IF

CRC Generation

Independent Clock

MICROPROCESSOR IF

Cell Insertion

Cell Extraction

ConÞg Registers

Maintenance Access

EGRESS SWITCH IF

Extract Overhead

CRC Check

Independent Clock

UTOPIA IF

MICROPROCESSOR IF

UTOPIA IF

MC92501

2

MOTOROLA

TABLE OF CONTENTS

SECTION 1. ATM NETWORK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

1.1. ATM Network Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

1.2. ATM Network Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

SECTION 2. FUNCTIONAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.1. System Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.2. MC92501 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.3. First Generation Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

SECTION 3. PACKET-BASED UPC Discard Algorithms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.1. Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

3.1.1. AAL5 Packet Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

3.2. Cell-Based UPC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.3. Partial Packet Discard (PPD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3.4. Early Packet Discard (EPD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.5. Limited Early Packet Discard (Limited EPD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

SECTION 4. SELECTIVE DISCARD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

SECTION 5. Available Bit Rate (ABR) Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.1. Overview and Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.2. RM Cell Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

5.3. RM Cell Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.4. Cell Marking (CI, NI, PTI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5.4.1. Sources for Ingress Flow Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.4.1.1. Ingress Flow Status from Global Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.4.1.2. Ingress Flow Status from CellÕs Overhead . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.4.1.3. Ingress Flow Status from Context Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.4.1.4. Logic of Ingress Flow Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.4.2. Sources for Egress Flow Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.4.2.1. Egress Flow Status from Global Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

5.4.2.2. Egress Flow Status from CellÕs Overhead . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

5.4.2.3. Egress Flow Status from Context Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.4.2.4. Logic of Egress Flow Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.4.3. Ingress ABR Marking Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.4.3.1. Logic of Ingress ABR Marking Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.4.4. Egress ABR Marking Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

5.4.4.1. Logic of Egress ABR Marking Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

5.4.5. Cell Marking Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

5.5. Ingress Switch ABR Priority Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.5.1. An Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

5.6. Egress Reset EFCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

SECTION 6. CLP TRANSPARENCY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

6.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

SECTION 7. INDIRECT EXTERNAL MEMORY ACCESS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7.2. User Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7.2.1. Write Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7.2.2. Read Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

SECTION 8. IMPROVED HOST INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

8.1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

8.1.1. An Additional MDTACK Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

8.1.2. Programmable MREQ Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

8.1.3. Update the Definition of MWSH and MWSL Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

SECTION 9. EGRESS OVERHEAD MANIPULATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

SECTION 10. UTOPIA LEVEL 2 PHY INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

SECTION 11. Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

11.1. General Register List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

11.2. Status Reporting Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

11.2.1. Interrupt Register (IR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

11.2.2. Interrupt Mask Register (IMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

11.2.3. ATMC CFB Revision Register (ARR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

MOTOROLA

MC92501

3

TABLE OF CONTENTS (CONTINUED)

11.2.4. MC92501 Revision Register (RR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

11.3. Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

11.3.1. Ingress Processing Control Register (IPLR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

11.3.2. Egress Processing Control Register (EPLR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

11.3.3. Indirect External Memory Access Address Register (IAAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

11.3.4. Indirect External Memory Access Data Register (IADR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

11.4. Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

11.4.1. Ingress Processing Configuration Register (IPCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

11.4.2. Egress Processing Configuration Register (EPCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

11.4.3. ATMC CFB Configuration Register (ACR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

11.4.4. Egress Switch Interface Configuration Register (ESWCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

11.4.5. Egress Switch Overhead Information Register 0 (ESOIR0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

11.4.6. Microprocessor Configuration Register (MPCONR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

11.4.7. Maintenance Configuration Register (MACONR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

11.4.8. Ingress PHY Configuration Register (IPHCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

11.4.9. Egress PHY Configuration Register (EPHCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

11.4.10. MC92501 General Configuration Register (GCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

11.4.11. Egress Switch Overhead Information Register 1 (ESOIR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

11.4.12. RM Overlay Register (RMOR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

11.4.13. CLP Transparency Overlay Register (CTOR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

11.4.14. Context Parameters Extension Table Pointer Register (CPETP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

11.4.15. Egress Overhead Manipulation Register (EGOMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

SECTION 12. EXTERNAL MEMORY DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

12.1. Context Parameters Extension Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

12.1.1. Common Parameters Extension Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

12.2. CONTEXT PARAMETERS TABLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

12.2.1. Egress Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

12.2.2. Ingress Parameters: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

12.2.3. Common Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

SECTION 13. DATA STRUCTURES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

13.1. General Fields . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

13.1.1. Reason . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

SECTION 14. SIGNAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

14.1. Microproccessor Signals (MP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

14.2. Ingress PHY Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

14.3. Egress PHY Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

SECTION 15. TEST OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

15.1. Device Identification Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

15.2. Boundary Scan Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

SECTION 16. Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

16.1. Electrical Specification for Clocks and Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

16.2. DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

SECTION 17. Packaging Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

17.1. Additional Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

17.2. Pin Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

17.3. 256-Lead GTBGA Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

MC92501

4

MOTOROLA

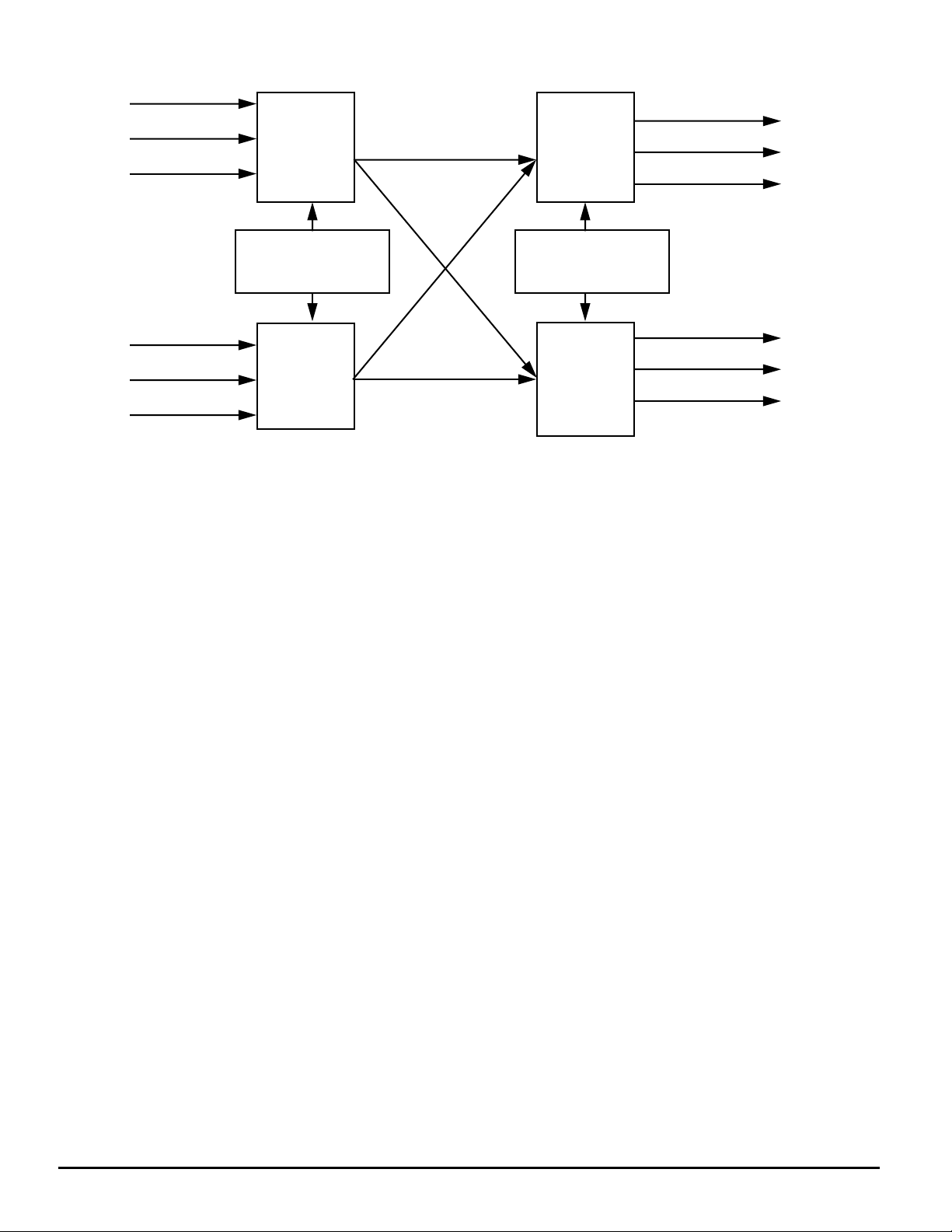

SECTION 1. ATM NETWORK

1.1. ATM Network Description

A typical ATM network consists of user end stations that

transmit and receive 53-byte data cells on virtual connections

(see Figure 1). Physical links and switching systems

interconnect the virtual connections. A virtual connectionÕs

path is established at the beginning of the data transfer,

maintained while the end-stations are communicating, and

torn down after the transfer is complete. This transmission

method increases the transfer speed because the

determination of the path the data will take is done only at the

beginning of the data transfer instead of when each data subblock or packet is transferred.

On a given physical link, each connection is assigned a

unique connection identiÞer. The connection identiÞer is

placed in the header of each cell by the transmitting equipment

and is used by the receiving equipment to route the cell to the

next physical link on the connection path. All cells belonging

to a speciÞc virtual connection follow the identical path from

VCs

Switch

the transmitting end station through the switching systems to

the receiving end station.

An ATM switch contains a high-speed switching fabric that

connects multiple line cards. The switching fabric connects the

input port to the output port based on the switchÕs routing table.

The line card interfaces between the physical medium and the

switching fabric by recovering incoming cells from the arriving

bit stream or converting outgoing cells into a bit stream for

transmission. An ATM swtich partitioned in this fashion can

efÞciently handle multiple physical links by independently

transferring each incoming ATM cell from its source port to its

destination port, based on the switchÕs routing table.

ATM standards divide the tasks to be performed on each

side of the switch fabric into PHY layer and ATM layer tasks.

The PHY layer tasks are dependent on the physical medium

that connects ATM switches. The ATM layer tasks operate at

the cell level and are independent of the physical medium.

Switch

VCs

END STATIONS

SWITCH

CLK REC

Switch

LINE

CARD

PHY

Switch Switch Switch

SWITCHING FABRIC

MC92501

ATM LAYER FUNCTIONS

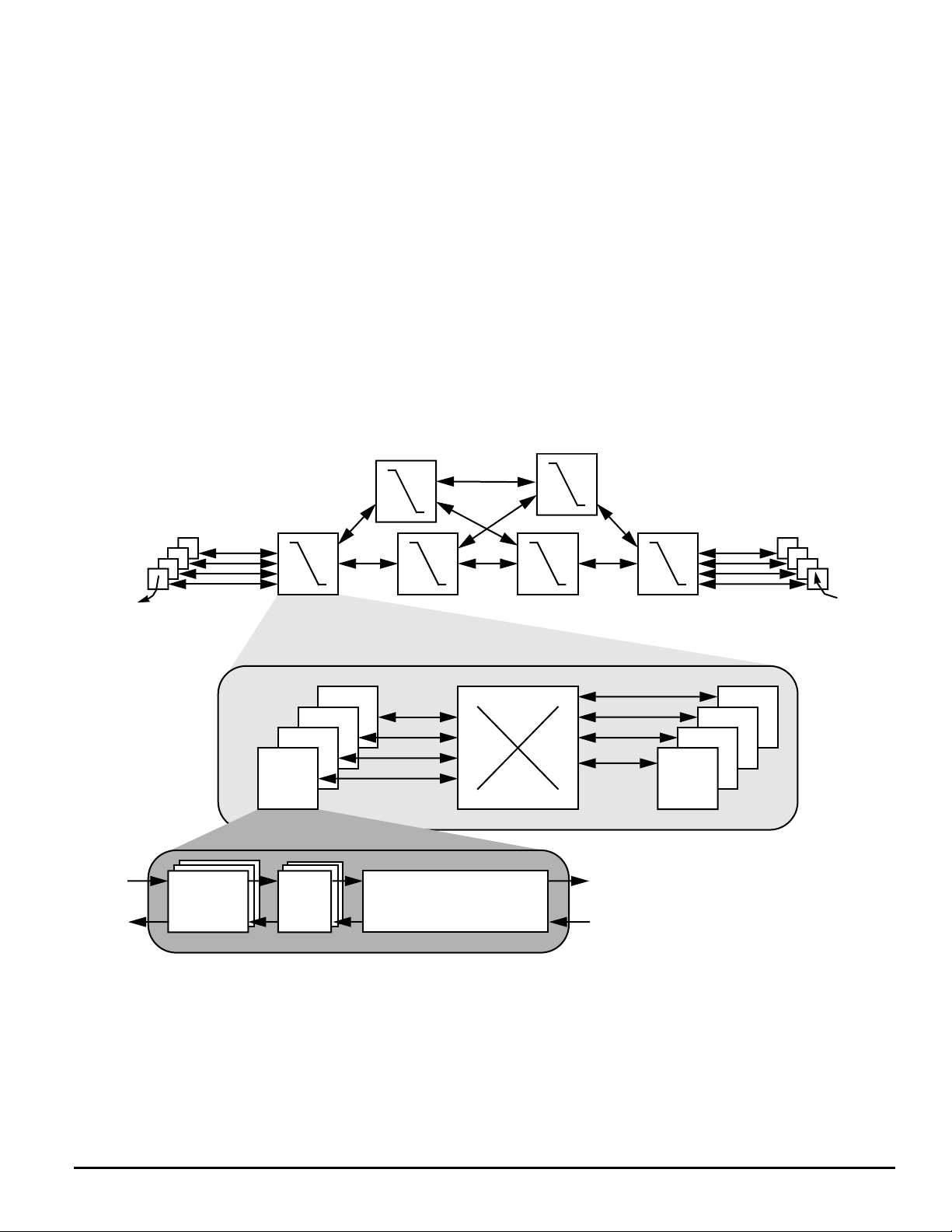

Figure 1. MC92501 in an ATM Network Application

END STATIONS

LINE

CARD

LINE CARD

MOTOROLA

MC92501

5

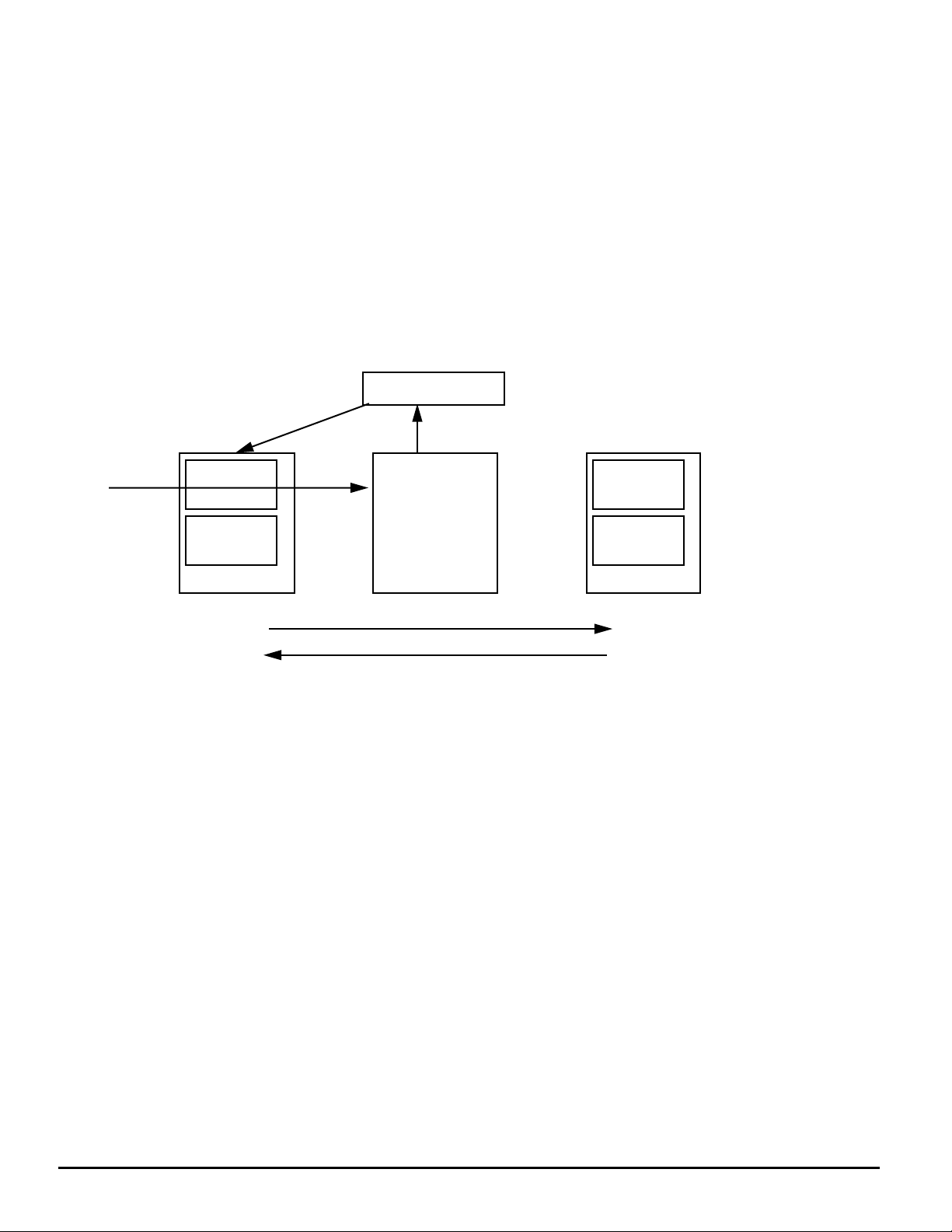

1.2. ATM Network Applications

The MC92501 performs the ATM layer functions in an ATM

switch such as cell processing and routing. Since the

MC92501 is an ATM layer device, it is PHY layer independent.

Figure 2 illustrates a typical ATM line card. The MC92501

uses an external memory for storing the cells that it

processes. In addition, the MC92501 offers an option to utilize

an external address compression device accessed via the

same external memory bus.

The microprocessor is used for conÞguration, control, and

status monitoring of the MC92501 and is responsible for

initializing and maintaining the external memory. The

MC92501 is the master of the external memory bus. At regular

intervals, the MC92501 allows the microprocessor to access

the external memory for updating and maintenance.

System RAM can also be located on the line card. The

MC92501 can support a DMA device to allow efÞcient data

transfer to this RAM without processor intervention.

RAM

MICRO-

PROCESSOR

DMA

DMA

The physical interface (PHY-IF) implements the physical

layer functions of the B-ISDN Protocol Reference Model. This

includes the physical medium dependent functions required

to transport ATM cells between the ATM user and the ATM

switch (UNI) or between two ATM switches (NNI). The cells

are transferred between the physical interface and the

MC92501 using the UTOPIA Level 2 standard.

The MC92501 implements B-ISDN UNI/NNI ATM layer

functions required to transfer cells to and from the switch over

virtual connections. These functions include usage

enforcement, address translation, and Operation,

Administration, and Maintenance (OAM) processing. The

MC92501 provides context management for up to 65,536

(64K) Virtual Connections (VCs). The VCs can be either Virtual

Path Connections (VPCs) or Virtual Channel Connections

(VCCs). ATM cells belonging to a particular VCC on a logical

link have the same unique Virtual Path IdentiÞer/Virtual

Channel IdentiÞer (VPI/VCI) value in the cell header. Similarly,

cells belonging to a particular VPC on the same logical link

share a unique VPI.

EXTERNAL

MEMORY

EXTERNAL

ADDRESS

COMPRESSION

MICROPROCESSOR BUS

RECOVERY

LINE CARD

CLOCK

PHY-IF

PHY-IF

PHY IF

MC92501

Figure 2. Typical MC92501 Line Card Application

EXTERNAL

MEMORY

BUS

TO SWITCH

FROM SWITCH

MC92501

6

MOTOROLA

SECTION 2. FUNCTIONAL DESCRIPTION

2.1. System Functional Description

A serial transmission link operating at up to 155.52 Mbit/sec

(PHY) is coupled to the MC92501 via a byte-based interface.

The transmission link timing is adapted to the MC92501 and

switch timing by means of internal cell buffers. A common clock

supplies both the PHY IF and MC92501.

The host microprocessor initializes and provides real-time

control information to the data-ßow chips (PHY IF and

MC92501) using slave accesses.

The MC92501 operates in conjunction with an external

connection memory, which provides one context entry for each

active connection. The entry consists of two types of context

parameters: static and dynamic. The static parameters are

loaded into the context memory when the VC is established,

and are valid for the duration of that connection. The static

parameters include trafÞc descriptors, OAM ßags, and ATM

switch parameters. The dynamic context parameters include

cell counters, UPC/NPC Þelds, and OAM parameters. The

dynamic parameters can be modiÞed while a particular

connection is being processed. The microprocessor can

access the external memory through the MC92501 to collect

trafÞc statistics and to update the OAM parameters. During

normal cell processing, the MC92501 has exclusive access

to the external memory and maintains external memory

coherency.

At user-programmable intervals, the MC92501 provides the

microprocessor with a Òmaintenance slot.Ó During this time,

cell processing is halted and control of the external memory

bus is relinquished. The break in cell processing is made

possible by the difference between the MC92501 cellprocessing rate and the line rate.

The microprocessor can use the maintenance slot for any

of the following tasks:

¥ Connection setup and tear down

¥ Statistics collection

¥ Updating OAM parameters of active connection

The microprocessor is responsible for the external memory

coherency during the maintenance interval.

2.2. MC92501 Functional Description

MC92501 General Features:

¥ Implements ATM layer functions for broadband ISDN

according to CCITT recommendations, ATM Forum

UNI 4.0 and TM 4.0 speciÞcations, and ITU and Bellcore

recommendations.

¥ Provides 155 Mbit/sec throughput capacity and is physical

layer independent.

¥ Optionally supports up to 16 physical links.

¥ Optionally conÞgured as a User Network Interface (UNI) or

Network Node Interface (NNI) on a per-link basis.

¥ Provides Available Bit RateÐRelative Rate (ABRÐRR)

marking and EFCI marking according to TM 4.0.

¥ Supports advanced discard policies such as Selective

Discard, Partial Packet Discard (PPD), Early Packet

Discard (EPD), and Limited Early Packet Discard (Limited

EPD).

¥ Operates in conjunction with an external memory (up to

16 MB) to provide context management for up to 64K virtual

connections.

¥ Provides cell counter coherency on a per-connection basis

by maintaining redundant copies of the counter tables and

dynamically switching between them.

¥ Provides per-link cell counters in both directions.

¥ Provides per-connection Usage Parameter Control (UPC)

or Network Parameter Control (NPC) using a leaky bucket

design with up to four buckets per connection.

¥ Provides support for Operation, Administration, and

Maintenance (OAM) Continuity Check function for all

connections.

¥ Supports Virtual Path (VP) and Virtual Channel (VC) level

alarm surveillance, OAM fault management loopback test,

and OAM performance monitoring on all connections.

¥ Interfaces with either big-endian or little-endian

microprocessors.

¥ Supports cell insertion into the cell streams using direct

access registers which may be written by the

microprocessor or by a DMA device.

¥ Supports copying cells from the cell streams using direct

access registers which may be read by the microprocessor

or by a DMA device.

¥ Supports multicast operation.

2.3. First Generation Features

The MC92501 is a second generation ATM cell processor

that enhances the MC92500 (Þrst generation) functionality.

The MC92501 is backwards-compatible and pincompatible with the MC92500.

This document describes the second generation

enhancements and is meant to supplement the MC92500

speciÞcation. The MC92500 speciÞcation can be ordered from

the Motorola Literature Center by requesting document

MC92500/D.

MOTOROLA

MC92501

7

SECTION 3. PACKET-BASED UPC DISCARD ALGORITHMS

3.1. Introduction

The MC92501 UPC function performs cell-based discard or

packet-based discard according to ATM Forum TM 4.0. It

supports packet discard on VC connections AAL5 packets (not

including OAM cells). The MC92501 also performs Partial

Packet Discard or Early Packet Discard.

The MC92501 offers four modes of UPC operation on a perconnection basis: Cell-Based UPC, Partial Packet Discard

(PPD), Early Packet Discard (EPD), and Limited Early Packet

Discard (Limited EPD). These modes are selected on a perconnection basis using the

Mode

bit in the Common Extension Parameters Table. Packet-

based UPC is enabled globally by the

Enable

bit in the ACR register.

IUOMÑIngress UPC Operation

IPCVÑIngress Features

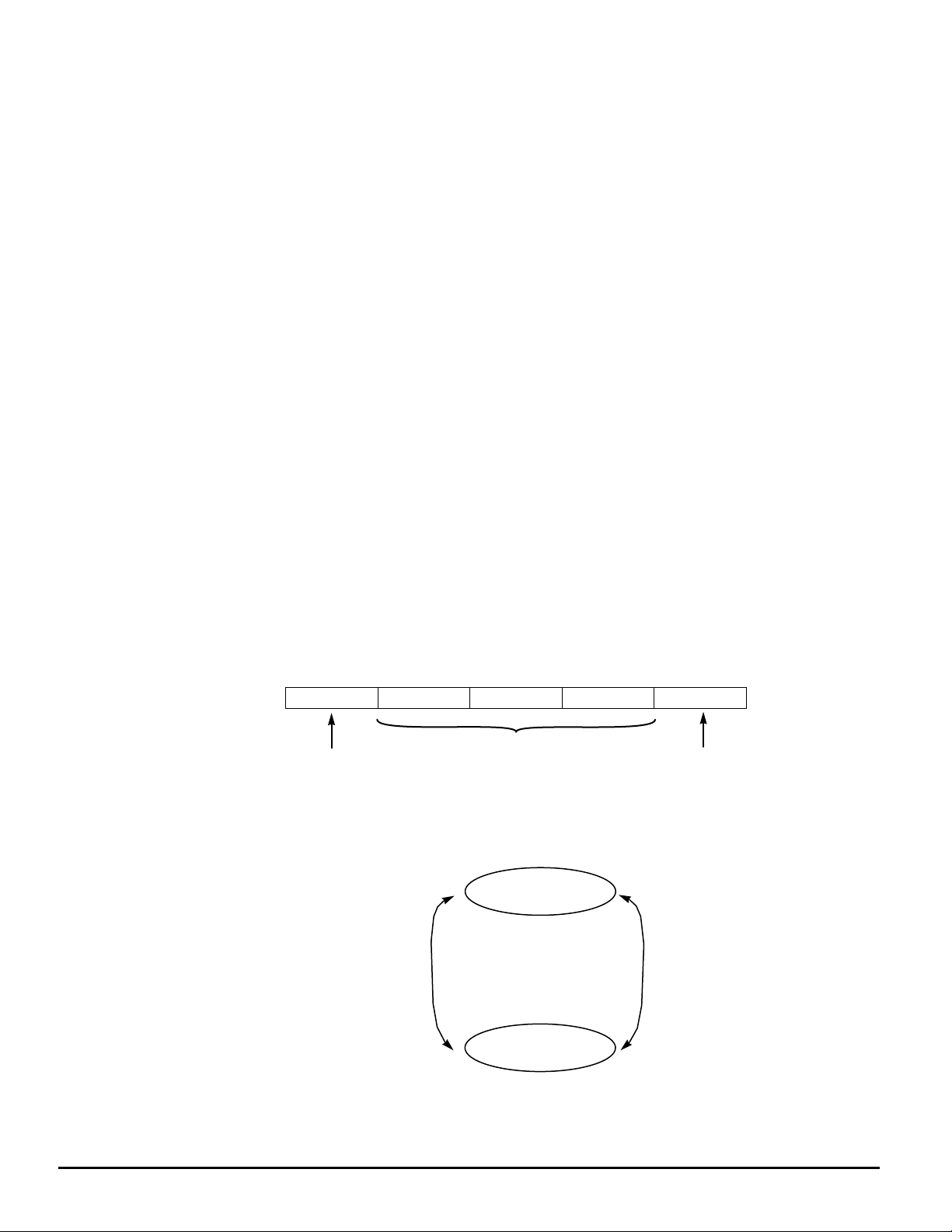

3.1.1. AAL5 Packet Definition

A packet is deÞned as a stream of user cells belonging to

the same virtual connection that has a series of one or more

cells with the PTI[0] bit set to 0 and the last PTI[0] bit set to 1.

(See Figure 3.)

3.2. Cell-Based UPC

This is the default mode. The MC92501 discards cells on a

per-cell basis as deÞned in MC92500/D.

3.3. Partial Packet Discard (PPD)

According to the PPD algorithm, if a cell is discarded then

all subsequent cells belonging to that packet are discarded up

to but not including the last cell. Following is a detailed

explanation of the UPC function.

¥ The UPC is a two-state machine: discarding and not-

discarding. See Figure 4.

¥ While the UPC is in the not-discarding state, it performs

normal cell-based operation with tagging and policing

counter updates.

¥ The UPC transitions from the not-discarding to the

discarding state on the Þrst discarded cell.

¥ While the UPC is in the discarding state, it does not update

the UPC bucket but it does increment the policing discard

counter.

¥ When in the discarding state and the last cell of a packet

is received, there are two options:

Ñ If

all the cells belonging to that packet were discarded,

then this last cell is discarded.

Ñ If

not all the cells belonging to that packet were

discarded, then this means that the packet was

truncated and this last cell is admitted in order to

delineate the corrupted packet from the next packet.

There is however one exception: if this last cell is

violating cell-based UPC then it is discarded.

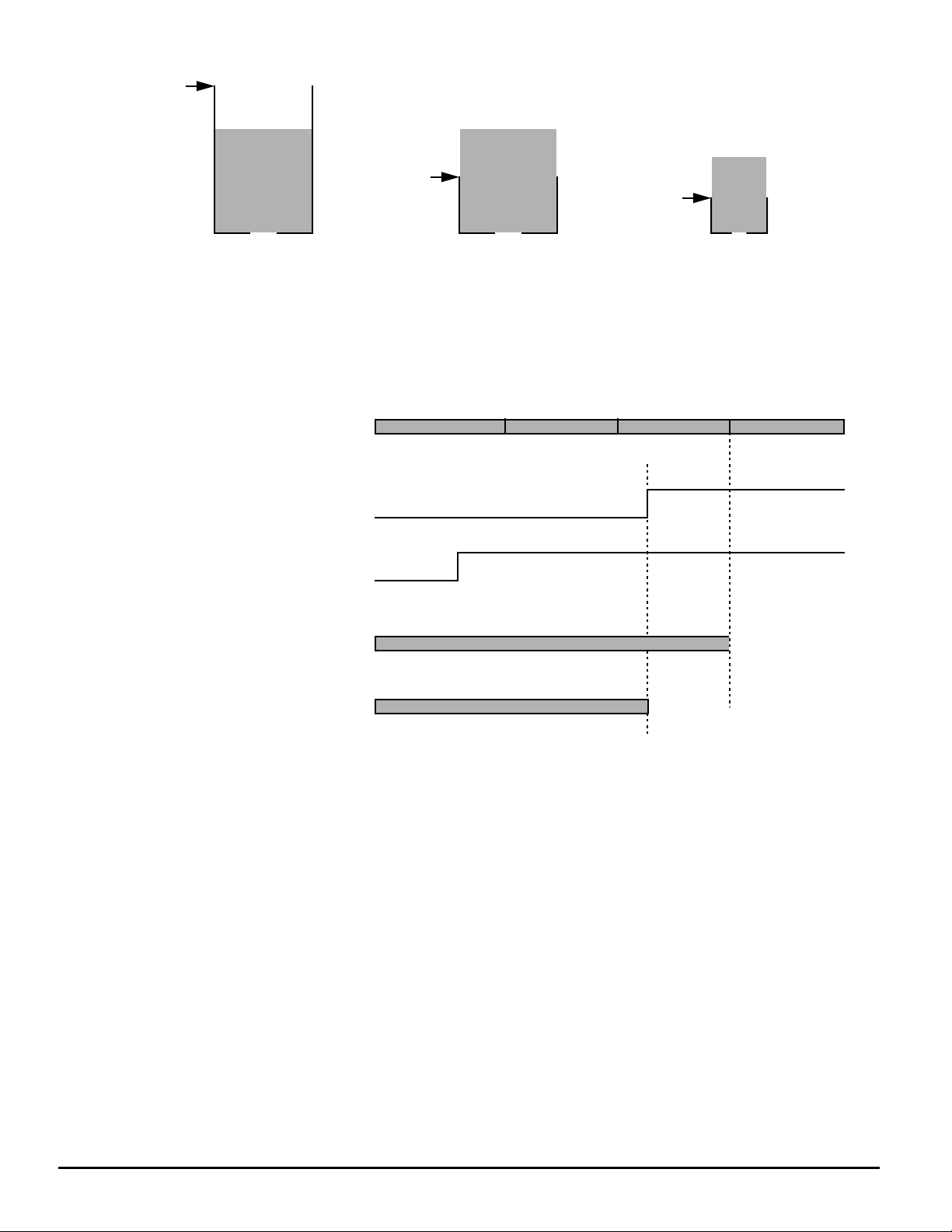

Figure 5 illustrates an example for the PPD algorithm. A

UPC policy violation occurs during the transmission of the Þrst

packet. The UPC detects the violation and discards the

remainder of the packet except for the last cell. The last cell

of the Þrst packet is transmitted to avoid the concatenation of

the corrupted packet with the subsequent Packet #2. If the

UPC detects that the Þrst cell of Packet #3 violates its policy

then Packet #3 is truncated. Packet #3Õs last cell is not

transmitted because it cannot be admitted by the cell-based

UPC. Packet #4 is not transmitted either because its Þrst cell

violates the UPC policy.

CELL STREAM

PTI[0] = 1 PTI[0] = 0 PTI[0] = 0 PTI[0] = 1 PTI[0] = 0

LAST CELL OF

PACKET 0

Figure 3. Delineation of a Packet Within a Cell Stream

LAST CELL OF PACKET ARRIVES

If all cells within a packet are discard

OR

If the last cell is violating UPC policy

then discard the last cell

If not all calls within packet discarded, then admit last cell

Figure 4. UPC Discarding State Machine

PACKET 1

NOT-DISCARDING

DISCARDING

FIRST CELL OF

PACKET 2

CELL VIOLATES

UPC POLICY

MC92501

8

MOTOROLA

Input Stream

UPC Discard Decision

Packet #1 Packet #2 Packet #3 Packet #4

Output Stream

L

Figure 5. Partial Packet Discard

3.4. Early Packet Discard (EPD)

According to the EPD algorithm, the decision to discard a

packet takes place only at the beginning of a packet. This

means that the complete packet is either fully discarded or

fully passed. The following explains how EPD is implemented.

¥ When the EPD is discarding cells, the buckets are not

updated but the policing discard counter is incremented.

¥ When the EPD decides that a frame should be passed this

means that:

Ñ All tagging buckets continue to work in a cell-based

fashion.

Ñ All discarding buckets perform their calculations as if

the limit parameter is inÞnite, and therefore increment

the bucket content and do not discard any cells. As a

result, their bucket content can be greater than their

bucket limit.

Ñ The MC92501 may increment its police tagging counter.

Figure 6 illustrates an example for the EPD algorithm. A cell

within the Þrst packet violates the UPC, but due to EPD this

packet is fully passed. Since the Þrst cell of Packet #2 violates

the UPC, the second packet is fully discarded. Likewise, cells

within Packet #3 violate the UPC, but this packet is not

discarded. Since the fourth packet comes after a relatively

long time, which allows the UPC buckets to drain, Packet #4Õs

cells do not violate the UPC policy.

3.5. Limited Early Packet Discard (Limited

EPD)

One disadvantage of the EPD algorithm is that once it

decides to admit a packet it cannot change its decision until

the last cell of that packet. In the case of big packets, the switch

can run into congestion. Using the Limited EPD algorithm, a

connection can stop passing cells because of EPD once it

reaches a predeÞned limit. That limit, in the case of the

MC92501, is reached once the

cells. The Þrst bucket should have the same parameters as

one of the other buckets except for the limit, which is bigger.

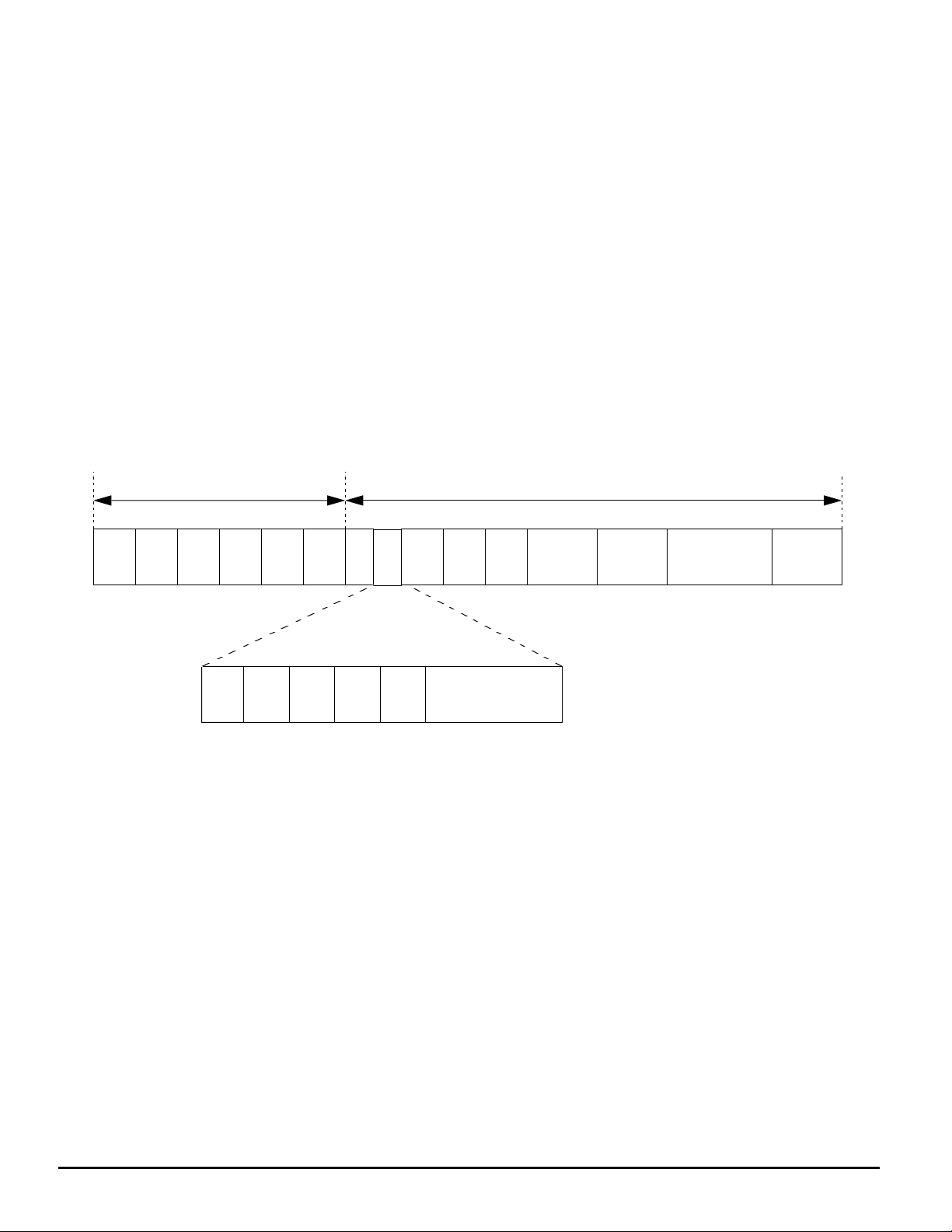

Figure 7 describes a UPC which contains three buckets.

The Þrst bucket is for limiting EPD, and there are two other

buckets. The Þrst and second buckets share the same

parameters except for the limit. Therefore, their bucket content

is always the same, although the second bucketÕs content is

higher than its limit and cells are admitted by the EPD

algorithm. When the Þrst bucket reaches its limit, then cells

will be discarded.

Figure 8 describes the EPD and Limited EPD functions.

Þrst bucket starts discarding

Input Stream

UPC Discard Decision

Output Stream

MOTOROLA

Packet #1 Packet #2

Figure 6. Early Packet Discard

Packet #3

Packet #4

MC92501

9

Limit

Limit

Limit

First Bucket Second Bucket Third Bucket

Figure 7. Limited Early Packet Discard

.

Input Stream

First Bucket Limit

Other BucketsÕ Limit

EPDÐUPC Output Stream

Limited EPDÐUPC Output Stream

Figure 8. Difference Between Early Packet Discard and Limited Early Packet Discard

Packet #1 Packet #2

Packet #3

Packet #4

MC92501

10

MOTOROLA

SECTION 4. SELECTIVE DISCARD

ATM Forum TM 4.0 deÞnes procedures according to which

cells can be discarded by network elements. A switching

element may discard cells belonging to selected connections

or cells whose CLP = 1 in case of congestion. This function is

called selective discard and it is implemented by the

MC92501. Selective discard is enabled by the

Ingress Congestion NotiÞcation

Control Register (IPLR). Selective discard can be enabled on

bit in the Ingress Processing

ICNGÑGlobal

a per-connection basis by the

Discard Operation Mode

Extension Word. This Þeld determines whether selective

discard is enabled and whether selective discard is performed

on CLP = 1 or on CLP = 0+1 trafÞc. Selective discard can be

enabled globally by the

CFB ConÞguration Register (ACR).

Þeld in the Common Parameters

IPCVÑIngress Enable bit in the ATMC

ISDMÑIngress Selective

MOTOROLA

MC92501

11

SECTION 5. AVAILABLE BIT RATE (ABR) SUPPORT

5.1. Overview and Features

The MC92501 provides a full Available Bit Rate (ABR)

solution for switch behavior relative rate marking and EFCI

marking in accordance with ATM Forum TM 4.0. It also

provides the switch fabric with an interface to increase the RM

cellsÕ trafÞc priority. Following is a list of features:

¥ Performs Relative Rate (RR) marking on Forward

Resource Management (FRM) and/or Backward Resource

Managment (BRM) cells, on selected connections. This

feature is enabled by either setting the ATMC CFB

ConÞguration RegisterÕs (ACR) VP RM Cell PTI (NPRP) bit

or by setting the PTI Þeld in the cellÕs header to Ò110BÓ.

¥ Performs EFCI marking on non-RM cells whose PTI[2] =

0, on selected connections. This feature is enabled by

either control registers or by Þelds that it gets from the

overhead of cells which are received from the switch fabric.

¥ Resets EFCI on non-RM cells whose PTI[2] = 0, on

selected connections.

Header = 5 bytes Payload = 48 bytes

GFC/ VPI

VPI

VCI

PTI CLP HEC

8

PID ER CCR MCR QL SN

2 x 8 4 x 8 4 x 82 x 8 2 x 8

8 30 x 8 + 6

¥ Checks CRC on received RM cells and generates CRC for

transmitted RM cells.

¥ Provides different priority to RM cells.

¥ Can copy RM cells to the microprocessor or remove them

from the ßow.

5.2. RM Cell Definition

A cell is an RM cell if and only if at least one of the following

conditions is met:

¥ The cell belongs to a VC connection and its PTI = 6.

¥ The cell belongs to a VP connection, its VCI = 6, and its

PTI = 6.

¥ The cell belongs to a VP connection, its VCI = 6, and the

ATMC CFB ConÞguration Register has the

Cell PTI

bit set.

VPRPÑVP RM

5.3. RM Cell Fields

10

Reserved

CRC-10

DIR

BN

1

1

NOTES:

PID = 1

DIR = Direction

¥ 0 = Forward RM cell

¥ 1 = Backward RM cell

BN = Backward Explicit Congestion

¥ 0 = Generated by source

¥ 1 = Generated not by the source

CI = Congestion Indication

NI = No Increase Bit

ER = Explicit Rate

CCR = Current Cell Rate

MCR = Minimum Cell Rate

CRC - 10

CI 1NI 1RA

1

Figure 9. RM Cell Fields

Reserved

3

MC92501

12

MOTOROLA

5.4. Cell Marking (CI, NI, PTI)

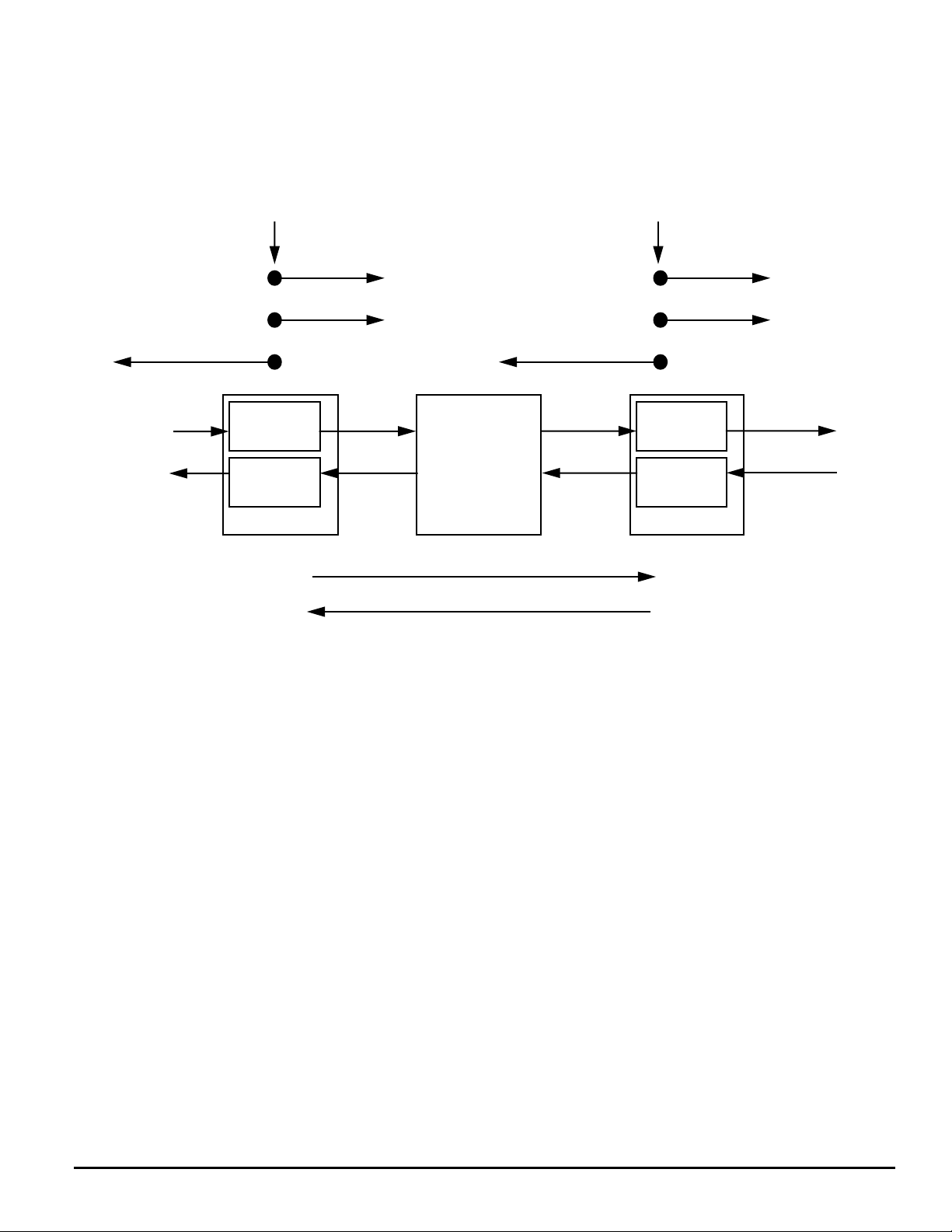

Figure 10 illustrates two MC92501 devices connected to a

switch fabric. In this example, the ABR ßow travels from left to

right. This means that data cells are ßowing from left to right,

FRM cells are ßowing from left to right, and BRM cells are

ßowing from right to left. The switch marks FRM and user cells

Ingress Flow Status

Ingress User Cell Marking (EFCI)

Ingress FRM Cell Marking (CI or NI)

Egress BRM Cell Marking (CI or NI)

EFCI, FRM

BRM

Ingress

Switch Fabric

Egress

MC92501 #1 MC92501 #2

ßowing downstream, and BRM cells ßowing upstream. This

switch function can be implemented in the ingress of MC92501

#1 and in the egress of MC92501 #2. MC92501 #1 marks cells

because of the ingress ßow status (for example, ingress ßow

congestion) while MC92501 #2 marks cells because of the

egress ßow status.

Egress Flow Status

Egress User Cell Marking (EFCI)

Egress FRM Cell Marking (CI or NI)

Ingress BRM Cell Marking (CI or NI)

Egress

Ingress

Downstream Direction

Upstream Direction

Figure 10. ABR Flow Cell Marking Example

The MC92501 can take the following actions in response to

the ingress ßow status:

¥ Perform EFCI marking on ingress cells; i.e., set PTI[1] bit

in cells on which PTI[2] = 0.

¥ Set CI or NI in ingress FRM cells.

¥ Set CI or NI in egress BRM cells.

The MC92501 can take the following actions in response to

the egress ßow status:

¥ Perform EFCI marking on egress cells; i.e., set PTI[1] bit

in cells on which PTI[2] = 0.

¥ Set CI or NI in egress FRM cells.

¥ Set CI or NI in ingress BRM cells.

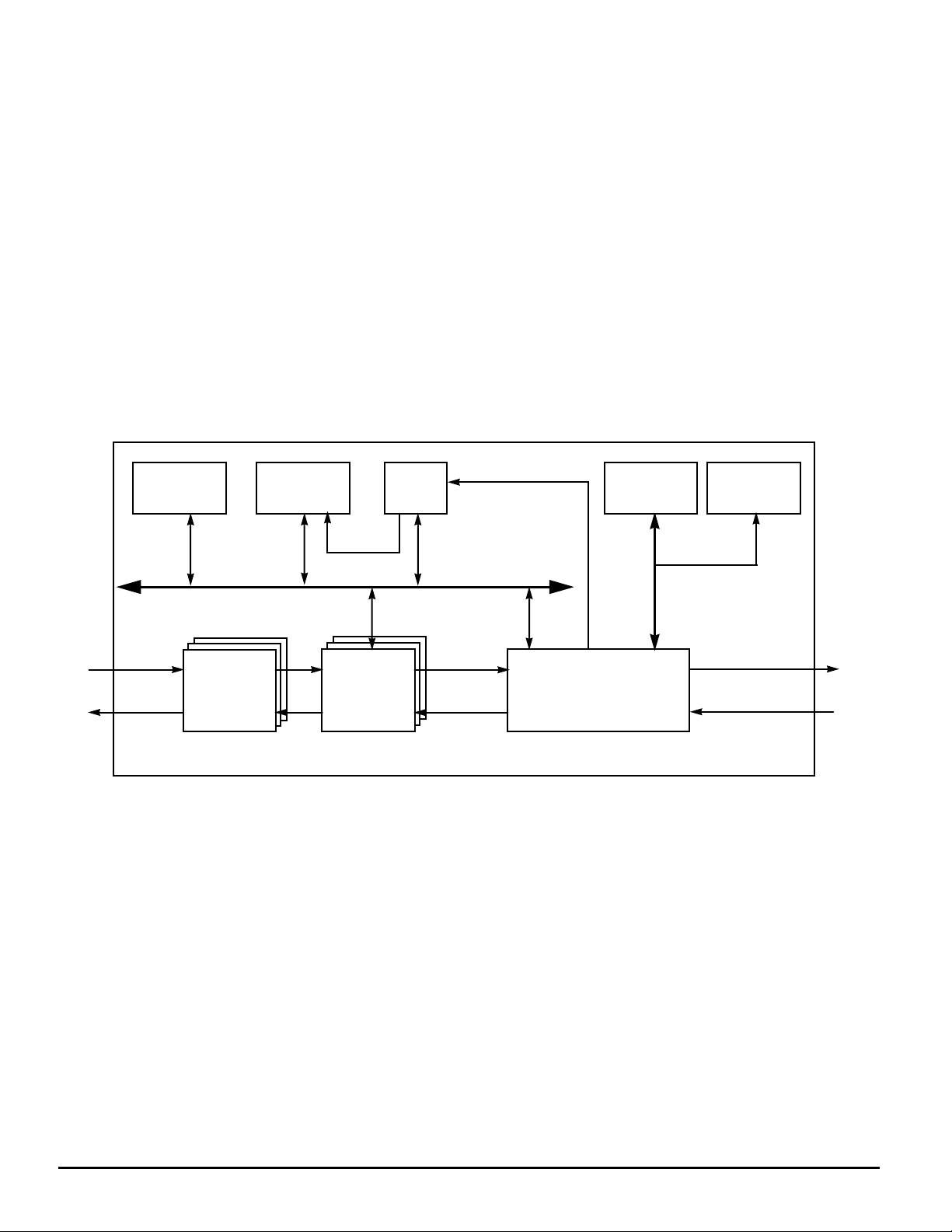

Figure 11 is an overview of the MC92501 marking scheme.

MOTOROLA

MC92501

13

OR

Global Reg.

CellÕs Overhead

Context Bit

Ingress

Status

Collection

Global Registers

Ingress Flow Status

Ingress

Action:

Marking

Global Registers

Context Bits

Cell Type

Set CI

Set NI

Set PTI

Global Reg.

CellÕs Overhead

Context Bit

Egress

Status

Collection

Egress Flow Status

Figure 11. Cell Marking Scheme

There are various ways to inform the MC92501 that it should

mark a cell due to the ingress ßow status or the egress ßow

status. This scheme also shows that the status of the ingress

ßow, the status of the egress ßow, global registers, a context

bit, and the cell type impact the decision of setting CI, NI, and

PTI. Following is a detailed description of each of the function

boxes.

5.4.1. Sources for Ingress Flow Status

The ingress ßow status is gathered from three sources:

global register, cellÕs overhead, or context bit.

5.4.1.1. Ingress Flow Status from Global Register

The switch fabric can notify the MC92501 that it should mark

cells because of the ingress ßow status by setting the

Global Ingress ABR Mark Enable

bit in the Ingress Processing

Control Register (IPLR).

5.4.1.2. Ingress Flow Status from CellÕs Overhead

The switch fabric can notify the MC92501 that it should mark

cells because of the ingress ßow status of connection #n by

setting the

IFSÑOverhead Ingress Flow Status bit in the

overhead of egress cells belonging to that connection. The

location of this bit in the overhead is programmable using the

EIBYÑIFS Byte Location bit and the EIBIÑIFS Bit Location

bit in the Egress Switch Overhead Information Register 1

(ESOIR1). This bit is enabled by the

EIASÑGlobal IFS Enable

bit in the Egress Switch Interface ConÞguration Register

(ESWCR). The MC92501 can be programmed that in such a

case it will mark egress BRM cells.

IAMEÑ

Set CI

Egress

Action:

Marking

Section 5.4.1.2 for details on enabling of

Ingress Flow Status

receives that cell, it copies the bit into the

Ingress Flow Status

Set NI

Set PTI

IFSÑOverhead

bit and its location.) When the MC92501

CIFSÑConnection

bit in the Common Parameters Extension

Word of connection #n. The MC92501 can be programmed

that in such a case it will mark ingress FRM cells or perform

EFCI marking.

5.4.1.4. Logic of Ingress Flow Status

The ingress ßow status equals 1 if:

IAME = 1

IFS = 1 and EIAS = 1 and egress = 1 OR

CIFS = 1 and EIAS = 1 and ingress = 1

Where:

IAME = Global Ingress ABR Mark Enable

IFS = Overhead Ingress Flow Status

EIAS = Global IFS Enable

CIFS = Connection IFS Enable

Egress = Programmed Overhead Egress Bit

Ingress = Programmed Overhead Ingress Bit

5.4.2. Sources for Egress Flow Status

The egress ßow status is gathered from three sources:

global register, cellÕs overhead, and context memory.

5.4.2.1. Egress Flow Status from Global Register

The switch fabric can notify the MC92501 that it should mark

cells because of the egress ßow status by setting the

Global Egress ABR Mark Enable

bit in the Egress Processing

EAMEÑ

Control Register (EPLR).

5.4.1.3. Ingress Flow Status from Context Memory

The switch fabric can notify the MC92501 that it should mark

cells because of the ingress ßow status of connection #n by

setting the

IFSÑOverhead Ingress Flow Status bit in the

overhead of egress cells belonging to that connection. (See

MC92501

14

5.4.2.2. Egress Flow Status from CellÕs Overhead

The switch fabric can notify the MC92501 that it should mark

cells because of the egress ßow status of connection #n by

setting the

EFSÑOverhead Egress Flow Status bit in the

overhead of egress cells belonging to that connection. The

MOTOROLA

location of this bit in the overhead is programmable using the

EEBYÑEFS Byte Location bit and the EEBIÑEFS Bit

Location

Register 1 (ESOIR1). This bit is enabled by the

EFS Enable

Register (ESWCR). The MC92501 can be programmed that

in such a case it will mark egress FRM cells or perform EFCI

marking.

5.4.2.3. Egress Flow Status from Context Memory

cells because of the egress ßow status of connection #n by

setting the

overhead of egress cells belonging to that connection. (See

Section 5.4.2.2 for details on enabling of EFSÑOverhead

Egress Flow Status bit and its location.) When the MC92501

receives that cell, it copies the bit into the CEFSÑConnection

Egress Flow Status bit in the Common Parameters Extension

Word of connection #n. The MC92501 can be programmed

that in such a case it will mark ingress BRM cells.

5.4.2.4. Logic of Egress Flow Status

5.4.3. Ingress ABR Marking Bits

ßow status or egress ßow status.

MC92501 can perform one or more of the following:

¥ Set CI bit in an ingress FRM cell Ñ when the ISFCEÑ

¥ Set NI bit in an ingress FRM cell Ñ when the ISFNEÑ

¥ Set PTI[1] bit in an ingress cell whose PTI[2] = 0 Ñ when

MC92501 can perform one or more the following:

¥ Set CI bit in an ingress BRM cell Ñ when the ISBCEÑ

¥ Set NI bit in an ingress BRM cell Ñ when the ISBNEÑ

bit in the Egress Switch Overhead Information

EEASÑGlobal

bit in the Egress Switch Interface ConÞguration

The switch fabric can notify the MC92501 that it should mark

EFSÑOverhead Egress Flow Status bit in the

The egress ßow status equals 1 if:

EAME = 1 OR

EFS = 1 and EEAS = 1 and egress = 1 OR

CEFS = 1 and EEAS = 1 and ingress = 1

Where:

EAME = Global Egress ABR Mark Enable

EFS = Overhead Egress Flow Status

EEAS = Global EFS Enable

CEFS = Connection EFS Enable

Egress = Programmed Overhead Egress Bit

Ingress = Programmed Overhead Ingress Bit

The MC92501 can mark cells as a result of either ingress

In the case where ingress ßow status is asserted, the

Global Ingress Set FRM CI Enable bit in the Ingress

Processing ConÞguration Register (IPCR) is set.

Global Ingress Set FRM NI Enable bit in the IPCR is set.

the ISPEÑGlobal Ingress Set PTI Enable bit in the IPCR

is set.

In the case where egress ßow status is asserted, the

Global Ingress Set BRM CI Enable bit in the IPCR is set.

Global Ingress Set BRM NI Enable bit in the IPCR is set.

All cell marking on the ingress is enabled on a per-

connection basis by the CIMEÑConnection Ingress Marking

Enable bit in the Common Parameters Extension Word.

5.4.3.1. Logic of Ingress ABR Marking Bits

The CI bit is set if:

FRM cell and CIME = 1 and ingress ßow status = 1

and ISFCE = 1 OR

BRM cell and CIME = 1 and egress ßow status = 1

and ISBCE = 1

The NI bit is set if:

FRM cell and CIME = 1 and ingress ßow status = 1 and

ISFNE = 1 OR

BRM cell and CIME = = 1 and egress ßow status = 1 and

ISBNE = 1

The PTI[1] bit is set if:

PTI[2] = 0 and CIME = 1 and ingress ßow status = 1 and

ISPE = 1

Where:

CIME = Connections Ingress Marking Enable

FRM Cell = Cell marked as FRM cell

BRM Cell = Cell marked as BRM cell

Ingress Flow Status = Set as deÞned in Section 5.4.1.4

Egress Flow Status = Set as deÞned in Section 5.4.2.4

ISFCE = Global Ingress Set FRM CI Enable

ISFNE = Global Ingress Set FRM NI Enable

ISPE = Global Ingress Set PTI Enable

ISBCE = Global Ingress Set BRM CI Enable

ISBNE = Global Ingress Set BRM NI Enable

5.4.4. Egress ABR Marking Bits

The MC92501 can mark cells as a result of either ingress

ßow status or egress ßow status.

In the case where egress ßow status is asserted, the

MC92501 can perform one or more of the following:

¥ Set CI bit in an egress FRM cell Ñ when the ESFCEÑ

Global Egress Set FRM CI Enable bit in the Egress

Processing ConÞguration Register (EPCR) is set.

¥ Set NI bit in an egress FRM cell Ñ when the ESFNEÑ

Global Egress Set FRM NI Enable bit in the EPCR is set.

¥ Set PTI[1] bit in an egress cell whose PTI[2] = 0 Ñ when

the ESPEÑGlobal Egress Set PTI Enable bit in the EPCR

is set.

In the case where ingress ßow status is asserted, the

MC92501 can perform one or more the following:

¥ Set CI bit in an egress BRM cell Ñ when the ESBCEÑ

Global Egress Set BRM CI Enable bit in the EPCR is set.

¥ Set NI bit in an egress BRM cell Ñ when the ESBNEÑ

Global Egress Set BRM NI Enable bit in the EPCR is set.

All cell marking on the egress is enabled on a per-

connection basis by the CEMEÑConnection Egress Marking

Enable bit in the Common Parameters Extension Word.

MOTOROLA

MC92501

15

5.4.4.1. Logic of Egress ABR Marking Bits

The CI bit is set if:

FRM cell and CEME = 1 and egress ßow status = 1

and ESFCE = 1 OR

BRM cell and CEME = 1 and ingress ßow status = 1

and ESBCE = 1

The NI bit is set if:

FRM cell and CEME = 1 and egress ßow status = 1 and

ESFNE = 1 OR

BRM cell and CEME = 1 and ingress ßow status = 1 and

ESBNE = 1

The PTI[1] bit is set if:

PTI[2] = 0 and CEME = 1 and egress ßow status = 1 and

ESPE = 1

Where:

CEME = Connections Egress Marking Enable

FRM Cell = Cell marked as FRM cell

BRM Cell = Cell marked as BRM cell

Ingress Flow Status = Set as deÞned in Section 5.4.1.4

Egress Flow Status = Set as deÞned in Section 5.4.2.4

ESFCE = Global Egress Set FRM CI Enable

ESFNE = Global Egress Set FRM NI Enable

ESPE = Global Egress Set PTI Enable

ESBCE = Global Egress Set BRM CI Enable

ESBNE = Global Egress Set BRM NI Enable

5.4.5. Cell Marking Examples

Figure 12, Figure 13, and Figure 14 provide examples for

CI and NI marking.

NOTE 1

NOTE 3

NOTE 4

MC92501 #1 MC92501 #2

NOTES:

1. Initially the microprocessor conÞgures the MC92501 #1 as follows:

¥ Sets the ISFCEÑGlobal Ingress Set FRM CI Enable bit.

¥ Sets the CIMEÑConnection Ingress Marking Enable bit for selected ABR connections.

2. The switch fabric informs the microprocessor that ingress ABR queues have reached

some limit.

3. The microprocessor sets the IAMEÑGlobal Ingress ABR Mark Enable bit.

4. The MC92501 sets the CI bit for FRM cells belonging to the selected ABR connections.

Microprocessor

NOTE 2

Switch Fabric

Downstream Direction

Upstream Direction

Figure 12. Enable Marking CI Bits of Ingress FRM Cells

MC92501

16

MOTOROLA

Loading...

Loading...