Page 1

查询MC92308供应商

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Product Preview

OFDM Demodulator

The MC92308 is a Orthogonal Frequency Division Multiplex Demodulator for 2K

transmission mode according to the ETSI specification for digital terrestrial broadcasting (PR ETS 300744). The MC92308 contains all the functionality required to demodulate the information transmitted in one UHF channel.

Feature Summary

• Usable for 8MHz/7MHz/6MHz channels by adjusting the clock rate

• Digital I/Q separation on-chip

• Supports QPSK, 16-QAM and 64-QAM

• Supports all guard interval lengths (1/32, 1/16, 1/8, 1/4)

• Accepts 8-bit TTL-compatible twos-complement data input

• Provides the required control signals for Automatic Gain Control and ADC clock

frequency control

• Performs channel estimation and correction by using the embedded pilot carriers

•I2C serial bus compatible interface (M-Bus) and parallel interface for external pro-

gramming and control of the device

• Transmission Parameter Signalling is decoded and made available to the system

controller via M-Bus or parallel microprocessor interface

• Companion to DVB compliant 2K-FFT Processor (MC92307)

• Output interface for DBV compliant FEC

• Fast synchronization at power-on and after channel switch

• Low implementation margin

• 0.5µ CMOS Process at 3.3V

Current Information@www.mot.com/ADC

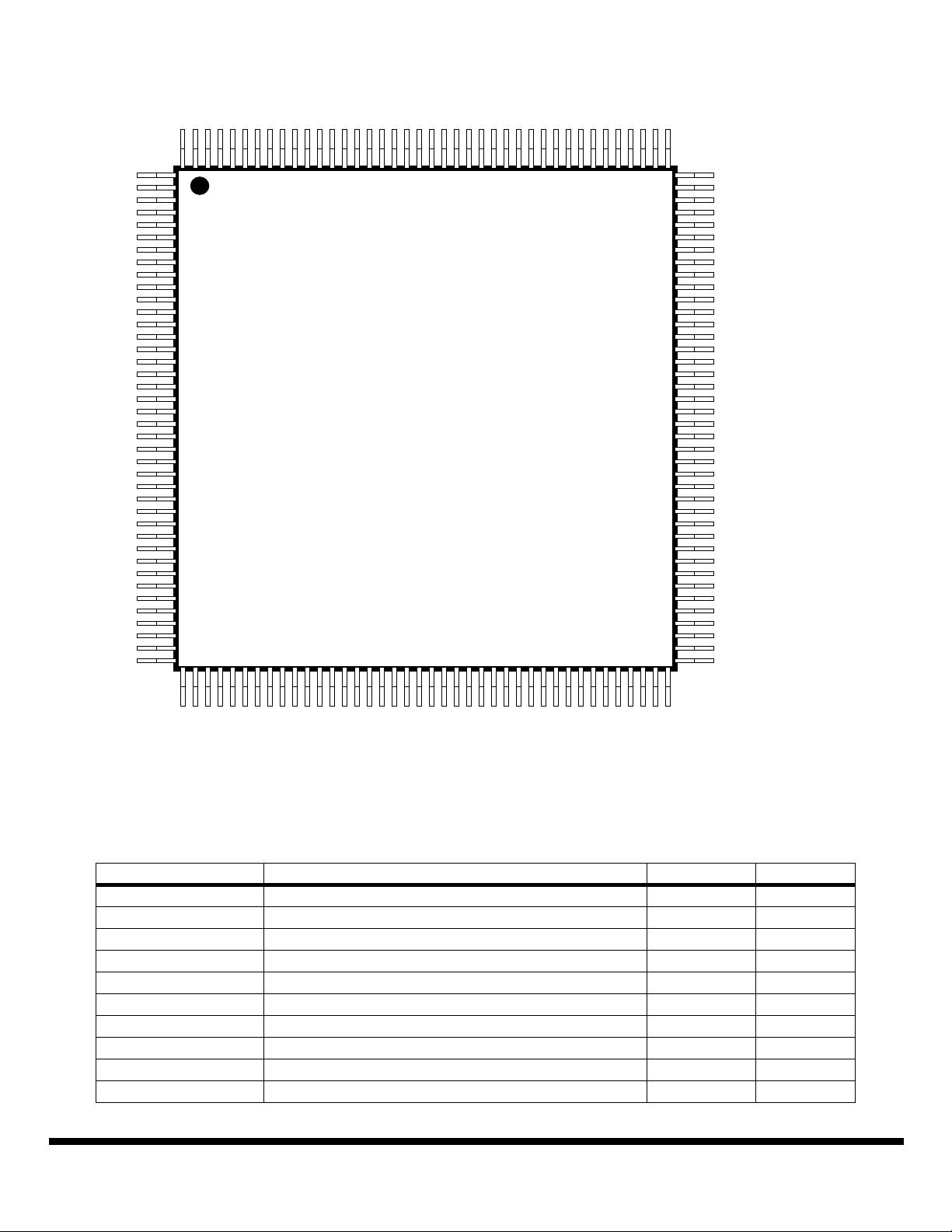

MC92308

RESB

CLK

ADCDATA[7:0]

CLKEN18

SYMSYNC

FFTDI[11:0]

MBUS[1:0]

Ordering Information

Device

MC92308CI

CLKCTLP

CLKCTLN

AGCCTLP

AGCCTLN

FFTSTART

FFTDO[7:0]

FECCLK

DVALID

G1DATA[2:0]

G2DATA[2:0]

Package

160MQUAD

Figure 1. OFDM Frontend Processing

This document contains information on a product under development.

Motorola reserves the right to change or discontinue this product without notice.

MOTOROLA, INC. 1997 5/7/97

Page 2

VSS

VSS

VSS

VDD

VDD

VSS

FFTDO7

FFTDO6

FFTDO5

VDD

FFTDO4

FFTDO3

FFTDO2

VSS

FFTDO1

FFTDO0

FFTSTART

SYMSYNC

FFTDI11

VDD

VSS

FFTDI10

FFTDI9

FFTDI8

FFTDI7

VDD

FFTDI6

FFTDI5

FFTDI4

FFTDI3

VSS

FFTDI2

FFTDI1

FFTDI0

VDD

VDD

VSS

VSS

VDD

VDD

ADCDATA0

ADCDATA1

ADCDATA2

ADCDATA3

VDD

VSS

ADCDATA4

ADCDATA5

ADCDATA6

ADCDATA7

VDD

VSS

VDD

VSS

CLKEN18

CLK

VDD

VSS

VDD

CLKCTLP

CLKCTLN

VDD

VSS

AGCCTLP

AGCCTLN

VDD

VSS

VSS

VSS

VDD

VDD

VDD

VSS

VSS

VDD

VSS

MADDR0

MADDR1

MADDR2

MADDR3

160MQUAD

reserved (VSS)

reserved (VSS)

reserved (VSS)

VSS

VDD

reserved (VSS)

reserved (VSS)

reserved (VSS)

reserved (VSS)

reserved (VSS)

reserved (VSS)

VSS

VDD

reserved (VSS)

reserved (VSS)

RESB

VSS

VDD

reserved (open)

reserved (open)

reserved (open)

reserved (open)

reserved (open)

reserved (open)

VSS

VDD

reserved (open)

reserved (open)

reserved (open)

VSS

VDD

reserved (open)

reserved (open)

VSS

VDD

reserved (open)

reserved (open)

reserved (open)

VSS

VDD

VDD

MADDR4

MADDR5

VSS

VDD

VSS

VSS

VDD

MDATA0

MDATA1

MDATA2

MDATA3

MDATA4

MDATA5

MCSB

MDATA6

MDATA7

MRDB

MWRB

VDD

VSS

MBUSID0

MBUSID1

MBUSID2

MBUSID3

MSCL

MSDA

VDD

VSS

MSEL

FECVALID

FECCLK

G1DATA0

G1DATA1

VSS

VDD

G1DATA2

G2DATA0

G2DATA1

G2DATA2

Table 1. MC92308 Pin Description

SIGNAL FUNCTIONALITY TYPE POLTY

CLK Common clock input (36.57 MHz) TTL - IN high

RESB Reset (synchronous) TTL - IN low

CLKEN18 ADC data strobe TTL - IN high

ADCDATA[7:0] Input for samples from ADC TTL - IN high

CLKCTLP ADC clock synchronization loop (+) TTL - OUT high

CLKCTLN ADC clock synchronization loop (-) TTL - OUT low

AGCCTLP Analog AGC loop (+) TTL - OUT high

AGCCTLN Analog AGC loop (-) TTL - OUT low

FFTSTART FFT start signal TTL - OUT high

FFTDO[7:0] Complex data output to FFT (muxed) TTL - OUT high

MOTOROLA MC92308

2 Rev.1.4

Page 3

Table 1. MC92308 Pin Description (Continued)

SIGNAL FUNCTIONALITY TYPE POLTY

FFTDI[11:0] Complex data input from FFT (muxed) TTL - IN high

SYMSYNC Symbol start signal from FFT TTL - IN high

G1DATA[2:0] Data output for Viterbi decoder TTL - OUT high

G2DATA[2:0] Data output for Viterbi decoder TTL - OUT high

FECCLK Clock for Viterbi Decoder (free running) TTL - OUT high

FECDVALID Data valid signal for Viterbi Decoder TTL - OUT high

2

MSDA I

MSCL I

MBUSID[3:0]] I

MSEL Enable Microprocessor parallel interface TTL - IN high

MDATA[7:0] Microprocessor interface bidirectional databus TTL - bidir high

MADDR[5:0] Microprocessor interface address bus TTL - IN high

MCSB Microprocessor interface chip select TTL - IN low

MWRB Microprocessor interface write enable TTL - IN low

MRDB Microprocessor interface read enable TTL - IN low

C compatible control bus, data pin TTL - OD -

2

C compatible control bus, clock pin TTL - IN high

2

C compatible control bus, variable ID selector TTL - IN high

Notes:

_________________________________________________________

_________________________________________________________

_________________________________________________________

_________________________________________________________

_________________________________________________________

_________________________________________________________

_________________________________________________________

_________________________________________________________

_________________________________________________________

_________________________________________________________

_________________________________________________________

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the

suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters which may be provided in Motorola

data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including

“Typicals” must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the

rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other

applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury

or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold

Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney

fees arising out of directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that

Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal

Opportunity/Affirmative Action Employer.

MC92308 MOTOROLA

Rev.1.4 3

Page 4

How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; JAPAN: Nippon Motorola Ltd.; Tatsumi-SPD-JLDC, 6F Seibu-Butsuryu-Center,

P.O. Box 5405, Denver Colorado 80217. 1-800-441-2447 or 303-675-2140 3-14-2 Tatsumi Koto-Ku, Tokyo 135, Japan. 81-3-3521-8315

TM

: RMFAX0@email.sps.mot.com -TOUCHTONE (602) 244-6609 ASIA/PACIFIC:Motorola Semiconductors H.K. Ltd.; 8B T ai Ping Industial P ark,

Mfax

INTERNET:http://mot-sps.com/sps/General/sales.html 51 Ting Kok Road, Tai Po, N.T., Hong Kong. 852-26629298

MC92308

Loading...

Loading...