MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Product Preview

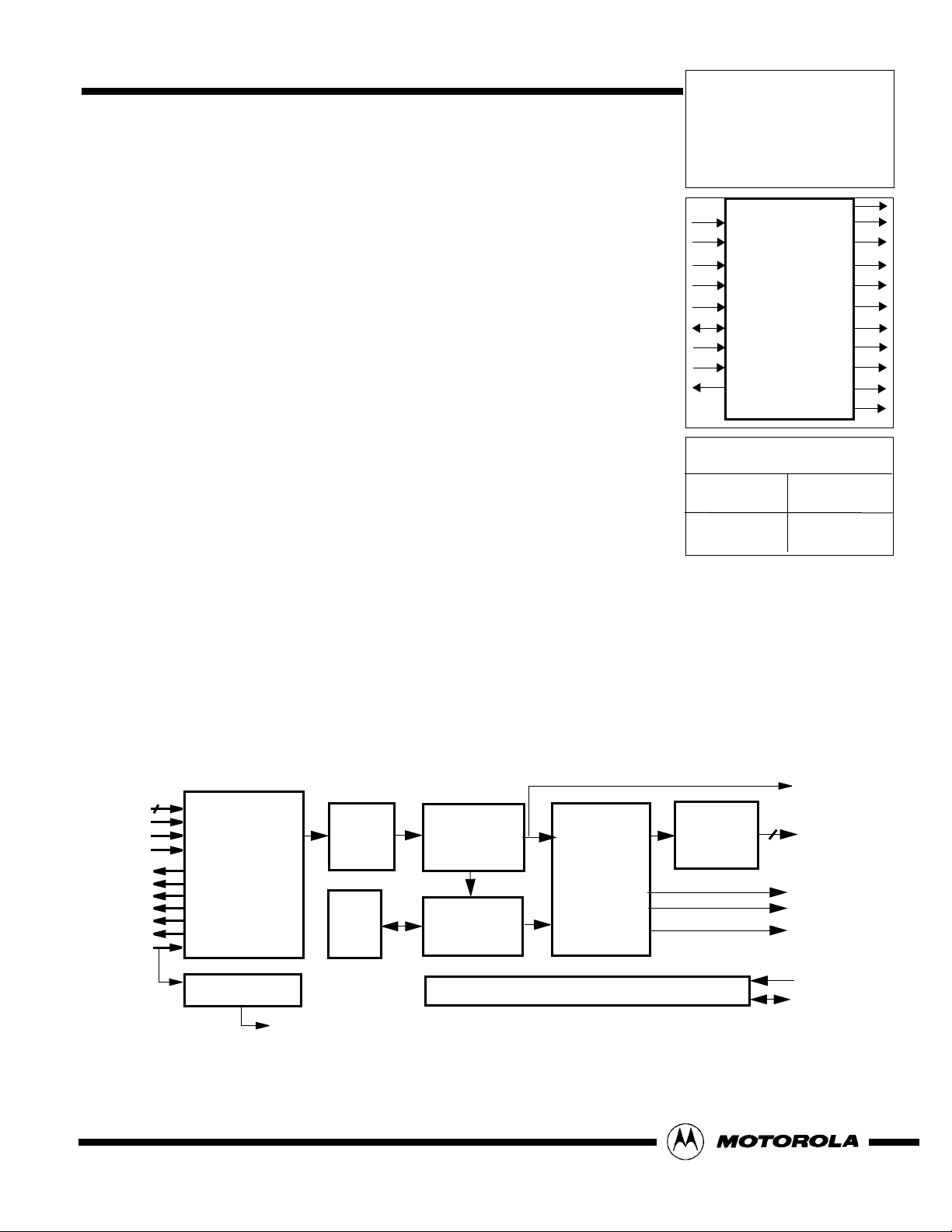

16/32/64/128/256 QAM RECEIVER AND

REED-SOLOMON DECODER

The MC92305 is a high performance digital demodulator/decoder optimized for

demodulation and block error correction of QAM signals used in Digital Video Broadcast by Cable (DVB-C) and DAVIC 1.0 compliant applications.

Feature Summary

• Single A/D IF interface

• Maximum signaling rate of 7Mbaud (42Mbits/sec for 64 QAM and

56Mbits/sec for 256 QAM)

• DVB compliant QAM Coherent Demodulator

• Transversal/Decision Feedback adaptive equalizer

No external components or control required

• Micro-reflection cancellation up to 1.4µs

• Nyquist baseband filtering (α=0.15)

• 1-bit Σ∆ control outputs for AGC, VCO and optional external NCO

• Programmable De-Interleaving For MPEG Transport Packets

• DVB Compliant (204,188,16) Reed Solomon Decoding

• DVB Compliant PRBS Descrambling

• 0.5 micron CMOS, 3.3V technology

•I2C Interface for control/monitoring of system

Current Information @ www.mot.com/ADC

MC92305

AGCOUT

RESETB

I&Q[9:0]

IQSWAP

ADCLKIN

SYMFE

SDATA

IN_FMT

SCLK

BITCLK

Ordering Information

Device

MC92305CD

ADCLKOUT

VCOOUT

CTLOUT

DMODLOCK

MSSLOCK

DOUT[7:0]

DO_VAL

FRAME_SYNCH

FRAME_ERR

FRAME_START

Package

80QFP

FRAME_SYNCH

8

DOUT

FRAME_START

FRAME_ERR

DO_VAL

SCLK

SDATA

I &Q

SYMFE

RESETB

IN_FMT

ADCLKOUT

CTLOUT

VCOOUT

AGCOUT

MSSLOCK

DMODLOCK

ADCLKIN

10

16/32/64/128/256

QAM DEMOD.

APLL

BITCLK

Symbol

To Byte

Mapping

RAM

Synch Word

Synchronization

Programmable

De-Interleaver

Reed-Solomon

Decoder

2

I

C Interface

PRBS

Descrambler

Figure 1. MC92305 Block Diagram

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

MOTOROLA, INC. 1997 4/9/97

Demodulator Interface

The MC92305 is interfaced to a single 8-bit (10-bit for

256 QAM) A/D converter which is clocked at 4 times the

symbol rate (4Rs). A pin-programmable input format selector allows the use of A/D converters which produce output samples in either offset binary or 2's complement

format.

The demodulator function performs all required signal processing to extract the I and Q symbols from the received data stream. Fully internal digital clock recovery/

synchronization, Nyquist filtering and LTE/DFE adaptive

equalization are employed to recover symbol information

in the presence of channel noise and micro-reflections.

The equalizer is able to converge with random received

data and no special training sequence is required.

Single-bit (Sigma-Delta converted) outputs are provided for automatic gain control (AGC) and A/D voltage

controlled oscillator(VCO) feedback functions within the

external IF circuitry.

De-Interleaving

After synchronization with the MPEG framing structure the data stream is convolutionally de-interleaved. To

obtain the maximum data throughput (i.e. minimum latency) under various channel SNR's the de-interleaver

can be programmed.

Table 1 describes the usable parameter settings

with varying delay (latency) and burst (error correction).

N is the block size in bytes, DEPTH is the number of

paths in the de-interleaver and INC is the increment (in

bytes) in which data is moved through the de-interleaver

paths. DELAY is defined as the latency (in bytes) in the

de-interleaver (after frame synchronization has been

achieved) and BURST is defined as the maximum number of bytes that can be affected by bursty noise before

more than eight bytes are corrupted in a de-interleaved

MPEG frame. Minimum burst error correction of 8 bytes

is guaranteed by the Reed Solomon decoder.

Table 1. De-Interleaver Configurations

The demodulator carrier tracking loop is capable of

locking to signals which contain moderate frequency offsets (0.06Rs) from the specified IF frequencies. The carrier tracking loop is normally closed digitally, using an

internal numerically controlled oscillator (NCO) but a single bit control output is also provided for closing the loop

through an external VCO.

External signals indicate when the demodulator has

successfully acquired the data stream and recovered the

data clock (MSSLOCK), and when the received symbols

are consistently below a programmable error threshold

(DMODLOCK).

Symbol To Byte Mapping

The received symbols are mapped into bytes according to the DVB/Davic 1.0 specifications. An internal I2C

register can be used to select an alternative de-coding

scheme which is specified as a mask programmable option.

Sync Word Synchronization.

After demodulation of the received data, the byte

stream is examined for MPEG synchronization (inverted

and non-inverted) bytes and when the number detected

exceeds programmable thresholds, the received byte

stream is recognized as valid MPEG data.

FRAME_SYNCH is asserted when the programmed number of synchronization bytes have been recognized.

FRAME_START is asserted for one byte width at the start

of each MPEG frame.

N Depth Inc Delay Burst

1110 8

204 4 51 612 30

204 6 34 1020 44

102 17 6 1632 54

204 12 17 2244 86

The operation of the de-interleaver is software con-

figurable via the I2C interface during system operation.

Reed Solomon Decoding

The Reed Solomon decoder block implements a

shortened Reed-Solomon decoder with field generator

polynomial X8 + X4 + X3 + X2 + 1 as per the DVB specification.

The decoder is able to correct up to 8 byte errors in

each received packet. Following error correction the

Reed Solomon decoder outputs the MPEG packets and

asserts the DO_VAL output for each byte output (50%

duty cycle per byte).

If the error correcting ability of the Reed Solomon

decoder is exceeded (more than 8 byte errors in a single

packet), the original, uncorrected, data is output and the

DO_VAL output is not asserted. The FRAME_ERR signal is asserted for the duration of the uncorrected MPEG

frame.

MOTOROLA MC92305

2 Rev.1.1

Loading...

Loading...