Motorola MC44723FT, MC44722FT Datasheet

MC44722/3 Rev 0.23 3/24/'97

No.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

1

Advance Information

NTSC

Digital Video Encoder

HCMOS Technology

MC44722

MC44723

FT SUFFIX

48 QFP

(0.8mm Pitch)

The MC44722 and MC44723 are Digital Video Encoders (DVE).

They convert ITU-601/656 standard 4:2:2 Bit-Paralellel data into

analog composite video, S-Video or Y/Cb/Cr in PAL and NTSC

formats. They accept the multiplexed ((CB,Y,CR)Y) signals from

digital sources such as MPEG decoders and can act as a sync

generator master. All video processing is done digitally and

requires no external adjustment.

Specifically designed for digital satellite, digital cable decoders

and multimedia terminals.

• World Wide Operation (PAL-BDGHI, PAL-N,PAL-M, NTSC-M)

• SMPTE 170M / ITU - R 624 composite video output

• Programmable Color Sub-carrier Frequencies

• Analog Horizontal, Vertical, Frame or Composite Sync Outputs

• Sync Extraction From Digital Input Data (SAV, EAV)

• Sync Polarity and Horizontal Phase Control

• Master or Slave Sync (H/Vsync, H/Fsync, ITU-R656 slave) Operation

• Interlaced or Non-Interlaced Support

• 625/50 or 525/60 ITU-601/656 8-bit ((CB,Y,CR)Y) Digital Input

• Luma 2X / Chroma 4X Oversampling Filtering

• External VBI Information Data Input (such as TeleText Information Data)

• CVBS / YS / CS or Y / Cb / Cr Analog Outputs Through 10-bit DACs

• Easily programmed via Serial Bus ( I2C or SPI Bus)

• 2 Hardware I2C Chip Addresses

• Closed-Caption and CGMS Information data Insertion

• MACROVISION ver. 7.01 Anti-Copy Signal Insertion

(MC44722 Only support NTSC mode)

• On Chip Color - bar Generator

• +3.3V Power Supply or +3.3V(Digital)/+5V(Analog) Power Supply

• Pin Compatible with MC44720FT

The MC44722 device is protected by U.S. patent number 4,631,603,4,577,216 and 4,819,098 and other

intellectual property rights. The use of Macrovision's copy protection technology in the device must be

authorized by Macrovision and is intended for home and other limited pay-per-view uses only, unless

otherwise authorized in writing by Macrovision. Reverse engineering or disassembly is prohibited.

MC44722/3 Rev 0.23 3/24/'97

No.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

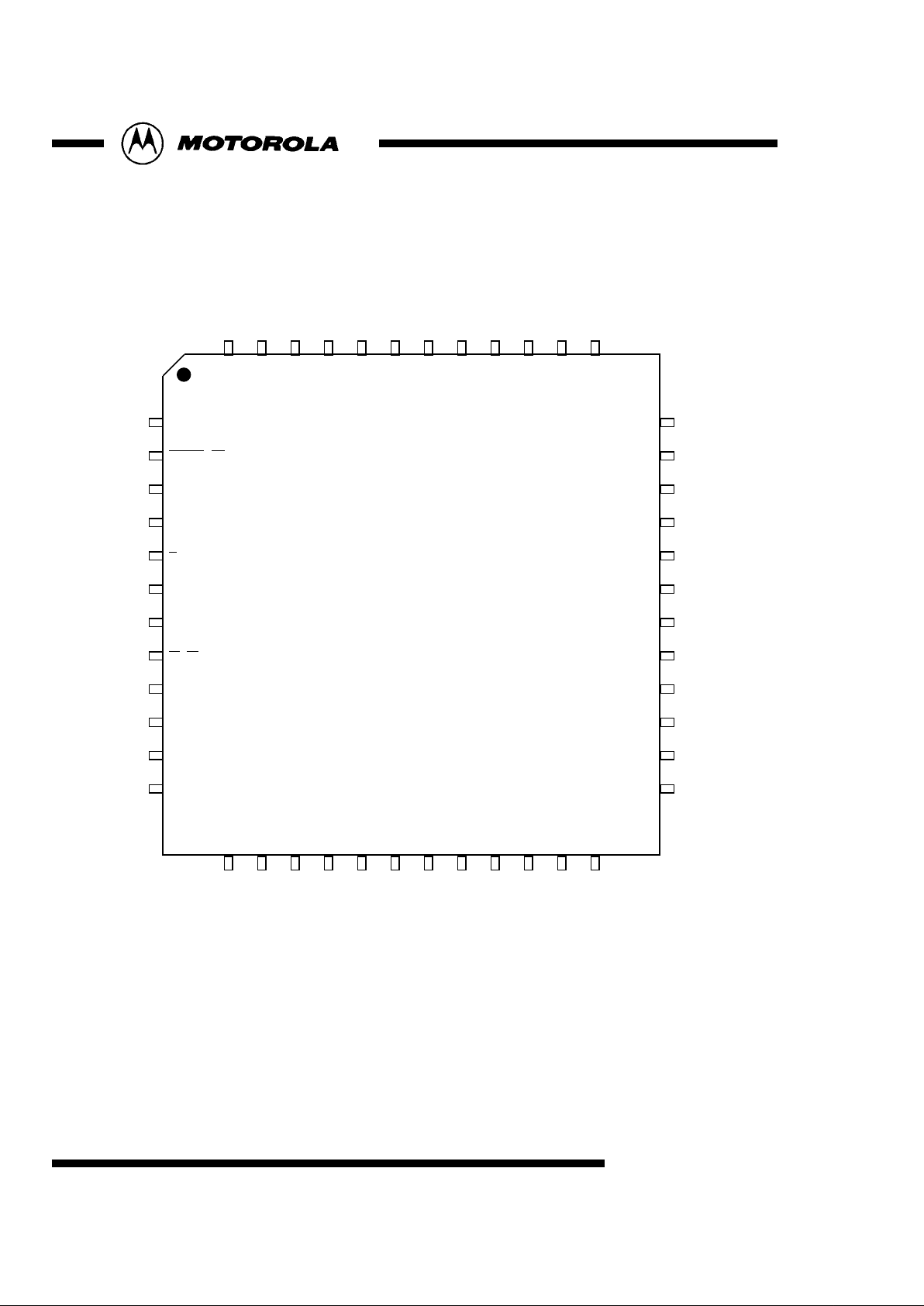

[Pin Assignment]

CVBS / Cb

Hsync

EXT

TVIN

DVIN3

DVIN4

DVIN5

DVIN6

DVIN7

TP9

TP8

TP7

TP6

TP5

DVss

DVdd

TP4

MC44722

MC44723

2

1

2

3

4

5

6

7

8

9

12

14

15

16

17

18

19

20

21

VReff

13

24

22

10

11

36

35

34

33

32

31

30

29

28

25

27

26

23

47

46

45

44

43

42

41

40

48

37

39

38

CVBS / Cb

CVBS/CbVdd

Y

Y

YVdd

C / Cr

C / Cr

CVdd

DAVss

Ibias

DAVdd

ChipA

TEST

SO

SDA/SI

SCL/SCK

SEL

DVss

clock

DVdd

Reset

PAL/NTSC

DVIN0

DVIN1

DVIN2

F / Vsync

TP3

TP2

TP1

TP0

MC44722/3 Rev 0.23 3/24/'97

No.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

[Pin Descriptions]

1 CVBS / Cb O Analog composite video signal output or Cb signal output current drive(positive)

2 CVBS /Cb O Analog composite video signal output or Cb signal output current drive(negative)

3 CVBS/CbVdd Power Supply for CVBS / Cb DAC circuit

4 Y O Analog luminance signal output current drive(positive)

5 Y O Analog luminance signal output current drive(negative)

6 YVdd Power Supply for Y DAC circuit

7 C/Cr O Analog chrominance signal output or Cr signal output current drive(positive)

8 C/Cr O Analog chrominance signal output or Cr signal output current drive(negative)

9 C/CrVdd Power Supply for C / Cr DAC circuit

10 DAVss Ground for DAC circuit

11 Ibias O Reference current for the 3 DACs

12 DAVdd Power Supply for DAC circuit

13 VReff Reference full scale voltage for the 3 DACs

14 ChipA I2C chip address select { 0 : 42(hex)/43(hex) 1 : 1C(hex )/1D(hex) }

15 TEST I TEST pin(Ground)

16 SO z(O) If SPI mode, serial data output / If I2C mode, connect to Ground

17 SDA/SI I/O(I) Serial data input, Open drain output / If SPI mode, serial data input

18 SCL/SCK I Serial clock

19 SEL (I) Connect to Ground / If SPI mode, this pin is chip select

20 DVss Ground for Digital circuit

21 CLOCK I 27MHz clock input

22 DVdd Power Supply for Digital circuit

23 Reset I Reset signal, active LOW

24 PAL/NTSC I NTSC/PAL select . This pin active only Reset time. (NTSC : Low PAL : High )

25~32 DVIN7~0 I 8-bit Multiplexed Y/Cr/Cb 4:2:2 data(CCIR Rec656) input(1)

33 TVIN I TEST data input

34 EXT I/O Csync/Frame sync output or external VBI information input

35 F/Vsync I/O Frame sync or Vertical sync input/output

36 Hsync I/O Horizontal sync input/output

37 TP9 I/O for D/A converter test

38 TP8 I/O MUX switch in 8-bit Multiplexed Y/Cr/Cb 4:2:2 data(CCIR Rec656) input mode, or

Test data input/output

39~41 TP7~5 I/O 8-bit Multiplexed 4:2:2 data(CCIR Rec656/601) input(2), or Multiplexed Cr/Cb data

(CCIR Rec656/601) input in 16-bit input mode (MSB : TP7), or Test data input/output

42 DVss Ground for Digital circuit

43 DVdd Power Supply for Digital circuit

44~48 TP4~0 I/O 8-bit Multiplexed 4:2:2 data(CCIR Rec656/601) input(2), or Multiplexed Cr/Cb data

(CCIR Rec656/601) input in 16-bit input mode (LSB : TP0), or Test data input/output

3

PIN NAME I/O DESCRIPTIONS

MC44722/3 Rev 0.23 3/24/'97

No.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

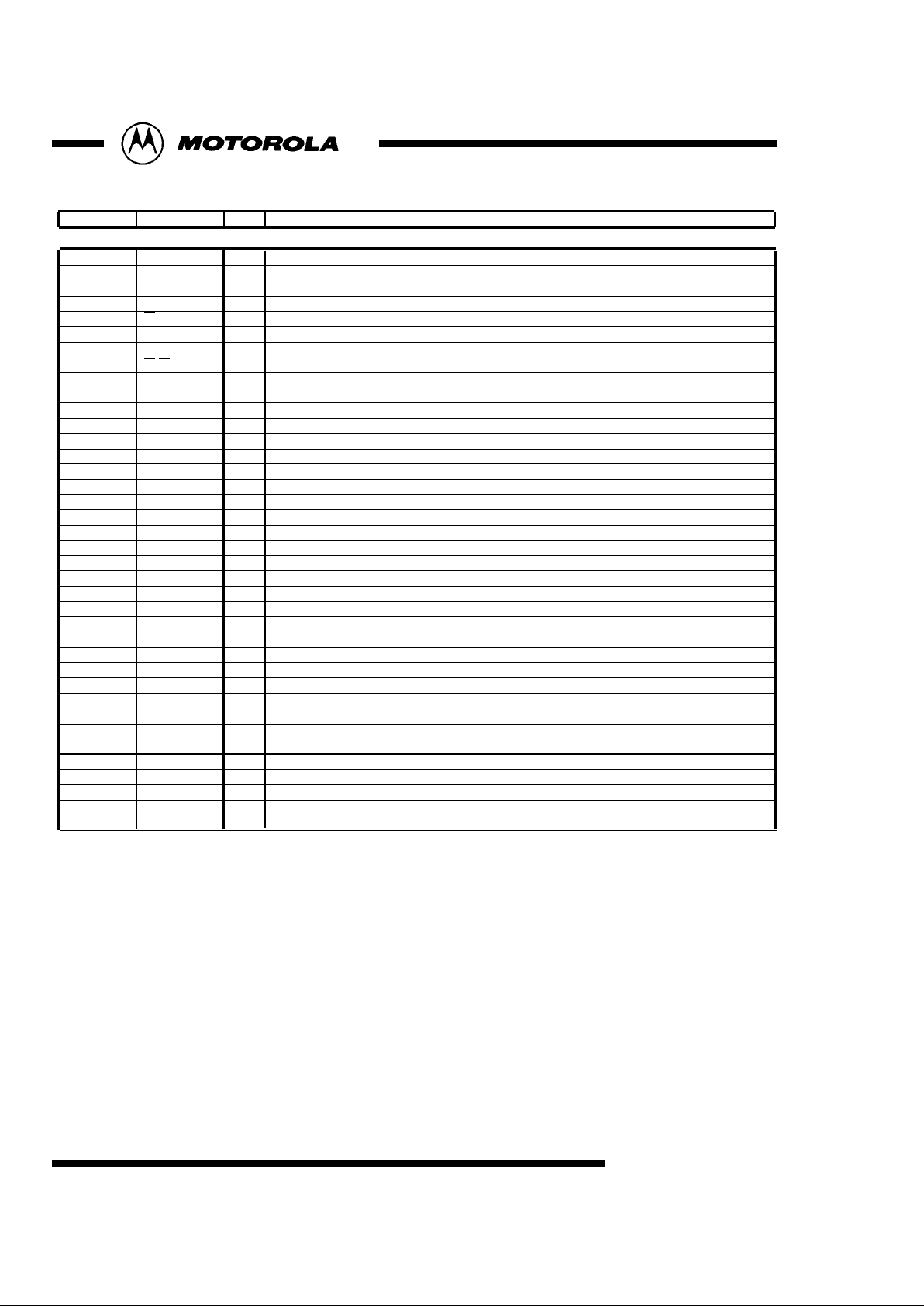

4

DAC

YOUT

YOUT

COUT / Cr

COUT / Cr

CVBSOUT / Cb

CVBSOUT / Cb

YVdd

CVBS/CbVdd

C/CrVdd

DAVdd

DAVss

Ibias

BIAS

EXT

F/Vsync

Hsync

DVIN

SDA/SI

SCL/SCK

0

0

0

0

CGMS_gen CC_gen

Sync_generator

copy

protection

bus

off_set

BG

Modulator

subcarrier

gen

0

DAC

0

DAC

0

TP0~9

TEST

TEST

PAL/NTSC

Reset

TVIN

demux

Y

Cb

Cr

H,V

ChipA

DVdd

DVdd

DVss

DVss

I2C/SPI chip-address 42/43(hex)

1C/1D(hex)

clock

[Block Diagram]

MC44722/3

VReff

SEL

SO

I2C / SPI

TP0~7

MC44722/3 Rev 0.23 3/24/'97

No.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

5

Clock

27.0Mhz is necessary. This signal on the clock pin needs to be active before the reset pin is de-asserted.

( see figures 1 and 2 )

[Function Descriptions]

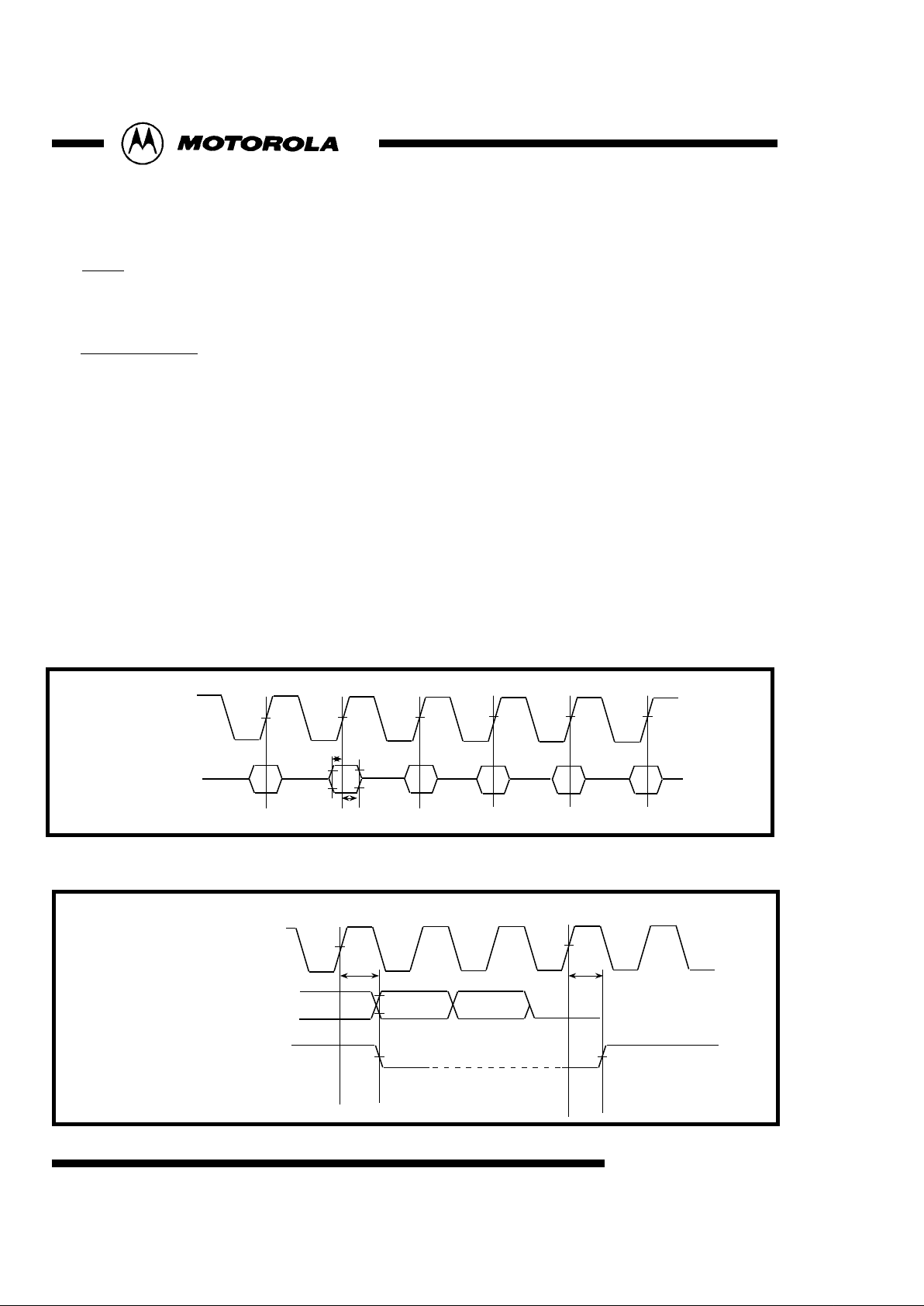

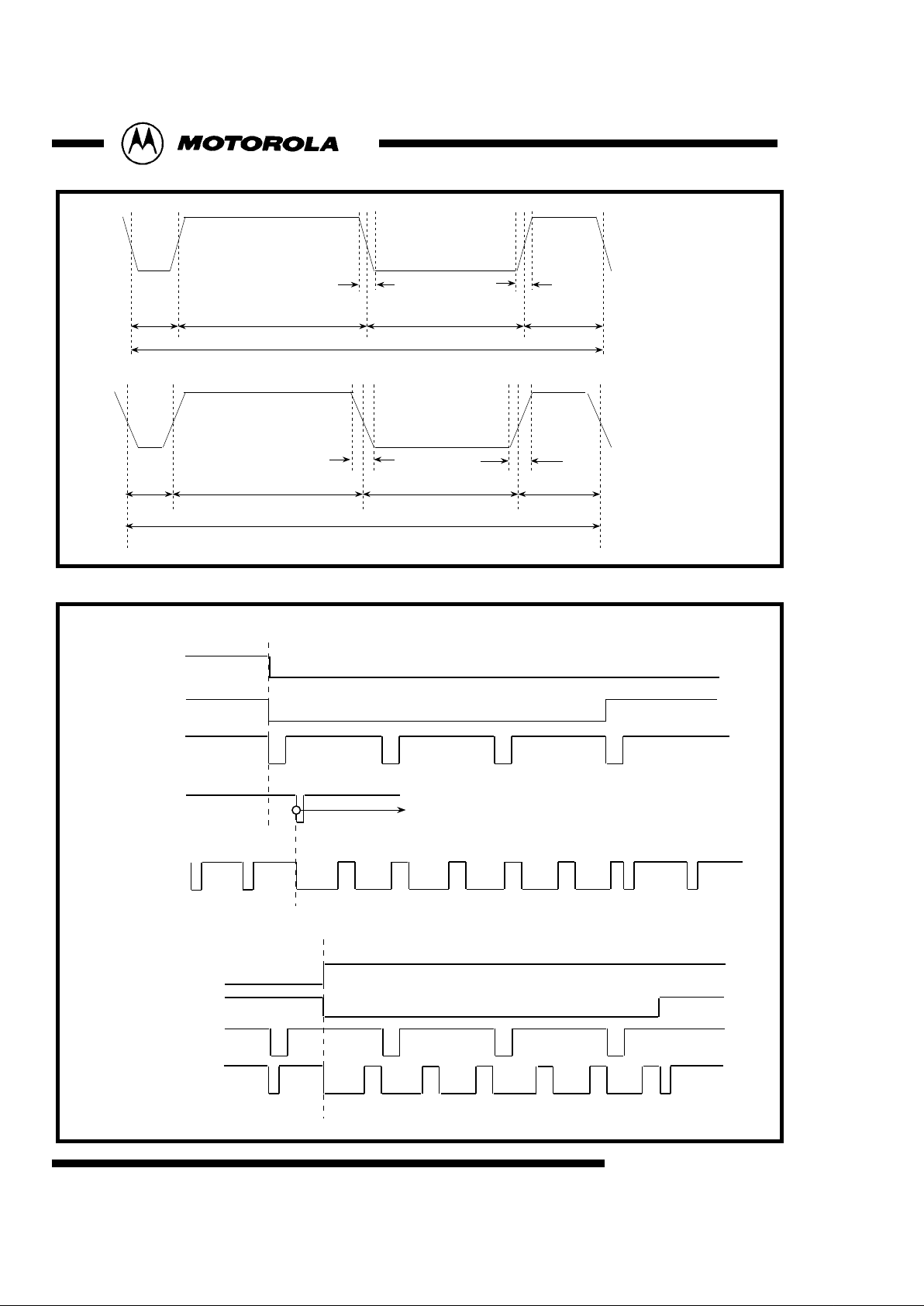

Fig 1 : DVIN Data Input Timing

Input Clock 27MHz

Input Data

DVIN0~7

50%

Tds

Tdh

Clock 27MHz

Output data

H/VF sync

Output Data

TP0~8

Td

Td

Fig 2 : Sync Data Output Timing

Reset Procedure

RESET is a level sensitive input pin. Driving the RESET pin low causes a DVE reset. The 27Mhz DVE

clock signal must be active before RESET is released. De-asserting reset will latch the status of the PAL/

NTSC, TVIN and SEL pins.

The PAL/NTSC pin determines the default values for the DVE control registers. The default register

values have been chosen so that standard PAL or NTSC video will appear at the DAC outputs immediately

when a valid input digital video data stream is present.

The value on the SEL pins determine the default serial communication mode. If Low, the DVE use I2C bus

operation. If High, the DVE use 4-wire SPI operation.

After reset, the VBI signals (Closed-Caption and CGMS) are disabled.

(see page --- for sub-address register descriptions.)

MC44722/3 Rev 0.23 3/24/'97

No.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

Video Timing / Sync Generator

The DVE outputs PAL-B,D,G,H,I, PAL-N, PAL-M or NTSC-M standard video signals.

The DVE sync generator can be operated in two modes, master or slave.

In master mode, the DVE generates all the correct Horizontal and Vertical or Frame sync signals

internally, or it is output Csync signal through the EXT pin(C/Fsync).

In slave mode, the DVE derives the sync signals from the Bit-Parallel input data stream Start Active

Video (SAV) and End Active Video (EAV) data packet information. Sync signals are output on the

Hsync and F/Vsync or EXT pins and can be programmed for positive or negative polarity. The phase of

Hsync can also be controlled.

Also, the DVE allows more two slave modes. One is H/Vsync slave, and the aother is H/Fsync slave

mode.

Vertical Blanking corresponds to the following lines.

625/50 624-22 311-335 ITU-R line numbering

525/60 1-19 264-282 SMPTE line numbering

(see figures 3,4,5,6,7,8,9,10, and 11 for sub-address register descriptions.)

6

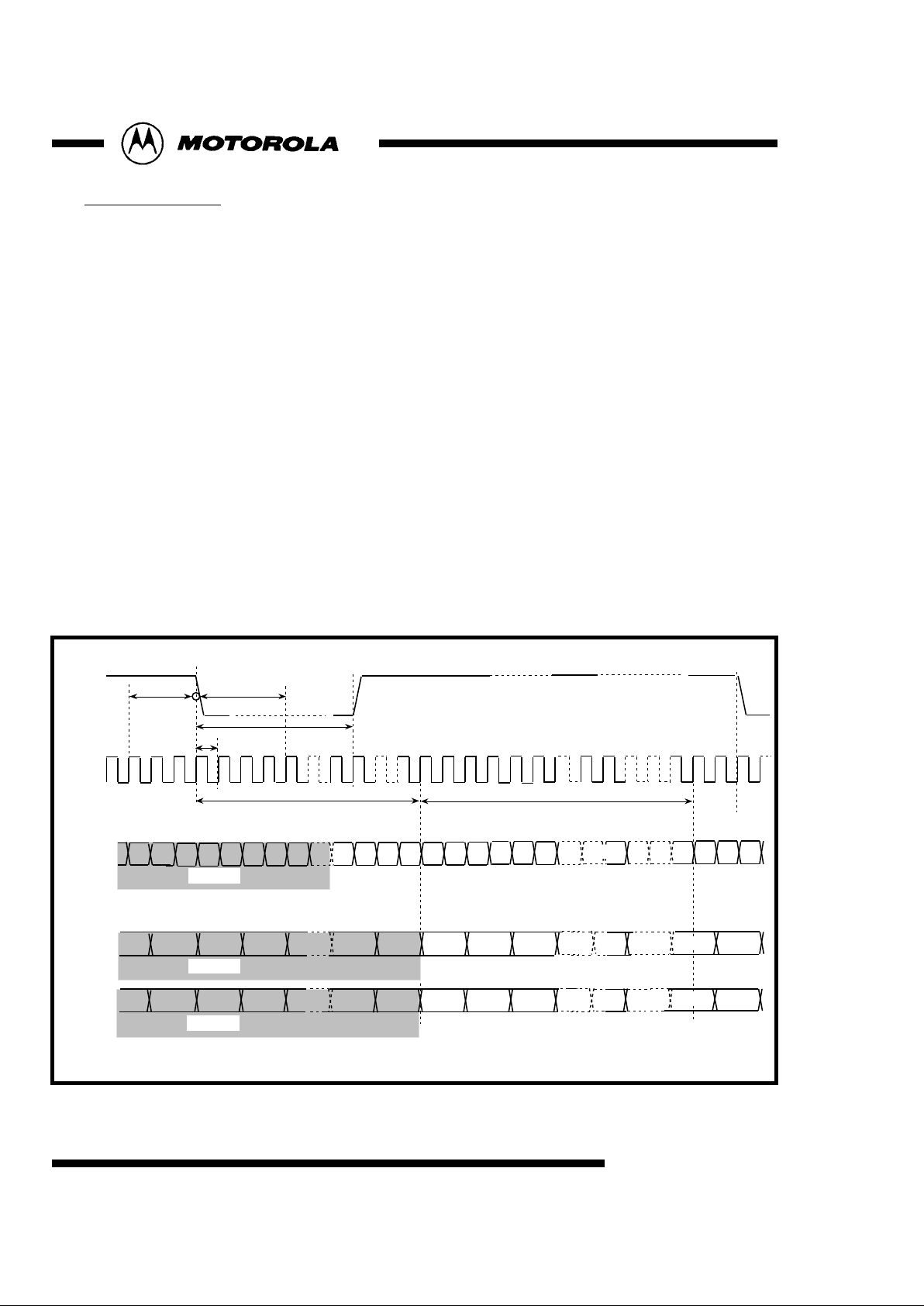

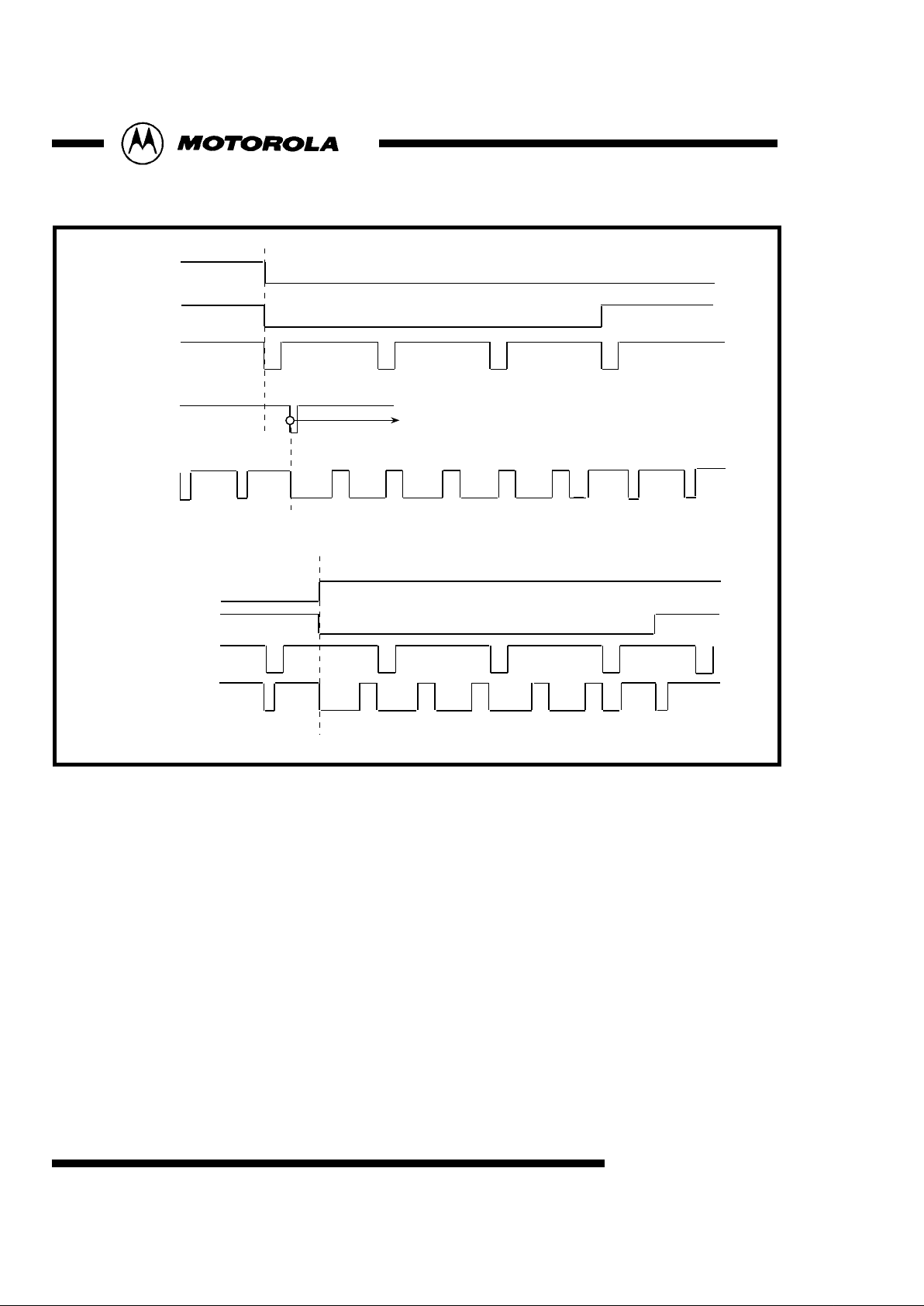

Fig 3 : Digital Input Timing(525/60 system) in Master Mode

1440T

Hsync phase

sub-address71[2:0]

Hsync

clock

124T

T

242T

Hsync polarity

sub-address71[5]

+3T delay-4T delay

DVIN0~7

Cr718

Cb718

Y718

Y719

00 00

FF

Cb2Cr0

Cb0

Y0 Y1 Y2

INVALID

00 00 XY

FF

70(hex){[1:0]=01}

Y718 Y719

TP0~7

Cr718Cb718

Cb2

Cr0Cb0

INVALID

DVIN0~7

Y2

Y1Y0

INVALID

16-bit input mode

Cb718Cr718

Cr2

Cr0 Cb0

or

Input Data Format

The input digital video is in accord with the ITU-R Rec.656 and SMPTE 125M standards. It is two 8-bit or

16-bit multiplexed 4:2:2 ((CB,Y,CR)Y) data stream. Samples are latched on the rising edge of the clock

signal. Data is input on pins DVIN[ 7 : 0 ] and TP[ 8 : 1 ]

(see figures 3 and 4 for sub-address register descriptions.)

8-bit input mode

MC44722/3 Rev 0.23 3/24/'97

No.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

7

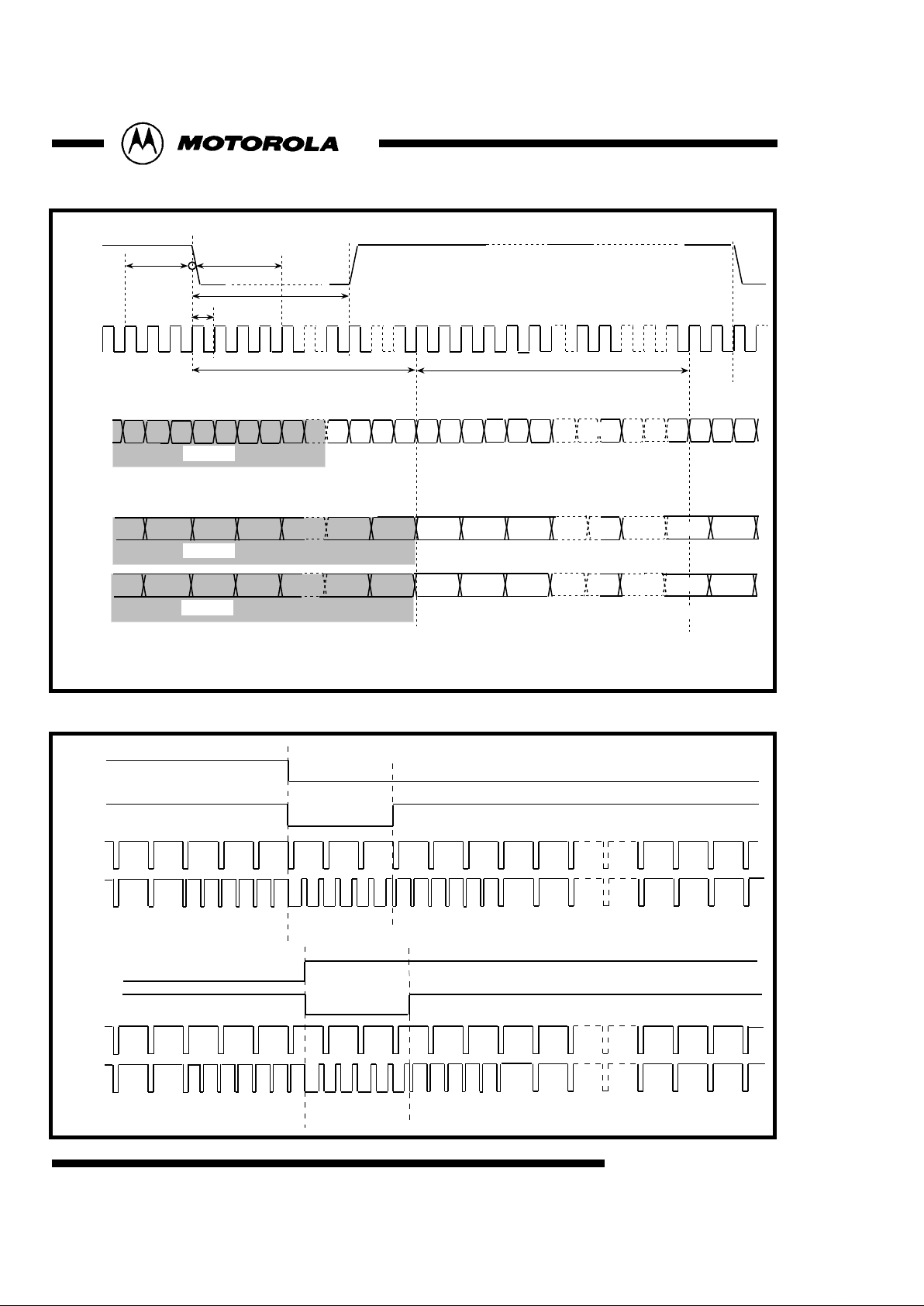

CSYNC

CSYNC

525524 1 2 3 4 5 6 7 8 9 10 11 21 22 23

262261 263 264 265 266 267 268 269 270 271 272 273 283 284 285

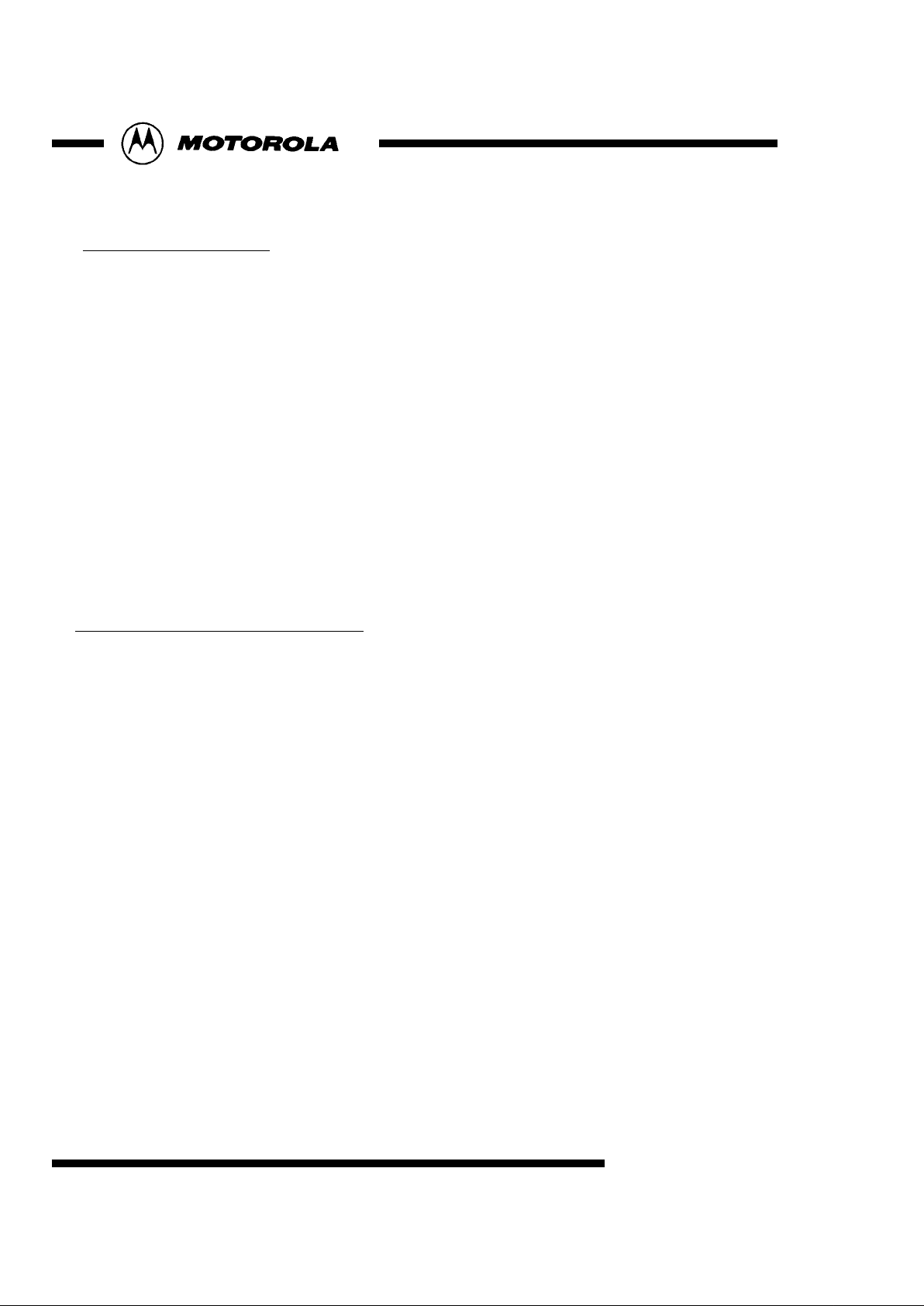

Fig 5 : Sync Timing::525/60 Interlaced System in Master Mode

Vsync

Hsync

Vsync

Hsync

sub-address71[7] =0

Fsync

Fsync polarity

sub-address71[3]

Vsync polarity

sub-address71[4]

Fsync

Fig 4 : Digital Input Timing(625/50 system) in Master Mode

DVIN0~7

1440T

Cr718

Cb718

Y718

Y719

00 00

FF

Cb2Cr0

Cb0

Y0 Y1 Y2

INVALID

00 00 XY

FF

Hsync phase

sub-address71[2:0]

Hsync

clock

124T

T

262T

Hsync polarity

sub-address71[5]

+3T delay-4T delay

70(hex){[1:0]=01}

Y718 Y719

TP0~7

Cr718Cb718

Cb2

Cr0Cb0

INVALID

DVIN0~7

Y2

Y1Y0

INVALID

16-bit input mode

Cb718Cr718

Cr2

Cr0 Cb0

or

8-bit input mode

MC44722/3 Rev 0.23 3/24/'97

No.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

8

CSYNC

262261 1 2 3 4 5 6 7 8 9 10 11 21 22 23

Fig 7 : Sync Timing::525/60 Non-interlaced System in Master Mode

CSYNC

310 311 312 1 2 3 4 6 7 8

21 22 23

5309308

Vsync

Hsync

Vsync

Hsync

Fig 8 : Sync Timing::625/50 Non-interlaced System in Master Mode

9

sub-address71[7] =1

Fsync polarity

sub-address71[3]

Vsync polarity

sub-address71[4]

Fsync

Fsync polarity

sub-address71[3]

Vsync polarity

sub-address71[4]

Fsync

sub-address71[7] =1

CSYNC

623 624 625 1 2 3 4 6 7 8

21 22 23

CSYNC

311 312 313 314 315 316 317 318 319 320 321

334 335

5622621

310309

Vsync

Hsync

Vsync

Hsync

Fig 6 : Sync Timing::625/50 Interlaced System in Master Mode

9

Fsync

Fsync polarity

sub-address71[3]

Vsync polarity

sub-address71[4]

Fsync

sub-address71[7] =0

MC44722/3 Rev 0.23 3/24/'97

No.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

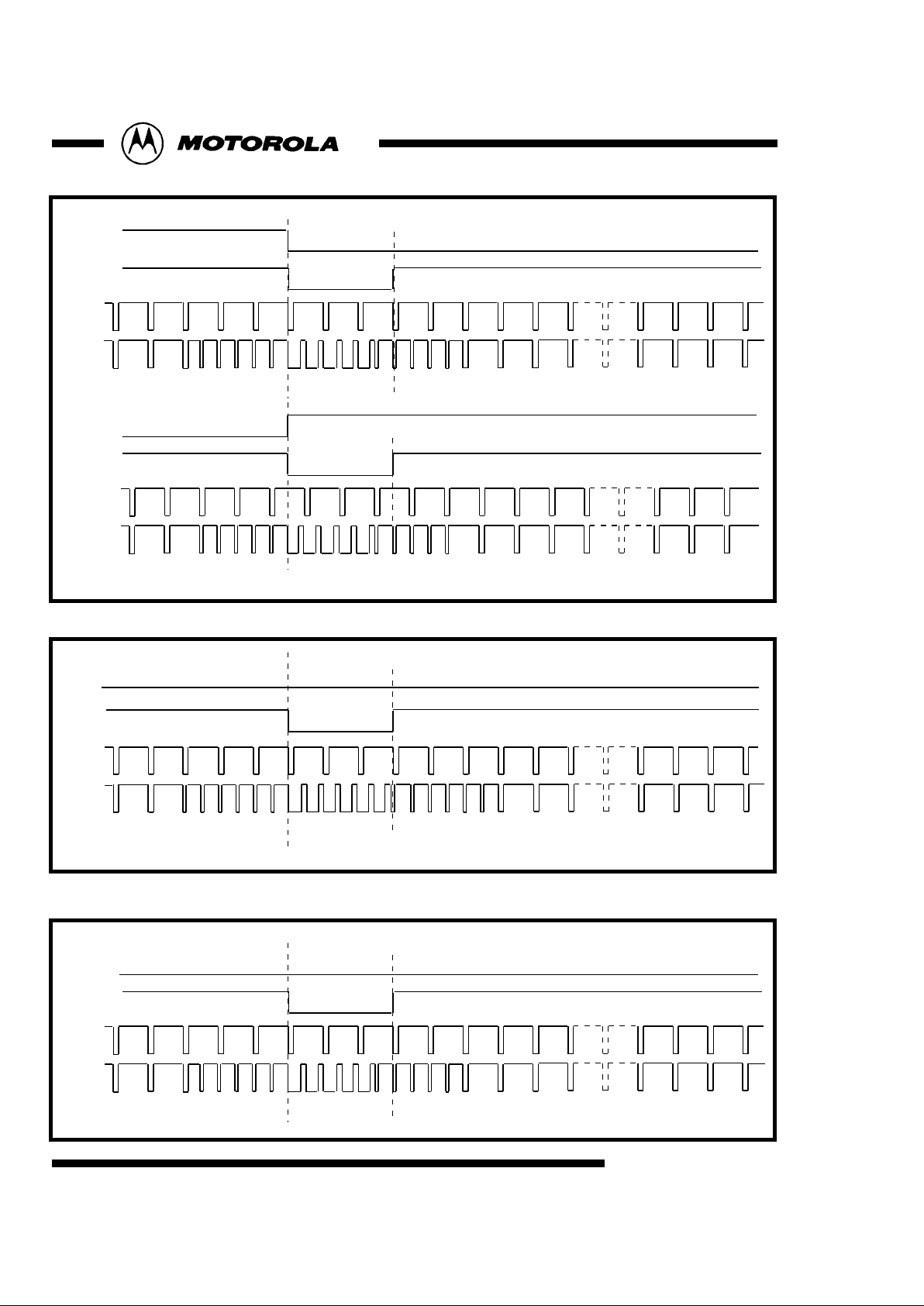

Fig 10 : Sync Timing::525/60 Interlaced System in Slave Mode

Vsync

Hsync

Fsync

Vsync polarity

sub-address71[5]

CSYNC

3 4 5 6 7

Fsync polarity

sub-address71[4]

Odd field

CSYNC

Vsync

Hsync

Fsync

266 267 268 269

Even field

sub-address71[1:0] =10, 11

Hsync Delay

sub-address 7A[7:0], 71[3:0]

Internal Hsync

reset counter

9

Fig 9 : Analog Sync Timing::Rise and fall

2.37uS 29.41uS 27.04uS

4.74uS

0.148uS 0.148uS

63.56uS

NTSC

PAL

0.222uS

0.222uS

2.37uS

29.63uS 27.26uS

4.74uS

64.00uS

MC44722/3 Rev 0.23 3/24/'97

No.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

10

Fig 11 : Sync Timing::625/50 Interlaced System in Slave Mode

Vsync

Hsync

Fsync

Vsync polarity

sub-address71[5]

Fsync polarity

sub-address71[4]

Odd field

CSYNC

625 1 2 3 4

CSYNC

Vsync

Hsync

Fsync

313 314 315 316

Even field

sub-address71[1:0] =10, 11

Hsync Delay

sub-address 7A[7:0], 71[3:0]

Internal Hsync

reset counter

MC44722/3 Rev 0.23 3/24/'97

No.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

Chroma / Luma Encoding

The DVE de-multiplexes the 4:2:2 digital video data stream.

The de-multiplexed Y or Luma samples are interpolated (2X oversampled) at the clock rate. Offset

compensation is then added, next any VBI signals consisting of Closed-Caption and VID are added to the

appropriate lines, then finally composite sync pulses are added to the Luma signal.

(see figure 12.)

De-multiplexed component color CB and CR samples are interpolated (4X oversampled) at the clock rate.

Interpolating simplifies the output filter and allows more accurate encoding. The DVE generates the

necessary subcarrier color frequency for PAL or NTSC encoding from the 27Mhz system clock. This

color subcarrier is then modulated by the base band component color CB and CR signals to create the

video Chroma signal. (see figure 13.)

A 7.5 IRE pedestal is added for the 60Hz field rate. This can be added for the 50Hz field rate through

serial bus control. (see sub-address register descriptions)

11

CVBS and S-VIDEO or YCbCr Outputs

The internal digital video signals drive 10-bit D/A converters. Converter outputs are bi-directional current

sources where the current is proportional to the digital data with reference to the IBIAS reference current. The

pins CVBS/Cb, Y and C/Cr are the respective composite, Luma and Chroma or Y/Cb/Cr signal current source

pins. Also, each DACs can drive 75ohm load register.

(see "Application Diagram" and "sub-address register descriptions".)

Bias Current Gain

DACs can be switched off through serial bus control to reduce power consumption. Both outputs of unused

DACs should be connected to ground through a resister to avoid charge buildup.

Loading...

Loading...