Motorola MC44463B Datasheet

SEMICONDUCTOR

TECHNICAL DATA

REPLAY AND MULTIPLE

PICTURE–IN–PICTURE

(PIP) CONTROLLER

B SUFFIX

PLASTIC PACKAGE

CASE 859

(SDIP)

56

1

Order this document from Analog Marketing

Device

Operating

Temperature Range

Package

ORDERING INFORMATION

MC44463B TJ = –65° to +150°C SDIP

1

MOTOROLA ANALOG IC DEVICE DATA

The MC44463 Picture–In–Picture (PIP) controller is a low cost member of

a family of high performance PIP controllers and video processors for

television. It is a follow–up to the MC44461 PIP, in which two additional

modes of operation have been added. A replay mode is provided, which

captures several seconds of the main picture for replay in four different

speeds. The capture time is programmable in four resolutions (ratio of

captured fields to total fields), which trade the number of fields captured to

the length of replay time. The second additional mode provides for multiple

small picture overlays from a second non–synchronized source. The number

of PIP images is 3 for the 1/9 screen area and 4 for the 1/16 screen area.

Like the MC44461 this is NTSC compatible, I2C bus controlled and available

in the 56–pin shrink dip (SDIP) package.

The main features of the MC44463 are:

• Three PIP Functional Modes: Standard Single Active PIP Mode, Up to 8

Seconds of Capture and Replay Mode, and a 3 or 4 Multiple PIP Mode –

Vertical Stacked with 1 Active at Any One Time

• 4 Capture Resolutions – 1 out of 10, 1:8, 1:6, 1:4. 4 Playback Speeds =

1 Times Acquire Speed; 1/2; 1/4; 1/8

• Full 2 Frame Store for the Single PIP Removes the Rolling

Store/Playback Memory Interference – “Joint Line”

• External Memory for Replay and Multiple Modes: 4 Meg and 16 Meg

• Two NTSC CVBS Inputs – Switchable Main and PIP Video Signals

• Single NTSC CVBS Output Allows Simple TV Chassis Integration

• Two PIP Sizes; 1/16 and 1/9 Screen Area – Freeze Field Feature

• Variable PIP Position in 64–X by 64–Y Steps

• PIP Border with Programmable Color

• Programmable PIP Tint and Saturation Control

• Automatic Main to PIP Contrast Balance

• Vertical Filter

• I

2

C Bus Control – No External Variable Adjustments Needed

• Operates from a Single 5.0 V Supply

• Economical 56–Pin Shrink DIP Package

Composite Video Simplified System Diagram

Video

Processor

CV

1

PIP

MC44463

IIC

Tuner/IF

Back Panel

Composite

Video Input

R

G

B

CV

2

CV CV

in

4

Meg

Memory

This document contains information on a product under development. Motorola reserves the

right to change or discontinue this product without notice.

Motorola, Inc. 1996 Issue 1

MC44463

2

MOTOROLA ANALOG IC DEVICE DATA

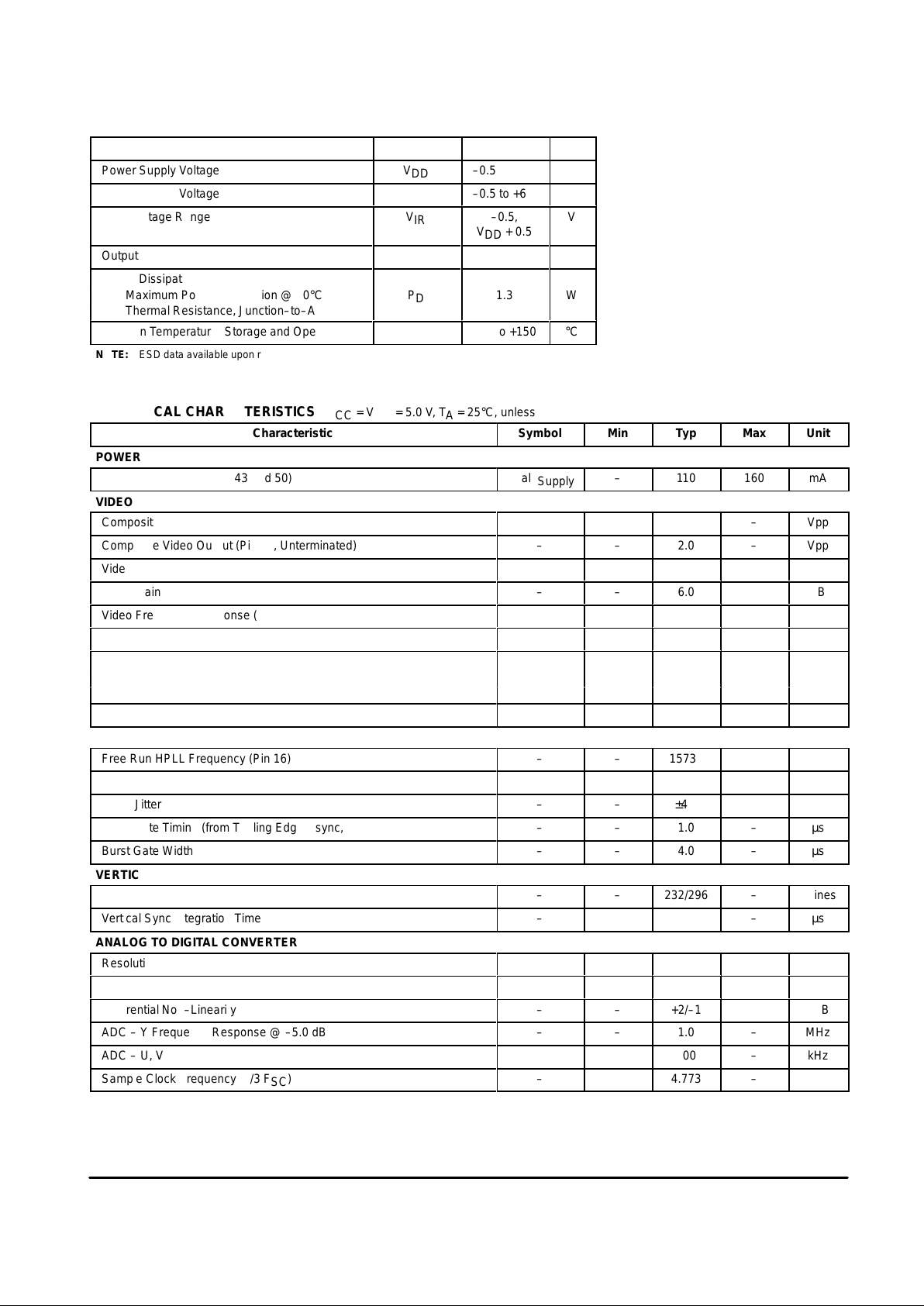

MAXIMUM RATINGS

Rating Symbol Value Unit

Power Supply Voltage

V

DD

–0.5 to +6.0

V

Power Supply Voltage

V

CC

–0.5 to +6.0

V

ББББББББББББ

Á

Input Voltage Range

ÁÁ

Á

V

IR

ÁÁÁ

Á

–0.5,

V

DD

+ 0.5

Á

Á

V

Output Current

I

O

160

mA

Power Dissipation

Maximum Power Dissipation @ 70°C

P

D

1.3

W

Thermal Resistance, Junction–to–Air

R

θJA

59

°C/W

Junction T emperature (Storage and Operating)

T

J

–65 to +150

°C

NOTE: ESD data available upon request.

ELECTRICAL CHARACTERISTICS (V

CC

= VDD = 5.0 V , TA = 25°C, unless otherwise noted.)

Characteristic

Symbol Min Typ Max Unit

POWER SUPPLY

Total Supply (Pins 8, 15, 43 and 50)

Total I

Supply

–

110

160

ÁÁÁ

mA

VIDEO

Composite Video Input (Pin 34 or 36)

CVi

–

1.0

–

ÁÁÁ

Vpp

Composite Video Output (Pin 49, Unterminated)

–

–

2.0

–

ÁÁÁ

Vpp

Video Output DC Level (Sync Tip)

–

–

1.0

–

ÁÁÁ

Vdc

Video Gain

–

–

6.0

–

ÁÁÁ

dB

Video Frequency Response (Main Video to –1.0 dB)

–

–

10

–

ÁÁÁ

MHz

Color Bar Accuracy

–

–

±4.0

–

ÁÁÁ

deg

Video Crosstalk (@ 75% Color Bars)

–

ÁÁÁ

dB

Main to PIP

–

55

–

ÁÁÁ

PIP to Main

–

55

–

БББББББББББББББББ

Output Impedance

ÁÁÁ–ÁÁ–ÁÁ

5.0

ÁÁ

–

ÁÁÁ

ÁÁ

Ω

HORIZONTAL TIMEBASE

Free Run HPLL Frequency (Pin 16)

–

–

15734

–

ÁÁÁ

Hz

HPLL Pull–In Range

–

–

±400

–

ÁÁÁ

Hz

HPLL Jitter

–

–

±4.0

–

ÁÁÁ

ns

Burst Gate Timing (from Trailing Edge Hsync, Pin 24)

–

–

1.0

–

ÁÁÁ

µs

Burst Gate Width

–

–

4.0

–

ÁÁÁ

µs

VERTICAL TIMEBASE

Vertical Countdown Window

–

–

232/296

–

ÁÁÁ

H lines

Vertical Sync Integration T ime

–

–

31

–

ÁÁÁ

µs

ANALOG TO DIGITAL CONVERTER

Resolution

–

–

–

6

ÁÁÁ

Bits

Integral Non–Linearity

–

–

±1

–

ÁÁÁ

LSB

Differential Non–Linearity

–

–

+2/–1

–

ÁÁÁ

LSB

ADC – Y Frequency Response @ –5.0 dB

–

–

1.0

–

ÁÁÁ

MHz

ADC – U, V Frequency Response @ –5.0 dB

–

–

200

–

ÁÁÁ

kHz

Sample Clock Frequency (4/3 FSC)

–

–

4.773

–

ÁÁÁ

MHz

MC44463

3

MOTOROLA ANALOG IC DEVICE DATA

ELECTRICAL CHARACTERISTICS (continued) (V

CC

= VDD = 5.0 V , TA = 25°C, unless otherwise noted.)

Characteristic UnitMaxTypMinSymbol

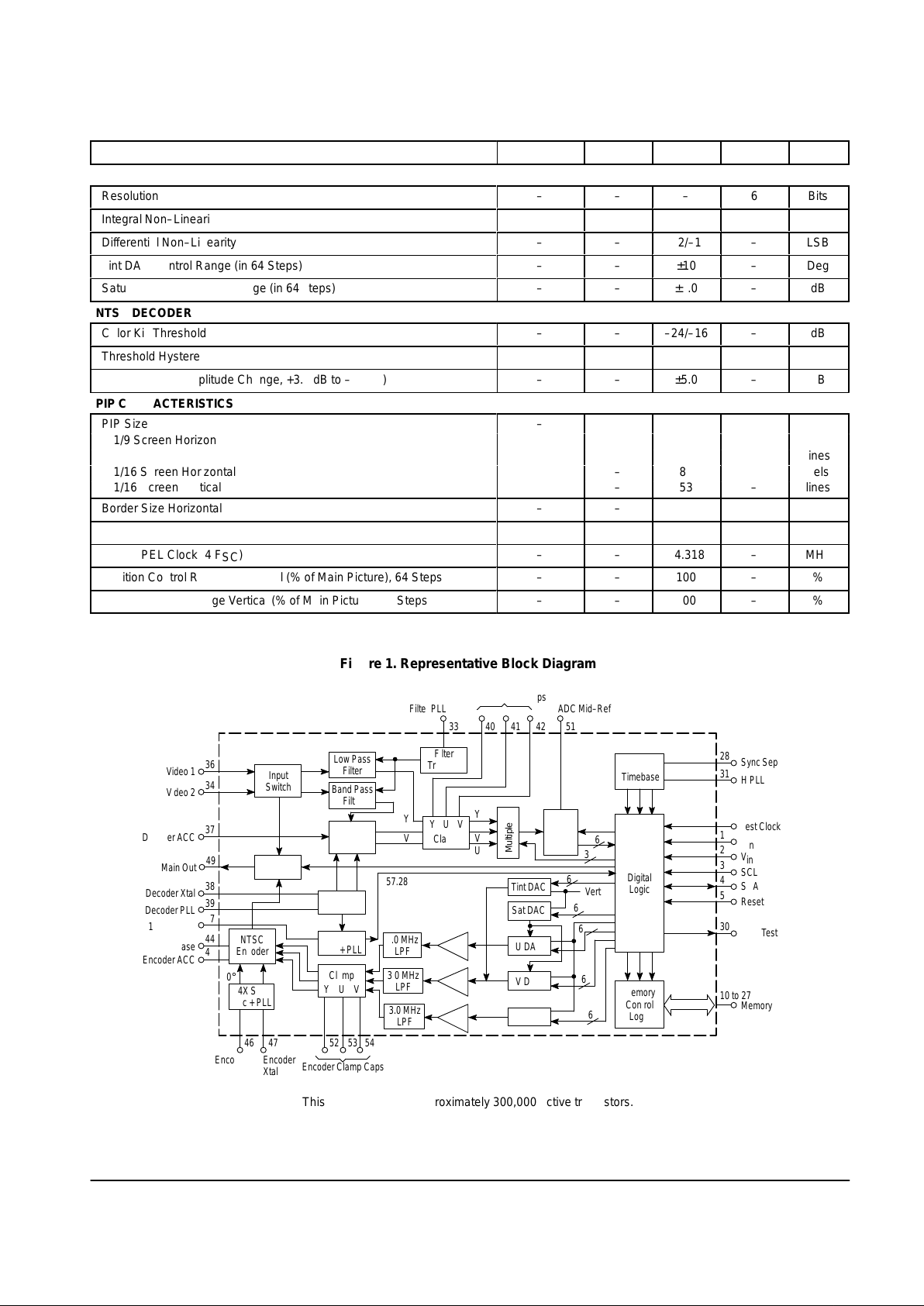

DIGITAL TO ANALOG CONVERTER

Resolution

–

–

–

6

ÁÁÁ

Bits

Integral Non–Linearity

–

–

±1

–

ÁÁÁ

LSB

Differential Non–Linearity

–

–

+2/–1

–

ÁÁÁ

LSB

Tint DAC Control Range (in 64 Steps)

–

–

±10

–

ÁÁÁ

Deg

Saturation DAC Control Range (in 64 steps)

–

–

±6.0

–

ÁÁÁ

dB

NTSC DECODER

Color Kill Threshold

–

–

–24/–16

–

ÁÁÁ

dB

Threshold Hysteresis

–

–

±1.0

–

ÁÁÁ

dB

ACC (Chroma Amplitude Change, +3.0 dB to –12 dB)

–

–

±5.0

–

ÁÁÁ

dB

PIP CHARACTERISTICS

PIP Size

–

ÁÁÁ

1/9 Screen Horizontal

–

114

–

ÁÁÁ

pels

1/9 Screen Vertical

–

71

–

ÁÁÁ

lines

1/16 Screen Horizontal

–

84

–

ÁÁÁ

pels

1/16 Screen Vertical

–

53

–

ÁÁÁ

lines

Border Size Horizontal

–

–

3

–

ÁÁÁ

pels

Border Size Vertical

–

–

2

–

ÁÁÁ

lines

Output PEL Clock (4 FSC)

–

–

14.318

–

ÁÁÁ

MHz

Position Control Range Horizontal (% of Main Picture), 64 Steps

–

–

100

–

ÁÁÁ

%

Position Control Range Vertical (% of Main Picture), 64 Steps

–

–

100

–

ÁÁÁ

%

Figure 1. Representative Block Diagram

This device contains approximately 300,000 active transistors.

Y

V

U

YUV

Clamp

Input

Switch

Low Pass

Filter

Band Pass

Filter

NTSC

Decoder

PIP

Switch

4X S/C

Osc + PLL

16X S/C

Osc + PLL

YUV

Clamp

NTSC

Encoder

4X S/C

Osc + PLL

Filter

Tracking

6–Bit

ADC

H and V

Timebase

Digital

Logic

Tint DAC

Sat DAC

V DAC

Y DAC

3.0 MHz

LPF

3.0 MHz

LPF

3.0 MHz

LPF

33

Y

V

U

40 41 42 51

28

31

1

2

3

4

5

30

5453524746

6

6

6

6

6

3

6

Vert

57.28 MHz

90

°

0

°

14.32 MHz

90

°

0

°

36

34

37

49

38

39

7

44

45

Multiplexer

Video 1

Video 2

Decoder ACC

Main Out

Decoder Xtal

Decoder PLL

16 FSC PLL

Encoder Phase

Encoder ACC

Sync Sep

H PLL

H

in

V

in

SCL

SDA

Reset

Multi T est

Encoder Clamp Caps

Encoder

Xtal

Encoder

PLL

Decoder Clamp Caps

ADC Mid–RefFilter PLL

U DAC

Memory

Control

Logic

6

T est Clock

10 to 27

Memory

Loading...

Loading...