Motorola MC14554BCL, MC14554BCP, MC14554BD Datasheet

MOTOROLA CMOS LOGIC DATA

1

MC14554B

The MC14554B 2 x 2–bit parallel binary multiplier is constructed with

complementary MOS (CMOS) enhancement mode devices. The multiplier

can perform the multiplication of two binary numbers and simultaneously add

two o ther b inary n umbers to t he p roduct. T he M C14554B h as t wo

multiplicand inputs (X0 and X1), two multiplier inputs (Y0 and Y1), f ive

cascading or adding inputs (K0, K1, M0, M1, and M2), and five sum and

carry outputs (S0, S1, S2, C1 [S3], and C0). The basic multiplier can be

expanded into a straightforward m–bit by n–bit parallel multiplier without

additional logic elements.

Application areas include arithmetic processing (multiplying/adding,

obtaining square roots, polynomial evaluation, obtaining reciprocals, and

dividing), Fast Fourier Transform processing, digital filtering, communications (convolution and correlation), and process and machine controls.

• Diode Protection on All Inputs

• All Outputs Buffered

• Straight–forward m–Bit By n–Bit Expansion

• No Additional Logic Elements Needed for Expansion

• Multiplies and Adds Simultaneously

• Positive Logic Design

• Supply Voltage Range = 3.0 Vdc to 18 Vdc

• Capable of Driving Two Low–Power TTL Loads or One Low–Power

Schottky TTL Load Over the Rated Temperature Range

MAXIMUM RATINGS* (Voltages Referenced to V

SS

)

Symbol

Parameter Value Unit

V

DD

DC Supply Voltage – 0.5 to + 18.0 V

Vin, V

out

Input or Output Voltage (DC or Transient) – 0.5 to VDD + 0.5 V

Iin, I

out

Input or Output Current (DC or Transient),

per Pin

± 10 mA

P

D

Power Dissipation, per Package† 500 mW

T

stg

Storage Temperature – 65 to + 150

_

C

T

L

Lead Temperature (8–Second Soldering) 260

_

C

*Maximum Ratings are those values beyond which damage to the device may occur.

†Temperature Derating:

Plastic “P and D/DW” Packages: – 7.0 mW/_C From 65_C To 125_C

Ceramic “L” Packages: – 12 mW/_C From 100_C To 125_C

PIN ASSIGNMENT

13

14

15

16

9

10

11

125

4

3

2

1

8

7

6

K0

X1

X0

Y0

V

DD

S1

K1

S0

C0

M1

M0

Y1

V

SS

S2

C1 (S3)

M2

SEMICONDUCTOR TECHNICAL DATA

Motorola, Inc. 1995

REV 3

1/94

This device contains protection circuitry to

guard against damage due to high static

voltages or electric fields. However, precautions must be taken to avoid applications of

any voltage higher than maximum rated voltages to this high–impedance circuit. For proper

operation, Vin and V

out

should be constrained

to the range VSS v (Vin or V

out

) v VDD.

Unused inputs must always be tied to an

appropriate logic voltage level (e.g., either V

SS

or VDD). Unused outputs must be left open.

L SUFFIX

CERAMIC

CASE 620

ORDERING INFORMATION

MC14XXXBCP Plastic

MC14XXXBCL Ceramic

MC14XXXBD SOIC

TA = – 55° to 125°C for all packages.

P SUFFIX

PLASTIC

CASE 648

D SUFFIX

SOIC

CASE 751B

S = (X x Y) + K + M

Where:

x Means Arithmetic Times.

+ Means Arithmetic Plus.

S = S3 S2 S1 S0, X = X1X0, Y = Y1Y0,

K = K1 K0, M = M1 M0 (Binary Numbers).

Example:

Given: X = 2(1), Y = 3(11)

K = 1(01), M = 2(10)

Then: S = (2 x 3) + 1 + 2 = 9

S = (10 x 11) + 01 + 10 = 1001

EQUATIONS

NOTE: C0 connected to M2 for this size

multiplier. See general expansion

diagram for other size multipliers.

MOTOROLA CMOS LOGIC DATAMC14554B

2

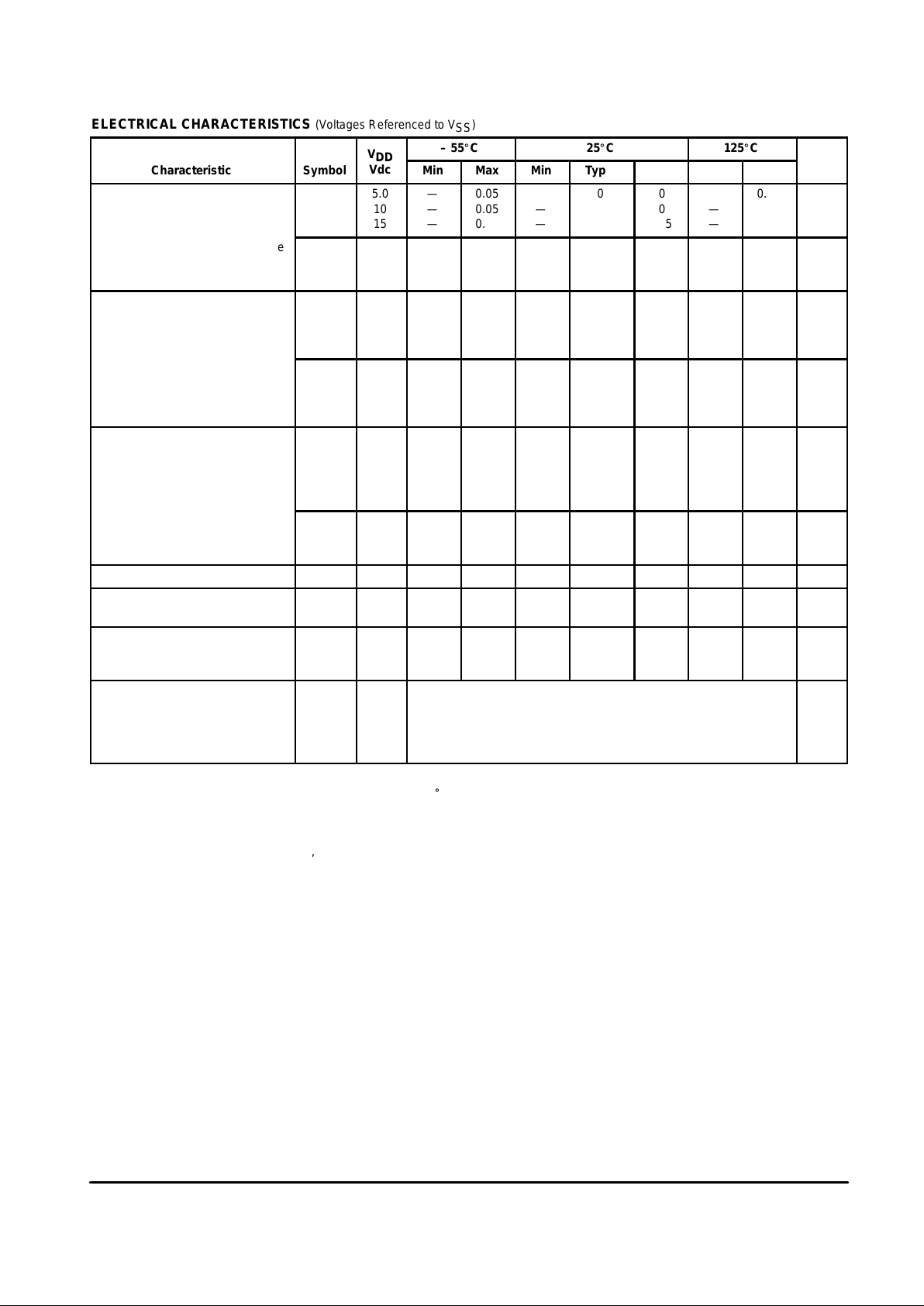

ELECTRICAL CHARACTERISTICS (Voltages Referenced to V

SS

)

V

– 55_C 25_C 125_C

Characteristic

Symbol

V

DD

Vdc

Min Max Min Typ # Max Min Max

Unit

Output Voltage “0” Level

Vin = VDD or 0

V

OL

5.0

10

15

—

—

—

0.05

0.05

0.05

—

—

—

0

0

0

0.05

0.05

0.05

—

—

—

0.05

0.05

0.05

Vdc

“1” Level

Vin = 0 or V

DD

V

OH

5.0

10

15

4.95

9.95

14.95

—

—

—

4.95

9.95

14.95

5.0

10

15

—

—

—

4.95

9.95

14.95

—

—

—

Vdc

Input Voltage “0” Level

(VO = 4.5 or 0.5 Vdc)

(VO = 9.0 or 1.0 Vdc)

(VO = 13.5 or 1.5 Vdc)

V

IL

5.0

10

15

—

—

—

1.5

3.0

4.0

—

—

—

2.25

4.50

6.75

1.5

3.0

4.0

—

—

—

1.5

3.0

4.0

Vdc

“1” Level

(VO = 0.5 or 4.5 Vdc)

(VO = 1.0 or 9.0 Vdc)

(VO = 1.5 or 13.5 Vdc)

V

IH

5.0

10

15

3.5

7.0

11

—

—

—

3.5

7.0

11

2.75

5.50

8.25

—

—

—

3.5

7.0

11

—

—

—

Vdc

Output Drive Current

(VOH = 2.5 Vdc) Source

(VOH = 4.6 Vdc)

(VOH = 9.5 Vdc)

(VOH = 13.5 Vdc)

I

OH

5.0

5.0

10

15

– 3.0

– 0.64

– 1.6

– 4.2

—

—

—

—

– 2.4

– 0.51

– 1.3

– 3.4

– 4.2

– 0.88

– 2.25

– 8.8

—

—

—

—

– 1.7

– 0.36

– 0.9

– 2.4

—

—

—

—

mAdc

(VOL = 0.4 Vdc) Sink

(VOL = 0.5 Vdc)

(VOL = 1.5 Vdc)

I

OL

5.0

10

15

0.64

1.6

4.2

—

—

—

0.51

1.3

3.4

0.88

2.25

8.8

—

—

—

0.36

0.9

2.4

—

—

—

mAdc

Input Current I

in

15 — ±0.1 — ±0.00001 ±0.1 — ±1.0 µAdc

Input Capacitance

(Vin = 0)

C

in

— — — — 5.0 7.5 — — pF

Quiescent Current

(Per Package)

I

DD

5.0

10

15

—

—

—

5.0

10

20

—

—

—

0.005

0.010

0.015

5.0

10

20

—

—

—

150

300

600

µAdc

Total Supply Current**†

(Dynamic plus Quiescent,

Per Package)

(CL = 50 pF on all outputs, all

buffers switching)

I

T

5.0

10

15

IT = (1.0 µA/kHz) f + I

DD

IT = (2.0 µA/kHz) f + I

DD

IT = (3.0 µA/kHz) f + I

DD

µAdc

#Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

**The formulas given are for the typical characteristics only at 25_C.

†To calculate total supply current at loads other than 50 pF:

IT(CL) = IT(50 pF) + (CL – 50) Vfk

where: IT is in µA (per package), CL in pF, V = (VDD – VSS) in volts, f in kHz is input frequency, and k = 0.0035.

Loading...

Loading...